# INSIGHTFUL PERFORMANCE ANALYSIS OF MANY-TASK RUNTIMES THROUGH TOOL-RUNTIME INTEGRATION

by

### NICHOLAS A. CHAIMOV

### **A DISSERTATION**

Presented to the Department of Computer and Information Science and the Graduate School of the University of Oregon in partial fulfillment of the requirements for the degree of Doctor of Philosophy

June 2017

### DISSERTATION APPROVAL PAGE

Student: Nicholas A. Chaimov

Title: Insightful Performance Analysis of Many-Task Runtimes through Tool-Runtime Integration

This dissertation has been accepted and approved in partial fulfillment of the requirements for the Doctor of Philosophy degree in the Department of Computer and Information Science by:

Allen D. Malony Chair

Boyana R. Norris Core Member Hank R. Childs Core Member

Gregory Bothun Institutional Representative

and

Scott L. Pratt Dean of the Graduate School

Original approval signatures are on file with the University of Oregon Graduate School.

Degree awarded June 2017

© 2017 Nicholas A. Chaimov

### DISSERTATION ABSTRACT

Nicholas A. Chaimov

Doctor of Philosophy

Department of Computer and Information Science

June 2017

Title: Insightful Performance Analysis of Many-Task Runtimes through Tool-Runtime Integration

Future supercomputers will require application developers to expose much more parallelism than current applications expose. In order to assist application developers in structuring their applications such that this is possible, new programming models and libraries are emerging, the *many-task runtimes*, to allow for the expression of orders of magnitude more parallelism than currently existing models.

This dissertation describes the challenges that these emerging many-task runtimes will place on performance analysis, and proposes deep integration between runtimes and performance tools as a means of producing correct, insightful, and actionable performance results. I show how tool-runtime integration can be used to aid programmer understanding of performance characteristics and to provide online performance feedback to the runtime for Unified Parallel C (UPC), High Performance ParalleX (HPX), Apache Spark, the Open Community Runtime, and the OpenMP runtime.

This dissertation includes previously published co-authored material.

### **CURRICULUM VITAE**

NAME OF AUTHOR: Nicholas A. Chaimov

### GRADUATE AND UNDERGRADUATE SCHOOLS ATTENDED:

University of Oregon, Eugene, OR Portland State University, Portland, OR Reed College, Portland, OR

### **DEGREES AWARDED:**

Doctor of Philosophy, Computer and Information Science, 2017, University of Oregon

Master of Science, Computer and Information Science, 2012, University of Oregon

Bachelor of Science, Computer and Information Science, 2010, University of Oregon

Bachelor of Science, Biology, 2007, University of Oregon

### AREAS OF SPECIAL INTEREST:

High-Performance Computing Scientific Computing Performance Monitoring

### PROFESSIONAL EXPERIENCE:

Graduate Research Fellow, Computer and Information Science, University of Oregon, 2010-2017

Software Engineering Intern, Intel Federal LLC, Summer 2016

Research Assistant, Lawrence Berkeley National Lab, Summer 2015

Research Assistant, Lawrence Berkeley National Lab, Summer 2014

### GRANTS, AWARDS AND HONORS:

- Gurdeep Pall Graduate Student Fellowship, University of Oregon, 2016

- Student Travel Grant, High Performance Distributed Computing (HPDC), 2016

- Member of 1st Place Graduate Team, Eugene Luks Programming Competition, University of Oregon, 2015

- Member of 1st Place Graduate Team, Eugene Luks Programming Competition, University of Oregon, 2012

- Member, Upsilon Pi Epsilon International Honor Society for the Computing and Information Disciplines, 2010-Present

### **PUBLICATIONS:**

- Nicholas Chaimov, Allen Malony, Shane Canon, Costin Iancu, Khaled Z Ibrahim, and Jay Srinivasan. "Scaling Spark on HPC Systems." *International Symposium on High-Performance Parallel and Distributed Computing* (HPDC). 2016.

- Nicholas Chaimov, Allen Malony, Costin Iancu, and Khaled Ibrahim. "Scaling Spark on Lustre." Workshop On Performance and Scalability of Storage Systems. 2016.

- **Nicholas Chaimov**, Allen Malony, Khaled Ibrahim, Costin Iancu, Shane Canon, and Jay Srinivasan. "Performance Evaluation of Apache Spark on Cray XC Systems." *Cray Users Group.* 2016.

- Md Abdullah Shahneous Bari, **Nicholas Chaimov**, Abid M Malik, Kevin A Huck, Barbara Chapman, Allen D. Malony, Osman Sarood. "ARCS: Adaptive Runtime Configuration Selection for Power-Constrained OpenMP Applications." *IEEE International Conference on Cluster Computing* (CLUSTER). 2016.

- Nicholas Chaimov, Khaled Ibrahim, Sam Williams and Costin Iancu. "Reaching Bandwidth Saturation Using Transparent Injection Parallelization." *International Journal of High Performance Computing Applications*. 2016.

- Kevin Huck, Allan Porterfield, **Nicholas Chaimov**, Hartmut Kaiser, Allen D. Malony, Thomas Sterling, and Rob Fowler. "An Autonomic Performance Environment for Exascale." *Supercomputing Frontiers and Innovation* 2, no. 3 (2015): 49-66.

- Robert Lim, Allen Malony, Boyana Norris, and **Nicholas Chaimov**. "Identifying Optimization Opportunities Within Kernel Execution in GPU Codes." *Euro-Par 2015: Parallel Processing Workshops*, pp. 185–196. 2015.

- Nicholas Chaimov, Khaled Ibrahim, Sam Williams and Costin Iancu. "Exploiting Communication Concurrency on High Performance Computing Systems." International Workshop on Programming Models and Applications for Multicores and Manycores (PMAM). 2015.

- Nicholas Chaimov, Boyana Norris, and Allen D. Malony. "Toward Multi-target Autotuning for Accelerators." *International Conference on Parallel and Distributed Systems* (ICPADS). 2014.

- Nicholas Chaimov, Boyana Norris, and Allen D. Malony. "Integration and Synthesis for Automated Performance Tuning: the SYNAPT Project." *International Workshop on Automatic Performance Tuning* (iWAPT). 2014.

- Nicholas Chaimov, Scott Biersdorff, and Allen D. Malony. "Tools for machine-learning-based empirical autotuning and specialization." *International Journal of High Performance Computing Applications* 27.4 (2013): 403-411.

### ACKNOWLEDGEMENTS

I thank my advisor, Prof. Allen Malony, for his help with research, with identifying research areas, with securing interesting and useful internships, and, most of all, for convincing me to pursue a PhD. I also thank Prof. Hank Childs and Prof. Boyana Norris for their help with my research, as well as Sameer Shende and Kevin Huck of the Performance Research Lab. I thank my collaborators at Lawrence Berkeley National Lab: Costin Iancu, Khaled Ibrahim, and Sam Williams; and my collaborators at Intel: Bala Seshasayee, Romain Cledat, Bryan Pawlowski, and Nick Pepperling.

Parts of this document were supported by the DOE Office of Advanced Scientific Computing Research (contract number DE-AC02-05CH11231). Parts of this document are based upon work supported by the Department of Energy Office of Science under Award Number DE-SC0008717. Support for this work was provided through the Scientific Discovery through Advanced Computing (SciDAC) program funded by U.S. Department of Energy, Office of Science, Advanced Scientific Computing Research (and Basic Energy Sciences/Biological and Environmental Research/High Energy Physics/Fusion Energy Sciences/Nuclear Physics) under award numbers DE-SC0008638, DE-SC0008704, DE-FG02-11ER26050 and DE-SC0006925. This research used resources of the National Energy Research Scientific Computing Center, a DOE Office of Science User Facility supported by the Office of Science of the U.S. Department of Energy under Contract No.

DE-AC02-05CH11231. This research used resources of the Oak Ridge Leadership Computing Facility at the Oak Ridge National Laboratory, which is supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC05-00OR22725. This work was partially supported by the Intel Parallel Computing Center at Lawrence Berkeley National Laboratory - Lustre.

# TABLE OF CONTENTS

| Chapter |       |                                                  | Pag | e   |

|---------|-------|--------------------------------------------------|-----|-----|

| I.      | INTRO | ODUCTION                                         |     | 1   |

|         | 1.1.  | Thesis Statement                                 |     | 2   |

|         | 1.2.  | Dissertation Outline                             |     | 5   |

|         | 1.3.  | Coauthored Material                              |     | 11  |

| II.     | BACK  | GROUND AND RELATED WORK                          |     | 12  |

|         | 2.1.  | Current Programming Models                       |     | 13  |

|         | 2.2.  | Capturing Performance Data                       |     | 23  |

|         | 2.3.  | Autotuning                                       |     | 26  |

|         | 2.4.  | Performance Modeling                             |     | 37  |

|         | 2.5.  | Performance Diagnosis                            |     | 43  |

|         | 2.6.  | Exascale Computing and Future Programming Models |     | 53  |

|         | 2.7.  | Conclusion                                       |     | 69  |

| III.    | ONLI  | NE COMMUNICATIONS ADAPTATION IN UPC              |     | 72  |

|         | 3.1.  | Introduction                                     |     | 72  |

|         | 3.2.  | Maximizing Message Concurrency                   |     | 73  |

|         | 3.3.  | Communication and Concurrency                    |     | 76  |

|         | 3.4.  | Runtime Design                                   |     | 79  |

|         | 3.5.  | Network Performance and Saturation               |     | 85  |

|         | 3.6.  | Parallelizing Injection in Applications          |     | 95  |

|         | 3.7.  | Discussion                                       |     | 105 |

|         | 3.8.  | Other Related Work                               |     | 107 |

|         | 3.9.  | Conclusion                                       |     | 108 |

| Cha | ıpter |                                                            | Page | 9           |

|-----|-------|------------------------------------------------------------|------|-------------|

|     | 3.10. | Bridge                                                     |      | 109         |

| IV. |       | ORMANCE MEASUREMENT AND ONLINE CATION IN HPX               |      | 112         |

|     | 4.1.  | Introduction                                               |      | 112         |

|     | 4.2.  | APEX Design                                                |      | 113         |

|     | 4.3.  | Experimental Results                                       |      | 119         |

|     | 4.4.  | Tuning with a Global View                                  |      | 123         |

|     | 4.5.  | Conclusion                                                 |      | 124         |

|     | 4.6.  | Bridge                                                     |      | 125         |

| V.  | STORA | AGE OPTIMIZATION AND VARIABILITY IN SPARK                  |      | 127         |

|     | 5.1.  | Introduction                                               |      | 127         |

|     | 5.2.  | Motivation                                                 |      | 128         |

|     | 5.3.  | Spark Architecture                                         |      | 132         |

|     | 5.4.  | Experimental Setup                                         |      | 139         |

|     | 5.5.  | Single Node Performance                                    |      | 142         |

|     | 5.6.  | Scaling Concerns                                           |      | 143         |

|     | 5.7.  | Improving Shuffle Scalability With Better Block Management |      | 159         |

|     | 5.8.  | Spark-Perf Benchmark on Lustre                             |      | 162         |

|     | 5.9.  | Localizing Metadata Operations with Shifter                |      | 165         |

|     | 5.10. | Input Disk I/O versus Shuffle Disk I/O                     |      | 166         |

|     | 5.11. | Localizing JVM and Spark Runtime Metadata Accesses         |      | 168         |

|     | 5.12. | Xeon Phi and the Effect of Straggler Tasks                 |      | 169         |

|     | 5.13. | Network Latency                                            |      | <b>17</b> 0 |

|     | 5.14. | Discussion                                                 |      | 171         |

|     | 5.15. | Related Work                                               |      | 174         |

|     | 5.16. | Conclusion                                                 |      | 175         |

| Cha  | Chapter |                             | Page | e   |

|------|---------|-----------------------------|------|-----|

|      | 5.17.   | Bridge                      |      | 176 |

| VI.  | STRA    | GGLER ANALYSIS IN OCR       |      | 194 |

|      | 6.1.    | Introduction                |      | 194 |

|      | 6.2.    | APEX-OCR Integration        |      | 195 |

|      | 6.3.    | Task Eligibility            |      | 200 |

|      | 6.4.    | Tracing OCR Applications    |      | 200 |

|      | 6.5.    | Blame Analysis              |      | 203 |

|      | 6.6.    | Load Balancing              |      | 205 |

|      | 6.7.    | Conclusion                  |      | 206 |

|      | 6.8.    | Bridge                      |      | 208 |

| VII. | OPTI    | MIZING SCHEDULING IN OPENMP |      | 209 |

|      | 7.1.    | Introduction                |      | 209 |

|      | 7.2.    | Motivation                  |      | 210 |

|      | 7.3.    | Framework                   |      | 214 |

|      | 7.4.    | Experiment Design           |      | 218 |

|      | 7.5.    | Related Work                |      | 236 |

|      | 7.6.    | Conclusions                 |      | 238 |

|      | 7.7.    | Bridge                      |      | 239 |

| VIII | . CON   | CLUSIONS                    |      | 240 |

| REF  | ERENC   | CES CITED                   |      | 242 |

# LIST OF FIGURES

| ire                                                  | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Comparison of fork-join and task parallelism         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ·                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| -                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| - 1                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

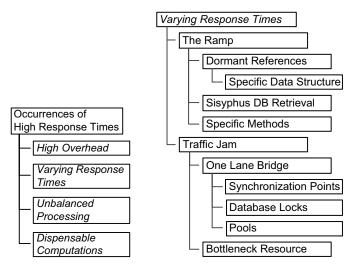

| Examples of the Paradyn "why" and "when" hierarchies |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Architecture of the PERISCOPE system                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Symptom and cause hierarchies                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

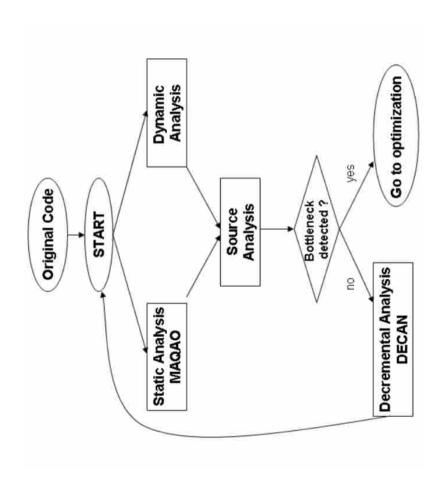

| Methodology of DECAN                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

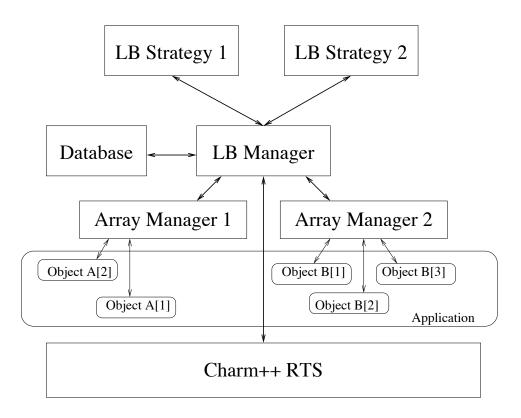

| Architecture of the Charm++ load balancer            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Decision procedure used by PICS                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

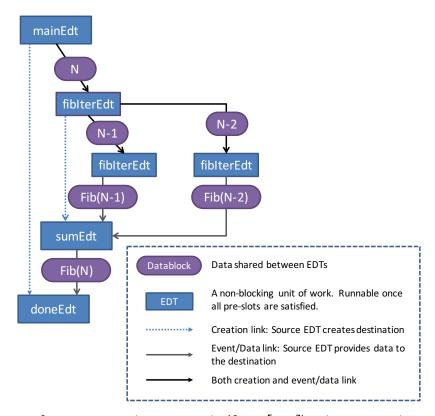

| DAG for an OCR Fibonacci code                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

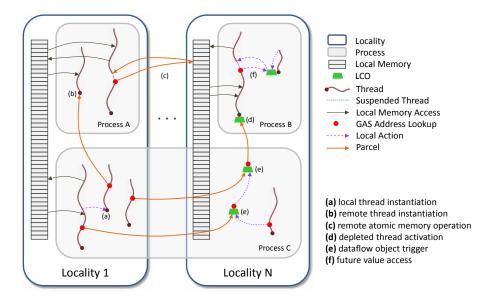

| Computational model of HPX                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

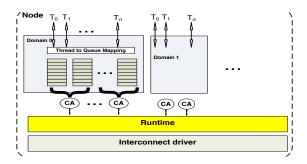

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

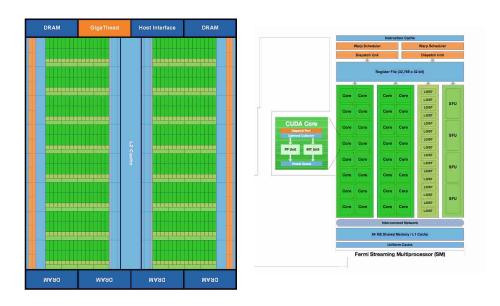

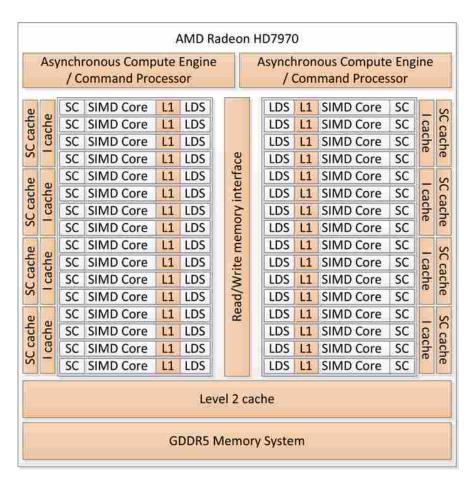

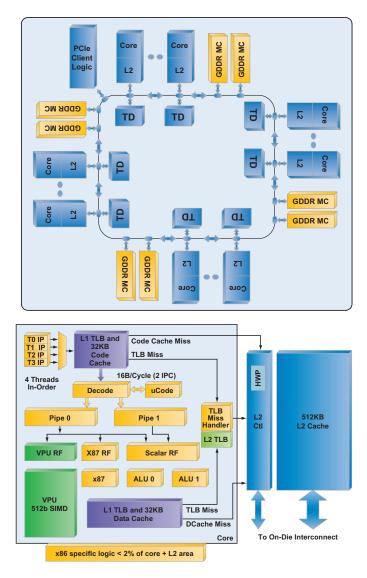

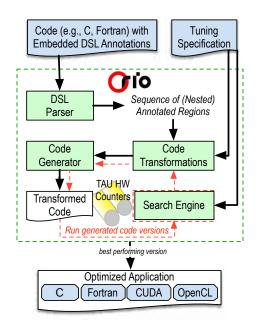

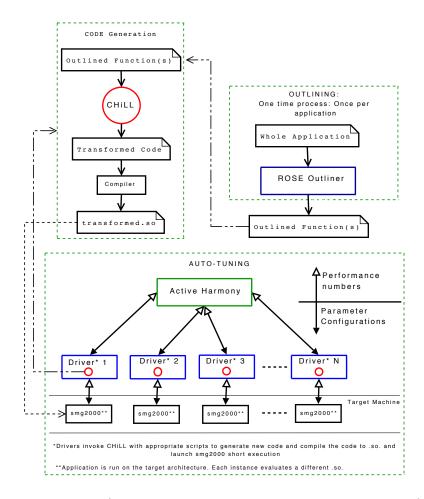

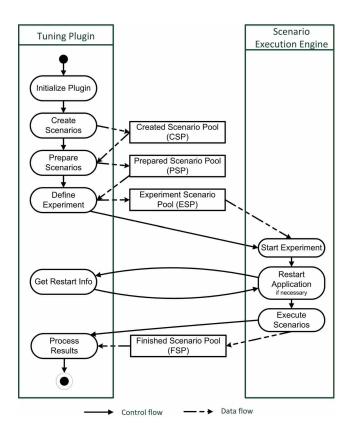

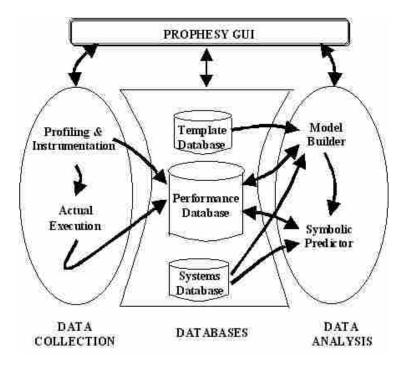

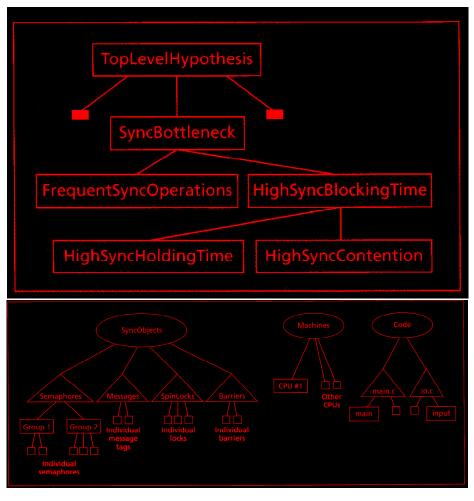

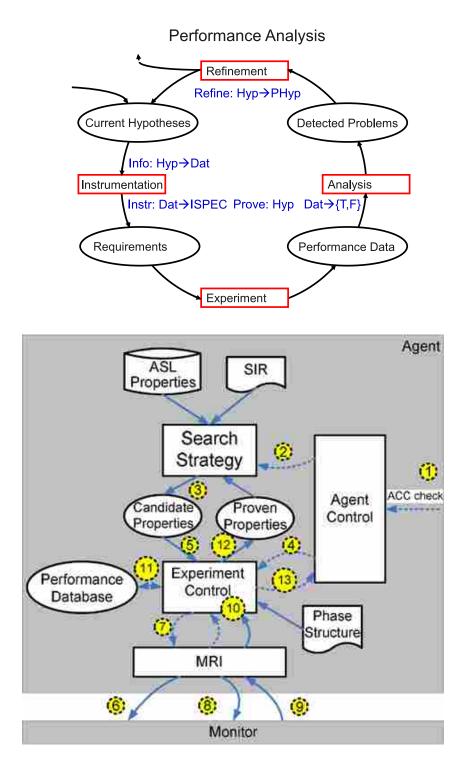

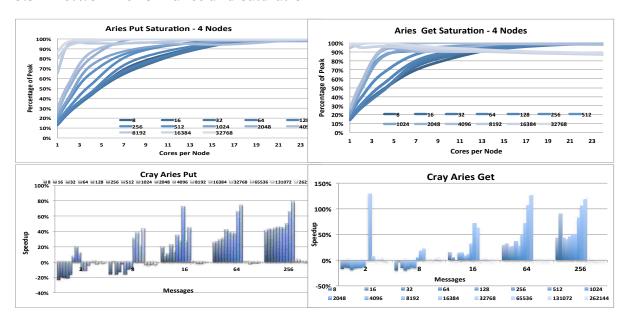

|                                                      | Comparison of fork-join and task parallelism.  The fork-join model as used in OpenMP.  The Communicating Sequential Processes model as used in MPI.  Architecture of the NVIDIA Fermi GPU family.  Architecture of the AMD Radeon 7000 GPU family.  Architecture of the Intel Xeon Phi Knights Corner family.  Hypothetical architecture for a unified autotuning system.  Architecture of Orio.  Architecture of an autotuning system using ROSE.  Architecture of the Periscope Tuning Framework.  Architecture of Prophesy.  Architecture of the Brainy data structure selection system.  Examples of the Paradyn "why" and "when" hierarchies.  Architecture of the PERISCOPE system.  Symptom and cause hierarchies.  Methodology of DECAN.  Architecture of the Charm++ load balancer.  Decision procedure used by PICS.  DAG for an OCR Fibonacci code.  Computational model of HPX.  Runtime architecture of THOR. | Comparison of fork-join and task parallelism.  The fork-join model as used in OpenMP.  The Communicating Sequential Processes model as used in MPI.  Architecture of the NVIDIA Fermi GPU family.  Architecture of the AMD Radeon 7000 GPU family.  Architecture of the Intel Xeon Phi Knights Corner family.  Hypothetical architecture for a unified autotuning system.  Architecture of Orio.  Architecture of an autotuning system using ROSE.  Architecture of the Periscope Tuning Framework.  Architecture of Prophesy.  Architecture of the Brainy data structure selection system.  Examples of the Paradyn "why" and "when" hierarchies.  Architecture of the PERISCOPE system.  Symptom and cause hierarchies.  Methodology of DECAN.  Architecture of the Charm++ load balancer.  Decision procedure used by PICS.  DAG for an OCR Fibonacci code.  Computational model of HPX.  Runtime architecture of THOR.  Cray Aries network saturation. |

| Figu | ire                                                                                           | Pag | e   |

|------|-----------------------------------------------------------------------------------------------|-----|-----|

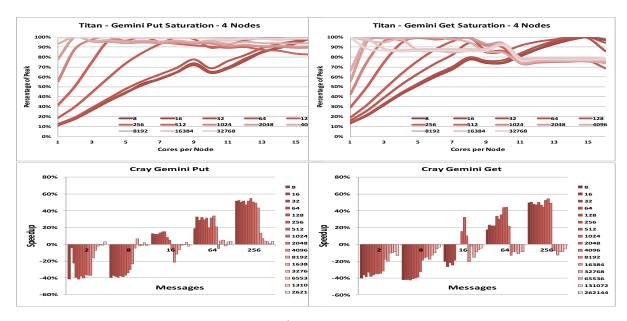

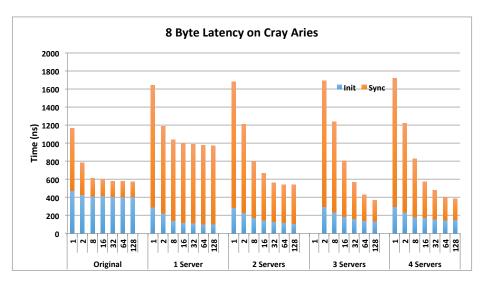

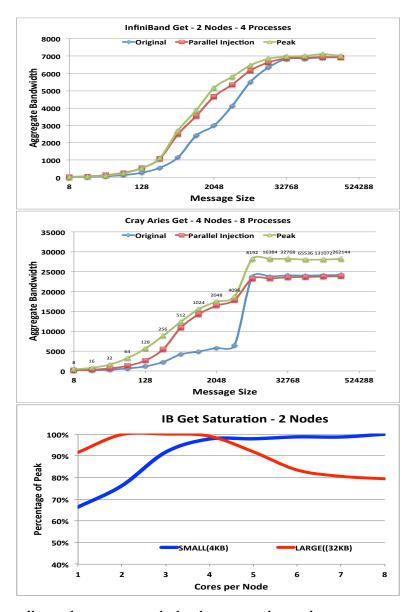

| 23.  | Cray Gemini network saturation                                                                |     | 86  |

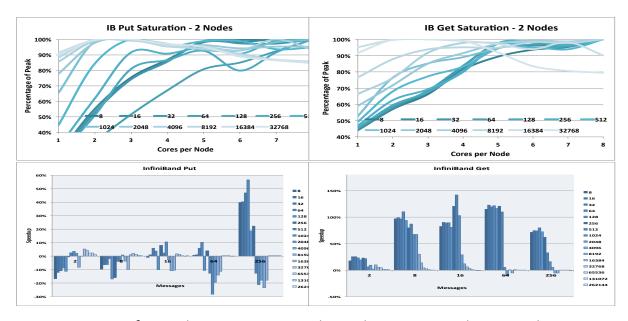

| 24.  | InfiniBand network saturation                                                                 |     | 86  |

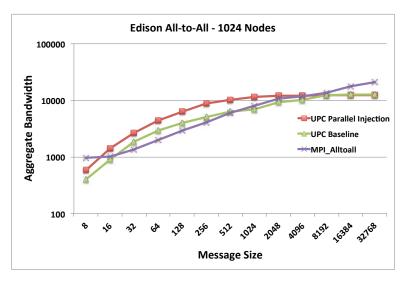

| 25.  | Speedup with parallel injection for an all-to-all microbenchmark                              |     | 94  |

| 26.  | The exchange boundary communication phase                                                     |     | 97  |

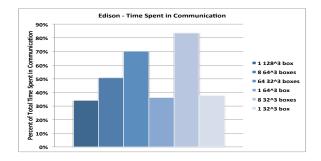

| 27.  | Fraction of time spent communicating in miniGMG                                               |     | 97  |

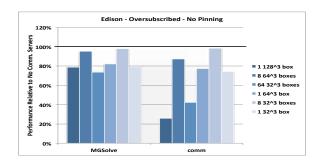

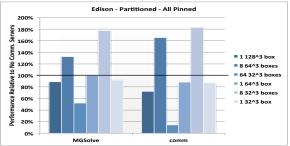

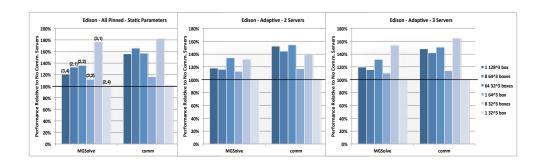

| 28.  | Performance of UPC miniGMG with parallelization relative to without parallelization           |     | 99  |

| 29.  | Performance of UPC miniGMG with selective parallelization relative to without parallelization |     | 99  |

| 30.  | Performance of UPC miniGMG with communication servers relative to without parallelization     |     | 100 |

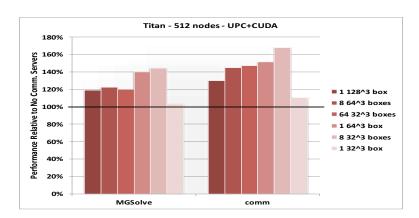

| 31.  | Performance of UPC+CUDA miniGMG with communication servers                                    |     | 102 |

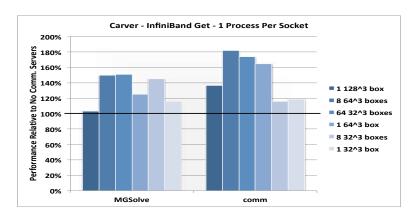

| 32.  | Aggregate bandwidth achieved with one-sided Put and Get operations                            |     | 110 |

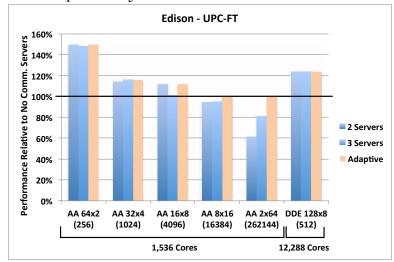

| 33.  | Performance of the UPC-FT benchmark                                                           |     | 110 |

| 34.  | Overall trends comparing hybrid setup                                                         |     | 111 |

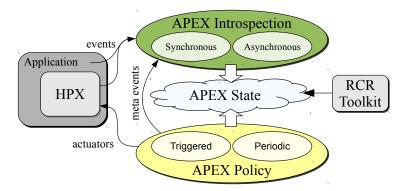

| 35.  | Design of the APEX introspection system                                                       |     | 113 |

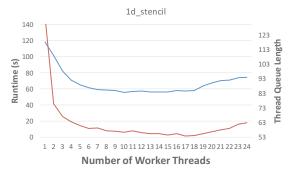

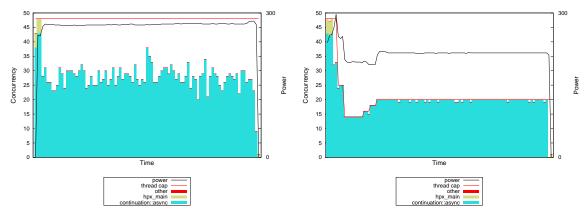

| 36.  | Performance behavior of HPX 1D Stencil under different throttling policies.                   |     | 121 |

| 37.  | HPX miniGhost strong scaling                                                                  |     | 122 |

| 38.  | Energy usage of HPX miniGhost under different throttling policies                             |     | 123 |

| 39.  | Local and global tuning sessions of HPX 1D stencil                                            |     | 124 |

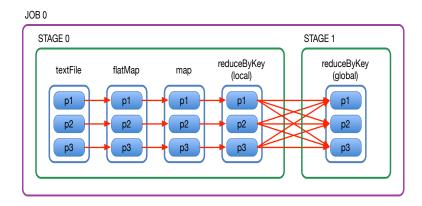

| 40.  | Decomposition of a Spark job into stages and tasks                                            |     | 133 |

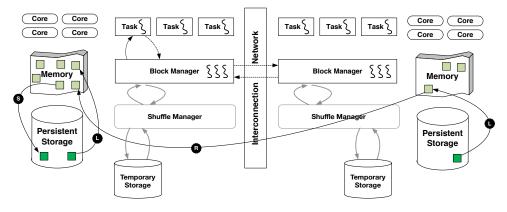

| 41.  | Data movement in Spark                                                                        |     | 133 |

| 42.  | Architecture of the Lustre filesystem                                                         |     | 134 |

| 43.  | Node architecture of the Cori Burst Buffer                                                    |     | 135 |

| 44.  | Network topology of the Cori Burst Buffer                                                     |     | 135 |

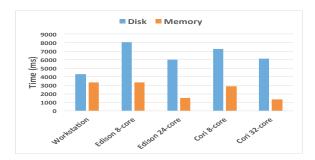

| 45.  | Big Data Benchmark single node performance                                                    |     | 142 |

| Figu | ıre                                                                        | Page | 2   |

|------|----------------------------------------------------------------------------|------|-----|

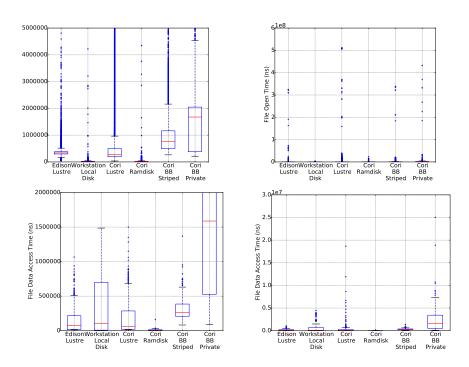

| 46.  | Distribution of file I/O on Lustre vs. ext4 local disk                     |      | 144 |

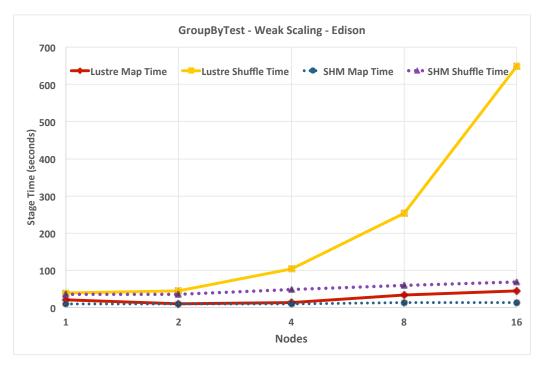

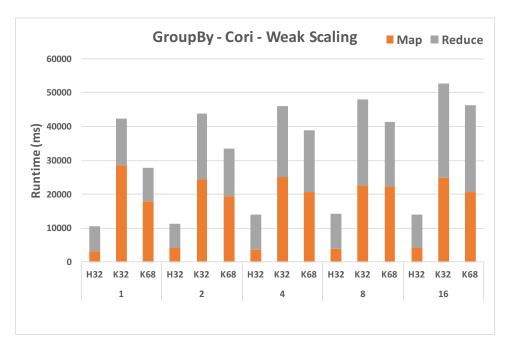

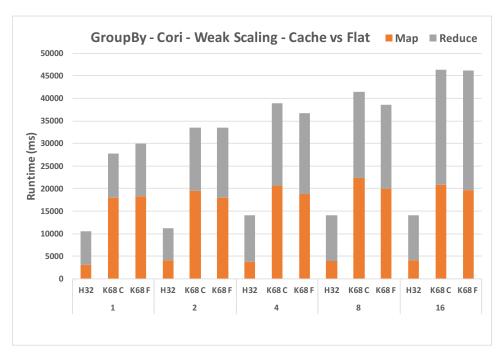

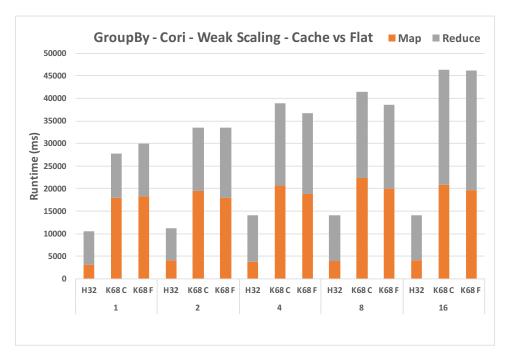

| 47.  | Time for map and reduce phases of GroupBy                                  |      | 148 |

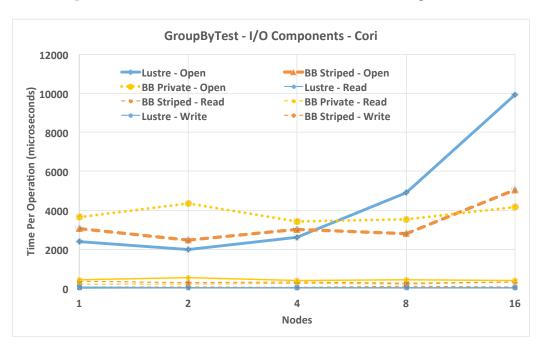

| 48.  | Average time for open, read, and write operations                          |      | 149 |

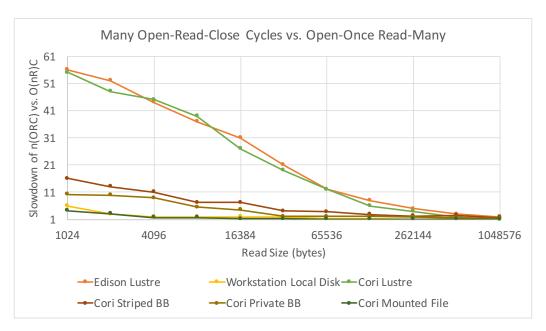

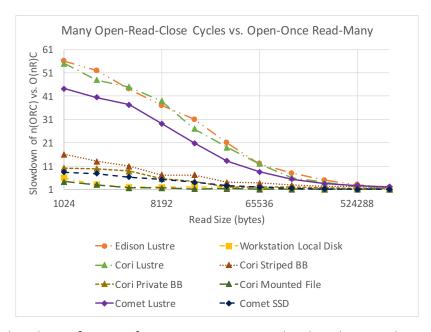

| 49.  | Performance improvements from amortizing file opens                        |      | 151 |

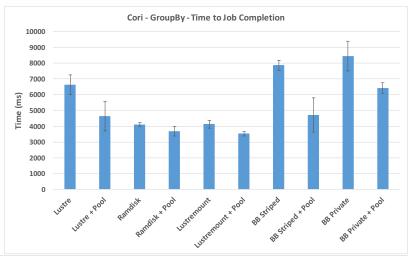

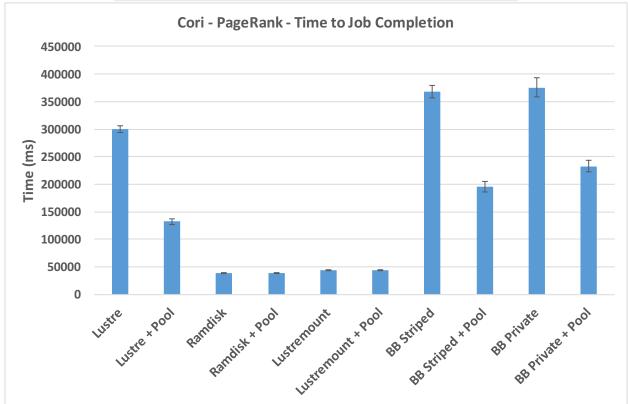

| 50.  | GroupBy and PageRank performance on Cori                                   |      | 153 |

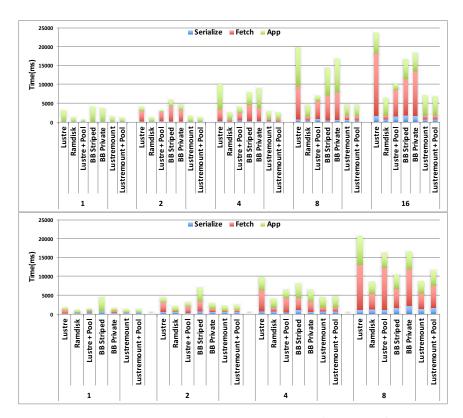

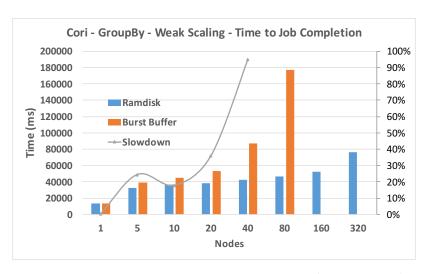

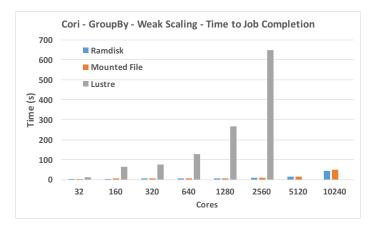

| 51.  | GroupBy weak scaling on Cori                                               |      | 154 |

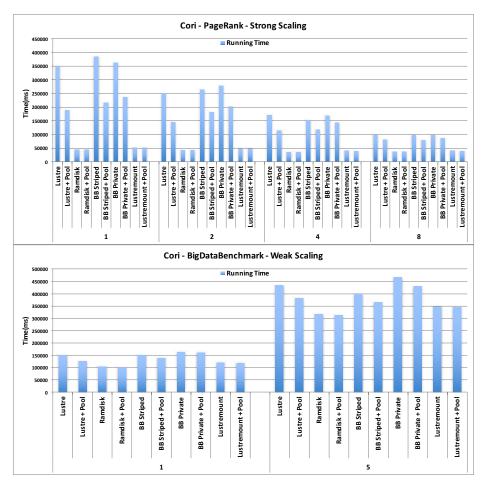

| 52.  | PageRank and Big Data Benchmark scaling on Cori                            |      | 155 |

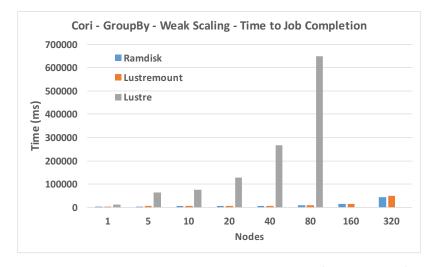

| 53.  | GroupBy at large scale on Cori on Lustre                                   |      | 158 |

| 54.  | GroupBy at large scale on Cori on Lustremount                              |      | 158 |

| 55.  | PageRank perfomrance on Edison.                                            |      | 160 |

| 56.  | I/O behavior of PageRank on Edison                                         |      | 160 |

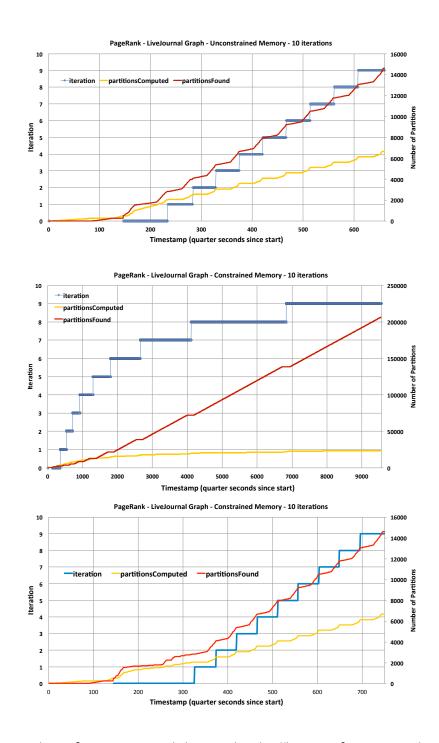

| 57.  | Number of partitions read during shuffe for PageRank                       |      | 177 |

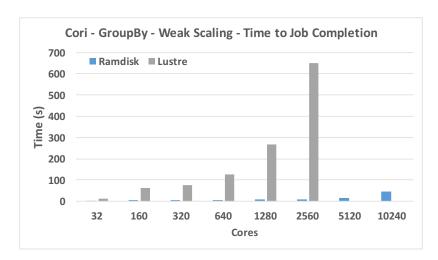

| 58.  | GroupBy performance on Lustre or RAMdisk                                   |      | 178 |

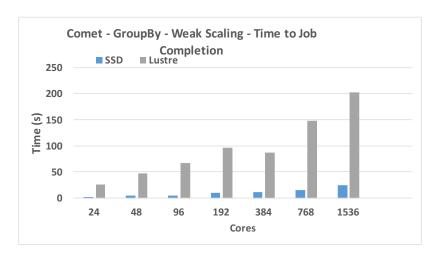

| 59.  | GroupBy performance on Lustre or local SSD                                 |      | 178 |

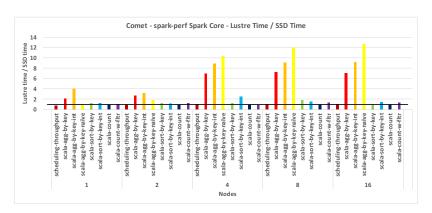

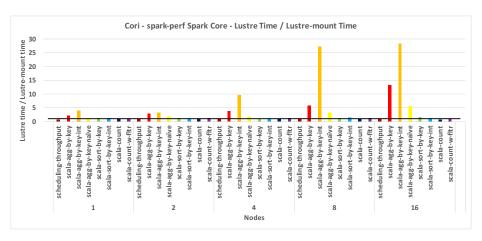

| 60.  | Slowdown of Spark Core benchmarks on Comet                                 |      | 179 |

| 61.  | Slowdown from open-per-read rather than single-open                        |      | 179 |

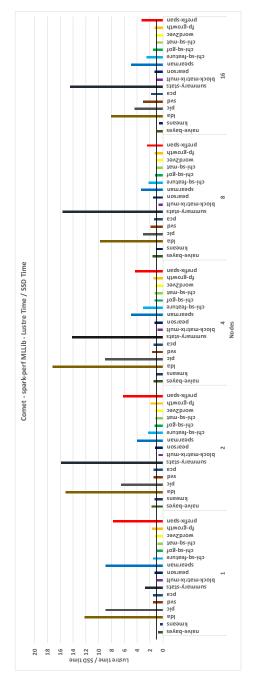

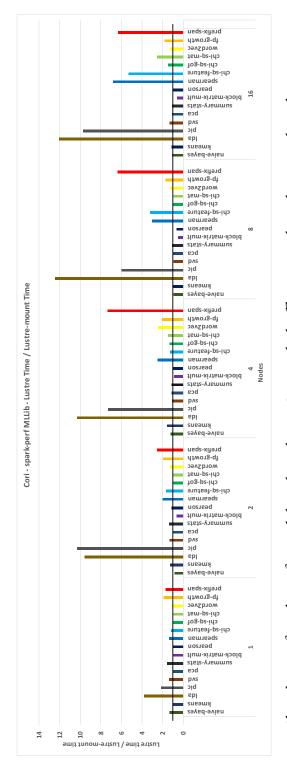

| 62.  | Slowdown of MLLib on Comet                                                 |      | 180 |

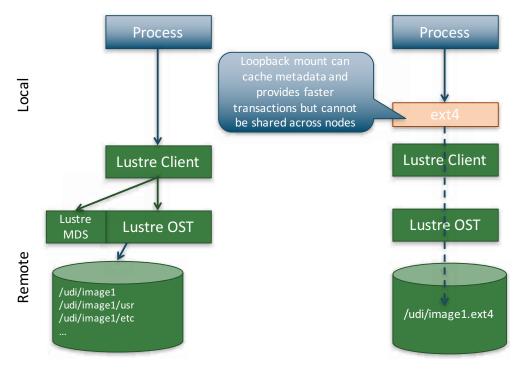

| 63.  | Architecture of Shifter                                                    |      | 181 |

| 64.  | GroupBy benchmark on Lustre, RAMdisk, or per-node loopback filesystem.     |      | 181 |

| 65.  | Slowdown of Spark Core on Cori with Lustre instead of loopback filesystem. |      | 182 |

| 66.  | Slowdown of MLLib on Cori with Lustre instead of loopback filesystem       |      | 183 |

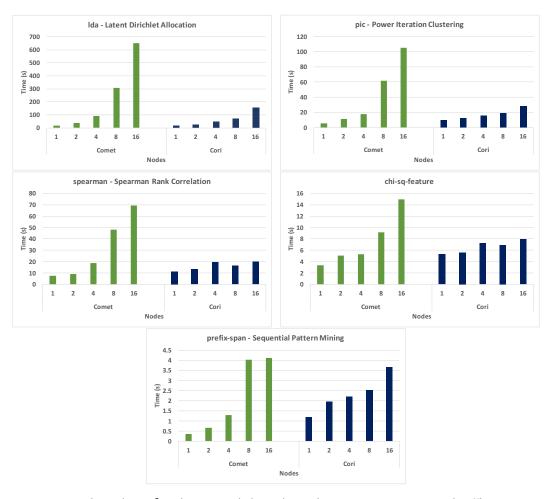

| 67.  | Weak scaling for MLLib on loopback filesystems and local SSDs              |      | 184 |

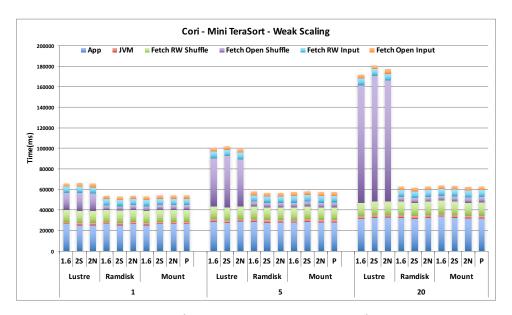

| 68.  | Weak Scaling results for Mini TeraSort                                     |      | 185 |

| 69.  | Weak Scaling results for Big Data Benchmark                                |      | 185 |

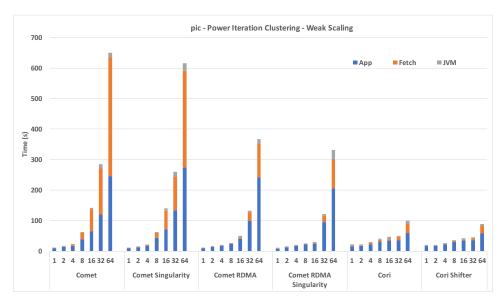

| 70.  | Weak Scaling results for Power Iteration Clustering                        |      | 186 |

| Figu | ire                                                                                      | Page | e           |

|------|------------------------------------------------------------------------------------------|------|-------------|

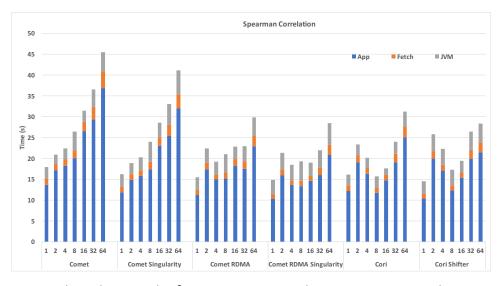

| 71.  | Weak Scaling results for Spearman Correlation                                            |      | 186         |

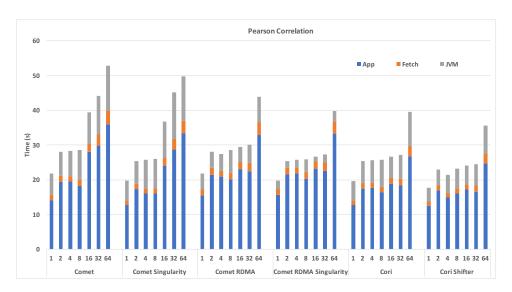

| 72.  | Weak Scaling results for Pearson Correlation                                             |      | 187         |

| 73.  | Weak Scaling results for GroupBy on Xeon Phi                                             |      | 187         |

| 74.  | Weak Scaling results for GroupBy on Xeon Phi in Cache vs Flat MCDRAM mode                |      | 188         |

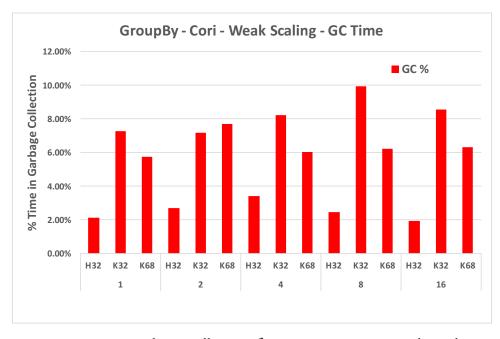

| 75.  | Time spent in garbage collection for GroupBy on Xeon Phi                                 |      | 188         |

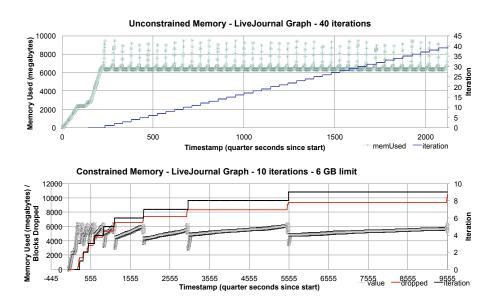

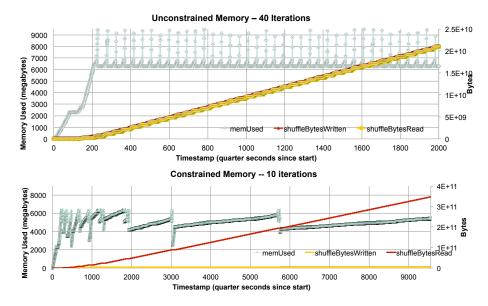

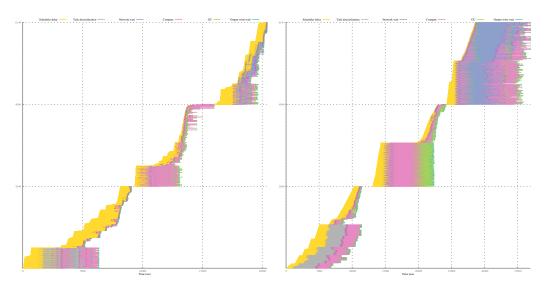

| 76.  | Execution traces of GroupBy on Haswell and Xeon Phi                                      |      | 189         |

| 77.  | Hypothetical execution time of GroupBy after removing stragglers                         |      | 189         |

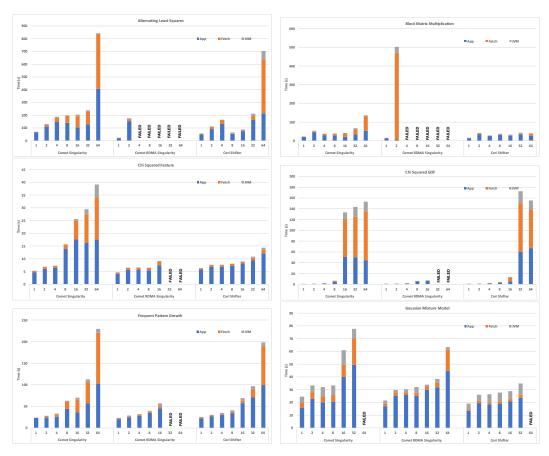

| 78.  | Weak scaling for the first block MLLib benchmarks for Comet IPoIB, Comet RDMA, and Cori  |      | <b>19</b> 0 |

| 79.  | Weak scaling for the second block MLLib benchmarks for Comet IPoIB, Comet RDMA, and Cori |      | 191         |

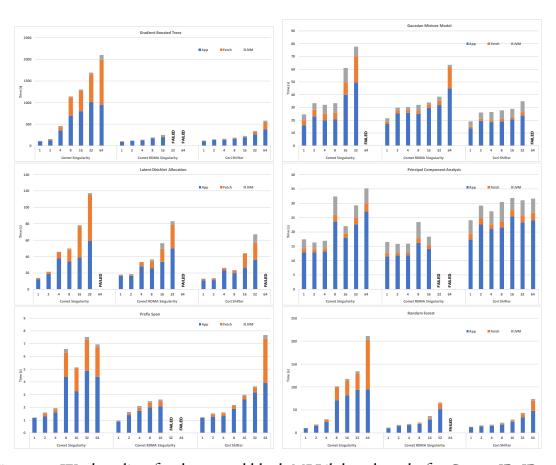

| 80.  | Weak scaling for the third block MLLib benchmarks for Comet IPoIB, Comet RDMA, and Cori  |      | 192         |

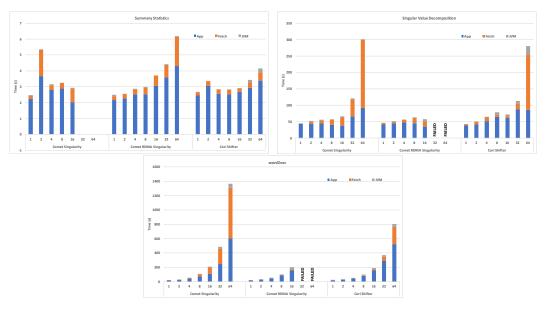

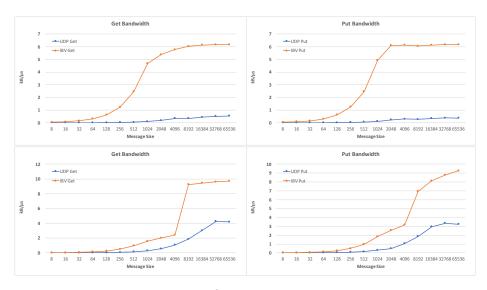

| 81.  | Bandwidth by message size for UDP and native RDMA on Comet and Cori                      |      | 192         |

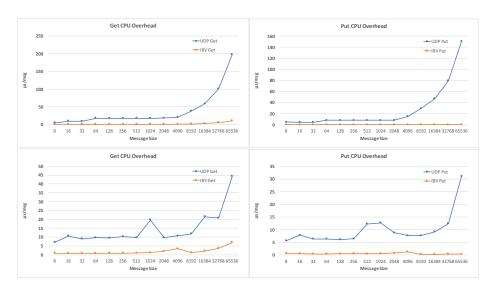

| 82.  | Injection CPU overhead by message size for UDP and native RDMA on Comet and Cori         |      | 193         |

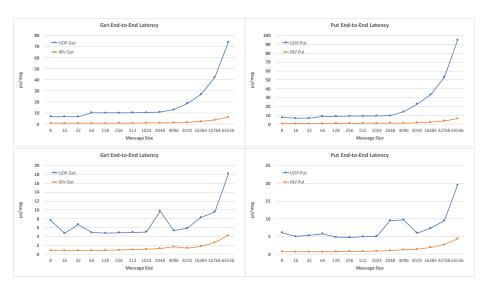

| 83.  | End-to-end latency by message size for UDP and native RDMA on Comet and Cori             |      | 193         |

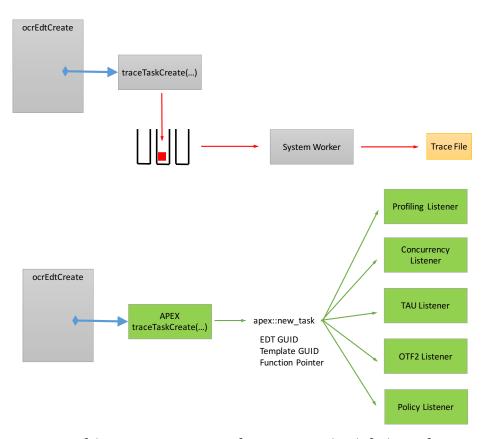

| 84.  | Design of the OCR-APEX interface                                                         |      | 196         |

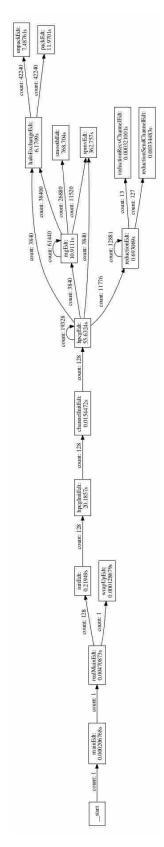

| 85.  | Task creation graph of the HPCG miniapp                                                  |      | 198         |

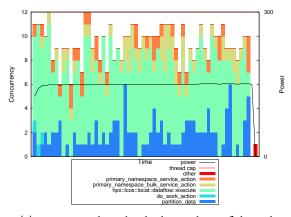

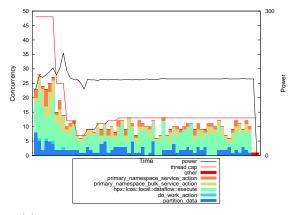

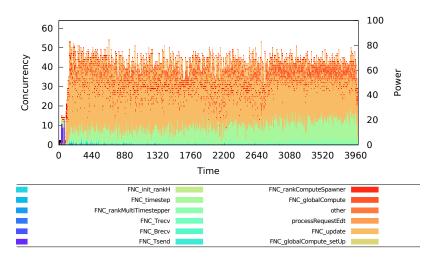

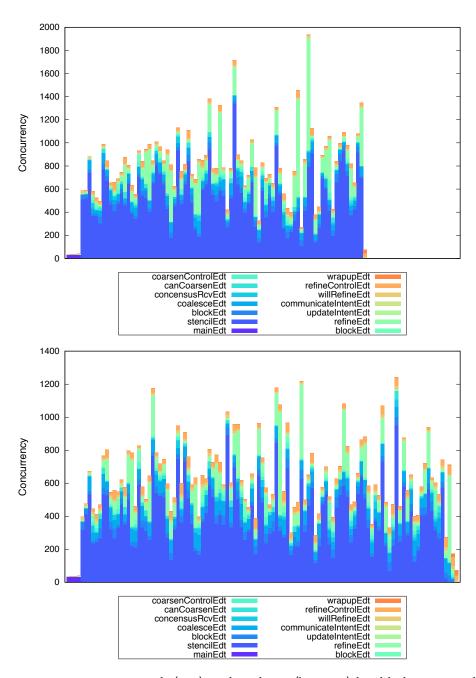

| 86.  | Concurrency visualization of the Stencil2D benchmark                                     |      | 199         |

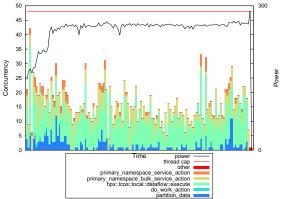

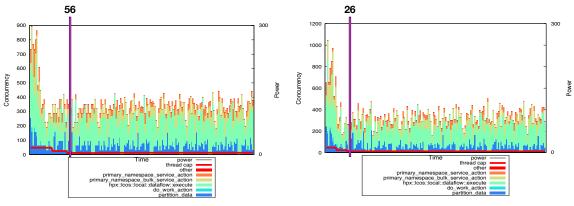

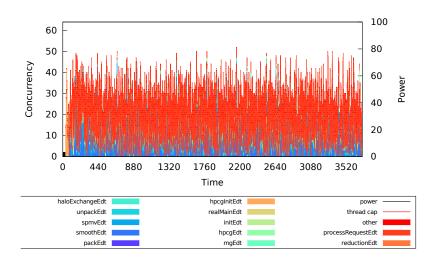

| 87.  | Concurrency visualization of the HPCG miniapp                                            |      | 199         |

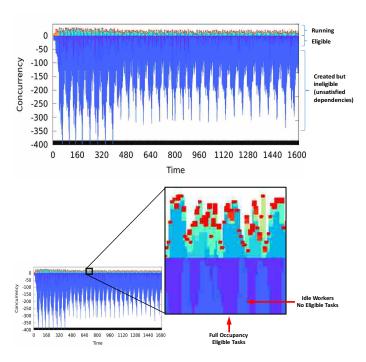

| 88.  | Task eligibility visualization of the HPCG miniapp                                       |      | 201         |

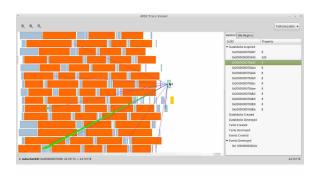

| 89.  | User interface of the APEX Trace Viewer                                                  |      | 202         |

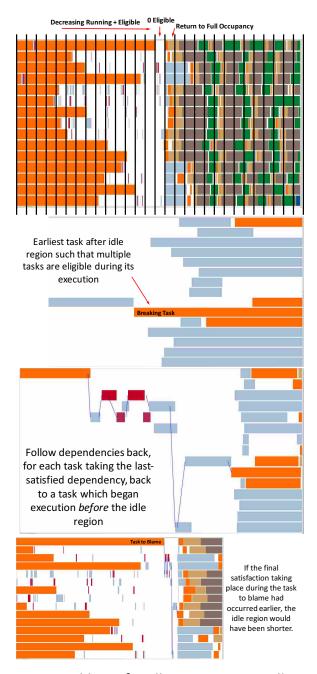

| 90.  | Process for assigning blame for idle regions                                             |      | 204         |

| 91.  | OCR MiniAMR with and without load balancing policy                                       |      | 207         |

| rigu | re                                                                                                                         | Page | е   |

|------|----------------------------------------------------------------------------------------------------------------------------|------|-----|

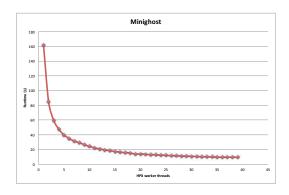

| 92.  | Execution time for compute_rhs using different OpenMP runtime configurations                                               |      | 212 |

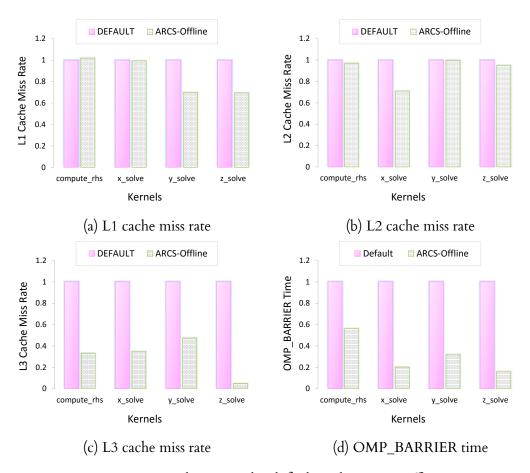

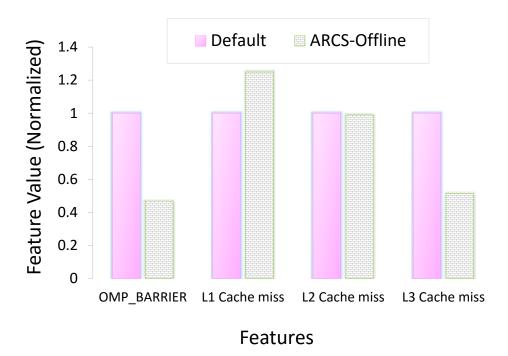

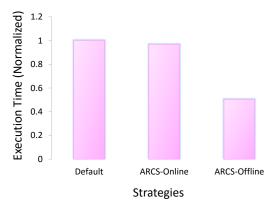

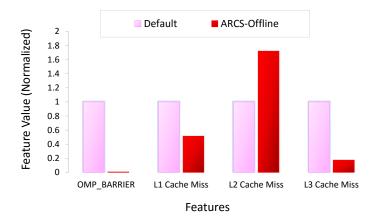

| 93.  | Feature comparison between the default and ARCS-Offline strategy                                                           |      | 226 |

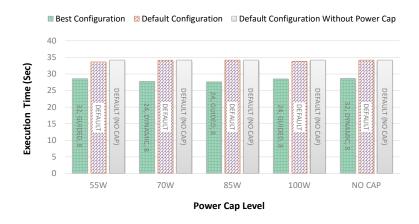

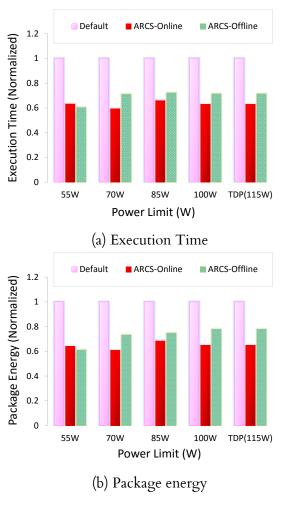

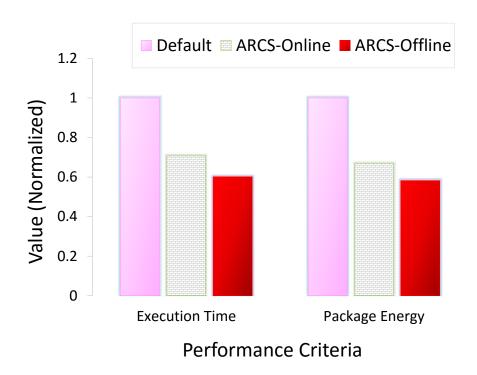

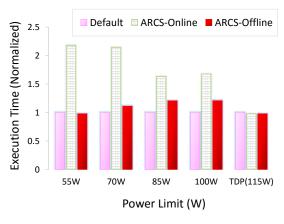

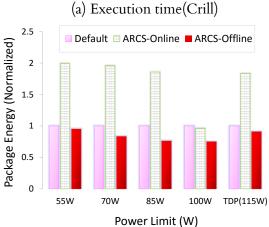

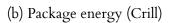

| 94.  | Execution time and package energy comparison among the default and ARCS strategies in SP                                   |      | 227 |

| 95.  | Execution time and energy consumption comparison of ARCS strategies and the default strategy in data set C of SP           |      | 228 |

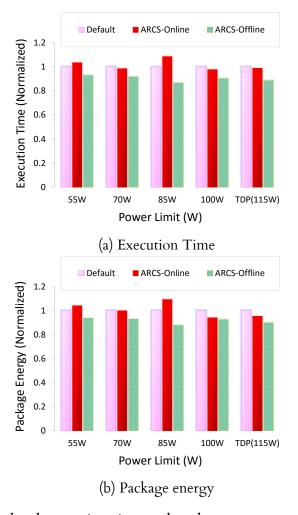

| 96.  | Feature comparison between the default and ARCS-Offline strategy at TDP power level for compute_rhs region of BT           |      | 230 |

| 97.  | Application level execution time and package energy comparison among the default and ARCS strategies in BT with data set B |      | 232 |

| 98.  | Application level execution time and package energy comparison among the default and ARCS strategies in LULESH             |      | 234 |

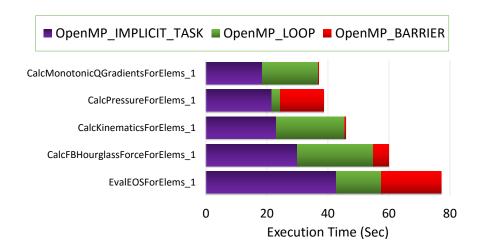

| 99.  | OpenMP events data for top 5 time consuming regions from LULESH                                                            |      | 235 |

| 100. | Feature comparison among default and ARCS strategies on CalcFBHourglassForceForElems_1 region                              |      | 236 |

## LIST OF TABLES

| Γable |                                                                                        |  | e   |

|-------|----------------------------------------------------------------------------------------|--|-----|

| 1.    | Sizes of messages sent by UPC+CUDA miniGMG                                             |  | 102 |

| 2.    | Messages sent in MLLib pic benchmark                                                   |  | 167 |

| 3.    | Per-parallel-region parameter settings with best performance for NAS OpenMP benchmarks |  | 211 |

| 4.    | Set of ARCS search parameters for OpenMP parallel regions                              |  | 217 |

| 5.    | Optimal configuration chosen by ARCS-Offline strategy for SP regions                   |  | 224 |

### CHAPTER I

### INTRODUCTION

Current supercomputers are equipped with O(10,000) nodes, each with within-node concurrency of O(100), providing performance of tens to one hundred petaflops [216]. Reaching exascale performance will require increases in both within-node concurrency to O(1,000) and in the number of nodes to O(100,000), with the effect that in order to make use of the available resources, programs will need to expose multi-billion-way concurrency [6]. The requirement to make available such a large volume of concurrent work is driving the development of new programming models and runtimes for those models: the many-task runtime [56].

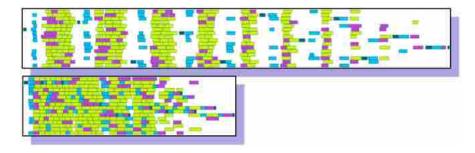

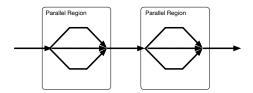

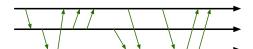

The central idea behind task parallelism is that work is divided into discrete chunks which carry dependency information. The runtime's primary responsibility is to schedule work whose dependencies have been satisfied, and to switch between tasks with as little overhead as possible. Traditional runtimes such as MPI and OpenMP rely on synchronization primitives such as locks and barriers to enforce correct ordering of operations, resulting in the potential for load imbalance to severely limit utilization of available computational resources. Task-based runtimes replace locks and barriers with runtime awareness of dependencies, reducing idleness by allowing cores to begin processing work as soon as it is available, rather than waiting at barriers until an entire phase of the application has completed. They also allow for adaptation to system variability by allowing work to migrate across nodes to address load imbalance caused by node variability; to do this, units of work are virtualized relative to hardware. Data is often also virtualized, so that data can be moved to work, or work can be moved to data, depending upon whichever is cheaper [199]. Figure 1 demonstrates the advantage of a task-based approach over a traditional fork-join approach.

Figure 1. Comparison of fork-join and task parallelism. Execution trace of the same algorithm implemented using fork-join parallelism (top) and task-based parallelism (bottom). The bottom version executes in less time because worker threads can continue executing tasks as soon as the tasks' dependencies have been satisfied. From [244].

Application developers need performance-monitoring tools in order to understand the performance of their application so that they can determine what optimizations are needed to increase performance. Many such tools exist for programs written using traditional programming models. Changing from a fork-join or bulk synchronous programming model to a much more dynamic task-based model, in which different runs of the same application on the same data can result in different task schedules, and in which the assignment of both work and data to computational and storage resources are under the control of the runtime rather than the application, will require new tools. This document proposes new tools to aid in producing correct, insightful, and actionable performance measurements in emerging task-based runtimes.

#### 1.1 Thesis Statement

The central premise of the dissertation is that correct, insightful, and actionable performance monitoring requires integration between tools and runtimes.

Applying a performance monitoring tool designed for traditional programming models to applications using a task-based runtime may yield results which are *not*

correct: the tool may prevent the application from running to completion, such as by making assumptions about a maximum number of threads which are violated by the runtime, or by introducing overheads which are acceptable for the lower levels of concurrency exposed by traditional runtimes but which unacceptably distort timings when a large number of short-running tasks are timed.

They may produce results which are *not insightful*: by being unaware of the greater levels of abstraction found in task-based runtimes, a traditional performance monitoring tool will provide data at the level of the runtime and not of the application. For example, sampling the processes being executed and providing a report of the amount of time spent in each function is unlikely to provide insight, as it is not useful for an application developer to learn that during execution of the application, time was spent in various scheduling and network functions internal to the runtime. The tool must instead map runtime operations to their associated application-level task, providing the developer with performance data *at the level of the application*.