# SYSTEMWIDE POWER MANAGEMENT TARGETING EARLY HARDWARE OVERPROVISIONED HIGH PERFORMANCE COMPUTERS

by

## DANIEL ELLSWORTH

## A DISSERTATION

Presented to the Department of Computer and Information Science and the Graduate School of the University of Oregon in partial fulfillment of the requirements for the degree of Doctor of Philosophy

June 2017

## DISSERTATION APPROVAL PAGE

Student: Daniel Ellsworth

Title: Systemwide Power Management Targeting Early Hardware Overprovisioned High Performance Computers

This dissertation has been accepted and approved in partial fulfillment of the requirements for the Doctor of Philosophy degree in the Department of Computer and Information Science by:

Allen Malony Chair

Martin Schulz Core Member Henry Childs Core Member Reza Rejaie Core Member

Douglas Toomey Institutional Representative

and

Scott L. Pratt Dean of the Graduate School

Original approval signatures are on file with the University of Oregon Graduate School.

Degree awarded June 2017

© 2017 Daniel Ellsworth

## DISSERTATION ABSTRACT

Daniel Ellsworth

Doctor of Philosophy

Department of Computer and Information Science

June 2017

Title: Systemwide Power Management Targeting Early Hardware Overprovisioned High Performance Computers

High performance computing (HPC) systems are an important enabling tool for modern scientific discovery. These large scale computing systems have, since the 1990s, been increasing built as clusters of commodity computers. The operational energy needs of these clusters has lead the HPC community to focus on energy efficient hardware and programming practices. One of the major side effects of introducing energy efficient hardware is variability in power consumption between components within the cluster. In practice, power variability at scale has resulted in poor power utilization and challenges for energy providers contracted to provide the needed power. Hardware overprovisioned HPC systems have been proposed to improve power utilization however production deployment of such a system would compound the challenge for energy providers.

This dissertation presents foundational work on HPC power scheduling, a technique that reduces the risks associated with operating hardware overprovisioned HPC systems. Power scheduling is formalized using the power scheduling invariant. Generalized application behavior, for applications running under a power cap, are experimentally studied. Study insights are used to develop a power scheduler

and a power capping cluster simulator. Comparative behavior of different power scheduling strategies as also examined.

Utilizing the power scheduling invariant, the safety of any power scheduler for deployment can be proven through analyzing scheduler's algorithm and mechanism. A general trend exists in power capped application performance that can be related to application progress, the underlying physics of the hardware, and expected runtime dilation. PowSched provides a proof by construction that power scheduling can be done safely and effectively without application specific models using a simple feedback mechanism. Experimentally, PowSched was shown to produce a 14% improvement in throughput compared to a fair distribution of power between cluster components. PowSim provides a proof by construction that the generalized effects on runtime can be efficiently simulated at scale, providing critical simulation infrastructure for researchers exploring power scheduling at scale. Using simulation, power scheduling strategies are studied and dynamic power scheduling appears to out perform static and reservation based techniques.

This dissertation includes previously published and unpublished co-authored material.

## CURRICULUM VITAE

NAME OF AUTHOR: Daniel Ellsworth

## GRADUATE AND UNDERGRADUATE SCHOOLS ATTENDED:

University of Oregon, Eugene

## DEGREES AWARDED:

Doctor of Philosophy, Computer Science, 2017, University of Oregon Bachelor of Science, Computer Science, 2004, University of Oregon

## AREAS OF SPECIAL INTEREST:

High Performance Computing Programming Language Acquisition

## PROFESSIONAL EXPERIENCE:

Graduate Teaching Fellow, University of Oregon, 2011-2017

Intern, Lawerence Livermore National Laboratory, 2014-2017

Software Developer, Electrical Geodesics Incorporated, 2013-2014

Owner, Octahedral Softworks, 2005-2011

Security Software Architect, Guident, 2010-2011

Trainer & Developer, Nortel Government Solutions, 2009-2010

Director of Application Architecture, Croix Connect, 2009

## GRANTS, AWARDS AND HONORS:

- Don Hubbard Scholarship Award, Computer and Information Science Department, University of Oregon, 2016

- Best Graduate Teaching Fellow, Computer and Information Science Department, University of Oregon, 2013

## **PUBLICATIONS:**

- Ellsworth, D., Patki, T., Schulz, M., Rountree, B., & Malony, A. (2016, November). A Unified Platform for Exploring Power Management Strategies. In Proceedings of the 4th International Workshop on Energy Efficient Supercomputing (pp. 24-30). IEEE Press.

- Ellsworth, D. (2016). Dynamic Power Management For Hardware Overprovisioned Systems (No. LLNL-CONF-705518). Lawrence Livermore National Laboratory (LLNL), Livermore, CA.

- Ellsworth, D., Patki, T., Perarnau, S., Seo, S., Amer, A., Zounmevo, J., ... & Schulz, M. (2016, May). Systemwide Power Management with Argo. In Parallel and Distributed Processing Symposium Workshops, 2016 IEEE International (pp. 1118-1121). IEEE.

- Ellsworth, D. (2016). Topics Toward Automated Multiobjective HPC System Management.

- Ellsworth, D. A., Malony, A. D., Rountree, B., & Schulz, M. (2015, November). Dynamic Power Sharing for Higher Job Throughput. In Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis (p. 80). ACM.

- Ellsworth, D. A., Malony, A. D., Rountree, B., & Schulz, M. (2015, June). Pow: System-wide Dynamic Reallocation of Limited Power in HPC. In Proceedings of the 24th International Symposium on High-Performance Parallel and Distributed Computing (pp. 145-148). ACM.

- Ellsworth, D. (2013). Improving Dynamic Invariant Saliency with Static Dataflow Analysis.

## ACKNOWLEDGEMENTS

Part of this work was performed under the auspices of the U.S. Department of Energy by Lawrence Livermore National Laboratory under Contract DE-AC52-07NA27344.

This work was supported by the U.S. Dept. of Energy, Office of Science, Advanced Scientific Computing Research Program, under Contract DE-AC02-06CH11357.

## TABLE OF CONTENTS

| Chap | Pa <sub>i</sub>                 | ge |

|------|---------------------------------|----|

| I.   | INTRODUCTION                    | 1  |

|      | Previously Published Work       | 7  |

| II.  | BACKGROUND                      | 8  |

|      | Energy Efficiency               | 9  |

|      | Power Reduction                 | 13 |

|      | DPG Impact                      | 14 |

|      | DVFS Impact                     | 15 |

|      | RAPL Impact                     | 16 |

|      | Indirect Mechanisms             | 17 |

|      | Runtime Reduction               | 18 |

|      | Reflection on Energy Efficiency | 19 |

|      | Power Scheduling                | 20 |

|      | Global Power Limit Enforcement  | 21 |

|      | Hard Enforcement                | 22 |

|      | Soft Enforcement                | 23 |

|      | Schedule Time                   | 24 |

|      | Static Techniques               | 24 |

|      | Reservation Techniques          | 25 |

|      | Dynamic Techniques              | 25 |

|      | Literature                      | 26 |

| Chapter                           |    |   |       |  |   |   |   |   | Р | 'age |

|-----------------------------------|----|---|-------|--|---|---|---|---|---|------|

| Naive                             |    |   |       |  |   |   |   |   |   | 26   |

| PARM                              |    |   |       |  |   |   | • | • |   | 27   |

| RMAP                              |    |   |       |  |   |   | • | • |   | 28   |

| SLURM                             |    |   |       |  |   |   |   |   |   | 29   |

| PMJPC                             |    |   |       |  |   |   |   |   |   | 30   |

| PowSched                          |    |   |       |  |   |   | • | • |   | 31   |

| Shifter                           |    |   |       |  |   |   |   | • |   | 32   |

| DAPM                              |    |   |       |  |   |   | • | • |   | 33   |

| Discussion                        |    |   |       |  |   |   |   | • |   | 33   |

| Chapter Summary                   |    |   | <br>• |  |   |   |   | ٠ |   | 35   |

|                                   |    |   |       |  |   |   |   |   |   |      |

| III. POWER CAPPING RUNTIME EFFECT | Γ. |   |       |  |   |   |   |   |   | 36   |

| Power Monitoring                  |    | • |       |  |   |   |   |   |   | 37   |

| Missing Capabilities              |    |   |       |  |   |   |   |   |   | 37   |

| PowMon Design                     |    |   |       |  |   |   |   | • |   | 39   |

| Observation Mechanism             |    |   |       |  |   |   |   |   |   | 40   |

| Observation Timing                |    |   |       |  |   |   |   |   |   | 41   |

| Observation Storage               |    |   |       |  | • | • |   | • |   | 42   |

| Startup and Shutdown              |    |   |       |  |   |   |   |   |   | 43   |

| PowMon Performance Impact         |    |   | <br>• |  |   |   |   |   |   | 44   |

| Experimental Data                 |    |   | <br>• |  |   |   |   |   |   | 44   |

| Dynamic Response                  |    |   |       |  |   |   |   | • |   | 44   |

| Characteristic Power Consumption  |    |   |       |  |   |   |   |   |   | 45   |

| Decreasing Bounds                 |    |   |       |  |   |   |   |   |   | 47   |

| Summary of Experiments            |    |   |       |  |   |   |   |   |   | 52   |

| Chapte | er I                               | Page |

|--------|------------------------------------|------|

|        | Connecting Programs and Power      | 52   |

|        | Chapter Summary                    | 55   |

| IV.    | DYNAMIC POWER SCHEDULING           | 56   |

|        | Design Discussion                  | 56   |

|        | Scheduling Heuristic               | 60   |

|        | Algorithm                          | 62   |

|        | Hard Enforcement                   | 65   |

|        | Implementations                    | 67   |

|        | MPI                                | 68   |

|        | Glasgow Cache                      | 68   |

|        | Results                            | 69   |

|        | Overhead                           | 70   |

|        | MPI Experimental Results           | 70   |

|        | Window Size Sensitivity            | 75   |

|        | Scaling Experiment                 | 75   |

|        | Glasgow Cache Experimental Results | 76   |

|        | Chapter Summary                    | 80   |

| V.     | SIMULATING POWER CAPPING           | 82   |

|        | Modeling Power Capping             | 84   |

|        | Model Intuitions                   | 84   |

|        | Model Formalization                | 88   |

|        | Cluster Scale                      | 90   |

|        | Implementation                     | 92   |

| Chapt | Fage Page                       |

|-------|---------------------------------|

|       | Machine - sim.py                |

|       | Scheduler - schedulers.py       |

|       | Program - program.py            |

|       | Simulator Behavior              |

|       | Validation                      |

|       | Scaling Performance             |

|       | Simulated PowSched              |

|       | Cluster Simulation              |

|       | Anticipating Performance        |

|       | Best Case                       |

|       | Worst Case                      |

|       | Middle Case                     |

|       | Chapter Summary                 |

| VI.   | COMPARING SCHEDULING APPROACHES |

|       | Experimental Comparison         |

|       | Simulation Comparison           |

|       | Simulation Study                |

|       | Base Behavior                   |

|       | Random Queues                   |

|       | Chapter Summary                 |

| VII.  | CONCLUSION                      |

| Chapter Pa                        | ge |

|-----------------------------------|----|

| /III. FUTURE                      | 23 |

| Power Capped Application Behavior | 23 |

| Simulation Enrichment             | 24 |

| Utility of Application Awareness  | 25 |

| Degree of Overprovisioning        | 26 |

| Comparison Studies                | 27 |

|                                   |    |

| REFERENCES CITED                  | 29 |

# LIST OF FIGURES

| Figu | ire                                                                                                                                                                                 | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

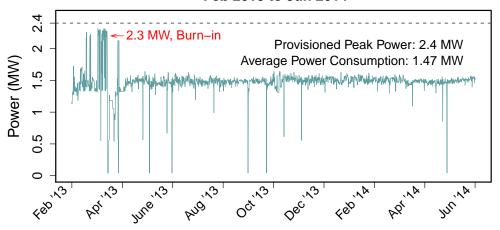

| 1.   | A plot of the power consumption of Vulcan over approximately 16 months. Reproduced from Patki et al. (2015)                                                                         | 5    |

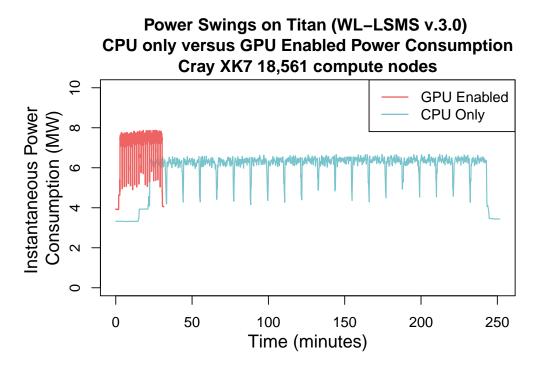

| 2.   | The same computation with and without GPU support. The GPU execution is significantly more energy efficient even though more power is required. Reproduced from Patki et al. (2016) | 12   |

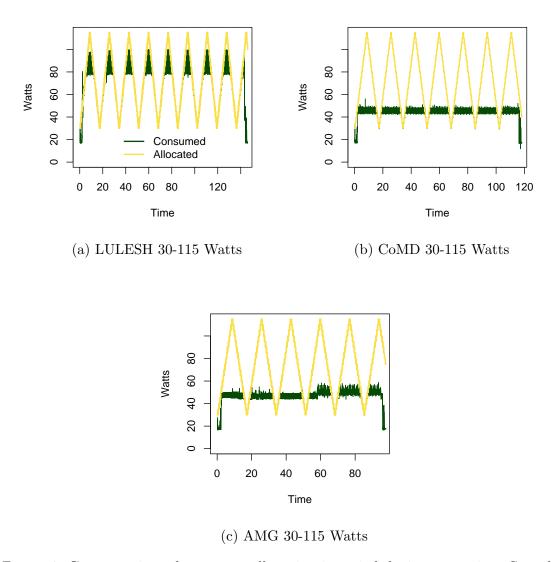

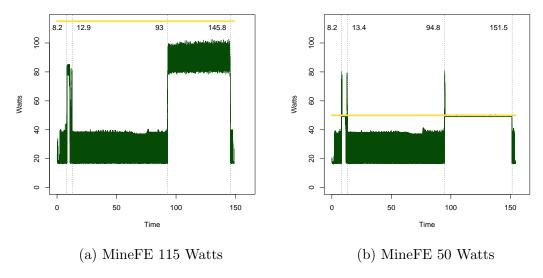

| 3.   | Consumption when power allocation is varied during execution. Sampling at 100 ms intervals with a 1000 ms Intel's Running Average Power Limit (RAPL) window                         | 46   |

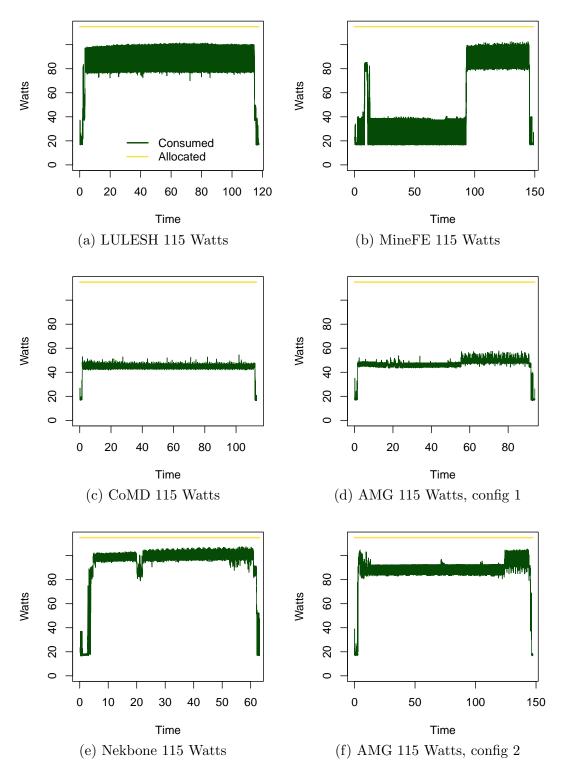

| 4.   | Consumption when power allocation matches the processor TDP. Sampling at 100 ms intervals with a 1000 ms RAPL window                                                                | 48   |

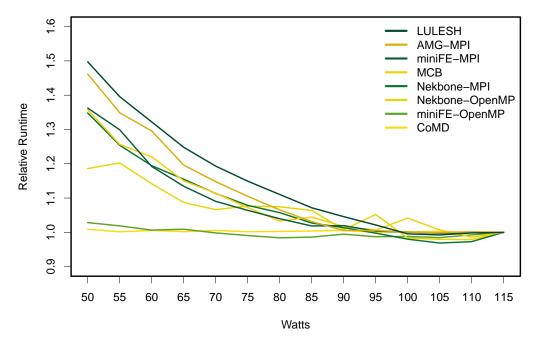

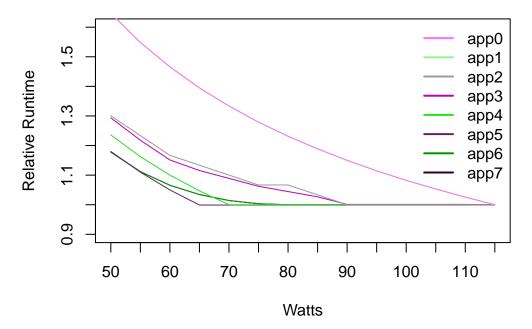

| 5.   | Runtime effect of decreasing power bounds for 8 benchmarks and parameters                                                                                                           | 49   |

| 6.   | Consumption when power allocation matches the processor TDP. Sampling at 100 ms intervals with a 1000 ms RAPL window                                                                | 50   |

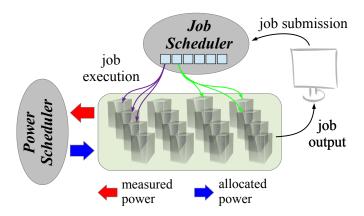

| 7.   | Model relating the cluster, job scheduler, and power scheduler. Graphic created by Allen Malony and reproduced from D. A. Ellsworth, Malony, Rountree, and Schulz (2015a)           | 58   |

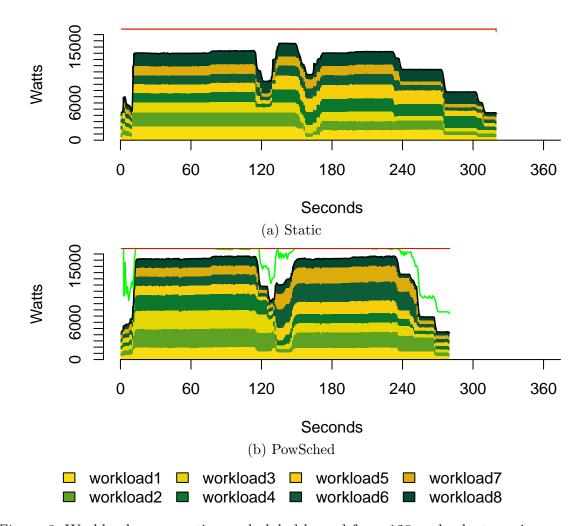

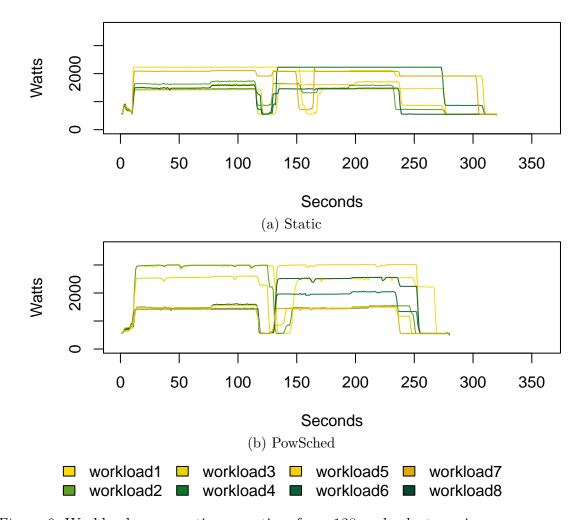

| 8.   | Workload consumption and global bound for a 128 node cluster using an average of 70 watts per socket                                                                                | 72   |

| 9.   | Workload consumption over time for a 128 node cluster using an average of 70 watts per socket                                                                                       | 73   |

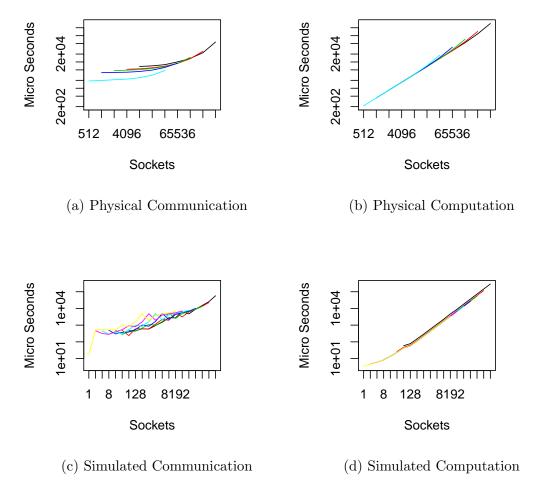

| 10.  | Lines represent the performance for physical node counts used from 8k to 512 nodes in (a) and (b). Lines represent simulated node count per physical node in (c) and (d)            | 77   |

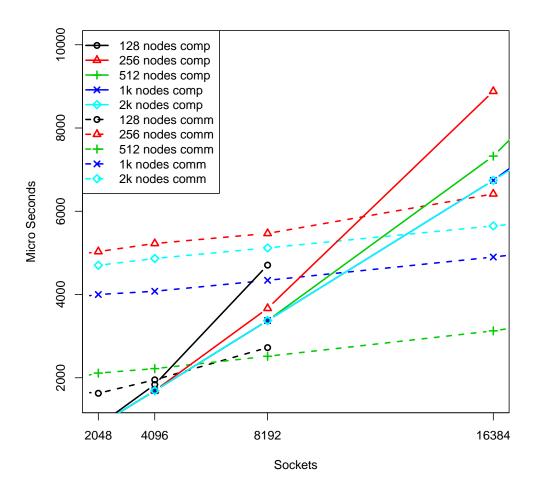

| 11.  | Crossover between computation and communication based on physical count                                                                                                             | 78   |

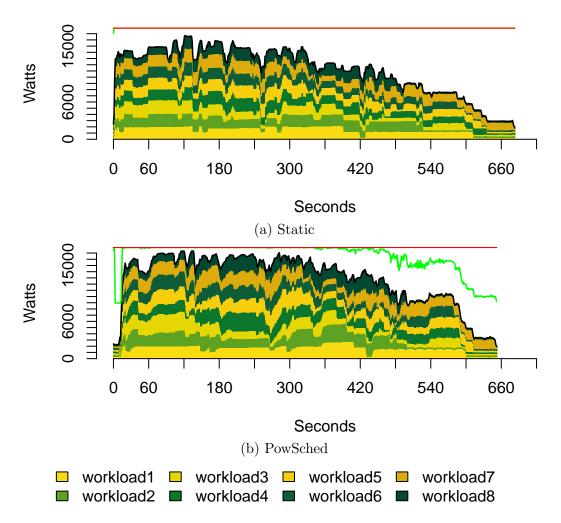

| 12.  | Job consumption and global bound for a 128 node cluster using an average of 70 watts per socket using the decoupled scheduler                                                       | 80   |

| Figu | re                                                                                                                                                             | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 13.  | Runtime effect of decreasing processor power caps for a collection of simulated programs                                                                       | 97   |

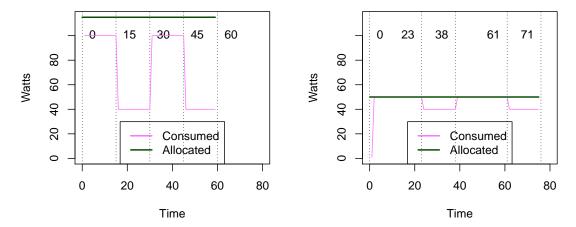

| 14.  | Power consumption for a simulated application with high and low power consumption phases (unbounded (left) and bounded(right))                                 | 98   |

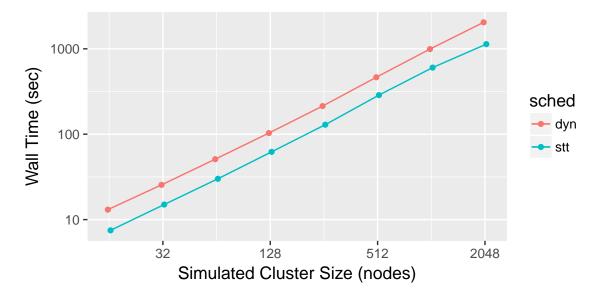

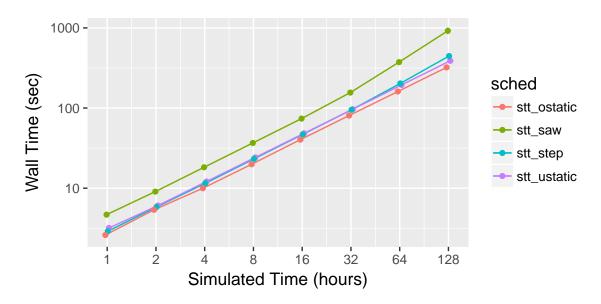

| 15.  | Wall clock time to simulate 12 hours of runtime with cluster node counts ranging from 16 to 2048 nodes. Static (stt) and Dynamic (dyn) schedulers are compared |      |

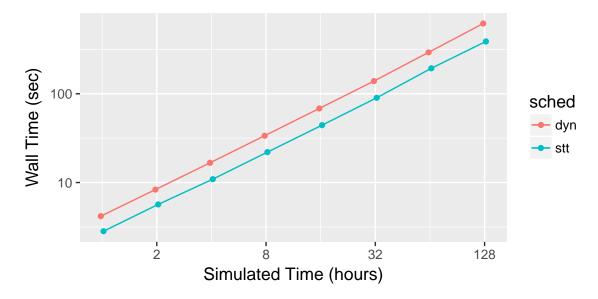

| 16.  | Wall clock time to simulate a cluster with 1024 nodes from 1 hour to 64 hours of simulated time. Static (stt) and Dynamic (dyn) schedulers are compared        | 100  |

| 17.  | Wall clock time to simulate a cluster with 1024 nodes for 1 to 64 hours of simulated time. Different job types are compared                                    |      |

| 18.  | Optimally time aligned consumption across jobs                                                                                                                 | 104  |

| 19.  | Worst case time aligned consumption across jobs                                                                                                                | 105  |

| 20.  | Bad time alignment with different rates of change across jobs                                                                                                  | 106  |

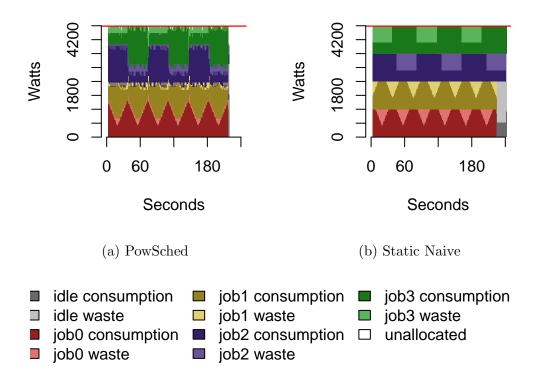

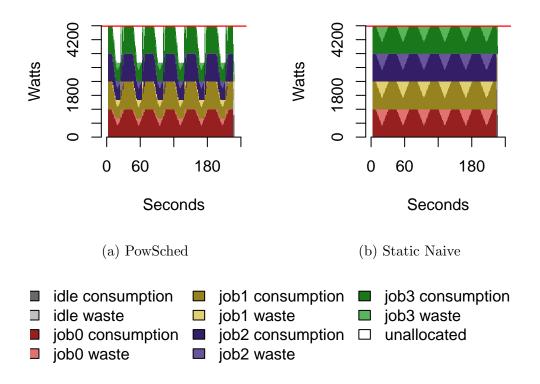

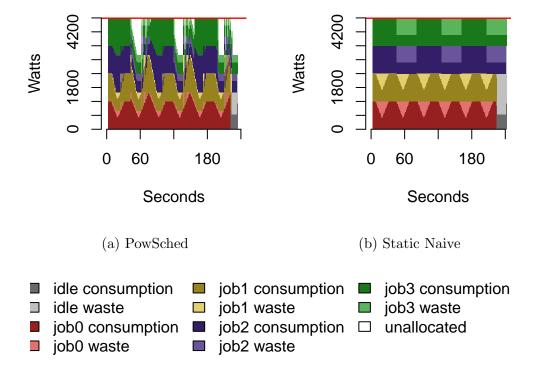

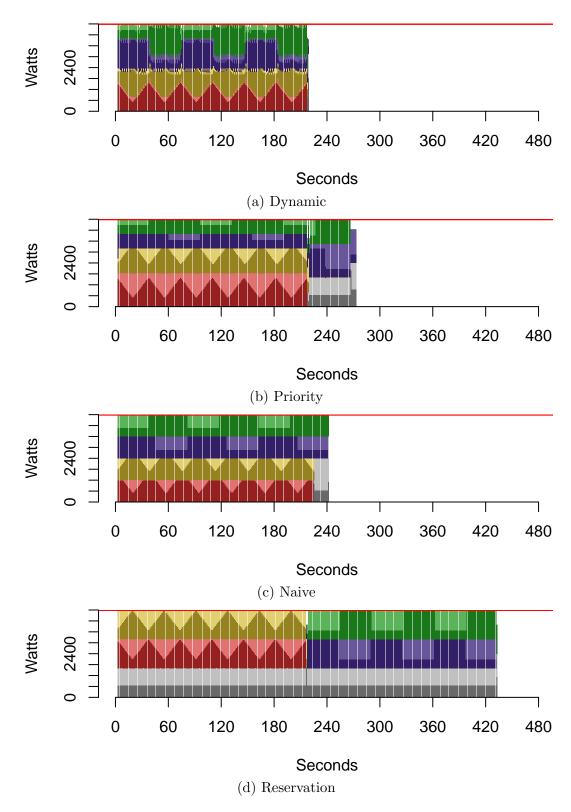

| 21.  | Scheduler comparison using optimally time aligned consumption across jobs for PowSched.                                                                        | 114  |

# LIST OF TABLES

| Tab | ole ————————————————————————————————————                                                                                                                                                                                                                                                                                                                   | Page |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.  | 2010 estimate of first generation exascale system properties compared to 2010 petascale systems. (GF: giga (10 <sup>9</sup> ) flops; TF: tera (10 <sup>1</sup> 2) flops; PF: peta (10 <sup>1</sup> 5) flops: EF: exa (10 <sup>1</sup> 8) flops; BW: bandwidth; MW: megawatt; GB: giga byte; TB: tera byte; PB: peta byte; MTTI: mean time to interruption) | 3    |

| 2.  | Mapping between prior work and dissertation chapters containing shared material                                                                                                                                                                                                                                                                            | 7    |

| 3.  | Table mapping energy reduction research to the primary knob used (power or runtime reduction) and mechanism used to actuate that knob                                                                                                                                                                                                                      | 11   |

| 4.  | Table defining the symbols used in the power scheduling invariant (Equation 2.3)                                                                                                                                                                                                                                                                           | 22   |

| 5.  | Table relating work to enforcement and scheduling strategy                                                                                                                                                                                                                                                                                                 | 26   |

| 6.  | Runtimes for three High Performance Computing (HPC) benchmarks at differing node counts with and without PowMon (Wrapped and Unwrapped, respectively). Observed performance is well within system jitter indicating that PowMon overheads are negligible                                                                                                   | 45   |

| 7.  | Runtime and energy for AMG (configuration 2), LULESH, MiniFE, and Nekbone under varying power caps                                                                                                                                                                                                                                                         | 51   |

| 8.  | Runtimes reported by the benchmarks in seconds. PowSched @115W run forces PowSched to assign 115W per socket over the lifetime of the job. PowSched @dyn allows PowSched to dynamically adjust the per socket allocation with a global bound permitting 115W per socket                                                                                    | 70   |

| 9.  | 128 nodes, 16 nodes workloads per workload, 10 runs, same workload for all runs reported with improvement percent and energy                                                                                                                                                                                                                               | 72   |

| 10. | Benchmarks used for 8 node workloads in the 128 and 256 node experiments                                                                                                                                                                                                                                                                                   | 74   |

| 11. | Comparison of 1 decoupled run with averaged runs using static                                                                                                                                                                                                                                                                                              | 77   |

| 12. | Comparison of static and decoupled with more varied workloads at 128 and 256 nodes                                                                                                                                                                                                                                                                         | 79   |

| Tab | le                                                                                                                  | Page |

|-----|---------------------------------------------------------------------------------------------------------------------|------|

| 13. | Symbols use in the simulation model                                                                                 | 88   |

| 14. | Description of the simulated jobs plotted in Fig 13. Runtime in this table refers to the job runtime in normal time | 97   |

| 15. | Simulation parameters                                                                                               | 102  |

| 16. | Simulated runtime with random workloads                                                                             | 102  |

| 17. | Runtimes of the schedulers ordered by error and run duration for constant type work.                                | 116  |

| 18. | Runtimes of the schedulers ordered error and run duration for prepost type work.                                    |      |

| 19. | Runtimes of the schedulers ordered by error and run duration for step type work                                     |      |

| 20. | Runtimes of the reservation scheduler with constant type work for fixed estimate errors                             | 118  |

## CHAPTER I

## INTRODUCTION

This chapter contains ideas and themes that have been previously published in D. Ellsworth (2016); D. Ellsworth, Patki, Perarnau, et al. (2016); D. Ellsworth, Patki, Schulz, Rountree, and Malony (2016); D. A. Ellsworth et al. (2015a); D. A. Ellsworth, Malony, Rountree, and Schulz (2015b). The narrative as presented in this chapter is my original work derived from discussions with the co-authors of the previously published works regarding the motivation for the power capping when the work was initiated.

High performance computing (HPC) platforms are a critical enabling technology for modern science and engineering. Both of these disciplines make extensive use of mathematical models to analyze observations and make predictions. Executing the models is computationally intense due to the mathematics and amount of data used to represent a physical system under study. In the case of simulations, these computations must be done repeatedly to accumulate effects as the system understudy evolves through simulated time. The computational power provided by HPC platforms allow cost prohibitive, impractical, or technologically impossible hypothises to be explored via simulation.

Early HPC platforms like the Cray-1, capable of 160 million (10<sup>6</sup>) floating point operations per second (FLOPS)<sup>1</sup>(Cray-1, n.d.), were engineering marvels. Efficient techniques for getting higher performance from shared memory computing

<sup>&</sup>lt;sup>1</sup>Computational power, in the context of HPC, is measured in floating point operations per second. A floating point number is a rounded representation of real number. An operation is something like adding or multiplying. A person capable of multiplying two floating point numbers per second would be a computer operating at 1 FLOPS.

were pioneered using early HPC machines. Vector processing and other technologies common in modern consumer devices were pioneered in the HPC setting. The market for such powerful shared memory systems was very small since few organizations can afford the expense of these machines. Scaling (i.e., increasing the computational power) for early HPC systems required new engineering effort and completely replacing the machine.

Starting in the late 90s, the majority of HPC machine designs moved to clusters. Rather than purchase an extremely expensive single computer, a cluster is made by connecting many individual computers. Cluster computing allows system owners to take advantage of the economies of scale when pricing and repairing a machine. The shift brought new challenges as coordination across nodes became a key concern (e.g., interconnection technologies, distributed programming abstractions, etc.). As the community has improved techniques to coordinate across cluster nodes, HPC scaling has become a problem primarily of identifying how many nodes an organization can afford to include in the cluster. The top cluster based HPC system in 2016, Sunway TaihuLight, is theoretically able to complete 125 quintillion (10<sup>15</sup>) FLOPS and contains over 10 million processor cores(November 2016 — TOP500 Supercomputer Sites, n.d.).

Around 2010, the US Department of Energy (DOE) became interested in the procurement of an HPC system capable of roughly 1 sextillion (10<sup>18</sup>) FLOPS, an exascale system. Table 1, common in presentations and reports produced by the HPC community, compares 2010 petascale system attributes to the expected first generation exascale system attributes. Of particular concern for horizontal scaling was the power requirement, as most system attributes would increase by two or three orders of magnitude, but power was only to increase by a single order

| Attribute                  | 2010                | 2018                | Increase                               |

|----------------------------|---------------------|---------------------|----------------------------------------|

| System Peak                | 2 PF                | 1 EF                | $\mathcal{O}(1000)$                    |

| Power                      | 6 MW                | 20 MW               | $\mathcal{O}(10)$                      |

| Memory                     | 0.3 PB              | 32-64 PB            | $\mathcal{O}(100)$                     |

| Node Performance           | 125 GF              | 1-10 TF             | $\mathcal{O}(10) - \mathcal{O}(100)$   |

| Node Memory BW             | 25  GB/s            | .4-4 TB/s           | $\mathcal{O}(100)$                     |

| Node Concurrency           | 12                  | 1-10k               | $\mathcal{O}(100) - \mathcal{O}(1000)$ |

| Total Concurrency          | 225 000             | $10^{9}$            | O(10000)                               |

| Total Node Interconnect BW | $1.5~\mathrm{GB/s}$ | $200~\mathrm{GB/s}$ | $\mathcal{O}(100)$                     |

| MTTI                       | days                | 1 day               | $-\mathcal{O}(10)$                     |

Table 1. 2010 estimate of first generation exascale system properties compared to 2010 petascale systems. (GF: giga (10<sup>9</sup>) flops; TF: tera (10<sup>1</sup>2) flops; PF: peta (10<sup>1</sup>5) flops: EF: exa (10<sup>1</sup>8) flops; BW: bandwidth; MW: megawatt; GB: giga byte; TB: tera byte; PB: peta byte; MTTI: mean time to interruption)

of magnitude<sup>2</sup>. The consensus from the community was that the horizontal scaling approaches used for petascale systems would not be able to achieve the DOE objectives and energy efficiency emerged as a top problem for the HPC community.

Many of the techniques for increasing computational energy efficiency make power consumption variable. Different operations the computer can perform come at different energy costs based on the complexity of the operation and the speed at which the operation is performed. Energy efficiency is usually achieved by only performing the needed operations at the minimum speed required to avoid delays. Different programs and phases within the same program will use differing mixes

<sup>&</sup>lt;sup>2</sup>The 20 megawatt power consumption target for first generation exascale systems is likely motivated by cost. HPC systems are extremely expensive assets for the owning organization. Procurement and installation of hardware are multimillion dollar capital investments. Ongoing operational expenses from HPC systems are also significant. US wholesale power rates in 2017 are roughly estimated at one million dollars per megawatt of power purchased. The top US computer in 2016 was Titan(November 2016 — TOP500 Supercomputer Sites, n.d.). Titan had an estimated power cost of around 8 million dollars per year and a theoretical peak performance of roughly 27 petaflops (10<sup>15</sup> FLOPS). Observed performance on Titan was around 17 petaflops. Purely horizontal scaling of Titan to support 1 exaflop at theoretical peak would result in roughly 30 million dollars per year in power costs.

of operations, resulting in different energy needs over time. The power variability introduced by energy efficiency will be discussed more in Chapters II and III.

Traditionally, power for HPC systems is purchased and power distribution infrastructure built based on the theoretical maximum power consumption of the system, also known as worst case power provisioning. Figure 1 shows the power consumption of a relatively energy efficient HPC system, Vulcan<sup>3</sup>. Vulcan can consume roughly 2.4 megawatts of power at peak, resulting in roughly 2.4 megawatts of power being procured for the system. Vulcan is observed to consume almost 2.4 megawatts on occasion, however, usually consumes about 1.5 megawatts. This means that roughly 30% of the procured power goes unused during much of Vulcan's lifetime. Scaling up to a 20 megawatt exascale system, 6 megawatts would be expected to go unused most of the time. Since the energy contracts in some centers are based on a committed rate of power consumption, 30% of the fiscal power budget may be spent on energy that is never used.

Hardware overprovisioning has been recently proposed (Rountree, Ahn, de Supinski, Lowenthal, & Schulz, 2012) and aims to convert the power savings from energy efficient computation into useful computation. A hardware overprovioned HPC system will contain more hardware than can be run at peak consumption and yet will be controlled to stay within the procured power. In the case of Vulcan that would mean the ability to add 30% more nodes, making approximately 10 thousand more cores available for users. The additional nodes can then be used to run larger scale computations or run additional computations concurrently. Alternatively, the owning organization could leave Vulcan with the same node count but reduce

$<sup>^3</sup>$  Vulcan is an IBM BG/Q system hosted at Lawerence Livermore National Laboratory. Vulcan was initially deployed in 2012 and was ranked 21 on the Top500 list in 2016( Vulcan -  $BlueGene/Q,\ Power\ BQC\ 16C\ 1.600GHz,\ Custom\ Interconnect\ --\ TOP500\ Supercomputer\ Sites,\ n.d.).$

## Total Power Consumption of the BG/Q Vulcan Supercomputer Feb 2013 to Jun 2014

Figure 1. A plot of the power consumption of Vulcan over approximately 16 months. Reproduced from Patki et al. (2015).

the power procurement to something closer to 1.5 megawatts<sup>4</sup>. Applying either of these changes would result in a system that could significantly exceed the procured power, introducing risk to the owning organization.

A new and significant resource management challenge is introduced by hardware overprovisioning. Power generation and consumption must remain in balance across the larger power grid to avoid surges and brownouts that may damage the power infrastructure. Consuming significantly more energy than contracted for may cause the energy provider's generation capacity to be exceeded or have severe financial penalties. Supposing the energy provider can generate sufficient power, the distribution infrastructure may not be able to support the higher rate and will be damaged. Simply adding additional hardware without changing the power infrastructure is therefore unsafe. To safely deploy hardware

<sup>&</sup>lt;sup>4</sup>At an estimated 1 million dollars per megawatt, this would save nearly 1 million dollars per year on power that is never used.

overprovisioned HPC systems, a mechanism to contain HPC system power consumption is required.

This dissertation presents research on power scheduling, a mechanism to contain systemwide power consumption, done to support first generation hardware overprovisioned HPC systems. Energy and power in HPC have only recently become topics of interest to the research community and power control mechanisms like RAPL<sup>5</sup> have only recently become available for experimentation. The broader research question underlying this work is: how can power utilization be increased in large scale computing systems when there exists a fixed upper limit on available power. Contributions made in this dissertation may be relevant outside of the HPC context (e.g., datacenters). An exploration of these other contexts is out of scope for this work.

Chapter II discusses related work and introduces the power scheduling invariant to partion solutions by the provability of power schedule enforcement. Chapter III contributes research filling a foundational gap in the literature regarding HPC application power consumption behavior. Chapter IV contributes a novel power scheduler, experimentally shown to have good performance, that requires no apriori information regarding applications running on the cluster. Chapter V contributes the only simulator currently in the HPC community that is able to simulate the general effects of arbitrary power bounds on application progress at scale without extensive trace based modeling. Chapter VI contributes

<sup>&</sup>lt;sup>5</sup>Running average power limit (RAPL) is an Intel technology that allows software to set a target energy consumption, over a sliding window, that is enforced by hardware. Similar technology, with different names, are available from other vendors. Experiments reported in this dissertation were conducted only on Intel systems due to experimental platform availability but the results are expected to be portable to other architectures. Confirmation of result portability is out of scope for this dissertation.

|                                              | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

|----------------------------------------------|---|---|---|---|---|---|---|

| D. A. Ellsworth et al. (2015a)               | X | X |   | X |   |   | X |

| D. A. Ellsworth et al. (2015b)               | X | X | X | X | X |   | X |

| D. Ellsworth (2016)                          | X | X |   |   |   |   | X |

| D. Ellsworth, Patki, Perarnau, et al. (2016) | X | X |   | X |   |   | X |

| D. Ellsworth, Patki, Schulz, et al. (2016)   | X | X |   | X |   | X | X |

Table 2. Mapping between prior work and dissertation chapters containing shared material.

an approach to comparing power scheduling solutions to potentially be deployed on a hardware overprovisioned HPC system.

## Previously Published Work

Much of the core material presented in this dissertation has appeared in other venues, however, the presentation has been altered for use in the context of this dissertation. Table 2 summarizes the published works and chapters in which previously published material appears.

## CHAPTER II

## BACKGROUND

This chapter contains ideas and themes that have been previously published in D. Ellsworth (2016); D. Ellsworth, Patki, Perarnau, et al. (2016); D. Ellsworth, Patki, Schulz, et al. (2016); D. A. Ellsworth et al. (2015a, 2015b). The narrative as presented in this chapter is my original work summarizing existing research in the community. The power scheduling invariant is my original work, however the language used to express the invariant has been tuned through conversations with my co-authors in the previously published work.

Hardware overprovisioned systems have only recently been proposed in the HPC literature. In "Beyond DVFS: A First Look at Performance Under a Hardware-Enforced Power Bound", Rountree et al. (2012) observe that modern energy efficient processors are overprovisioned with respect to power. These processors have more circuitry than can be run at the highest clock frequency while remaining within the processor's thermal design power (TDP). Owners of these processors are buying the flexibility to achieve higher concurrency through activating more gates at lower frequency or fewer gates at a higher frequency. Energy efficient performance is achieved, in part, through more effective utilization of power in an overprovisioned processor. Rountree et al. (2012) suggest that a similar approach may be applicable to HPC system design.

Classically, HPC nodes and power are provisioned with the expectation that all nodes will operate at maximum power consumption at all times. In practice, nodes rarely consume the maximum amount of power resulting in unutilized, yet available power. A hardware overprovisioned system provides more nodes than

the provisioned power can support at maximum consumption. The extra nodes in the cluster are available to perform useful computation when sufficient unutilized power is available. System owners of hardware overprovisioned systems have the flexibility to run all nodes at low power or a subset of nodes at high power based on the needs of the running workloads. The hardware overprovisioned cluster, even if built from homogenous nodes, is a dynamically reconfigurable and heterogenous execution environment in the presence of variable power allocations. Both work and power must be scheduled across a hardware overprovisioned cluster to maximize system energy efficiency and performance.

Existing work on energy efficiency and power scheduling for HPC systems is briefly surveyed in this chapter. First work on energy efficiency in the HPC community will be briefly presented and categorized as using power reduction or runtime reduction as the primary mechanism to achieve effeciency. Energy efficiency work focuses on reducing the amount of energy expended to complete a given computation and is necessary to utilize hardware overprovisioned systems.

Next, work on HPC power scheduling is presented and categorized based on enforcement and when power allocation decisions are made. Power scheduling is the major focus of this thesis and existing work will be organized based on how the power bounding is enforced and when power allocations are adjusted.

## Energy Efficiency

Power and energy are strongly related concepts that are often used interchangeably in normal conversation, leading to confusion when these concepts must be discussed separately<sup>1</sup>. The standard unit of power, P, is the Watt and the standard unit of energy, E, is the Joule. Power is the rate at which energy is

<sup>&</sup>lt;sup>1</sup>For example, the residential "power bill" should be referred to as an energy bill since the utility is charging based on energy used rather than power. 1 kilowatt hour, kWh, is 3600 joules.

transfered, leading to the following standard formulas for conversion:

$$P = \frac{E}{t} \tag{2.1}$$

$$E = Pt (2.2)$$

Equation 2.1 states the power, P, in watts is equal to the energy, E, in joules divided by the time, t, in seconds. Similarly, equation 2.2 states that the energy, E, is equal to the power, P, times the duration, t. The values of power and energy are frequently related to one another by these formulas, which assume constant power over the interval.

Energy efficient computation techniques are important supporting technology for hardware overprovisioned systems since these provide opportunities to shift power between jobs. The objective of energy efficient computation techniques is to reduce the total energy required to complete a specific computation. There are two, nonexclusive, basic ways to accomplish energy reduction:

Power reduction Reduce the needed power without significantly increasing the time.

Runtime reduction Reduce the computation runtime without significantly increasing the needed power.

In some cases a significant power reduction and extended runtime may result in higher energy efficiency, however, extending runtimes are highly undesirable in HPC. Table 3 summarizes the works to be cited in this section.

Using either power reduction or runtime reduction, the energy per computation is reduced. Energy efficient techniques that make use of dynamic power gating (DPG) or dynamic voltage and frequency scaling (DVFS) are

| Research                                    | Reduces | Mechanism      |

|---------------------------------------------|---------|----------------|

| Bambagini, Bertogna, Marinoni, and Buttazzo | Power   | DPG, DVFS      |

| (2013)                                      |         |                |

| Rountree et al. (2009)                      | Power   | DVFS           |

| Tiwari, Laurenzano, Peraza, Carrington, and | Power   | DVFS           |

| Snavely (2012)                              |         |                |

| Marathe et al. (2015)                       | Power   | DVFS, RAPL     |

| Patki, Lowenthal, Rountree, Schulz, and de  | Power   | Indirect, RAPL |

| Supinski (2013)                             |         |                |

| Zhang and Hoffmann (2016)                   | Power   | Indirect, RAPL |

| Hoffmann, Maggio, Santambrogio, Leva, and   | Power   | Indirect       |

| Agarwal (2013)                              |         |                |

| Enos et al. (2010)                          | Runtime | GPGPU          |

| Betkaoui, Thomas, and Luk (2010)            | Runtime | FPGA           |

Table 3. Table mapping energy reduction research to the primary knob used (power or runtime reduction) and mechanism used to actuate that knob.

generally making use of the first strategy. Due to some properties of the computation, the processor can be slowed (i.e., clock frequency reduced) or halted, reducing power, without impacting perceived performance. Energy efficient techniques that make use of general purpose graphics processing unit (GPGPU) computing are generally making use of the second strategy. GPGPUs tend to require more energy per unit time than the processor however an overall energy savings is realized due to much shorter runtimes when the parallelism can be effectively utilized, see Figure 2.

The HPC community frequently uses floating point operations per second per watt, FLOPS/W, as the metric of choice when discussing both HPC power and energy. The metric represents the energy per floating point operation<sup>2</sup>. Supposing the number of floating point operations was known in advance, a total energy cost

<sup>&</sup>lt;sup>2</sup>Since both FLOPS and watts are rates, the time cancels out making the metric floating point operations per joule, FLOP/J. Like a power bill's use of kWh, leaving the watts in the FLOPS/W measure is misleading since it does not represent a rate.

Figure 2. The same computation with and without GPU support. The GPU execution is significantly more energy efficient even though more power is required. Reproduced from Patki et al. (2016).

for a computation could be computed. However, the runtime and power would still be unrecoverable. Knowing the number of parallel execution units does not resolve the problem of recovering runtime since any computation that is not embarrassingly parallel will involve some runtime in which some execution units are unused. Given the loss of information regarding the computation, FLOPS/W is not useful for comparing application energy performance and is better applied only to comparing hardware floating point energy costs.

Power Reduction. As a by-product of their operation, processors convert electrical energy into thermal energy. A major contributor to energy consumption and heat generation within a computer is transistor switching. Each transistor converts a small amount of energy to heat when changing state and that amount depends, in part, on the voltage and switching frequency. Additionally, some energy is lost due to leak current. A model to describe the power loss due to switching is  $W = \eta C V^2 f$  (De Vogeleer, Memmi, Jouvelot, & Coelho, 2014); the watts W lost are directly related to the square of the voltage V and the frequency f of switching. Since voltage and frequency must be increased together, resulting in a nonlinear relationship between watts and instruction execution speed dominated by the  $V^2$  term. Power lost to leak current is also related to the voltage.

Two major, processor internal, approaches to power management are power gating and DVFS. Power gating turns off circuits not currently being used within the processor. For the effected circuits, power gating avoids both leak and switching losses. DVFS changes the voltage and frequency of operation within the processor. For the effected circuits, DVFS reduces the leak and switching losses.

Three mechanisms exposed by modern processors for power control are dynamic power gating (DPG), dynamic voltage and frequency scaling (DVFS),

and capping<sup>3</sup>(e.g., Intel's Running Average Power Limit (RAPL)). DPG is used to signal that the processor should switch to an ultra low power mode, turning off most of the processor's circuitry. Reasoning about the performance impact of DPG is straight forward since the computation is effectively halted on the processor. DVFS is used to signal that the processor should change to a specific clock frequency and voltage. Reasoning about the performance impact of DVFS is more complex since runtime may or may not increase<sup>4</sup>. RAPL is an Intel feature used to signal that the processor should respect a power cap, which the processor does primarily through DVFS but may involve other internal mechanisms. Reasoning about the performance impact of a RAPL power cap is non-trivial since the processor frequency is variable based on the concurrent work executing within the processor.

Power reduction techniques are the most common energy efficiency techniques in the HPC literature. The power reduction work is organized in this section based on the primary mechanism used to achieve power reduction.

DPG Impact. DPG is a useful technique for embedded realtime workloads, but is less useful for HPC workloads. The embedded realtime workload is typified by a time driven sense-compute-act cycle<sup>5</sup>. Bambagini et al. (2013) present an effective scheduler for realtime systems with limited preemption using both DPG and DVFS that increases battery life. The effectiveness of the technique

<sup>&</sup>lt;sup>3</sup>Different vendors use different names for their power capping technology. Intel's Running Average Power Limit (RAPL) is the only mechanism we have seen used in the power scheduling literature.

<sup>&</sup>lt;sup>4</sup>Reducing frequency will proportionally extend hardware instruction execution time. The complexity in estimating effect comes from the interaction with the memory subsystem. If the rate of progress was bound by memory latency, reducing the clock speed will have limited effect on runtime.

<sup>&</sup>lt;sup>5</sup>Periodically, the device reads a sensor value, performs a computation based on the sensed value, and performs some action.

relies on the compute workload being predictably periodic with regular not-later-than deadlines to complete the computation. While a specific HPC job may internally have periodic behavior during execution, HPC jobs are typically a single computation with all input data available at launch. Effectively halting a processor participating in a job is risky since work allocated to the processor may be on the critical path and halting will extend the critical path. No HPC energy efficiency work using DPG was encountered while working on this dissertation.

DVFS Impact. The majority of work on energy efficiency in HPC is based on DVFS, possibly due to the similarity to the established technique of load balancing. A common technique for improving application performance in HPC applications is to use a technique called load balancing<sup>6</sup> to improve the time alignment of work completion by each computing unit. DVFS makes reasonably predictable changes to the runtime of compute intensive workloads on a node, allowing load balancing via adjusting relative node computation speed. We highlight two works here.

In "Adagio: Making DVS Practical for Complex HPC Applications",

Rountree et al. (2009) look at reducing energy consumption of HPC applications

while maintaining runtime performance using DVFS. The authors use the

insight that many nodes in an HPC application spend some amount of time

waiting, causing these nodes idle while other nodes complete computations.

As the application executes, Adagio records the time spent between collective

communication and the time spent waiting within the collective. On future

iterations, Adagio adjusts the clock frequency during the computation portion of

<sup>&</sup>lt;sup>6</sup>The load (i.e. amount of work) is the same (i.e. balanced) across all workers. Load imbalance leads to longer runtime since heavily loaded workers will take longer than lightly loaded workers and all workers must complete before the next iteration of the computation can begin.

execution to reduce the time spent waiting within the collective. Adagio runtime and energy savings are favorable across a wider range of applications than the comparison algorithms Rountree et al. tried.

In "Green Queue: Customized Large-scale Clock Frequency Scaling" Tiwari et al. (2012) also investigate energy saving for HPC applications using DVFS. The approach used by Green Queue is considerably more invasive than Adagio, involving static analysis and traced executions prior to the execution compared to the baseline. While the reported Green Queue results are impresive, with an average 17% energy savings, the results are somewhat out of context since the energy and time cost of executions needed to generate models are not considered. For applications that have consistent power behavior and must be run repeatedly, this energy cost for model building can be amortized though.

RAPL Impact. The runtime and energy performance impact of RAPL is still an area of active research in the HPC community, which complicates the application of RAPL to energy efficiency. One of the interesting and confounding properties of RAPL is that small manufacturing differences are exposed as noticeable performance differences when a power cap is applied (Inadomi et al., 2015; Rountree et al., 2012). Minute variations in the power cost for each individual transistor on a processor, summed over billions of transistors operating at gigahertz frequencies, can result in substantial variations in power consumption. Most HPC RAPL research focuses on execution in power limited contexts, which is a component of the power scheduling problem to be discussed in the next section. However energy efficiency gains can be inferred from this work.

In "A Run-Time System for Power-Constrained HPC Applications", Marathe et al. (2015) present *Conductor*. *Conductor* shifts power between nodes within a job, decreasing the aggregate power consumption of the job. The technique is actually hybrid, DVFS is used for load balance and estimates on the expected power impact is used to set the updated RAPL power cap. A way to understand *Conductor* in the context of energy savings is that *Conductor* provides the energy benefits of DVFS techniques and provides an enforced upper bound on job power consumption.

In "Exploring Hardware Overprovisioning in Power-Constrained, High Performance Computing", Patki et al. (2013) sweep node count, core count, and processor power cap. From the results presented, the energy cost of configurations can be computed. In many cases, the most energy efficient configuration does not use the maximum number of nodes and cores at the highest power setting. Followon work by Patki et al. (2015), discussed in the Power Scheduling section of this chapter, used energy efficiency gains from selecting energy optimal configurations to support power-aware job scheduling.

Indirect Mechanisms. Power consumption is a side effect of the active computations. In the case where direct processor power control mechanisms are not exposed, changes to the instruction stream or degree of parallelism can be used used to effect power consumption. Memory, network, fans, and other subsystems effect overall system power consumption as well and these subsystems rarely expose mechanisms for direct power control. Some work exists that addresses how to control power through only indirect means.

Hoffmann (2013) and Hoffmann et al. (2013) approach power reduction as a multiobjective optimization problem. Rather than looking at a bound as a hard limit, these works consider a bound as an optimization target when adjusting other properties of the environment. Environmental controls used in the work

extend beyond direct power control, actions like changing the DVFS settings, to indirect controls, like changing the work distribution across cores. Hoffmann (2013) demonstrates an ability to reduce energy cost without performance impact for applications where iterations faster than a realtime interval produce no benefit. Hoffmann et al. (2013) demonstrates a online tuning system, PTRADE, that can learn environmental settings to improve power efficiency during runtime.

The challenge with application of indirect mechanisms is the latency required to converge to a target power cap. Zhang and Hoffmann (2016) use RAPL in addition to indirect controls to achieve faster convergence to a power target than indirect control alone provides. In this dissertation, only the processor contribution to system power is considered due to the lack of a RAPL like mechanism for most other subsystems<sup>7</sup>. The timeliness guarantees required to respond to power allocation changes and maintain bounded consumption for safe operation of a hardware overprovisioned HPC system cannot currently be supported through indirect control mechanisms.

Runtime Reduction. Performance optimization, defined as minimizing job runtime, has been the classic measure for goodness in HPC systems and applications. Given the numerical intensity and duration of HPC jobs, even a small percentage gain in performance can result in significantly shorter time to solution. Compiler optimizations to maximally utilize processor, memory, and IO subsystems to reduce runtimes have been traditional areas of HPC. Accelerator technologies, like GPGPUs and vector units, have also been traditionally studied with respect to their impact on job runtimes. While significant work exists on reducing computational runtime for HPC applications and increasing hardware

$<sup>^7\</sup>mathrm{RAPL}$  also supports power capping memory, however this feature is often disabled in the BIOS.

energy efficiency, there is little work that discusses computational energy costs directly when runtime is reduced. Two papers are mentioned here.

In "Quantifying the Impact of GPUs on Performance and Energy Efficiency in HPC Clusters" (Enos et al., 2010), the energy cost of CPU only computation is compared to a computation using GPU acceleration. Four HPC codes are run with and without GPU acceleration on the test system. The authors conclude, for their hardware, a speedup of greater than 3x is required for the GPU accelerated code to be more energy efficient than a CPU-only code.

In "Comparing Performance and Energy Efficiency of FPGAs and GPUs for High Productivity Computing" (Betkaoui et al., 2010), the energy costs of CPU-only, FPGA, and GPU execution is compared. Four applications are run on the CPU, FPGA, and GPU. Comparison of the FPGA and GPU are of primary interest to the authors since the CPU, while having the lowest power, has the highest energy cost for large inputs. The memory access pattern of the workload was shown to have a major impact on the comparative efficiency of FPGA and GPU acceleration. For applications with streaming and sequential memory access, the GPU provided better performance. For applications with more random memory accessed, the FPGA solution provided better performance.

Reflection on Energy Efficiency. Energy efficiency is an important property for HPC computations and systems, but energy efficiency does not help in bounding power consumption. Power reduction strategies for energy efficiency reduce the power cost of a computation and enable the *extra* hardware within a hardware overprovisioned HPC system to be used. Runtime reduction strategies for energy efficiency may increase the power cost of a computation, but provide a net benefit if sufficient power can be made available for the computation. Which

strategy provides the best performance is dependent on the specific hardware and computation being optimized with respect to energy. Since improved energy efficiency may involve either increasing or decreasing power, work on energy efficiency alone is insufficient to safely support a hardware overprovisioned, with respect to power, HPC system.

Energy efficient computations are necessary however for realizing performance improvements from a hardware overprovisioned system. Job scheduling on HPC systems typically results in several applications, each application having an application specific power consumption, running concurrently on different partitions of the cluster. The presence of some applications using power reduction strategies, explicitly or due to hardware energy optimizations, and other applications using runtime reduction strategies provide excellent opportunities to load balance power rather than work across the cluster. An effective power scheduler will leverage these power differences across jobs to allocate power to nodes, allowing more work to complete per unit time, than would be possible if all node received an equal amount of power.

### Power Scheduling

Power scheduling allows the gains from energy efficiency to be converted into improved computational performance for the same system power bound. A system power bound may originate from an administrative concern (e.g. budgeting) or physical concern (e.g. electrical distribution infrastructure). In either case, power scheduling utilizes power shifting<sup>8</sup> to redistribute the available power across cluster nodes. Rather than attempt to reduce the total energy cost of the system, power

<sup>&</sup>lt;sup>8</sup>Power is conceptually *shifted* from one set of nodes to another set of nodes for some duration. Power shifting is also used internally by modern processors to improve performance with in the TDP (Felter, Rajamani, Keller, & Rusu, 2005).

scheduling work aims at maximizing power utilization within some upper power bound.

Two important attributes for partitioning existing power scheduling work are, limit enforcement and schedule time. These attributes will be discussed prior to a brief review of several power scheduling solutions in the literature. Following the review will be brief commentary and the performance comparability issues with the current literature.

Global Power Limit Enforcement. The environment an overprovisioned HPC system is deployed in, will determine how rigorously a power scheduler must maintain the system wide power bound. Exceeding the power bound for bounds originating from physical concerns may damage the computing or power infrastructure. In such environments, the power limit must be provably enforced for safe operation. In many cases power bounds are likely to originate due to administrative concerns (e.g. power is cheaper at different times of day.). For administratively power bound systems, failure to enforce the system power bound from time to time may be safe, but costly and therefore undesirable.

The power scheduling invariant can be used to reason about a power scheduler's ability to enforce the system wide power bound. Formally, the power scheduling invariant can be written as:

$$\forall t, L \ge \sum_{i=1}^{n} a_i^t \ge \sum_{i=1}^{n} c_i^t \tag{2.3}$$

Stated in english, at all times the system wide power bound must be greater than or equal to the power allocated to components within the system and each component must consume no more than the component's current allocation. Table 4 defines the variables used in the formalization.

| Symbol         | Meaning                                          |

|----------------|--------------------------------------------------|

| $\overline{L}$ | Global power limit                               |

| t              | Time interval                                    |

| n              | Total number of components                       |

| $a_i^t$        | Power allocated to component $i$ at interval $t$ |

| $c_i^t$        | Power consumed by component $i$ at interval $t$  |

Table 4. Table defining the symbols used in the power scheduling invariant (Equation 2.3).

An HPC power scheduler can be decomposed into algorithm and mechanism.

The algorithm determines when and how power is allocated (i.e. shifted) across nodes in the cluster and is modelled in the power scheduling invariant by:

$$\forall t, L \ge \sum_{i=1}^{n} a_i^t \tag{2.4}$$

Failure to provably meet the condition on the algorithm indicates that a power scheduler may, at some point during operation, produce allocations that will exceed the system wide power limit.

The mechanism determines how the component level power cap is maintained and is modelled in the power scheduling invariant by:

$$\forall t, a_i^t \ge c_i^t \tag{2.5}$$

Failure to provably meet the condition by the mechanism indicates that a component, at some point during operation, may disobey the power scheduler and exceed the allocation.

Hard Enforcement. Hard power limit enforcement matches the case where the power scheduling invariant is provably satisfied by the power scheduler. A scheduler capable of hard enforcement must be able to guarantee that the power bound is never exceeded by the cluster. Providing hard enforcement requires some hardware support due to the fine granularity of the timescale at which a power

bound must be maintained. In cases where physical limitations motivate the system wide power bound, operation of the cluster without a scheduler capable of hard enforcement may result in physical damage to the cluster.

Soft Enforcement. Soft power limit enforcement matches the case where algorithm or mechanism cannot be proven to satisfy the power scheduling invariant. There is an argument that power schedulers providing only soft enforcement should be rejected as unfit for purpose. A power scheduler has a requirement to allocate power such that a system wide power bound is maintained and, therefore, a power scheduler providing soft enforcement does not meet the functional requirements. On the other hand, systems without hardware support for direct power management can never be proven to meet the power scheduling invariant's requirements for mechanism. Research on power schedulers providing soft enforcement are interesting due to their ability to provide reasonable power bound enforcement without hardware support.

Another case for schedulers only providing soft enforcement can be made based on electricity provider contracts. Abrupt changes in power consumption create challenges for an electricity provider since power consumption and generation must remain balanced across the larger power grid. Some providers require large power customers to estimate their power consumption in advance and penalize customers for significantly going over or under the estimate. Another consideration is that the wholesale cost of power in many markets depends on the time of day the power is being used. A financially advantageous power schedule for an organization may involve operating the cluster with an artificially low power bound during times when power costs are higher. The infrastructure in these cases is capable

of supporting the full load of the HPC cluster but there are some benefits to attempting to maintain bounded consumption even if the attempt fails.

Schedule Time. When power schedules are computed and applied can also be a useful way to partition the space of power schedulers. The time and frequency of schedule application can effect the observed level of power utilization across the HPC system. One way to think about why schedule time should be expected to impact power utilization is to consider that each time a schedule is applied, there is an opportunity to adapt the power schedule to the current system conditions. Due to the entrance, execution behavior, and exit of jobs from the HPC system, the power needs of a cluster tend to be dynamic and evolve over time. These major schedule times are present in the literature: static, reservation, and dynamic.

Static Techniques. Static techniques set the power cap once at system install time and never change the cap there after. Trivially, the static algorithm can be shown to maintain the power scheduling invariant since there are no time varying allocations to consider. As long as the sum of the component power caps is less than the total system power bound at system start time the invariant will be satisfied.

The simplicity of reasoning about static power scheduling techniques makes them a common baseline for comparison. Current HPC systems use a degenerate form of this technique, where the component level power cap is the TDP of the component. Many works on hardware overprovisioned power scheduling will compare to a system where the power per component is statically set to the average

power for the system. One can imagine a cluster in which different nodes have different statically assigned power caps<sup>9</sup>.

Reservation Techniques. Reservation techniques set component power caps at job start time to keep the system within the total power budget. Each time a job is scheduled, the power scheduler is responsible for setting an appropriate power cap on the nodes associated with the entering job. In relation to the power scheduling invariant reservation based techniques group components by job and make job level power allocations, which are then distributed across the components assigned to the job. The invariant is satisfied if the sum of concurrent job power allocations is less than or equal to the system power bound. Most HPC power scheduling work to date uses this technique.

Generally, reservation techniques merge the job and power scheduling activities. A motivation for approaching job and power scheduling together is the ability to preserve job runtime. Since an insufficient power allocation will increase the runtime of individual jobs, the integrated job and power scheduler should only concurrently run jobs for which there is sufficient power available. One of the challenges in the implementation of reservation techniques is power consumption modeling for the jobs to be executed on the system since the component level power caps must be set prior to job launch.

Dynamic Techniques. Dynamic techniques adjust component power caps during job runtime such that the total power consumed remains beneath the system wide power limit. Proof of the power scheduling invariant must be done at the component level for systems using dynamic techniques since there may not be

<sup>&</sup>lt;sup>9</sup>Job scheduling in such a cluster might resemble job scheduling in a cluster with both fat and thin nodes. Users would select a partition to run their job in based in anticipated power consumption.

| Year | Scheduler | Enforcement | Schedule Time       |

|------|-----------|-------------|---------------------|

| NA   | Naive     | Hard        | Static              |

| 2014 | PARM      | Soft        | Reservation/Dynamic |

| 2015 | SLURM     | Soft        | Reservation         |

| 2015 | RMAP      | Hard        | Reservation         |

| 2015 | PowSched  | Hard        | Dynamic             |

| 2016 | PMJPC     | Soft        | Reservation         |

| 2016 | Shifter   | Hard        | Phase/Dynamic       |

| 2016 | DAPM      | Hard        | Dynamic             |

Table 5. Table relating work to enforcement and scheduling strategy

groupings in space (i.e. nodes) or time to use to simplify the analysis. HPC power scheduling work using dynamic techniques are currently limited.

The highest gains in system-wide power utilization are expected using fully dynamic power scheduling techniques. In static and reservation techniques, a job using less than the power allocated to its components has no mechanism to yield the power to other jobs that may be able to use the power, resulting in unutilized power. Power utilization improvements with dynamic techniques are possible since power can be shifted between jobs based on the current phase of the concurrently executing work. The gains in power utilization may cause application runtime determinism to be lost since power shifted away from a component may not be available when the component returns to a high power consumption phase.

Literature. There are many power schedulers in the literature, eight are discussed in this section. Two common baselines are used for comparison with hardware overprovisioned power schedulers, both of which are covered by what will be referred to as the naive power scheduling strategy. A matrix, comparing the schedulers based on enforcement and schedule time is in Table 5.

**Naive.** The naive power scheduling strategy is the only static technique considered in this thesis. Using this strategy, power is scheduled once at the time

the machine is installed an never changed there after. Using technology such as RAPL the naive strategy can provide hard enforcement of the node power caps. Existing HPC systems can be considered to use this strategy since each node receives a power allocation matching the node TDP. When using the naive scheduling strategy in a hardware overprovisioned system, the system power bound is typically divided evenly across all nodes in the HPC cluster.

Naive power scheduling, while capable of enforcing a system power bound, tends to produce suboptimal performance. A major limitation of the naive strategy is the lack of adaptation to the power consumption behavior of different nodes running different applications. For a given power cap, some application runtimes will be strongly penalized while other applications will not see an impact to runtime (D. A. Ellsworth et al., 2015b)<sup>10</sup>. The basic performance problem with the naive strategy is poor power utilization for applications that consume less than the average power and poor runtime for applications that would consume more than the average power allocation.

PARM. In "Maximizing Throughput of Overprovisioned HPC Data Centers Under a Strict Power Budget", Sarood, Langer, Gupta, and Kale (2014) present a power scheduler named PARM. PARM expects power capping to be available on the hardware and prefers jobs that support both moldability and malleability<sup>11</sup>. When a job is queued or a job terminates, PARM attempts to find and optimal job and power schedule to maximize job throughput. Hardware

$<sup>^{10}</sup>$ The relationship between power cap, consumption, and runtime is interesting and will be covered more in chapter III

$<sup>^{11}</sup>$ A moldable job allows the resource scheduler to launch the job on more or less nodes than were requested at job queue time. A malleable allows the compute resource allocation (e.g. number of nodes) to be changed dynamically at runtime

power capping and job malleability enable PARM to dynamically apply the new configurations.

The theoretical foundation formulates the problem is an integer linear programming (ILP) problem taking into account estimated power for all possible malleable configurations of work to be scheduled. ILP problems are NP-hard in the general case, which makes computing the optimal solution potentially intractable on the timelines required for online job scheduling. Sarood et al. (2014) introduce a power aware speedup metric to reduce the number of variables to be considered by the ILP solver, to improving scheduling time. Quantization of the power settings per node are also used to reduce solution search space.

Like other reservation strategies, PARM requires power estimates to be available apriori to make good scheduling decisions. The time and power costs required to generate sufficiently good power estimates were not discussed in "Maximizing Throughput of Overprovisioned HPC Data Centers Under a Strict Power Budget". Empirical evaluation of PARM was conducted using Charm++ and the baseline for performance comparison was a classically power provisioned cluster (i.e. a cluster where all nodes are allocated TDP). Additionally, simulation using a trace from a production system was used to evaluate PARM's expected performance. Results indicate a significant improvement in average job turnaround time from the baseline. A concern from the work is the time required to compute an updated schedule, the authors note 15 seconds were needed to compute a schedule from a queue of 200 jobs.

RMAP. In "Practical Resource Management in Power-Constrained, High Performance Computing", Patki et al. (2015) present RMAP, a power-aware backfilling scheduler. RMAP expects jobs to be moldable and to have a database

of job configurations that provides node count, power cap, and runtime for the job. When scheduling work, RMAP selects the most runtime efficient configuration for a job that fits within the available power. The job level power bound is enforced through setting a RAPL power cap on the components at job launch time.

Evaluation of RMAP is done exclusively using simulation. The exhaustive database of job configurations and runtime make the simulation results valid even though the simulator has no mechanism to compute runtime increases due to power capping<sup>12</sup>. The cost in runtime and power to generate the configuration database is not discussed and is expected to be substantial since the database must contain an exhaustive search of node counts, core counts, and component power caps.

Supposing such a database exists, RMAP can deliver improved job turn around time and enforce a system power bound.

SLURM. In "Adaptive Resource and Job Management for Limited Power Consumption", Georgiou, Glesser, and Trystram (2015) discuss extensions to SLURM that makes power a schedulable resource. A user is responsible for providing a power cap with their job submission. The job scheduler uses this information to generate job schedules that provide the requested power for all concurrently executing jobs. Enforcement is handled through selecting a DVFS setting for the node processors that guarantees the power cap cannot be exceeded. In addition to changing DVFS settings, SLURM is able to power on/off nodes to change the system power consumption. This scheduler is classified as providing soft enforcement since the DVFS settings are software controlled based on a model of the relation between DVFS setting and maximum power consumption, which is not guaranteed to be correct.

<sup>&</sup>lt;sup>12</sup>Runtime effects of different power caps can be retrieved from the configuration database avoiding the need to compute what the performance would be at a specific power cap.