# INDEX-BASED SEARCH TECHNIQUES FOR VISUALIZATION AND DATA ANALYSIS ALGORITHMS ON MANY-CORE SYSTEMS

by

## **BRENTON JOHN LESSLEY**

## A DISSERTATION

Presented to the Department of Computer and Information Science and the Graduate School of the University of Oregon in partial fulfillment of the requirements for the degree of Doctor of Philosophy

June 2019

## DISSERTATION APPROVAL PAGE

Student: Brenton John Lessley

Title: Index-Based Search Techniques for Visualization and Data Analysis Algorithms on

Many-Core Systems

This dissertation has been accepted and approved in partial fulfillment of the requirements for the Doctor of Philosophy degree in the Department of Computer and Information Science by:

Hank Childs Chair

Boyana Norris Core Member Christopher Wilson Core Member

Eric Torrence Institutional Representative

and

Janet Woodruff-Borden Vice Provost and Dean of the Graduate School

Original approval signatures are on file with the University of Oregon Graduate School.

Degree awarded June 2019

© 2019 Brenton John Lessley All rights reserved.

## DISSERTATION ABSTRACT

Brenton John Lessley

Doctor of Philosophy

Department of Computer and Information Science

June 2019

Title: Index-Based Search Techniques for Visualization and Data Analysis Algorithms on Many-Core Systems

Sorting and hashing are canonical index-based methods to perform searching, and are often sub-routines in many visualization and analysis algorithms. With the emergence of many-core architectures, these algorithms must be rethought to exploit the increased available thread-level parallelism and data-parallelism. Data-parallel primitives (DPP) provide an efficient way to design an algorithm for scalable, platform-portable parallelism. This dissertation considers the following question: What are the best index-based search techniques for visualization and analysis algorithms on diverse many-core systems? To answer this question, we develop new DPP-based techniques, and evaluate their performance against existing techniques for data-intensive visualization and analysis algorithms across different many-core platforms. Then, we synthesize our findings into a collection of best practices and recommended usage. As a result of these efforts, we were able to conclude that our techniques demonstrate viability and leading platform-portable performance for several different search-based use cases. This dissertation is a culmination of previously-published co-authored material.

## **CURRICULUM VITAE**

NAME OF AUTHOR: Brenton John Lessley

## **DEGREES AWARDED:**

**Ph.D.** in Computer ScienceUniversity of Oregon, 2019**M.S.** in Computer ScienceUniversity of Washington Tacoma, 2011**B.S.** in Business AdministrationUniversity of Washington Tacoma, 2009

## AREAS OF SPECIAL INTEREST:

Data-Parallel Algorithms

Parallel Data Structures

High-Performance Computing

Scientific Visualization

## PROFESSIONAL EXPERIENCE:

Graduate Research & Teaching Fellow University of Oregon, 2013 - 2019

Graduate Student Researcher Lawrence Berkeley Nat'l Lab, Summer 2017

Graduate Student Researcher Lawrence Berkeley Nat'l Lab, Summer 2016

Student Developer Google Summer of Code, Summer 2015

## **PUBLICATIONS:**

**Brenton Lessley**, Samuel Li, and Hank Childs (2019). HashFight: A Platform-Portable Hash Table for Multi-Core and Many-Core Architectures (in preparation).

**Brenton Lessley** and Hank Childs (2019). Data-Parallel Hashing Techniques for GPU Architectures (in submission).

- **Brenton Lessley**, Talita Perciano, Colleen Heinemann, David Camp, Hank Childs, and E. Wes Bethel (2018). DPP-PMRF: Rethinking Optimization for a Probabilistic Graphical Model Using Data-Parallel Primitives. *Proceedings of the IEEE Symposium on Large Data Visualization and Analysis (LDAV)*, Berlin, Germany, pp. 1–11.

- **Brenton Lessley**, Kenneth Moreland, Matthew Larsen and Hank Childs (2017). Techniques for Data-Parallel Searching for Duplicate Elements. *Proceedings of the IEEE Symposium on Large Data Visualization and Analysis (LDAV)*, Phoenix, AZ, pp. 1–5.

- **Brenton Lessley**, Talita Perciano, Manish Mathai, Hank Childs and E. Wes Bethel (2017). Maximal Clique Enumeration with Data-Parallel Primitives. *Proceedings of the IEEE Symposium on Large Data Visualization and Analysis* (*LDAV*), Phoenix, AZ, pp. 16–25.

- **Brenton Lessley**, Roba Binyahib, Robert Maynard, and Hank Childs (2016). External Facelist Calculation with Data-Parallel Primitives. *Proceedings of EuroGraphics Symposium on Parallel Graphics and Visualization (EGPGV)*, Groningen, The Netherlands, pp. 10–20.

- Sergio Davalos, Altaf Merchant, Gregory Rose, **Brenton Lessley**, and Ankur Teredesai (2015). 'The Good Old Days': An Examination of Nostalgia in Facebook Posts. *International Journal of Human-Computer Studies*, vol. 83, pp. 83–93.

- Daniel Lowd, **Brenton Lessley**, and Mino De Raj (2014). Towards Adversarial Reasoning in Statistical Relational Domains. *AAAI-14 Workshop on Statistical Relational AI (Star AI 2014)*, Quebec City, Canada.

- **Brenton Lessley**, Matthew Alden, Daniel Bryan, and Arindam Tripathy (2012). Detection of Financial Statement Fraud Using Evolutionary Algorithms. *Journal of Emerging Technologies in Accounting*, vol. 9, no. 1, pp. 71–94.

#### **ACKNOWLEDGEMENTS**

The path towards completing my Ph.D. has been quite an adventure, always seeing the light at the end of the tunnel, yet always one more challenging task to complete. In short, the past six years have more or less been a mind-training game that teaches me how to stay focused on a goal and work towards it tirelessly until completion, despite countless thoughts of giving up. To reach this point took more self-motivation than I ever knew I had and even more motivation and encouragement from those around me.

Throughout the Ph.D. process, my parents have provided the best support, advice, and encouragement that I could have asked for. They have been my number one cheering squad and, with great humor, make sure that I always remain optimistic, from one paper or milestone to the next. I cannot thank them enough.

The same thank you goes to my very good friend, Agrima, who has patiently heard every high note and low note from me while completing this long process. I know she sacrificed a lot of fun to join in on my many work sessions or postpone a trip due to a looming milestone. I truly appreciate her patience and sense of humor, and can't thank her enough.

If it wasn't for my advisor, Hank Childs, I likely would not have even completed the PhD degree. From the day I joined the CDUX research group and planned out a road map towards completing the PhD, Hank has helped me become a self-sufficient researcher and provided countless opportunities to hone my area of expertise. I thank him for all the guidance and support he has provided me, particularly in the past year. I am proud of all the work that we have completed and published during the four years under his advisement.

During my time at the University of Oregon, I have made some of my best friends, who provided so many nice memories and made the hard work much more enjoyable, even if it was as simple as going to a basketball or football game after completing some goal, holding a house party, or going to Starbucks for a coding session. You know who you are—thank you, you are the best.

I was fortunate to have many awesome officemates during my six years in Deschutes Hall, all of whom provided plenty of great humor, language learning, and a benchmark for working harder. I can confidently say that our whiteboards were rarely empty. To Ali, Pedram, Azaad, Soheil, Sam, Vince, Stephanie, Abhishek, Manish, Garrett, Sudhanshu, and Steve, it was a great pleasure. This thank you also extends to my fellow labmates and friends in CDUX. From the group parties and practice presentations to random office conversations, your sense of humor and friendship were awesome.

While most of my time was spent at the University of Oregon, I also spent two great summers at the Lawrence Berkeley National Lab with the Data Analytics & Visualization Group. The research projects and papers I completed during this time really boosted my confidence as a researcher and led to a pipeline of exciting work. I was lucky to have Wes Bethel and Talita Perciano as my mentors, and I appreciated the discussions and collaboration with David Camp, Colleen Heinemann, Dmitriy Morozov, Sugeerth Murugesan, Dani Ushizima, Burlen Loring, and Hari Krishnan.

Finally, I would like to thank Boyana Norris, Chris Wilson, and Eric Torrence for their willingness to serve on my PhD committee and provide great feedback throughout the dissertation phase.

## TABLE OF CONTENTS

| Ch  | apter |         |             |                              | Pa | age |

|-----|-------|---------|-------------|------------------------------|----|-----|

| I.  | IN'   | TRODU   | JCTION      |                              |    | 1   |

|     | 1.1.  | Dissert | tation Out  | line                         | •  | 4   |

|     | 1.2.  | Co-Au   | thored Ma   | iterial                      |    | 5   |

| Ι   | Tec   | hniqu   | es          |                              |    | 7   |

| II. | BA    | CKGR    | OUND .      |                              | •  | 9   |

|     | 2.1.  | Paralle | l Computi   | ng & Data-Parallelism        | •  | 9   |

|     | 2.2.  | Data P  | arallel Pri | mitives                      |    | 12  |

|     | 2.3.  | Genera  | al-Purpose  | GPU Computing                |    | 15  |

|     |       | 2.3.1.  | SIMT A      | chitecture                   | •  | 17  |

|     |       | 2.3.2.  | Optimal     | Performance Criteria         | •  | 19  |

|     | 2.4.  | Index-  | Based Sea   | rching                       | •  | 22  |

|     |       | 2.4.1.  | Searchin    | g Via Sorting                |    | 24  |

|     |       | 2.4.2.  | Searchin    | g Via Hashing                |    | 25  |

|     | 2.5.  | Data-P  | arallel Ha  | shing Techniques             |    | 30  |

|     |       | 2.5.1.  | Open-ad     | dressing Probing             |    | 31  |

|     |       |         | 2.5.1.1.    | Linear Probing-based Hashing |    | 32  |

|     |       |         | 2.5.1.2.    | Cuckoo-based Hashing         |    | 33  |

|     |       |         | 2.5.1.3.    | Double Hashing               |    | 38  |

|     |       |         | 2.5.1.4.    | Robin Hood-based Hashing     |    | 41  |

|     |       | 2.5.2.  | Separate    | Chaining                     |    | 43  |

| Chapter           |                                      | Page |

|-------------------|--------------------------------------|------|

| 2.6.              | Conclusion                           | 48   |

| III. DA           | ATA-PARALLEL SEARCHING FOR DUPLICATE |      |

| EL                | EMENTS                               | 49   |

| 3.1.              | Sorting-Based Algorithm              | 49   |

| 3.2.              | Hashing-Based Algorithm              | 51   |

|                   | 3.2.1. Algorithm Details             | 52   |

| 3.3.              | Dissertation Question                | 56   |

| IV. H             | ASHFIGHT: DATA-PARALLEL HASH TABLE   | 57   |

| 4.1.              | Design                               | 57   |

|                   | 4.1.1. Insertion Phase               | 59   |

|                   | 4.1.2. Query Phase                   | 64   |

|                   | 4.1.3. Peak Memory Footprint         | 66   |

| 4.2.              | Dissertation Question                | 67   |

| II A <sub>l</sub> | pplications                          | 68   |

| V. EX             | KTERNAL FACELIST CALCULATION         | 70   |

| 5.1.              | External Facelist Calculation        | 70   |

| 5.2.              | Combination and Challenges           | 72   |

| 5.3.              | Related Work                         | 72   |

| 5.4.              | Algorithms                           | 74   |

| 5.5.              | Experiment Overview                  | 75   |

|                   | 5.5.1. Factors                       | 75   |

|                   | 5.5.2. Software Implementation       | 76   |

|                   | 5.5.3. Configurations                | 76   |

| Chapter |        |                                          | Page |

|---------|--------|------------------------------------------|------|

|         |        | 5.5.3.1. Data Sets                       | . 77 |

|         |        | 5.5.3.2. Hardware Platforms              | . 77 |

|         |        | 5.5.3.3. Hash Table Size                 | . 78 |

| 5.6.    | Result | s                                        | . 78 |

|         | 5.6.1. | Phase 1: Base Case                       | . 79 |

|         | 5.6.2. | Phase 2: Hash Table Size                 | . 79 |

|         | 5.6.3. | Phase 3: Architecture                    | . 80 |

|         | 5.6.4. | Phase 4: Data Sets                       | . 81 |

|         | 5.6.5. | Phase 5: Concurrency                     | . 82 |

| 5.7.    | Compa  | aring to Existing Serial Implementations | . 83 |

| 5.8.    | Conclu | asion                                    | . 84 |

| VI. HA  | ASHINO | G INTEGER KEY-VALUE PAIRS                | . 86 |

| 6.1.    | Backg  | round                                    | . 86 |

|         | 6.1.1. | Parallel Hashing                         | . 86 |

|         |        | 6.1.1.1. CPU-based Techniques            | . 87 |

|         |        | 6.1.1.2. GPU-based Techniques            | . 88 |

| 6.2.    | Experi | mental Overview                          | . 91 |

|         | 6.2.1. | Algorithms                               | . 91 |

|         | 6.2.2. | Platforms                                | . 92 |

|         | 6.2.3. | Dataset Sizes                            | . 93 |

|         | 6.2.4. | Hash Table Load Factors                  | . 94 |

|         | 6.2.5. | Query Failure Rates                      | . 94 |

| 6.3.    | Result | s                                        | . 94 |

|         | 6.3.1. | GPU Experiments                          | . 95 |

|         |        | 6.3.1.1. Vary Data Size                  | . 95 |

| Chapter |           |            | Page                                       |

|---------|-----------|------------|--------------------------------------------|

|         |           | 6.3.1.2.   | Vary Load Factor                           |

|         |           | 6.3.1.3.   | Vary Query Failure Rate                    |

|         | 6.3.2.    | CPU Exp    | periments                                  |

| 6.4.    | Conclu    | ision      |                                            |

| VII. M  | AXIMA     | L CLIQU    | E ENUMERATION                              |

| 7.1.    | Backg     | round and  | Related Work                               |

|         | 7.1.1.    | Maximal    | Clique Enumeration                         |

|         | 7.1.2.    | Related V  | Work                                       |

|         |           | 7.1.2.1.   | Visualization and Data Parallel Primitives |

|         |           | 7.1.2.2.   | Maximal Clique Enumeration                 |

| 7.2.    | Algori    | thm        |                                            |

|         | 7.2.1.    | Initializa | tion                                       |

|         | 7.2.2.    | Hashing-   | Based Algorithm                            |

|         |           | 7.2.2.1.   | Algorithm Overview                         |

|         |           | 7.2.2.2.   | Algorithm Details                          |

| 7.3.    | Experi    | mental Ov  | rerview                                    |

|         | 7.3.1.    | Software   | Implementation                             |

|         | 7.3.2.    | Test Plati | forms                                      |

|         | 7.3.3.    | Test Data  | ı Sets                                     |

| 7.4.    | Results   | s          |                                            |

|         | 7.4.1.    | Phase 1:   | CPU                                        |

|         | 7.4.2.    | Phase 2:   | GPU                                        |

| 7.5.    | Conclu    | ision      |                                            |

| VIII CE | O A DLI D | OV CED IV  | IAGE SEGMENTATION 120                      |

| Chapter    |         |            | Pag                                         |

|------------|---------|------------|---------------------------------------------|

| 8.1.       | Backgr  | round      |                                             |

|            | 8.1.1.  | MRF-bas    | sed Image Segmentation                      |

|            | 8.1.2.  | Performa   | ance and Portability in Graph-based Methods |

| 8.2.       | Algori  | thm Desig  | n                                           |

|            | 8.2.1.  | Parallel M | MRF                                         |

|            | 8.2.2.  | DPP For    | mulation of PMRF                            |

|            |         | 8.2.2.1.   | Initialization                              |

|            |         | 8.2.2.2.   | Optimization                                |

| 8.3.       | Results | s          |                                             |

|            | 8.3.1.  | Source D   | Oata, Reference Implementation, and         |

|            |         | Computa    | tional Platforms                            |

|            |         | 8.3.1.1.   | Datasets                                    |

|            |         | 8.3.1.2.   | Hardware Platforms                          |

|            |         | 8.3.1.3.   | Software Environment                        |

|            |         | 8.3.1.4.   | Reference Implementation of PMRF            |

|            | 8.3.2.  | Verificati | on of Correctness                           |

|            |         | 8.3.2.1.   | Methodology: Evaluation Metrics             |

|            |         | 8.3.2.2.   | Verification Results                        |

|            | 8.3.3.  | Performa   | ance and Scalability Studies                |

|            |         | 8.3.3.1.   | Methodology                                 |

|            |         | 8.3.3.2.   | CPU Runtime Comparison: OpenMP              |

|            |         |            | vs. DPP-PMRF                                |

|            |         | 8.3.3.3.   | Strong Scaling Results                      |

|            |         | 8.3.3.4.   | Platform Portability: GPU Results           |

| <i>Q 1</i> | Conclu  | ision      | 15.                                         |

| Cha | apter |          |                                      | Page |

|-----|-------|----------|--------------------------------------|------|

| III | В     | est Pr   | actices                              | 156  |

| IX. | BE    | EST PRA  | ACTICES FOR DUPLICATE ELEMENT        |      |

|     | SE    | ARCHII   | NG                                   | 158  |

|     | 9.1.  | Introdu  | action                               | 158  |

|     | 9.2.  | Experi   | ment Overview                        | 159  |

|     |       | 9.2.1.   | Algorithm                            | 159  |

|     |       |          | 9.2.1.1. Algorithms                  | 160  |

|     |       |          | 9.2.1.2. Hash Function               | 161  |

|     |       | 9.2.2.   | Hardware Architecture                | 162  |

|     |       | 9.2.3.   | Data set                             | 162  |

|     | 9.3.  | Results  | S                                    | 163  |

|     |       | 9.3.1.   | Phase 1: Hash Functions              | 163  |

|     |       | 9.3.2.   | Phase 2: Architectures               | 166  |

|     |       | 9.3.3.   | Phase 3: Irregular Data Sets         | 169  |

|     | 9.4.  | Conclu   | sion                                 | 171  |

| X.  | SU    | MMAR     | RY, FINDINGS & RECOMMENDATIONS       | 174  |

|     | 10.1  | . Summ   | ary                                  | 174  |

|     | 10.2  | . Synthe | sis of Findings                      | 175  |

|     |       | 10.2.1.  | Decision: Search Routine             | 175  |

|     |       | 10.2.2.  | Decision: Duplicate Element Search   | 176  |

|     |       | 10.2.3.  | Decision: Index-Based Data Structure | 178  |

|     |       | 10.2.4.  | Decision: Static Hash Table          | 178  |

|     | 10.3  | . Recom  | mendations for Future Study          | 180  |

| Chapter                       | Page |

|-------------------------------|------|

|                               |      |

| APPENDIX: LEMMAS AND THEOREMS |      |

| REFERENCES CITED              |      |

## LIST OF FIGURES

| Figure | Page                                                           |

|--------|----------------------------------------------------------------|

| 1.     | Visualizations of two of the 3D data sets, Enzo-10M and        |

|        | Nek-50M, used in the external facelist calculation experiments |

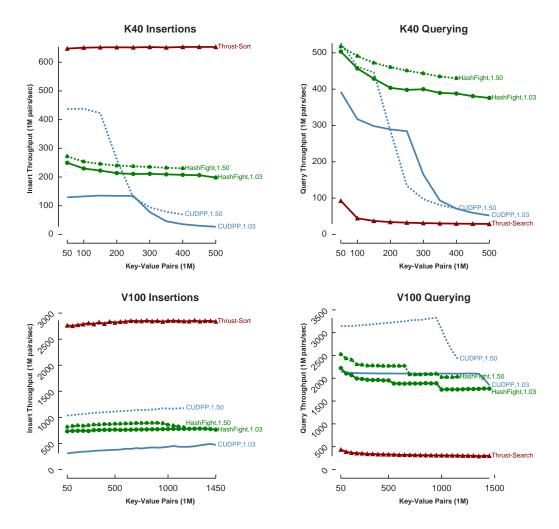

| 2.     | GPU insertion and query throughput as the number of            |

|        | key-value pairs is varied on the K40 and V100 devices          |

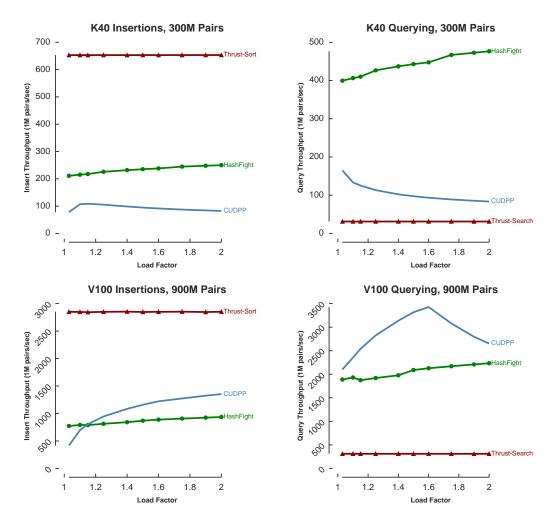

| 3.     | GPU insertion and query throughput as the hash table load      |

|        | factor, or capacity, is varied on the K40 and V100 devices     |

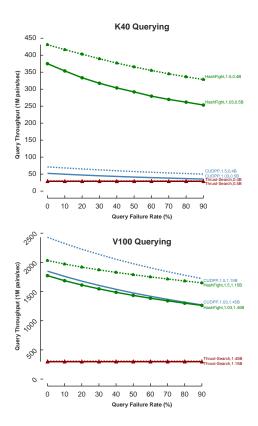

| 4.     | GPU query throughput as the percentage of failed, or           |

|        | unsuccessful, queries is varied on the K40 and V100 devices    |

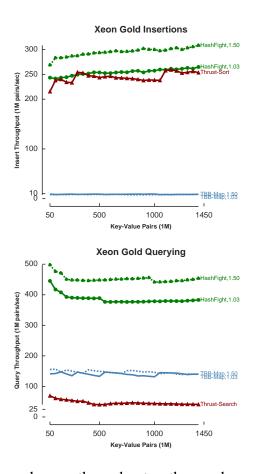

| 5.     | CPU insertion and query throughput as the number of            |

|        | key-value pairs is varied on the Xeon Gold device              |

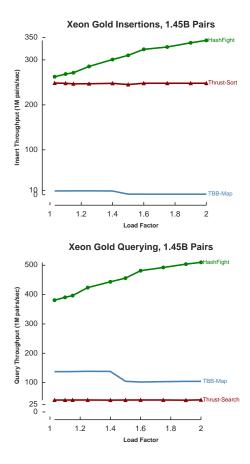

| 6.     | CPU insertion and query throughput as the hash table load      |

|        | factor is varied on the Xeon Gold device                       |

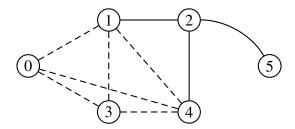

| 7.     | Example undirected graph that contains maximal cliques         |

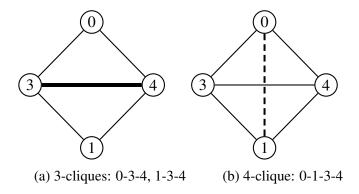

| 8.     | Initialization process to obtain a v-graph representation of   |

|        | an undirected graph                                            |

| 9.     | Clique expansion process for an example undirected graph       |

| 10.    | Example of clique expansion that merges two equally-           |

|        | sized cliques to produce a new larger clique                   |

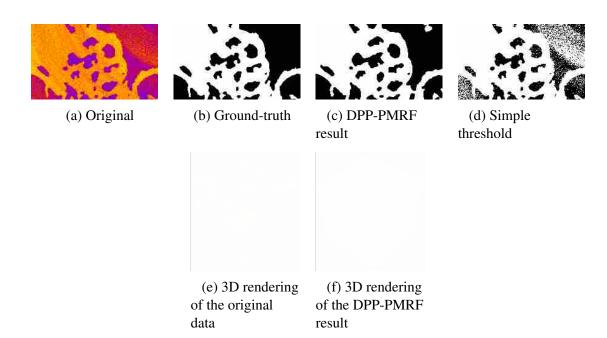

| 11.    | Results of applying our DPP-PMRF image segmentation            |

|        | algorithm to a synthetic image dataset                         |

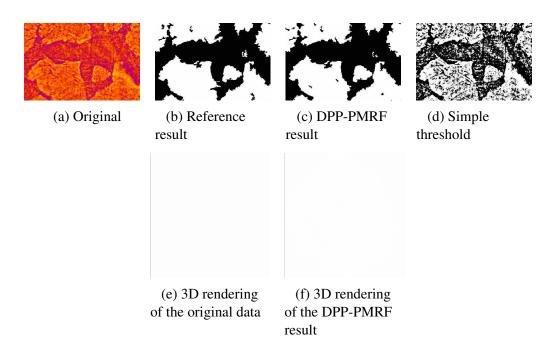

| 12.    | Results of applying our DPP-PMRF image segmentation            |

|        | algorithm to an experimental image dataset                     |

| Figure | Page                                                                 |

|--------|----------------------------------------------------------------------|

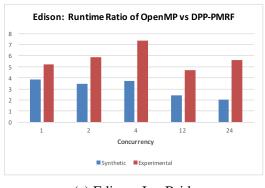

| 13.    | Comparison of image segmentation runtimes of our                     |

|        | DPP-PMRF algorithm and a reference implementation at                 |

|        | varying concurrency                                                  |

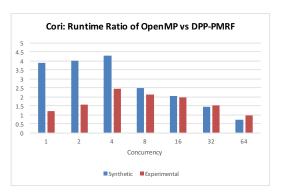

| 14.    | Image segmentation runtime speedup of synthetic and                  |

|        | experimental image datasets on the Edison and Cori CPU platforms 150 |

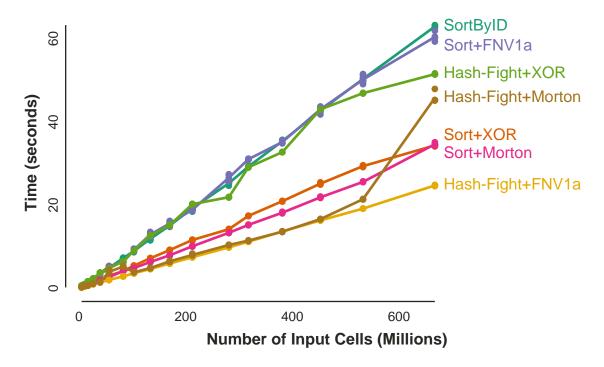

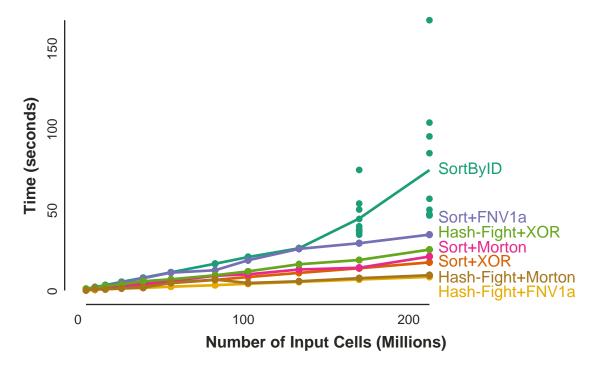

| 15.    | Intel Haswell CPU runtime comparison of all                          |

|        | algorithm/hash function pairs for external facelist                  |

|        | calculation, using a mesh dataset with non-randomized points 164     |

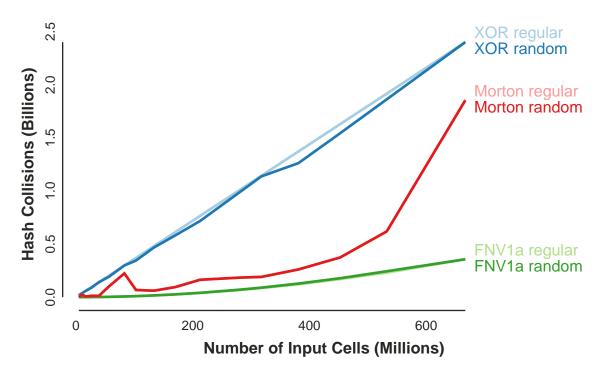

| 16.    | Comparison of the number of collisions produced by                   |

|        | different hash functions in external facelist calculation,           |

|        | over mesh datasets with both random and non-randomized points 165    |

| 17.    | Intel Knights Landing CPU runtime comparison of                      |

|        | all algorithm/hash function pairs for external facelist              |

|        | calculation, using a mesh datset with non-randomized points 167      |

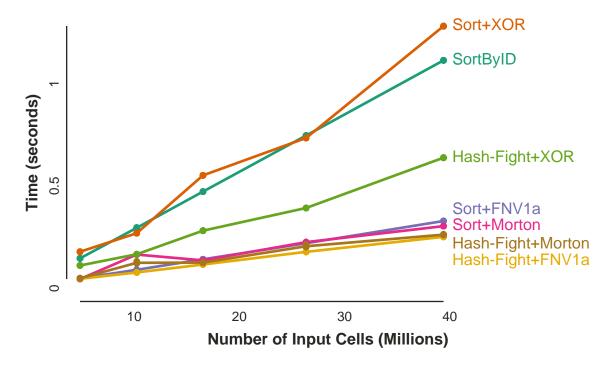

| 18.    | NVIDIA Tesla P100 GPU runtime comparison of                          |

|        | all algorithm/hash function pairs for external facelist              |

|        | calculation, using a mesh dataset with non-randomized points 168     |

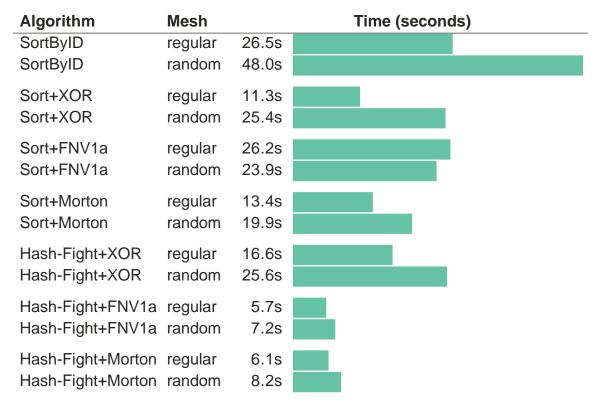

| 19.    | Comparison of the Intel Haswell CPU runtime                          |

|        | performance for external facelist calculation using mesh             |

|        | datsets with both randomized and non-randomized points               |

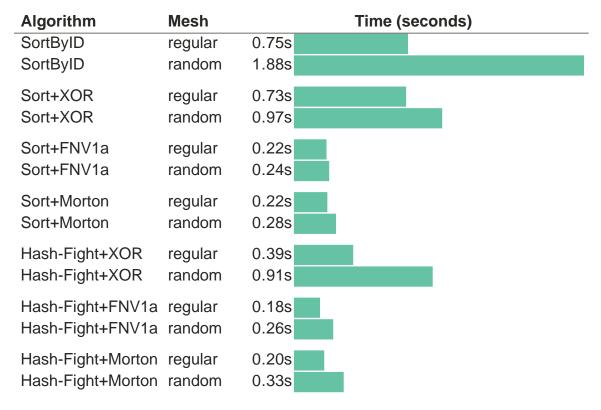

| 20.    | Comparison of the Intel Knights Landing CPU runtime                  |

|        | performance for external facelist calculation using mesh             |

|        | datsets with both randomized and non-randomized points               |

| Figure | Page                                                     |

|--------|----------------------------------------------------------|

| 21.    | Comparison of the NVIDIA Tesla P100 GPU runtime          |

|        | performance for external facelist calculation using mesh |

|        | datsets with both randomized and non-randomized points   |

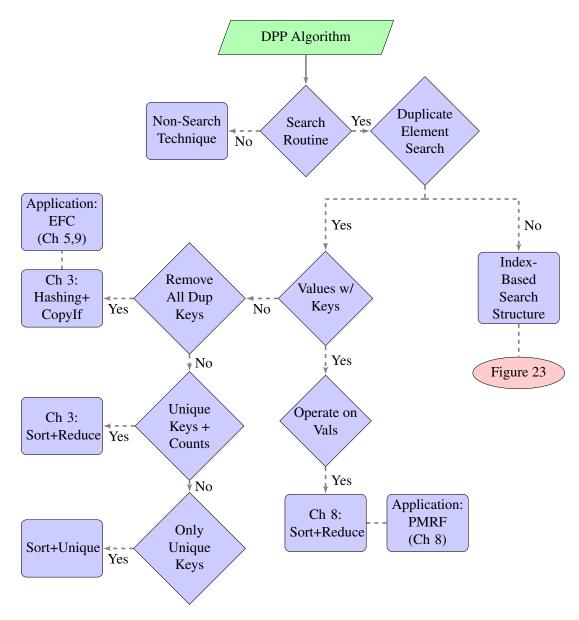

| 22.    | Decision tree flowchart that guides the selection of the |

|        | most-suitable index-based search technique for a given   |

|        | DPP-based algorithm                                      |

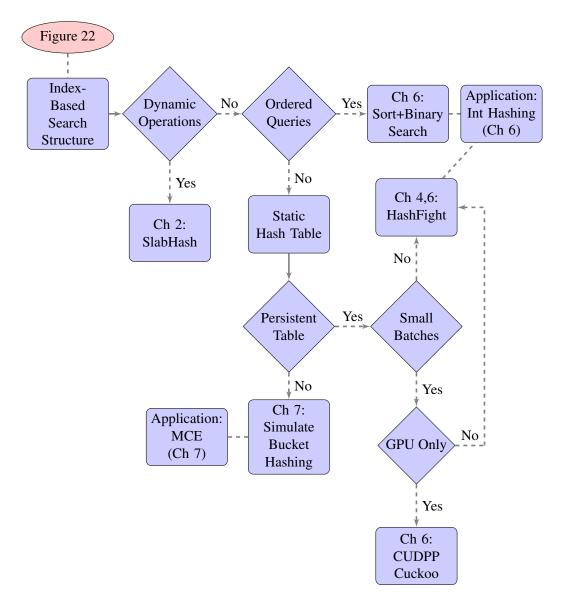

| 23.    | Subset of a decision tree flowchart that guides the      |

|        | selection of the most-suitable index-based search        |

|        | structure, such as a hash table, for a given DPP-based   |

|        | algorithm                                                |

## LIST OF TABLES

| Table | Page                                                                       |

|-------|----------------------------------------------------------------------------|

| 1.    | Comparison of CPU execution times (sec) for our sorting-                   |

|       | and hashing-based algorithms for external facelist calculation 79          |

| 2.    | Individual CPU phase times (sec) for our sorting-based                     |

|       | algorithm for external facelist calculation                                |

| 3.    | Individual CPU phase times (sec) for select DPP                            |

|       | operations of our hashing-based algorithm for external                     |

|       | facelist calculation                                                       |

| 4.    | CPU execution time (sec) of our hashing-based algorithm                    |

|       | for external facelist calculation, as a function of hash table size 80     |

| 5.    | GPU execution time (sec) for the main computation of our                   |

|       | sorting- and hashing-based algorithms for external facelist calculation 80 |

| 6.    | Individual GPU phase times (sec) for our sorting-based                     |

|       | algorithm for external facelist calculation                                |

| 7.    | Individual GPU phase times (sec) for our hashing-based                     |

|       | algorithm for external facelist calculation                                |

| 8.    | CPU and GPU execution times (sec) for different data                       |

|       | set/algorithm pairs for external facelist calculation                      |

| 9.    | Impact of the number of CPU cores on the execution                         |

|       | time (sec) of our sorting- and hashing-based algorithms                    |

|       | for external facelist calculation on a mesh dataset with                   |

|       | non-randomized points                                                      |

| Table | Page                                                                  |

|-------|-----------------------------------------------------------------------|

| 10.   | Impact of the number of CPU cores on the execution                    |

|       | time (sec) of our sorting- and hashing-based algorithms               |

|       | for external facelist calculation on a mesh dataset with              |

|       | randomized points                                                     |

| 11.   | Single-core (serial) CPU execution time (sec) for different           |

|       | EFC data set/algorithm pairs                                          |

| 12.   | Statistics for a subset of the real-world test graphs used in         |

|       | our maximal clique enumeration experiments                            |

| 13.   | Total CPU execution times (sec) for our maximal clique                |

|       | enumeration algorithm, as compared to serial benchmark algorithms 125 |

| 14.   | Total CPU execution times (sec) for our maximal clique                |

|       | enumeration algorithm, as compared to a distributed-                  |

|       | memory benchmark algorithm                                            |

| 15.   | Total GPU execution times (sec) for our maximal clique                |

|       | enumeration algorithm over a set of real-world test graphs            |

| 16.   | GPU image segmentation runtimes (sec) for our graph-                  |

|       | based DPP-PMRF algorithm                                              |

| 17.   | Intel Haswell CPU runtimes (sec) for each of the primary              |

|       | data-parallel operations of our sorting-based algorithms              |

|       | for external facelist calculation                                     |

| 18.   | NVIDIA Tesla P100 GPU runtimes (sec) for each of                      |

|       | the primary data-parallel operations of our sort-based                |

|       | algorithms for external facelist calculation                          |

## LIST OF ALGORITHMS

| Algorithm |                                                                                                                                    | Page |

|-----------|------------------------------------------------------------------------------------------------------------------------------------|------|

| 1         | Pseudocode for the sorting-based technique for identifying duplicate elements of a comparable type T                               | 50   |

| 2         | Pseudocode for the hashing-based technique for identifying duplicate elements of a comparable type T                               | 53   |

| 3         | Pseudocode for the construction of a v-graph data structure used in our maximal clique enumeration algorithm                       | 114  |

| 4         | Pseudocode for our DPP-based maximal clique enumeration algorithm                                                                  | 119  |

| 5         | Pseudocode of the benchmark Parallel MRF (PMRF) algorithm for performing graph-based image segmentation using Markov Random Fields | 134  |

| 6         | Pseudocode of our DPP-based DPP-PMRF algorithm for performing graph-based image segmentation using Markov Random Fields            | 137  |

## LIST OF LISTINGS

| Listing |                                                   | Page |

|---------|---------------------------------------------------|------|

| 1.      | Pseudocode for the HashFight Insert function      | . 60 |

| 2.      | Pseudocode for the HashFight Fight function       | . 62 |

| 3.      | Pseudocode for the HashFight CheckWinner function | . 63 |

| 4.      | Pseudocode for the HashFight Query function       | . 64 |

| 5.      | Pseudocode for the HashFight Probe function       | . 65 |

## CHAPTER I

## INTRODUCTION

Within the scientific visualization and data analysis domains, a large body of algorithms are built upon search-based subroutines, in which one or more elements are queried within a larger set of elements. Canonical methods to perform this search task are primarily based on sorting, hashing, and spatial partitioning [66], each using an implementation-specific data structure to efficiently facilitate the searching operation. These data structures can be as simple as a sorted (ordered) variant of the original unordered elements, a hash table, or a tree-based partitioning of the elements (e.g., with a kd-tree, octree, or binary search tree). In searching via sorting and hashing, the sorted array and hash table can be considered *index-based* data structures, since elements are logically stored and indexed within a linear array.

The evolution of hardware architectures over the past two decades have informed the research directions for index-based search techniques. With the emergence of multi-processor CPU architectures and thread-based programming, significant research initially focused on the design of lock-free, parallel index-based search techniques for single-node, shared memory [101, 134, 45]. Subsequently, studies began to investigate external-memory (off-chip) and multi-node, distributed-memory parallel techniques that could accommodate the oncoming shift towards large-scale data processing [15, 22]. Over the past decade, computational platforms have advanced from nodes containing small numbers of CPU cores to nodes containing many-core GPU accelerators with massive threading and memory bandwidth capabilities. With this increase in available parallelism comes the ability to process larger workloads and data in parallel [95, 54]. By explicitly parallelizing fine-grained computations that operate on this data, scalable data-parallelism can be attained, whereby a single instruction is performed over multiple

data elements (SIMD) in parallel (e.g., via a vector instruction), as opposed to over single scalar data values (SISD).

Traditional single-threaded (non-parallel) and multi-threaded index-based search designs, however, do not demonstrate node-level scalability for the massive number of concurrent threads and data-parallelism offered by emerging many-core architectures, particularly GPU accelerators. Hardware differences in on-chip caching, shared memory, instruction execution (e.g., vectorization and branch prediction), and threading models require new code implementations to achieve optimal performance on these emerging architectures. Additionally, algorithms that use these search techniques are not structurally designed to exploit increased available parallelism, e.g., due to significant non-parallel code and an insufficient amount of parallel work.

For software developers and projects, this has led to a significant change. Algorithms cannot simply be ported over to a new architecture or platform while retaining optimal performance, and they may need to be supported on multiple architectures simultaneously. One approach to this problem is to maintain a different algorithm implementation for each different architecture. For example, developers can provide an efficient NVIDIA CUDA implementation [115] for NVIDIA GPUs and an efficient Intel TBB implementation [53] for Intel CPUs (or  $N \times M$  separate implementations for N algorithms and M architectures). However, this approach has drawbacks, as it increases software development time and is neither adaptable nor future-proof to new processor architectures, and also would require separate algorithm implementations.

A more preferred approach is to re-think an algorithm in terms of *data-parallel primitives* (DPPs), which are highly-optimized "building block" operations that are combined together to compose a larger algorithm. To qualify as a DPP, an operation must execute in  $O(\log N)$  time on an array of size N, given the availability of N or more

processing units (e.g., parallel hardware threads or cores) [11]. Well-known operations, such as map, reduce, gather, scatter, scan (prefix sum), and sort all meet this property, and are some of the most commonly-used DPPs. By providing efficient implementations of each DPP for each different platform architecture, a single algorithm composed of DPPs can be executed efficiently across multiple platforms. The DPP paradigm thus provides a way to explicitly design and program an algorithm for scalable, platform-portable dataparallelism, as increases in processing units and data enable unrestricted increases in speedup.

In this dissertation work, we answer the following dissertation question: What are the best index-based search techniques for visualization and analysis algorithms on diverse many-core systems? To answer this question, we needed to develop a novel hashing-based search technique that is designed entirely in terms of DPPs. Additionally, we propose novel methods of using existing sorting- and hashing-based search techniques. We introduce these techniques in two phases:

- 1. Design sorting- and hashing-based techniques for the search of duplicate elements.

- 2. Expand the hashing-based technique to a general-purpose hash table data structure.

Then, we consider three data-intensive visualization and/or analysis algorithms, each of which has a search-oriented procedure as part of the algorithm. In each case, our first step is to re-think these algorithms in terms of these techniques and other DPPs. Finally, we look for patterns and commonalities across these solutions, and synthesize our findings with a set of best practices and a decision tree flowchart that guides the selection of a most-suitable search technique.

The culmination of this work answers our dissertation question, i.e., identifying the best index-based search techniques for visualization and analysis algorithms on diverse many-core systems. This question is the subject of this dissertation.

#### 1.1 Dissertation Outline

This dissertation is organized into the following three parts:

1. Techniques: Chapters II through IV.

2. Applications: Chapters V through VIII.

3. Best Practices: Chapters IX and X.

Part I surveys existing index-based search techniques and then introduces new data-parallel index-based search techniques. Part II incorporates the techniques of Part I into the design of data-parallel algorithms for different scientific visualization and data analysis algorithms. Part III synthesizes the findings and best practices of Parts I and II.

In particular, the content of the individual dissertation chapters is as follows. Chapter II provides a background data-parallelism and existing index-based search techniques. Chapter III introduces new data-parallel sorting- and hashing-based techniques for duplicate element searching. Chapter IV expands the hashing-based techniques of Chapter III to a general-purpose hash table data structure. Chapter V applies the techniques of Chapter III to the scientific visualization algorithm of external facelist calculation (EFC). Chapter VI applies the techniques of Chapter IV to the task of hashing unsigned integers. Chapter VII applies the techniques of Chapter III to the graph algorithm of maximal clique enumeration (MCE). Chapter VIII applies the techniques of Chapter III to graph-based image segmentation using Markov random fields (MRF). Chapter IX identifies specific test configurations and use cases that lead to the best performance for the duplicate element searching task of Chapters III and V. Chapter X concludes this dissertation by synthesizing the findings and best practices of the previous chapters and offering recommendations for future research.

4

#### 1.2 Co-Authored Material

A significant portion of the content in this dissertation is adopted from collaborative research work and manuscripts that I have completed, as lead author, during my PhD program. Each manuscript has been either already published or is currently under submission at a journal. The content of each manuscript includes the text, figures, and experimental results, all of which are primarily composed by myself. The following listing indicates the chapters that contain manuscript content and the authors that contributed to the manuscript (i.e., myself and co-authors); note that a detailed division of labor for each manuscript is provided at the beginning of its corresponding chapter.

- Chapter II is mainly based on an under-submission journal publication, and is a collaboration between Hank Childs and myself.

- Chapters III and V are mainly based on an accepted conference publication, and is a

collaboration between Roba Binyahib, Robert Maynard, Hank Childs, and myself.

The content of this publication is divided between the two chapters, without any

overlap.

- Chapters IV and VI are mainly based on an under-submission journal publication,

and is a collaboration between Samuel Li, Hank Childs, and myself. The content of

this publication is divided between the two chapters, without any overlap.

- Chapter VII is mainly based on an accepted conference publication, and is a collaboration between Talita Perciano, Manish Mathai, Hank Childs, Wes Bethel, and myself.

- Chapter VIII is mainly based on an accepted conference publication, and is a collaboration between Talita Perciano, Colleen Heinemann, David Camp, Hank Childs, Wes Bethel, and myself.

Chapter IX is mainly based on an accepted conference publication, and is a collaboration between Kenneth Moreland, Matthew Larsen, Hank Childs, and myself.

## Part I

**Techniques**

In this part of the dissertation, we provide a background on data-parallelism and index-based searching, and then introduce our collection of DPP-based search techniques for duplicate element detection and hashing.

## CHAPTER II

## **BACKGROUND**

The task of searching for elements in an indexed array is a well-studied problem in computer science. Canonical methods for this task are primarily based on sorting and hashing [66]. This chapter provides the necessary background to understand these methods and the work of this dissertation. Specifically, the following concepts are covered in sequence, each in their own section:

- 1. Parallel Computing and Data-Parallelism

- 2. Data-Parallel Primitives

- 3. General Purpose GPU Computing

- 4. Index-Based Searching

- 5. Data-Parallel Hashing Techniques

The material in this chapter is primarily adopted from a collaborative survey manuscript completed by myself and Hank Childs [80]. As lead author of this manuscript, I contributed the majority of the literature review and paper writing. Hank Childs provided significant guidance towards optimizing the scope of the survey, improving the message of our contributions, and editing the final submission. This manuscript is currently in preparation for a journal submission and is based on the work of my Ph.D. area exam.

## 2.1 Parallel Computing & Data-Parallelism

Lamport [73] defines *concurrency* as the decomposition of a process into independently-executing events (subprograms or instructions) that do not causally affect each other. *Parallelism* occurs when these events are all executed at the same time and perform roughly the same work. According to Amdahl [4], a program contains both non-parallelizable, or serial, work and parallelizable work. Given *P* processors (e.g., hardware

cores or threads) available to perform parallelizable work, *Amdahl's Law* defines the *speedup*  $S_P$  of a program as  $S_P \leq T_1/T_P$ , where  $T_1$  and  $T_P$  are the times to complete the program with a single processor and P processors, respectively. As  $P \to \infty$ ,  $S_\infty \leq \frac{1}{f}$ , where f is the fraction of serial work in the program. So, the speedup, or *scalability*, of a program is limited by its inherent serial work, as the number of processors increases. Ideally, a linear speedup is desired, such that P processors achieve a speedup of P; a speedup proportional to P is said to be scalable.

Often a programmer writes and executes a program without explicit design for parallelism, assuming that the underlying hardware and compiler will automatically deliver a speedup via greater processor cores and transistors, instruction pipelining, vectorization, memory caching, etc [54]. While these automatic improvements may benefit *perfectly parallelizable work*, they are not guaranteed to address *imperfectly parallelizable* work that contains data dependencies, synchronization, high latency cache misses, etc [95]. To make this work perfectly parallelizable, the program must be refactored, or redesigned, to expose more *explicit* parallelism that can increase the speedup ( $S_P$ ). Brent [16] shows that this explicit parallelism should first seek to minimize the *span* of the program, which is the longest chain of tasks that must be executed sequentially in order. Defining  $T_1$  as the total serial work and  $T_\infty$  as the span, *Brent's Lemma* relates the work and span as  $T_P \leq (T_1 - T_\infty)/P + T_\infty$ . This lemma reveals that the perfectly parallelizable work  $T_1 - T_\infty$  is scalable with  $T_0$ , while the imperfectly parallelizable span takes time  $T_\infty$  regardless of  $T_0$  and is the limiting factor of the scalability of  $T_0$ .

A common factor affecting imperfectly parallelizable work and scalability is memory dependencies between parallel (or concurrent) tasks. For example, in a *race condition*, tasks contend for exclusive write access to a single memory location and must

synchronize their reads to ensure correctness [95]. While some dependencies can be refactored into a perfectly parallelizable form, others still require synchronization (e.g., locks and mutexes) or hardware atomic primitives to prevent non-deterministic output. The key to enabling scalability in this scenario is to avoid high contention at any given memory location and prevent blocking of tasks, whereby tasks remains idle (sometimes deadlocked) until they can access a lock resource. To enable lock-free progress of work among tasks, fine-grained atomic primitives are commonly used to efficiently check and increment values at memory locations [52, 31]. For example, the compare-and-swap (CAS) primitive atomically compares the value read at a location to an expected value. If the values are equal, then a new value is set at the location; otherwise, the value doesn't change.

Moreover, programs that have a high ratio of memory accesses to arithmetic computations can incur significant *memory latency*, which is the number of clock or instruction cycles needed to complete a single memory access [121]. During this latency period, processors should perform a sufficient amount of parallel work to *hide* the latency and avoid being idle. Given the *bandwidth*, or instructions completed per cycle, of each processor, *Little's Law* specifies the number of parallel instructions needed to hide latency as the bandwidth multiplied by latency [88]. While emerging many-core and massively-threaded architectures provide more available parallelism and higher bandwidth rates, the memory latency rate remains stagnant due to physical limitations [95]. Thus, to exploit this greater throughput and *instruction-level parallelism* (ILP), a program should ideally be decomposed into fine-grained units of computation that perform parallelizable work (*fine-grained parallelism*).

Furthermore, the increase in available parallelism provided by emerging architectures also enables larger workloads and data to be processed in parallel [95, 54].

Gustafson [47] noted that as a problem size grows, the amount of parallel work increases much faster than the amount of serial work. Thus, a speedup can be achieved by decreasing the serial fraction of the total work. By explicitly parallelizing fine-grained computations that operate on this data, scalable *data-parallelism* can be attained, whereby a single instruction is performed over multiple data elements (SIMD) in parallel (e.g., via a vector instruction), as opposed to over a single scalar data values (SISD). This differs from *task-parallelism*, in which multiple tasks of a program conduct multiple instructions in parallel over the same data elements (MIMD) [121]. Task-parallelism only permits a constant speedup and induces *coarse-grained parallelism*, whereby all tasks work in parallel but an individual task could still be executing serial work. By performing inner fine-grained parallelism within outer course-grained parallel tasks, a *nested parallelism* is attained [12]. Many recursive and segmented problems (e.g., quicksort and closest pair) can often be refactored into nested-parallel versions [11]. Flynn [39] introduces SIMD, SISD, and MIMD as part of a taxonomy of computer instruction set architectures.

## 2.2 Data Parallel Primitives

The redesign of serial algorithms for scalable data-parallelism offers platform portability, as increases in processing units and data are accompanied by unrestricted increases in speedup. *Data-parallel primitives* (DPPs) provide a way to explicitly design and program an algorithm for this scalable, platform-portable data-parallelism. DPPs are highly-optimized *building blocks* that are combined together to compose a larger algorithm. The traditional design of an algorithm is thus refactored in terms of DPPs. By providing highly-optimized implementations of each DPP for each platform architecture, an algorithm composed of DPPs can be executed efficiently across multiple platforms. This use of DPPs eliminates the combinatorial (cross-product) programming issue of having to implement a different version of the algorithm for each different architecture.

The early work on DPPs was set forth by Blelloch [11], who proposed a *scan vector model* for parallel computing. In this model, a vector-RAM (V-RAM) machine architecture is composed of a vector memory and a parallel vector processor. The processor executes vector instructions, or *primitives*, that operate on one or more arbitrarily-long vectors of atomic data elements, which are stored in the vector memory. This is equivalent to having as many independent, parallel processors as there are data elements to be processed. Each primitive is classified as either *scan* or *segmented* (persegment parallel instruction), and must possess a parallel, or *step*, time complexity of  $O(\log n)$  and a serial, or *element*, time complexity of O(n), in terms of n data elements; the element complexity is the time needed to simulate the primitive on a serial random access machine (RAM). Several canonical primitives are then introduced and used as building blocks to refactor a variety of data structures and algorithms into data-parallel forms.

The following are examples of DPPs that are commonly-used as building blocks to construct data-parallel algorithms:

- Map: Applies an operation on all elements of the input array, storing the result in an output array of the same size, at the same index;

- Reduce: Applies an aggregate binary operation (e.g., summation or maximum) on

all elements of an input array, yielding a single output value. ReduceByKey is a

variation that performs segmented Reduce on the input array based on unique key,

yielding an output value for each key;

- Gather: Given an input array of values, reads values into an output array according to an array of indices;

- Scan: Calculates partial aggregates, or a prefix sum, for all values in an input array

and stores them in an output array of the same size;

- Scatter: Writes each value of an input data array into an index in an output array, as specified in the array of indices;

- Compact: Applies a unary predicate (e.g., if an input element is greater than zero)

on all values in an input array, filtering out all the values which do not satisfy the

predicate. Only the remaining elements are copied into an output array of an equal or smaller size;

- SortByKey: conducts an in-place segmented Sort on the input array, with segments based on a key or unique data value in the input array;

- Unique: Ignores duplicate values which are adjacent to each other, copying only

unique values from the input array to the output array of the same or lesser size; and

- Zip: Binds two arrays of the same size into an output array of pairs, with the first

and second components of a pair equal to array values at a given index.

Several other DPPs exist, each meeting the required step and element complexities specified by Blelloch [11]. Cross-platform implementations of a wide variety of DPPs form the basis of several notable open-source libraries.

The Many-Core Visualization Toolkit (VTK-m) [109] is a platform-portable library that provides a growing set of DPPs and DPP-based algorithms [148]. With a single code base, back-end code generation and runtime support are provided for use on GPUs and CPUs. Currently, each GPU-based DPP is a modified variant from the Nvidia CUDA Thrust library [117], and each CPU-based DPP is adopted from the Intel Thread Building Blocks (TBB) library [53]. VTK-m also provides the flexibility to implement DPPs for new architectures or parallel programming languages as they become available. A single VTK-m algorithm code base can be executed on one of several devices at runtime. The choice of device is either specified at compile-time by the user, or automatically selected by VTK-m. VTK-m, Thrust, and TBB all employ

a generic programming model that provides C++ Standard Template Library (STL)-like interfaces to DPPs and algorithms [125]. Templated arrays form the primitive data structures over which elements are parallelized and operated on by DPPs. Many of these array types provide additional functionality on top of underlying vector iterators that are inspired by those in the Boost Iterator Library [13].

The CUDA Data Parallel Primitives Library (CUDPP) [27] is a library of fundamental DPPs and algorithms written in Nvidia CUDA C [115] and designed for high-performance execution on CUDA-compatible GPUs. Each DPP and algorithm incorporated into the library is considered best-in-class and typically published in peer-reviewed literature (e.g., radix sort [100, 6], mergesort [128, 29], and cuckoo hashing [2, 3]). Thus, its data-parallel implementations are constantly updated to reflect the state-of-the-art.

# 2.3 General-Purpose GPU Computing

A graphical processing unit (GPU) is a special-purpose architecture that is designed specifically for high-throughput, data-parallel computations that possess a high arithmetic intensity—the ratio of arithmetic operations to memory operations [121]. Traditionally used and hard-wired for accelerating computer graphics and image processing calculations, modern GPUs contain many times more execution cores and available instruction-level parallelism (ILP) than a CPU of comparable size [115]. This inherent ILP is provided by a group of processors, each of which performs SIMD-like instructions over thousands of independent, parallel threads. These *stream processors* operate on sets of data, or *streams*, that require similar computation and exhibit the following characteristics [60]:

- High Arithmetic Intensity: High number of arithmetic instructions per memory instruction. The stream processing should be largely compute-bound as opposed to memory bandwidth-bound.

- High Data-Parallelism: At each time step, a single instruction can be applied to a large number of streams, and each stream is not dependent on the results of other streams.

- High Locality of Reference: As many streams as possible in a set should align

their memory accesses to the same segment of memory, minimizing the number

of memory transactions to service the streams.

General-purpose GPU (GPGPU) computing leverages the massively-parallel hardware capabilities of the GPU for solving general-purpose problems that are traditionally computed on the CPU (i.e., non-graphics-related calculations). These problems should feature large data sets that can be processed in parallel and satisfy the characteristics of stream processing outlined above. Accordingly, algorithms for solving these problems should be redesigned and optimized for the data-parallel GPU architecture, which has significantly different hardware features and performance goals than a modern CPU architecture [114].

Modern GPGPUs with dedicated memory are most-commonly packaged as discrete, programmable devices that can be added onto the motherboard of a compute system and programmed to configure and execute parallel functions [121]. The primary market leaders in the design of discrete GPGPUs are Nvidia and Advanced Micro Devices (AMD), with their GeForce and Radeon family of generational devices, respectively. Developed by Nvidia, the CUDA parallel programming library provides an interface to design algorithms for execution on an Nvidia GPU and configure hardware elements [115]. For the remainder of this survey, all references to a GPU will be with

respect to a modern Nvidia CUDA-enabled GPU, as it is used prevalently in most of the GPU hashing studies.

The following subsections review important features of the GPU architecture and discuss criteria for optimal GPU performance.

**2.3.1 SIMT Architecture.** A GPU is designed specifically for *Single*-Instruction, Multiple Threads (SIMT) execution, which is a combination of SIMD and simultaneous multi-threading (SMT) execution that was introduced by Nvidia in 2006 as part of the Tesla micro-architecture [116]. On the host CPU, a program, or kernel function, is written in CUDA C and invoked for execution on the GPU. The kernel is executed N times in parallel by N different CUDA threads, which are dispatched as equally-sized thread blocks. The total number of threads is equal to the number of thread blocks times the number of threads per block, both of which are user-defined in the kernel. Thread blocks are required to be independent and can be scheduled in any order to be executed in parallel on one of several independent *streaming multi-processors* (SMs). The number of blocks is typically based on the number of data elements being processed by the kernel or the number of available SMs [115]. Since each SM has limited memory resources available for resident thread blocks, there is a limit to the number of threads per block—typically 1024 threads. Given these memory constraints, all SMs may be occupied at once and some thread blocks will be left inactive. As thread blocks terminate, a dedicated GPU scheduling unit launches new thread blocks onto the vacant SMs.

Each SM chip contains hundreds of ALU (arithmetic logic unit) and SFU (special function unit) compute cores and an interconnection network that provides *k*-way access to any of the *k* partitions of off-chip, high-bandwidth global DRAM memory. Memory requests first query a global L2 cache and then only proceed to global memory upon a cache miss. Additionally, a read-only texture memory space is provided to cache global

memory data and enable fast loads. On-chip thread management and scheduling units pack each thread block on the SM into one or more smaller logical processing groups known as *warps*—typically 32 threads per warp; these warps compose a *cooperative thread array* (CTA). The thread manager ensures that each CTA is allocated sufficient shared memory space and per-thread registers (user-specified in kernel program). This on-chip shared memory is designed to be low-latency near the compute cores and can be programmed to serve as L1 cache or different ratios thereof (newer generations now include these as separate memory spaces) [48].

Finally, each time an instruction is issued, the SM instruction scheduler selects a warp that is ready to execute the next SIMT scalar (register-based) instruction, which is executed independently and in parallel by each active thread in the warp. In particular, the scheduler applies an active mask to the warp to ensure that only active threads issue the instruction; individual threads in a warp may be inactive due to independent branching in the program. A synchronization barrier detects when all threads (and warps) of a CTA have exited and then frees the warp resources and informs the scheduler that these warps are now ready to process new instructions, much like context switching on the CPU. Unlike a CPU, the SM does not perform any branch prediction or speculative execution (e.g., prefetching memory) among warp threads [121].

SIMT execution is similar to SIMD, but differs in that SIMT applies one instruction to multiple independent warp threads in parallel, instead of to multiple data lanes. In SIMT, scalar instructions control individual threads, whereas in SIMD, vector instructions control the entire set of data lanes. This detachment from the vector-based processing enables threads of a warp to conduct a form of SMT execution, where each thread behaves more like a heavier-weight CPU thread [121]. Each thread has its own set of registers, addressable memory requests, and control flow. Warp threads may take

divergent paths to complete an instruction (e.g., via conditional statements) and contribute to starvation as faster-completing threads wait for the slower threads to finish.

The two-level GPU hierarchy of warps within SMs offers massive nested parallelism over data [121]. At the outer, SM level of granularity, coarse-grained parallelism is attained by distributing thread blocks onto independent, parallel SMs for execution. Then at the inner, warp level of granularity, fine-grained data and thread parallelism is achieved via the SIMT execution of an instruction among parallel warp threads, each of which operates on an individual data element. The massive data-parallelism and available compute cores are provided specifically for high-throughput, arithmetically-intense tasks with large amounts of data to be independently processed. If a high-latency memory load is made, then it is expected that the remaining warps and processors will simultaneously perform sufficient work to hide this latency; otherwise, hardware resources remain unused and yield a lower aggregate throughput [146]. The GPU design trades-off lower memory latency and larger cache sizes (such as on a CPU) for increased instruction throughput via the massive parallel multi-threading [121].

This architecture description is based on the Nvidia Maxwell micro-architecture, which was released in 2015 [48]. While certain quantities of components (e.g., SMs, compute cores, memory sizes, and thread block sizes) change with each new generational release of the Nvidia GPU, the general architectural design and execution model remain constant [115]. The CUDA C Programming Guide [115] and Nvidia PTX ISA documentation [116] contain further details on the GPU architecture, execution and memory models, and CUDA programming.

**2.3.2 Optimal Performance Criteria.** The following performance strategies are critical for maximizing utilization, memory throughput, and instruction throughput on the GPU [114].

Sufficient parallelism: Sufficient instruction-level and thread-level parallelism should be attained to fully hide arithmetic and memory latencies. According to Little's Law, the number of parallel instructions needed to hide a latency (number of cycles needed to perform an instruction) is roughly the latency times the throughput (number of instructions performed per cycle) [88]. During this latency period, threads that are dependent on the output data of other currently-executing threads in a warp (or thread block) are stalled. Thus, this latency can be hidden either by having these threads simultaneously perform additional, non-dependent SIMT instructions in parallel (instruction-level parallelism), or by increasing the number of concurrently running warps and warp threads (thread-level parallelism) [146].

Since each SM has limited memory resources for threads, the number of concurrent warps possible on an SM is a function of several configurable components: allocated shared memory, number of registers per thread, and number of threads per thread block [115]. Based on these parameters, the number of parallel thread blocks and warps on an SM can be calculated and used to compute the *occupancy*, or ratio of the number of active warps to the maximum number of warps. In terms of Little's Law, sufficient parallel work can be exploited with either a high occupancy or low occupancy, depending on the amount of work per thread. Based on the specific demands for SM resources, such as shared memory or register usage, by the kernel program, the number of available warps will vary accordingly. Higher occupancy, usually past 50 percent, does not always translate into improved performance [114]. For example, a lower occupancy kernel will have more registers available per thread than a higher occupancy kernel, allowing low-latency access to local variables and minimizing register spilling into high-latency local memory.

Memory coalescing: When a warp executes an instruction that accesses global memory, it coalesces the memory accesses of the threads within the warp into one or more memory transactions, or cache lines, depending on the size of the word accessed by each thread and the spatial coherency of the requested memory addresses. To minimize transactions and maximize memory throughput, threads within a warp should coherently access memory addresses that fit within the same cache line or transaction. Otherwise, memory divergence occurs and multiple lines of memory are fetched, each containing many unused words. In the worst case alignment, each of the 32 warp threads accesses successive memory addresses that are multiples of the cache line size, prompting 32 successive load transactions [114].

The shared memory available to each thread block can help coalesce or eliminate redundant accesses to global memory [121]. The threads of the block (and associated warp) can share their data and coordinate memory accesses to save significant global memory bandwidth. However, it also can act as a constraint on SM occupancy—particularly limiting the number of available registers per thread and warps—and is prone to *bank conflicts*, which occur when two or more threads in a warp access an address in the same bank, or partition, of shared memory [115]. Since an SM only contains one hardware bus to each bank, multiple requests to a bank must be serialized. Thus, optimal use of shared memory necessitates that warp threads arrange their accesses to different banks [115]. Finally, the read-only texture memory of an SM can be used by a warp to perform fast, non-coalesced lookups of cached global memory, usually in smaller transaction widths.

Control flow: Control flow instructions (e.g., if, switch, do, for, while) can significantly affect instruction throughput by causing threads of the same warp to diverge and follow different execution paths, or branches. Optimal control flow is realized when

all the threads within a warp follow the same execution path [114]. This scenario enables SIMD-like processing, whereby all threads complete an instruction simultaneously in lock-step. During *branch divergence* in a warp, the different executions paths, or branches, must be serialized, increasing the total number of instructions executed for the warp. Additionally, the use of atomics and synchronization primitives can also require additional serialized instructions and thread starvation within a warp, particularly during high contention for updating a particular memory location [138].

### 2.4 Index-Based Searching

Let  $U = \{i\}_{0 \le i < u}$  be the universe for some arbitrary positive integer u. Then let  $S \subset U$  be an unordered array of n = |S| elements, or keys, belonging to U. The search problem seeks an answer to the query: "Is key k a member of S?" If  $k \in S$ , then we return its corresponding value, which is either k itself or a different value. A data structure is built or constructed over S to efficiently facilitate the searching operation. The data structure is implementation-specific and can be as simple as a sorted (ordered) variant of the original array, a hash table, or a tree-based partitioning of the elements.

A generalization of the search task is the *dictionary problem*, which seeks to both modify and query key-value pairs (k, v) in S. A canonical dictionary data structure supports insert(k, v), delete(k, v), query(k),  $range(k_1, k_2)$  (returns  $\{k|k_1 \le k \le k_2\}$ ), and  $count(k_1, k_2)$  (returns  $|range(k_1, k_2)|$ ). To support these operations, the dictionary must be dynamic and accommodate incremental or batch updates after construction; this contrasts to a static data structure, which either does not support updates after a one-time build or must be rebuilt after each update. In multi-threaded environments, these structures must also provide concurrency and ensure correctness among mixed, parallel operations that may access the same elements simultaneously.

An extensive body of work has embarked on the redesign of data structures for construction and general computation on the GPU [119]. Within the context of searching, these *acceleration* structures include sorted arrays [2, 129, 3, 57, 79, 81, 7] and linked lists [152], hash tables (see section 2.5), spatial-partitioning trees (e.g., *k*-d trees [156, 62, 150], octrees [155, 62], bounding volume hierarchies (BVH) [76, 62], R-trees [91], and binary indexing trees [65, 131]), spatial-partitioning grids (e.g., uniform [71, 59, 43] and two-level [58]), skiplists [111], and queues (e.g., binary heap priority [51] and FIFO [20, 133]).

Due to significant architectural differences between the CPU and GPU, search structures cannot simply be "ported" from the CPU to the GPU and maintain optimal performance. On the CPU, these structures can be designed to fit within larger caches, perform recursion, and employ heavier-weight synchronization or hardware atomics. However, during queries, the occurrence of varying paths of pointers (pointer chasing) and dependencies between different phases or levels of the structure can limit the parallel throughput on the GPU. If the pointers are scattered randomly in memory, then memory accesses may be uncoalesced and induce additional global memory transactions (cache line loads). These attributes are particularly important to real-time, interactive applications, such as surface reconstruction and rendering, that make frequent updates and queries to the acceleration structure.

Spatial-partitioning or tree-based search structures are particularly vulnerable to these portable performance issues. For example, a canonical method of searching within a spatial domain involves explicitly computing a bounding box over the domain and then recursively subdividing it into smaller and smaller regions, or cells. Each cell contains a subset of elements, such as points coordinates or integers within an interval. This subdivision hierarchy can then be represented by a grid (e.g., uniform and two-level)

or tree (e.g., *k*-d tree, octree, or bounding volume hierarchy) data structure that conducts a query operation by traversing a path through the hierarchy until the queried element is found. While these search structures are designed for fast, highly-parallel usage, they typically do not exhibit fast reconstruction rates due to complex spatial hierarchies, and may contain deep tree structures that are conducive to thread branch divergence during parallel query traversals.

For searching an unordered array of elements on the GPU, two canonical, spatially-linear data structures exist: the sorted array and the hash table. Both of these data structures are amenable to data-parallel design patterns [7] and, thus, avoid most of the portable-performance design challenges faced by tree-based search structures. In this dissertation, we focus exclusively on data-parallel sorting- and hashing-based search techniques. A background on both of these approaches is presented as follows.

**2.4.1 Searching Via Sorting.** Given a set of *n* unordered elements, a canonical searching approach is to first sort the elements in ascending order and then conduct a binary or *k*-nary search for the query element. This search requires a logarithmic number of comparisons in the worst-case, but is not as amenable to caching as consecutive comparisons are not spatially close in memory for large *n*. Moreover, on the GPU, an ordered query pattern by threads in a warp can enable memory coalescing during comparisons.

The current version of the CUDA Thrust library [117] provides fast and high-throughput data-parallel implementations of mergesort [128] and radix sort [100] for arrays of custom (e.g., comparator function) or numerical (i.e., integers and floats) data types, respectively. Similarly, the latest version of the CUDPP library [27] includes best-in-class data-parallel algorithms for mergesort [128, 29] and radix sort [100, 6], each of

which are adapted from published work. Singh et al. [136] survey and compare the large body of recent GPU-based sorting techniques.

A few studies have investigated various factors that affect the performance of data-parallel sort methods within the context of searching [2, 3, 81]. Kaldewey and Blas introduce a GPU-based p-ary search that first uses p parallel threads to locate a query key within one of p larger segments of a sorted array, and then iteratively repeats the procedure over p smaller segments within the larger segment. This search achieves high memory throughput and is amenable to memory coalescing among the threads [57]. Moreover, the algorithm was also ported to the CPU to leverage the SIMD vector instructions in a fashion similar to the k-ary search introduced by Schlegel et al. [129]. However, the fixed vector width restricts the degree of parallelism and value of p, which is significantly higher on the GPU.

Inserting or deleting elements into a sorted array is generally not supported and requires inefficient approaches such as appending/removing new elements and re-sorting the larger/smaller array, or first sorting the batch of new insertions and then merging them into the existing sorted array. Ashkiani et al. [7] present these approaches and the resulting performance for a dynamic sorting-based dictionary data structure, along with setting forth the current challenges of designing dynamic data structures on the GPU.

**2.4.2 Searching Via Hashing.** Instead of maintaining elements in sorted order and performing a logarithmic number of lookups per query, *hash tables* compactly reorganize the elements such that only a constant number of direct, random-access lookups are needed on average [26]. More formally, given a universe U of possible keys and an unordered set  $S \subseteq U$  of n keys (not necessarily distinct), a *hash function*,  $h: U \mapsto H$ , maps the keys from S to the range  $H = \{j\}_{0 \le j < m}$  for some arbitrary positive integer  $m \ge n$ . Defining a memory space over this range of size m specifies a hash table,

into which keys are inserted and queried. Thus, the hash table is addressable by the hash function. During an insertion or query operation for a key q, the hash function computes an address h(q) = r into H. If the location H[r] is empty, then q is either inserted into H[r] (for an insertion) or does not exist in H (for a query). If H[r] contains the key q (for a query), then either q or an associated value of q is returned<sup>1</sup>, indicating success. Otherwise, if multiple distinct keys  $q' \neq q$  are hashed to the same address h(q') = r, then a situation known as a hash collision occurs. These collisions are typically resolved via  $separate\ chaining\ (i.e.,\ employing\ linked\ lists\ to\ store\ multiple\ keys\ at\ a\ single\ address)$  or  $open\ addressing\ (e.g.,\ when\ an\ address\ is\ occupied,\ then\ store\ the\ key\ at\ the\ next\ empty\ address).$

The occurrence of collisions deteriorates the query performance, as each of the collided keys must be iteratively inspected and compared against the query key. According to the birthday paradox, with a discrete uniform distribution hash function that outputs a value between 1 and 365 for any key, the probability that two random keys hash to the same address in a hash table of size 23 is 50 percent [140]. More generally, for n hash values and a table size of m, the probability p(n,m) of a collision is

$$p(n,m) = \begin{cases} 1 - \prod_{k=1}^{n-1} \left(1 - \frac{k}{m}\right) & n \le m \\ 1 & n > m \end{cases}$$

$$pprox 1 - \left(\frac{m-1}{m}\right)^{\frac{n(n-1)}{2}}.$$

Thus, for a large number of keys (n) and small hash table (m), hash collisions are inevitable.

<sup>&</sup>lt;sup>1</sup>In practice, the values should be easily stored and accessible within an auxiliary array or via a custom arrangement within the hash table.

In order to minimize collisions, an initial approach is to use a good quality hash function that is both efficient to compute and distributes keys as evenly as possible throughout the hash table [26]. One such family of functions are randomly-generated, parameterized functions of the form  $h(k) = (a \cdot k + b) \mod p \mod |H|$ , where p is a large prime number and a and b are randomly-generated constants that bias h from outputting duplicate values [3]. However, the effectiveness of h also depends on the hash table size, |H|. If |H| is too small, then not even the best of hash functions can avoid an increase in collisions. Given the table size, the *load factor*  $\alpha$  of the table is defined as  $\alpha = n/|H|$ , or the percentage of occupied addresses in the hash table, which |H| is typically larger than n. If new keys are inserted into the table and  $\alpha$  reaches a maximum threshold, then typically the table is allocated to a larger size and all the keys are *rehashed* into the table.