# Old Dominion University ODU Digital Commons

**Computer Science Theses & Dissertations**

**Computer Science**

Summer 2015

# High Performance Large Graph Analytics by Enhancing Locality

Naga Shailaja Dasari Old Dominion University

Follow this and additional works at: https://digitalcommons.odu.edu/computerscience\_etds Part of the <u>Computer Sciences Commons</u>

#### **Recommended** Citation

Dasari, Naga S.. "High Performance Large Graph Analytics by Enhancing Locality" (2015). Doctor of Philosophy (PhD), dissertation, Computer Science, Old Dominion University, DOI: 10.25777/3080-hj26 https://digitalcommons.odu.edu/computerscience\_etds/52

This Dissertation is brought to you for free and open access by the Computer Science at ODU Digital Commons. It has been accepted for inclusion in Computer Science Theses & Dissertations by an authorized administrator of ODU Digital Commons. For more information, please contact digitalcommons@odu.edu.

# HIGH PERFORMANCE LARGE GRAPH ANALYTICS

# BY ENHANCING LOCALITY

by

Naga Shailaja Dasari B.Tech. June 2003, Kakatiya University, India M.Tech. June 2006, Indian Institute of Technology, Kanpur, India

A Dissertation Submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirements for the Degree of

## DOCTOR OF PHILOSOPHY

### COMPUTER SCIENCE

OLD DOMINION UNIVERSITY August 2015

Approved by:

Desh Ranjan (Co-Director)

Mohammad Zubair (Co-Director)

Jing\_He (Member)

Bharat Madan (Member)

ProQuest Number: 3664141

All rights reserved

INFORMATION TO ALL USERS The quality of this reproduction is dependent upon the quality of the copy submitted.

In the unlikely event that the author did not send a complete manuscript and there are missing pages, these will be noted. Also, if material had to be removed, a note will indicate the deletion.

ProQuest 3664141

Published by ProQuest LLC(2015). Copyright of the Dissertation is held by the Author.

All rights reserved. This work is protected against unauthorized copying under Title 17, United States Code. Microform Edition © ProQuest LLC.

> ProQuest LLC 789 East Eisenhower Parkway P.O. Box 1346 Ann Arbor, MI 48106-1346

### ABSTRACT

# HIGH PERFORMANCE LARGE GRAPH ANALYTICS BY ENHANCING LOCALITY

Naga Shailaja Dasari Old Dominion University, 2015 Co-Directors: Dr. Desh Ranjan and Dr. Mohammad Zubair

Graphs are widely used in a variety of domains for representing entities and their relationship to each other. Graph analytics helps to understand, detect, extract and visualize insightful relationships between different entities. Graph analytics has a wide range of applications in various domains including computational biology, commerce, intelligence, health care and transportation. The breadth of problems that require large graph analytics is growing rapidly resulting in a need for fast and efficient graph processing.

One of the major challenges in graph processing is poor locality of reference. Locality of reference refers to the phenomenon of frequently accessing the same memory location or adjacent memory locations. Applications with poor data locality reduce the effectiveness of the cache memory. They result in large number of cache misses, requiring access to high latency main memory. Therefore, it is essential to have good locality for good performance. Most graph processing applications have highly random memory access patterns. Coupled with the current large sizes of the graphs, they result in poor cache utilization. Additionally, the computation to data access ratio in many graph processing applications is very low, making it difficult to cover the memory latency using computation. It is also challenging to efficiently parallelize most graph applications. Many graphs in real world have unbalanced degree distribution. It is difficult to achieve a balanced workload for such graphs. The parallelism in graph applications is generally fine-grained in nature. This calls for efficient synchronization and communication between the processing units.

Techniques for enhancing locality have been well studied in the context of regular applications like linear algebra. Those techniques are in most cases not applicable to the graph problems. In this dissertation, we propose two techniques for enhancing locality in graph algorithms: access transformation and task-set reduction. Access transformation can be applied to algorithms to improve the spatial locality by changing the random access pattern to sequential access. It is applicable to iterative algorithms that process random vertices/edges in each iteration. The task-set reduction technique can be applied to enhance the temporal locality. It is applicable to algorithms which repeatedly access the same data to perform certain task. Using the two techniques, we propose novel algorithms for three graph problems: k-core decomposition, maximal clique enumeration and triangle listing. We have implemented the algorithms. The results show that these algorithms provide significant improvement in performance and also scale well. Copyright, 2015, by Naga Shailaja Dasari, All Rights Reserved.

#### ACKNOWLEDGEMENTS

Foremost, I would like to thank my advisors, Dr. Desh Ranjan and Dr. Mohammad Zubair, for their continuous support and guidance. They have always been very encouraging and provided with valuable advise, both academic and non-academic. I have been very fortunate to have them as my advisors and without their support I would not have finished my thesis.

I would like to thank my committee members, Dr. Jing He and Dr. Bharat Madan, for their valuable time and support, for reviewing my thesis and for constructive feedback.

A big fat thanks to my husband, Neel, for being by my side through out the journey, for his love and support, and especially for taking care of our little daughter while I work.

I would like to express my gratitude to my parents, Narasaiah and Anjani, for their unconditional love, support, encouragement and for giving me the freedom of choice.

I would like to thank my little daughter, Lasya, for letting me work despite how much she hated it. Her smile and charm always kept me going.

# TABLE OF CONTENTS

|    |                 | Pag                                           | ge            |  |

|----|-----------------|-----------------------------------------------|---------------|--|

| LI | ST O            | TABLES                                        | iii           |  |

| LI | ST O            | FIGURES                                       | xi            |  |

| Cł | napte           |                                               |               |  |

| 1  | 1. INTRODUCTION |                                               |               |  |

| 1. | 1.1             | BIG DATA GRAPH ANALYTICS                      | $\frac{1}{2}$ |  |

|    | 1.1             | RESEARCH CHALLENGES IN LARGE GRAPH PROCESSING | 3             |  |

|    | 1.4             | 1.2.1 POOR LOCALITY OF REFERENCE              | 3             |  |

|    |                 | 1.2.2 LOW COMPUTATION TO DATA ACCESS RATIO    | 4             |  |

|    |                 | 1.2.3 SEQUENTIAL NATURE OF ALGORITHMS         | 4             |  |

|    |                 | 1.2.4 LOAD BALANCING                          | 4             |  |

|    |                 | 1.2.5 SYNCHRONIZATION AND COMMUNICATION COST  | 5             |  |

|    | 1.3             | PARALLEL ARCHITECTURES                        | 5             |  |

|    | 1.0             | 1.3.1 SHARED MEMORY ARCHITECTURE              | 6             |  |

|    |                 | 1.3.2 DISTRIBUTED MEMORY ARCHITECTURE         | 8             |  |

|    | 1.4             | OVERVIEW OF DISSERTATION AND CONTRIBUTIONS    | 8             |  |

| 2. | ACO             | ESS TRANSFORMATION                            | 12            |  |

| 4. | 2.1             |                                               | <br>15        |  |

|    |                 |                                               | 15            |  |

|    |                 |                                               | <br>16        |  |

|    | 2.2             |                                               | 16            |  |

|    |                 |                                               | 17            |  |

|    |                 |                                               | 20            |  |

|    | 2.3             |                                               | 21            |  |

|    |                 |                                               | 23            |  |

|    |                 |                                               | 24            |  |

|    |                 | 2.3.3 ANALYSIS OF THE ALGORITHM               | 24            |  |

|    | 2.4             | PARALLEL METHODOLOGY OF PARK ALGORITHM        | 25            |  |

|    | 2.5             | EXPERIMENTAL RESULTS                          | 27            |  |

|    | 2.6             | SUMMARY                                       | 31            |  |

| 3. | TAS             | K-SET REDUCTION                               | 37            |  |

|    | 3.1             | MAXIMAL CLIQUE ENUMERATION                    | 39            |  |

|    | 3.2             |                                               | 41            |  |

|    |                 | 3.2.1 SEQUENTIAL ALGORITHMS                   | 41            |  |

|    |                 |                                               | 43            |  |

|    |                 | 3.2.3 THE BK ALGORITHM                        | 45            |  |

|     |      | 3.2.4  | THE TOMITA ET AL.'S ALGORITHM               | 46  |

|-----|------|--------|---------------------------------------------|-----|

|     |      | 3.2.5  | THE EPPSTEIN ET AL.'S ALGORITHM             | 48  |

|     | 3.3  | PBIT   | MCE APPROACH                                | 52  |

|     |      | 3.3.1  | DEGENERACY ORDERING                         | 52  |

|     |      | 3.3.2  | PRE-PROCESSING                              | 53  |

|     |      | 3.3.3  | PARTIAL BIT ADJACENCY MATRIX                | 53  |

|     |      | 3.3.4  | ENUMERATION                                 | 55  |

|     |      | 3.3.5  | HYPERGRAPH VS PBAM                          | 57  |

|     |      | 3.3.6  | COMPUTATIONAL COMPLEXITY                    | 58  |

|     |      | 3.3.7  | OPTIMIZATION                                | 59  |

|     | 3.4  | SEQU   | ENTIAL PERFORMANCE RESULTS                  | 59  |

|     | 3.5  |        | LLEL METHODOLOGY AND EXPERIMENTAL RESULTS . | 63  |

|     |      | 3.5.1  | LOAD BALANCING                              | 63  |

|     |      | 3.5.2  | SCALABILITY                                 | 66  |

|     |      | 3.5.3  | RESULTS ON DISTRIBUTED ARCHITECTURE         | 66  |

|     | 3.6  | PBIT   | MCE ON HADOOP FRAMEWORK                     | 69  |

|     |      | 3.6.1  | IMPLEMENTATION                              | 71  |

|     |      | 3.6.2  | ANALYSIS                                    | 75  |

|     |      | 3.6.3  | EXPERIMENTAL RESULTS                        | 75  |

|     | 3.7  | SUMM   | MARY                                        | 80  |

| 4.  | TRI  | ANGLI  | E LISTING                                   | 81  |

|     | 4.1  | DEFII  | NITION AND NOTATIONS                        | 81  |

|     | 4.2  | APPL   | ICATIONS                                    | 81  |

|     | 4.3  | RELA   | TED WORK                                    | 82  |

|     |      | 4.3.1  | EDGE-ITERATOR ALGORITHM                     | 83  |

|     |      | 4.3.2  | ANALYSIS OF MEMORY LOCALITY                 | 85  |

|     | 4.4  | WINL   | OOW-ITERATOR ALGORITHM                      | 86  |

|     |      | 4.4.1  | MEMORY LOCALITY ANALYSIS                    | 86  |

|     |      | 4.4.2  | IMPLEMENTATION                              | 88  |

|     | 4.5  | EXPE   | RIMENTAL RESULTS                            | 90  |

|     | 4.6  | SUMN   | 1ARY                                        | 92  |

| 5.  | COI  | NCLUS  | ION                                         | 93  |

| RJ  | EFER | RENCES | 5                                           | 95  |

| v   | TA   |        |                                             | 105 |

| V 1 |      |        |                                             | 100 |

# LIST OF TABLES

| Table |                                                                                                                                                                                                            | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.    | Details of graphs and time(in seconds) taken by BZ and <i>ParK</i> Algorithms.<br>$n, m$ and $k_{max}$ denote the number of vertices and edges (both in millions) and the maximum core value of the graphs |      |

| 2.    | Comparing <i>pbam</i> and <i>hypergraph</i>                                                                                                                                                                | . 58 |

| 3.    | Experimental results on different datasets                                                                                                                                                                 | . 62 |

| 4.    | Degeneracy vs k-degree                                                                                                                                                                                     | . 75 |

| 5.    | Time taken(in seconds) for enumeration using various orderings                                                                                                                                             | . 76 |

| 6.    | Comparison of <i>edge-iterator-deg</i> and <i>window-iterator</i> algorithms. $n, m$ and $T$ refer to number of vertices, edges and triangles(all in millions) and time(in seconds)                        |      |

# LIST OF FIGURES

| Figu | ire F                                                                                                                                 | age |

|------|---------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.   | Architectural overview of Intel Xeon X7560 processor                                                                                  | 7   |

| 2.   | Plot showing the memory latency for random writes                                                                                     | 13  |

| 3.   | An example graph showing different cores                                                                                              | 15  |

| 4.   | The k-core decomposition algorithm outline                                                                                            | 17  |

| 5.   | The algorithm of Batagelj et al.                                                                                                      | 18  |

| 6.   | A figure showing the memory accesses required for an iteration in BZ algorithm                                                        | 19  |

| 7.   | ParK algorithm                                                                                                                        | 22  |

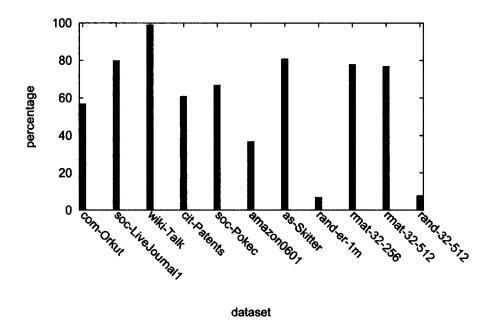

| 8.   | A plot showing the percentage of vertices processed in first sub-level of all the levels                                              | 24  |

| 9.   | Parallel version of <i>ParK</i> algorithm                                                                                             | 33  |

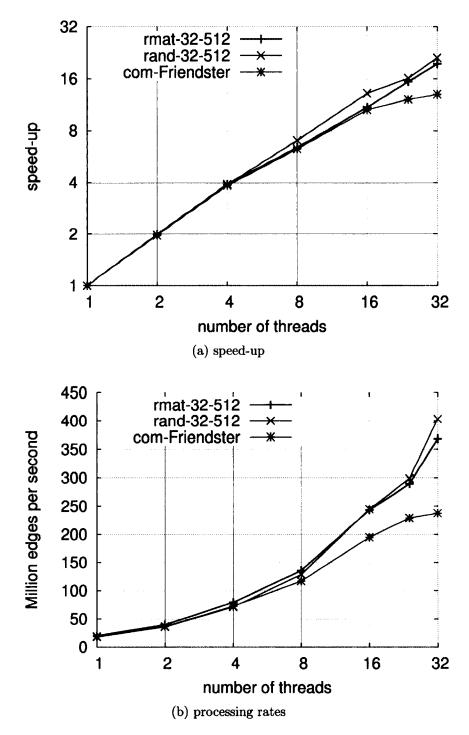

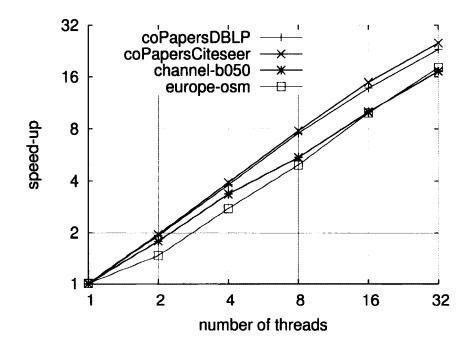

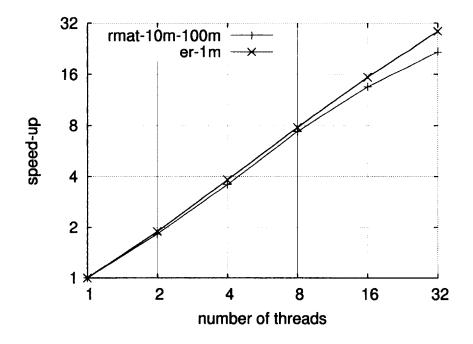

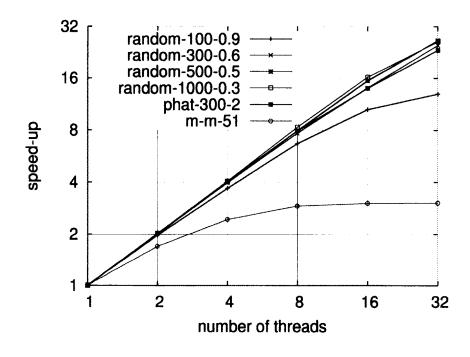

| 10.  | Scalability and Performance results for different graphs                                                                              | 34  |

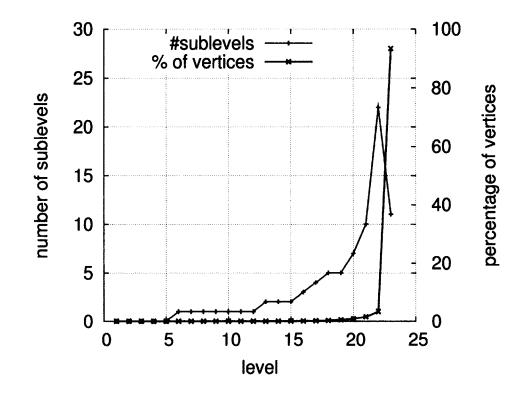

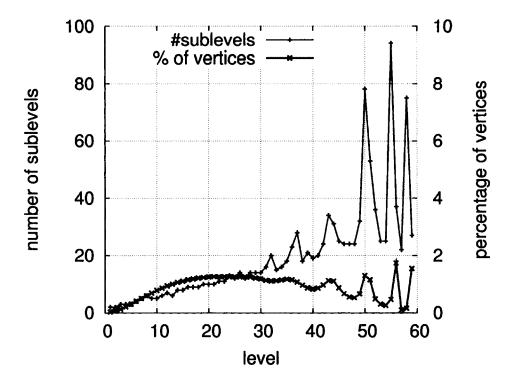

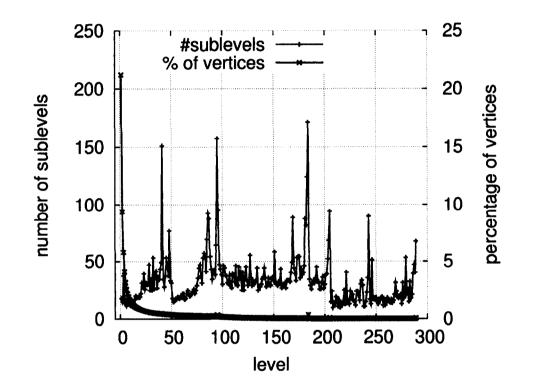

| 11.  | Plots showing the number of sub-levels in a level and the percentage of vertices processed in a level for <i>rand-32-512</i> graph    | 35  |

| 12.  | Plots showing the number of sub-levels in a level and the percentage of vertices processed in a level for <i>rmat-32-512</i> graph    | 35  |

| 13.  | Plots showing the number of sub-levels in a level and the percentage of vertices processed in a level for <i>com-Friendster</i> graph | 36  |

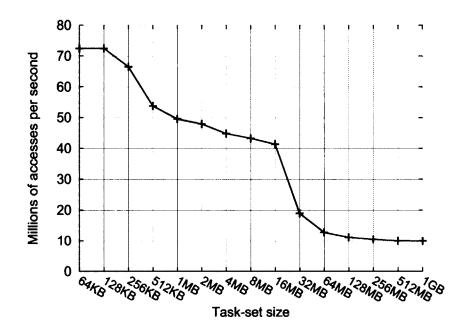

| 14.  | Plot showing the memory latency relative to the <i>task-set</i> size                                                                  | 38  |

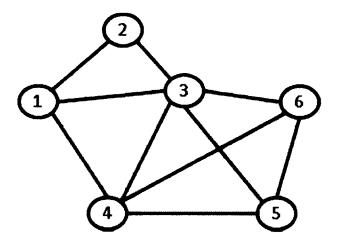

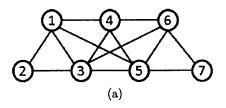

| 15.  | A simple graph                                                                                                                        | 40  |

| 16.  | A Moon-Moser graph                                                                                                                    | 40  |

| 17.  | The BK algorithm                                                                                                                      | 45  |

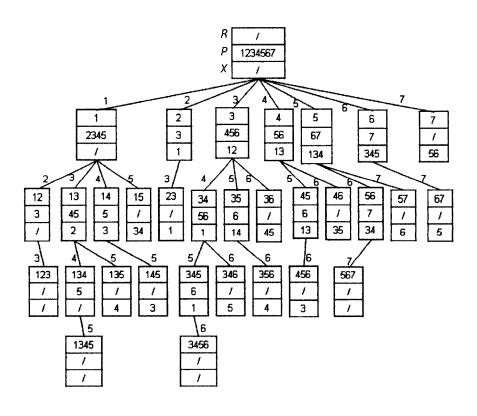

| 18.  | An example graph and its BK search tree                                                                                               | 47  |

| 19.  | The Tomita et al.'s algorithm                                                                                                         | 48  |

| 20.         | TTT search tree for the graph in Figure 18a                                                                                                                                            | 49 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 21.         | The Eppstein et al.'s algorithm                                                                                                                                                        | 50 |

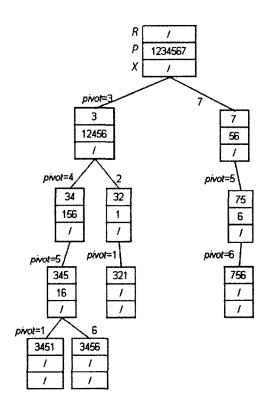

| 22.         | ELS search trees for the graph in Figure 18a. The degeneracy ordering for the graph is $\{2, 7, 1, 3, 4, 5, 6\}$ . Each search tree in the figure corresponds to a vertex in the graph | 51 |

| 23.         | The <i>pbitMCE</i> algorithm                                                                                                                                                           | 56 |

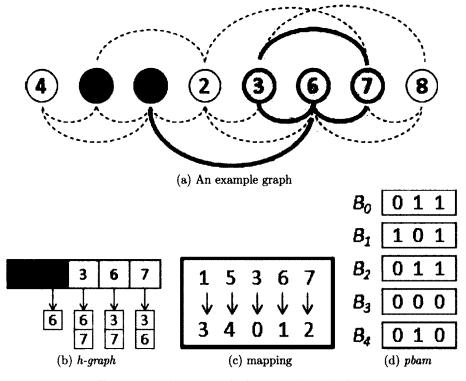

| 24.         | An example $h - graph$ and $pbam$                                                                                                                                                      | 57 |

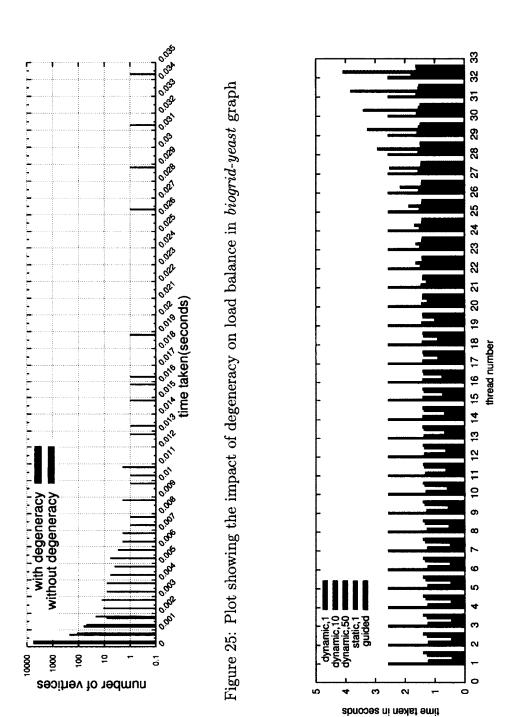

| 25.         | Plot showing the impact of degeneracy on load balance in <i>biogrid-yeast</i> graph                                                                                                    | 64 |

| 26.         | Plot showing the impact of different scheduling types on the load balance<br>and overall time taken                                                                                    | 64 |

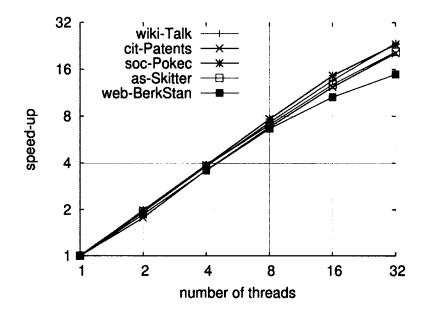

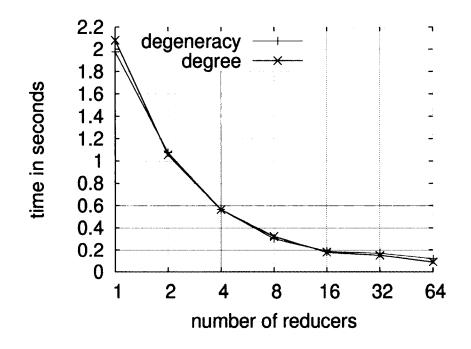

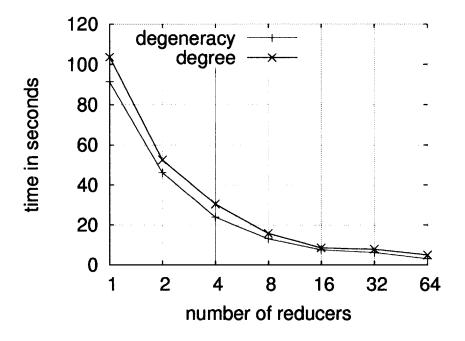

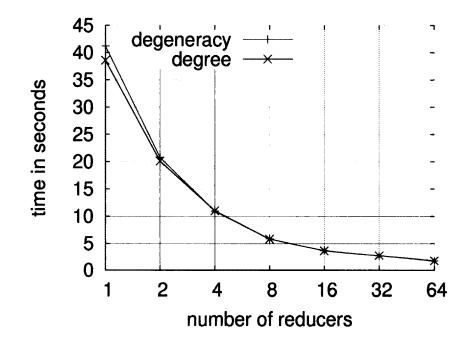

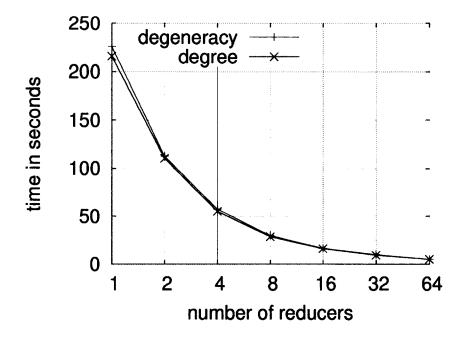

| 27.         | Scalability plot for dataset 1                                                                                                                                                         | 66 |

| 28.         | Scalability plot for dataset 2                                                                                                                                                         | 67 |

| 29.         | Scalability plot for dataset 3                                                                                                                                                         | 67 |

| 30.         | Scalability plot for dataset 4                                                                                                                                                         | 68 |

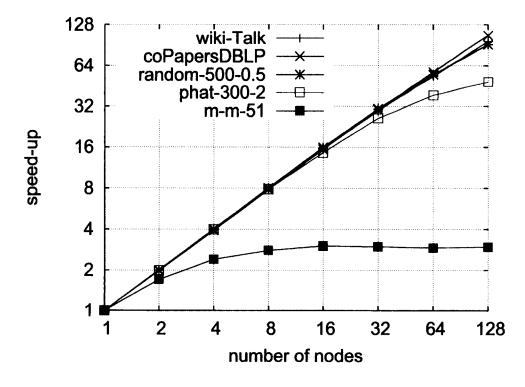

| 31.         | Scalability on distributed memory architecture                                                                                                                                         | 68 |

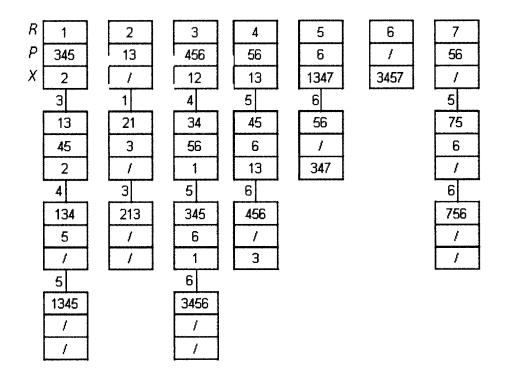

| 32.         | First job                                                                                                                                                                              | 72 |

| 33.         | Second job                                                                                                                                                                             | 73 |

| 34.         | Third job                                                                                                                                                                              | 74 |

| 35.         | Comparison of time taken by <i>pbitMCE</i> using different orderings for <i>cit-Patents</i> graph                                                                                      | 78 |

| 36.         | Comparison of time taken by <i>pbitMCE</i> using different orderings for <i>wiki-Talk</i> graph                                                                                        | 78 |

| 37.         | Comparison of time taken by <i>pbitMCE</i> using different orderings for <i>web-BerkStan</i> graph                                                                                     | 79 |

| 38.         | Comparison of time taken by <i>pbitMCE</i> using different orderings for <i>co-PapersDBLP</i> graph                                                                                    | 79 |

| <b>39</b> . | The edge-iterator algorithm                                                                                                                                                            | 83 |

х

| 40. | The edge-iterator with degree ordering algorithm                | 84 |

|-----|-----------------------------------------------------------------|----|

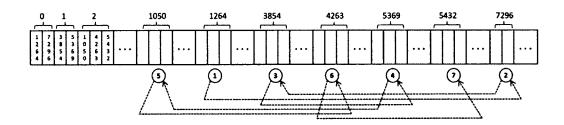

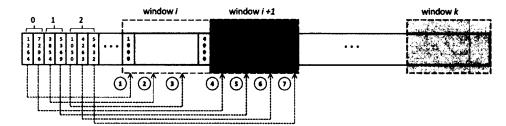

| 41. | Memory access pattern of the <i>edge-iterator-deg</i> algorithm | 85 |

| 42. | The window-iterator algorithm                                   | 87 |

| 43. | Memory access pattern of the window-iterator algorithm          | 88 |

| 44. | A simple optimization                                           | 90 |

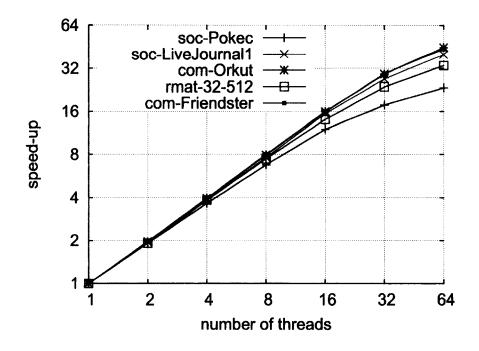

| 45. | Scalability of window-iterator algorithm                        | 91 |

### CHAPTER 1

### INTRODUCTION

A graph is a set of vertices and edges that represent entities and the relationship between entities, respectively. Graphs are widely used in various domains. For example, the air traffic network can be represented using a graph where each vertex represents an airport and an edge represents a connection between the two airports. In a social network, each person can be represented by a vertex and the relationships can be represented by edges. In a web graph, each web page can be represented by a node and a hyperlink between web pages can be denoted by an edge. Graphs are also heavily used in many other fields including computational biology, commerce and sociometry.

The volume of data has been exploding in recent years. There is massive amounts of data being generated every minute. According to the statistics published in 2012 [1][2], every minute, Facebook users share over 700k posts, Twitter users send over 100k tweets, Instagram users share over 3600 photos, and over 500 new websites are created. Walmart receives over 1 million transactions per hour which is stored in its database which is estimated to be more than 2.5 petabytes. Now more than ever, the data collected is being made use of. The data is processed, modified, combined, analysed and visualized to extract useful information. The benefits of the extracted information can be very substantial. According to a case study published in [3], UPS, a postal service company acquired data from the sensors attached to more than 46,000 vehicles to track the speed, direction, braking and drive train performance. The data was then analysed and led to savings of over 8.4 million gallons of fuel by cutting 85 million miles off of daily routes.

In the recent years, a lot of attention has been paid for analysis of graphs. There has been significant rise in the breadth of problems requiring graph analytics. As a result, it is becoming increasingly important to efficiently solve the graph problems. There are many interesting and complex graph problems that needs to be solved for graph analysis. Unfortunately many graph problems are computationally expensive to solve. Coupled with the current large sizes of the graphs, it is highly challenging to solve many graph problems in practical amount of time. One of the major challenges in graph processing relates to the poor locality of reference. In this thesis, we focus on the problem of locality and present two techniques, *access transformation* and *task-set reduction*, to improve the memory locality in graph applications.

In this chapter, we present a brief introduction of graph analytics and its applications. We then discuss the challenges in large graph processing. A brief description of some high performance computing systems is presented. We then present an overview of the dissertation and contributions.

#### **1.1 BIG DATA GRAPH ANALYTICS**

In this era of big data, graphs are widely being used to model data. The graph based problems are evolving in multiple disciplines including social networks, transportation, bioinformatics, health care, security and intelligence analysis. The volume of data being represented in graph structure is rapidly increasing. As a result, graph analytics has emerged as a topic of great interest. Graph analytics is applied to uncover insightful relationships between people, places, objects and other entities. The graphs conform to the three Vs associated with big data: volume, velocity and variety. The volume refers to the large amounts of data generated every second. The velocity refers to the speed at which the new data is generated. The variety refers to the different kinds of data both structured and unstructured.

Graphs analytics has large number of applications in various fields. They are used in health care to study the spread of diseases, to detect and prevent epidemics [4]. Graph analysis plays a crucial role in systems biology [5][6]. It is used in the study of protein-protein interaction complex. It is an important tool in understanding the gene expression. Graphs are used to model the gene regulatory networks. Graph analytics is used in finding motifs and patterns in large gene networks. It is used in identifying new protein complexes and for studying and modelling metabolism in various organisms. Graphs are used to represent social networks. The range of applications of social network analysis is rapidly growing. It is used in studying the spread of information and influence [7][8]. It is used for targeted advertising [9], recommender system development [10], and community detection [11]. It is also used in intelligence, in anomaly detection, for example, in uncovering terrorist networks [12].

#### **1.2 RESEARCH CHALLENGES IN LARGE GRAPH PROCESSING**

Graph analytics is emerging as a powerful tool to extract value from big data. However, there are many difficult challenges to be addressed. The irregular nature of the graph processing applications makes it difficult to efficiently utilize the computational resources. As data from different domains are mapped to the graph model and as the scale of the data continues to grow, the graph problems outgrow the current computational and memory capabilities of sequential processors. It is essential to use the parallel computing resources to solve problems of large scale. Unfortunately, it is not straight forward to directly map the graph problems to the parallel hardware. Again, the irregular structure of the graph makes it highly difficult to parallelize the graph problems. The techniques that work for regular scientific applications may not be suitable to solve the graph problems. In this section, we discuss the problems involved in large graph processing.

#### **1.2.1 POOR LOCALITY OF REFERENCE**

Locality of reference is a fundamental principle of computing. It is the principle behind the caching technique that is used to improve computer system performance. There are two kinds of locality: temporal and spatial. Temporal locality is based on the idea that when some data/instruction is referred to, it is likely that it will be referred to again within a small duration. Spatial locality is based on the idea that when data/instructions are accessed, it is likely that nearby data/instructions will be accessed. Any data that an application needs to access is accessed through cache memory. If the data is not present in cache memory, it is first brought to cache memory from the global memory(main memory) and then accessed. However, if the data is present in cache memory it can be accessed directly from cache. The access to cache is orders of magnitude faster than access to main memory. Therefore, it is important for an application to exploit the cache memory to improve its performance.

An important factor that adversely affects the performance of a graph application is poor locality of reference. A graph application, typically, proceeds by visiting vertices. Visiting a vertex refers to accessing its adjacency list or some other data related to the vertex. The order in which the vertices are visited is very random in nature for many graph applications. Therefore, those graph applications tend to have highly random memory access pattern. By random access we mean access to memory addresses that are not sequential and that are not to the same address or adjacent addresses. The principle of locality might not be applicable when the access pattern is random. The cache utilization for many graph applications is low when processing large graphs, resulting in high data access time. Therefore, it is hard to extract good performance from such graph applications, even on serial computers.

The random access pattern also makes it difficult for the hardware prefetcher to work efficiently. Most modern processors are equipped with hardware prefetchers. The purpose of a prefetcher is to bring the data from the memory into the cache before they are needed. When the application needs to access data that has been prefetched, it can directly access it from the cache instead of waiting for it to be loaded from main memory. The prefetching mechanism can result in significant performance improvement as it reduces the number of cache misses. A prefetcher works by monitoring the data access pattern and predicting which data will be accessed. However, in the case of many graph applications, since the memory access pattern is random, it is often difficult for the prefetchers to predict which data will be accessed.

#### **1.2.2 LOW COMPUTATION TO DATA ACCESS RATIO**

Many graph applications only explore the vertices and edges of the graph without performing large computations using the accessed data. The applications spend most of the time accessing the data and there is very little computation performed on the accessed data. In applications involving large amount of computations it is often possible to hide the memory latency by overlapping the data access with computation. However, in case of aforementioned graph applications, since the computation to data access ratio is low, it is difficult to hide the memory latency using computation.

#### **1.2.3 SEQUENTIAL NATURE OF ALGORITHMS**

Most traditional graph algorithms are sequential in nature. The outcome of an iteration/task influences the following iteration/task. So the iterations/tasks can only be executed in sequence. It is difficult to efficiently map the traditional algorithms to the current parallel systems. Therefore, for many graph problems new parallel algorithms have been developed that can take advantage of the parallel resources. However, often these algorithms come at the expense of increased computational complexity. In most cases, the parallel implementations fail to outperform the most efficient sequential implementations.

#### **1.2.4 LOAD BALANCING**

Another major challenge in developing parallel graph applications is load balancing. For most graph problems, the computations are data-driven. The computations performed by an application is dictated by the graph structure. For efficient parallelization the tasks must be fairly distributed among the available computing units. In the case of graph algorithms, it is difficult to predict the work load corresponding to a task. The work load is not known until the data assigned to a task is accessed. Adding to this, many graphs in real world networks are irregular and have highly unbalanced degree distribution. This poses additional challenges in achieving load balanced partitioning.

#### 1.2.5 SYNCHRONIZATION AND COMMUNICATION COST

The parallelism in most graph applications is fine-grained. It is difficult to divide a task into multiple tasks that can work independently. Often the tasks need to communicate and synchronize. In multicore architecture, the tasks communicate by reading and writing data into common segments of shared memory. Each core has one or more private caches. When multiple tasks are accessing the same data, it is possible to have copies of the data in multiple caches. To maintain consistency of the data, cache coherency protocols are used. The cache coherency protocols can severely impact the scalability of the application.

Synchronization is essential for the correctness of the algorithms. However, heavy synchronization can result in degraded performance. Synchronization is achieved in multicore architecture using barriers, locks and atomic operations. These constructs are expensive and often result in temporarily blocking the tasks. Therefore, it is necessary to carefully design applications so that the impact of cache coherency protocols and synchronization is minimized. In distributed memory systems, the tasks communicate by passing messages. Since most graph applications exhibit finegrained parallelism, the communication cost can be very significant.

#### **1.3 PARALLEL ARCHITECTURES**

With the current scale of the graphs and the rate at which it is growing, it is becoming inevitable to use parallel computing. The current graphs are very large, with number of vertices and edges ranging from several millions to billions. The current workstations are incapable of processing such large graphs in practical time due to physical memory limitations and also the processing capacity. In recent years, there have been significant advance in parallel computing capabilities. There are different types of parallel architectures currently available. Based on the memory accessibility, they can be classified into shared memory and distributed memory architectures.

#### **1.3.1 SHARED MEMORY ARCHITECTURE**

In shared memory architecture all the processors have access to all memory as global address space. The processes can run in parallel on multiple processors/cores and they communicate by reading from and writing into the shared memory. Multicore processors are the most commonly used systems with shared memory architecture. Over the past few decades, there has been a consistent improvement in the computational power of the hardware. According to Moore's law, the number of transistors in an integrated circuit has doubled approximately every two years. However, due to heating issues and increased power consumption, it has become impractical to follow the phenomenon. Instead, the industry has moved toward multicore processors, which contain multiple computing units called cores integrated on a single chip.

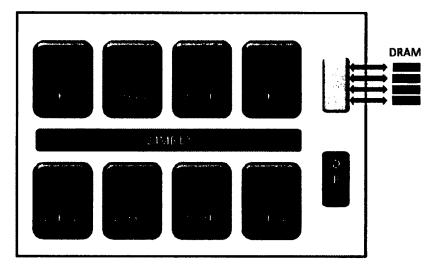

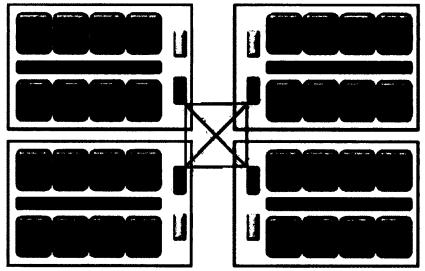

Multicore processors typically have multiple levels of caches and may also have a shared cache. In this dissertation, most of the results are obtained using Intel Xeon X7560 processor. It has four sockets and each socket has eight cores. Figure 1 shows an overview of the architecture. Each core has a 32KB L1 data cache and 256KB L2 cache. Additionally, there is also an L3 cache of size 24MB which is shared by all the cores in a socket. All the sockets are connected using a high speed QuickPath Interconnect which gives over a 100GB/sec bandwidth. IMC and QPI in the figure refer to integrated memory controller and QuickPath Interconnect respectively.

Shared memory machines are often classified into uniform memory access and non-uniform memory access(NUMA), based on the memory access times. In uniform access, all the processes take equal time to access the memory. These are often called as symmetric multiprocessors(SMP). In NUMA architecture, the memory access time depends on the memory location relative to the processor. These are often made by linking multiple SMPs like the X7560 architecture shown in Figure 1. Each core has access to memory in all the sockets but the access to non-local memory is

(a) Single Socket

(b) Four sockets connected using Quick Path Interconnect

Figure 1: Architectural overview of Intel Xeon X7560 processor

slower. OpenMP and Pthreads are the most common programming interfaces used for developing programs for shared memory architecture.

#### **1.3.2 DISTRIBUTED MEMORY ARCHITECTURE**

Distributed memory architecture constitutes multiple processors connected by a communication network. Each processor has its own local memory. Memory addresses of one processor do not map with another processor. Interprocess communication is achieved using message passing. The individual processors in a distributed architecture are usually made of commodity hardware.

MPI is the most commonly used interface for distributed computing. In distributed memory machines, the users are responsible to distribute the data among the processors and assigning tasks to the processors. When a processor needs to access the data in another processor, it is usually the task of the programmer to define how the data will be communicated. As the processors are connected by a network, the remote access time can take much longer time than the local access time, based on the network. The communication time is an important aspect to be considered when developing applications for distributed systems. The major advantage of distributed systems is its scalability. The computing and memory capacity of a distributed system can easily be extended by adding more processors. However, as the number of processors in a distributed system increases, so does the chance of hardware, software or network failures. Since programming on distributed systems can be an arduous task, there are many frameworks developed to make the task of programming easier. These frameworks provide features like fault tolerance, load balancing, scalability and reliability. The most popular frameworks include MapReduce [13], Spark [14], Pregel [15] and Graphlab [16]. Among these Pregel and Graphlab are developed for graph processing.

#### 1.4 OVERVIEW OF DISSERTATION AND CONTRIBUTIONS

The performance of many graph processing applications is dominated by memory access time. Therefore, it is critical to exploit the data locality to improve the performance. Graph processing application have highly random memory access pattern. When the graph size is large, random access to large data results in frequent cache misses, resulting in degraded performance. Optimizing the data locality is well studied for regular applications like linear algebra. Blocking is a well known optimization technique that improves the effective cache utilization [17]. The idea of blocking is to organize the memory accesses such that a small subset of data is loaded into the cache and is used/reused. It ensures that the data remains in cache across multiple accesses. The technique has been proven to be very effective for regular applications.

In this dissertation, we propose two techniques to improve the locality in graph algorithms: access transformation and task-set reduction. Access transformation technique changes the random memory access pattern in an application to more of a sequential access pattern. In many graph algorithms, the vertices/edges are systematically processed based on some property. In each iteration, a subset of vertices are processed. Most often the vertices are processed in a random order and the order is determined by some data structure. The key idea of access transformation technique is to use scan-and-extract operation in each iteration which sequentially scans all the vertices and extracts the vertices that are to be processed in a given iteration. The order of vertices obtained by the scan-and-extract operation is more likely to result in sequential access improving the spacial locality of the algorithm. We show the applicability of the technique using the k-core decomposition algorithm and triangle listing algorithm.

The task-set reduction technique focuses on improving the temporal locality. We define task-set as the collection of data that is repeatedly accessed to process a task. If the size of *task-set* is very large, then repeated random accesses to the data in *task-set* can result in large number of cache misses, severely impacting the performance. It is, therefore, very crucial to keep the *task-set* to a minimal size. Task-set reduction can be achieved in different ways like compression, blocking and elimination. Compression refers to storing the data using minimal amount of memory. By carefully examining the nature of the data and possible values of the data, it is often possible to reduce the size of the data structure that stores the data. For example, representing data in bit format can result in significant reduction in taskset size. The blocking technique [17] used for regular applications can also be used for task-set reduction. The idea is to partition the tasks such that each task works on a smaller *task-set*. However, unlike in regular applications, it may not be easily applicable. It might require significant changes to the algorithm to utilize blocking technique. Elimination refers to disposing of data structures which store data that can be extracted using other sources/data structures.

In this dissertation, we propose algorithms using these techniques for three graph

problems: k-core decomposition, maximal clique enumeration and triangle listing. The k-core of a graph is the largest induced subgraph with minimum degree k. The largest value of k that a vertex belongs to a k-core is called *core number* of the vertex. The k-core decomposition problem is to find the core number of all the vertices in a graph. It has applications in many areas including network analysis, computational biology and graph visualization. The primary reason for it being widely used is the availability of an O(n+m) algorithm. The algorithm was proposed by Batagelj and Zaversnik [18] and is considered the state-of-the-art algorithm for k-core decomposition. However, the algorithm is less suitable for parallelization and to the best of our knowledge there is no algorithm proposed for k-core decomposition on multicore processors. Also, the algorithm has not been experimentally analyzed for large graphs. In Chapter 2, we present an experimental analysis of the algorithm of Batagelj and Zaversnik and propose a new algorithm, ParK, that uses the access transformation technique to improve the memory locality. We provide an experimental analysis of the algorithm using graphs with up to 65 million vertices and 1.8 billion edges. We compare the *ParK* algorithm with state-of-the-art algorithm and show that it is up to 6 times faster than the state-of-the-art algorithm. We also provide a parallel methodology and show that the algorithm is amenable to parallelization on multicore architecture. We present experimental results obtained using a 4 socket Nehalem-EX processor which has 8 cores per socket which show that the algorithm scales up to 21 times using 32 cores.

A clique in a graph is a subgraph in which every pair of vertices is connected by an edge. A maximal clique is a clique which is not contained in any other clique. Maximal clique enumeration(MCE) problem is to find all the maximal cliques in a graph. MCE is a fundamental problem in graph theory. It plays a vital role in many network analysis applications and in computational biology. MCE is an extensively studied problem [60][61][32][65][69]. Recently, Eppstein et al. [32] proposed a state-of-theart sequential algorithm that uses degeneracy based ordering of vertices to improve the efficiency. In Chapter 3, we present an analysis of *task-set* size of Eppstein et al.'s algorithm. We propose a new algorithm using the *task-set reduction* technique. The new algorithm uses a new bit-based data structure. The new data structure not only reduces the *task-set* size significantly but also improves the performance of the algorithm by enabling the use of bit-parallelism. We illustrate the significance of degeneracy ordering in load balancing and experimentally evaluate the impact of

scheduling on the performance of the algorithm. We present experimental results on several types of synthetic and real-world graphs with up to 50 million vertices and 100 million edges. We show that our approach outperforms Eppstein et al.'s approach by up to 4 times and also scales up to 29 times when run on a multicore machine with 32 cores. We have also implemented the new algorithm on distributed architecture and the experimental results show that the algorithm scales well, up to 106 times using 128 processes.

~ 144

A triangle in a graph refers to a clique of size 3. Triangle listing problem is to find all the triangles in a graph. The triangle counting/listing problems are of high interest in network analysis applications. They are primarily used in finding a key statistical property of a graph called clustering coefficient. Many algorithms for the triangle listing problem exist in the literature [92][93][94]. Out of those, the *edge-iterator* algorithm [93] is the most widely used algorithm. The algorithm repeatedly accesses the adjacency lists of the vertices and in random order resulting in poor memory locality. In Chapter 4, we propose a new algorithm, called *window-iterator* that uses the *access transformation* and *task-set reduction* techniques to improve the locality. Unlike, the *edge-iterator* algorithm, the *window-iterator* algorithm has limited number of iterations, each iteration working on a smaller *task-set*. The *window-iterator* outperforms the *edge-iterator* algorithm for large graphs(upto 1.4 times) and the gap increases as the graph size increases. We have implemented the approach for multicore architecture. Our experimental results show that the new algorithm scales well, more than 29 times using 32 cores.

### **CHAPTER 2**

### ACCESS TRANSFORMATION

Graphs are ubiquitous. There are many interesting and complex graph problems that have applications in different domains. Graph problems have been well studied and there exist efficient algorithms for most of the problems. The main focus of the traditional algorithms was to reduce the computational complexity. Though many algorithms are NP-hard, since the graphs were small in size, the problems were solvable in practical amount of time. However, since the graph problems are being applied in a variety of domains and as the graph sizes are rapidly growing, it is becoming increasingly important to redesign traditional algorithms considering various other factors like memory access pattern, data structures and memory bandwidth.

One of the major factors governing performance of graph algorithms is poor locality of reference. The memory access pattern in most graph algorithms is highly random. The random access pattern coupled with the large size of the graphs results in poor utilization of the cache memory. Most of the data accesses result in cache misses and the data has to be accessed from the main memory which has greater latency, degrading the performance of the application.

In this chapter, we present a technique called *access transformation* which improves the locality of reference by changing the memory access pattern. Many graph algorithms are based on systematic exploration of the graphs. They traverse the nodes in some order that is specific to the problem. For example, in BFS, the nodes are traversed based on their distance from the source node, in k-core decomposition algorithm, the nodes are traversed based on their degree. The algorithms explore the graphs in multiple iterations, processing a subset of nodes in each iteration. However, the order of vertices processed in an iteration is mostly random which can severely impact the performance.

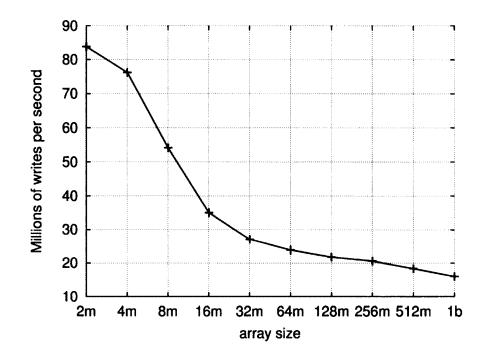

To show the impact of random access, we ran an experiment which performs read and writes on all the elements in an integer array in random order. The graph in Figure 2 clearly shows that the memory latency increases as the data size increases. The array size is shown in millions(m) and billions(b).

Figure 2: Plot showing the memory latency for random writes

The access transformation technique refers to changing the random access pattern to sequential access. In some algorithms it may be straight forward to achieve it while in some cases it may be required to redesign the algorithm. Often, some data structure is used to store problem specific data such as the vertices to be processed in the next iteration, the order of vertices, or the distance of a vertex from a source vertex. This data structure, in general, governs the access pattern of the next iteration. The main idea behind access transformation technique is to use scan-andextract operation to extract the data when required instead of storing it in a data structure. By eliminating the random access causing data structure, the operation results in a relatively more sequential access pattern thus improving the performance of the application.

The *scan-and-extract* operation reduces the random nature of the access pattern. However, it comes at the expense of increased number of operations which are required for the scan operation. As, the scan operation is performed in each iteration, if the number of iterations is too high, the overall time taken for the scan operation can be significant and might result in degraded performance. Therefore, the number of iterations and the cost of *scan-and-extract* operation must be considered when applying the *access transformation* technique.

The technique is inspired from the paper [19] which proposes a new read-based algorithm for BFS. The traditional BFS algorithms are queue-based in which a queue is used to store the vertices to be processed. Processing a vertex involves accessing its adjacency list(array) and adding its neighbors to the queue if they have not already been processed. The vertices are added in random order to the queue resulting in a highly random access pattern. The new algorithm eliminates the use of queue by scanning all the vertices to extract the vertices that are to be processed in the current iteration. Since the vertices extracted are not in random order, the algorithm improves the opportunity of sequential access pattern and is shown to outperform the traditional BFS algorithms.

The access transformation technique is applicable to algorithms with limited number of iterations that process a subset of vertices in each iteration. The applicability of the technique is, nevertheless, not limited to those algorithms. It is a more general approach and can also be applied in other scenarios. However, the algorithms might need to be redesigned to limit the number of iterations. For example, the triangle listing problem has highly random access pattern but the algorithm has large number of iterations. In Chapter 4, we show how the algorithm can be redesigned to limit the number of iterations facilitating the use of access transformation technique and also the task-set reduction technique discussed in the next chapter.

There is also an added advantage to the access transformation technique. The technique, in general, results in an approach that is amicable to parallelization. Since the random access pattern limits the benefits of parallelism, by transforming the access pattern to sequential the technique results in a better scalable approach. We have seen that the access transformation technique can be used at the expense of increased cost of scan-and-extract operation. However, the scan-and-extract operation is embarrassingly parallel and the computational time for the operation can be greatly reduced by using parallelism.

In the rest of the chapter, we show how the *access transformation* technique can be applied to the k-core decomposition algorithm. We first present, in Section 2.1, some definitions and notations and then in Section 2.2 explain in detail the state-ofthe-art algorithm for k-core decomposition focusing on its memory access pattern. In Section 2.3, we discuss how the *access transformation* technique can be used for

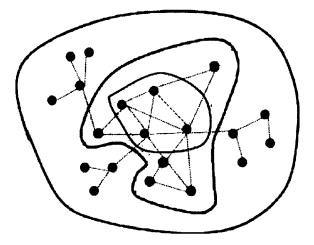

Figure 3: An example graph showing different cores

this problem and present a new algorithm, called ParK, that adopts the technique. The parallel methodology of ParK algorithm is discussed in Section 2.4. In Section 2.5, we present the experimental results using various graphs from different datasets and show that the new algorithm outperforms the start-of-the-art algorithm by upto 6 times and the performance gap becomes larger as the graph size grows. Also the new algorithm is scalable resulting in speed-up of upto 21 time using 32 cores.

#### 2.1 K-CORE DECOMPOSITION

The k-core of a graph is the largest induced subgraph with minimum degree k. The notion of a core was first introduced in 1983 by Seidman et al. [20]. Since then, it has been extensively studied and used in applications in many areas including network analysis, computation biology and visualization. k-core has been primarily applied in identifying the cohesive subgroups in a network. Many notions can be considered for identifying such groups including cliques, k-plexes, n-cliques [21]. While most other approaches are computationally expensive, k-core decomposition can be computed in linear time.

#### 2.1.1 DEFINITION AND NOTATIONS

Let G = (V, E) be a graph where V is the set of vertices and E is the set of edges and let n = |V| and m = |E|. The k-core of the graph G, is the largest

induced subgraph in which every vertex has degree at least k. The core number or coreness of a vertex v, is the largest value of k for which v belongs to the k-core i.e.  $core(v) = max\{k | v \in k\text{-core}\}$ . Note that (k + 1)-core is a subset of k core. A k-shell of a graph G is the subgraph induced by the set of vertices in G whose core number is k, i.e. the vertices that belong to k-core but not (k + 1)-core. In Figure 3, all the vertices inside the blue, green and red boundaries belong to 1-core, 2-core and 3-core respectively. The vertices colored in blue, green and red belong to 1-shell, 2-shell and 3-shell respectively and have core numbers 1, 2 and 3 respectively. The problem of k-core decomposition of the graph is to find all the k-cores of the graph or in other words, find the core numbers of all the vertices in the graph. In the rest of the chapter, we use N(v) to denote the neighborhood of v (note that  $v \notin N(v)$ ) and core(v) to denote the number of v. The degree of vertex v is denoted by deg(v). n and m denote the number of vertices and edges in the graph, respectively.

#### 2.1.2 APPLICATIONS

k-core decomposition has been used in analyzing and understanding the internet topology [22][23]. It has been used in the study of influential spreaders in complex networks [24]. It was shown that the most efficient spreaders are those located within the core of the network. It was used in detecting dense communities in large, social networks [25][26]. k-core decomposition is considered as an important tool in visualization [27][28][29]. In computational biology it was used in analyzing and detecting protein interactions [30] and analyzing gene networks [31]. k-core decomposition is used as a pre-processing step in other graph problems like finding maximal and maximum cliques [32][33]. It is considered an important tool in network analysis and is included in network analysis packages [34][35][16].

#### 2.2 RELATED WORK

The algorithm for computing the core numbers of all the vertices in the graph is shown in Figure 4. It involves repeatedly removing the minimum degree vertices from the graph. The degree of the vertex when it is being removed is the core number of the vertex. The function getSmallestDegreeVertex in Figure 4 returns the smallest degree vertex in the remaining graph. The main challenge in k-core decomposition is to find, in each iteration, the minimum degree vertex in the remaining graph. A simple way is to scan the degrees of all the vertices in the graph. Clearly, this method 1: while G is not empty do 2: v = getSmallestDegreeVertex(G)3: core(v) = deg(v)4: for each vertex  $u \in N(v)$  do 5: decrement deg(u) by 1 6: end for 7: delete v from G 8: end while

Figure 4: The k-core decomposition algorithm outline

is highly inefficient. Another method is to maintain a sorted list of vertices. This is the idea behind the BZ algorithm explained in the next section.

#### 2.2.1 THE BZ ALGORITHM

The algorithm for k-core decomposition that is considered state-of-the-art is proposed by Batagelj and Zaversnik (we refer to it as BZ algorithm in the rest of the chapter). It is a linear time algorithm. It solves the problem of finding the minimum degree vertex in the graph by maintaining a list of vertices sorted in increasing order of degree. In each iteration, when a vertex is processed and the degree of its neighbors is reduced, the neighbors are moved to the appropriate position in the sorted list. The algorithm uses count sort to compute the initial sorted list.

Figure 5 shows the BZ algorithms. The algorithm takes the graph G as input. It uses four arrays: deg, vert, pos and bin, to keep tract of their degree and the order of the vertices to be processed. The arrays deg, vert, pos are of size n, where n is the number of vertices in the graph. The array bin is of size M + 1 where M is the maximum degree of the graph. The function getSortedArray takes the graph as input, It initializes the four arrays and returns them as output. The array deg is initialized to contain the degree of the vertices in the graph. Note that the vertices are numbered from 0 to n - 1. deg[i] represents the degree of vertex i. The vert array contains all the vertices in the graph in increasing order of degree. The pos array stores the positions/indexes of vertices in vert array. For example, if vertex u is at index i in vert array i.e vert[i] = u, then pos[u] = i. The sorted array vert can be viewed as an array of bins, each bin containing a set of vertices of same degree. So, the array vert is nothing but bin of degree 0 vertices followed by bin of degree 1

1: procedure kcoreBZ(G)(deg, vert, pos, bin) = getSortedArray(G)2: for i = 0 to n - 1 do 3: 4: v = vert[i]for each vertex  $u \in N(v)$  do 5: if deg[u] > deg[v] then 6: 7: pu = pos[u]pw = bin[deg[u]] $\triangleright$  get the position of first vertex in bin 8: w = vert[pw] $\triangleright$  get the first vertex in bin 9: 10: if  $u \neq w$  then vert[pu] = wvert[pw] = u $\triangleright$  swap u and w in vert 11: 12: pos[w] = pupos[u] = pw > update their positions in pos end if 13: increment bin[deg[u]] by 1 14: decrement deg[u] by 1 15: end if 16: 17: end for end for 18: 19: end procedure 20: function getSortedArray(G)maxDeg = 021: 22: for i = 0 to n - 1 do deg[i] = getDegree(i, G)23: if deg[i] > maxDeg then maxDeg = deg[i] end if 24: end for 25: for i = 0 to maxDeg do bin[i] = 0 end for 26: 27: for i = 0 to n - 1 do increment bin[deg[i]] by 1 end for 28: start = 0for i = 0 to maxDeg do 29: num = bin[i]30: bin[i] = start31: 32: increment start by num end for 33: for i = 0 to n - 1 do 34: pos[i] = bin[deg[i]]35: vert[pos[i]] = i36: increment bin[deg[i]] by 1 37: 38: end for for i = maxDeg down to 1 do bin[i] = bin[i-1] end for 39: **return** (deg, vert, pos, bin) 40: 41: end function

Figure 5: The algorithm of Batagelj et al.

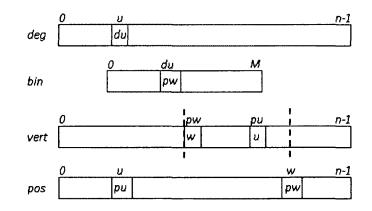

Figure 6: A figure showing the memory accesses required for an iteration in BZ algorithm

vertices and so on. The array bin contains the index of the first vertex in each bin i.e. bin[i] contains the index of the first vertex with degree i in the vert array.

The function getSortedArray uses count sort to compute the sorted array vert which can be computed in O(n) time. The function getDegree in line 23 returns the degree of a vertex. Once the initial four arrays are returned by the getSortedArray function, the vertices are processed one at a time in the order given in vert array. Processing a vertex v involves reducing the degree of all its neighbors by 1 and updating the vert, pos and bin arrays accordingly. Whenever, the degree of a vertex is decremented (by 1) it needs to be moved to appropriate bin (to the preceding bin). To achieve that, the vertex is swapped with the first vertex in the current bin by updating appropriate values in vert and pos arrays. And then, bin array is updated such that the vertex belongs to the preceding bin. The time complexity of the algorithm is shown to be O(n + m).

#### Memory access pattern in BZ algorithm

We have seen that BZ algorithm provides a linear time solution for k-core decomposition and is considered the state-of-the-art algorithm. However, we observe that the memory access pattern of the algorithm is more random in nature. As can be seen in Figure 5, the algorithm uses four arrays deg, vert, pos and bin. It can be observed that the memory access pattern of these arrays is highly random. Each iteration requires random read and write access to these arrays. Figure 6 shows the memory accesses required when a vertex v is processed and its neighbor u's degree is reduced. du in the figure denotes deg[u]. The operation requires read and write access to deg[u], vert[pu], vert[pw], pos[u], pos[w] and bin[du]. Notice that all these data elements are in random positions in the four arrays. While the size of bin array may be small, the sizes of the other three arrays can be very large. So there is a high chance that the access to each of these data elements incurs a cache miss and requires access to main memory. The access pattern of the adjacency lists also impacts the performance. It can be seen from Figure 5 that the adjacency list of a vertex is accessed exactly once in the algorithm. The order in which the adjacency lists are accessed is governed by the *vert* array. Though, the accesses are more sequential in the initial iterations, as the vertices are processed and as the *vert* array is updated, the access pattern of adjacency lists becomes more random in nature.

#### Parallelizing the BZ algorithm

We have seen in Section 2.2.1 that the *vert* array can be viewed as an array of bins. Each bin consists of vertices of same degree. Parallelizing the BZ algorithm for multicore architecture can be done by distributing all the vertices in a bin to the available processing units. Each processing unit processes the vertices assigned to it. Recall that processing a vertex involves reducing the degree of its neighbors and accessing multiple locations in the four arrays (for example, in Figure 6 the locations deg[u], vert[pu], vert[pw], pos[u], pos[w] and bin[du] are accessed). However, since multiple processing units are sharing the four arrays and reading and writing into the arrays, it might result in race conditions and inconsistent results. To avoid that, synchronization constructs like locks need to be used. For example, in Figure 6, all the data elements deg[u], vert[pu], vert[pw], pos[u], pos[u], pos[w] and bin[du] should be locked before reading from and writing into them. Due to the high cost of synchronization constructs which are very expensive, the BZ algorithm is not amicable to parallelization.

#### 2.2.2 DISTRIBUTED ALGORITHM

There is a distributed algorithm proposed for k-core decomposition [36]. Each process is assigned a set of vertices and is responsible for calculating the core numbers of the vertices assigned to it. If there are p processes, numbered 0 to p - 1, then a vertex i is assigned to the process numbered  $i \mod p$ . For each vertex assigned to

a process, it stores an array consisting of core numbers of its neighbors. The core number of each vertex is initialized to the degree of the vertex and is updated during the decomposition process. The algorithm is based on the idea that the core number of a vertex can be calculated based on the core number of its neighbors according to the following theorem:

**Theorem:** For each vertex  $u \in V$ , core(u) = k if and only if

- 1. there is a subset  $V_k \subseteq N(u)$  such that  $|V_k| = k$  and  $\forall v \in V_k : core(v) \ge k$

- 2. there is no subset  $V_{k+1} \subseteq N(u)$  such that  $|V_{k+1}| = k+1$  and  $\forall v \in V_{k+1}$ :  $core(v) \ge k+1$

The core number of the vertices is calculated using the core number of their neighbors. Once the core number of a vertex is updated it is communicated to the other processes to which its neighbors are assigned. This is repeated until core number of none of the vertices is updated. Unlike the BZ algorithm, in which the adjacency list of a vertex is accessed only once, the adjacency list of a vertex is accessed multiple times i.e. whenever the core number of any of its neighbors is updated. This approach results in significant increase in number of operations. Therefore, it is more suitable to a distributed environment where there are large number of computing nodes and each computing node is assigned only a few vertices. However, this approach is less suitable for multicore architecture with only a limited number of threads and each thread is assigned large number of vertices. Since each thread has to repeatedly access the adjacency lists of the vertices assigned to it, the working set for the thread consists of all its vertices and their neighbors which can be too large to fit in cache memory thus resulting in poor locality of reference.

There are approaches proposed for for k-core decomposition of dynamic networks [37][38][39]. These approaches primarily focus on efficiently maintaining the core numbers of the vertices as the graph changes over time.

#### 2.3 PARK ALGORITHM

The k-core decomposition problem is a good candidate for applying the access transformation technique. It uses different arrays (vert, pos, bin) that result in random memory access pattern. Though the original approach, i.e. BZ, requires n iterations, it can easily be modified to limit the number of iterations to maximum degree, M. We propose a new algorithm for k-core decomposition called ParK (parallel

```

1: procedure kcoreParK(G)

2:

todo = n

level = 0

3:

for i = 0 to n - 1 do deg[i] = getDegree(i, G) end for

4:

while todo > 0 do

5:

curr = scan-and-extract(deg, level)

6:

while |curr| > 0 do

7:

8:

decrement todo by |curr|

next = processSublevel(curr, deg, level)

9:

10:

curr = next

end while

11:

increment level by 1

12:

end while

13:

14: end procedure

15: function scan-and-extract(deg, level)

16:

curr = \emptyset

17:

for i = 0 to n - 1 do

if deg[i] = level then

18:

19:

add i to curr

end if

20:

end for

21:

22:

return curr

23: end function

24: function processSublevel(curr, deg, level)

next = \emptyset

25:

for each vertex v in curr do

26:

27:

for each vertex u adjacent to v do

if deg[u] > level then

28:

decrement deg[u] by 1

29:

30:

if deg[u] = level then

31:

add u to next

end if

32:

end if

33:

end for

34:

end for

35:

return next

36:

37: end function

```

Figure 7: ParK algorithm

k-core) which adapts the access transformation technique. The algorithm eliminates the use of the three arrays (vert, pos and bin) and uses scan-and-extract operation to get the list of vertices to be processed in an iteration.

#### 2.3.1 DESCRIPTION

The *ParK* algorithm processes the vertices in levels. Processing a vertex refers to accessing its adjacency list and reducing the degree of its neighbors that have not already been processed. In level *i*, all the vertices in shell *i* are processed (recall that *k*-shell contains all the vertices that belong to *k*-core but not k + 1-core). The *ParK* algorithm is based on the idea that instead of maintaining a sorted array of vertices, we can generate the array at each level. The outline of the *ParK* algorithm is given in Figure 7. The algorithm uses three arrays *deg*, *curr* and *next*. The *deg* array is initialized to contain the degree of the vertices similar to the BZ algorithm. Note that the vertices in the graph are numbered from 0 to n - 1. *deg*[*v*] contains the degree of vertex *v*. As the vertices are processed and degree of their neighbors are reduced, the *deg* array is updated. The *deg* array at the end of *kcoreParK* procedure contains the core numbers of all the vertices in the graph.

Processing a level l is done in two phases: scan phase and loop phase. In scan phase (which is same as *scan-and-extract* operation in *access transformation* technique), the *deg* array is scanned and the vertices that are to be processed in the current level are extracted into *curr* array. Note that the vertices in *curr* are in sequential order i.e. if u = curr[i] and v = curr[j] where i < j then u < v. The scan phase is performed using *scan-and-extract* function given in Figure 7. The loop phase consists of one or more sub-levels (or iterations). In each sub-level, all the vertices in *curr* array are processed. When processing a vertex v in *curr*, if any neighbor vertex, u, is moved to the current level i.e. deg[u] is reduced to l, then u is added to *next* array. At the end of each sub-level, the contents of *next* are transferred to *curr* so that they can be processed in the next sub-level. The lines 7 through 11 in Figure 7 correspond to the loop phase. The *processSublevel* function in Figure 7 processes the vertices in current sub-level and returns the array of vertices that are to be processed in the next sub-level.

Figure 8: A plot showing the percentage of vertices processed in first sub-level of all the levels

# 2.3.2 MEMORY ACCESS PATTERN OF THE PARK ALGORITHM

As can be seen in Figure 7, the *ParK* algorithm uses three arrays *deg*, *curr* and *next* arrays. The read and write accesses to *curr* and *next* arrays is sequential. Also, the access to *deg* array in *scan-and-extract* function is sequential. However, the loop phase requires random access to the *deg* array (line 28 in Figure 7). Note that, BZ algorithm also performs the same random accesses to the *deg* array.

The access pattern of the adjacency lists in ParK algorithm is governed by the order in which vertices are added to the *curr* and *next* arrays. In the *scan-and-extract* function, the order of vertices added to the *curr* array is guaranteed to be sequential. Therefore, the first sub-level in each level of the algorithm results in sequential access of the adjacency lists. However, in subsequent sub-levels there is no such guarantee and the adjacency lists are accessed in random order. From our experiments, we observe that, for most graphs, the majority of vertices are processed in first sub-level. The plot in the Figure 8 shows the percentage of vertices processed in first sub-level in all the levels.

# 2.3.3 ANALYSIS OF THE ALGORITHM

In this section, we analyse the time complexity of the ParK algorithm.

**Lemma 1.** The maximum number of levels in *ParK* algorithm is  $k_{max}$ , where  $k_{max}$  is the largest value of k for which k-core is present in the graph.

**Proof:** The algorithm uses a variable todo to keep track of the number of vertices to be processed. It can be seen from the procedure kcoreParK in Figure 7 that todo is decremented in each sub-level by the number of vertices processed in the sub-level. Therefore, todo always contains the count of number of vertices to be processed. Since at the end of level  $k_{max}$  all the vertices have been processed and the value of todo is zero, the maximum number of levels is  $k_{max}$ .

Lemma 2. The combined time taken for scan phase in all the levels is  $O(k_{max}n)$  *Proof:* The scan phase in each level takes O(n) and since there are  $k_{max}$  levels, the combined scan time for all the levels is  $O(k_{max}n)$

**Lemma 3.** The combined time taken for loop phase in all the levels is O(m)

**Proof:** In a single call to processSublevel a subset of vertices is processed. Combinedly in all the calls to processSublevel, all the n vertices are processed. Note that, each vertex is processed exactly once i.e. when its degree becomes equal to the current level. We have seen that processing a vertex v includes reducing the degree for each of its neighbor if it has not already been processed which takes  $O(d_v)$  time where  $d_v$  is the degree of vertex v. Therefore, to process all the n vertices it takes O(m) time.

Combining lemmas 2 and 3 (and O(m) time for line 4), the computational complexity of ParK algorithm is  $O(k_{max}n + m)$ . Though the computational complexity of BZ algorithm, which is O(n+m), is less compared to the ParK algorithm, our experimental results show that ParK algorithm outperforms BZ algorithm. The reason is that by using the scan phase, ParK significantly reduces the number of random memory access resulting in better locality of reference. The BZ algorithm requires random read and write accesses to three different arrays of size n while in ParKalgorithm requires random access to only one array. Though the theoretical time taken for the scan phase seems significant, in practice the time taken for scan phase is less compared to the time saved due to the scan phase. Another major advantage of scan phase is that it is embarrassingly parallel. It can easily and efficiently be distributed among different processors and can scale linearly.

#### 2.4 PARALLEL METHODOLOGY OF PARK ALGORITHM

In this section, we describe a level-synchronous approach to parallelizing the ParK algorithm. We have seen that the ParK algorithm processes the vertices in levels. Since the number of levels is limited, there is generally sufficient degree of parallelism available in each level. Parallelizing the ParK algorithm involves individually parallelizing the two phases in the algorithm: scan phase and loop phase. Parallelizing the scan phase is simple and trivial. The *n* vertices are equally divided among the *t* threads and each thread scans n/t vertices. Note that distributing the *n* vertices among *t* threads can be done in several ways. To minimize cache misses, contiguous chunks of vertices are assigned to the threads. To process each vertex, a thread reads its degree and if it is equal to the current level it adds the vertex to curr array. Since there are only a few operations performed for each vertex, the load is well balanced resulting in linear speed-up.

Though, it is simple to parallelize the scan phase, there is one issue to be addressed. It is to be noted that, the array *curr* is shared between all the threads and multiple threads writing to it may result in race conditions. The parallel version of scan - and - extract function that addresses the issue of race conditions is shown in Figure 9. The function atomicIncrement(idx, 1) increments the value of idx by 1 and returns its old value atomically (implemented using  $atomic \ capture$  construct in OpenMP). Using atomic operations the race conditions are eliminated. However, the atomic operations are expensive and too many atomic operations can significantly downgrade the performance. To reduce the number of atomic operations, the vertices are added in batches instead of a single vertex. We use a local buffer of size b. Instead of adding each vertex to *curr*, they are first added to the local buffer. When the buffer is full, idx is atomically incremented by b and all the vertices are transferred from local buffer to *curr*. This reduces the number of atomic operations by a factor of b. Note that, to avoid cache invalidation we choose the size of local buffer to be a multiple of cache line size.

The major component in loop phase is the function *processSublevel*. We have seen that in *processSublevel* all the vertices in *curr* are processed i.e. the degree of all their neighbors are reduced and if any of the neighbors belong to the current level, it is added to *next*. Parallelizing the function is done by equally distributing the vertices in *curr* to all the threads. However, it might result in race conditions as multiple threads access the *deg* and *next* arrays. To avoid race conditions, all updates to

these arrays are performed atomically. However, it is possible that the degree of a neighbor u, i.e. deg[u] is reduced to a value less than the current level value. For example, let deg[u] = level + 1 and two or more threads execute the line 17 at the same time, test positive for the condition and execute line 18. The resultant value of deg[u] will be less than *level* which the correct value of deg[u] is *level*. This issue is fixed using the lines 19 through 21. Vertices are added to the *next* array in batches similar to the way vertices are added to *curr* in the *scan* phase i.e. using atomic increments and local buffers.