# Old Dominion University ODU Digital Commons

**Computer Science Theses & Dissertations**

**Computer Science**

Fall 2017

# Efficient Machine Learning Approach for Optimizing Scientific Computing Applications on Emerging HPC Architectures

Kamesh Arumugam Karunanithi Old Dominion University

Follow this and additional works at: https://digitalcommons.odu.edu/computerscience\_etds Part of the <u>Computer Sciences Commons</u>

#### **Recommended** Citation

Karunanithi, Kamesh A.. "Efficient Machine Learning Approach for Optimizing Scientific Computing Applications on Emerging HPC Architectures" (2017). Doctor of Philosophy (PhD), dissertation, Computer Science, Old Dominion University, DOI: 10.25777/ s49t-1525

https://digitalcommons.odu.edu/computerscience\_etds/33

This Dissertation is brought to you for free and open access by the Computer Science at ODU Digital Commons. It has been accepted for inclusion in Computer Science Theses & Dissertations by an authorized administrator of ODU Digital Commons. For more information, please contact digitalcommons@odu.edu.

# EFFICIENT MACHINE LEARNING APPROACH FOR OPTIMIZING SCIENTIFIC COMPUTING APPLICATIONS ON EMERGING HPC ARCHITECTURES

by

Kamesh Arumugam Karunanithi B.E. July 2010, Visvesvaraya Technological University, India

A Dissertation Submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirements for the Degree of

# DOCTOR OF PHILOSOPHY

COMPUTER SCIENCE

OLD DOMINION UNIVERSITY December 2017

Approved by:

Mohammad Zubair (Co-Director)

Desh Ranjan (Co-Director)

Balša Terzić (Co-Director)

Andrey Chernikov (Member)

# ABSTRACT

# EFFICIENT MACHINE LEARNING APPROACH FOR OPTIMIZING SCIENTIFIC COMPUTING APPLICATIONS ON EMERGING HPC ARCHITECTURES

Kamesh Arumugam Karunanithi Old Dominion University, 2017 Co-Directors: Dr. Mohammad Zubair Dr. Desh Ranjan Dr. Balša Terzić

Efficient parallel implementations of scientific applications on multi-core CPUs with accelerators such as GPUs and Xeon Phis is challenging. This requires - exploiting the data parallel architecture of the accelerator along with the vector pipelines of modern x86 CPU architectures, load balancing, and efficient memory transfer between different devices. It is relatively easy to meet these requirements for highlystructured scientific applications. In contrast, a number of scientific and engineering applications are unstructured. Getting performance on accelerators for these applications is extremely challenging because many of these applications employ irregular algorithms which exhibit data-dependent control-flow and irregular memory accesses. Furthermore, these applications are often iterative with dependency between steps, and thus making it hard to parallelize across steps. As a result, parallelism in these applications is often limited to a single step. Numerical simulation of charged particles beam dynamics is one such application where the distribution of work and memory access pattern at each time step is irregular. Applications with these properties tend to present significant branch and memory divergence, load imbalance between different processor cores, and poor compute and memory utilization. Prior research on parallelizing such irregular applications have been focused around optimizing the irregular, data-dependent memory accesses and control-flow during a single step of the application independent of the other steps, with the assumption that these patterns are completely unpredictable. We observed that the structure of computation leading to control-flow divergence and irregular memory accesses in one step is similar to that in the next step. It is possible to predict this structure in the current step by observing the computation structure of previous steps.

In this dissertation, we present novel machine learning based optimization techniques to address the parallel implementation challenges of such irregular applications on different HPC architectures. In particular, we use supervised learning to predict the computation structure and use it to address the control-flow and memory access irregularities in the parallel implementation of such applications on GPUs, Xeon Phis, and heterogeneous architectures composed of multi-core CPUs with GPUs or Xeon Phis. We use numerical simulation of charged particles beam dynamics simulation as a motivating example throughout the dissertation to present our new approach, though they should be equally applicable to a wide range of irregular applications. The machine learning approach presented here use predictive analytics and forecasting techniques to adaptively model and track the irregular memory access pattern at each time step of the simulation to anticipate the future memory access pattern. Access pattern forecasts can then be used to formulate optimization decisions during application execution which improves the performance of the application at a future time step based on the observations from earlier time steps. In heterogeneous architectures, forecasts can also be used to improve the memory performance and resource utilization of all the processing units to deliver a good aggregate performance. We used these optimization techniques and anticipation strategy to design a cache-aware, memory efficient parallel algorithm to address the irregularities in the parallel implementation of charged particles beam dynamics simulation on different HPC architectures. Experimental result using a diverse mix of HPC architectures shows that our approach in using anticipation strategy is effective in maximizing data reuse, ensuring workload balance, minimizing branch and memory divergence, and in improving resource utilization.

Copyright, 2017, by Kamesh Arumugam Karunanithi, All Rights Reserved.

# ACKNOWLEDGMENTS

The work presented in this dissertation, as well as other work completed during my graduate career, would have not have been possible without the support of the following people -

- I would like to thank **Dr. Mohammad Zubair** who decided to supervise my doctorate degree and share his experience and knowledge of high performance computing. His ability to ask fundamental questions to understand the given problem has helped me to develop a rational thought process.

- I would like to thank **Dr**. **Desh Ranjan** who decided to co-supervise my doctorate degree despite his many other academic and administrative commitments. His capability of proposing interesting solutions to problems and proving correctness of the proposed solution always inspired and motivated me.

- I would like to thank **Dr. Balša Terzić** for co-supervising my doctorate degree, and for being a constant source of real world scientific problems that have given my dissertation its purpose with immense practical value. His patience and intuitive explanations of the complex computational physics problems have sparked in me a newfound interest in computational sciences.

- I would like to thank **Dr. Andrey Chernikov** for giving precious advice and participating in my final defense committee.

- I would like to thank my parents, sister, and friends for their continued support and understanding when my PhD has led to periods of reduced social interaction and contact.

This work was supported in part by National Science Foundation through grant 1535641, Jefferson Science Associates Project No. 712336 and the U.S. Department of Energy (DOE) Contract No. DE-AC05-06OR23177, and Old Dominion University's Modeling and Simulation Graduate Research Fellowship during 2013-2016. I would also like to acknowledge the support of NVIDIA Corporation for the donation of Tesla K40 GPUs used in this research.

# TABLE OF CONTENTS

| LI | IST OF TABLES                                                                                                                                                            | ix                  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| LI | IST OF FIGURES                                                                                                                                                           | xi                  |

| C  | HAPTER                                                                                                                                                                   |                     |

| 1  | INTRODUCTION1.1AIM OF THE THESIS1.2THESIS CONTRIBUTIONS1.3THESIS ORGANIZATION                                                                                            | $\frac{4}{7}$       |

| 2  | <ul> <li>BACKGROUND.</li> <li>2.1 OVERVIEW OF PARALLEL ARCHITECTURES</li></ul>                                                                                           | 9<br>12<br>20<br>21 |

| 3  | <ul> <li>BEAM DYNAMICS SIMULATION</li> <li>3.1 OUTLINE OF THE ALGORITHM</li> <li>3.2 SEQUENTIAL SIMULATION</li> <li>3.3 PRIOR RESEARCH IN PARALLEL SIMULATION</li> </ul> | 32<br>41            |

| 4  | EFFICIENT PARALLEL SIMULATION ON GPUS4.1 MODELING ACCESS PATTERNS4.2 PARALLEL ALGORITHM4.3 EVALUATION AND EXPERIMENTAL RESULTS                                           | 66<br>70            |

| 5  | EFFICIENT PARALLEL SIMULATION ON HETEROGENEOUS ARCHI-<br>TECTURE                                                                                                         | 84<br>85            |

| 6  | CONCLUSIONS                                                                                                                                                              | 99                  |

| R  | EFERENCES                                                                                                                                                                | 101                 |

| A  | PPENDICES                                                                                                                                                                |                     |

| А  | ADAPTIVE MULTI-DIMENSIONAL INTEGRATION<br>A.1 OVERVIEW OF CUHRE<br>A.2 GPU-ACCELERATED PARALLEL ALGORITHM                                                                | 110                 |

| В  | PER | RFOF | RMA  | NCE           | 2 AN | ALY  | YSIS | 5Т | 00 | LS. |     |     | <br> | <br> | <br> |     | <br>. 115 |

|----|-----|------|------|---------------|------|------|------|----|----|-----|-----|-----|------|------|------|-----|-----------|

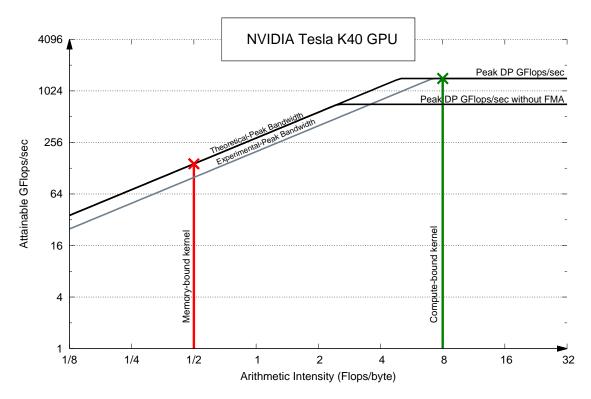

|    | B.1 | RO   | OFL  | INE           | PER  | FO   | RM   | AN | CE | MC  | DDE | ĽL. | <br> | <br> | <br> | ••• | <br>115   |

|    | B.2 | PRO  | OFIL | $\mathbf{ER}$ | МЕТ  | [RIC | CS . |    |    |     |     | ••• | <br> | <br> | <br> | ••• | <br>116   |

|    |     |      |      |               |      |      |      |    |    |     |     |     |      |      |      |     |           |

| VI | ТΑ  |      |      |               |      |      |      |    |    |     |     |     | <br> | <br> | <br> |     | <br>. 119 |

vii

# LIST OF TABLES

| Tabl | e Pa                                                                                                                                                                                                                                                                                                                                       | age |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1    | Specifications of three supercomputers from world's top-5 (as of June 2017).                                                                                                                                                                                                                                                               | 2   |

| 2    | Newton-Cotes formulae for different degrees.                                                                                                                                                                                                                                                                                               | 27  |

| 3    | Performance of TWO-PHASE-RP-KERNEL for computing retarded po-<br>tentials in a beam dynamics simulation with 100000 particles and for<br>different grid resolutions on NVIDIA Tesla K40 GPU                                                                                                                                                | 53  |

| 4    | Performance of HEURISTICS-RP-KERNEL for computing retarded poten-<br>tials in a beam dynamics simulation with 100000 particles and for different<br>grid resolutions on NVIDIA Tesla K40 GPU                                                                                                                                               | 62  |

| 5    | Performance of PREDICTIVE-RP-KERNEL for computing retarded poten-<br>tials in a beam dynamics simulation with 100000 particles and for different<br>grid resolutions on NVIDIA Tesla K40 GPU                                                                                                                                               | 78  |

| 6    | Execution time of compute retarded potentials stage of the simulation<br>using PREDICTIVE-RP-KERNEL for different simulation configurations<br>on NVIDIA Tesla K40 GPU                                                                                                                                                                     | 83  |

| 7    | Speedup of PREDICTIVE-RP-KERNEL compared against Two-PHASE-<br>RP-KERNEL and HEURISTICS-RP-KERNEL for different simulation con-<br>figurations on NVIDIA Tesla K40 GPU.                                                                                                                                                                    | 83  |

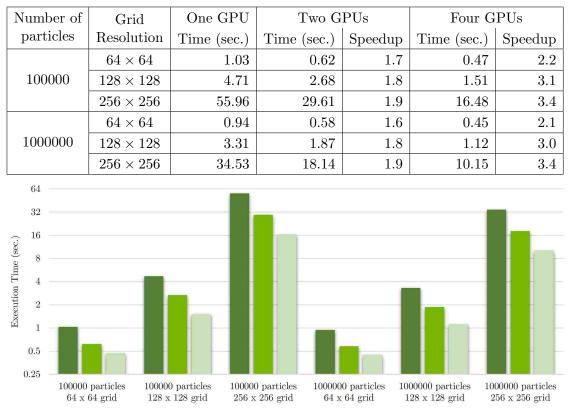

| 8    | Execution time of the parallel implementation of compute retarded po-<br>tentials stage of the simulation on MACHINE-G in GPU-only execution<br>mode for different simulation configurations with varying number of Tesla<br>K40 GPUs.                                                                                                     | 92  |

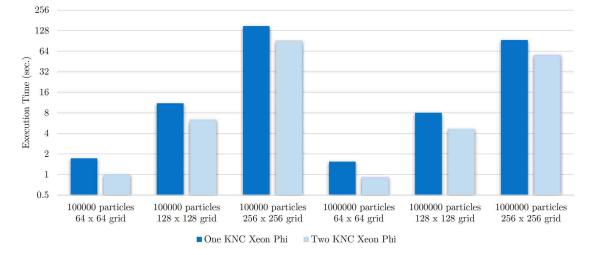

| 9    | Execution time of the parallel implementation of compute retarded poten-<br>tials stage of the simulation on MACHINE-X in Xeon Phi-only execution<br>mode for different simulation configurations with varying number of KNC<br>Xeon Phi coprocessor                                                                                       | 93  |

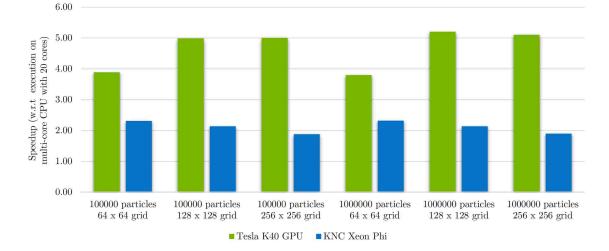

| 10   | Performance comparison of the parallel implementation of compute retar-<br>ded potentials stage on different HPC architectures - (a) Multi-core CPU<br>with 20 cores (using the CPU from MACHINE-X which is the fastest of the<br>two available multi-core CPUs), (b) Tesla K40 GPU from MACHINE-G,<br>and (c) KNC Xeon-Phi from MACHINE-X | 94  |

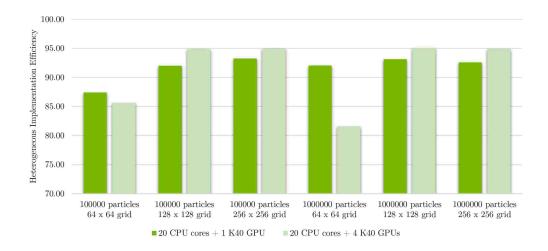

| 11 | Performance of the heterogeneous implementation of compute retarded  |    |

|----|----------------------------------------------------------------------|----|

|    | potentials stage of the simulation on MACHINE-G which is composed of |    |

|    | multi-core CPU and four NVIDIA Tesla K40 GPUs                        | 97 |

|    |                                                                      |    |

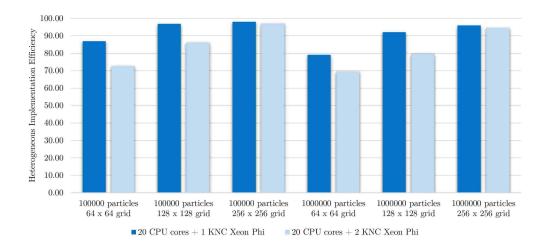

| 12 | Performance of the heterogeneous implementation of compute retarded  |    |

|    | potentials stage of the simulation on MACHINE-X which is composed of |    |

|    | multi-core CPU and two KNC Xeon Phi coprocessor                      | 98 |

# LIST OF FIGURES

| Figu | ure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1    | CUDA programming model for general purpose computing on NVIDIA GPUs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 10 |

| 2    | Memory latency divergence when the addresses accessed by SIMD group<br>are scattered in the memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 14 |

| 3    | Memory latency divergence when: (a) the addresses accessed by SIMD group are uniform (all equal), (b) the addresses accessed by SIMD group are consecutive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 15 |

| 4    | Control-flow divergence in GPUs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 16 |

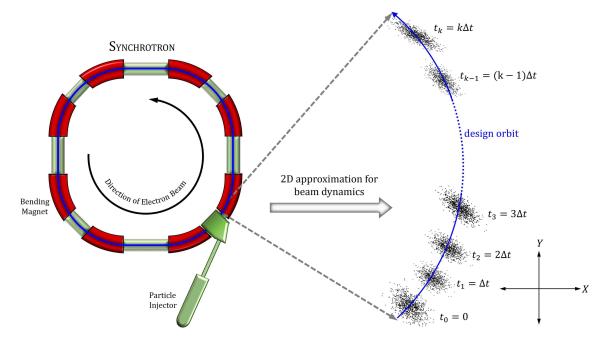

| 5    | Conceptual view of charged particles beam dynamics on a 2D plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 23 |

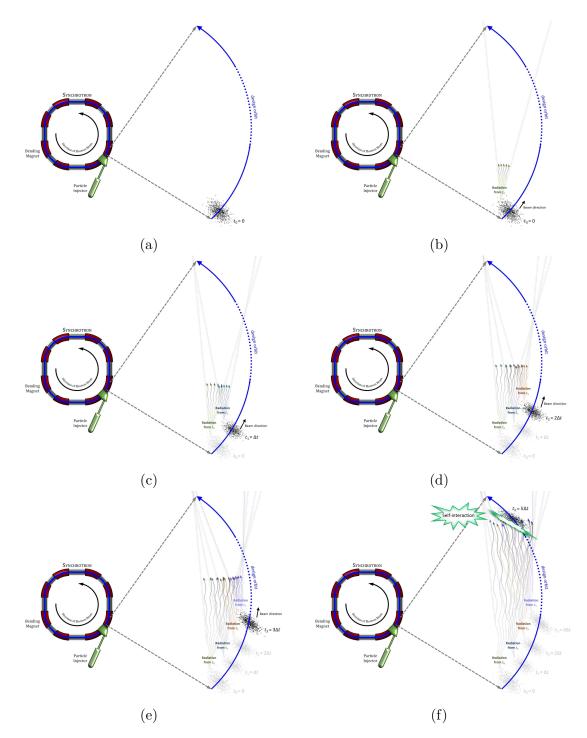

| 6    | Simulation of charged particles beam dynamics. (a) Particle distribution<br>for charged particle beam at time $t_0$ is generated from Monte Carlo sam-<br>pling of initial DF of N particles with a total charge of Q. (b) - (e) The<br>charged particles in the beam emits synchrotron radiation when forced to<br>travel along a curved trajectory under the influence of a bending force of a<br>accelerator magnets (referred to as <i>Bending Magnet</i> in the above figure).<br>(f) The radiations emitted from all the earlier time steps catch up with<br>the charged particle beam at time $t_k = k\Delta t$ for all integers $k > 0$ , and<br>these synchrotron radiations leads to hazardous self-interactions | . 24 |

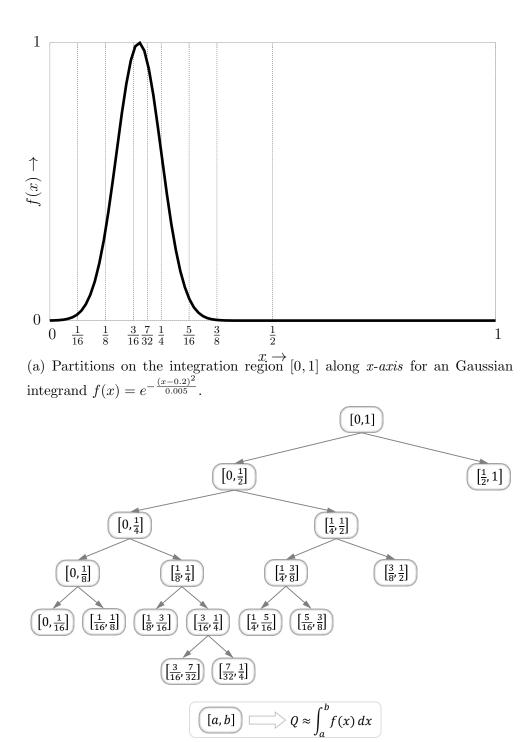

| 7    | Adaptive quadrature for the Gaussian integral $\int_0^1 e^{-\frac{(x-0.2)^2}{0.005}} dx$ using Simpson's quadrature rule with error tolerance $\tau = 0.001$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 29 |

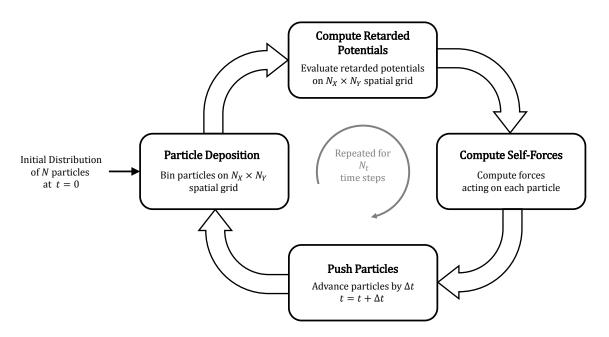

| 8    | Outline of charged particle beam dynamics simulation algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . 33 |

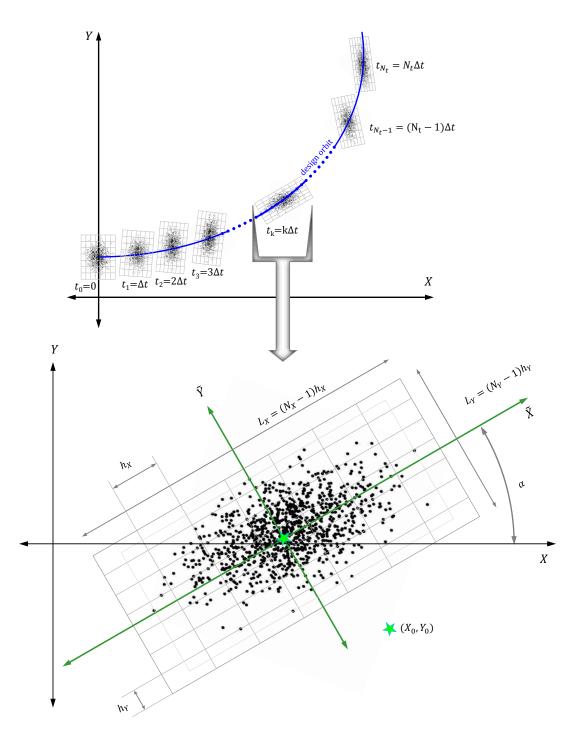

| 9    | Spatial-grid enclosing the particle distribution at a particular time step<br>of the simulation. Its size is determined by the outliers of the distribution<br>along the principal axes. Blue line denotes the design orbit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 35 |

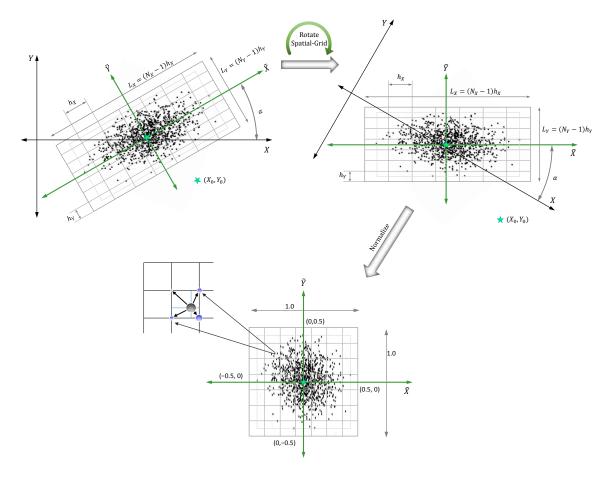

| 10   | Steps in particle deposition stage of the beam dynamics simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | . 36 |

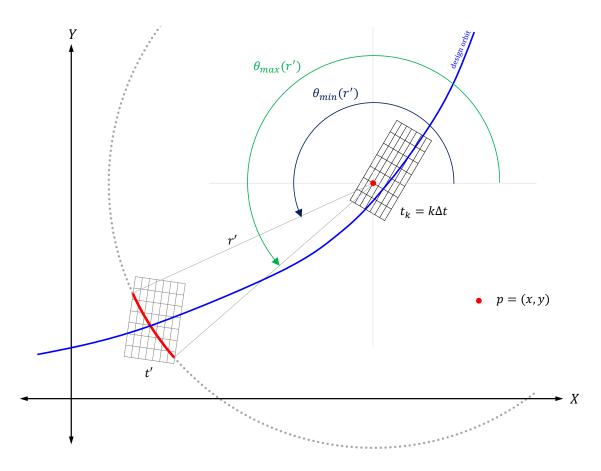

| 11   | Evaluation of integration limits in rp-integral.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 38 |

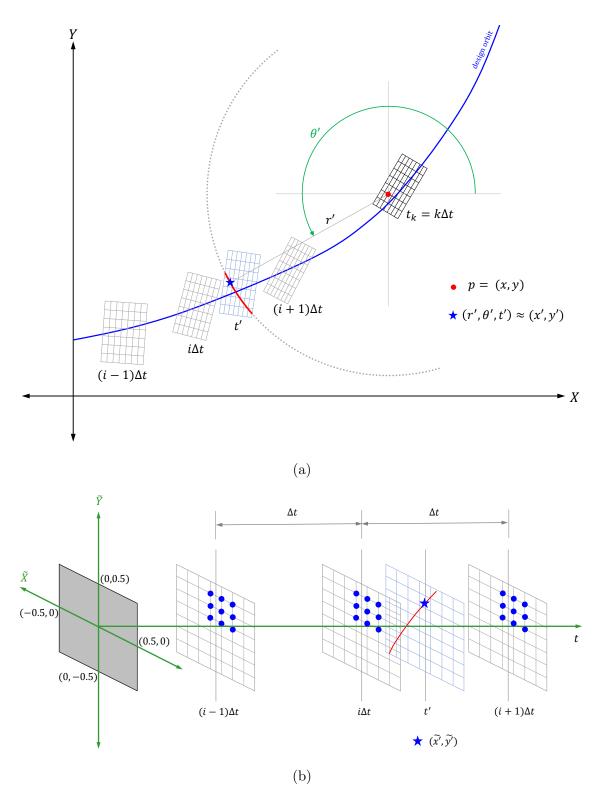

| 12   | Numerical approximation of integrand values in rp-integral using interpo-<br>lation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 39 |

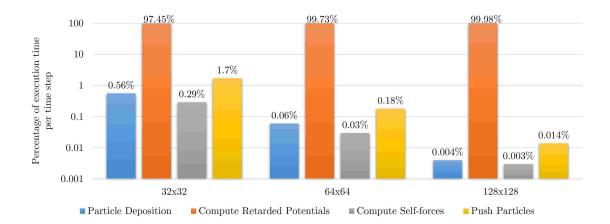

| 13 | Percentage of sequential execution time spent by different stages of the beam dynamics simulation per time step averaged over all time steps for various grid resolutions.                                                                                                                                                                      | 42  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

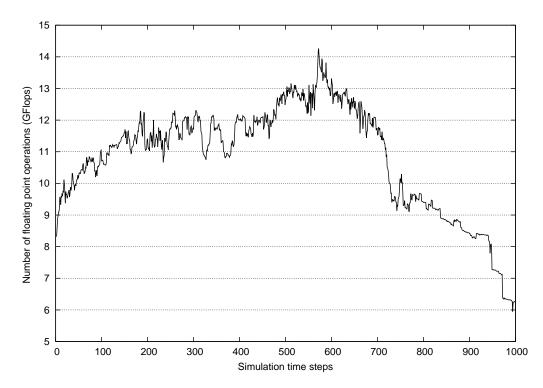

| 14 | Computational workload characteristics of beam dynamics simulation at different time steps                                                                                                                                                                                                                                                      | 45  |

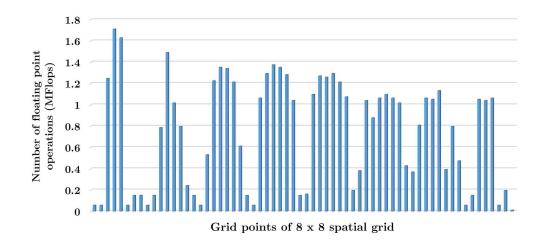

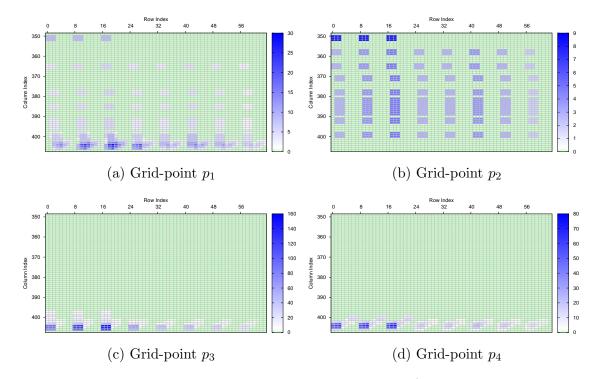

| 15 | Computational workload characteristics of beam dynamics simulation at different grid points.                                                                                                                                                                                                                                                    | 45  |

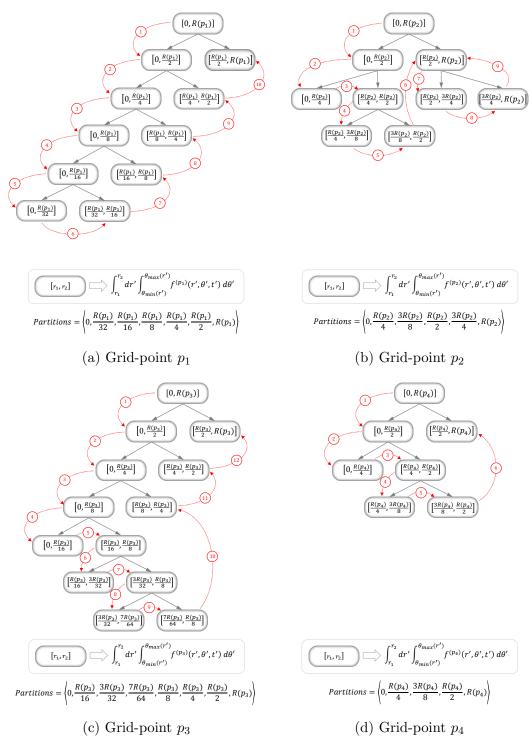

| 16 | Control-flow properties of rp-integral at different grid points                                                                                                                                                                                                                                                                                 | 47  |

| 17 | Memory access properties of rp-integral evaluation at different grid points.                                                                                                                                                                                                                                                                    | 49  |

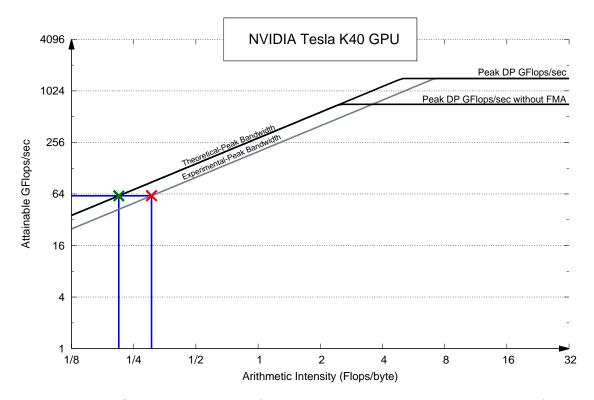

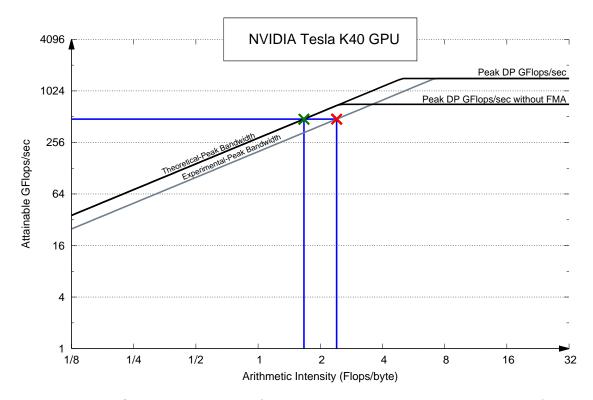

| 18 | Roofline model analysis for TWO-PHASE-RP-KERNEL on NVIDIA Tesla<br>K40 GPU                                                                                                                                                                                                                                                                      | 54  |

| 19 | Roofline model analysis for HEURISTICS-RP-KERNEL on NVIDIA Tesla<br>K40 GPU                                                                                                                                                                                                                                                                     | 63  |

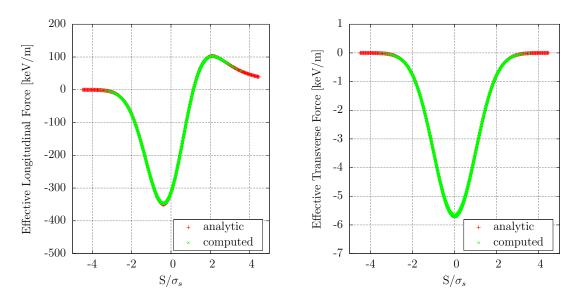

| 20 | Analytic versus computed effective longitudinal (left) and transverse (right) forces for the LCSL bend [47]: $N = 1000000$ particles on a $128 \times 128$ grid, bend radius $R_0 = 25.13$ m, $\theta_b = 11.4^{\circ}$ , longitudinal rms beam size $\sigma_s = 50$ $\mu$ m, emittance $\epsilon = 1$ nm, and total beam charge of $Q = 1$ nC. | 77  |

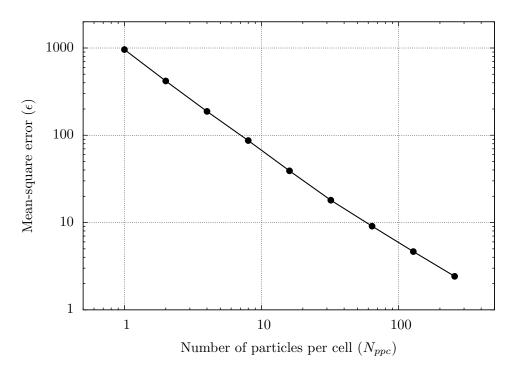

| 21 | Mean-square error for the longitudinal force, as defined in the text, as a function of the number of particles per cell $N_{\rm ppc} = N/N_{\rm grid}$ , for a fixed grid of $128 \times 128$ (or $N_{\rm grid} = 128^2$ ).                                                                                                                     | 77  |

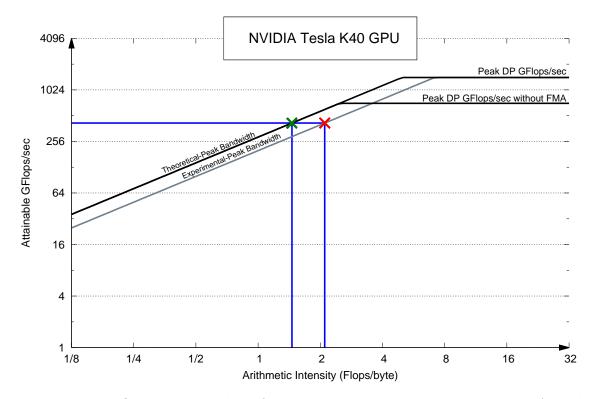

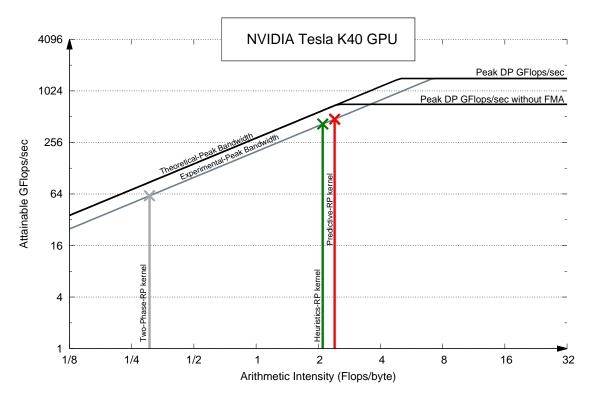

| 22 | Roofline model analysis for PREDICTIVE-RP-KERNEL on NVIDIA Tesla<br>K40 GPU                                                                                                                                                                                                                                                                     | 79  |

| 23 | Roofline model analysis of PREDICTIVE-RP-KERNEL (red line) compa-<br>red against HEURISTICS-RP-KERNEL (green line) and TWO-PHASE-RP-<br>KERNEL (grey line) on NVIDIA Tesla K40 GPU.                                                                                                                                                             | 80  |

| 24 | Efficiency of the heterogeneous implementation of compute retarded po-<br>tentials stage of the simulation on MACHINE-G which is composed of<br>multi-core CPU and four NVIDIA Tesla K40 GPUs                                                                                                                                                   | 97  |

| 25 | Efficiency of the heterogeneous implementation of compute retarded po-<br>tentials stage of the simulation on MACHINE-X which is composed of<br>multi-core CPU and two KNC Xeon Phi coprocessor                                                                                                                                                 | 98  |

| 26 | Roofline model for NVIDIA Tesla K40 GPU                                                                                                                                                                                                                                                                                                         | 116 |

# CHAPTER 1

# INTRODUCTION

Heterogeneous architectures are now becoming ubiquitous in the computing systems ranging from supercomputers to embedded systems. These architectures integrate different types of processing units (PUs) with different hardware and performance characteristics, for example, multi-core CPUs, GPUs, Intel Many Integrated Core (MIC), and FPGAs. These processing units have the potential to improve performance for many scientific applications [38]. At present, a large fraction of Top500 [72] and Green500 [31] supercomputers now use heterogeneous computing architectures. Accelerators, in particular, have played a significant role in the evolution of these architectures. In fact, systems composed of multi-core CPUs and different types of accelerators, like NVIDIA GPUs and Intel MIC (e.g. Xeon Phis), are among the most common type of heterogeneous architectures in world's top supercomputers [72]. For instance, three of top-5 supercomputers in the world are heterogeneous architectures with hardware accelerators: Tianhe-2 (Milkyway-2) employs Intel Xeon Phi manycore accelerators [57], Piz Daint [74] and ORNL Titan [29] employ NVIDIA Tesla GPUs. Table 1 gives a breakdown on the hardware specification of different PUs in these three systems along with their theoretical performance in PFlop/s. The presence of accelerators in these systems boost the overall raw performance as well as the price-to-performance and power-to-performance ratios of these systems when compared to the traditional symmetric CPU architectures. With power consumption as one of the major design constrains in todays computing systems, this trend towards heterogeneous architectures comprising of multi-core CPUs with GPUs, Xeon-Phi and other accelerators will continue.

The vastly different architectures and programming models of multi-core CPUs and accelerators, however, present several challenges in achieving good performance. Optimizing overall application performance requires taking into account the individual characteristics of the PUs. For instance, multi-core CPUs use fewer cores, which are typically out-of-order, multi-instruction issue cores which run at high-frequency and use large-sized caches to minimize the latency of a single thread. This makes

|                                        | Tianhe-2 | Piz Daint | Titan |

|----------------------------------------|----------|-----------|-------|

| CPU cores per node                     | 24       | 12        | 16    |

| Accelerators per node                  | 3        | 1         | 1     |

| Number of nodes                        | 16000    | 5320      | 18688 |

| Total system memory (TB)               | 1024     | 340       | 710   |

| Theoretical Peak Performance (PFlop/s) | 54.90    | 25.33     | 27.11 |

| Power consumption (MW)                 | 17.81    | 2.27      | 8.21  |

Table 1: Specifications of three supercomputers from world's top-5 (as of June 2017).

CPUs more suitable for latency-critical applications. In contrast, GPUs use thousands of cores, which are in-order cores that share their control unit and are designed for handling multiple tasks simultaneously where the memory access latency is typically hidden with calculations instead of big data caches. This makes GPUs more suitable for throughput-oriented applications which are typically expressed as dataparallel computations - the same program is executed on many data elements in parallel. For this reason, conventional architecture specific optimizations techniques alone may not work well in a heterogeneous system and hence, novel techniques are required to realize the potential and promise of heterogeneous computing. In other words, performance on heterogeneous architecture can only be achieved if the application workload is partitioned and mapped to the PUs such that all the PUs are best utilized and combined to deliver good aggregate performance.

Heterogeneous architectures composed of multi-core CPUs and accelerators are most effective in accelerating applications with dense and highly-structured workloads common in many problem domains ranging from graphics applications to molecular dynamics simulation and climate modeling. This is because many of these applications use regular algorithms that operate on structured data like large vectors or matrices, and access them in statically predictable ways which fit well on these architectures where they can exploit the data-parallel, single-instruction multiple data (SIMD) nature of the accelerators and the vectorization support of x86 CPUs to improve performance. In particular, these algorithms exhibit high computational demands, extensive data parallelism, access memory in a streaming fashion, and require little synchronization. These characteristics in an application make them effective in achieving coalesced memory accesses, minimizing thread divergence and synchronization, improving SIMD and vector pipeline utilizations, etc., which are some of the important factors to achieve good performance on many parallel architectures. Moreover, there exist a plethora of optimization techniques, methods, and languages models to achieve efficient parallelization of regular algorithms [44, 34, 55], and their implementation on GPUs and Intel MIC can be at least an order of magnitude faster than fine-tuned parallel CPU version [24].

However, a number of scientific and engineering applications are unstructured. Getting performance on accelerators for these applications is extremely challenging because many of these applications employ algorithms which exhibit data-dependent control-flow and memory accesses that are not readily amenable to these architectures. Algorithms with these properties are said to be *irregular*, and pose problems for high-performance parallel implementations due to the following characteristics in them -

- Irregular algorithms often demonstrate significant memory access irregularity which leads to severe performance bottlenecks on SIMD architectures [18, 14]. The data-dependent memory accesses in these programs tend to have less spatial locality compared to traditional graphics and regular general-purpose applications.

- Input values in these algorithms determine the program's runtime behavior, which therefore cannot be statically predicted. These properties in the algorithm pose problems for high-performance parallel implementations, where equal distribution of work over processor cores and locality of reference are required within each cache sharing processor core.

- Performance of applications on data-parallel, SIMD architectures relies on high SIMD lane occupancy and efficient memory coalescing for inter-thread data locality, where the former requires minimal divergent branching for threads in a SIMD group, while the latter requires regular memory access patterns and data structure layouts [23, 59]. Unfortunately, irregular algorithms tend to present both significant branch and memory divergence which leads to severe performance bottlenecks.

Irregular algorithms are the core of many scientific computing applications that arise from several domains of science and engineering. Some of the well-known applications that employ irregular algorithms are charged particles beam dynamics simulation [77, 39], n-body simulations [9], data mining [75], Boolean satisfiability [17], social networks [37], system modeling [66], compilers [2], meshing [25], and discreteevent simulation [54]. The irregular nature of the underlying algorithms makes these applications difficult to parallelize and more challenging to map to modern parallel architectures. Several efficient implementations for some of these applications using accelerators and other parallel architectures have been published in recent literature, demonstrating that individually most of these architectures are capable of accelerating at least some irregular applications relative to the CPUs [19, 51, 53]. However, developing parallel implementations for these application using collaborative computing on heterogeneous architectures to deliver the best aggregate performance from all the PUs remains a challenge.

### 1.1 AIM OF THE THESIS

Efficient parallel implementations of scientific applications on multi-core CPUs with accelerators such as GPUs and Xeon Phis is challenging. This requires - exploiting the data parallel architecture of the accelerator along with the vector pipelines of modern x86 CPU architectures (using 128-bit Streaming SIMD Extensions (SSE) or 256-bit Advanced Vector Extensions (AVX)), load balancing, and efficient memory transfer between different devices. It is relatively easy to meet these requirements for highly-structured scientific applications. In contrast, getting good performance on accelerators for unstructured applications that employ irregular algorithms is extremely challenging, thereby making their efficient parallel implementation a daunting task. Furthermore, these applications are often iterative with dependency between steps, and thus making it hard to parallelize across steps. As a result, the parallelism in these applications is often limited to a single step.

Numerical simulation of charged particles beam dynamics is one such irregular application that has gained increased interest in computational physics, especially in recent years, as these simulations are crucial in understanding and the design of: (i) high-brightness synchrotron light sources - powerful tools for cutting-edge research in physics, biology, medicine and other fields, and (ii) electron-ion particle colliders, which probe the nature of matter at unprecedented depths. This application simulates the time evolution of charged particles in particle accelerator by computing the collective effects (*e.g.* forces from self-interaction, forces from external magnetic fields, and so on) acting on individual particles of a beam for a few hundreds or thousands of time steps where the computation of collective effects at each time step is irregular. In particular, distribution of work and data in the accurate computation of collective effects at each time step of the simulation is highly unstructured and cannot be characterized a priori, as these quantities are input-dependent and evolve with the computation itself. To obtain high performance in such irregular algorithms is extremely challenging, and to this end, much effort has been devoted in the development of suitable algorithms that enable unprecedented fidelity and precision in the study of collective effects [10]. However, implementing algorithms with such highaccuracy and resolution have proven to be extremely challenging due to the data- and compute-intensive nature of the underlying numerical methods [47, 46, 42, 16, 49]. Consequently, many of the existing algorithms employ a number of approximations and simplifications to reduce the computational load [16, 49]. This improves the performance while sacrificing the accuracy.

Another well-known irregular application is n-body simulation using the Barnes-Hut algorithm which computes the gravitational forces acting on n different celestial objects for a number of time steps where each time step simulates a particular moment in the time evolution of the celestial bodies. Barnes-Hut algorithm hierarchically decomposes the space around the celestial bodies into successively smaller volumes, called grids, and computes summary information for the bodies contained inside each grid, allowing the algorithm to quickly approximate forces that the n bodies induce upon each other. The hierarchical decomposition is recorded in an octree data structure and the force calculations at each step require tree-building and repeated traversal of the unbalanced octree which is highly irregular. Other examples of such irregular scientific applications include - molecular dynamics simulation, finite elements methods, simulation of wave and sound propagation in 3D objects, etc.

Prior research on parallelizing such applications have been focused around optimizing the irregular, data-dependent memory accesses and control-flow during a single step of the application, independent of the other steps, with the assumption that these patterns are completely unpredictable [18, 9, 5]. Multiple analysis of these applications executing irregular workloads for a few hundreds or thousands of steps show that control-flow and data access patterns made by the irregular algorithm follow a loosely similar pattern between steps. In such situation, one effective approach to reduce the irregularities is to analyze the control-flow and data access patterns at each step of the application and then anticipate future data dependence and controlflow before it is needed. Given the complexity and diversity of control-flow and data access patterns in these applications, we believe anticipation strategies are best realized via intelligent application-specific prediction models that can adaptively model and track access patterns. Access pattern forecasts can then be used to make optimization decisions during application execution which improves the performance at a future step based on the observations from the earlier steps.

In this thesis, we aim to use such predictive analytics and forecasting techniques to optimize irregular scientific computing applications like beam dynamics simulation on emerging high-performance computing (HPC) architectures. In particular, we target on attaining the following two optimization goals while developing efficient parallel implementations on GPUs, Xeon Phis and heterogeneous architectures composed of multi-core CPUs with GPUs or Xeon Phis -

- Performance exploitation of individual PUs of heterogeneous systems Architecture specific optimizations to reduce the control-flow and memory access irregularities while mapping these applications on to the parallel architectures.

- Effective workload partitioning between the hybrid mix of PUs of the underlying heterogeneous architecture to obtain the best aggregate performance.

To optimize the irregularities, we explore the use supervised learning to adaptively model and track irregular access patterns in the irregular algorithm at each step of the application to anticipate the future control-flow and data access patterns. Access pattern forecasts are then used to formulate runtime decisions that optimize the irregular computations at a future step based on the observations from earlier time steps. For example, forecasts can be used to determine computations to thread mapping that maximize data reuse within a cache sharing thread group and minimize thread divergence, improve data prefetching, linearize the irregularities, etc. Most of these runtime decisions improve the performance of the application on each PU independently. In order to improve the performance in the collective computing environment of the heterogeneous architecture, the forecasts are used to create and distribute sub-problems to different PUs of the heterogeneous architecture which maximizes the resource utilization.

Throughout this thesis, we use numerical simulation of charged particles beam dynamics simulation as a motivating example to develop and illustrate all the optimization techniques. However, the techniques presented here are equally applicable to a wide range of iterative applications that have characteristics similar to that of beam dynamics simulation.

# **1.2 THESIS CONTRIBUTIONS**

The main contributions of this thesis are -

- We present supervised learning based optimization techniques to address the control-flow and memory access irregularities in the parallel implementation of iterative scientific applications on GPU and Intel MIC architectures. The new optimization technique uses predictive analytics and forecasting techniques to adaptively model and track the irregular memory access patterns at each step of the application to anticipate the future memory access patterns. Access pattern forecasts are used to make optimization and prefetch decisions during application execution which improves the performance at a future step based on observations from earlier steps.

- We present optimization techniques that use machine learning algorithms to divide the original problem into multiple smaller sub-problems and then distribute these sub-problems efficiently between different PUs of the underlying heterogeneous architecture such that it improves the memory performance and resource utilization of all the PUs and delivers a good aggregate performance.

- We demonstrate all our optimization techniques from previous bullets using numerical simulation of charged particle beam dynamics simulation which require execution of irregular workloads for multiple time steps. In particular, we present a cache-aware and memory efficient parallel algorithm that use the proposed machine learning based optimization techniques to address the irregularities in the parallel implementation of beam dynamics simulation on heterogeneous architectures composed of GPUs, Xeon Phis and multi-core CPUs.

## **1.3 THESIS ORGANIZATION**

The structure of this thesis as follows:

• Chapter 2 provides a brief overview of several topics that are essential for understanding the problems addressed in this thesis, namely: overview of different

parallel architectures, implementation challenges on GPUs and Xeon Phis, heterogeneous computing challenges, irregular algorithms and its implementation challenges, physical problem of charged particles beam dynamics simulation and related work, and numerical integration algorithms which is one of the core irregular algorithm used in beam dynamics simulations and in many other scientific computing applications.

- Chapter 3 describes the algorithm to numerically simulate charged particles beam dynamics, its limitation on sequential machines, challenges in developing efficient parallel implementation, and a brief survey of previous research in developing parallel algorithms for this problem.

- Chapter 4 presents the memory efficient parallel algorithm that use machine learning based optimization techniques to address the challenges from irregularities in the parallel implementation of charged particles beam dynamics on GPUs. Further, it presents a quantitative analysis of its performance on NVI-DIA Tesla K40 GPU.

- Chapter 5 presents the parallel algorithm and its implementation on heterogeneous architectures for the irregular computations in beam dynamics simulation. In addition to addressing the irregularities, the algorithm presented in this chapter extends the machine learning approach from Chapter 4 to optimize the resource utilization of all the PUs of underlying heterogeneous architecture.

- Chapter 6 provides a concluding discussion on the optimization techniques and algorithms presented in this dissertation.

# CHAPTER 2

# BACKGROUND

This chapter provides a brief overview of several topics that are essential for understanding the problems addressed in this thesis. In particular, Section 2.1 provides a overview of the parallel architectures used in this study, and Section 2.2 presents the parallel implementation challenges on these architectures. Next, in Section 2.3, we discuss irregular algorithms and its parallel implementation challenges. Section 2.4 presents the physical problem of charged particle beam dynamics simulation and provides a overview of the related work in its numerical simulation methods. Finally, in Section 2.5, we a take brief look at numerical integration algorithms, which is the core irregular algorithm used in beam dynamics simulations and in many other scientific computing applications.

#### 2.1 OVERVIEW OF PARALLEL ARCHITECTURES

In this section, we take a brief look at the typical architecture of two widely used accelerator - NVIDIA's General Purpose GPU and Intel's Xeon Phi coprocessor architecture.

#### 2.1.1 GENERAL PURPOSE GPUS

At the hardware level, NVIDIA's GPU architecture is an scalable array of multithreaded Streaming Multiprocessors (SMs). Each SM features several Streaming Processor (SP) cores and double-precision logic units (DP unit), where each SP core is a fully pipelined integer arithmetic logic unit (ALU) and single-precision floating point unit (FPU). In addition to SP cores and DP units, each SM features (i) load/store units, (ii) special function units (SFU) for transcendental instructions such as sin, cosine, reciprocal, and square root, (iii) schedulers and instruction dispatch units, (iv) instruction cache, (v) register file, (vi) on-chip shared-memory and L1cache, (vii) read-only cache, and (viii) texture units. The size and number of each unit vary form one generation of GPUs to another. Each core also supports Fused Multiply-Add (FMA) instructions for both single precision and double precision

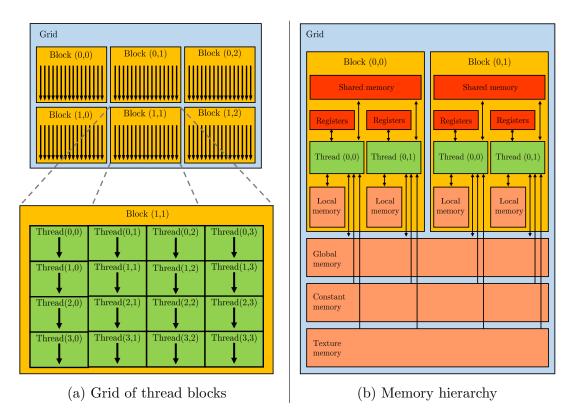

Figure 1: CUDA programming model for general purpose computing on NVIDIA GPUs.

floating point operations. GPUs also supports larger off-chip global, constant and texture memory that are shared among all SMs. The global/texture memory are often cached and use two-level caching system, where L1-cache is located within each SM, while the L2-cache is located off-chip and is shared among all the SMs.

Compute Unified Device Architecture (CUDA) is the general purpose parallel computing platform and programming model used for designing parallel computations on NVIDIA GPUs. CUDA programming allows the programmer to define functions, called *kernels*, that when called, are executed on the GPUs by many different parallel CUDA threads. The programmer or compiler organizes these CUDA threads into one-dimensional, two-dimensional, or three-dimensional block of threads, called a *thread block* where each thread within a thread block executes an instance of the kernel. The maximum number of threads in a thread block vary from one generation of GPUs to another, for example, a thread block may contain up to 1024 CUDA threads for programming Kepler GPUs. The thread blocks are further organized into a one-dimensional, two-dimensional, or three-dimensional grid of thread blocks as illustrated by Figure 1a. The number of thread blocks in a grid is usually dictated by the size of the data being processed or the number of processors in the system, which it can greatly exceed. Thread blocks are executed independently which allows it to be scheduled in any order across any number of cores as illustrated in [60], and this enables the programmers to write code that scales with the number of cores.

CUDA threads have access to data from six different memory space during their course of execution: register memory, constant memory, shared memory, texture memory, local memory, and global memory. Figure 1b illustrates how CUDA threads can access data from the different memory spaces. Each thread has private perthread registers that are often used to hold frequently accessed data, and these are not programmer controlled. Each thread has private local memory that is used for register spills, function calls, and automatic array variables. Each thread block has a per-block shared memory which is visible to all threads of the block and has the same lifetime as the block. Shared memory is often used for inter-thread communication and data sharing in parallel algorithms. The global, constant and texture memory spaces are accessible from all threads and these three memory spaces are persistent across kernel launches by the same application.

When a CUDA kernel is invoked by the host CPU, the blocks of threads that constitute the kernel grid are enumerated and scheduled on the available SMs in any order, concurrently or sequentially, so that the compiled CUDA kernel can execute on any number of SMs. Multiple thread blocks can execute concurrently on a single SM and as the thread blocks terminate, new blocks are launched on the vacated SM. Each SM employs SIMT architecture to manage and execute hundreds of threads concurrently [60]. The SM creates, manages, schedules and executes threads in groups of 32 parallel threads called *warps*. Individual threads composing a warp start their execution at the same program address, but they have their own program counter and register state and are therefore free to branch and execute independently. At any given time, all threads within a warp execute the same instruction in a lockstep. As a result, full warp efficiency is realized when all 32 threads of a warp agree on their execution path, or more formally referred to as control-flow (*warp execution*) efficiency is the average percentage of active threads in each executed warp). However, the presence of data dependent conditional branch often cause threads within the same warp to follow different control-flow paths (also known as *branch* or *control*flow divergence) and this causes the warp to serially execute each branch path taken,

disabling threads that are not on that path, and when all paths complete, the threads converge back to the same execution path. It is important to note that such branch divergence occurs only within a warp; different warps execute independently regardless of whether they are executing common or disjoint code paths.

## 2.1.2 INTEL XEON PHI COPROCESSOR

The Intel Xeon Phi coprocessor is based on the Many Integrated Core (MIC) architecture. This architecture uses previous concepts developed by Intel for the Larrabee many core architecture, as well as the Teraflops Research Chip and the Intel Single-chip Cloud computer. We will discuss one of the Xeon Phi variants, the Knight Corner (KNC). This is the model used in this thesis. The KNC architecture is primarily composed of processing cores (more than 50), caches, memory controllers, PCIe client logic, and a very high bandwidth, bidirectional ring interconnect . Each core is equipped with (i) Vector processing unit (VPU), (ii) scalar processing unit, (iii) Extended Math Unit (EMU) for transcendental instructions such as sin, cosine, reciprocal, and square root, (iv) scalar and vector registers, (v) a L1 cache (data and instruction), and (vi) a unified L2 cache. Caches within a core are fully coherent and implement the x86 memory order model. The L1 and L2 caches provide an aggregate bandwidth that is approximately 15 and 7 times, respectively, faster compared to the aggregate memory bandwidth.

The Xeon Phi is highly optimized for vector processing and it implements SIMD execution model in all VPUs. Each VPU features a 512-bit SIMD instructions, as a replacement for the more commonly found Intel SSE, MMX and AVX instructions. With 512-bit SIMD instructions, VPU provides data parallelism at a very fine grain, working on 512 bits of 16 single-precision floats or 16 integers or 8 double-precision floats at a time. The VPU also supports Fused Multiply-Add (FMA) instructions and hence can execute 32 single-precision or 16 double-precision floating point operations per cycle. A more comprehensive overview of Intel Xeon Phi architecture can be found in [40].

## 2.2 PARALLEL COMPUTING CHALLENGES

In this section, we first illustrate the impact of data-parallel, SIMD nature of NVI-DIA's GPU and Intel's Xeon Phi architecture on application performance. Next, in Section 2.2.2, we take a brief look at the parallel computing challenges in heterogeneous architectures.

## 2.2.1 ARCHITECTURAL INFLUENCES ON PERFORMANCE

Effectively exploiting data parallelism using SIMD pipelines is one of the most important aspects in achieving high performance on PUs such as GPU, Intel MIC and modern x86 architectures. For example, Intel MIC has 512-bit VPU units per core to expose SIMD parallelism, GPUs by design employ SIMT architecture within each streaming multiprocessors that execute threads in group of 32 (equivalent to 1024-bit SIMD for single precision floating point), x86 architectures uses 128-bit Streaming SIMD Extensions or 256-bit Advanced Vector Extensions (AVX) to support SIMD parallelism. In these PUs, data parallelism using SIMD pipelines is a power efficient way of boosting the peak performance, and such parallelism is exploited at different granularities: usually, several work items (also called threads) are organized into a work group. These are broken down into several SIMD groups (*e.g.* warps in GPUs) that are executed by a SIMD pipeline. Each PU may have multiple SIMD pipelines to execute SIMD groups in parallel, where effective hardware utilization of the PU relies largely on exploiting the SIMD pipelines.

Programming applications to maximize the utilizations of SIMD pipelines and to deliver high-performance of the application code on the PUs remains a challenge. In particular, the nature of SIMD execution requires that all threads in a SIMD thread group (*e.g.*, a warp in GPUs) to execute the same instruction in lockstep. While this allows the processor design in PUs to be relatively simple, application performance may suffer significantly whenever threads in the same SIMD group behave differently due to control or memory latency divergence [60]. Control divergence results in serialized execution of divergent control paths, leaving execution resources idle and throttling parallelism. Similarly, memory latency divergence causes a SIMD group to stall until the longest memory request for a vector load completes before executing any dependent instructions. In this section, we first briefly overview the effects of control-flow and memory latency divergence on application performance. Then, we look at the SIMD architectural features that affect control-flow and memory latency divergence, and those that try to mitigate them.

#### Memory Latency Divergence

When a SIMD thread group of size w issues a load instruction (e.g., w = 32 threads for GPUs, w = 8 double precision loads in Intel Xeon-Phi's 512-bit VPU), the SIMD group will block once an instruction dependent upon the load data becomes the next to issue. As a result, this group of threads is unable to make progress until all the data for the constituent load instructions are available. In particular, for SIMT architectures, a single delinquent load can block forward progress of the SIMD group. This introduces the problem of *memory latency divergence*, where a SIMD group can be stalled until the last memory request from a vector load instruction is returned, potentially long after other memory requests from the vector load have completed. In many workloads, this load latency cannot be hidden by executing other SIMD groups. Several studies have highlighted how memory latency divergence can be a significant performance bottleneck in GPUs and Xeon Phis [52, 68, 22]. This problem of memory latency divergence is not unique to GPUs (or Xeon Phis) and can also manifest itself in other SIMD/vector architectures that support "gather" load operations.

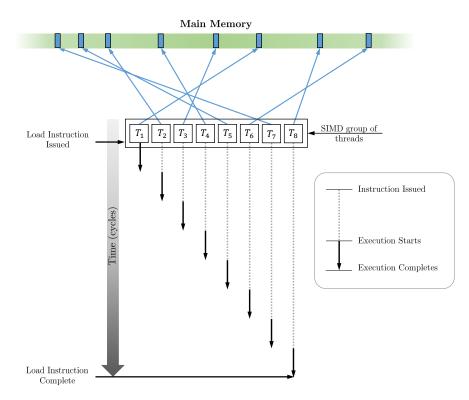

Figure 2: Memory latency divergence when the addresses accessed by SIMD group are scattered in the memory.

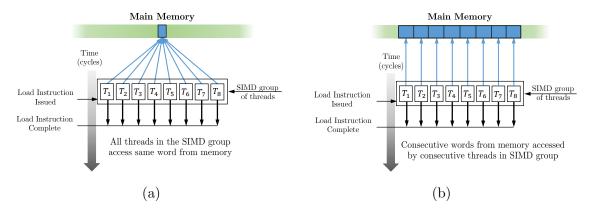

Figure 3: Memory latency divergence when: (a) the addresses accessed by SIMD group are uniform (all equal), (b) the addresses accessed by SIMD group are consecutive.

Memory latency divergence arises from several factors. First, the target data for a set of memory requests from a SIMD group may reside in different levels of memory hierarchy, and the memory hierarchy service different requests at different times due to hits and misses at various levels. Second, the time to complete each memory request depends on several factors, including which DRAM bank the target memory resides in, contention in the interconnect network, and availability of resources in the memory controller. Third, current memory systems are primarily optimized to support traditional, structured workloads with low degree of memory access irregularity. In case of workloads with high degree of irregular or non-coalesced memory accesses, the memory system serializes the execution of memory references from a SIMD thread group, which stalls the SIMD group until the last memory reference is returned. For example, consider a SIMD group of size w that executes a load instruction. In the worst case, all w addresses are scattered in the address space, which results in w data loads from the memory. This serializes the execution of load instructions, which stalls the SIMD group until the last load instruction is returned. Figure 2 illustrates the memory divergence for load instruction within a SIMD group of size w = 8 where all the w addresses are scattered in the address space. On the other hand, if the addresses are uniform (*i.e.*, all equal) or consecutive, only a single load has to be issued (see Figure 3a and Figure 3b).

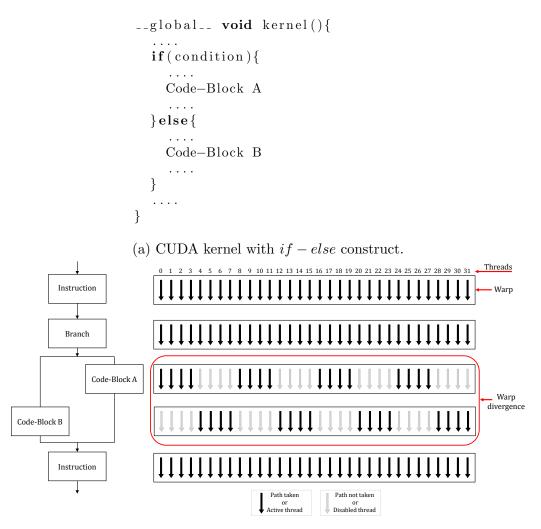

(b) Control-flow for an warp executing the if - else branch condition when half of warps thread evaluate the branch condition to true.

Figure 4: Control-flow divergence in GPUs.

#### **Control-flow Divergence**

Consider a SIMD group of threads executing the if - else construct shown in Figure 4a. The threads within the SIMD group works with full efficiency when all the threads execute the if part or all execute the else part. On the other hand, when threads within a SIMD group take different control-flow paths then the execution of the group takes multiple passes through the divergent paths. The first pass executes the threads that follow *if* part (Code-Block A) and the second pass executes those that follow the *else* part (Code-Block B). In other words, each thread from the SIMD group takes both the branch paths sequentially, even though it just executes one of them. This results in poor to suboptimal hardware utilization which often degrades the application performance. For example, Figure 4b illustrates the control-flow in a GPU warp when half of the its thread evaluate the branch condition to true. In the first pass, only half the threads takes the path for *if* condition (denoted by black arrow) and the other half remains disabled (denoted by grey arrow). Similarly, in the second pass, half the threads take the path for *else* condition (denoted by black arrow) and the other half remains disabled (denoted by grey arrow). This reduces the SMID groups or warp execution efficiency to 50%. Such reduction in execution efficiency often leads to poor utilization of the compute resources, which severely degrades the application performance on SIMD architectures [32]. As a result, it is of vital importance to mitigate the control-flow divergence and subsequently increase the execution efficiency of all SIMD thread groups for obtaining good application performance on SIMD architectures.

#### Mitigating Divergence

The architectural features in GPUs and Intel MIC that affect memory latency divergence (besides the SIMD execution model illustrated in the previous section) and those that try to mitigate divergence are -

• Memory Coalescing - A common architectural technique that reduces memory bandwidth demand in SIMD architectures is *memory coalescing*. In this technique, the individual requests from a SIMD group are combined, based on their target address, to form as few cache-line sized (*e.g.* 128B in GPUs) requests as possible. Coalescing is primarily designed to reduce bandwidth requirements by eliminating redundant accesses to the same cache line. However, it also reduces the opportunity for memory latency divergence by minimizing the number of distinct memory requests per SIMD group. Coalescing is not effective, however, if the data accessed by the threads in a SIMD group are not spatially colocated, as is commonly the case in applications that exhibit memory access patterns that are not readily amenable to the SIMD architecture. Previous studies have shown that coalescing is extremely effective for traditional structured workloads with uniform memory access patterns, but its effectiveness falls short for workloads with irregular memory accesses [22].

- Multithreading SIMD architectures leverage thread-level parallelism to hide memory access latency. The effect of long divergence-induced stalls can be mitigated if there are enough ready SIMD thread groups in the system to hide the latency of the slowest request. Previous studies [22, 27, 41] have shown, however, that in spite of having a large number of thread contexts to choose from, a SIMD processor core will frequently sit idle as all the SIMD groups are stalled on pending memory accesses. For instance, recent NVIDIA GPUs support at most 48 to 64 warps within a SP, while the main memory latency have been measured to exceed 400 cycles. It is, therefore, important to note that thread-level parallelism cannot always completely hide main memory latency [8].

- Caches Caches have low latency when compared to the global memory. As a result, memory requests from a SIMD thread group that hit in a cache are returned sooner even with access irregularities or latency divergence when compared to servicing the same requests from global memory. This improves the average memory latency. However, for memory latency divergence to be meaningfully addressed with caches, a substantial fraction of SIMD groups must be able to serve all of their memory requests with cache hits. Otherwise, the cache misses for a SIMD group will be serviced from the global memory, and faces the latency divergence issues described above.

#### 2.2.2 HETEROGENEOUS COMPUTING CHALLENGES

The presence of different type of PUs with different processing capabilities introduces many challenges to the application design. In particular, the level of heterogeneity in these systems introduces non-uniformity in system development, programming practices, and overall system capability. These non-uniformities presents a significant challenge to the programming community in developing applications that can fully exploit the capabilities of the multiple PUs and in approaching their combined theoretical performance. Several studies have been devoted to developing programming models that can exploit these heterogeneous architectures in a unified way, *e.g.*, OpenCL [43], OpenACC [63] and OpenMP [64]. These models simplify the programming effort required in exploiting these architectures, however, achieving good performance on heterogeneous architectures still largely depends on (i) performance exploitation of each single PU, and (ii) performance aggregation from all the PUs. This requires partitioning the application workload and mapping them efficiently between the PUs such that all the PUs are best utilized and combined to deliver best aggregate performance.

Performance exploitation of the individual PU is achieved using architecturespecific optimization strategies, [60, 59, 80]. Researchers have developed several optimizations techniques and tools on top of the programming models to extract more performance on each type of architecture [70, 69, 79]. On the other hand, vastly different architectures and programming models of different PUs in a heterogeneous system presents several challenges in optimizing applications to deliver good aggregate performance from all the PUs. Several factors relating to both the PU and the application itself, and spanning from microarchitecture-level to system-level need to be taken into account for fully leveraging their potential in heterogeneous computing systems [55]. In particular, designing effective workload partitioning between a hybrid mix of PUs is challenging because -

- Heterogeneity of the platform requires partitioning algorithms to fully consider the PUs differences in processing capability, hardware architecture, and memory model. For example, GPUs and Xeon Phis usually offer higher processing throughput than CPUs (on average 2.5X in [45]), but have separate memory spaces and low data communication bandwidth to the CPU memory (GPUs are connected with the host CPU through a PCI Express bus). Due to the interaction between the PUs in a heterogeneous environment, optimizing performance and energy efficiency requires taking into account the individual characteristics of the PUs. Some of the dominant PU-specific factors that needs to be considered are

- Current load on PUs and achieving load balancing between them,

- Memory bandwidth and CPU to accelerator data transfer overhead; avoiding and/or amortizing overhead of launching kernels on accelerators,

- Overlapping data transfer with computation or CPU computation with computation on accelerators,

- Taking into account the limitations of PUs, e.g. CPU to GPU/Xeon-Phi memory bandwidth, size of GPU/Xeon-Phi and CPU memory, number

of threads in GPU/Xeon-Phi and CPU cores, reduced performance of GPU/Xeon-Phi for double-precision computations etc. [78]. Additionally, aggressively using CPU for computation affects its ability to act as a host, which harms the performance [30, 73].

- The diversity of platforms, applications, and datasets increases the partitioning complexity [71]. The diversity lies in the fact that heterogeneous platforms exist in different configurations and forms (*e.g.*, multi-core CPUs with accelerators, embedded systems, MPSoC, etc.), and that data parallel applications (with different datasets) present various kinds of performance behavior even on the same platform.

- Application or problem specific factors that influence workload partitioning -

- Subdividing the workload and selecting suitable work sizes to be allocated to different PUs

- Accounting for data dependencies, e.g. if a task has data dependencies on previous task, where was the previous task executed?

- From programmer's viewpoint, it is challenging to obtain, with limited time and effort, the optimal partitioning that leads to the best performance for a given heterogeneous platform, application, and dataset.

A more comprehensive survey of heterogeneous computing techniques and the challenges involved in heterogeneous computing can be found in [55].

#### 2.3 IRREGULAR ALGORITHMS

The terms *regular* and *irregular* stem from the compiler literature. *Regular al*gorithms operate on structured data like large vectors or matrices, and access them in statically predictable ways - *e.g.* dense linear algebra computations, matrix vector multiplications, etc. These algorithms often have high computational demands, exhibit extensive data parallelism, access memory in a streaming fashion, and require little synchronization [50]. This sort of regularity in the algorithm exhibit data independent control-flow and memory references which can be exploited to minimize memory divergence by coalescing memory accesses, and minimize thread divergence and synchronization by maintaining workload balance. In fact, there exists a plethora of techniques, methods and languages to achieve efficient parallelization of regular algorithms [44, 34], and their implementation on GPUs and Xeon Phis can be at-least an order of magnitude faster than fine tuned parallel CPU version [24].

On the other hand, *irregular algorithms* are characterized by control-flow and memory references that are data dependent. In particular, distribution of work and data in these algorithms cannot be characterized a priori because these quantities are input-dependent and evolve with the computation itself. Irregular algorithms are the core of many high-performance applications, such as n-body simulations [9], data mining [75], Boolean satisfiability [17], social networks [37], system modeling [66], compilers [2], meshing [25], and discrete-event simulation [54]. Efficient parallel implementation of irregular algorithms are challenging because:

- Irregular algorithms often demonstrate significant Memory Access Irregularity (MAI) [18] which leads to severe performance bottlenecks on SIMD architectures [14]. The data dependent memory accesses in these programs tend to have less spatial locality compared to traditional graphics and regular general-purpose applications.

- Input values in these algorithms determine the program's runtime behavior, which therefore cannot be statically predicted. These properties in the algorithm pose problems for high-performance parallel implementations, where equal distribution of work over processors cores and locality of reference are required within each cache sharing processor cores.

- Performance of applications on SIMD architectures relies on high SIMD lane occupancy and efficient memory coalescing for inter-thread data locality, where the former requires minimal divergent branching for threads in a SIMD group, while the latter requires regular memory access patterns and data structure layouts [23, 59]. Unfortunately, irregular algorithms tend to present both significant branch and memory divergence which leads to severe performance bott-lenecks.

## 2.4 BEAM DYNAMICS

In this section, we present an overview of charged particle beam dynamics and the general equations that govern the dynamics of charged particles in a *synchrotron* (a type of cyclic particle accelerator).

#### 2.4.1 PHYSICAL PROBLEM

The dynamics of charged particle beams is captured by the Lorentz force [47]:

$$\frac{d}{dt}\left(\gamma m_e \boldsymbol{v}\right) = e\left(\boldsymbol{E} + \boldsymbol{\beta} \times \boldsymbol{B}\right),\tag{1}$$

with the relativistic  $\boldsymbol{\beta}$  and  $\gamma$ , velocity  $\boldsymbol{v}$ , electric field  $\boldsymbol{E}$  and magnetic field  $\boldsymbol{B}$  specified as, respectively,

$$\boldsymbol{\beta} \equiv \boldsymbol{v}/c, \ \gamma = \frac{1}{\sqrt{1+\boldsymbol{\beta}^2}}, \ \boldsymbol{v}(\boldsymbol{p}) = \frac{\boldsymbol{p}/m_e}{\sqrt{1+\boldsymbol{p}\cdot\boldsymbol{p}/(m_ec)^2}},$$

(2a)

$$\boldsymbol{E} = -\nabla \phi - \frac{1}{c} \partial_t \boldsymbol{A}, \quad \boldsymbol{B} = \nabla \times \boldsymbol{A}.$$

<sup>(2b)</sup>

$\phi$  and  $\boldsymbol{A}$  the retarded scalar and retarded vector potentials, respectively. They are obtained by integrating the charge distribution  $\rho$  and the charge current density  $\boldsymbol{J}$  over the retarded time  $t' = t - |\boldsymbol{r} - \boldsymbol{r}'|/c$ :

$$\begin{bmatrix} \phi(\boldsymbol{r},t) \\ \boldsymbol{A}(\boldsymbol{r},t) \end{bmatrix} = \int_0^\infty \begin{bmatrix} \rho(\boldsymbol{r'},t-\frac{\boldsymbol{r}-\boldsymbol{r'}}{c}) \\ \boldsymbol{J}(\boldsymbol{r'},t-\frac{\boldsymbol{r}-\boldsymbol{r'}}{c}) \end{bmatrix} \frac{d^2\boldsymbol{r'}}{|\boldsymbol{r}-\boldsymbol{r'}|},$$

(3a)

$$\begin{bmatrix} \rho(\boldsymbol{r},t) \\ \boldsymbol{J}(\boldsymbol{r},t) \end{bmatrix} = \int_0^\infty \begin{bmatrix} 1 \\ \boldsymbol{v}(\boldsymbol{p}) \end{bmatrix} f(\boldsymbol{r},\boldsymbol{p},t) d\boldsymbol{p}.$$

(3b)