University of North Dakota UND Scholarly Commons

Theses and Dissertations

Theses, Dissertations, and Senior Projects

January 2016

# Experimental Super High Frequency Rectifier And DC To DC Converter For Application In Space Solar Power

Robert Bernaciak

Follow this and additional works at: https://commons.und.edu/theses

**Recommended** Citation

Bernaciak, Robert, "Experimental Super High Frequency Rectifier And DC To DC Converter For Application In Space Solar Power" (2016). *Theses and Dissertations*. 1993. https://commons.und.edu/theses/1993

This Thesis is brought to you for free and open access by the Theses, Dissertations, and Senior Projects at UND Scholarly Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of UND Scholarly Commons. For more information, please contact zeinebyousif@library.und.edu.

#### EXPERIMENTAL SUPER HIGH FREQUENCY RECTIFIER AND DC TO DC CONVERTER FOR APPLICATION IN SPACE SOLAR POWER

by

Robert C. Bernaciak

Bachelor of Science, University of North Dakota, 2013

A Thesis

Submitted to the Graduate Faculty

of the

University of North Dakota

in partial fulfillment of the requirements

for the degree of

Master of Science

Grand Forks, North Dakota December 2016

Copyright 2016 Robert Bernaciak

This thesis, submitted by Robert C. Bernaciak in partial fulfillment of the requirements for the Degree of Master of Science from the University of North Dakota, has been read by the Faculty Advisory Committee under whom the work has been done and is hereby approved.

Dr. Hossien Salehfar

S Noghanian Dr. Sima Noghanian

Frakash Ranganathe

Dr. Prakash Ranganathan

This thesis is being submitted by the appointed advisory committee as having met all of the requirements of the School of Graduate Studies at the University of North Dakota and is hereby approved.

Dr. Grant McGimpsey Dean of the School of Graduate Studies

December 8, 2016

Date

### PERMISSIONS

Title: Experimental Super High Frequency Rectifier and DC To DC Converter For Application In Space Solar Power

Department: Electrical Engineering

Degree: Masters of Science

In presenting this thesis in partial fulfillment of the requirements for a graduate degree from the University of North Dakota, I agree that the library of this University shall make it freely available for inspection. I further agree that permission for extensive duplication for scholarly purposes may be granted by the professor who supervised my thesis work or, in her (or his) absence, by the Chairperson of the department or the dean of the School of Graduate Studies. It is understood that any copying or publication or other use of this thesis (or dissertation) or part thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of North Dakota in any scholarly use which may be made of any material in my thesis.

> Robert C. Bernaciak 08 December 2016

### **TABLE OF CONTENTS**

| PERMISSIONS                                  | iv   |

|----------------------------------------------|------|

| TABLE OF FIGURES                             | viii |

| LIST OF TABLES                               | xi   |

| ACKNOWLEDGMENTS                              | xii  |

| ABSTRACT                                     | xiii |

| CHAPTERS                                     | 1    |

| I. INTRODUCTION                              | 1    |

| a. State-of-the-Art:                         | 3    |

| b. Research Problem:                         | 7    |

| c. Methodology:                              | 9    |

| d. System Application and Design Constraints |      |

| II. SYSTEM DESIGN                            | 14   |

| a. Antenna Design                            | 14   |

| b. Rectifier Design                          | 15   |

| i. Diode Selection                           | 15   |

| ii. Diode Matching to Coplanar Strips        | 24   |

| iii. Harmonic Rejection Filter               | 25   |

| iv. DC Bypass Capacitor                      |      |

| v. Half-wave Versus Full-wave Rectifying     |      |

| c. Rectenna Array Design                     |      |

| d. DC-to-DC Converter                        |      |

| i. Converter Design analysis                 |      |

| e. Substrate and PCB Materials               |      |

| i. Rectifier Substrate Material              |      |

| ii. Buck/Boost Converter PCB Material        |      |

| III. PROTOTYPE DESIGN                        |      |

| a. Rectenna Design                           |      |

| i. Diode Analysis                            |      |

| b. Rectenna Array Design              | 47 |

|---------------------------------------|----|

| c. DC-to-DC Converter                 |    |

| IV. PROTOTYPE MANUFACTURING & TESTING | 53 |

| a. Rectifier Manufacturing            | 53 |

| b. Rectifier Filter Manufacturing     | 55 |

| c. DC-to DC-Converter Manufacturing   | 55 |

| d. Rectifier Testing                  | 59 |

| e. Rectifier Filter Testing           | 60 |

| f. DC-to-DC Converter Testing         | 62 |

| g. Testing Setup Notes                | 63 |

| VI. RESULTS                           | 65 |

| a. Rectifier Filter                   | 73 |

| b. Rectifier Results                  | 78 |

| i. Simulation results                 | 78 |

| ii. Prototype Measurement Results     | 81 |

| c. DC-to-DC Converter                 |    |

| VII. CONCLUSIONS                      | 91 |

| a. Review of Methodology              | 91 |

| b. Simulation Results                 | 93 |

| c. Prototype Results                  | 94 |

| i. Rectifier                          | 95 |

| ii. Rectifier Filter                  |    |

| iii. DC-to-DC Converter               | 96 |

| d. Future Research Areas              |    |

| i. Rectifier Design                   |    |

| ii. Rectenna Array Design             |    |

| iii. DC-to-DC Converter               |    |

| iv. Space-Qualified Materials         |    |

| APPENDICIES                           |    |

| Appendix A                            |    |

| Appendix B                            |    |

| Appendix C                            |    |

| Appendix D                            |    |

| Appendix E                            |    |

| Appendix F                            |    |

| Appendix G | 130 |

|------------|-----|

| REFERENCES | 132 |

### **TABLE OF FIGURES**

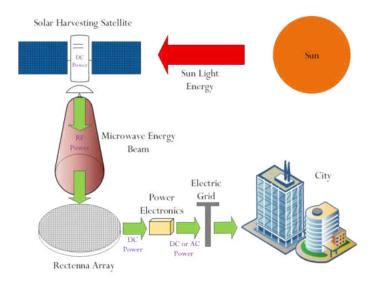

| Figure 1: Image of a wireless power transmitting and receiving satellite [1]                               | 1  |

|------------------------------------------------------------------------------------------------------------|----|

| Figure 2: Grid tied overview of space solar power [1]                                                      | 2  |

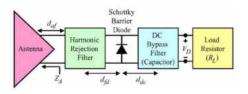

| Figure 3: Block diagram of a rectenna [2]                                                                  |    |

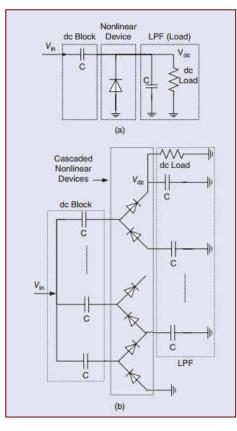

| Figure 4: RF-DC converters: (a) single diode detector, (b) a charge pump [5]                               | 6  |

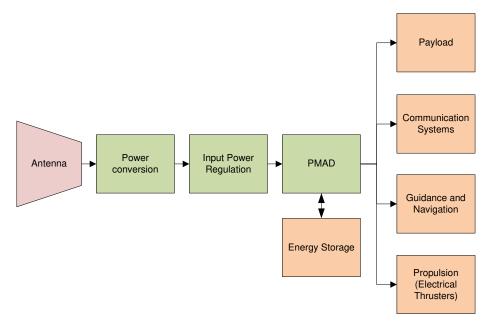

| Figure 5: MWPT receiving satellite power flowchart                                                         | 9  |

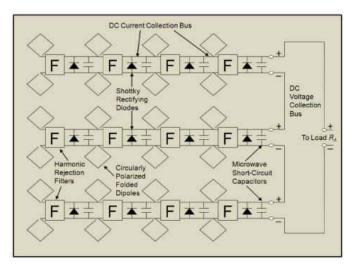

| Figure 6: An Array of 12 individual rectennas [2].                                                         | 11 |

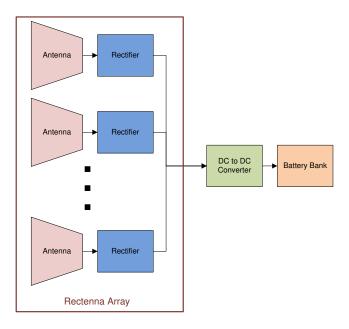

| Figure 7: Block diagram of the MWPT system                                                                 | 14 |

| Figure 8: Internal material and symbolic view of a Schottky diode                                          | 16 |

| Figure 9: The rectification cycle of the shunt diode is represented by the input fundamental and overla    | id |

| on the diode Current-Voltage curve. This model assumes that there are no losses due to the harmonics       | S  |

| and $\theta = \omega t \cdot \phi$ [4]                                                                     | 19 |

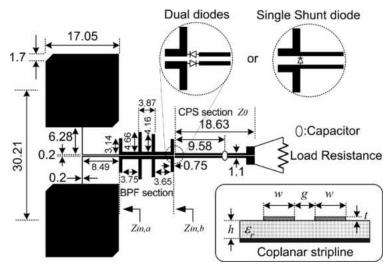

| Figure 10: Layout of the previous dual-diode rectenna design, single shunt diode rectenna, and CPS. Al     | I  |

| dimensions are in millimeters [10]                                                                         | 22 |

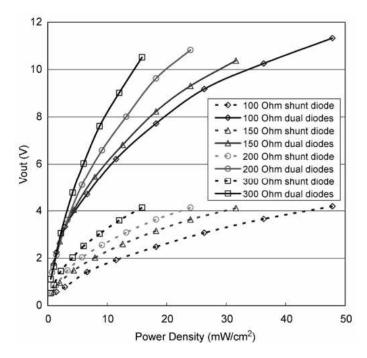

| Figure 11: Measured DC output voltages of the dual-diode and single shunt diode rectennas [10]             | 23 |

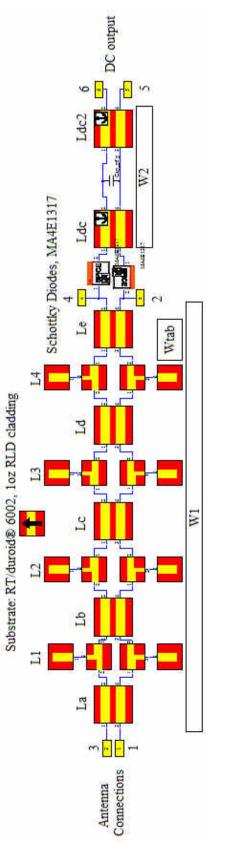

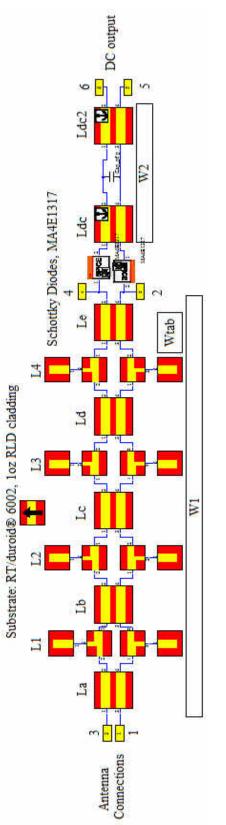

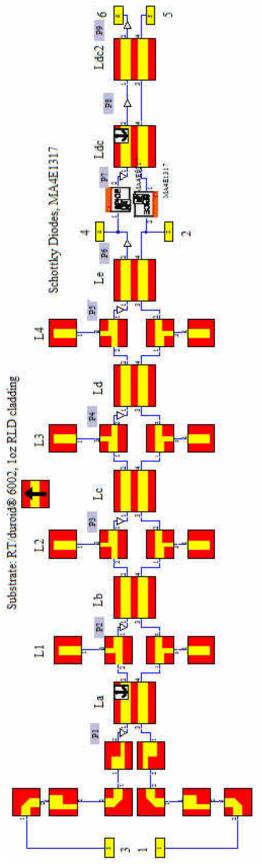

| Figure 12: Layout of Harmonic Rejection Filter (HRF) with Dual Diode design. The red and yellow blocks     | ;  |

| are representations of CPS. The spice blocks to the right of the Ports "2" and "4" are links to spice file |    |

| representations of the diode MA4E1317 [12].                                                                | 28 |

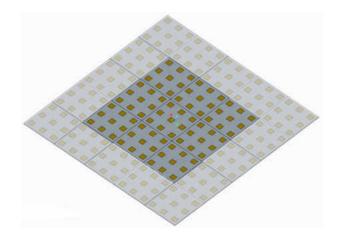

| Figure 13: Image of the receiving satellite with a 4x4 panel area or a 3x3 panel area [1] [12]             | 31 |

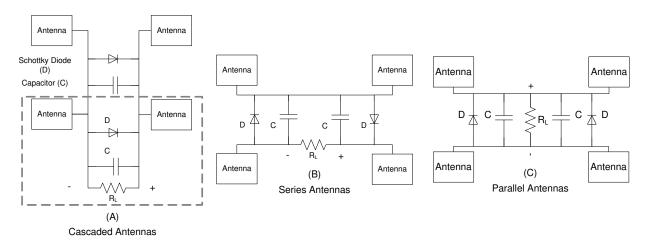

| Figure 14: (A) Cascaded Antennas, (B) Series Antennas, and (B) Parallel antennas                           | 32 |

| Figure 15: Block diagram showing the position of the DC-to-DC converter                                    |    |

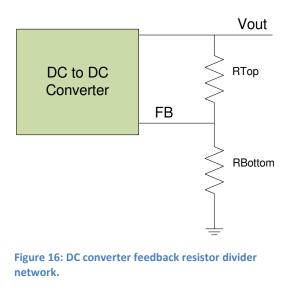

| Figure 16: DC converter feedback resistor divider network                                                  | 37 |

| Figure 17: Layout of Harmonic Rejection Filter (HRF) with Dual Diode design. The red and yellow blocks     | ;  |

| are representations of CPS. The spice blocks to the right of the Ports "2" and "4" are links to spice file |    |

| representations of the diode MA4E1317 [12].                                                                |    |

| Figure 18: BAT17 single diode calculated impedance.                                                        | 45 |

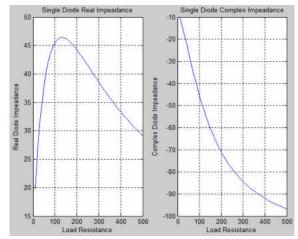

| Figure 19: MA4E1317 single diode calculated impedance.                                                     |    |

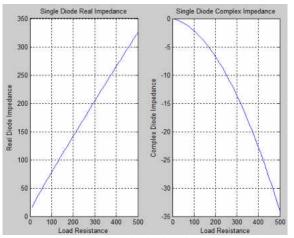

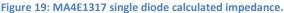

| Figure 20: BAT17 calculated single and dual diode efficiency                                               |    |

| Figure 21: MA4E1317 calculated single and dual diode efficiency                                            |    |

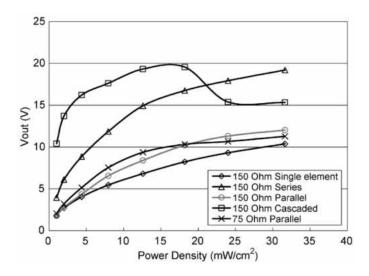

| Figure 22: Measured DC output voltage of the rectenna array [10].                                          |    |

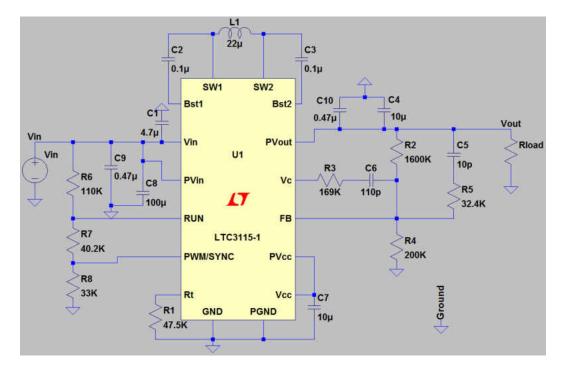

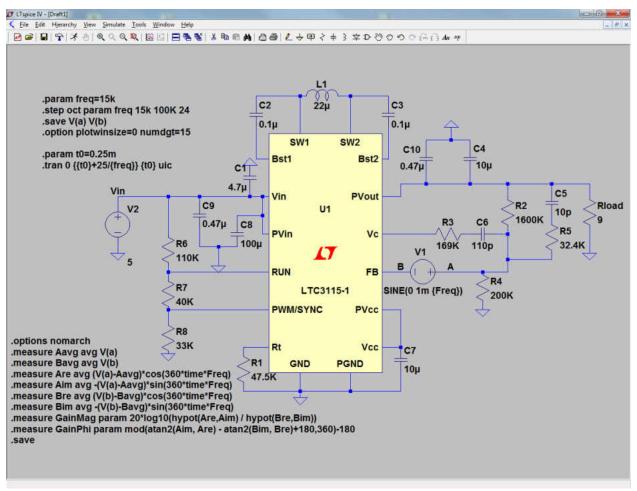

| Figure 23: LTC3115-1 DC to DC buck/boost converter laid out in LTSPICE [36]                                |    |

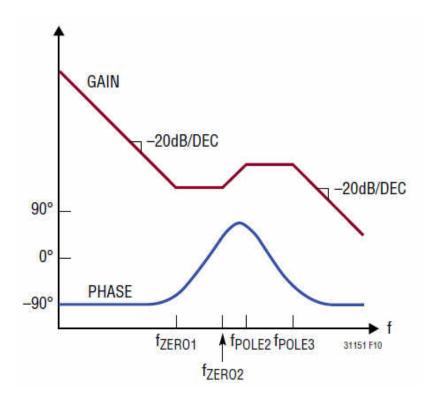

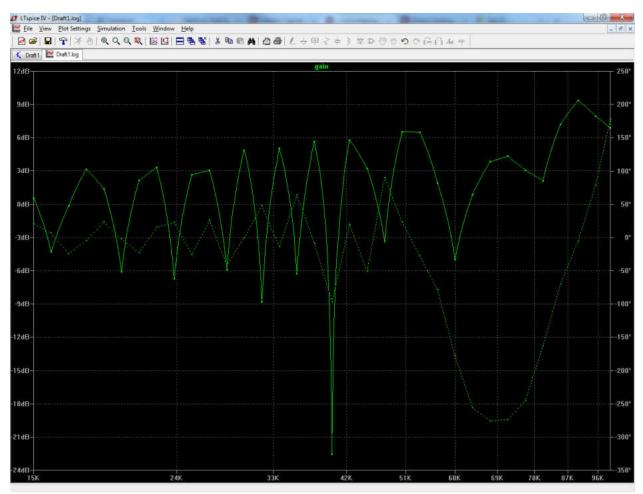

| Figure 24: Bode plot example from the LT31151 DC-to-DC converter data sheet [25].                          |    |

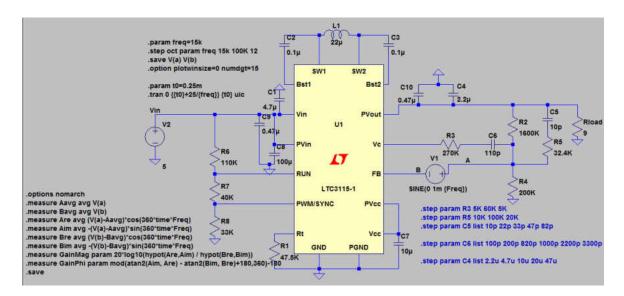

| Figure 25: DC-to-DC converter and test set up used to determine the Bode plot using LTSPICE [36]           | 52 |

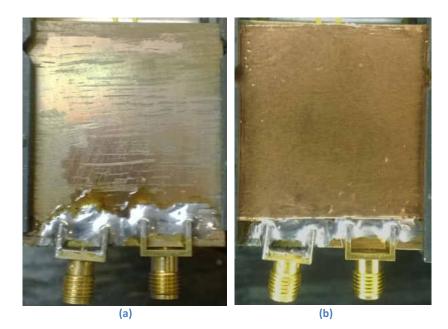

| Figure 26: a) Image of the deteriorated ground plane on the rectifier b) Image of the ground plane with    | ٦  |

| the attached copper tape                                                                                   | 54 |

| Figure 27: Image of the rectifier prototype. The arrow indicates the diodes that were placed on the        |    |

| board                                                                                                      | 55 |

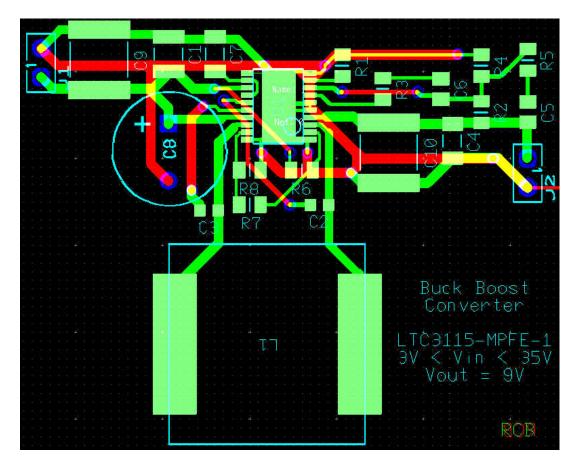

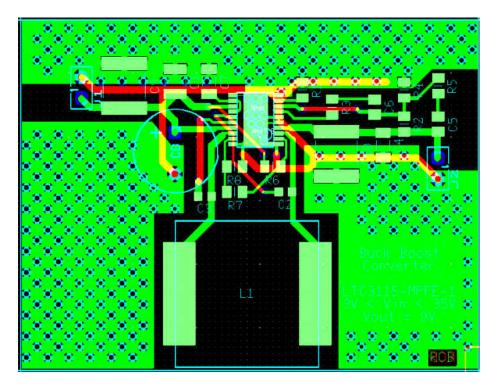

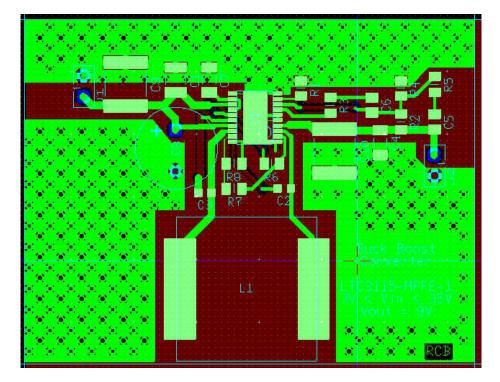

| Figure 28: Single converter lay out. Approximate size: 2" wide x 1.7" high. Copper Top is green and the    | е    |

|------------------------------------------------------------------------------------------------------------|------|

| copper bottom is colored red. The bottom also has a ground plane to assist with heat dissipation, not      |      |

| shown                                                                                                      | . 57 |

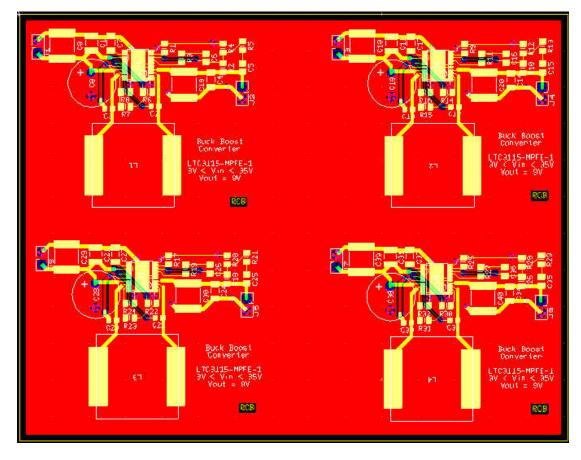

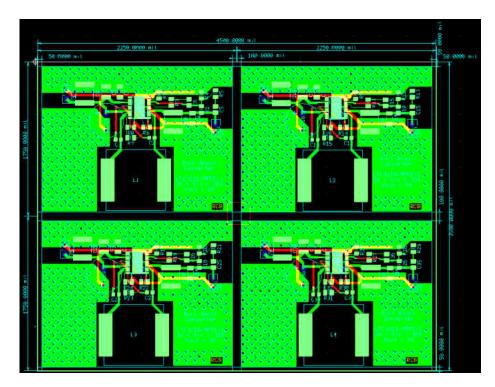

| Figure 29: Array of 4 converters placed on a single PCB. Approximate size: 4.5" wide x 3.5" high. Copp     | er   |

| Top is green and the copper bottom is colored red. The bottom also has a ground plane, shown here, t       |      |

| assist with heat dissipation                                                                               |      |

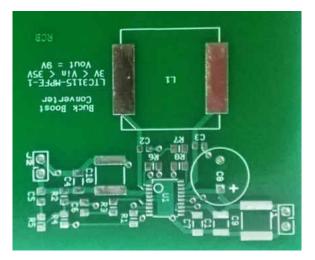

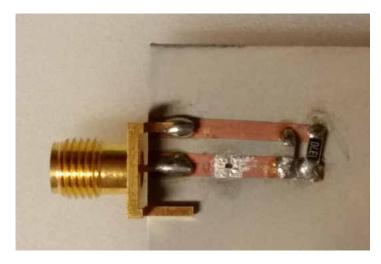

| Figure 30: Image of a single DC converter PCB produced by Advanced Circuits                                |      |

| Figure 31: Image of a single DC-DC buck/boost converter PCB the author populated by hand                   |      |

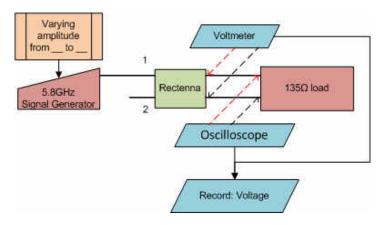

| Figure 32: Test setup for rectifier. A single port was tested at a time since the signal generator used or |      |

| had a single RF output.                                                                                    | -    |

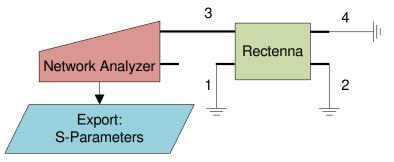

| Figure 33: Test setup for the testing of the rectifier filter. The network analyzer has 2 ports to be able | to   |

| test the S <sub>12</sub> parameter and other combinations listed in step 11 of the testing                 |      |

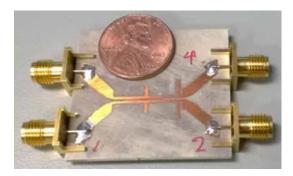

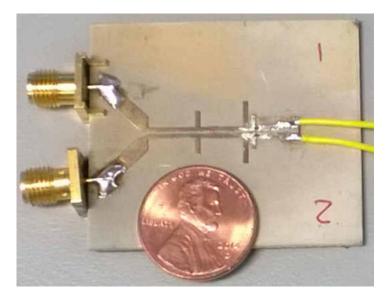

| Figure 34: Filter only design. The port nearest to the penny is port 3.                                    |      |

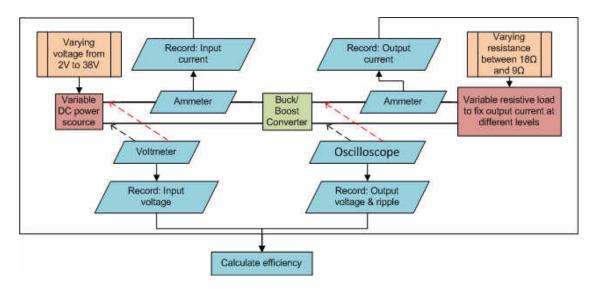

| Figure 35: Test setup of the buck/boost converter.                                                         |      |

| Figure 36: Rectifier layout showing the test points used in the spectral density testing. Each gray box h  |      |

| an increasing probe number starting at the left of Length A or La                                          |      |

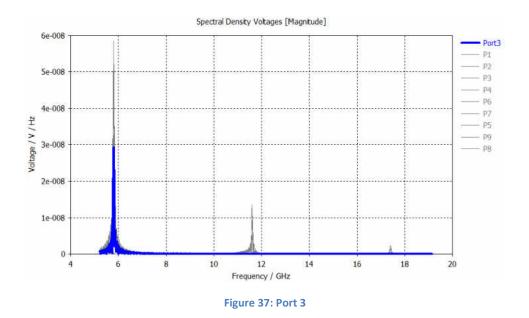

| Figure 37: Port 3                                                                                          |      |

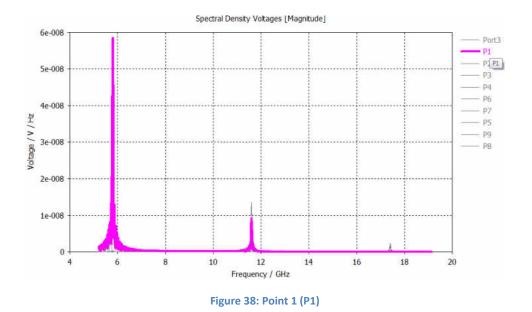

|                                                                                                            |      |

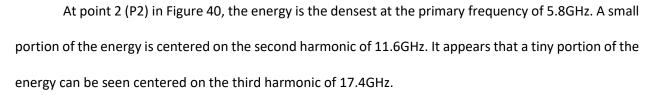

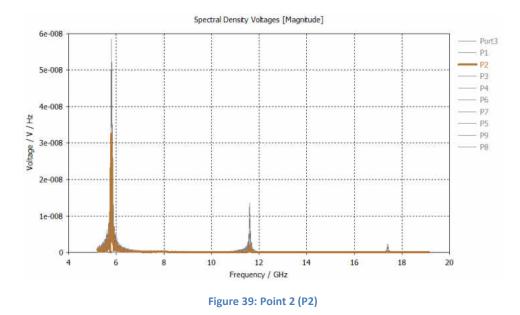

| Figure 39: Point 2 (P2)                                                                                    |      |

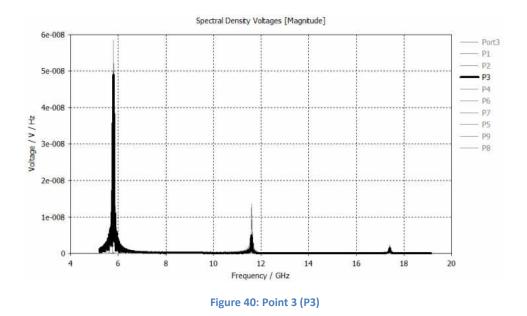

| Figure 40: Point 3 (P3)                                                                                    | .70  |

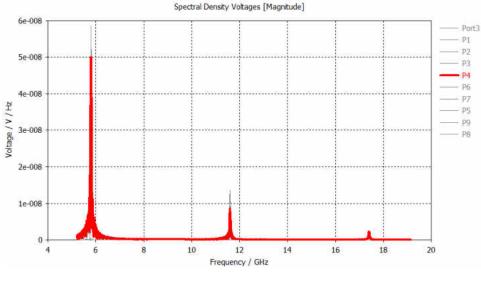

| Figure 41: Point 4 (P4)                                                                                    | .70  |

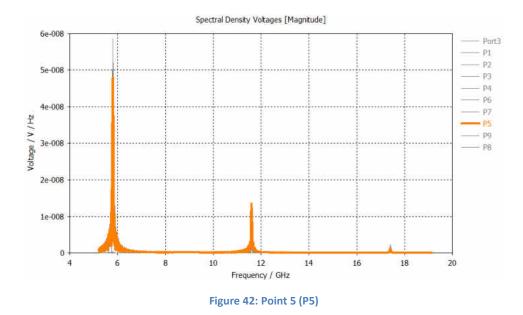

| Figure 42: Point 5 (P5)                                                                                    |      |

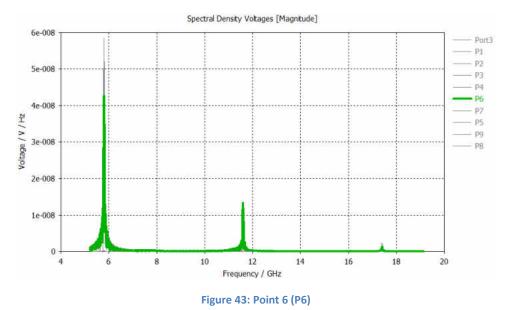

| Figure 43: Point 6 (P6)                                                                                    |      |

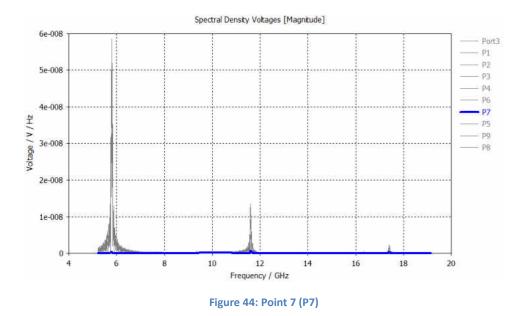

| Figure 44: Point 7 (P7)                                                                                    | .72  |

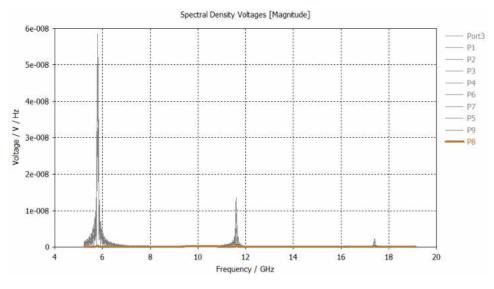

| Figure 45: Point 8 (P8)                                                                                    | .72  |

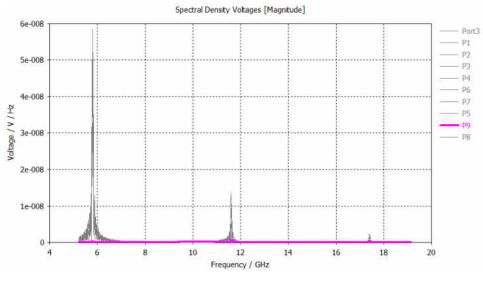

| Figure 46: Point 9 (P9)                                                                                    | .73  |

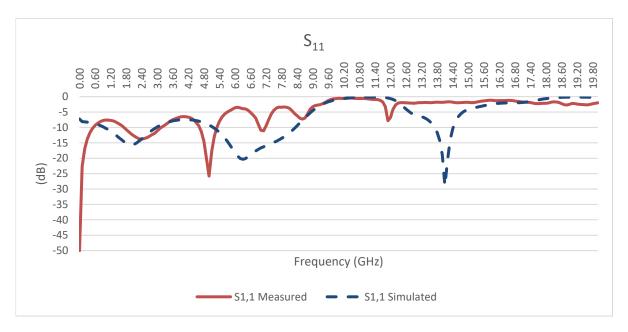

| Figure 47: Measured and simulated S <sub>11</sub> parameters of the filter only prototype                  | .74  |

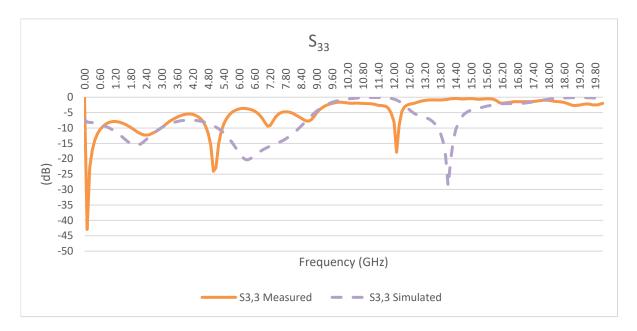

| Figure 48: Measured and simulated S <sub>33</sub> parameters of the filter only prototype                  | .75  |

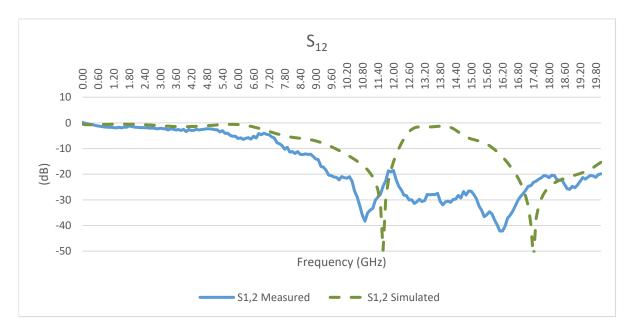

| Figure 49: Measured and simulated S <sub>12</sub> parameters of the filter only prototype                  | .76  |

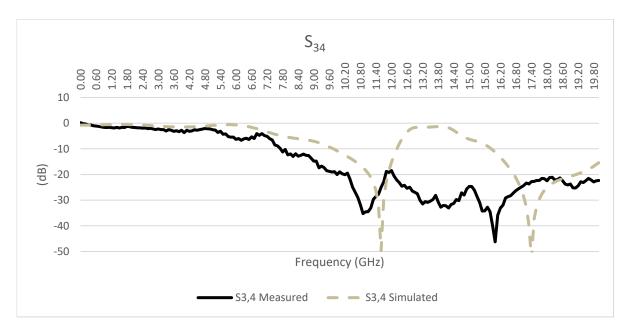

| Figure 50: Measured and simulated S <sub>34</sub> parameters of the filter only prototype                  |      |

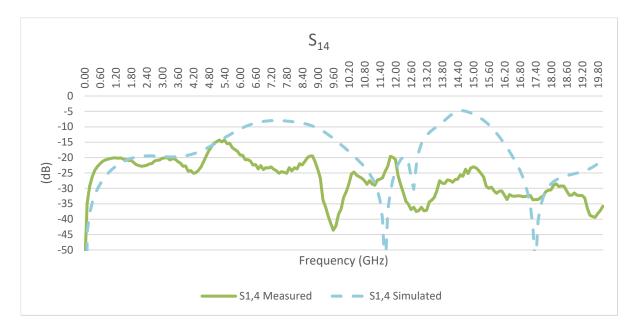

| Figure 51: Measured and simulated S <sub>14</sub> parameters of the filter only prototype                  |      |

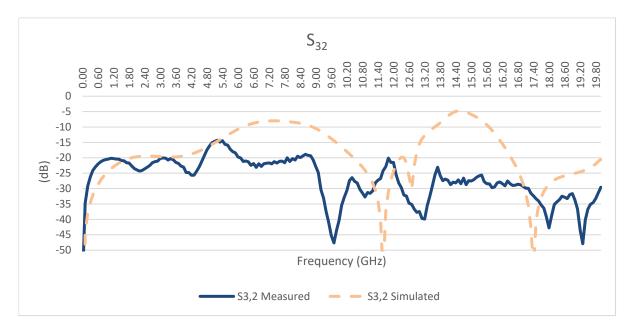

| Figure 52: Measured and simulated S <sub>32</sub> parameters of the filter only prototype                  |      |

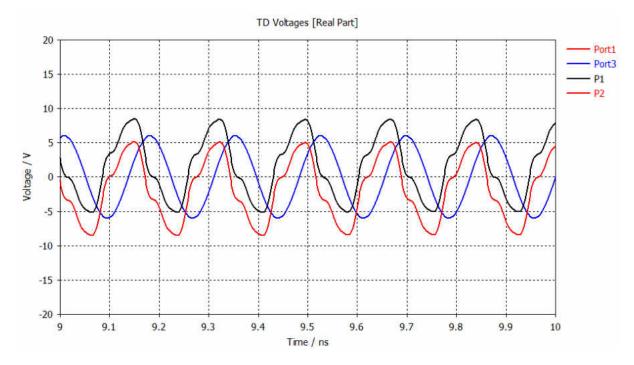

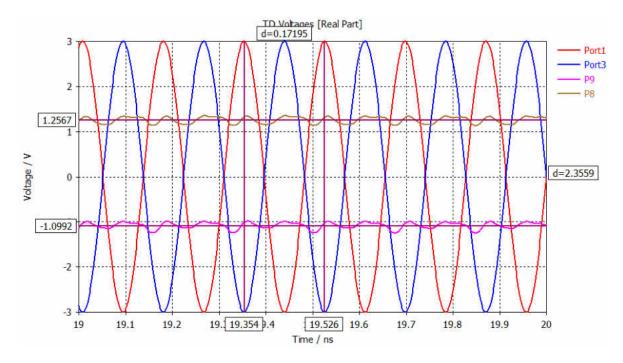

| Figure 53: When inputs are in phase (dual diode configuration) [12]                                        |      |

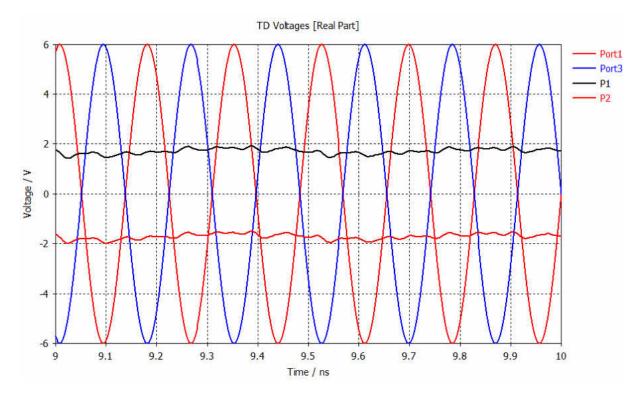

| Figure 54: When inputs have phase shift of 180° (dual diode configuration) [12] (Delay = 0.086207ns)       |      |

| Figure 55: Rectifier simulation used for Rectification simulation [12].                                    | . 80 |

| Figure 56: Rectifier simulation of the prototype built for laboratory measurements                         | .81  |

| Figure 57: Image of the rectifier prototype in relation to a penny                                         |      |

| Figure 58: Image of the second attempt at the prototype rectifier.                                         | .83  |

| Figure 59: Image of the third attempt at the prototype rectifier                                           | .83  |

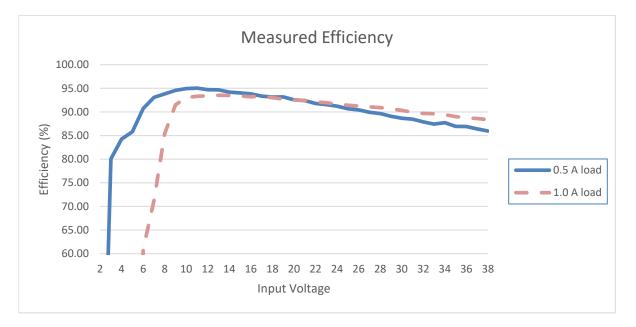

| Figure 60: Measured efficiency of the LTC3115-1 buck/boost converter.                                      |      |

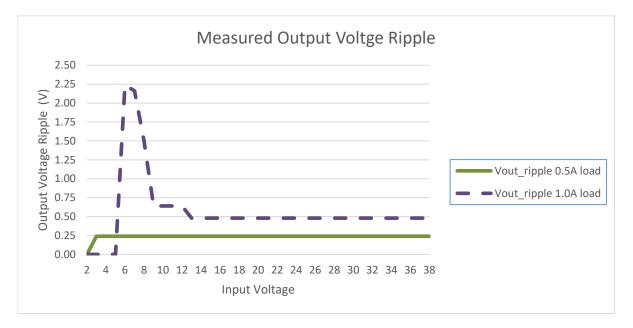

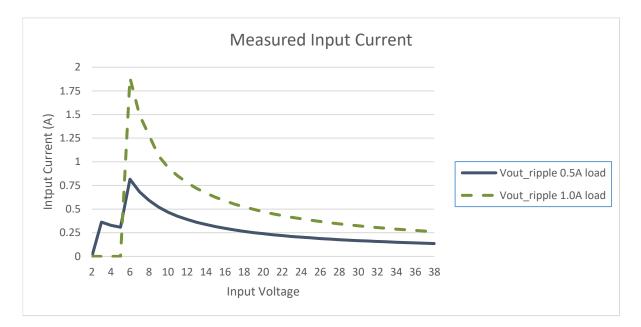

| Figure 61: Measured voltage ripple on the output of the LTC3115-1 buck/boost converter                     |      |

| Figure 62: Measured input current on the output of the LTC3115-1 buck/boost converter                      |      |

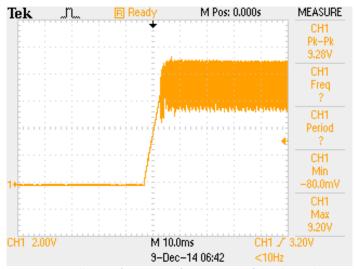

| Figure 63: Oscilloscope's capture of an instance of the thermal shutdown and zoomed into the leading       |      |

| edge of the output voltage waveform. The converter was operating with an input voltage of 14V and a        | -    |

| load current of 1A.                                                                                        |      |

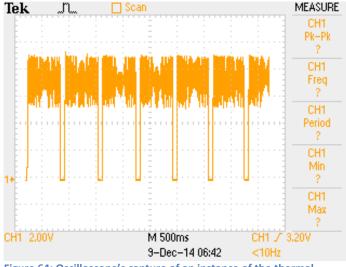

| Figure 64: Oscilloscope's capture of an instance of the thermal shutdown and zoomed to show multipl        | le   |

| periods of the output voltage waveform. The converter was operating with an input voltage of 14V an        | d    |

| a load current of 1A                                                                                       | .87  |

| 3 |

|---|

| 9 |

|   |

| ) |

|   |

| ) |

|   |

| Э |

| 1 |

| ) |

|   |

| ) |

| 5 |

| 7 |

|   |

| ) |

|   |

| 1 |

|   |

### **LIST OF TABLES**

| Table 1: Quick reference description of the variables used to calculate the diode impedance             | 19  |

|---------------------------------------------------------------------------------------------------------|-----|

| Table 2: Quick reference description of the variables used to calculate the diode efficiency            | 21  |

| Table 3: Goals for optimization of harmonic rejection filter.                                           | 29  |

| Table 4: List of DC to DC Converter design constraints with the capabilities of the chosen part for the |     |

| design                                                                                                  | 49  |

| Table 5: List of components and component values for LTC3115-1 buck/boost converter                     | 50  |

| Table 6: Table AA shows the values of the spectral energy density of Figure 37 through Figure 46. The   | 2   |

| values shown are multiplied by 10 <sup>-8</sup> . The units are V / V / Hz                              | 68  |

| Table 7: Measured data from testing the LTC3115-1 at 0.5A load                                          | 128 |

| Table 8: Measured data from testing the LTC3115-1 at 1.0A load                                          | 129 |

### ACKNOWLEDGMENTS

I would like to thank Dr. Corey Bergsrud for working with him on an extension of his research. He proved to be a great sounding board for ideas and areas to research. I wish to express my sincere appreciation to my co-advisors Dr. Hossein Salehfar and Dr. Sima Noghanian. I am grateful for the comments, suggestions, and thoughtful reviews they provided. I would also like to express thanks to my committee member Dr. Prakash Ranganathan who provided critical feedback and suggestions.

I would like to thank the one person that has constantly pushed me to finish my masters with constant support, my wife Thyra. My family, Pete, Carol, and Erin, have also been very supportive in my journey to finish my work. Dedicated to my wife Thyra, my father Pete, My mother Carol and my sister Erin.

### ABSTRACT

Due to the continuous rise in the global energy demands, new sources of fuel and energy need to be explored. One area of research that is currently underdeveloped is the study and application of space solar power. Space solar power (SSP) is a broad topic that covers the idea of capturing and transmitting renewable solar energy from space to earth. There has been lots of research in the area of SSP, but there are yet any test platforms operating in space continuously to gather data for supporting the commercialization of SSP. This research document looks at the design of the sub assembly level of components while keeping in mind the end application of SSP. The most innovative idea of this research work to be implemented is adding a DC to DC converter to a rectenna array to regulate the output so that the output may be used in a constant charging application. A rectenna is a rectifying antenna used to convert microwave energy into a DC output. The process used in the following work developed a rectifier that has been shown to work through simulations and a buck/boost converter to regulate the output voltage from the rectifier. Simulations using the developed rectifier produced more than 1.8V DC when excited by two 6V peak to peak 5.8GHz sine waves. The sine waves were out of phase by 180°. The filter on the designed rectifier was able to reject re-radiation of the 2<sup>nd</sup> and 3<sup>rd</sup> harmonics of the 5.8 GHz input signal by more than 25 dB and 22 dB, respectively. The efficiency of the designed rectifier is unknown due to the simulations not having a current output for a power calculation and the assembled prototypes did not produce any measurable results. The efficiency of the buck/boost

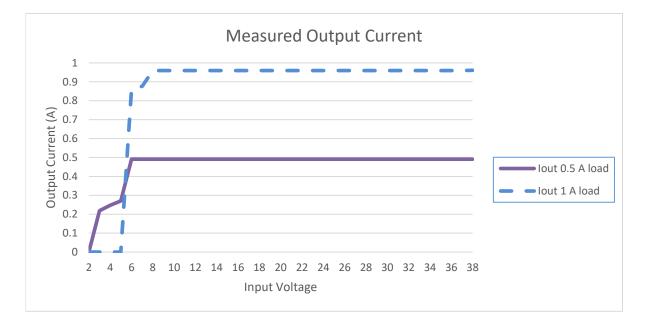

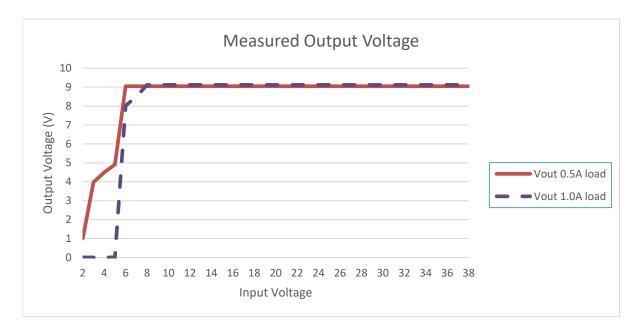

converter has been measured to be 80% efficient and up to 95% efficient, depending on the input voltage and the load requirements.

### **I. INTRODUCTION**

The demand for renewable energy does not appear to be slowing down anytime soon. The desire for more renewable energy has led to a continuous study and investigation of space solar power (SSP). SSP is the idea or concept in which solar energy is harvested by satellites in space and then the energy can be wirelessly transmitted to the surface of the earth using microwaves. The transmission of wireless power via microwaves can be used in numerous applications including powering other satellites (Figure 1), space missions or space travel, used on Earth (Figure 2), and many other applications [1].

Power Recieving Spacecraft

Figure 1: Image of a wireless power transmitting and receiving satellite [1]

Figure 2: Grid tied overview of space solar power [1]

In recent years, there have been numerous researchers and institutions working to advance the systems of SSP so that they could one day be used commercially for microwave wireless power transmission (MWPT) systems. The technology that is being improved for MWPT are the power receiving antenna arrays, rectifiers, and receiving antenna arrays, which will improve the end-to-end system of MWPT systems. MWPT is often received by an integrated microwave antenna and a DC rectifier on a single substrate. The union of the antenna and rectifier into a single design is called a rectenna. Rectennas and their arrays are by no means a novel idea due to the amount of research conducted on them in the past and the current numerous ongoing studies around the world. The general layout of a rectenna can be seen in Figure 3, which was obtained from [2]. The following sections will discuss the approach, design and testing of a single rectifier to be used in conjunction with an antenna developed by another member of the research team.

Figure 3: Block diagram of a rectenna [2].

#### a. State-of-the-Art:

Wireless power transmission (WPT) has been experimented with all the way back to 1879 when David Edward Hughes became the inventor of the crystal radio. People to follow Hughes' work with WPT included Heinrich Hertz with his work on electromagnetic wave propagation and Nikola Tesla with his work on wireless power transmission towers or commonly known as Tesla Coils or his large-scale project of the Tesla Towers. Modern WPT has been forever improved through the inventions of two devices conceived around 1940 by the Klystron tube and the magnetron [2].

The most relevant modern history of WPT began with the works of William Brown of the Raytheon Company. In 1971 the Raytheon Corporation conducted a full-scale experiment of a MWPT system for beam collection and rectification resulting in an efficiency of 82.4% at 2.446GHz [2]. The 82.4% system efficiency achieved by Raytheon was measured from the beam collection to the output of the rectification. Since then, the current state-of-the-art radio frequency (RF) to direct current (DC) rectifiers operating at Super High Frequencies (SHF), 3GHz-30GHz, have achieved efficiencies up to 60% at 10GHz [3]. The measured 60% efficiency includes the losses of the antenna, not just the rectifier [3]. When comparing different designs, one has to keep in mind the type of subsystems that are included in the efficiency calculations and the frequency at which the results are obtained. If two tests do not have the same system included in the efficiency calculations or the same operating frequency, then the two tests cannot be directly compared.

One system that has seen several improvements is the RF-to-DC conversion. This subsystem has been achieving efficiencies greater than 82% since at least 1974. In 1974 Brown and other Raytheon colleagues achieved a RF to DC conversion efficiency of 82.4% with a 2.446GHz signal [2]. The 1974 testing by Brown was technically not a small-scale test, but the measured results of a full-scale experiment on the specific portion of the system directly pertinent to the state-of-the-art for this paper. On the larger scale side of MWPT, a test in 1975 was conducted by a collaboration between Brown at Raytheon, NASA, and the Jet Propulsion laboratory (JPL). The 1975 testing was completed with a one mile distance between the transmission antenna and the receiving rectenna. The first MWPT experiment in space was the International Space Year – Microwave Energy Transmission in Space (ISY-METS). ISY-METS transferred energy from one rocket to another while in space. The experiment used microstrip antennas on the transmitting rocket and two different rectennas on the rocket that received the antennas [2].

In 1998 James McSpaden developed a rectifier that used a printed dipole antenna and a Silicon Schottky diode to achieve a RF-to-DC conversion efficiency of 82% [4]. Since then several new techniques for designing rectennas have been developed. In 2000 Texas A&M researchers developed a RF-to-DC converter that utilizes a circularly polarized pair of antennas with improved Schottky diodes. The Texas A&M researchers achieved an efficiency of 82% with a 5.8 GHz signal

4

[2]. The improved Schottky diodes have lower parasitic capacitances with allow the diodes to be faster and thus more efficient when changing between conducting and blocking modes.

Although the 2008 experiment conducted by John Makins is not a feat of engineering for its efficiency, it is a feat of engineering in overcoming regulations and budgetary constraints for the distance tested. In 2008 Mankins transmitted using an antenna array on Maui, HI, and received the power on the Island of Hawaii, HI (The big island). His power received was less than  $1/1000^{\text{th}}$  of 1%. However, his impressive distance traveled was 148km (91miles). Mankins budget for the experiment was less than a million dollars restricting the size of his transmitting and receiving arrays. Mankins accomplished this with the collaboration of researchers at Texas A&M University (TX, USA) and Kobe University (Kobe, Japan) [2].

The operating frequency (center frequency) of 5.8GHz is most often chosen as a compromise in transmission and reception system size, the ability of the microwave energy to travel through the atmosphere with minor attenuation losses and the ability to transmit long distances. The higher the frequency the less efficient a system will be in the rectification process. The efficiency loss is due to the electrical parts not operating as efficiently due to parasitic effects of capacitance and resistance that are internal to the diodes and capacitors used in rectifiers. However, the increased frequency gives a longer transmission distance because it takes longer for the beam of transmitted power to spread out and leads to a reduction in the size of the MWPT system [3].

Previous rectifier designs used in MWPT developments have focused on half wave rectifiers. Half wave rectifiers decrease the number of parts needed, compared to full wave

5

rectifier designs, thus simplifying the design [2]. Half wave rectifiers are also commonly used since there is a nominal gain in efficiency when compared to a full wave rectifier in the SHF range [5, 6]. These designs often have a single diode to convert the energy. As shown in Figure 3, typical topology for a SHF rectifier is an input filter, a single shunt diode and an output capacitor to short the remaining RF energy [2, 5]. The typical MWPT rectifier design is shown in Figure 4 (a), and can be compared to a charge pump topology using multiple diodes in Figure 4 (b). A charge pump is a half wave rectifier that continuously multiplies the voltage output relative to the input voltage received. Another common name for a charge pump is a voltage doubler. The charge pump is often used in extremely low power designs, such as Radio Frequency Identification (RFID) applications [5].

Figure 4: RF-DC converters: (a) single diode detector, (b) a charge pump [5].

The most common method to connect the rectifiers and antennas in rectennas is by using Co-Planar Strips (CPSs). CPSs are typically impedance matched to the diode and the antenna to maintain the highest power transfer to the load [7]. Impedance matching means that each component has the same impedance so that the power received is divided equally among all parts of the system. Previous research has focused on increasing the rectification efficiency. This has been done by using a fixed load connected directly to the output of the rectifier.

Previous designs have not yet leveraged the advantages from recent discoveries to build a scale model for a specific business case, such as Space Solar Powered Satellite (SSPS) energy utility. In 2009 there was a public release stating that Solaren Corporation would launch and begin selling energy using a Space Solar Power (SSP) system to transmit MWP by the year 2016 [8]. Since the Solaren public announcement in 2009, there has been no indication through public releases to judge if the company will indeed be able to make their intended goal of production starting in 2016. Other researchers, such as Susumu Sasaki of the Japan Aerospace Exploration Agency, have suggested that a commercialized version of SSP system would be viable by the year 2030 or later [9].

#### **b.** Research Problem:

To advance a technology into the production stage of a life cycle one transition that needs to be made is from the technology development process (TDP) to the product development process (PDP). From the state-of-the-art it can be seen that several entities are looking into not just the TDP of MWPT, but they are also looking into the PDP of MWPT. The ongoing research to design space solar power systems (SSPSs) could one day be the future electrical energy source for Earth. To stay current with product development, research entities should also be looking at the system level incorporation of the MWPT technologies. In order for MWPT to be a commercially viable option, the design of rectennas and their Power Management and Distribution (PMAD) systems are essential to meeting an adequate end-to-end efficiency.

The following section will discuss a development process used to produce subsystem prototypes of the Rectifier, rectenna filter, and power converter; which are intended to be able to test the proof of concept of a full scale rectenna array design. The full scale rectenna array and PMAD design should eventually lead to the production and testing of an orbiting spacecraft. Due to the lack of funding towards SSPSs and the complexity of testing a full-scale system, the subsystems of a commercially viable MWPT system need to be dissected and improved towards a better overall efficiency [2].

To break apart the MWPT system into manageable pieces, only a portion of the power receiving spacecraft, such as the receiving satellite seen in Figure 1, will be discussed. This research work will focus on the power conversion (rectenna), regulation (rectenna array), and its management (PMAD) onboard a receiving satellite. Those three things will begin immediately after the power has been received by the antennas that are located on the power receiving satellite as shown in Figure 1. The power converter will be a rectifier that will connect to the antenna and form a rectenna. For simplicity, the power regulation will be considered a sub set of the power management system. The power regulation and power management will be referred to as the PMAD system. The parts being designed can be seen in the green blocks in Figure 5.

8

Figure 5: MWPT receiving satellite power flowchart

#### c. Methodology:

To conduct the proposed work, the following tasks were performed.

## Task 1: Conduct a literature review to understand previous work on MWPT systems. In order to design an efficient rectifier and its associated PMAD for the MWPT system, further

investigation into the characteristics and performance of previous designs is necessary. This investigation exercise would help in a thorough understanding of the previous MWPT designs. The advantages of each previous designs can then be leveraged for the optimal design of the new MWPT system proposed. The design goal of the rectifier was to have an efficiency of 70%. An additional understanding of Schottky Diodes needed to be obtained. An initial literature search revealed that numerous researchers point to using them in their rectifier designs [2, 5].

Task 2: Design and verify the rectifier circuit. Several rectifying topologies were researched to determine the best conversion efficiency. Rectifier topologies that were

9

investigated are single shunt diode [2, 4, 5], dual diodes [10], full wave rectifiers [6], and charge pumps [11]. Since the larger picture of this project was to create a rectenna, a coplanar strip was investigated as the transmission and filtering method for each of the aforementioned rectifier circuits.

After researching each rectifier topology, the design that meets the needs of the SSPS system best was chosen. The chosen topology was simulated in the software package CST Studio Suite [12]. Through design analysis and results from simulations, the selected rectifier topology was tuned to a frequency of 5.8 GHz. This frequency has an accumulated history, has less regulation by the FCC, and has the necessary properties of propagation through the atmosphere for transmission to earth [2]. The Federal Communication Commission (FCC) has deregulated the center frequencies for 2.45 GHz, 5.8 GHz, 24.125 GHz and many other center frequencies for Industrial, Scientific, and Medical (ISM) use and research. These ISM band frequencies are unregulated so that armatures and corporations can use these RF bands for private or public communication between devices. Some devices that operate in these bands are microwave ovens, cordless phones, Wireless LANs (Wifi and Bluetooth), and many other applications. Simulation and design iterations will produce the expected efficiency of the chosen topology and would aid in the design of the harmonic rejection filter as will be covered in Chapter "II", Section "b", Sub-section "iii". As stated earlier, the efficiency goal of the rectification process was set at 70%. After simulation studies were completed and the appropriate rectifier design was selected and finalized, the physical rectifier circuit was fabricated and tested for its efficiency.

The amount of output power from the rectifier depends on the power received from the transmitting antenna. Previous research work suggests that the rectenna array receives a power

irradiance of about 25mW/cm<sup>2</sup> at the center and about 1mW/cm<sup>2</sup> at the outer edges of the array [13]. The size of the rectenna array will be 30 cm by 30 cm as determined by the area of the surface of the application aboard a one unit (1U) class CubeSat. More description of the 1U CubeSat will be provided in the Sub-section "d" of this Chapter. The size of the rectenna array will greatly impact the rectifier design and the PMAD system. An example of a rectenna array design is shown in Figure 6.

Figure 6: An Array of 12 individual rectennas [2].

**Task 3: Design and verify the PMAD system.** The last design aspect of this work focused on the PMAD system. A buck/boost converter design was the primary candidate for the PMAD design of this work. The efficiency of the PMAD power transfer capability was expected to be above 85%.

Task 4: Perform research on how to design an array of rectennas. This process was similar to designing an array of photovoltaic panels to be regulated by a charge controller. Using the output of the rectennas, the PMAD was designed to maintain a constant voltage level on the

load side of the rectenna array. The constant voltage from the designed PMAD, allow multiple rectenna arrays to be combined in parallel as shown in Figure 6. In Figure 6, the PMAD will be placed where "To load  $R_L$ " is shown and the load will be connected to the output of the PMAD.

#### d. System Application and Design Constraints

Throughout the design process of this work the goal will be to design the rectifier and PMAD as if they were going to be used in space, by attempting to use space qualified parts and materials to maintain a sense of authenticity for the designated application on SSPSs. The PMAD system described is intended to be implemented on an experimental satellite that will test the viability of MWPT in a scaled test in outer space.

The satellite mentioned in this design is receiving the MWPT. The proposed initial space application is aboard a 1 Unit (1U) CubeSat. The CubeSat class of satellites are frequently used by universities due to the lowered build and launch costs [14]. The MWPT system will be installed on a 1U satellite. The 1U satellite is a constrained payload so that it would be economically feasible for Universities to send payloads to space. The constraints that a 1U platform provides are a total mass of 1.33 kg and a maximum outer dimensions of 10 cm x 10 cm x 10 cm.

The system was designed as if it is incorporating a Clyde Space CubeSat Standalone battery [15]. The output voltage of the battery should be 9V to ensure a voltage over the 8.2V end of charge voltage benchmark of the Clyde Space battery so the system could successfully charge the battery [16]. The Clyde Space battery has numerous conditions for charging and discharging current rates, but a maximum charge current of 1.875A is recommended [16]. Designing a separate DC to DC converter is a little impractical in the design of the system since the Clyde Space CubeSat Standalone battery can come equipped with a DC to DC converter and does not need to be designed from scratch [16]. The converter incorporated with the Clyde Space battery would be space qualified, unlike the circuit that will be described later. However, obtaining one of these batteries and converters for the purpose of testing is impractical due to the high cost of the battery [15]. This testing is also the first known case in which a DC converter would be incorporated in a MWPT system, making the risk of damage to the expensive DC converter and battery module an unnecessary risk. Since obtaining a Clyde battery would not be possible, a DC to DC converter will be designed and tested with a load to simulate the characteristics of the Clyde battery. The load will be implemented using a fixed resistor load during the testing of the system.

Future calculations and simulations will need to be done on the thermal properties of space and the components in space temperatures. Parts will be chosen to be operational from at least -55oC to 125oC. This temperature range should give the best results for the anticipated harsh environment of space. The temperature range also coincides with the automotive grading of the AECQ-200 standards for parts, making parts for this temperature range widely available and at a reduced cost compared to custom parts.

13

### **II. SYSTEM DESIGN**

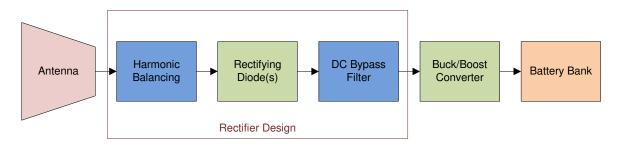

The system design will consider application and design constrains already set in place. The complete system is divided into 4 subsystems; antenna design, rectifier design, rectenna array design, and the DC to DC converter. This research work will only cover the rectifier and DC to DC converter designs. The rectifier design will be comprised of three separate pieces. The rectifier will include a Harmonic Rejection Filter (HRF), rectifying diode(s), and a DC bypass filter. The block diagram of the whole system can be seen in Figure 7. The rectenna array design can be viewed in Figure 6. The following sections will describe each block of Figure 7 in more detail.

Figure 7: Block diagram of the MWPT system

#### a. Antenna Design

The design of the antenna used in this design was completed by another member of the research team, a colleague at the University of North Dakota. The results of the antenna are important to note since all of the pieces of the MWPT system need to be designed to match each other. The antenna was designed to match a  $100\Omega$  transmission line. The reasoning for matching to the  $100\Omega$  will be described in Chapter "III". The antenna design is not a part of this thesis work.

#### **b.** Rectifier Design

As stated, part of this research work is focused on the rectifier design component of the MWPT system. The general design process for the RF rectifier system, was based on the process laid out in [2]. The RF rectifier design process is as follows:

- 1. Select a Schottky diode

- 2. Decide on a Schottky diode configuration

- Design the transmission lines, HRF and load to match the impedance of the chosen diode

- 4. Tune out the reactance of the impedance of the chosen diode

- 5. Select a DC bypass capacitor

Design steps are explained in the following subsections.

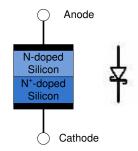

#### i. Diode Selection

The primary device in RF rectifiers is the Schottky diode [2, 4, 5, 7, 10, 17, 18]. The Schottky diode is used due to its low forward voltage and the reduced amount of time it takes the diode to start and stop conducting. Both of these properties leads to improved efficiency. The aforementioned properties are due to the physics of the materials that make up the diodes. The Schottky diode consists of a metal contact and an N-doped silicon substrate as seen in Figure 8. In Schottky diodes P-doped silicon does not exist, despite most other diodes [19]. The lack of P-doped silicon means that there are no minority carrier build-ups; the diode stops conducting as soon as voltage is in reversed biased [5, 20]. The lack of a minority carrier and the presence of a majority carrier junction means that there is a lower barrier voltage, which allows some Schottky

diodes to begin conducting at about 0.3 Volts in comparison to a standard diode conducting at 0.7 Volts. The turn on voltage is the minimum voltage potential across the diode in which the diode will become forward biased and begins to conduct [19]. This reduced turn-on voltage is quite important to the rectifier efficiency since rectifiers are normally dealing with low input voltages. The higher the turn-on voltage, the less power rectified and the more power consumed by the diode. All of the above properties make Schottky diodes a suitable and a common choice in rectifiers operating at high frequencies such as 5.8GHz.

Figure 8: Internal material and symbolic view of a Schottky diode.

An added design challenge when using or considering Schottky diodes is their nonlinear properties. Schottky diodes are nonlinear due to the way they are designed. The interaction between the insulator and the internal metal wires of the diode causes the nonlinearity [5]. A description of how a nonlinear device works is presented by Boaventura [5] "when fed with an RF input signal, the nonlinear device produces several spectral components at the output: DC, fundamental frequency, harmonics of the fundamental, and intermodulation mixing products (if the input signal is modulated)." A nonlinear device has been proven to be quite effective and efficient in rectification for applications of MWPT as described in [2, 4, 17].

#### Schottky Diode Selection

When searching for a diode, it is important to keep in mind that there are no "ideal diodes" on the market, unlike in most of the analysis done in simple circuit theory. There were two types of diodes incorporated into the design analysis process of the rectifier in this work. The BAT17 and MA4E1317 diodes were chosen. The BAT17 was initially chosen due to the low turn on voltage of ≈ 0.3V. However, the BAT17 is limited by a breakdown voltage of 4V. Upon a deeper investigation of the part it was also noted that the part was recommended for use in mixer applications in the Very High Frequency (VHF) and Ultra High Frequency (UHF) [21] circuits. VHF frequency band is defined from 30 MHz to 300 MHz and UHF frequency band is defined as 300 MHz to 3 GHz. Neither of which are overlapping the SHF operating range. The BAT17 is recommended for use in the lower bands due to its relatively large junction capacitance of 0.55pF [21]. In comparison, the MA4E1317 has a maximum operating frequency of 80 GHz and a much lower junction capacitance of 0.02pF. Junction capacitance is the parasitic capacitance that negatively impacts the operating frequency of diodes. While exploring the potential efficiency and preforming impedance calculations of the BAT17; the MA4E1317 was used as a control to compare the results and compare the results to previous works, since it had been used in [10, 17, 18]. A selection between the two diodes was made that will be explained in Chapter "III". The calculations preformed to determine the impedance of a diode are as follows [2, 4].

$$Z_D = \frac{\pi R_S}{D + jE} \tag{1}$$

where,

$$D = \cos \theta_{on} \left( \frac{\theta_{on}}{\cos \theta_{on}} - \sin \theta_{on} \right)$$

(2)

$$\mathsf{E} = \omega R_s (C_j \sqrt{\frac{V_{bi}}{V_{bi} + V_D}}) (\frac{\pi - \theta_{on}}{\cos \theta_{on}} + \sin \theta_{on})$$

(3)

and  $\theta_{on}$  is found by solving equation (4)

$$\tan\theta_{on} - \theta_{on} = \frac{\pi R_s}{R_L (1 + \frac{V_{bi}}{V_D})}.$$

(4)

The junction capacitance  $C_i$  in (3) is defined as

$$C_j = C_{jo} \sqrt{\frac{V_{bi}}{V_{bi} + |V_D|}}.$$

(5)

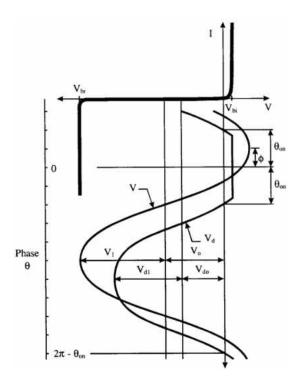

The variables and parameters used in the diode calculation can be seen in Table 1 along with a description of each variable. The datasheet of Schottky diodes provide these parameter definitions as:  $R_s$  is the diode series resistance;  $C_{jo}$  is the zero-bias junction capacitance;  $V_{bi}$  is the built-in turn on voltage;  $V_D$  is set at the operating voltage and is also called the voltage across the diode, which should be ½ of the breakdown voltage ( $V_{br}$ ) [4, 17]. The maximum of  $V_D$  should be about ½ of  $V_{br}$  so that the diode will not be put into an avalanche breakdown mode. Derating of the  $V_D$ , diode voltage, is also a good idea if the part being used has a wide tolerance between the minimum and typical  $V_{br}$ . However, the efficiency of the diode will increase as the rectifier increases  $V_D$  closer to  $V_{br}$ . It should be noted the closer the diode is operated to  $V_{br}$ , the more likely the diode will be saturated and burned out. The load resistance  $R_L$  is the projected load of the system. The  $\theta_{on}$  variable is the forward-bias turn-on angle of the Schottky diode [4, 17]. The forward-bias turn-on angle must be calculated using equation (4).  $\theta_{on}$  can be viewed in relation to other independent variables of the diode and the rectification signal in Figure 9.

| Variable        | Description                                      |

|-----------------|--------------------------------------------------|

| ZD              | Complex impedance of the diode                   |

| R <sub>s</sub>  | Series resistance of the diode                   |

| $\theta_{on}$   | Forward-bias turn-on angle of the Schottky diode |

| $C_j$           | Junction capacitance                             |

| $V_{bi}$        | Built-in turn on voltage (forward voltage)       |

| $V_D$           | Voltage across the diode (operating voltage)     |

| $R_L$           | Load resistance                                  |

| C <sub>jo</sub> | Zero-bias junction capacitance                   |

| V <sub>br</sub> | Breakdown voltage                                |

Table 1: Quick reference description of the variables used to calculate the diode impedance.

Figure 9: The rectification cycle of the shunt diode is represented by the input fundamental and overlaid on the diode Current-Voltage curve. This model assumes that there are no losses due to the harmonics and  $\theta = \omega t - \varphi$  [4].

The diode efficiency is also used to assist in comparing diodes. The calculated efficiency for a can be found by [4, 17]

$$\eta_d = \frac{1}{1 + A + B + C} \tag{6}$$

where,

$$A = \frac{R_L}{\pi R_s} \left( 1 + \frac{V_{bi}}{V_D} \right)^2 \left[ \theta_{on} \left( 1 + \frac{1}{2 \left( \cos \theta_{on} \right)^2} \right) - \frac{3}{2} \tan \theta_{on} \right]$$

(7)

$$B = \frac{R_s R_L C_j^2 \omega^2}{2\pi} \left( 1 + \frac{V_{bi}}{V_D} \right) \left( \frac{\pi - \theta_{on}}{(\cos \theta_{on})^2} + \tan \theta_{on} \right)$$

(8)

and

$$C = \frac{R_L}{\pi R_s} \left( 1 + \frac{V_{bi}}{V_D} \right) \frac{V_{bi}}{V_D} (\tan \theta_{on} - \theta_{on}).$$

(9)

The diode efficiency calculations do not include the effects of the harmonics created by the non-linear operation of the Schottky diode. If the harmonics effects were accounted for in the calculations, the diode efficiency would be higher than the values calculated using the equations (6-9). Many of the parameters and variables used in the diode efficiency calculation are the same as in the diode impedance. All variables used in the diode efficiency calculation are listed with a description in Table 2. The efficiency of the Schottky diodes will approach 100% if the junction voltage ( $V_j$ ) (forward voltage drop) of the diodes is much lower than the breakdown voltage ( $V_{br}$ ) [3]. For example, a  $V_j$  of 0.8V is much lower than a  $V_{br}$  of 60V. Also, the lower the  $C_j$ , the lower the breakdown voltage. Typically, as the  $C_j$  decreases,  $R_s$  increases [3]. While an increase in  $C_j$  reduces the diode efficiency. Also as  $C_j$  decreases, the speed at which the diode can switch between conducting and not conducting increases [3]. Since a highly efficient design requires  $V_{br}$

between the diode characteristics while selecting a diode. If the power input across the diode increases above saturation, the diodes will burn out and stop working.

| Variable                         | Description                                                          |

|----------------------------------|----------------------------------------------------------------------|

| $\eta_d$                         | Efficiency of the diode, excluding effects of harmonics of the diode |

| R <sub>L</sub><br>R <sub>s</sub> | Load resistance                                                      |

|                                  | Series resistance of the diode                                       |

| $V_{bi}$                         | Built-in turn on voltage (forward voltage)                           |

| $V_D$                            | Voltage across the diode (operating voltage)                         |

| $\theta_{on}$                    | Forward-bias turn-on angle of the Schottky diode                     |

| C <sub>j</sub>                   | Junction capacitance                                                 |

| ω                                | Operating frequency                                                  |

Table 2: Quick reference description of the variables used to calculate the diode efficiency.

## **Rectifier Topology**

The two most prominent configurations of a rectifier are a single shunt diode and a Dual diode configuration, as seen in Figure 10. While operating at 5.8GHz, a single shunt diode configuration can achieve the highest overall efficiency (up to 82% [2, 4, 17]). Previous works have achieved efficiency higher than 80% in the power range from 50mW-130mW for a single element test [4, 17]. A single element is the composition of a pair of antennas, HRF, rectifying diode(s) and a DC bypass capacitor, as seen in Figure 10. In Figure 10, the section labeled BPF is the HRF. The rectifying diodes in Figure 10 are at the location shown by the exploded bubble of the "Dual Diodes". The DC bypass capacitor is in the middle of the CPS section and the symbol for the capacitor is shown by the legend on the right side of the image. The critical flaw of the single shunt diode is that the voltage output is low. Higher output voltages are important for all applications that require more than microwatts of power. For this application, the increased voltage is important so that less energy is wasted in order for the output voltage regulation to be closer to the battery or load voltage requirements. The increased voltage of the single element

will lower the efficiency when compared to a single shunt diode topology [10]. However, the dual diodes will allow for an increased efficiency when interconnecting array elements. The importance of the voltage per rectenna will be discussed further in Section "c" of this Chapter. The voltages of the single shunt diode and the dual diode are compared in Figure 11 based on the results of [10]. However, the dual diode configuration has achieved a maximum RF to DC conversion efficiency of only 76% [10].

Figure 10: Layout of the previous dual-diode rectenna design, single shunt diode rectenna, and CPS. All dimensions are in millimeters [10].

Figure 11: Measured DC output voltages of the dual-diode and single shunt diode rectennas [10].

The diode efficiency of dual diodes can be obtained for the BAT17 and the MA4E1317 by the substitution stated by Ren in [10]. The substitution replaces  $R_L$  and  $R_s$  in equations (7) - (9) of this work. To approximate the dual diode efficiency, substitute all instances of  $R_L$  in equations (7) - (9) with  $(R_L + R_D)$  [10].  $R_D$  is the diode resistance or the real portion of  $Z_D$  found in (1). Then all instances of  $R_s$  in equations (7) - (9) should be substituted by  $(R_s + R_L)$  [10]. As a result of this substitution. Equations (7) - (9) will be changed to:

$$A = \frac{(R_L + R_D)}{\pi (R_S + R_L)} \left( 1 + \frac{V_{bi}}{V_D} \right)^2 \left[ \theta_{on} \left( 1 + \frac{1}{2 (\cos \theta_{on})^2} \right) - \frac{3}{2} \tan \theta_{on} \right]$$

(10)

$$B = \frac{(R_s + R_L)(R_L + R_D)C_j^2 \omega^2}{2\pi} \left(1 + \frac{V_{bi}}{V_D}\right) \left(\frac{\pi - \theta_{on}}{(\cos \theta_{on})^2} + \tan \theta_{on}\right)$$

(11)

and

$$C = \frac{(R_L + R_D)}{\pi (R_s + R_L)} \left( 1 + \frac{V_{bi}}{V_D} \right) \frac{V_{bi}}{V_D} (\tan \theta_{on} - \theta_{on}).$$

(12)

The most significant advantage of the dual diode configuration is that it will have two to three times the voltage of the single shunt diode configuration, as seen in Figure 11 [10]. Figure 3 shows the rectenna layout for a single diode configuration. If a dual diode were to be chosen, it would look like the dual diode balloon in the top center of the image seen in Figure 10. The dual diodes used in [10] was a brand-new idea and topology design in research [10]. Previous designs have used multiple diodes in their rectification process [11, 22, 23]. Previous designs using multiple diodes are more closely related to charge pumps, as seen in Figure 4 (b) [11]. Charge pumps are typically used for much lower power devices such as RFID tags and produce only microwatts of power [11]. All of the filtering blocks in Figure 3 allow more RF power to be retained and converted into DC.

#### ii. Diode Matching to Coplanar Strips

One of the most important factors in the rectifier design, is ensuring the transmission lines are matched properly to the impedance characteristics of the chosen diode. If the transmission lines are not matched properly, there will be a loss in efficiency. The impedance of the Schottky diode needs to be first calculated by using calculations in equations (1) - (4). Once the impedance calculation is completed, a graph of the diode impedance versus the load resistance can be created. The Diode impedance should match to the circuit should be made with the real impedance and not the complex portion of the impedance [2]. The complex impedance should be matched to the antenna's complex impedance so that it is tuned out and the power can be transmitted as efficiently as possible. If the antenna, HRF and diodes are not matched impedances, the efficiency of the system will suffer. The use for the complex portion of the diode impedance will be discussed later in this Section under Sub-section "iv". The efficiency calculations using equations (6) - (9) are used to find the efficiency of the Schottky diode. To choose an impedance for matching the coplanar strips to the diode, both the impedance and efficiency graphs should be consulted. The matched impedance should allow the diode to operate near the highest possible diode efficiency. However, choosing high load impedance will result in a low output current. A compromise between output current and the efficiency needs to be made. This is to maximize the power transfer of the system to achieve greater power transfer efficiency.

#### iii. Harmonic Rejection Filter

The HRF prevents the reradiating of RF energy at frequencies other than the center frequency. The filter does this by allowing the 5.8GHz signal received by the antennas to pass, but will not allow the various harmonic frequencies 2f, 3f, 4f, etc. (where f is the fundamental frequency) to be returned to the antenna. The harmonic frequencies are created by the nonlinear operation of the Schottky diode.

There are several types of filters that could be used to achieve these results. First is a High Pass Filter (HPF) which allows only high frequency signals to pass through. Second is a Low Pass Filter (LPF) which allows only low frequency signals to pass through. Next is a Band Pass Filter (BPF) which is a combination of a HPF and a LPF so that only a specific band of frequencies is allowed to pass through the filter. Next is a Band Stop Filter (BSF) which is a combination of a HPF and a LPF so that only a specific band of frequencies is prevented from passing through the filter. The HRF in this work can represented as a combination of a Band Stop Filter (BSF) and a Band Pass Filter (BPF), since the center frequency of 5.8GHz is allowed to pass and the 2<sup>nd</sup> and 3<sup>rd</sup> harmonics are rejected. This work could have also been completed by using a low pass filter. The type of filter is intended to be a maximally flat filter so that the frequencies between the areas of interest have a nearly constant amplitude attenuation. The initial filter design chosen was based on the filter used in [10], which can be seen noted by the "BPF" in Figure 10.

The rectenna filter in [10] was used in this work as an initial starting point due to simplistic design and ease of optimization using the software package from Computer Simulation Technology (CST) [12]. It is important that the impedance of the HRF to be matched to the real impedance of the diode(s) to maximize the rectification efficiency [2]. The design and layout of the rectifier circuit can be seen in Figure 12. The label "La" and the items below and to the right are the optimized filter and rectifier. "La" is the length "a" of the first coplanar strip (CPS). A CPS is two parallel transmission lines separated by an air gap and a dielectric constant between the lines and a ground plane. The thin blue lines in Figure 12 are representations of the electrical connections between the blocks. The "T" looking block is a junction that allows the filter stub, "L1" to be connected to the CPSs on either side of the "T". The design continues like this until it reaches the SPICE representations of the diodes. Since the design is symmetrical between the top and bottom halves of the filter and rectifier, "La" does not need the Prime of "La" below the strip of "La". Inside the simulation, CST accounts for the dielectric constant, width length and height of each transmission line, along with the gap between the transmission lines and the ground plane. The SPICE Models for the diodes are based on the parameters found in the diode datasheet and then entered into a text file and uploaded to CST through a SPICE model. Once the

filter design from [10] was imported to CST it was optimized to meet the author's specific goals for the filter seen in goals 0 through 7, as seen in Table 3. The design parameters for Figure 12 are located in Appendix G. The impedance line diagram of Figure 12 is also located in Appendix G.

| Description     | Operator | Target | Frequency (GHz) | Weight of Goal |

|-----------------|----------|--------|-----------------|----------------|

| S <sub>11</sub> | Min      | 0      | 5.8             | 1              |

| S <sub>33</sub> | Min      | 0      | 5.8             | 1              |

| S <sub>12</sub> | Max      | 1      | 5.8             | 1              |

| S <sub>34</sub> | Max      | 1      | 5.8             | 1              |

| S <sub>12</sub> | Min      | 0      | 11.6            | 1              |

| S <sub>34</sub> | Min      | 0      | 11.6            | 1              |

| S <sub>12</sub> | Min      | 0      | 17.4            | 1              |

| S <sub>34</sub> | Min      | 0      | 17.4            | 1              |

Table 3: Goals for optimization of harmonic rejection filter.

In Table 3, a target value of 0 represents that the signal at the specified frequency will not be allowed to pass, a target value of 1 represents that the signal at the specified frequency will be allowed to pass. In Figure 12, each yellow box represents a port. S<sub>ij</sub> is the S parameter between ports i and j.

#### iv. DC Bypass Capacitor

The DC bypass filter acts as a short for the high frequency harmonics and allows the DC power to pass onto the load. The complex portion of the diode impedance will be tuned out by the reactive size of the bypass capacitor [2]. The distance between diode and the bypass capacitor,  $d_{dc}$ , can be viewed in Figure 3. The length  $d_{dc}$  is decided through experimentation, as shown by previous researchers [17, 18]. If a dual diode topology is chosen, then the complex impedance of the two diodes can be assumed to be canceled out since the diodes will not be acting like the single shunt diode [10]. The size of the capacitor is a difficult choice. The capacitor should be large enough to remove the ripple from the rectifying process, but small enough so that the capacitor can fully recharge to the input voltage so that no voltage is dropped across the

capacitor. Ripple, or voltage ripple is unwanted radiation of an AC signal or noise on an output intended to be a DC output signal.

#### v. Half-wave Versus Full-wave Rectifying

The consideration for using a half-wave rectifier versus a full-wave rectifier was determined on two terms. First reason is the reduction of parts and thus a reduction in building cost [5]. Second reason is that the difference between conversion efficiency of half- and full-wave rectifiers at SHF (5.8GHz) is extremely small based on the comments of [5, 6]. The largest benefit that a full-wave rectifier has over a half-wave rectifier is that the full-wave rectifier can divide the input power across more diodes than a half-wave rectifier. When the power is divided in the full-wave rectifier the rectifier can operate at higher power levels before the diodes reach their breakdown ratings [6]. With a full wave rectifier, there will also be a smaller output voltage ripple on the end of the rectenna. However, the full-wave rectifier requires a higher operating voltage range due to the increased number of diodes. The full-wave rectifier system power conversion efficiency at lower input power levels will be much lower when compared to a half-wave rectifier due to the voltage drop across the extra diodes. Meaning the small signal conversion of a full wave rectifier is potentially worse or marginally better than the half-wave rectifier when efficiency is the most important factor in compare to smooth DC voltage.

## c. Rectenna Array Design

The goal in designing the rectenna array is to capture and convert the most power possible for the given area. The area will be constrained by the size of the satellite. In this case the spacecraft will be  $10 \text{cm} \times 10 \text{cm} \times 10 \text{cm}$ . The size of the array will be  $30 \text{cm} \times 30 \text{cm}$  built of

30

nine separate  $10 \text{cm} \times 10 \text{cm}$  panels arranged in a  $3 \times 3$  panel square, similar to Figure 13. The array will need to balance the spacing of the rectenna elements close enough to fit as many rectennas on the array surface as possible, but also far enough away from each other so each element can absorb the optimal amount of energy.

Figure 13: Image of the receiving satellite with a 4x4 panel area or a 3x3 panel area [1] [12].

Like any other portion of the RF to DC conversion process, the design of the rectenna array can make or break the efficiency of the system. The rectenna array can be made more or less efficient by how elements are inter-connected. An element consists of two antennas and the rectifier, as seen in the dashed boxed in Figure 14 (A). There are two basic ways to connect elements into an array, series and parallel as seen in Figure 14 (B) and (C) [10, 24]. A third method, cascaded, can be implemented by using series and parallel to connect elements into an array, as seen in Figure 14 [10]. In [10] results were published on all three interconnection methods using the dual diodes seen in Figure 10 instead of the shunt diode method shown in Figure 14. The experiment results described in [10] discovered that the cascaded array produced a greater voltage and had a better efficiency than any other connection method. In [10, 24] the efficiency of array elements in series and parallel connections were studied, and found that elements

connected in parallel produced more power than those elements connected in series. It was also noted that elements in an array generally produce equal or less power than the sum of the power generated by the elements individually [24]. The ability to have fewer rectennas in series will increase the overall system efficiency. This is because it has been shown that rectennas cascaded in parallel are more efficient than their counter parts connected in series [10, 24].

Figure 14: (A) Cascaded Antennas, (B) Series Antennas, and (B) Parallel antennas

## d. DC-to-DC Converter

The DC-to-DC converter is a transition between the rectenna arrays and the batteries onboard the satellite, as seen in Figure 16. The purpose of the DC-to-DC converter is to regulate the energy gathered from the rectenna array and use it to charge a battery bank. The type of DCto-DC converter chosen for this work will be a buck/boost converter. A buck/boost converter is a combination of a buck converter and a boost converter. The buck converter can regulate input voltages at or above a desired output voltage, thus reducing or bucking the input voltage. A boost converter can regulate input voltages at or below a desired output voltage, thus increasing or boosting the voltage. The combination of a buck and boost converter into a single design is highly advantageous for an application with a large input voltage range. The buck/boost converter was also chosen since the designs are familiar to the author from previous projects that have been completed.

Figure 15: Block diagram showing the position of the DC-to-DC converter.

The most important reasons for having a DC-to-DC converter is to regulate the input voltage and protect the batteries, improve the system design for use on multiple spacecraft, and assist the rectenna array to be designed for the greatest power reception.

The DC-to-DC converter will allow the battery to be charged while the satellite is not in the optimal power density. This will protect the batteries from being over and under charged. This will be a result of the buck/boost converter's ability to increase the voltage received high enough to charge a battery or decrease the voltage received so the battery does not over charge. In a more advanced design, the buck/boost converter could be replaced by a charge controller. The converter will maximize the amount of energy that can be stored in the batteries when the satellite is coming into and out of the primary RF beam by allowing the battery to begin charging at lower input powers. This ability will allow the batteries to be charged effectively for a longer amount of time.

The properties of the converter will also allow the rectenna array to be used on multiple receiving satellites that receive different power densities. The multiple power densities may happen due to different orbiting elevations and relative closeness to the transmitting spacecraft.

If a DC-to-DC converter was not used in the design, and the same rectenna array design was used on two satellites, which received different power densities, the array would produce different output voltages and would have different efficiencies. Without a DC-to-DC converter and by using the same rectenna array for multiple power densities, the system could produce a voltage, which could damage the battery bank or other circuitry in the system. On the contrary, the satellite may produce a low voltage situation, in which the system may not maintain its operation as expected or it may never turn on.

To show how a converter would assist in the optimal rectenna array design an example is given:

Presume that the transmitting power beam cannot be changed, and the rectenna array was designed without a DC-to-DC converter to produce an output of 8 volts to charge a battery bank and the power irradiance of the array is 10mW/cm<sup>2</sup>. The 10mW/cm<sup>2</sup> is chosen because it is located near the midpoint of the 0.1-20mW/cm<sup>2</sup> expected operating range of the receiving satellite being designed. Also, presume that the number of rectenna elements in an array is fixed at eight elements, for ease of calculation. Based on the results from [10] and those shown in

34

Figure 11 a single shunt diode could produce about 2V [10]. This would require the array to have a sub-array of two cascaded elements and four sub-arrays in series to produce the required voltage for a charging, 8V. If the satellite shifted position and the power irradiance increased to 20mW/cm<sup>2</sup>, the output voltage could then be 12V. The four extra volts above the charging voltage could cause damage or diminish the lifespan of the battery bank.

If a DC-to-DC converter is added to the example system design, then the dual diode array can have all eight elements cascaded because the DC-to-DC converter would maintain the battery charging voltage at 8V even if the input fluctuates, based on the results from Figure 11 [10]. However, for the single shunt diode array example, there could be four elements cascaded into a sub-array and two sub-arrays could be connected in parallel to increase the efficiency of the rectenna array over adding elements in series. The reduction of antennas in series is important because studies have shown that more power can be produced in an array if elements are cascaded or are in parallel compared to elements being tied in series [5, 10, 24]. The new design would also include all of the other mentioned benefits of a DC-to-DC converter.

The downsides of adding a DC-to-DC converter are the additional losses in system efficiency and an increase in system cost and complexity. The advantages of a converter are an expanded operating voltage range for operation of a load or battery charging, an increase in array efficiency achieved by more cascaded and parallel rectennas, a common design can be used on multiple receiving satellites without needing an array redesign. It is important to note that every DC-to-DC converter is different and has different efficiency curves. However, DC-to-DC converters easily achieve efficiencies above 85% [25, 26].

35

The design criteria for selecting and designing the DC-to-DC converter are:

- 1. Buck/boost converter

- 2. Acceptable range of Vin, ~  $4V < V_{in} < 30V$

- 3. V<sub>out</sub> = 9V

- 4. Maximum  $I_{out} \ge 2A$

#### i. Converter Design analysis

Much of the design analysis for the converter can be found in the datasheets [27] or application notes [28] produced by DC-to-DC converter manufacturers. Beyond the calculations found in the converter datasheet, the two most important parameters for the converter is the tolerances of the resistors to ensure that a resistor does not cause the output of the converter to be changed; and the maximum power consumed by each resistor.

When using resistors in any design it is importance to check that their variance in manufacturing will not impact the design. The easiest way to show the variance is to look the feedback resistor divider used by most converters to set the output voltage of the DC converter. This is done by checking the minimum and maximum voltage output based on the divider network. The following equations assume that the divider network looks like Figure 16.

The starting equation for the resistor divider is as follows,

$$V_{FB\_desired} = V_{out} \frac{R_{Bottom}}{R_{Top} + R_{Bottom}}.$$

(13)

Solving equation (13) for  $R_{Bottom}$  creates the following equation,

$$R_{Bottom} = \left(\frac{V_{out}}{V_{FB\_desired}} - 1\right) * R_{Top}.$$

(14)

$V_{FB\_desired}$  is the nominal voltage on net FB in Figure 16 in which the converter will attempt to maintain in order to regulate the output voltage ( $V_{out}$ ). Equation (14) assumes that the value  $V_{out}$  has been specified by the application description, along with the value of  $V_{FB\_desired}$  which should be specified in the DC converter datasheet or application note. Since the value of the two resistors are still unknown, a second equation, equation (15), will be used to substitute into equation (14) in order to find the resistor values. Since the converter is attempting to achieve the highest possible efficiency, the sum of  $R_{Top}$  and  $R_{Bottom}$  should be very high. It is recommended that the sum of the two resistors meet exceed 1 M $\Omega$ , as:

$$R_{Top} + R_{Bottom} >= 1M\Omega. \tag{15}$$

Now that the values of the resistors are known, the Resistor tolerance needs to be specified and the minimum and maximum resistance for both resistors need to be calculated as seen by the following equations for the resistor minimum and maximum,

$$R_{XXXX\_min} = R_{XXXX} \left( 1 - \frac{Tol_R}{100} \right)$$

(16)

and

$$R_{XXXX\_max} = R_{XXXX} \left( 1 + \frac{Tol_R}{100} \right).$$

(17)

The new minimum and maximum output voltage is checked to ensure that the resistor tolerances will not impact the output voltage significantly, as seen in the following two equations

$$V_{out\_max} = V_{FB\_desired} \frac{R_{Top\_max} + R_{Bottom\_min}}{R_{Bottom\_min}}$$

(18)

and

$$V_{out\_min} = V_{FB\_desired} \frac{R_{Top\_min} + R_{Bottom\_max}}{R_{Bottom\_max}}.$$

(19)

The power requirements can now be checked for the two resistors using  $P_R = \frac{V^2}{R}$ . The following

equations are implemented in the divider network shown in Figure 16,

$$P_{R\_Bottom} = \frac{\left(\frac{V_{max\_out*R_{Top\_min}}}{R_{Bottom\_max}+R_{Top\_min}}\right)^2}{R_{Bottom\_max}}$$

(20)

$$P_{R\_Top} = \frac{\left(\frac{V_{\max\_out*R_{Bottom\_min}}}{R_{Top\_max}+R_{Bottom\_min}}\right)^2}{R_{Top\_max}}.$$

(21)

In equations (20) - (21) the value of  $V_{max\_out}$  is not the same value of  $V_{out\_max}$  calculated in (18). The value  $V_{max\_out}$  is the specified maximum voltage the load of the converter will possibly see.  $V_{max\_out}$  should be about 5-10% higher than the typical value of  $V_{out}$ . The following check should be completed and passed,

$$V_{out\_max} < V_{\max\_out} \tag{22}$$

The minimum value of the inductance and the output ripple current calculations were obtained from the application note by Green [28]. The minimum inductance value is a crucial step in designing a monolithic buck/boost converter. The minimum inductance needed is first determined by calculating the minimum inductances for the buck mode and boost mode with

$$L_{Min\_Buck} > \frac{V_{out} * (V_{in\_max} - V_{out})}{K_{ind} * F_{sw} * V_{in\_max} * I_{out}}$$

(23)

and,

$$L_{Min\_Boost} > \frac{V_{in\_min}^{2} * (V_{out-V_{in\_min}})}{K_{ind} * F_{sw} * I_{out} * V_{out}^{2}}.$$

(24)

The maximum inductance between  $L_{Min_Buck}$  and  $L_{Min_Boost}$  is then chosen as the converter's overall minimum inductance ( $L_{Min}$ ), as seen by

$$L_{Min} = max[L_{Min\_Boost}, L_{Min\_Boost}].$$

(25)

The following are an explanation of the parameters used in (23) and (24).  $V_{out}$  is the typical output value of the converter.  $V_{in_max}$  is the maximum possible input voltage that the converter could anticipate.  $K_{ind}$  is a constant to reflect the output current ripple. This value can

be approximated to be between 0.2 and 0.4 ( $20\% < K_{ind} < 40\%$ ).  $F_{sw}$  represents the chosen switching frequency.  $I_{out}$  is the anticipated load current of the converter.  $V_{in\_min}$  is the minimum input voltage in which the converter will operate.

## e. Substrate and PCB Materials