University of North Dakota UND Scholarly Commons

Theses and Dissertations

Theses, Dissertations, and Senior Projects

January 2012

# Wideband Wilkinson Power Divider For Uav Phased Array Radar

Jonathan Michael Musselwhite

Follow this and additional works at: https://commons.und.edu/theses

**Recommended** Citation

Musselwhite, Jonathan Michael, "Wideband Wilkinson Power Divider For Uav Phased Array Radar" (2012). *Theses and Dissertations*. 1303. https://commons.und.edu/theses/1303

This Thesis is brought to you for free and open access by the Theses, Dissertations, and Senior Projects at UND Scholarly Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of UND Scholarly Commons. For more information, please contact zeinebyousif@library.und.edu.

# WIDEBAND WILKINSON POWER DIVIDER FOR UAV PHASED ARRAY RADAR

by

Jonathan Musselwhite Bachelor of Science, University of North Dakota, 2010

A Thesis

Submitted to the Graduate Faculty

of the

University of North Dakota

in partial fulfillment of the requirements

for the degree of

Master of Science

Grand Forks, North Dakota August 2012 This thesis, submitted by Jonathan Musselwhite in partial fulfillment of the requirements for the Degree of Master of Science from the University of North Dakota, has been read by the Faculty Advisory Committee under whom the work has been done, and is hereby approved.

Dr. Hossein Salehfar, Chairperson

Dr. Sima Noghanian

Dr. William Semke

This thesis is being submitted by the appointed advisory committee as having met all of the requirements of the Graduate School at the University of North Dakota and is hereby approved.

Wayne Swisher, Dean of the Graduate School

Date

# PERMISSION

| Title:      | Wideband Wilkinson Power Divider for UAV Phased Array Radar |

|-------------|-------------------------------------------------------------|

| Department: | Electrical Engineering                                      |

| Degree:     | Master of Science                                           |

In presenting this thesis in partial fulfillment of the requirements for a graduate degree from the University of North Dakota, I agree that the library of this University shall make it freely available for inspection. I further agree that permission for extensive copying for scholarly purposes may be granted by the professor who supervised my thesis work, or in his absence, by the chairperson of the department or the dean of the Graduate School. It is understood that any copying of publication or other use of this thesis or part thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of North Dakota in any scholarly use which may be made of any material in my thesis.

Signature Jonathan Musselwhite

Date <u>07/25/2012</u>

# TABLE OF CONTENTS

| LIST OF FIGURESvii                                                                   |

|--------------------------------------------------------------------------------------|

| LIST OF TABLESxi                                                                     |

| ACKNOWLEDGMENTSxii                                                                   |

| ABSTRACTxiii                                                                         |

| 1. INTRODUCTION                                                                      |

| 1.1 Unmanned Aircraft System's Barrier for Entry in the National Airpsace System . 1 |

| 1.2 Cooperative Sense and Avoid Using Automatic Dependent Surveillance-<br>Broadcast |

| 1.3 Phased Array Radar UAS for Non-Cooperative Sense and Avoidance 2                 |

| 1.4 Laserlith Corporation and Private Corporation Involvement                        |

| 1.5 Prior Work                                                                       |

| 1.6 Review of Literature7                                                            |

| 1.7 Work Performed                                                                   |

| 2. WILKINSON POWER DIVIDER PRINCIPLES                                                |

| 2.1 Introduction9                                                                    |

| 2.2 Definitions                                                                      |

| 2.3 Power Divider History11                                                          |

|      | 2.4 Design Procedure                  | . 17 |

|------|---------------------------------------|------|

|      | 2.5 Coupling and Isolation            | . 22 |

|      | 2.6 Straight Split and Circular Split | . 23 |

|      | 2.7 Multistage Wilkinson Splitter     | . 24 |

|      | 2.8 Design Considerations             | . 27 |

|      | 2.9 The System Overview               | . 28 |

|      | 2.10 Phase Array Radar Principles     | . 28 |

| 3. N | METHODOLOGY                           | . 32 |

|      | 3.1 Phased Array Radar Requirements   | . 32 |

|      | 3.2 Power Divider Requirements        | . 35 |

|      | 3.3 Wilkinson Power Divider Variables | . 36 |

|      | 3.4 Simulation Results                | . 37 |

|      | 3.5 Fabrication                       | . 51 |

| 4. F | RESULTS                               | . 54 |

|      | 4.1 Introduction                      | . 54 |

|      | 4.2 Measurement Result                | . 54 |

|      | 4.3 Port Isolation                    | . 61 |

| 4.4 Phase and Power Error                        | 62 |

|--------------------------------------------------|----|

| 4.5 Board Integration With The System            | 71 |

| 4.6 Comparison of Measured and Simulated Results | 72 |

| 5. CONCLUSION                                    | 74 |

| 5.1 Final Assessment                             | 74 |

| 5.2 Future Considerations                        | 76 |

| APPENDICES                                       | 77 |

| Appendix A: Wilkinson Split VNA Results          | 78 |

| Appendix B: Matlab Code                          | 92 |

| REFERENCES 1                                     | 08 |

# LIST OF FIGURES

| FIGURE 1: 5.8 GHZ PHASE ARRAY PROOF OF CONCEPT SYSTEM4                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| FIGURE 2: UND UASE SUPER HAULER5                                                                                                                       |

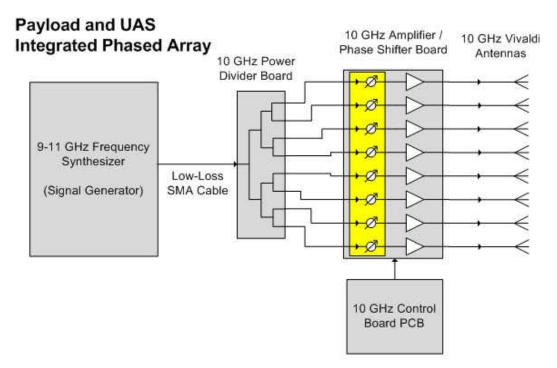

| FIGURE 3: 10 GHZ PHASED ARRAY BLOCK DIAGRAM6                                                                                                           |

| FIGURE 4: MITERING RIGHT ANGLES11                                                                                                                      |

| FIGURE 5: BASIC CONCEPT FOR (A) POWER DIVISION, (B) POWER COMBINING [18]12                                                                             |

| FIGURE 6: TRANSMISSION LINE MODEL OF T-JUNCTION DIVIDER [18]14                                                                                         |

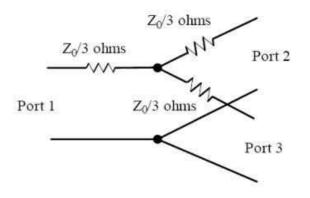

| FIGURE 7: RESISTIVE POWER DIVIDER [19]15                                                                                                               |

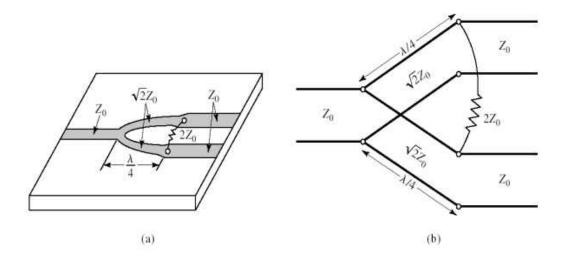

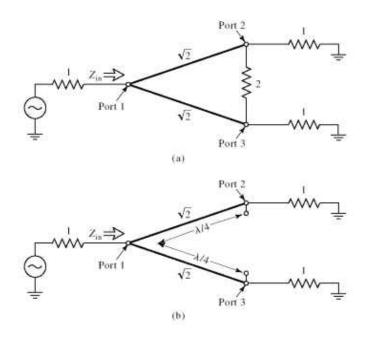

| FIGURE 8: THE WILKINSON POWER DIVIDER: (A) AN EQUAL-SPLIT WILKINSON POWER DIVIDER IN<br>MICROSTRIP FORM, (B) EQUIVALENT TRANSMISSION LINE CIRCUIT [18] |

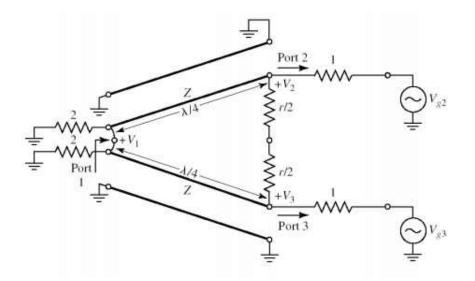

| FIGURE 9: THE WILKINSON POWER DIVIDER MODEL IN NORMALIZED AND SYMMETRIC FORM. [18]18                                                                   |

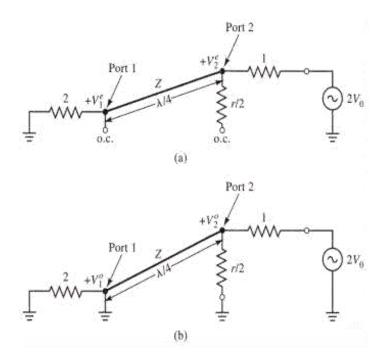

| FIGURE 10: BISECTION OF WILKINSON POWER DIVIDER: (A) EVEN-MODE EXCITATION, (B) ODD-MODE EXCITATION [17]                                                |

| FIGURE 11: ANALYSIS OF THE WILKINSON DIVIDER TO FIND S11: (A) TERMINATED WILKINSON DIVIDER, (B)<br>BISECTION OF THE CIRCUIT IN (A) [17]21              |

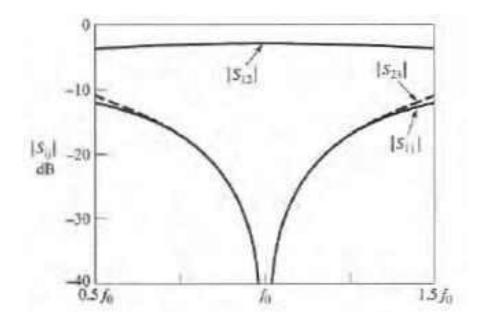

| FIGURE 12: POWER DIVIDER CHARACTERISTICS EXAMPLE [17]23                                                                                                |

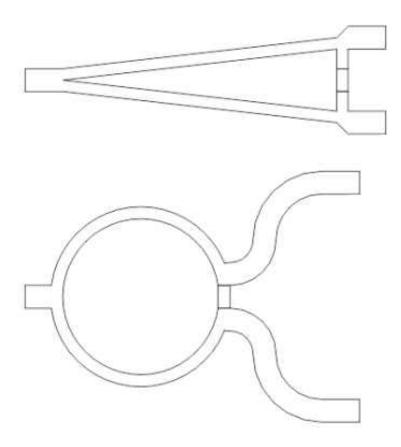

| FIGURE 13: STRAIGHT AND CIRCULAR WILKINSON POWER DIVIDER [15]24                                                                                        |

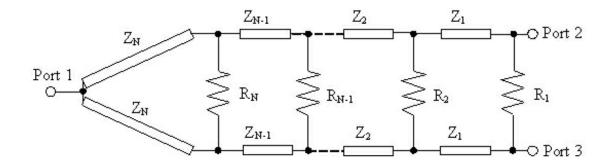

| FIGURE 14: MULTISTAGE WILKINSON POWER DIVIDER SCHEMATIC [13]25                                                                                         |

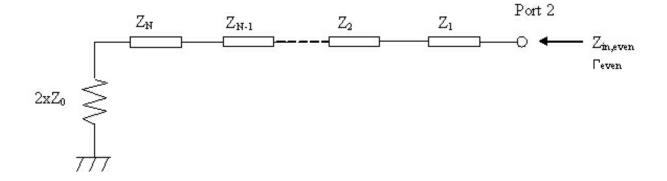

| FIGURE 15: EVEN MODE MULTISTAGE WILKINSON [13]25                                                                                                       |

| FIGURE 16: ODD MODE MULTISTAGE WILKINSON [13]26                                                                                                        |

| FIGURE 17: PHASED ARRAY BLOCK DIAGRAM [24]29                                                                                                           |

| FIGURE 18: PHASED ARRAY STEERING [25]                                                                                                                  |

| FIGURE 19: UND UASE SUPER HAULER PAYLOAD BAY                                                                                                           |

| FIGURE 20: UND UASE SUPER HAULER WING CROSS-SECTION [29]                                                                                               |

| FIGURE 21: WING POD FOR PHASED ARRAY SYSTEM                                                      | 35 |

|--------------------------------------------------------------------------------------------------|----|

| FIGURE 22: MALE TO MALE SMA CONNECTOR                                                            | 36 |

| FIGURE 23: AGILENT TECHNOLOGIES APPCAD [30]                                                      | 37 |

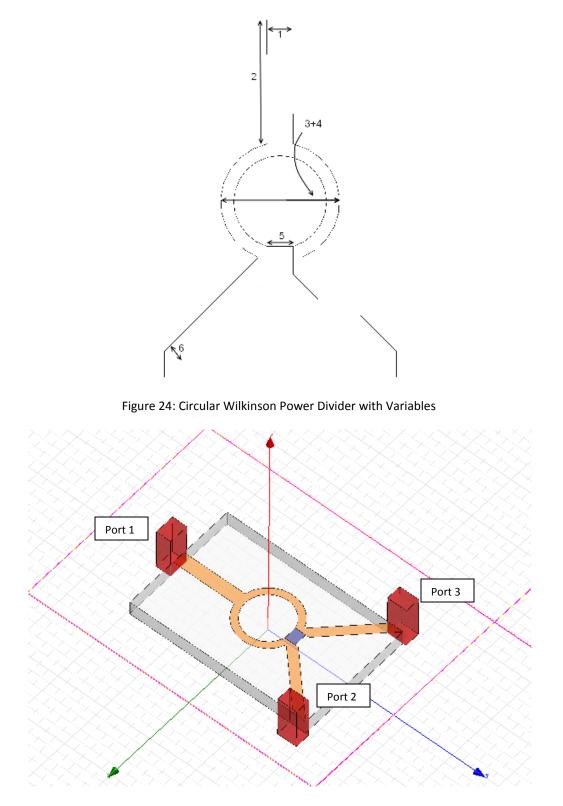

| FIGURE 24: CIRCULAR WILKINSON POWER DIVIDER WITH VARIABLES                                       | 39 |

| FIGURE 25: CIRCULAR SINGLE SPLIT WILKINSON                                                       | 39 |

| FIGURE 26: CIRCULAR SINGLE SPLIT WILKINSON RESULTS                                               | 40 |

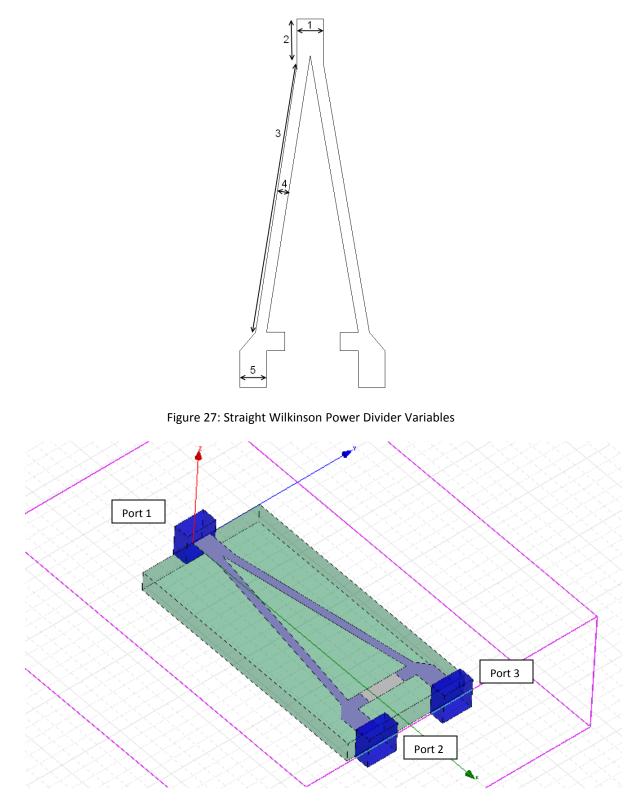

| FIGURE 27: STRAIGHT WILKINSON POWER DIVIDER VARIABLES                                            | 42 |

| FIGURE 28: STRAIGHT SINGLE SPLIT WILKINSON                                                       | 42 |

| FIGURE 29: STRAIGHT SINGLE SPLIT WILKINSON RESULTS                                               | 43 |

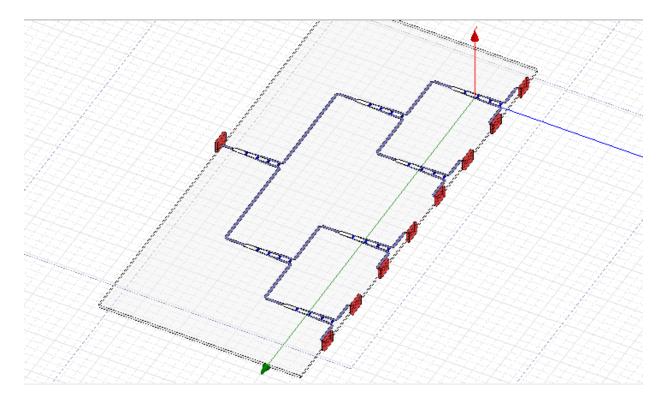

| FIGURE 30: MULTISECTION SINGLE SPLIT WILKINSON                                                   | 46 |

| FIGURE 31: MULTISECTION SINGLE SPLIT WILKINSON SIMULATION RESULTS                                | 47 |

| FIGURE 32: 20 GHZ FREQUENCY SWEEP MULTISTAGE WILKINSON POWER DIVIDER                             | 48 |

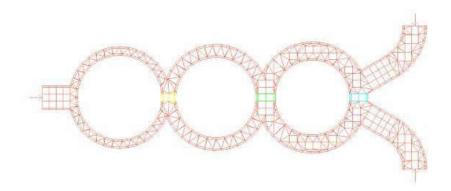

| FIGURE 33: MULTISTAGE 8-SPLIT WILKINSON POWER DIVIDER                                            | 49 |

| FIGURE 34: MULTISTAGE 8-WAY WILKINSON POWER DIVIDER SIMULATION RESULTS                           | 49 |

| FIGURE 35: LARGE FREQUENCY SWEEP 8-WAY WILKINSON POWER DIVIDER SIMULATION RESULTS                | 50 |

| FIGURE 36: EAGLE WILKINSON DESIGN                                                                | 52 |

| FIGURE 37: FINAL FABRICATED WILKINSON POWER DIVIDER                                              | 53 |

| FIGURE 38: VNA CALIBRATION SETUP WITH ZV-Z54                                                     | 55 |

| FIGURE 39: SMA-50Ω TERMINATOR                                                                    | 55 |

| FIGURE 40: AVERAGE REFLECTION COEFFICIENT OF NETWORK                                             | 56 |

| FIGURE 41: AVERAGE REFLECTION COEFFICIENT BANDWIDTH (TERMINATED PORTS)                           | 57 |

| FIGURE 42: WILKINSON POWER DIVIDER WITH VIVALDI ANTENNA TEST SET-UP                              | 58 |

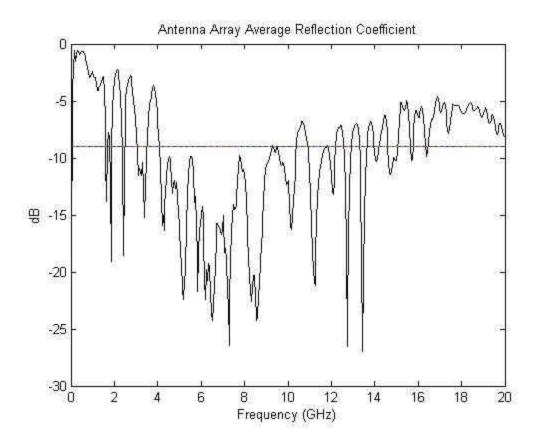

| FIGURE 43: AVERAGE REFLECTION COEFFICIENT FOR THE COMBINATION OF POWER DIVIDER AND ANTENNA ARRAY | 59 |

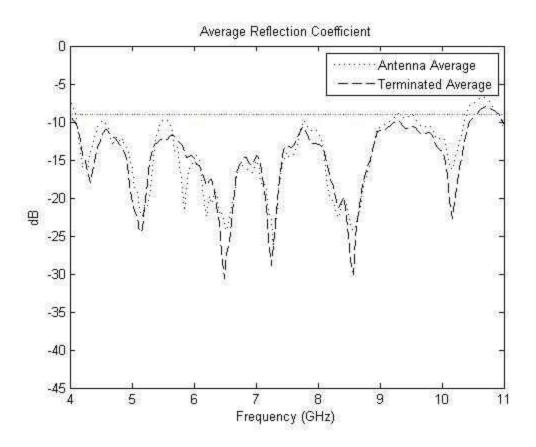

| FIGURE 44: TERMINATED AND ANTENNA ARRAY AVERAGE RETURN LOSS              | 60 |

|--------------------------------------------------------------------------|----|

| FIGURE 45: OUTPUT PORT 1 ISOLATION OPEN PORT                             | 61 |

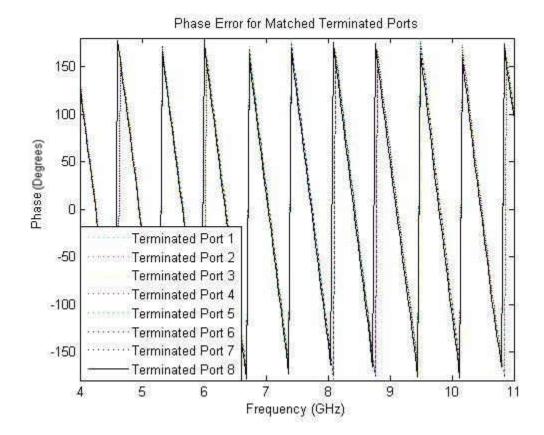

| FIGURE 46: PHASE ACROSS MATCHED TERMINATED OUTPUT PORTS                  | 63 |

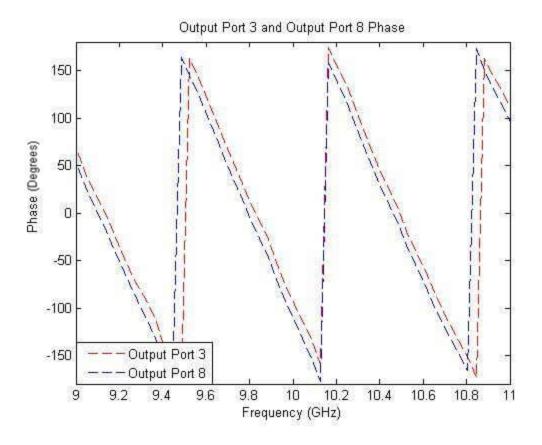

| FIGURE 47: PORT 3 AND 8 PHASE WITH MATCHED TERMINATOR                    | 64 |

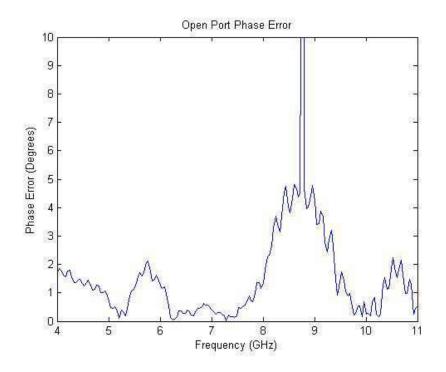

| FIGURE 48: OPEN PORT PHASE ERROR BETWEEN OUTPUT PORT 3 AND OUTPUT PORT 8 | 65 |

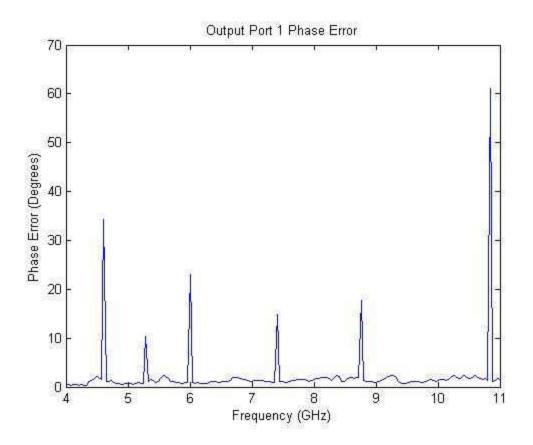

| FIGURE 49: OUTPUT PORT 1 AVERAGE PHASE ERROR                             | 66 |

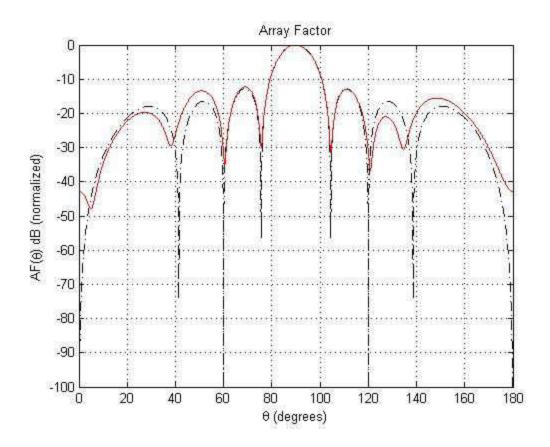

| FIGURE 50: 90 DEGREE RADIATION ARRAY FACTOR                              | 67 |

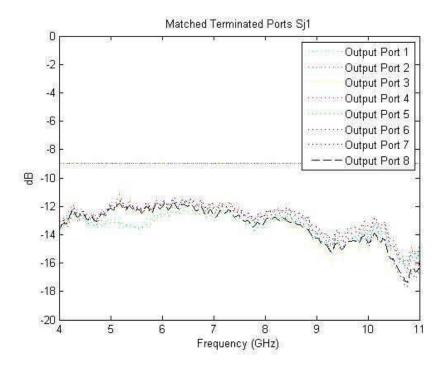

| FIGURE 51: MEASURED S21 BETWEEN INPUT AND BALANCED OUTPUT PORTS          | 68 |

| FIGURE 52: MEASURED S21 BETWEEN INPUT AND UNBALANCED OPEN OUTPUT PORTS   | 69 |

| FIGURE 53: MEAURED S21 BETWEEN INPUT AND UNBALANCED ANTENNA OUTPUT PORTS | 69 |

| FIGURE 54: MEASURED S21 AT OUTPUT PORT 1                                 | 70 |

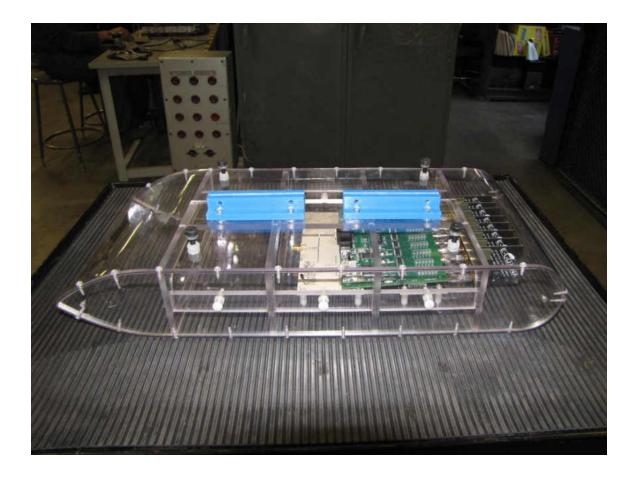

| FIGURE 55: 10 GHZ PHASED ARRAY SYSTEM WITHOUT CONTROL BOARD              | 71 |

| FIGURE 56: 10 GHZ PHASED ARRAY SYSTEM WITH CONTROL BOARD                 | 72 |

| FIGURE 57: PROPOSED MULTISTAGE CIRCULAR WILKINSON POWER DIVIDER [34]     | 75 |

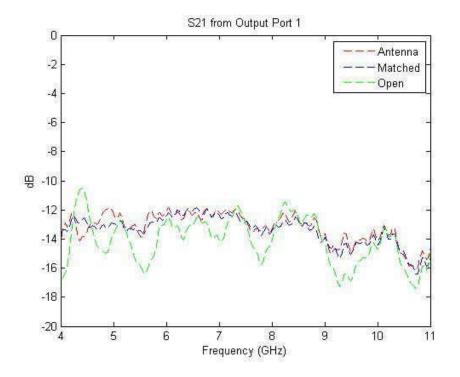

| FIGURE 58: S21 OUTPUT PORT 1                                             | 78 |

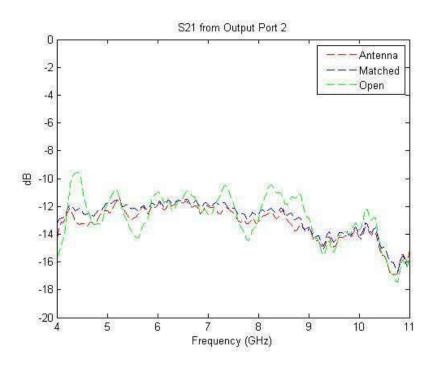

| FIGURE 59: S21 FROM OUTPUT PORT 2                                        | 79 |

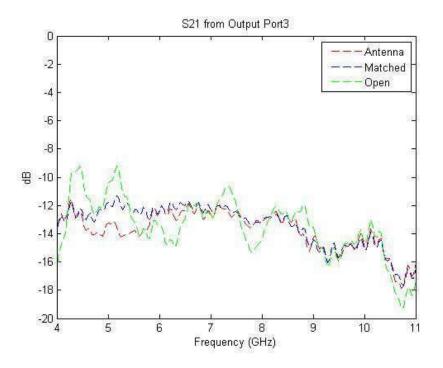

| FIGURE 60: S21 FROM OUTPUT PORT 3                                        | 79 |

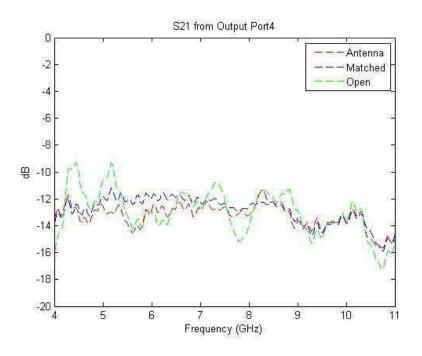

| FIGURE 61: S21 FROM OUTPUT PORT 4                                        | 80 |

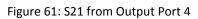

| FIGURE 62: S21 FROM OUTPUT PORT 5                                        | 80 |

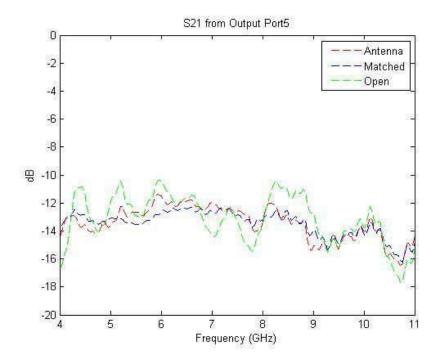

| FIGURE 63: S21 FROM OUTPUT PORT 6                                        | 81 |

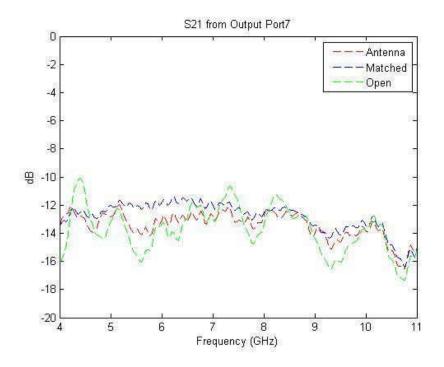

| FIGURE 64: S21 FROM OUTPUT PORT 7                                        | 81 |

| FIGURE 65: S21 FROM OUTPUT PORT 8                                        | 82 |

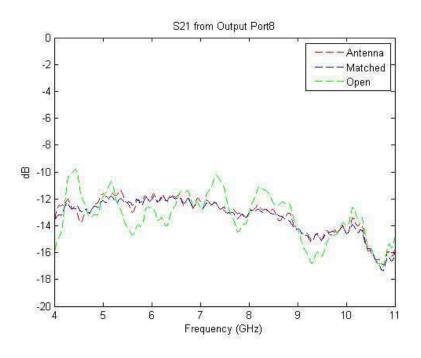

| FIGURE 66: ISOLATION BETWEEN PORT 1 AND OUTPUT PORTS                     | 83 |

| FIGURE 67: ISOLATION BETWEEN PORT 2 AND OUTPUT PORTS8 | 33             |

|-------------------------------------------------------|----------------|

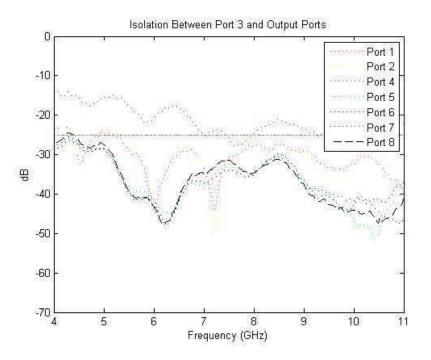

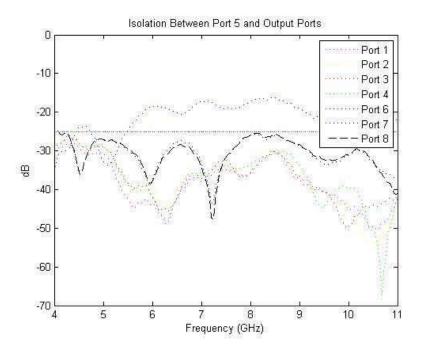

| FIGURE 68: ISOLATION BETWEEN PORT 3 AND OUTPUT PORTS8 | 34             |

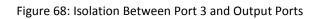

| FIGURE 69: ISOLATION BETWEEN PORT 4 AND OUTPUT PORTS8 | 34             |

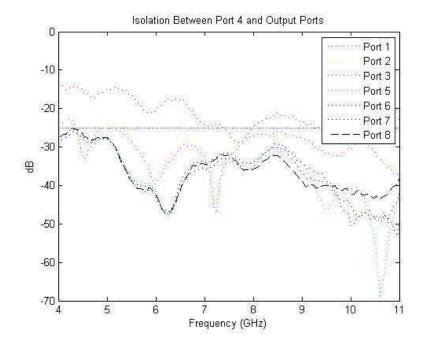

| FIGURE 70: ISOLATION BETWEEN PORT 5 AND OUTPUT PORTS8 | 35             |

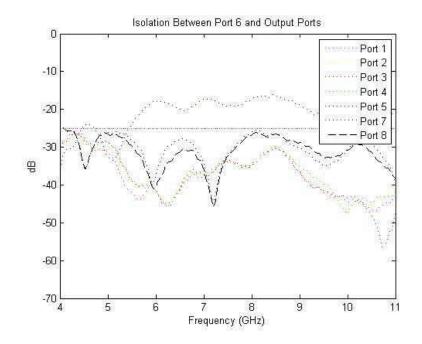

| FIGURE 71: ISOLATION BETWEEN PORT 6 AND OUTPUT PORTS8 | 35             |

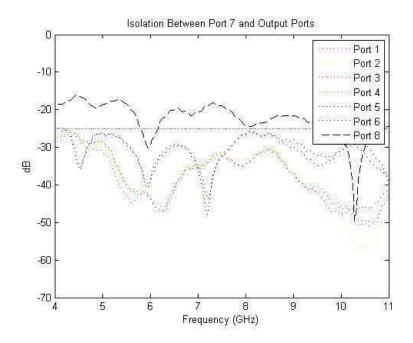

| FIGURE 72: ISOLATION BETWEEN PORT 7 AND OUTPUT PORTS8 | 36             |

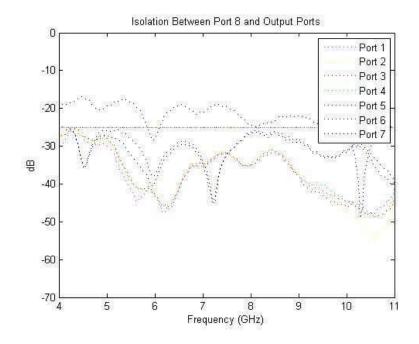

| FIGURE 73: ISOLATION BETWEEN PORT 8 AND OUTPUT PORTS8 | 36             |

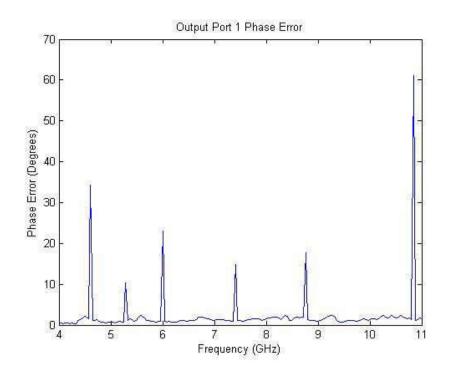

| FIGURE 74: OUTPUT PORT 1 PHASE ERROR8                 | 37             |

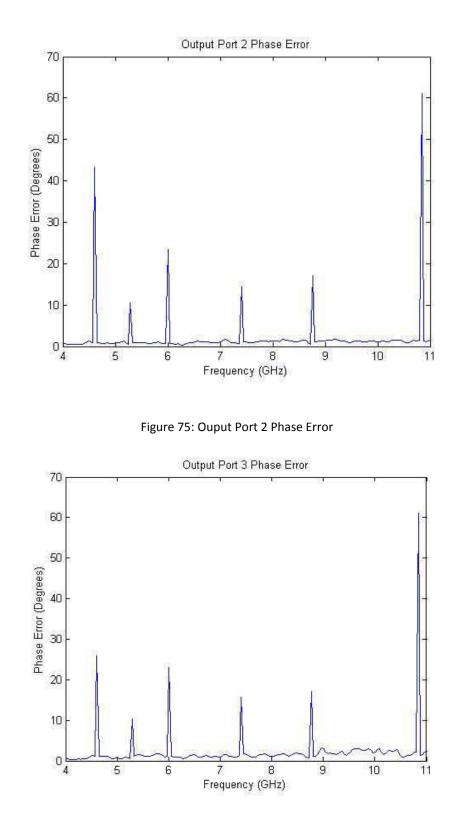

| FIGURE 75: OUPUT PORT 2 PHASE ERROR8                  | 38             |

| FIGURE 76: OUTPUT PORT 3 PHASE ERROR8                 | 38             |

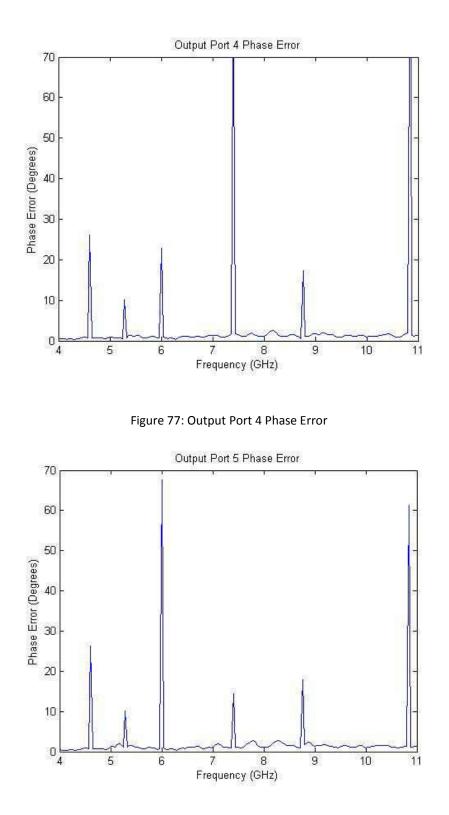

| FIGURE 77: OUTPUT PORT 4 PHASE ERROR8                 | 39             |

| FIGURE 78: OUTPUT PORT 5 PHASE ERROR8                 | 39             |

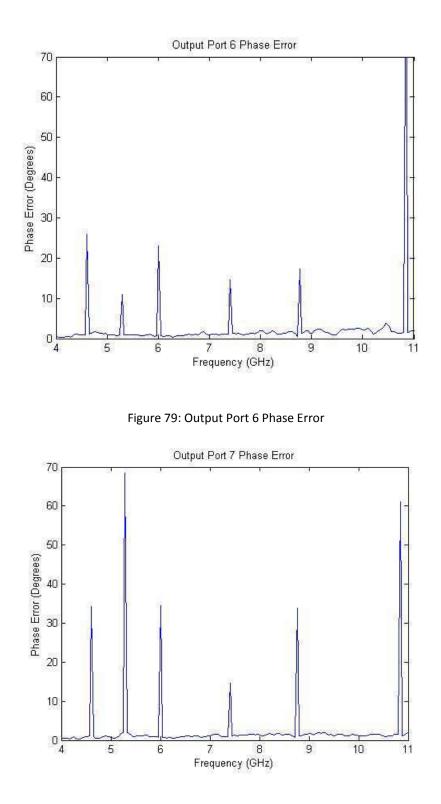

| FIGURE 79: OUTPUT PORT 6 PHASE ERROR9                 | <del>)</del> 0 |

| FIGURE 80: OUTPUT PORT 7 PHASE ERROR9                 | <del>)</del> 0 |

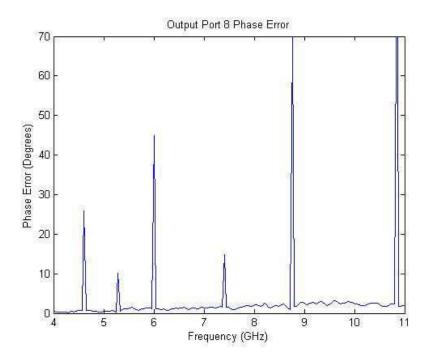

| FIGURE 81: OUTPUT PORT 8 PHASE ERROR9                 | €              |

# LIST OF TABLES

| TABLE 1: PASSIVE POWER DIVIDERS                             | 17 |

|-------------------------------------------------------------|----|

| TABLE 2: CIRCULAR SINGLE SPLIT VARIABLES                    | 38 |

| TABLE 3: STRAIGHT SINGLE SPLIT VARIABLES                    | 41 |

| TABLE 4: CIRCULAR AND STRAIGHT WILKINSON COMPARISON         | 44 |

| TABLE 5: MULTISTAGE POWER DIVIDER VALUES                    | 45 |

| TABLE 6: MULTISTAGE QUARTERWAVE TRANSFORMER'S LINE WIDTHS   | 45 |

| TABLE 7: MULTISTAGE 8-WAY POWER DIVIDER SIMULATION ANALYSIS | 51 |

| TABLE 8: COMPARISON OF MEASURED AND SIMULATED RESULTS       | 73 |

| TABLE 9: DESIGN REQUIREMENTS                                | 74 |

#### ACKNOWLEDGMENTS

I would like to thank the University of North Dakota for the opportunity to study for both his degrees at this institution. I would like to thank Dr. Noghanian, Dr. Salehfar, and Dr. Semke for working with me through my thesis and providing guidance for the past years in the research and school, particularly after the passing of the late Dr. Schultz, who encouraged me to pursue this degree. They provided the support in helping me complete this thesis. I would like to also thank my family and friends who have provided assistance and support throughout the research and writing of this thesis.

This work is dedicated to my mother and father who have always supported my endeavors and sacrificed themselves to provide me the opportunities to push myself to new limits. Throughout this research, they have been a constant support with a listening ear, sympathetic understanding, and encouraging words. I definitely would not have been able to do this without their support.

xii

#### ABSTRACT

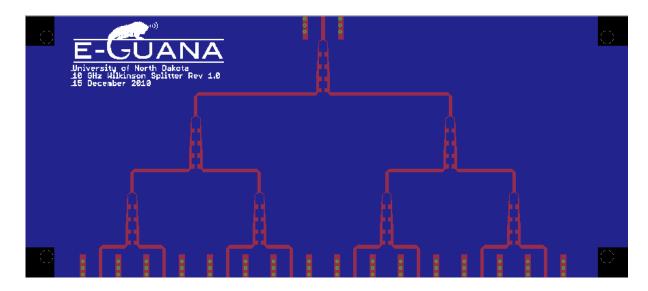

The purpose of this project is to design a wideband Wilkinson power divider as part of an active phased array radar system for use in Unmanned Aerial Vehicle (UAV) applications. In order to comply with the entire system, the power divider was restricted in size, operating frequency, and bandwidth. The proposed power divider was integrated into a 10 GHz phased array system for future development in a transmitting and receiving system.

The Wilkinson power divider was designed to provide 2 GHz bandwidth centered at 10 GHz. In order to provide the bandwidth, a 4-stage Wilkinson power divider was designed and fabricated. It was then tested thoroughly to provide Printed Circuit Board (PCB) characteristics for integration within the system. Port isolation, phase error, and PCB power losses were found for the power divider and recorded to provide better integration into the radar system. The experimental results compared well with the simulated models created in the design phase.

The final modularly designed phased array radar consisted of a Vivaldi antenna array, phase shifter and amplifier module, and control module. The focus of the work presented is the Wilkinson power divider that was designed to meet stringent design requirements for space, operating frequency, and phase error. The result is a fabricated Wilkinson power divider that met all the requirements and the module functions within the phased array system.

# CHAPTER 1

## INTRODUCTION

1.1 Unmanned Aircraft Systems' Barrier for Entry in the National Airspace System The commercialization of Unmanned Aircraft Systems (UAS) applications for use in the U.S. National Airspace System (NAS) are being stifled by the strict safety regulations imposed by the Federal Aviation Administration (FAA). These regulations are to provide safety in commercial airspace for both those in the air and on the ground. One of the primary concerns with Unmanned Aerial Vehicles (UAVs) is the communication between aircrafts and the procedure to avoid airborne collisions.

In addition to the communication and avoidance of other aircrafts, a noncooperative method is necessary to provide collision avoidance from non-responsive aircrafts, birds, gliders, power lines, buildings, hot air balloons, and any other type of airborne structure that would possibly not have the ability to properly communicate with the UAV. Until both cooperative and non-cooperative sense and avoid method can be integrated into UAVs, they will not be available for commercial use in the NAS.

# 1.2 Cooperative Sense and Avoid Using Automatic Dependent Surveillance-Broadcast

Research done at the University of North Dakota (UND) has produced a system that uses an Automatic Dependent Surveillance-Broadcast (ADS-B) for sense and avoid

[1]. The designed system uses the communication between different aircraft's ADS-B units to provide the UAV a procedure for proper FAA avoidance maneuvers.

While this system provides a UAV with proper FAA regulation collision avoidance techniques [2], it does not take into consideration old aircrafts or crop dusters that do not have ADS-B units on them. There are also other obstacles within the NAS that could prove to be harmful to the aircraft such as birds, power lines, etc. Because of these factors, it is necessary to complement a sense and avoid system such as UND's Unmanned Aircraft Systems Engineering (UASE) ADS-B payload with a non-cooperative sense and avoid application [3].

1.3 Phased Array Radar UAS for Non-Cooperative Sense and Avoidance

A potential solution for non-cooperative sense and avoid applications is a smallscale phased array radar for UAS platforms. Using multiple antennas in an array, the signal can be shifted using a phase shifter which will alter the antenna array radiation direction. The alterations in the array radiation can be controlled through the phase shifters to create a sweeping motion. This phased array antenna can be integrated into a radar [4].

These phased arrays radars have lower costs and smaller size as opposed to mechanically driven radar designs. Additionally, the deterioration of the mechanical radar system is decreased due to the reduction in moving parts. The phased array radar can provide a non-cooperative sense and avoid solution for UAVs that includes higher efficiency, lower costs, and a smaller size.

#### 1.4 Laserlith Corporation and Private Corporation Involvement

Laserlith Corporation instituted a program to create and manufacture Electronically Steered Antenna Arrays (ESAs) with the cooperation of the Army Research Laboratory and the Air Force Research Laboratory. The Wilkinson power divider of this research work was designed with the intention of integration with the Laserlith Corporation's phase shifters. These phase shifters utilize new MEMS technology designed by Laserlith that provides higher efficiency with lower power consumption. Laserlith's MEMS based phase shifters will provide a much quicker phase change which increases the radar's sweeping speed. Currently, these phase shifters have not been provided for integration and the system of this study uses commercial off-the-shelf hardware instead. The final goal is to have the Laserlith Corporation's phase shifters replacing the off-the-shelf mounted phase shifters in the full phased array radar of this research work.

#### 1.5 Prior Work

Previous work on this project has been done by others with the creation of a 2.4 GHz tracking array with printed dipole antennas and commercial off-the-shelf products. Research on tracking a video signal from an in-flight UAV payload provided a base concept for the design of our system [5]. Using this concept, a C-band 5.8 GHz tracking phased array has been developed and characterized. This system provided a proof of concept for phased array sense and avoid applications (Figure 1).

Figure 1: 5.8 GHz Phase Array Proof of Concept System

The phased array radar system when integrated into a small-scale Unmanned Aerial System (UAS) provides multiple commercial and military applications. Another proposed application is the tracking of targets located on the horizon. Would provide a method for self defense for ships against low altitude attacks [6]. In order to aid the radar's field of view on a Naval ship, a low power radar system can be placed on an inflight UAV. The aircraft could find low altitude targets that were out of the ship's mounted radar range. This tracking capability can be applied to multiple other applications within the commercial sector.

In addition to the previous Naval research, prior studies at the UASE program at UND in the area of sense and avoid technology also prompted the research and design of a non-cooperative sense and avoid platform [1]. A linear array was designed, manufactured, and integrated into UAV's wing structure with antenna elements [7]. This work led to the initial concept of creating a phased array sense and avoid system that is wing-mounted on the UND UASE Super Hauler (shown in Figure 2).

#### Figure 2: UND UASE Super Hauler

The Wilkinson power divider design of this thesis was intended to be eventually integrated into the phased array sense and avoid system. In coordination with the UASE program at UND, a small-scale payload system that operates at 10 GHz has been designed to perform tracking and radar applications. This system consists of a Radio Frequency (RF) source, a power divider, phase shifting module, amplifiers, and antenna elements [8]. Figure 3 displays the design for the 10 GHz phased array system. The system is comprised of four separate modules, the power divider board, amplification and phase shifter board, control board, and antenna array. This thesis focuses on the design of a 10 GHz Wilkinson power divider board with a 2 GHz bandwidth centered at 10 GHz. A power divider board with a wide bandwidth that integrates into the system is to be designed and fabricated. The board has multiple constraints for integration into the system. The size of the board along with the distance between each output port, the operating frequency bandwidth, and the power loss with the anticipated phase error are

critical to the design of the power divider module.

Figure 3: 10 GHz Phased Array Block Diagram

Work has been performed by D. Hajicek in creating a phased array control module and phase shifter with amplifier module [9]. Through digital phase shifting modules with a fixed number of phase shifting states, a simple control system was created to control the array steering performance. The quantization that comes with fixed states was lessened by using high resolution phase shifter. Therefore, a more precise control with the array steering was provided that reduced degradation of the phase control [10].

As shown in Figure 3, steering is achieved by the phase shifting module. This is the basic principle of a phase array system. The details of the design of a 10 GHz wideband Vivaldi antenna elements is provided by J. Alme [11].

#### 1.6 Review of Literature

Prior literature was reviewed to provide a better understanding of the research and to also ensure that this thesis was pertinent to research within the realm of Wilkinson power dividers. The papers covered efficacy and designs of Wilkinson power dividers. Many of the readings were on the Wilkinson design and potential design modifications.

E. Wilkinson first created the design of a power divider which was named after his work [12]. His findings offered a basic design for the N-way power divider. This design was modified by S. Cohn who provided a basic design for a multi-stage N-way power divider [13]. He was the first to propose using Chebyshev polynomials to roughly determine the size of the isolation resistors.

Recent research has been performed by J. Cooper who modeled multiple Wilkinson power dividers to create a complex reflection coefficient detector [14]. By using five Wilkinson power dividers, he was able to implement the detector on a much smaller scale. D. Harty also provides recent research within the design of Wilkinson power dividers. His work provides a novel design of a wideband Wilkinson power divider for a ribcage-dipole array [15].

Chapter 2 further explores the work of others in the design of power dividers specifically the Wilkinson power divider and its design methodology. The Wilkinson power divider provides large bandwidth to a system with multiple designs.

## 1.7 Work Performed

The tasks performed and discussed in this thesis are the design and testing of a wideband Wilkinson Power Divider for the X-band frequency. This module is integrated into a phased array system that is mounted on a small-scale UAV which is being operated by the UASE Laboratory at UND.

Chapter 2 provides the evolution of the power divider and the theory for designing a Wilkinson power divider. The methodology of designing the wideband Wilkinson power divider for UAV application is covered within Chapter 3. The results from simulation and testing are provided in Chapter 4. Chapter 5 presents the conclusions which will briefly sum up the research performed and covers the suggested future work on the project.

#### CHAPTER 2

## WILKINSON POWER DIVIDER PRINCIPLES

## 2.1. Introduction

The Wilkinson power divider is a variation of power dividers that uses a microstrip design and allows for the low loss division of a signal N-ways. This section with look into the evolution of the power divider into the Wilkinson design and will discuss the theory behind the design of the power divider.

#### 2.2. Definitions

Before further delving into power divider in general and the Wilkinson power divider in particular, several definitions should be expressed to avoid confusion. The scattering parameters, which is also called the S-parameters, describe the behavior of networks, such as dividers and couplers. S-parameters are provided in an  $M \times M$  matrix for an M-port network. A general description of a single S-parameter is given in Equation 2.1 where *i* is the row number and *j* is the column number.

$$S_{ij} = \frac{b_i}{a_j} \tag{2.1}$$

$b_i$  is the voltage leaving *i* port and  $a_j$  is the incident voltage at *j* port.

Throughout the theory, the reflection coefficient will be used in the evaluation of the power dividers. The reflection coefficient is commonly given as Equation 2.2

$$\Gamma = \frac{Z_L - Z_0}{Z_L + Z_0} \tag{2.2}$$

where  $Z_L$  is the load impedance and  $Z_0$  is the line characteristic impedance. The reflection coefficient is used to provide the anticipated reflection of the signal back towards the source from the load. When *i=j* in the S-parameters, the resulting parameter provides the reflection coefficient for the network.

Quarterwave impedance transformers are used in the design of the Wilkinson power divider and are a length of transmission line which is exactly a quarter of a wavelength long. In the design of the power divider, these types of impedance transformers were used. For the transformer, the impedance is found by Equation 2.3.

$$Z_T = \sqrt{(Z_i Z_L)}$$

,  $Z_i = \frac{Z_T^2}{Z_L}$  (2.3)

Where  $Z_T$  is the transformer line impedance,  $Z_i$  is the input impedance which is typically used as the characteristic impedance or  $Z_0$ , and  $Z_L$  is the load impedance.

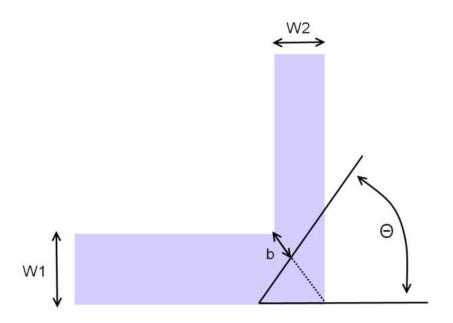

For a planar design, microstrip lines may be used to form a transformer. When designing a microstrip line, it is important to decrease the losses that sharp corners create. In order to perform this, the angles can be mitered or chamfered. Figure 4 provides a visual representation of how to calculate the required chamfer for the angle [16].

Figure 4: Mitering Right Angles

Using the variables found in Figure 4, Equations 2.4 - 2.5 will provide the values needed to successfully chamfer the angle and reduce losses.

$$\theta = \tan^{-1}(\frac{W_1}{W_2}) \tag{2.4}$$

$$b = 0.4\sqrt{(W_1^2 + W_2^2)}$$

(2.5)

Where *W* is the width of each microstrip line entering the right angle. Figure 4 shows which width is attributed to which transmission line.

# 2.3. Power Divider History

Power dividers were first discovered in the Massachusetts Institute of Technology (MIT) Radiation Laboratory back in the 1940s. During several experiments, waveguide couplers and power dividers were characterized and invented [17]. The T-

junction power divider from the research of this thesis provides a power division for a 3-

port network. This 3-port design can be repeated multiple times to provide an N-way division.

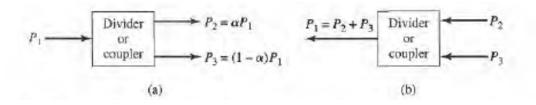

The T-junction power divider is a simple three-port network typically with two outputs and one input, but the reverse can be also be applied for power combining. Figure 5 provides a visual representation of power division and combination [18].

Figure 5: Basic Concept for (a) Power division, (b) Power Combining [18]

$\alpha$  is the ratio of the first output power to input power. The equation representation of the  $\alpha$  parameter in Figure 5 is given in Equation 2.6.

$$\alpha = \frac{P_3}{P_1} \tag{2.6}$$

The scattering matrix for this 3-port network has nine independent elements (Equation 2.7):

$$[S] = \begin{bmatrix} S_{11}S_{12}S_{13} \\ S_{21}S_{22}S_{23} \\ S_{31}S_{32}S_{33} \end{bmatrix}$$

(2.7)

Ideally, a power divider would be lossless, reciprocal, and matched at all ports. In order to create a lossless three-port with no anisotropic materials, the scattering matrix must be not only unitary and reciprocal but also symmetric which would provide the following matrix (Equation 2.8) [19].

$$[S] = \begin{bmatrix} 0 & S_{12}S_{13} \\ S_{12} & 0 & S_{23} \\ S_{13}S_{23} & 0 \end{bmatrix}$$

(2.8)

The matrix should meet the following conditions (Unitary):

$$\sum_{k=1}^{N} S_{ki} S_{kj}^{*} = 1, \quad \text{for } i = j$$

(2.9)

$$\sum_{k=1}^{N} S_{ki} S_{kj}^{*} = 0, \text{ for } i \neq j$$

(2.10)

If these conditions are expanded with the reciprocal matrix shown in Equation 2.7, the following conditions are created (Equations 2.11-2.16):

$$|S_{12}|^2 + |S_{13}|^2 = 1 (2.11)$$

$$|S_{12}|^2 + |S_{23}|^2 = 1 (2.12)$$

$$|S_{13}|^2 + |S_{23}|^2 = 1 (2.13)$$

$$S_{13}^* S_{23} = 0 \tag{2.14}$$

$$S_{23}^* S_{12} = 0 \tag{2.15}$$

$$S_{12}^* S_{13} = 0 (2.16)$$

where  $|S_{ij}|$  is the magnitude of  $S_{ij}$ . Analyzing these conditions, there is a direct conflict between the equations. In order to satisfy Equations 2.14-2.16, there must be at least two zero valued parameters which would conflict with Equations 2.11-2.13. Thus, it is apparent that it is impossible to make a lossless and reciprocal 3-port network that is matched at all ports. However, if one of these conditions is neglected, then the other two can be met [18].

Because of this compromise, there are three commonly used passive three-port power dividers: the T-junction, resistive, and Wilkinson dividers. Each design brings a specific compromise which in turn provides distinct advantages and disadvantages to each.

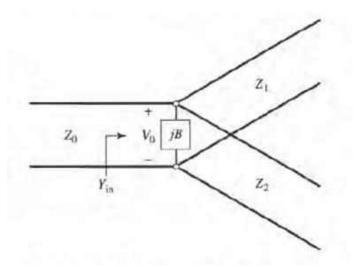

The T-junction is a versatile yet simple three-port power divider. Sacrificing matching, this network provides a lossless system aside from transmission line loss. Figure 6 provides a transmission line model of the T-junction.

Figure 6: Transmission Line Model of T-Junction Divider [18]

Stored energy from fringing fields and discontinuity at higher order modes at the junction create stored energy or lumped susceptance, *B*, which is the imaginary part of the admittance.

The resistive power divider provides the ability to match all the ports while sacrifices isolation and uses lossy lumped-element resistors. Figure 7 displays a resistive power divider that uses lumped-element resistors.

Figure 7: Resistive Power Divider [19]

The input power into the divider is given in Equation 2.17. Additionally, the output power are equal and given in Equation 2.18.

$$P_{in} = \frac{1}{2} \frac{V_1^2}{Z_0} \tag{2.17}$$

$$P_2 = P_3 = \frac{1}{2} \frac{\left(\frac{V_1}{2}\right)^2}{Z_0} = \frac{1}{8} \frac{V_1^2}{Z_0} = \frac{1}{4} P_{in}$$

(2.18)

where  $V_1$  is the voltage at port 1. This equation shows that the two output powers are a quarter of the input power and have dissipated the input power by half. This is a large loss of power through the network and is a large disadvantage of the resistive power dividers [18].

The final passive three-port power divider is the Wilkinson power divider. Discovered in 1960 by Ernest Wilkinson, the Wilkinson power divider is treated as a lossless network that uses a resistor to match the ports [12]. It uses quarter-wavelength transformers to match the output ports to the input port. Figure 8 shows a Wilkinson power divider in microstrip form and its transmission line model where  $Z_0$  is the characteristic impedance.

Figure 8: The Wilkinson Power Divider: (a) An Equal-Split Wilkinson Power Divider in Microstrip Form, (b) Equivalent Transmission Line Circuit [18].

When the network is matched at all ports, the Wilkinson divider has all three network characteristics: low loss, reciprocal, and matched. It is impossible to achieve all three characteristics but the Wilkinson power divider uses lossless quarterwave impedance transformers and each division has an inherent -3dB loss, due to dividing the power by a factor of 2. The Wilkinson power divider is lossless when the output ports are matched and balanced but when there is a reflected wave, the Wilkinson will have lossy characteristics. Because of this, the Wilkinson power divider provides the best results for passive power dividers. The following table provides a brief summary of the three passive power dividers.

Table 1: Passive power dividers

| Power Divider | Lossless                         | Matched Ports | Reciprocal |

|---------------|----------------------------------|---------------|------------|

| T-junction    | Yes                              | No            | Yes        |

| Resistive     | No                               | Yes           | Yes        |

| Wilkinson     | Lossy only for reflected<br>wave | Yes           | Yes        |

## 2.4. Design Procedure

The Wilkinson power divider's lossless quarterwave impedance transformers have a characteristic impedance of  $\sqrt{2}Z_0$  to match the ports and a lumped resistor of  $2Z_0$  to assist with isolation. These attributes allow for a high isolation between the two output ports [12].

In order to analyze the S-parameter matrix for the Wilkinson power divider, the even-odd mode analysis must be performed [18]. Using superposition, the network can be split into two symmetrical modes, even and odd. The transmission line model of the network is normalized to the character impedance,  $Z_0$ . The circuit is as shown in the Figure 9.

Figure 9: The Wilkinson Power Divider Model in Normalized and Symmetric Form. [18] In order to provide symmetry the single input resistor whose value is 1 after normalization is split into two parallel resistors which have the value of 2. Additionally, the quarterwave transformer normalized impedance is *Z* and the normalized resistor value is *r* as shown in Figure 9.

The even and odd modes are defined as (Figure 9):

$$V_{g2}^e = V_{g3}^e = 2V_0$$

, for even mode (2.19)

$$V_{q2}^o = -V_{q3}^o = 2V_0$$

, for odd mode (2.20)

Using superposition, it is found that  $V_{g2} = V_{g2}^0 + V_{g2}^e = 4V_0$  and  $V_{g3} = 0$ . Taking these two values the S parameters can be derived. Because of the short circuit at Port 1, current does not flow between the parallel resistors. The circuit can then be split and treated as two separate modes, even and odd [18].

Figure 10: Bisection of Wilkinson Power Divider: (a) Even-Mode Excitation, (b) Odd-Mode Excitation [17]. Looking toward the ground from Port 2 in Figure 10a and applying the values  $Z_L = 2$  and  $Z_T = Z$  into Equation 2.3, the even-mode has an input impedance of

$$Z_{in}^e = \frac{Z^2}{2}$$

(2.21)

where  $Z_{in}^e$  is equal to 1 for matched condition. The ports are matched when the normalized line impedance, Z in Equation 2.21, is equal to  $\sqrt{2}$  and thus  $Z_{in}^e$  becomes equal to 1. The transmission line voltage for the network is found to be:

$$V(x) = V^{+}(e^{-j\beta x} + \Gamma e^{j\beta x})$$

(2.22)

where  $\Gamma$  is the reflection coefficient and  $\beta$  is the phase constant and is equal to  $\frac{2\pi}{\lambda}$  for lossless line. Assuming x = 0 at port 1 and  $x = -\lambda/4$  at port 2 where  $\lambda$  is the wavelength of the transmission line, the port voltages are found to be, where  $\beta x = \frac{2\pi}{\lambda} \frac{\lambda}{4} = \frac{\pi}{2}$ :

$$V_2^e = V\left(-\frac{\lambda}{4}\right) = jV^+(1-\Gamma) = V_0$$

(2.23)

$$V_1^e = V(0) = V^+(1+\Gamma) = jV_0 \frac{\Gamma+1}{\Gamma-1}$$

(2.24)

The reflection coefficient is observed at Port 1 in Figure 10a. The values found for  $Z_0$ and  $Z_L$  are substituted into Equation 2.2 which gives the reflection coefficient as:

$$\Gamma = \frac{2-\sqrt{2}}{2+\sqrt{2}} \tag{2.25}$$

Thus

$$V_1^e = -jV_0\sqrt{2} (2.26)$$

The odd-mode shown in Figure 10b has an input impedance of

$$Z_{in} = \frac{1}{2} \left(\sqrt{2}\right)^2 = 1 \tag{2.27}$$

when matched. The voltages of the odd-mode branch are  $V_2^o = V_0$  and  $V_1^o = 0$ .

Figure 11a is the resulting circuit when Port 2 and 3 are matched. Looking at the circuit, it is noted that  $V_2^0 = V_3^0$  thus there will be no current flow through the normalized resistor therefore it can be removed as shown in Figure 11b. The input impedance at Port 1 can now be found as

$$Z_{in}^0 = \frac{(\sqrt{2})^2}{2} = 1 \tag{2.28}$$

Figure 11: Analysis of the Wilkinson Divider To Find S11: (a) Terminated Wilkinson Divider, (b) Bisection of the Circuit in (a) [17].

Taking the results found through the even-odd mode analysis, the following S parameters can be derived.

$$S_{11} = 0$$

(2.29)

$$S_{22} = S_{33} = 0 \tag{2.30}$$

$$S_{12} = S_{21} = \frac{v_1^e + v_1^o}{v_2^e + v_2^o} = -j/\sqrt{2}$$

(2.31)

$$S_{13} = S_{31} = -j/\sqrt{2} \tag{2.32}$$

$$S_{23} = S_{32} = 0 \tag{2.33}$$

These parameters explain the nature of the Wilkinson power divider. When the network is driven by port 1 with the ports matched, the resistor does not dissipate any power, thus the network is a lossless network. The resistor only dissipates reflected power from ports 2 and 3 [17]. The resulting S-parameter matrix is given as:

$$[S] = -\frac{j}{\sqrt{2}} \begin{bmatrix} 0 & 1 & 1\\ 1 & 0 & 0\\ 1 & 0 & 0 \end{bmatrix}$$

(2.34)

# 2.5. Coupling and Isolation

The Wilkinson power divider has multiple measurement parameter values that help quantify the efficiency of the network. Equations 2.35-2.37 give the return loss at Input Port 1 and Output Port 2 ( $RL_1[dB]$  and  $RL_2[dB]$ ), coupling between Ports 1 and 2 ( $CP_{12}[dB]$ ), and the isolation between Ports 2 and 3 ( $IL_{23}[dB]$ ), respectively [15][20].

$$RL_1[dB] = -20 \log |S_{11}|$$

,  $RL_2[dB] = -20 \log |S_{22}|$  (2.35)

$$CP_{12}[dB] = -20 \log|S_{12}| \tag{2.36}$$

$$IL_{23}[dB] = -20 \log|S_{23}| \tag{2.37}$$

It is important to note that the return loss is the absolute dB measurement of the reflection coefficient since  $\Gamma = S_{11} = S_{22}$ . These measurements are typically determined through simulation or testing of a power divider on a vector network analyzer. Using a simulator, an example of a graphical representation of these measurements are shown in the Figure 12.

Figure 12: Power Divider Characteristics Example [17]

In Figure 12, the characteristics of the power divider are shown in dB scale. Each line is identified and is measured across an operating frequency,  $f_0$ . The coupling between Ports 1 and 2,  $S_{12}$ , is close to -3 dB which is the inherent power loss with each division. Additionally, the return loss and the isolation between the output ports, have a drop at the operating frequency.

### 2.6. Straight Split and Circular Split

Single stage planar Wilkinson power dividers have two commonly used designs: straight split and circular split designs (Figure 13). The circular Wilkinson power divider is smaller in size than the straight Wilkinson power divider. In Chapter 3 a sample design of both single stage, single split models will be given and the simulated results will be discussed [21].

Figure 13: Straight and Circular Wilkinson Power Divider [15]

### 2.7. Multistage Wilkinson Power Divider

Adding multiple stages of quarter wavelength transformers within the network allows for a larger bandwidth of operation. The bandwidth can be increased to include over a decade of frequency which allows for a wide use of components [22]. In order to design a multistage Wilkinson, the even-odd method is again utilized but instead of a single stage, multiple stages are observed [13].

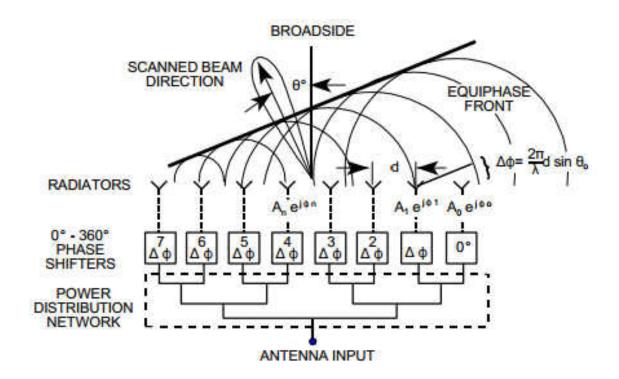

A general schematic for an N-stage Wilkinson power divider is given in Figure 14.

Figure 14: Multistage Wilkinson Power Divider Schematic [13]

As with the single stage divider, the even mode is created by assuming that Ports 2 and 3 are in-phase thus negating the voltage across the isolation resistors which allows for the resistors to be ignored. The odd mode has the excitations 180° out of phase and a virtual ground is placed across the axis of symmetry. The even and odd segments for analysis are as follows respectively:

Figure 15: Even Mode Multistage Wilkinson [13]

Figure 16: Odd Mode Multistage Wilkinson [13]

Note that in the odd mode, the resistors are halved.

From the even-odd mode, the reflection coefficients can be calculated, but first the impedance from the input must be defined using the transformer equation [23]. For a lossless case and looking towards the ground from Port 2, the input impedance is found as:

$$Z_{in} = \frac{Z_L + jZ_0 \tan(\beta l)}{Z_0 + jZ_L \tan(\beta l)}$$

(2.38)

where  $Z_{in}$  is the input impedance,  $Z_L$  is the inductive impedance,  $Z_0$  is the line impedance, l is the length, and  $\beta$  is the phase constant.

Using Equation 2.2, the reflection coefficient for port 1,  $S_{11}$ , is found to be the same as the even-mode reflection coefficient while the reflection coefficients for ports 2 and 3,  $S_{22}$  and  $S_{33}$  respectively, are averaged between the even and odd mode reflection coefficients [13].

$$\Gamma_2 = \Gamma_3 = \frac{(\Gamma_{even} + \Gamma_{odd})}{2}$$

(2.39)

If it is assumed that the network is lossless to provide ease of design before optimization, the transmission coefficient between the input port and the output ports can be calculated using the reflection coefficients. The isolation between the output ports is half of the difference between the two modes' reflection coefficients.

$$|t_{21}| = |t_{31}| = \sqrt{\frac{1}{2}(1 - \Gamma_e)^2}$$

(2.40)

$$t_{23} = \frac{(\Gamma_{even} - \Gamma_{odd})}{2} \tag{2.41}$$

where *t* is the transmission coefficient with the subscripts representing the network ports.

The input reflection coefficient was solved using Chebyshev polynomials. The coefficient is not a function of the isolation resistors which means that it is a function of line impedances [23].

#### 2.8. Design Considerations

There are several considerations that were necessary to contemplate while looking into the design of the power divider. The system that was being integrated into required the divider to operate over 10 GHz. Additionally, the system was to be utilized by UAVs which requires size constraints to be considered during the modeling.

The X-band was chosen as an operating frequency. There were three main reasons the X-band was chosen. First, the previous system modules were designed for this band. Secondly, commercial off-the-shelf phase shifters were most readily available within this frequency band. Lastly, the X-band frequency provides an inherent small form-factor that the wavelengths can accommodate.

Working at a high frequency brought several other considerations that were necessary during development. The selection of the substrate material was critical to the successful operation of the system. Further discussions on the design considerations will be in Chapter 3.

# 2.9. The System Overview

The phased array radar system consists of several modules that must be integrated successfully together. This requires understanding of their operation at the design stage and careful calibration at the implementation stage. The system consists of a power divider, phase shifter module, control PCB, and a Vivaldi antenna array. This system must be small enough to easily fit into the UASE Super Hauler. The following section discusses the phased array radar principles.

#### 2.10. Phase Array Radar Principles

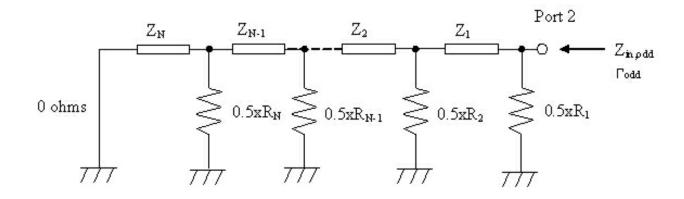

In a phased array system a signal is generated at the system's operating frequency. This frequency goes through a power divider to provide N number outputs that match the number of array elements. After the division, the signals are sent through a transmit module. The module delays each signal which in principle "phase shifts" the signals. After the phase shift, the signal is amplified then sent to the array of antennas. The following figure provides a general overview of the process.

28

Figure 17: Phased Array Block Diagram [24]

The phased array radar system should also receive the back scatter signals from objects of interest. Figure 17 shows the transmitting section of the phased array antenna system. A receiving module and data processing component need to be integrated into the entire system to create fully functional phased array radar.

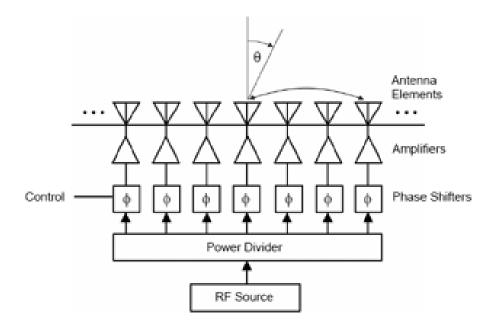

Figure 18 further details the antenna array radiation pattern when phase shifters are utilized.

Figure 18: Phased Array Steering [25]

In Figure 18, the broadside angle is at  $\theta = 0$  and scanned beam is at  $\theta = \theta_0$ . If the antennas in the array are equally spaced and their pointing radiation patter are to the same direction, the following equations can be used to calculate the steering angle ( $\Theta_0$ ) and differential phase shift ( $\Delta \varphi$ ), respectively:

$$\Theta_0 = \sin^{-1}(\frac{\Delta\varphi\lambda}{2\pi d}) = \sin^{-1}(\frac{\Delta\varphi}{\beta d})$$

(2.40)

$$\Delta \varphi = \frac{2\pi}{\lambda} \cdot \sin(\Theta_0) \tag{2.41}$$

In which  $\lambda$  is the operating frequency, *d* is the distance between each antenna element,  $\Theta_0$  is the steering angle, and  $\Delta \varphi$  is the differential phase shift for a uniform array of isotropic elements. The achievable scan angle can be found as a function of the differential phase shift if the operating frequency is constant [27]. The proposed system is using digital phase shifters which allow for a rapid state change in the phase shifters, thus providing quick scanning capabilities. Because of the speed of scanning capability, phase array systems are an extremely viable design for radar applications.

### CHAPTER 3

#### METHODOLOGY

### 3.1. Phased Array Radar Requirements

As mentioned in Chapter 2, the system was designed to operate at 10 GHz or the X-band frequency with a bandwidth of 2 GHz. Working at a high frequency poses several design constraints that have to be taken into account, specifically the choice of a substrate material. Thick substrates with a low dielectric constant are the ideal choice because they are more efficient, but the disadvantage is that the wavelength is larger for low permittivity substrate. Because of this disadvantage, substrates with a high dielectric constant are preferred when size is limited [17][27]. The substrate that was chosen for the Wilkinson power divider was Rogers RT/duroid 6006/6010LM [28]. The high dielectric constant of 10.2 of this substrate provided the ability to shrink the circuit size with a low loss tangent of 0.0023 at 10 GHz. These two factors provide a good substrate material to create a power divider with small dimensions.

The size of the system must be small enough to easily integrate into the UAV. Originally, the system was required to fit inside the payload cavity of the UND UASE's Super Hauler. The bay is approximately 21" x 11" x 12" and can carry approximately 30 pounds.

32

Figure 19 shows the payload bay with a payload attached at the bottom through quarter-turn locks.

Figure 19: UND UASE Super Hauler Payload Bay

Since it was not possible to scan the beam to angles in front of the airplane without interference with the fuselage and engine, one solution was dropping the system lower than the plane but this risks damaging the system on take off and landings. A better solution was to place the system inside the wing ribs. This caused more restrictions on the size. The cross-section of the wing provided approximately two inches in the thicker section of the wing and around six inches between each rib. The system can be connected with cables that run through the unused hole in the ribs. Figure 20 shows the wing cross-section with the available space.

Figure 20: UND UASE Super Hauler Wing Cross-Section [29]

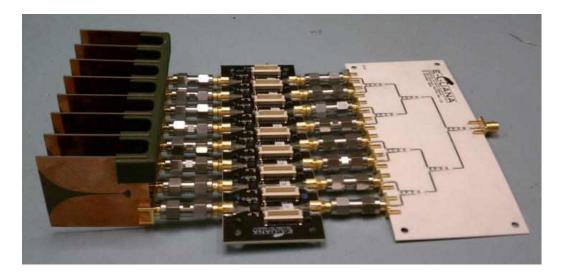

Modifying the wing embedded system; the final system design included a wing mounted pod that would hangs below the wing. The system would still will be attached by cables that are dispersed through the unused hole in the wing's rib but it has less restricted forward looking orientation through the pod. The dimensions of the pod are slightly larger than the wing and the system was designed with the size constraints within the wing, thus it provided ease of transition to the pod design (Figure 21).

Figure 21: Wing Pod for Phased Array System

# 3.2. Power Divider Requirements

The desired power divider for integration into the phased array system needs a bandwidth of 2 GHz that is centered at 10 GHz. A single signal needs to be received and a balanced, in-phase 8-way output needs to be produced.

In order to reduce losses of the system and still keep it modular, the Wilkinson power divider must have the ability to directly connect to the phase shifter board. This required the exact spacing of the output ports at a half wave of the operating frequency, or 590 mils. Eight female SMA connectors on the power divider must align perfectly with the eight female connectors on the phase shifter board. A Federal Custom Cable component with male SMA connectors on both sides and a machined metal sleeve in between them were used to connect the two boards (Figure 22). A torque wrench is used to tighten the connectors to exactly 8 in/lb.

Figure 22: Male to Male SMA Connector

The board width was less than six inches with this design requirement which fits into the size constraints placed on the system by the pod. Additionally, because the operating frequency was high the components had a small size and the entire board was less than half an inch in height.

#### 3.3. Wilkinson Power Divider Variables

The Wilkinson power dividers were designed based on the theory discussed in Chapter 2. Using Equations 2.21 – 2.30, values for each quarterwave impedance transformer were calculated. Agilent Technologies' AppCAD software (Figure 23) was used to find the dimensions of the microstrip [30]. These were used to create a model of the power divider in Ansoft's HFSS software [31]. This software is uses a full-wave analysis to simulate the microwave components taking into account the characteristics of the substrate material such as the dielectric constant and the thickness of the substrate.

| AppCAD - [Microstrip]<br>File Calculate Select Parameters Options Help |                                         |

|------------------------------------------------------------------------|-----------------------------------------|

|                                                                        | Main Menu [F8]                          |

| Microstrip                                                             |                                         |

| $W \rightarrow 24$                                                     | Calculate Z0 [F4]                       |

|                                                                        | 20 = <b>55.51</b> Ω                     |

| 1925                                                                   | Elect Length = $0.282$ $\lambda$        |

| Dielectric: ≅r = 10.2                                                  | Elect Length = 101.7 degrees            |

| RT/duroid 🐵 6010                                                       | 1.0 Wavelength = 442.581 mil            |

|                                                                        | Vp = 0.375 fraction of c                |

| Frequency: 10 GHz 💌                                                    | ≊eff = 7.112<br>W/H = 0.768             |

| Length Units: mils                                                     | W/H = 0.700                             |

|                                                                        |                                         |

|                                                                        |                                         |

| Normal Click for Web: APPLICATION NOTES - MODELS - D                   | ESIGN TIPS - DATA SHEETS - S-PARAMETERS |

Figure 23: Agilent Technologies AppCAD [30]

Upon designing the multistage Wilkinson power divider, Chevyshev polynomials [17] were used to find the isolation resistors values and the impedance necessary for the quarterwave transformers. These values were imput into the AppCAD software which provided the dimensions for each stage of the transformers. These were then used for setting up a simulation modeled in HFSS.

# 3.4. Simulation Results

Simulations were performed in Ansoft's HFSS [31]. The power dividers were created on a 31.25 mil Rogers 6010 substrate. A microstrip line was designed given a

Perfect E characteristic which means that the E-field is normal to the selected plane. An infinite ground was considered. An analysis was done at 10 GHz operating frequency with a fast mode frequency sweep across 5-15 GHz to provide extra data beyond the required 2 GHz for analysis. This provided further information on the network's frequency bandwidth.

A circular single split Wilkinson power divider is modeled with the widths and lengths calculated through AppCad software. The width and length results were recorded as variables for the model. By creating variables, the model could easily be modified without having to completely redefine the model. Table 2 provides the values for each dimension as shown in Figure 24.

| In_strip_width (1)      | 27.5 mil |

|-------------------------|----------|

| In_strip_legnth (2)     | 138 mil  |

| Circle_strip_length (3) | 113 mil  |

| Circle_strip_width (4)  | 14 mil   |

| Circle_slot_width (5)   | 27.5 mil |

| Out_strip_width (6)     | 27.5 mil |

Table 2: Circular Single Split Variables

Taking these variables, a model was created within the HFSS simulating software. Figure 24 shows how each variables are used in the creation of the model. The numbers next each variable in Table 2 can be found in Figure 24. The entire model is shown in Figure 25.

Figure 25: Circular Single Split Wilkinson

Figure 25 shows the substrate, the designed microstrip Wilkinson power divider, the isolator resistor is the gray box, the three boxes that represent port locations, and is surrounded by a box that imitates network surrounding air shown in Figure 25. The Cartesian coordinates are the three arrows pointing out from the center of the figure.

The circular single split was then tested across the desired frequency spectrum to find the return loss and power loss. The results are depicted in Figure 26.

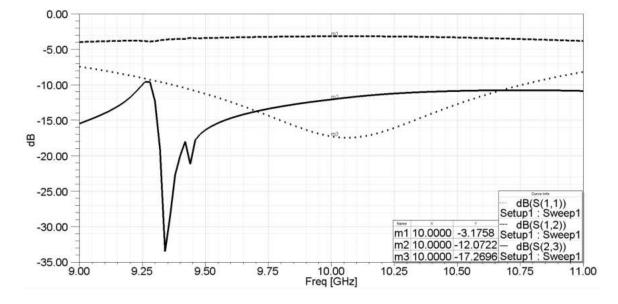

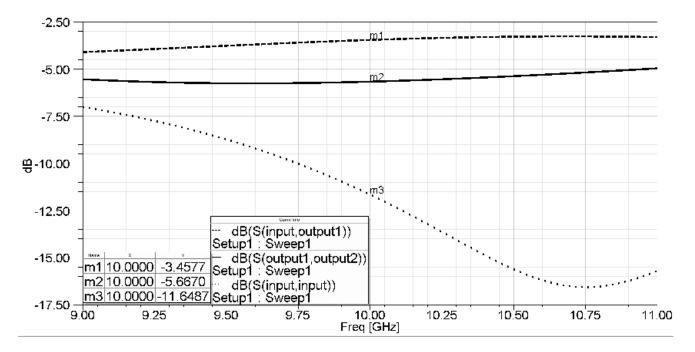

Figure 26: Circular Single Split Wilkinson Results

The circular single split Wilkinson power divider provided a low return loss (m3) of -17.27 dB at 10 GHz frequency which translates into a working power divider (dotted line in Figure 25). The threshold for reflection coefficient (m2) for this system is -9 dB thus the operating bandwidth for this power divider is approximately 1.5 GHz centered around 10.1 GHz. The power loss (m1) across the network is given by the dashed line and is measured as -3.1758. Taking into account the 3 dB division, the power loss is 0.176 dB. Finally, this network does not have the desired -25 dB measurement for isolation between Port 2 and Port 3.

Following the same procedure as the circular single split, a straight single split Wilkinson power divider was also modeled. Taking the values for the impedance quarterwave transformers, the following width and length values were derived with the AppCAD software.

| In_strip_width (1)        | 27.5 mil |

|---------------------------|----------|

| In_strip_legnth (2)       | 50 mil   |

| Straight_strip_length (3) | 301 mil  |

| Straight_strip_width (4)  | 14 mil   |

| Out_strip_width (5)       | 27.5 mil |

| Table 3: Straight Single | Split Variables |

|--------------------------|-----------------|

|--------------------------|-----------------|

These values are then set within the HFSS software and the straight single Wilkinson split is modeled. Figure 27 shows the use of the variables in the modeling of the Wilkinson power divider. The variables are numbered within Table 3. The final design is shown in Figure 28.

Figure 28: Straight Single Split Wilkinson

Following the same frequency sweep and analysis setup, the straight split is analyzed. In Figure 29, the results are provided. The center frequency has shifted by 0.75 GHz but the operating bandwidth has increased from 1.25 GHz to approximately 2 GHz for that the acceptable reflection coefficient of -9dB. The power loss through the network has increased to 0.46 dB and more importantly, the isolation between ports is reduced to only -5.67 dB.

Figure 29: Straight Single Split Wilkinson Results

Both the circular and straight divisions provide an operating power divider across the desired frequency. They also are extremely close to providing the required bandwidth for the system. The straight Wilkinson power divider has larger power loss across the board compared to the circular design. Both designs do not meet the required -25 dB port isolation (m2). Better matching with the isolator resistor would provide better isolation between both output ports. Table 4 provides a comparison of the two designs.

|                                            | Requirements | Circular Division | Straight Division |

|--------------------------------------------|--------------|-------------------|-------------------|

| Center Frequency                           | 10 GHz       | 10.1 GHz          | 10.75 GHz         |

| Bandwidth                                  | 2 GHz        | 1.5 GHz           | 2 GHz             |

| Power Loss at 10 GHz<br>(for single split) | 0.4 dB       | 0.176 dB          | 0.46 dB           |

| Port Isolation at 10<br>GHz                | -25 dB       | -12.07 dB         | -5.67 dB          |

Table 4: Circular and Straight Wilkinson Comparison

In both the single stage divisions the required distance of 590 mils between output ports are not met. Additionally, the bandwidth can be increased by increasing the number of stages. Therefore, a multistage Wilkinson power divider was designed. These factors were taken into account in the multistage single split design.

Using Chebyshev polynomials, the following values are found for the isolation resistors and the quarterwave transformers of the multistage power divider design. Note that the Isolation Resistor 1 and Transformer 1 are the closest ones to the output ports.

| Table 5. Multistage FOWEI Divider Values |         |

|------------------------------------------|---------|

| Isolation Resistor 1                     | 1010 Ω  |

| Isolation Resistor 2                     | 143 Ω   |

| Isolation Resistor 3                     | 143 Ω   |

| Isolation Resistor 4                     | 72.5 Ω  |

| Line Impedance for Transformer 1         | 52.59 Ω |

| Line Impedance for Transformer 2         | 62.51 Ω |

| Line Impedance for Transformer 3         | 79.98 Ω |

| Line Impedance for Transformer 4         | 95.07 Ω |

Table 5: Multistage Power Divider Values

The isolation resistors were modeled within the HFSS software. The quarterwave transformer dimensions were found using AppCad software. Due to the small wavelengths at high frequencies, the values are quite small so the closest round integer was used for the dimensions. Table 6 provides the dimensions found for the transformers with T width 1 being the transformer closest to the output ports.

| T_width_1 | 24 mil |

|-----------|--------|

| T_width_2 | 16 mil |

| T_width_3 | 8 mil  |

| T_width_4 | 4 mil  |

Table 6: Multistage Quarterwave Transformer's Line Widths

These values were utilized to build a model of the power divider in HFSS, with the center of the output ports being 590 mils apart. In order to avoid the losses that come with sharp edges, a Matlab microstrip chamfer program was used to derive values from Equations 2.4 - 2.5. The resulting design is shown in Figure 30.

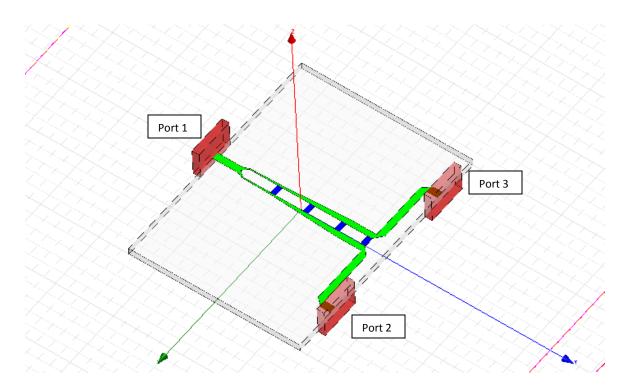

Figure 30: Multisection Single Split Wilkinson

The results from the simulation are provided in Figure 31.

Figure 31: Multisection Single Split Wilkinson Simulation Results

The results from the multisection single division Wilkinson power divider show that the power divider has an operating bandwidth from 9-11 GHz. The reflection coefficient (m2) at Port 1 is -12.16 dB at 10 GHz which is acceptable under the -9 dB threshold. The power loss (m1) from the network is 1.1 dB at 10 GHz which is anticipated with the higher bandwidth. For a single split, commercial power dividers typically have approximately 0.4 dB loss through the network which is the desired power loss. The multistage power divider is the furthest measurement from that value. The port isolation (m3) is not at the desired -25 dB measurement but is extremely close and much better than both single stage power dividers. Because of the narrow analysis of the 9 – 11 GHz frequency sweep, the multistage power divider analysis frequency sweep is increased. Figure 32 shows the results.

Figure 32: 20 GHz Frequency Sweep Multistage Wilkinson Power Divider

This larger frequency sweep provides more information on the network's performance. The bandwidth of the multistage power divider is over 10 GHz operating from 1 – 14 GHz. There are also visible dips and humps on the reflection coefficient (dotted line) which is a consequence of increasing the stages. To increase bandwidth of the system, the power loss of the network is increased. The low frequencies within the bandwidth have the lowest loss at 0.2 dB loss, and for high frequencies the power loss reaches 2 dB. Finally the port isolation is much better than the single split power dividers across the entire frequency span and it is optimal at 11.5 GHz with -37 dB value.

This design meets two major requirements of the power divider, bandwidth across the desired operating frequency and output ports distanced 590 mils apart. Also, the isolation is extremely close to the requirement. This design is cascaded to provide a corporate feed network. The resulting model can be seen in Figure 33.

Figure 33: Multistage 8-split Wilkinson Power Divider

The simulation results are given in Figure 34.

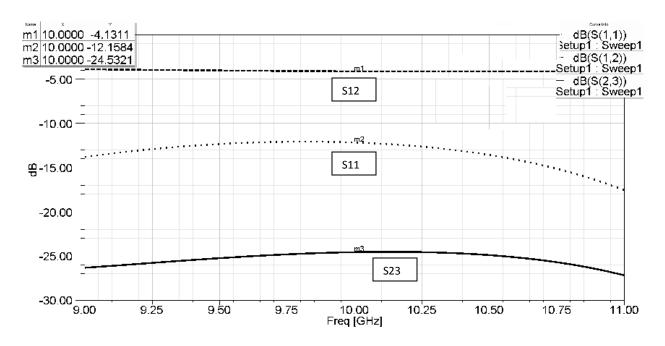

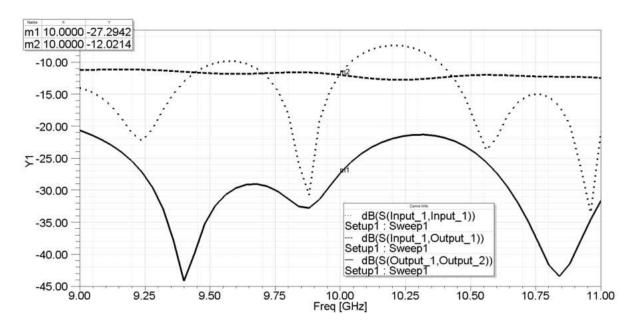

Figure 34: Multistage 8-way Wilkinson Power Divider Simulation Results

The return loss (m2) at 10 GHz is underneath the -9 dB threshold at -12.02 dB with the return loss remaining under the threshold at lower frequencies but a large

hump immediately after 10 GHz breaks this limit. While the return loss (m2) is acceptable, the dip at 9.85 GHz would be best the desired operating frequency of 10 GHz. The power loss across the board is just above -3 dB loss at 10 GHz with the loss varying approximately <u>+</u>1 dB across the frequency sweep. Finally, Figure 34 shows the port isolation (m1) at -27.3 dB at 10 GHz.

Further simulation provides a larger frequency sweep and better analysis. Figure 35 gives the results.

Figure 35: Large Frequency Sweep 8-way Wilkinson Power Divider Simulation Results

There is approximately 1.5 GHz operating bandwidth that includes but is not centered at 10 GHz. From 2.25 - 8.25 GHz there is a large operating bandwidth but this is not including the required frequency. The power loss of the network continually increases as the frequency increases. It ranges from 2 dB to 3 dB loss over the 1.5 GHz bandwidth (note that there is an inherent 9 dB loss from the power divider). Finally, the port isolation is performing as required from 9.2 - 10.1 GHz with large dips and humps

across the entire frequency span. It particularly gets worse at higher frequencies. Table 7 provides an analysis of the simulation compared to the requirements. The power loss and port isolation are taken across the operating bandwidth from 8.5 – 10.1 GHz.

|                     | Requirements | Simulation     |

|---------------------|--------------|----------------|

| Operating Frequency | 10 GHz       | 9.9 GHz        |

| Bandwidth           | 2 GHz        | 1.5 GHz        |

| Power Loss          | 2 dB         | 2 dB – 3dB     |

| Port Isolation      | -25 dB       | -17dB — -37 dB |

Table 7: Multistage 8-way Power Divider Simulation Analysis

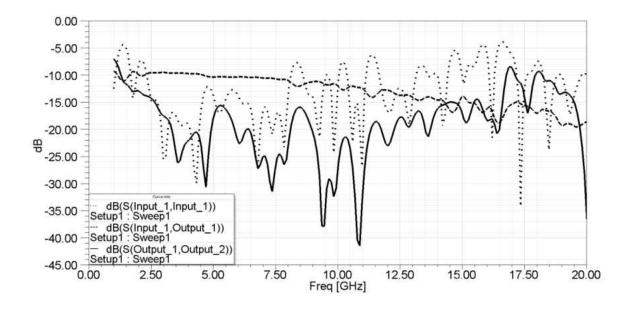

#### 3.5. Fabrication

Due to time constraints for system testing, the simulated multistage Wilkinson power divider was fabricated. CadSoft's Easy Applicable Graphical Layout Editor (EAGLE) was used to draw the PCB layout. Side mounted SMA female connectors were placed at the ports with vias placed in the soldering pads to provide better adhesion with the SMA to the PCB copper [32]. Additionally, the isolation resistors were attached to a soldering pad. RC0402 surface mounted lumped resistors were used because of their small size (0.039" x 0.020" x 0.016"). Because the desired isolator values are not standard, the standard resistors with closest resistances were used [33]. The PCB for the power divider is shown in Figure 36.

Figure 36: EAGLE Wilkinson Design

EAGLE produces Gerber design files were sent to Advanced Circuits for fabrication [32]. Once the board and components were received, the resistors were placed on the PCB. A board stencil was not purchased to provide guidance when applying the solder so the resistors and solder were placed carefully by hand with the aid of a microscope. Once the resistors were place, the board was put in a controlled oven to solder the resistors into place. After the resistors were set, the SMA connectors were placed by hand taking caution on centering the probe on the microstrip. The final fabricated board can be seen in Figure 37. The output ports are also numbered with the furthest to the left being labeled Output Port 1. This port numbering will be used in Chapter 4 while discussing the results.

Figure 37: Final Fabricated Wilkinson Power Divider

## CHAPTER 4

# RESULTS

# 4.1 Introduction

After the simulation and fabrication of the power divider, the network was tested. The simulation and experimental testing results are compared in this chapter to provide insight into the power divider.

# 4.2 Measurement Result

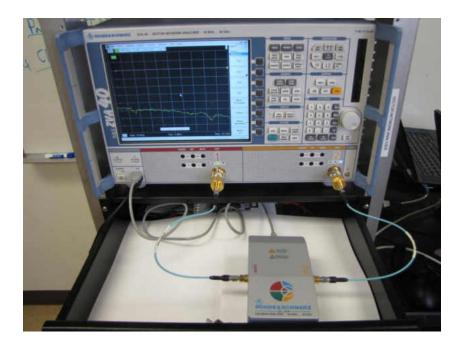

The fabricated Wilkinson power divider was tested with Rohde & Schwarz's VZA-40 Vector Network Analyzer (VNA). In order to ensure accurate results, the VNA was calibrated using a Rohde and Schwarz ZV-Z54 Calibration Unit. Figure 38 shows the calibration setup.

Figure 38: VNA Calibration Setup with ZV-Z54

After the unit was calibrated, using the same connectors and cables, the Wilkinson power divider was attached to the VNA. In order to test for a balanced load across each port, the VNA was set to have a 50 $\Omega$  termination at the ports and 7 SMA-50 $\Omega$  terminators were placed at the unmeasured output ports (Figure 39).

Figure 39: SMA-50 $\Omega$  Terminator

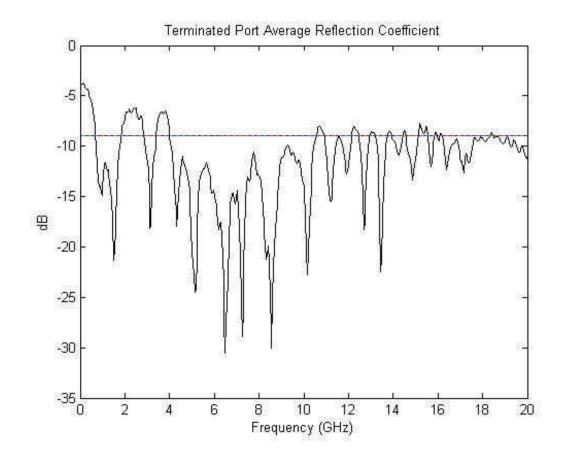

The terminators were alternated to cover all output ports whenever one port was attached to the VNA. The measured reflection coefficient (S11) for each output port was processed using Matlab (Appendix B) and then were plotted. Figure 40 provides the resulting plot.

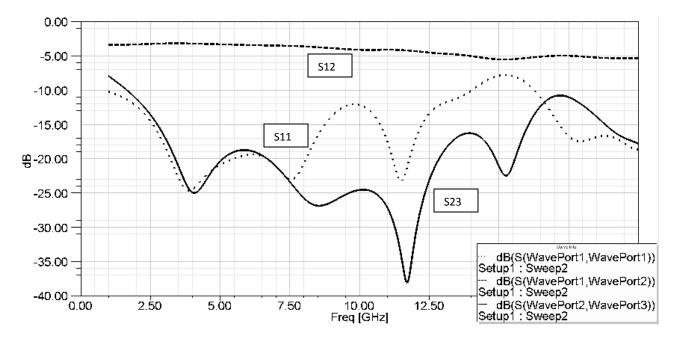

Figure 40: Average Reflection Coefficient of Network

The -9 dB threshold is plotted along with the average reflection coefficient for the network. This provides a visible representation for the operating bandwidth. At high and much low frequency bands the reflection coefficient was less than the threshold. The power divider has a 6.5 GHz bandwidth from 4 GHz to 10.5 GHz. The bandwidth is not centered at the desired 10 GHz. Figure 41 provides the network's reflection coefficient across the operating bandwidth.

Figure 41: Average Reflection Coefficient Bandwidth (Terminated Ports) Figure 41 better shows the bandwidth. There are multiple dips in the return loss which is a product of the design of the multistage power divider. For each stage, a dip wf created for a specific frequency. There is a dip of -25 dB reflection coefficient at approximately 10.1 GHz which is offset from the desired 10 GHz. Additionally, while the bandwidth is more than the required 2 GHz, it is not centered at 10 GHz.

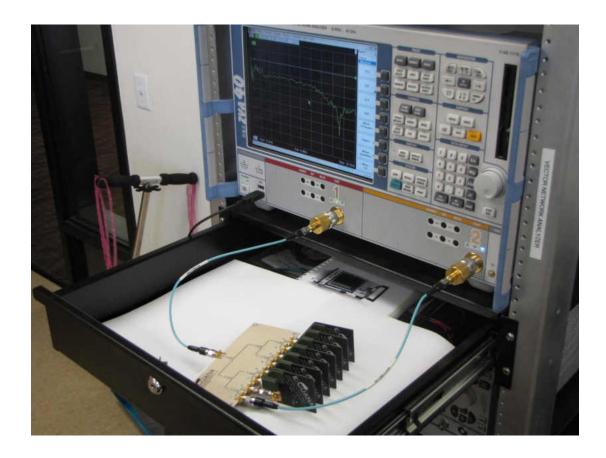

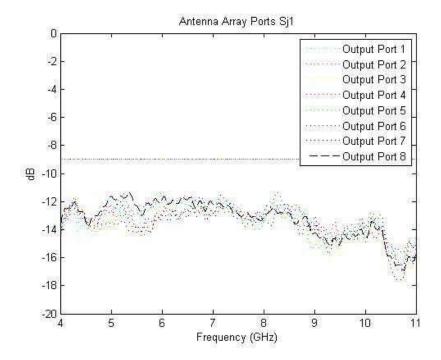

The same process was followed to measure the reflection coefficient (S11) while the antennas were attached. A fabricated brace was used to provide stability to the antennas and to ensure the linearity of the array during testing. It was noticed that occasional interference due to radiation of the antennas cause inaccuracies within the measurements. Figure 42 shows the set-up used for phased antenna array testing. Figure 43 shows the average measurement results from each port.

Figure 42: Wilkinson Power Divider with Vivaldi Antenna Test Set-up

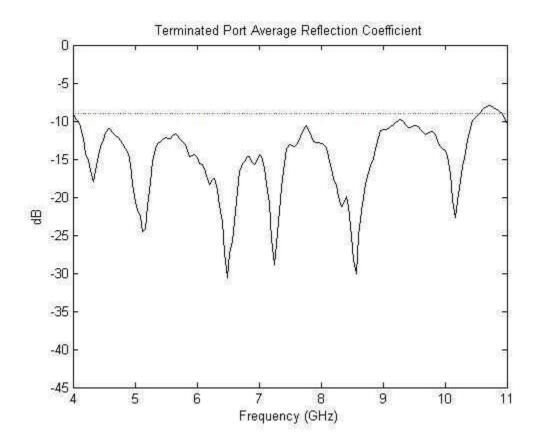

Figure 43: Average Reflection Coefficient for the Combination of Power Divider and Antenna Array

Much like the average reflection coefficient with terminated ports, the operating frequency bandwidth is also 6.5 GHz starting at 4 GHz. Even though the ports are terminated with antennas, their radiation causes more noise to be introduced to the network. A comparison of the terminated and antenna array average reflection coefficient measurements across the 6.5 GHz bandwidth is given in Figure 44.

Figure 44: Terminated and Antenna Array Average Return Loss

The noise in the antenna array return loss is noticeable when compared to the terminated ports. The antenna array does not have as severe dips throughout the bandwidth and also comes close to breaking the threshold several times.

During testing, several inaccuracies were observed. During the testing of the antenna array, the cable interfered with the radiation of several antennas in the array which affected the return loss during the measurement. There are also inaccuracies created by the bend in the cables connecting the network to the VNA. Care was taken in keeping the same position but the slightest alteration in the cable's bend could affect up to -3dB change across the measurements. A torque wrench was used to apply an equal torque of 8 in/lb to each port but it was noticed that the antenna SMA connectors often came loose. Additionally, each SMA connector on the network was placed individually by hand. Slight inaccuracies could occur based off the differences between each probe placement.

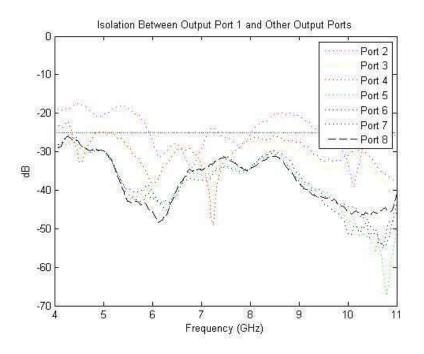

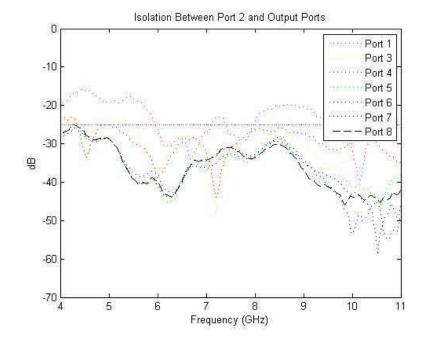

### 4.3 Port Isolation

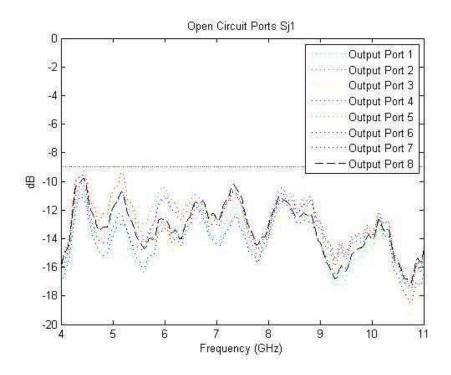

The isolation between ports is measured using the VNA. The desired measurement for port isolation is any value lower than -25 dB. Figure 45 depicts the isolation between Output Port 1 and all other ports over the 6.5 GHz operating bandwidth of the network. The isolation for all the Output Ports are provided in Appendix A.

Figure 45: Output Port 1 Isolation Open Port

Figure 45 displays that most of the output ports are well underneath the required -25 dB threshold. Output Port 2 which is located closest to Output Port 1 is often breaking the desired threshold. A better way to explain why the isolation between these two ports is not meeting the required value over the bandwidth is to trace the path from Output Port 1 to Output Port 2. There is only a single power division with four isolator resistors. The other output ports have multiple divisions and resistors to provide better isolation. Note that at 4 GHz, Output Port 3 and 4 are above the desired measurement. These two ports are the next closest ports to Output Port 1 and will act this way because of the design of the power divider.

A potential inaccuracy in the isolation could be the human error when soldering the resistors to the network. Care was taken in soldering but due to the resistor's size, they could be slightly off their pad. Also, when acquiring the resistors, the theoretical resistance value could not be met with the standard resistors on the market so the next highest standard resistor was used. Plots for other ports can be found in Appendix A.

#### 4.4 Phase and Power Error

The VNA produces a signal that is sent through the network. The initial signal is then compared to the received signal (the one that went through the network). The data was processed using Matlab and plotted to find the average phase error for each output port across the power divider's operating bandwidth. Data was acquired through the same method for testing the reflection coefficient. The phase for matched

62

terminated port, antenna terminated port, and open circuit port were then graphed.

Figure 46 shows the matched terminated phase across all eight ports.

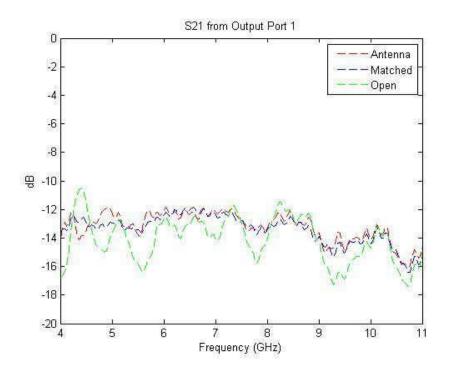

Figure 46: Phase Across Matched Terminated Output Ports

Looking at the graph of each output port's phase does not provide enough information on the differences between the phases. The phase measurement of the antenna array and open circuit ports look similar to Figure 46. As mentioned, there are differences between the output port signals. In order to better analyze the difference in phase at the output ports, the error for Output Port 3 and Output Port 8 were plotted for visual effect with a 2 GHz bandwidth (Figure 47).

Figure 47: Port 3 and 8 Phase with Matched Terminator