# University of North Dakota UND Scholarly Commons

Theses and Dissertations

Theses, Dissertations, and Senior Projects

January 2018

## Developing A New Storage Format And A Warp-Based Spmv Kernel For Configuration Interaction Sparse Matrices On The Gpu

Mohammed Mahmoud

Follow this and additional works at: https://commons.und.edu/theses

## Recommended Citation

Mahmoud, Mohammed, "Developing A New Storage Format And A Warp-Based Spmv Kernel For Configuration Interaction Sparse Matrices On The Gpu" (2018). *Theses and Dissertations*. 2415.

https://commons.und.edu/theses/2415

This Dissertation is brought to you for free and open access by the Theses, Dissertations, and Senior Projects at UND Scholarly Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of UND Scholarly Commons. For more information, please contact zeinebyousif@library.und.edu.

## DEVELOPING A NEW STORAGE FORMAT AND A WARP-BASED SpMV KERNEL FOR CONFIGURATION INTERACTION SPARSE MATRICES ON THE GPU

By

Mohammed Mahmoud Bachelor of Science, Helwan University, 2001 Master of Science, Helwan University, 2006

A Dissertation

Submitted to the Graduate Faculty

of the

University of North Dakota

in partial fulfillment of the requirements

for the degree of

Doctor of Philosophy

Grand Forks, North Dakota

December 2018

| This dissertation, submitted by Mohammed Mahmo<br>for the Degree of Doctor of Philosophy from the Uni<br>Faculty Advisory Committee under whom the work | versity of North Dakota, has been read by the |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Harca Kess                                                                                                                                              |                                               |

| Hassan Reza, Ph.D.                                                                                                                                      |                                               |

| Ma Hu                                                                                                                                                   |                                               |

| Mark Hoffmann, Ph.D.                                                                                                                                    |                                               |

| Semant Stark                                                                                                                                            |                                               |

| Emanuel Grant, Ph.D.                                                                                                                                    |                                               |

| Wenchen Hu, Ph.D.                                                                                                                                       |                                               |

| of sufer                                                                                                                                                |                                               |

| Pim Young, Ph.D.                                                                                                                                        |                                               |

|                                                                                                                                                         |                                               |

| This dissertation is being submitted by the appointed requirements of the School of Graduate Studies at the approved.                                   |                                               |

| Grant McGimpsey U  Dean of the School of Graduate Studies                                                                                               |                                               |

| Dealt of the School of Graduate Studies                                                                                                                 |                                               |

| December 5, 2018                                                                                                                                        |                                               |

| Date                                                                                                                                                    |                                               |

|                                                                                                                                                         |                                               |

|                                                                                                                                                         |                                               |

#### **PERMISSION**

Title Developing a New Storage Format and a Warp-Based SpMV Kernel for Configuration Interaction Sparse Matrices on the GPU.

Department Computer Science.

Degree Doctor of Philosophy in Scientific Computing with a Graduate Minor in

Chemistry.

In presenting this dissertation in partial fulfillment of the requirements for a graduate degree from the University of North Dakota, I agree that the library of this University shall make it freely available for inspection. I further agree that permission for extensive copying for scholarly purposes may be granted by the professors who supervised my dissertation work or, in their absence, by the Chairperson of the department or the dean of the School of Graduate Studies. It is understood that any copying or publication or other use of this dissertation or part thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of North Dakota in any scholarly use which may be made of any material in my dissertation.

Mohammed Mahmoud 11/13/2018

## TABLE OF CONTENTS

| LIST OF FIG | GURES                          | iv   |

|-------------|--------------------------------|------|

| LIST OF TA  | BLES                           | v    |

| LIST OF AL  | GORITHMS                       | vi   |

| ACKNOWL     | EDGEMENTS                      | vii  |

| ABSTRACT    | ,                              | viii |

| CHAPTER     |                                |      |

| I.          | INTRODUCTION                   | 1    |

| II.         | BACKGROUND                     | 9    |

| III.        | CONFIGURATION INTERACTION (CI) | 17   |

| IV.         | COMMON FORMATS                 | 29   |

| V.          | RELATED WORK                   | 39   |

| VI.         | THE PROPOSED MODEL             | 50   |

| VII.        | EXPERMENTAL RESULTS            | 61   |

| VIII.       | QUATERNIONS                    | 77   |

| IX.         | CONCLUSIONS AN D FUTURE WORK   | 97   |

| APPENDIX    | 1                              | 99   |

| APPENDIX    | 2                              | 115  |

| APPENDIX    | 3                              | 119  |

| APPENDIX    | 4                              | 131  |

| REFERENC    | ES                             | 146  |

#### LIST OF FIGURES

- Figure 1. The Configuration Interaction (CI) Matrix.

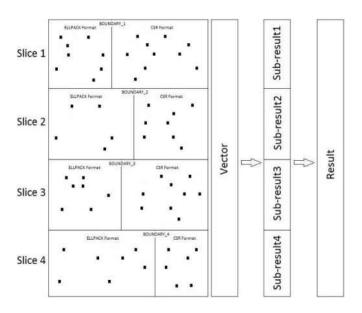

- Figure 2. Sparse matrix-vector multiplication (SpMV) for CI Matrices

- **Figure 3.** The GPU Memory Hierarchy.

- Figure 4. The Proposed Format.

- **Figure 5.** A Variation of the Proposed Model.

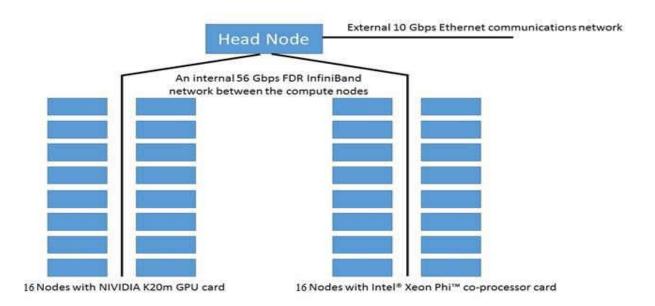

- Figure 6. Hodor Supercomputer.

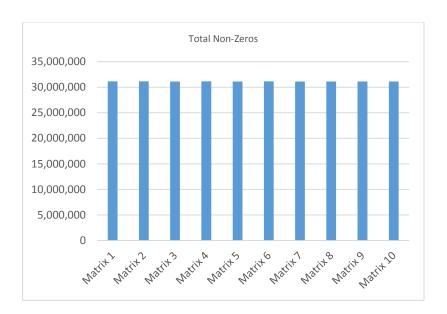

- **Figure 7.** Total Non-Zeros.

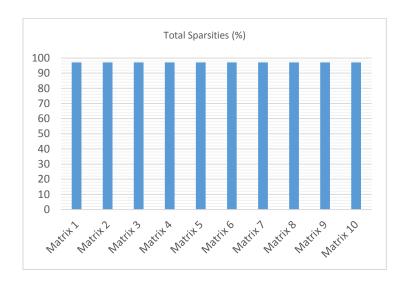

- Figure 8. Matrices Total Sparsities Information.

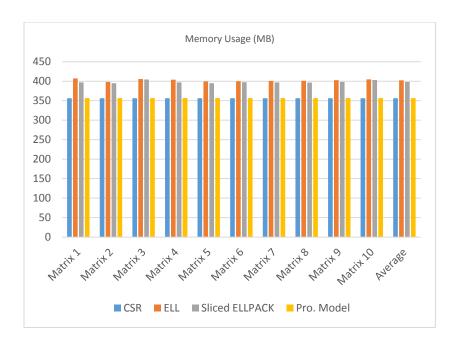

- Figure 9. Memory Usage.

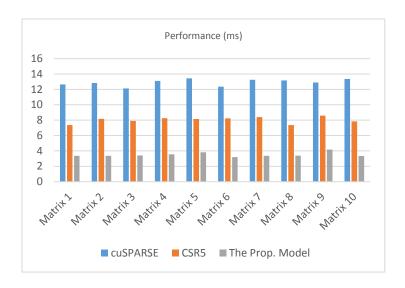

- Figure 10. Performance with a Block Size of 32.

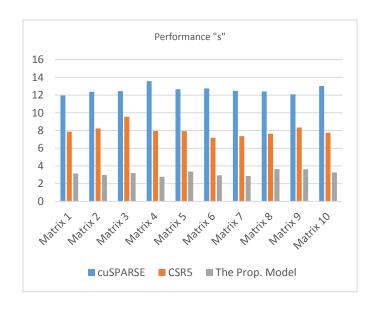

- **Figure 11.** Performance with a Block Size of 32 Using 10 Different 1048576 by 1048576 CI Sparse Matrices.

.

#### LIST OF TABLES

- **Table 1:** The number of singlet CSFs as a function of excitation level for H<sub>2</sub>O with a 6-31G(d) basis.

- **Table 2:** Common Formats.

- **Table 3:** GPU Properties.

- **Table 4:** The Proposed Storage Format Information.

- **Table 5:** Matrices Sparsities Information.

- **Table 6:** Memory Usage.

- **Table 7:** Running the nyprof profiler with a Block Size of 16.

- **Table 8:** Running the nvprof profiler with a Block Size of 32.

- **Table 9:** Running the nvprof profiler with a Block Size of 64.

- **Table 10:** Performance with a Block Size of 32.

- **Table 11:** Performance with a Block Size of 32 Using 10 Different 1048576 by 1048576 CI Sparse Matrices.

#### LIST OF ALGORITHMS

- **Algorithm 1.** The SpMV kernel for the CSR format.

- **Algorithm 2.** The SpMV kernel for the ELLPACK format (thread per row).

- **Algorithm 3.** The SpMV kernel for the ELLPACK-R format (thread per row).

- **Algorithm 4.** The SpMV kernel for the Sliced ELLPACK format (thread per row).

- **Algorithm 5.** The SpMV kernel for the Sliced ELLPACK-R format (thread per row).

- **Algorithm 6.** The proposed format.

- **Algorithm 7.** The SpMV kernel for the proposed format.

- **Algorithm 8.** The SpMV kernel for the variation of the proposed format.

#### **ACKNOWLEDGEMENTS**

I would like to thank my graduate advisory committee for their help and support throughout my doctoral research. I would like to thank my advisors for their patience with me. Also, I would like to thank them for their helpful updates and feedback regarding my dissertation and my papers:

Dr. Hassan Reza

Dr. Mark Hoffmann

And the rest of my committee members:

**Dr. Emanuel Grant**

Dr. Wenchen Hu

**Dr. Tim Young**

I would like to thank Dr. Travis Desell for his continuous technical and academic support.

I would like to thank the Computer Science department at the University of North Dakota. I would also like to thank the Chemistry Department at the University of North Dakota.

I would like to thank Aaron Bergstrom from the University of North Dakota for his help and support, Aaron is the Advanced Cyberinfrastructure Manager at the University of North Dakota Computational Research Center.

I would like to thank Aliakbar Sepehri and Eric Timian, who are members of our research group (Dr. Hoffmann's group) for their help and support with regard to the Configuration Interaction theory.

I would like to thank the Graduate School at the University of North Dakota for financially supporting this doctoral research.

I would like to thank Dean Grant McGimpsey, the Vice President for Research & Economic Development and Dean of the School of Graduate Studies for his support.

#### **ABSTRACT**

Configuration interaction (CI) is a post Hartree–Fock method that is commonly used for solving the nonrelativistic Schrödinger equation for quantum many-electron systems of molecular scale. CI includes instantaneous electron correlation and it can deal with the ground state as well as multiple excited states.

The CI matrix is a sparse matrix, and the bigger the CI matrix, the more electron correlation can be captured. However, due to the large size of the CI sparse matrix that is involved in CI computations, a good amount of the time spent on the eigenvalue computations is associated with the multiplication of the CI sparse matrix by numerous dense vectors, which is basically known as Sparse matrix-vector multiplication (SpMV).

Sparse matrix-vector multiplication (SpMV) can be used to solve diverse-scaled linear systems and eigenvalue problems that exist in numerous and varying scientific applications. One of the scientific applications that SpMV is involved in is Configuration Interaction (CI).

In this work, we have developed a new hybrid approach to deal with CI sparse matrices. The proposed model includes a newly-developed hybrid format for storing CI sparse matrices on the Graphics Processing Unit (GPU). In addition to the new developed format, the proposed model includes the SpMV kernel for multiplying the CI matrix (proposed format) by a vector using the C language and the CUDA platform. The proposed SpMV kernel is a vector kernel that uses the warp approach. We have gauged the newly developed model in terms of two primary factors, memory usage and performance.

Our proposed kernel was compared to the cuSPARSE library and the CSR5 (Compressed Sparse Row 5) format and already outperformed both. Our proposed kernel outperformed the CSR5 format by 250.7% and the cuSPARSE library by 395.1%

Keywords—CI, SpMV, Linear System, GPU, Kernel, CUDA.

#### CHAPTER 1

#### INTRODUCTION

Configuration Interaction (CI) is a post Hartree–Fock method that is commonly used for solving the nonrelativistic Schrödinger equation for quantum chemical multi-electron systems. CI has the advantage of dealing with the ground state beside multiple excited states as opposed to other methods that deal only with the ground state.

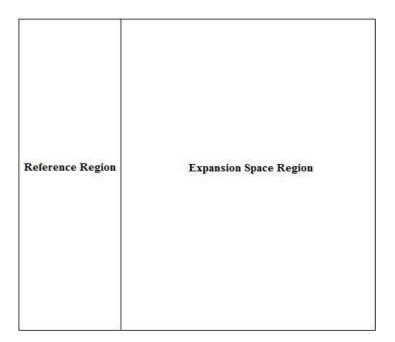

Whether we perform a full CI or only a limited CI, we must be able to express the Hamiltonian in a matrix form so that we can diagonalize it and obtain the eigenvectors and eigenvalues of interest to us. Figure 1 is a simple representation of the CI sparse matrix that shows the two major components of the matrix, namely the Reference Region and the Expansion Space region.

Fig. 1. The Configuration Interaction (CI) Matrix

The Hamiltonian or the CI matrix is a sparse matrix that can be very huge in size, as the CI matrix gets bigger, more electron correlation can be captured from it. Nonetheless, due to the large size of the CI sparse matrix that is involved in CI computations, a good amount of the time that is spent on the eigenvalue computations is already associated with the multiplication of the huge CI sparse matrix by numerous dense vectors, this process is commonly known as Sparse matrix-vector

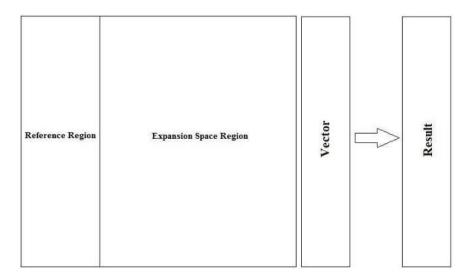

multiplication (SpMV). Figure 2 is a simple representation of the SpMV operation for CI sparse matrices.

Fig. 2. Sparse matrix-vector multiplication (SpMV) for CI Matrices

Sparse matrix-vector multiplication (SpMV) is one of the most common operations in scientific and high-performance applications. Achieving a good and high SpMV performance is challenging because performance is heavily affected by the density of nonzero entries or their sparsity pattern. As processors are getting increasingly diverse and complex, optimizing SpMV becomes much harder.

#### CONTRIBUTIONS

- Before the proposed format and the proposed kernel were developed, we were working on designing and developing other algorithms that helped us design and implement the proposed model appropriately. We started out by designing the algorithms and also the C code for the following sparse matrix formats:

- 1. The Compressed Sparse Row (CSR) or Compressed Row Storage (CRS) Format.

- 2. The ELLPACK (ELL) Format.

- 3. The ELLPACK-R (ELL-R) Format.

- 4. The Sliced ELLPACK (Sliced ELL) Format.

- 5. The Sliced ELLPACK-R (Sliced ELL-R) Format.

- We also worked on developing the algorithms for the GPU SpMV kernels for each of the previously mentioned SpMV formats. Then, we developed the GPU SpMV kernels for those algorithms.

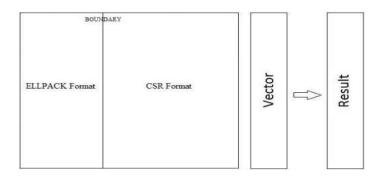

- In this study, a new storage format for storing CI sparse matrices on the GPU was implemented. The proposed format compresses the sparse matrix in a way that saves a considerable amount of GPU memory. Besides, we have developed the SpMV kernel for the proposed format on the GPU. The proposed SpMV kernel is a single SpMV vector kernel that assigns a warp to each single row in the Reference region (ELLPACK format) and assigns another warp to each single row in the Expansion Space region (CSR format). We used the C language [16] and the CUDA platform [9] [10] for implementation. The C language is considered a fast high performance computing programming language as well as easy to use. Numerous programming languages as well as operating systems are built using the C language. The C language supports system calls more conveniently than FORTRAN. The two factors that we are interested in assessing and evaluating are the amount of used memory and performance [5].

- Generally, the use of double-precision is very common in quantum chemistry. Double

precision generates more accurate results in addition to smaller errors [63]. The proposed CI

SpMV kernel was first developed using single precision as most of the SpMV kernels are single-precision kernels. Then, we converted the proposed CI SpMV kernel into double-precision for the sake of getting more accurate results.

• Our proposed kernel was compared to the cuSPARSE library and the CSR5 (Compressed Sparse Row 5) format and already outperformed both. Our proposed kernel outperformed the CSR5 format by 250.7% and the cuSPARSE library by 395.1%.

#### STRUCTURE OF THE DISSERTATION

<u>Chapter 1</u> is the introductory part to our work. In <u>Chapter 2</u>, we will be reviewing some basic concepts, such as GPU, CUDA, and SpMV. In Chapter 3, we will be discussing different ways that are used to solve the Schrödinger equation, with an emphasis on Configuration Interaction (CI). In Chapter 4, we will be discussing some common/conventional storage formats that are used to store sparse matrices. In **Chapter 5**, we will be reviewing some related work to Sparse matrix-vector multiplication (SpMV). In Chapter 6, we will be discussing the proposed model, more specifically, we will be talking about the proposed storage format and the developed SpMV kernel. In **Chapter 7**, we will be discussing the experimental results of comparing the proposed model to the cuSPARSE library and the CSR5 (Compressed Sparse Row 5) format and show how the proposed model outperformed both of them. In **Chapter 8**, we will be discussing Quaternions and show how they relate to Quantum Chemistry in general and also relate to Configuration Interaction specifically. Quaternions can be integrated with Configuration Interaction (CI) since they are optimized to deal with objects that have more interior structure, i.e., CI sparse matrices. The structure of the CI sparse matrix can be more compact using quaternionic representation, thus memory access time will be less. The real challenge that we will deal with when using quaternions for CI matrices is performance. Chapter 9 will include the conclusions and prospective future work, including the use of quaternions in lieu of real scalar coefficients; a detailed overview of features and widely-used functions.

## **TERMINOLOGIES**

**CI:** Configuration Interaction.

**SpMV:** Sparse matrix-vector multiplication.

**GPU:** Graphics Processing Unit.

**CUDA:** Compute Unified Device Architecture.

**CC**: Coupled Cluster.

**CSR**: Compressed Sparse Row.

**CRS**: Compressed Row Storage.

**ELL**: ELLPACK.

**ELL-R**: ELLPACK-R.

**Sliced ELL**: Sliced ELLPACK.

**Sliced ELL-R**: Sliced ELLPACK-R.

**CSB**: Compressed Sparse Blocks.

#### THE PROBLEM STATEMENT

One of the main issues in CI computations is the immensely huge size of the CI sparse matrix [13]. The construction of the CI sparse matrix is itself expensive. Some of the elements of the CI matrix are hard to calculate or recreate and some aren't. Different parts of the CI sparse matrix can be calculated using different ways, therefore we have two approaches. One approach would be to pre-calculate the sparse matrix once at the beginning [13]. This option fits some parts of the CI sparse matrix that are hard to recreate. Adopting this approach will be limited by the GPU memory. The other approach would be to calculate the elements of the CI sparse matrix on the fly. This option fits some parts of the CI sparse matrix that are easy to recreate. It's worth mentioning that CPUs are faster than the GPUs when calculating the elements on the fly since CPUs have more complex chips than GPUs. GPUs do branch prediction in a slower fashion than CPUs. CPUs have better caching and more caches than GPUs, whereas GPUs have only global memory (slow), constant memory, local memory, shared memory, and registers. Modern CI calculations are often done on the fly, but this doesn't mean that the entire problem should be done on the fly. Based on the pre-mentioned information, we are going to develop a hybrid approach in order to deal with the CI sparse matrix elements.

We developed a new storage format for storing CI sparse matrices on the GPU. In addition to that, we have implemented on the GPU the SpMV kernel that is based on the newly-developed storage format. The newly-implemented SpMV kernel is a single SpMV vector kernel that dedicates a single warp to every single row in the CI matrix's Reference region and dedicates another warp to every single row in the CI matrix's Expansion Space region. The CSR format is very efficient with regard to using memory (storage space) since it does not require zero-padding like the ELLPACK format. Also, the CSR format provides high performance for SpMV operations on CPUs that have multiple cores [2]. On the other hand, the CSR format provides lower performance than the ELLPACK format on GPUs when it comes to SpMV because of the lack of coalesced access to global memory on the GPU. The ELLPACK format provides higher performance than the CSR format on the GPU [2].

The Reference region of the CI matrix represents most of the electronic structure and performance is an important factor in this part, consequently we are going to store the Reference region in the ELLPACK format. The Expansion Space region that occupies the rest of the CI matrix has a noticeable high sparsity, so storage space is crucial and critical in this part. The CSR format is very powerful regarding storage space, therefore the Expansion Space region will be stored in the CSR format. If we tried to store the Expansion Space region in the ELLPACK format, we will end up with a huge amount of zero-padding especially if one or more rows in the Expansion Space region was not/were not as sparse as the other rows in the same region.

The proposed model can be further extended to be a quaternion-based model. Quaternions (fully described in Chapter 8) are 4-dimensional objects that extend complex numbers and they can be looked at as complex numbers whose components are complex numbers. Quaternions can be integrated with CI since they are optimized to deal with objects that have more interior structure, i.e., CI sparse matrices; they can be used to display objects that have more structure than the point-like nuclei. The structure of the CI sparse matrix can be more compact using quaternionic representation, thus memory access time will be considerably less.

#### **CHAPTER 2**

#### **BACKGROUND**

## **GPU:**

A Graphics Processing Unit (GPU) is an electronic chip that is designed for extremely fast parallel computations and processing of data. GPUs are more efficient and faster than CPUs at manipulating and processing data, especially computer graphics, because of their highly parallel structure and their capabilities to execute thousands of threads in parallel. A GPU is a specialized electronic chip that is designed to rapidly manipulate and alter memory to speed up the creation of images in a frame buffer intended for output to a display device. GPUs are used in many scientific and technical areas, i.e., embedded systems, mobile phones, personal computers, workstations, and game consoles. Modern GPUs are very efficient at manipulating computer graphics and image processing.

NVIDIA introduced the first GPU (GeForce 256) in August, 1999. A CPU includes a few cores that can handle a few threads at a time; on the other hand, a GPU is composed of hundreds of cores that can handle thousands of threads simultaneously in parallel, the matter that leads to faster and more efficient data computations.

Most GPUs are designed for a specific usage, real-time 3D graphics or other mass calculations:

#### 1. Gaming

- GeForce GTX

- nVidia Titan X[disambiguation needed]

- Radeon HD

- Radeon RX

#### 2. Cloud Gaming

- nVidia Grid

- Radeon Sky

#### 3. Workstation

nVidia Quadro

- nVidia Titan X

- AMD FirePro

- Radeon Pro

#### 4. Cloud Workstation

- nVidia Tesla

- AMD FireStream

## 5. Artificial Intelligence Cloud

- nVidia Tesla

- Radeon Instinct

#### 6. Automated/Driverless car

nVidia Drive PX

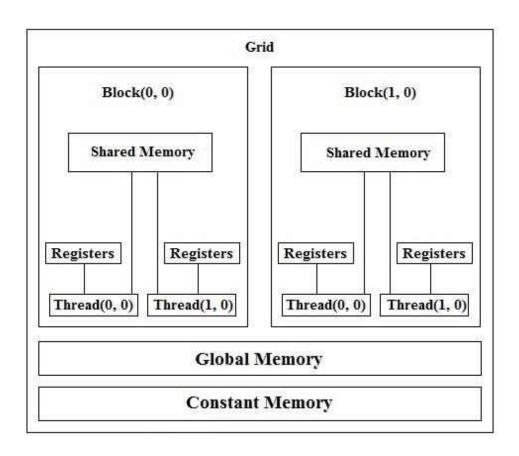

The GPU architecture is different from the CPU architecture in terms of memory. The GPU has multiple memory types (or levels). The global memory is the slowest memory and it's a read/write memory. The global memory can be accessed by all the threads within the grid. The constant memory is a read-only memory and it's faster than global memory. The constant memory can be accessed by all the threads within the grid, just like the global memory. The shared memory is defined for each block. The shared memory can be accessed by all the threads within the block. Automatic variables are stored in registers. Registers are faster than the shared memory. Registers can be accessed only by the current thread. The compiler sometimes places automatic variables in the local memory; for example: an array created within the kernel is likely to be stored in the local memory. The local memory space resides in the global memory, however other threads can't access it. Local memory accesses have the same high latency and low bandwidth as global memory accesses, so local memory is rarely used. The local memory is only accessible from the current thread. Registers are faster than the shared memory. The shared memory is faster than the constant memory. The constant memory is faster than the global memory. Figure 3 illustrates the memory hierarchy of the GPU:

Fig. 3. The GPU Memory Hierarchy [21]

#### **CUDA:**

Compute Unified Device Architecture (CUDA) [9] [10] is often mistaken for a programming language, or it might be thought of as an Application Programming Interface (API). In fact, CUDA is more than that. CUDA is a general purpose parallel computing platform created by NVIDIA in 2006. It aids software developers by allowing the compute engine in NVIDIA GPUs to solve a variety of complex problems faster and more efficient than Central Processing Units (CPUs). CUDA allows the software developer to parallelize some portions of the program's code in order to make the program run faster [20]. A kernel is a function (serial program) that will run on the GPU. The CPU launches the kernel on parallel threads.

CUDA can be viewed as a layer that enables software developers to access the GPU for the sake of executing compute kernels. CUDA is designed to work with various programming languages: i.e., C, C++, C#, FORTRAN, Java, Python, etc. [20]. This makes it possible for software developers who are experts in diverse programming languages to use the CUDA platform comfortably.

CUDA has numerous advantages over traditional general-purpose computation on GPUs. Some of these advantages are:

- Faster downloads and readbacks to and from the GPU.

- Scattered reads.

- Unified memory (CUDA 6.0 and above).

- Full support for integer and bitwise operations.

- Unified virtual memory (CUDA 4.0 and above).

- Shared memory CUDA exposes a fast shared memory region that can be shared among threads.

As already stated, CUDA is a general purpose parallel computing platform created by NVIDIA. One example of using CUDA kernels is given in the following steps:

1. The CPU allocates storage on the GPU (using cudaMalloc()).

- 2. The CPU copies input data from the CPU to the GPU (using cudaMemcpy()).

- 3. The CPU launches on the GPU multiple copies of the kernel on parallel threads to process the GPU data. A kernel is a Function (Serial program) that will run on the GPU. The CPU launches the kernel on parallel threads.

- 4. The CPU copies results back from the GPU to the CPU (using cudaMemcpy()).

- 5. Use or display the output.

#### **CUDA GPU Support:**

- CUDA SDK 6.5: Last Version with support for Compute Capability 1.x (Tesla)

- CUDA SDK 7.5 support for Compute Capability 2.0 5.x (Fermi, Kepler, Maxwell)

- CUDA SDK 8.0 support for Compute Capability 2.0 6.x (Fermi, Kepler, Maxwell,

Pascal), last version with support for Compute Capability 2.x (Fermi)

- CUDA SDK 9.0 support for Compute Capability 3.0 7.x (Kepler, Maxwell, Pascal, Volta).

Code1 in Appendix 1 is a simple GPU kernel called AddArrays that is used to add two integer arrays. In this case, the CPU launches on the GPU multiple copies of the AddArrays kernel on parallel threads (one kernel per thread) in order to perform the addition operation. Code 2 in Appendix 1 illustrates how to call the AddArrays kernel that was mentioned before.

Code 3 in Appendix 1 is a host function (a function that runs on the CPU) that is called PrintDeviceProperties(). This function can be used in order to list the GPU properties.

Code 4 in Appendix 1 shows how to call the previous function. The for loop is used to call the PrintDeviceProperties() function for each device.

Although CUDA allows us to run millions of threads or more, programs that run on the GPU aren't million times faster than the CPU for multiple reasons:

It takes time to copy data from the CPU to the GPU and vice versa.

CUDA doesn't allow all the threads to run simultaneously on the GPU since it depends on

the architecture of the GPU.

Kernel threads are accessing global memory which is implemented in DRAM (slow and

there is a lookup latency).

The following definitions summarize what we have described above:

**Host:** CPU. It runs the main program.

Device: GPU.

**Kernel:** Function (Serial program) that will run on the GPU. The CPU which launch the kernel on

parallel threads.

**GPU:** Graphics Processing Unit.

**CUDA:** Compute Unified Device Architecture.

**blockDim.x:** The number of threads within the block in the x dimension.

**gridDim.x:** The number of blocks within the grid in the x dimension.

threadIdx.x: The thread index within the block in the x dimension (0 to (blockDim.x - 1)).

**blockIdx.x:** The block index within the grid in the x dimension (0 to (gridDim.x - 1)).

In order to compile a CUDA program, run the following command:

nvcc 1.cu -o 1.out (c and c++)

In order to run a CUDA program, run either of the following commands:

./1.out

14

#### cuda-memcheck ./1.out

In order to run a CUDA program that accepts 3 arguments, namely <u>arg1</u>, <u>arg2</u>, and <u>arg3</u>, run either of the following commands:

## ./1.out arg1 arg2 arg3

## cuda-memcheck ./1.out arg1 arg2 arg3

If you want to compile and run a CUDA program in just a single step, run the following command:

#### nvcc 1.cu -run

If you want to compile and run a CUDA program that accepts 3 arguments, namely <u>arg1</u>, <u>arg2</u>, and <u>arg3</u> in a single step, run the following command:

## nvcc 1.cu -run -run-args arg1,arg2,arg3

### **SpMV**:

Sparse matrix-vector multiplication (SpMV) is a substantial computational kernel that has numerous applications in a wide variety of scientific areas and fields. SpMV is the main step of some iterative solvers such as Conjugate Gradient (CG) and Generalized Minimum Residual (GMRES) that can be used to solve sparse linear systems. SpMV has the form of Ax = y [8], where A is an m by n (m rows and n columns) sparse matrix, x is a dense vector of length n, y is a dense vector (The result of SpMV) of length m. A sparse matrix is a matrix in which most of its elements are zeros. A dense vector is a vector in which most of its elements are non-zeros. The sparsity of the matrix is the number of zero-valued elements divided by the total number of elements in the matrix (1 minus the density of the matrix, the sum of the sparsity and the density should equal 100%). SpMV itself isn't a complex algorithm [4], but it might take a huge amount of time especially when we deal with big matrices. When matrices are sparse, the algorithm wastes a great deal of time trying to multiply zero elements by vector elements and the more sparse the matrix is (increasing sparsity), the more time is wasted.

A linear system (system of linear equations) is a collection of two or more linear equations that include the same set of variables. SpMV can be effectively used to solve small-scale to large-scale linear systems [1] [3] (systems of linear equations) and eigenvalue problems. Eigenvalue problems in which only a subset of eigenvalues and eigenvectors are nearly ubiquitous targeting a subset of eigenspace in a big variety of scientific applications. Large eigenvalue problems are solved by iterative techniques which necessitates the need to efficiently improve the SpMV operation on the CPU and the GPU as well. As a matter of fact, improving the SpMV operation is extremely critical to the performance of a variety of scientific applications.

#### **CHAPTER 3**

## **CONFIGURATION INTERACTION (CI)**

## **The Schrödinger Equation:**

The Schrödinger equation is a mathematical equation that can be used to study non-relativistic (NR) quantum mechanical systems. It was named after Erwin Schrödinger, a scientist who deduced the equation in 1925. Although there are other formulations of Quantum Chemistry (e.g., Bohmian Mechanics), it is the case that most NR quantum mechanical system of interest to chemical physics and physical systems are most readily described and represented. Hence, the Schrödinger equation is considered the core of any quantum mechanical system of interest.

The Time-independent Schrödinger equation is illustrated below:

$$\left[-\frac{\overline{h}^{2}}{2m}\nabla^{2}+V(r)\right]\psi(r)=E\ \psi(r)$$

Where r is a 3N-Dimensional vector of the coordinates of particles.

$\stackrel{\wedge}{H} \psi = E \psi \text{ (General Form)}$

Where:

h: Planck's constant  $(6.62607004 \times 10^{-34} \text{ J.s})$ .

$\overline{h} = h/2 \pi$ .

m: Generalized Mass.

$\nabla^2$ : Second Derivative (Laplacian).

V: Potential Energy.

ψ: Wavefunction.

There are multiple techniques and methods that have been used to solve the Schrödinger equation (i.e., figuring out the wavefunction and the energy) for a quantum system. Mean field methods, Hartree-Fock (HF) [17] and density function field (DFT) methods, aka the self-consistent field (SCF) methods are, approximation methods that are widely used to determine the wavefunction and the energy of a quantum system. In the HF method, there is an assumption that the wavefunction can be approximated using a single Slater determinant (A representation of the wavefunction). DFT also uses a single determinant, but is more properly classified as an effective potential method, and as such the HF solution is considered a starting point for many methods that deal with many-electron systems.

### **Hartree-Fock Method:**

FC = SCE

Where:

F: Fock operator.

C: Matrix (a wavefunction) of expansion coefficients.

S: Overlap matrix.

E: Energy.

The electrons are repelled by mean fields of each other.

Post-Hartree-Fock methods are considered a group of methods that were created in order to improve the Hartree-Fock results. Electron correlation is the interaction among electrons in the electronic structure of a quantum system. Electron correlation is an accurate way of including the repulsions among electrons. Electron correlation is considered by post-Hartree-Fock methods as opposed to the Hartree-Fock method, where repulsions are averaged.

Consequently, it is convenient to define

$E_{corr} = \varepsilon_o - E_o$

E<sub>corr:</sub> Electron Correlation Energy.

$\varepsilon_0$ : True (exact) ground state energy.

E<sub>o</sub>: HF energy.

Coupled Cluster (CC) method [18] [60] is another numerical method that is used to describe

many-body systems. The CC method is considered the most accurate post-Hartree-Fock method

for solution to the Schrödinger equation for the ground electron state of molecules near their

equilibrium geometries. Instead of the linear expansion of the wavefunction used by Configuration

Interaction, CC uses an exponential expansion. CC takes the Hartree-Fock method and builds

multi-electron wavefunctions by using the exponential cluster operator to account for electron

correlation. One can think of CC as the product of excitations, while Configuration Interaction is

the sum of excitations.

**Perturbation Theory:**

The Møller-Plesset (MP) treatment of electron correlation is based on an approach that is used

to treat complex systems that are nearby, in a function space absolutely to a solvable simpler

system, called perturbation theory [61]. In perturbation theory, we have:

$\dot{H} = \dot{H}_o + \dot{V}$

$E = E_0 + E_1 + E_2 + \dots$

Where:

H: Perturbed Hamiltonian.

H<sub>o</sub>: Unperturbed Hamiltonian.

19

#### **Configuration Interaction:**

Turning attention to Configuration Interaction (CI), which is a very useful method in Quantum chemistry has made important contributions to understanding environmental fates of pollutants. Quantum mechanical calculations of molecular electronic structure contribute to the greening of many chemical practices [51]. This could be done via replacing experiments with computation as a variety of complex chemical species and reactions, including the green alternative. Configuration Interaction [19] is a linear method for solving the nonrelativistic Schrödinger equation for quantum chemical multi-electron systems. Relativistic wave equations are applicable to massive particles at high energies and high velocities comparable to the speed of light. Unlike other techniques and methods that can only deal with the ground state, the CI method can deal with the ground state as well as multiple excited states. The term "Configuration" basically refers to the linear combination of Slater determinants that are used for the wavefunction. The term "Interaction" refers to mixing many-electron basis functions. CI uses a linear combination of configuration state functions (CSFs), of which Hartree-Fock method uses only one. The CI approach suffers the size-extensivity problem, which has significantly reduced the use of the CI approach. Although its unique capabilities for excited states, the bigger the CI matrix, the more electron correlation can be captured. However, due to the large size of the CI sparse matrix that is involved in CI computations, a good amount of the time spent on the eigenvalue computations is associated with the multiplication of the CI sparse matrix by numerous vectors which is basically known as SpMV.

The trial CI wave function is written as a linear combination of determinants with the expansion coefficients determined by requiring that the energy should be a minimum. The MOs (Molecular Orbitals) used for building the excited Slater determinants are often taken from a Hartree–Fock calculation. Determinants can be Singly, Doubly, Triply, etc., excited from relative to the HF configuration.

#### **The CI Matrix Elements:**

The CI matrix elements  $H_{ij}$  can be calculated by a strategy similar to that employed for calculating the energy of a single determinant used for deriving the Hartree–Fock equations [57]. In the CI case, this will involve expanding the determinants in a sum of products of Molecular Orbitals, consequently making it possible to express the CI matrix elements in terms of MO integrals. There are some general features that make many of the CI matrix elements equal to zero.

When the HF wave function is a singlet, this excited determinant often contains 2 more open shells than the reference. The corresponding CI matrix element can be written in terms of integrals over MOs, and the spin dependence can be separated out. If there is a different number of  $\alpha$  and  $\beta$  spin-MOs, there will always be at least one integral  $\langle a|b\rangle = 0$ . That matrix elements between different spin states are zero may be fairly obvious. If we are interested in a singlet wave function, only singlet determinants can enter the expansion with non-zero coefficients. However, if the Hamiltonian operator includes for example the spin-orbit operator, matrix elements between singlet and triplet determinants are not necessarily zero, and the resulting CI wave function will be a mixture of singlet and triplet determinants.

The usual non-relativistic Hamiltonian operator does not contain spin, thus if two determinants have different total spin, the corresponding matrix element is zero. This situation occurs not only the obvious case if an electron is excited from an  $\alpha$  spin-MO to a  $\beta$  spin-MO, but also when an excitation is reducible to a sum of functions of spin states.

If the system contains point group symmetry, there are additional CI matrix elements that become zero. The symmetry of a determinant is given as the direct product of the symmetries of the MOs. The Hamiltonian operator always belongs to the totally symmetric representation, thus if two determinants belong to different irreducible representations, the CI matrix element is zero. This is again fairly obvious if the interest is in a state of a specific symmetry, only those determinants that have the correct symmetry can contribute.

The excited Slater determinants are generated by removing electrons from occupied orbitals, and placing them in virtual orbitals. The number of excited Slater Determinants (SDs) is thus a

combinatorial problem, and therefore increases factorially with the number of electrons and basis functions. Consider for example a system such as  $H_2O$  with a 6-31G(d) basis. There are 10 electrons and 38 spin-MOs, of which 10 are occupied and 28 are empty.

The number of SDs =

$$38! / [10! (38 - 10)!]$$

The number of determinants (or CSFs) that can be generated grows wildly with the excitation level! Even if the C<sub>2</sub>V symmetry of H<sub>2</sub>O is employed, there is still a total of 7536400 singlet CSFs with A<sub>1</sub>V symmetry.

| Excitation Level (n) | Total number of CSFs |

|----------------------|----------------------|

| 1                    | 71                   |

| 2                    | 2556                 |

| 3                    | 42596                |

| 4                    | 391126               |

| 5                    | 2114666              |

| 6                    | 7147876              |

| 7                    | 15836556             |

| 8                    | 24490201             |

| 9                    | 29044751             |

| 10                   | 30046752             |

TABLE 1: The number of singlet CSFs as a function of excitation level for H2O with a 6-31G(d) basis [57]

For the sake of developing a computationally tractable model [57], the number of excited determinants in the CI expansion has to be reduced. Truncating the excitation level at one (CI with Singles (CIS)) does not give any improvement over the HF result as all matrix elements between the HF wave function and singly excited determinants are zero. CIS is of the same accuracy as HF for the ground state energy, although higher roots from the secular equations may be used as approximations to excited states. Only doubly excited determinants have matrix elements with the HF wave function different from zero; thus the lowest CI level that gives an improvement over the HF result is to include only doubly excited states, yielding the CI with Doubles (CID) model. Compared with the number of doubly excited determinants, there are relatively few singly excited determinants, and including these gives the CISD method. Computationally, this is only a marginal increase in effort over CID. Although the singly excited determinants have zero matrix elements

with the HF reference, they enter the wave function indirectly as they have non-zero matrix

elements with the doubly excited determinants.

Configuration State Functions (CSFs) are a linear combination of Slater Determinants [58].

Molecular Orbitals (MO) are one dimensional objects that are used to create N-dimensional Slater

Determinants (or superposition of Slater Determinants) [59]. If we have a product of MOs and

apply the anti-symmetrizer operation to it, you will create a single N-dimensional SD.

Small systems, but larger than the 6-31G(d) model problem used above, at the CISD level result

in millions of CSFs. The variational problem is to extract one or possibly a few of the lowest

eigenvalues and eigenvectors of a matrix the size of millions squared. This cannot be done by

standard diagonalization methods where all the eigenvalues are found. There are iterative methods

for extracting one, or a few, eigenvalues and eigenvectors of a large matrix.

The CI Matrix:

In this section, the CI matrix is considered in more depth [60]. We will take a linear

combinations of Slater Determinants.

$|\Phi_0\rangle = |\psi_0\rangle + \sum_{ar} C_a^r |\psi_a^r\rangle + \sum_{arb} C_{ab}^{rs} |\psi_{ab}^{rs}\rangle + ...$

Where:

$|\Phi_0\rangle$ : CI wave function.

$|\Psi_0\rangle$ : Hartree-Fock wave function.

C: Some coefficient that describes amplitude of a specific Slater Determinant  $(\Psi)$ .

All the possible single excitations. An electron is excited from orbital a to orbital r:

$\sum C_a^r |\psi_a^r>$

23

All the possible double excitations:

$$\sum_{arb} C^{rs}_{ab} \mid \psi^{rs}_{ab} >$$

... All the way up to n excitations (excite n electrons).

If we take that to N-electron excitations, then we will have what is called Full CI. In the case of Full CI, we have every single electron and every possible Slater determinant using all the orbitals available to us. Full CI is the exact solution to the nonrelativistic Schrödinger equation within the basis set. If we truncate at Single Excitations, then we will have what's called CIS, if we have Double Excitations, then we will have CISD, and this will continue until we reach Full CI.

The Slater determinant is one such basis function i.e., it represents no electron excitation from the reference. The Hamiltonian is expressed in the basis of these Slater determinants. So, we will diagonalize the Hamiltonian matrix and get the lowest eigenvalue from that to be our ground state.

$$H c = E c$$

The Hamiltonian matrix (CI matrix, H) will act on a vector of all of our coefficients (c) which will give the energy out (E) and the coefficients back. So, what does the Hamiltonian matrix look like? It looks like the following:

$$H = \begin{bmatrix} <\Psi_0|H|\Psi_0> <\Psi_0|H|S> <\Psi_0|H|D> \cdots \\    \cdots \\    \cdots \\ \vdots & \vdots & \vdots & \vdots \\ . & \vdots$$

And, if there is no truncation, this will continue all the way to N Full Excitations  $\langle N|H|N\rangle$   $\langle \Psi o|H|S\rangle$  is the reference function interacting with single excitations.

$<\Psi$ o|H|D> is the reference function interacting with double excitations.

For single excitations, if we have N electrons and K basis functions, the number of single excitations we will have will be:

$$\binom{N}{1}\binom{2K-N}{1} = [N! / ((N-1)! * 1!)] * [(2K-N)! / ((2K-N-1)! * 1!)]$$

The previous value can be very large depending on the number of electrons you have (N) and the number of basis functions you have. The total number of Slater Determinants you will get is:

$$\binom{2K-N}{N}$$

For double excitations, if we have N electrons and K basis functions, the number of double excitations we will have will be:

$$\binom{N}{2} \binom{2K-N}{2}$$

So, our task is to calculate these matrix elements and then diagonalize this matrix [62] for the lowest eigenvalue which will be the ground state energy. We have to figure out what the energy of a linear combination of Slater determinants is.

If we have 2 Slater determinants which are exactly identical, for every pair of orbitals, the orbitals can be lined up exactly.

This matrix element will be  $\Sigma_i < i|h|i> + \frac{1}{2} \Sigma_{ij} < ij||ij>$ . This is the same for Hartree–Fock ground state.

If we have 2 Slater determinants that are different by 1 electron. One electron is in orbital m and one electron is in orbital p.

This matrix element will be  $\langle m|h|p \rangle + \Sigma_i \langle m|i||p|i \rangle$

If we have 2 Slater determinants that are different by 2 electrons.

This matrix element will be < m n || p q > - one 2-electron composite integral made from 2 usual integrals.

If we have 3 or more electrons different  $\Rightarrow$  0

# **Example:**

Let take H<sub>2</sub> as an example. It has one S orbital on each of the hydrogen atoms. In this case, the smallest basis set will contains only 2 functions and a small number of electrons (2). There are only 6 possible Slater determinants. We will include these 6 Slater determinants in the CI matrix and in this case, the CI matrix will be a 6 by 6 matrix.

$$|\psi_0\rangle$$

$|\psi_{\bar{1}}^{\bar{2}}\rangle$   $|\psi_{\bar{1}}^2\rangle$   $|\psi_1^2\rangle$   $|\psi_1^2\rangle$   $|\psi_{1\bar{1}}^{\bar{2}}\rangle$

S S T S T S

(Eliminated) (Eliminated) (Eliminated)

Before we do that, we can exclude some of them. Our ground state is a singlet. If we have a triplet, it is not going to mix with our ground state determinant. When we integrate out the spins, we will get 0 for that matrix element. So, anything that is a triplet is going to be eliminated since we are concerned with the ground state energy right now. In the ground state, we have 2 electrons that are in the  $\sigma_g$  orbital, g \* g gives you the g ground state, so the g ground state is not going to mix with the excited state. The only thing that is left is the double excitation (the first one from the right). The CI matrix will be:

$$\mathbf{H} = \begin{bmatrix} <\Psi_{0} \mid H \mid \Psi_{0} > & <\Psi_{0} \mid H \mid \Psi_{1\bar{1}}^{2\bar{2}} > \\ <\Psi_{1\bar{1}}^{2\bar{2}} \mid H \mid \Psi_{0} > & <\Psi_{1\bar{1}}^{2\bar{2}} \mid H \mid \Psi_{1\bar{1}}^{2\bar{2}} > \end{bmatrix}$$

Expressing the matrix elements in terms of integrals:

$$<\psi_{0} \mid H \mid \psi_{0}> = <1 \mid h \mid 1> + <\bar{1} \mid h \mid \bar{1}> + <1\bar{1} \mid 1\bar{1}> = 2h_{11} + j_{11}$$

$$(h_{11}) \qquad (h_{11})$$

$$<1\bar{1} \mid |1\bar{1}> = <1\bar{1} \mid |1\bar{1}> - <11 \mid |\bar{1}\bar{1}>$$

$$(j_{11}) \qquad (0)$$

$$<\psi_{1\bar{1}}^{\bar{2}\bar{2}} \mid H \mid \psi_{1\bar{1}}^{2\bar{2}}> = 2h_{22} + J_{22}$$

$$<\psi_{0} \mid H \mid \psi_{1\bar{1}}^{2\bar{2}}> = <1\bar{1} \mid |2\bar{2}> = <1\bar{1} \mid |2\bar{2}> - <12 \mid |\bar{1}\bar{2}> = K_{12} - 0 = K_{12}$$

The results are in the following 2 X 2 Hamiltonian matrix

$$\mathbf{H} = \begin{bmatrix} 2h_{11} + j_{11} & k_{12} \\ k_{12} & 2h_{22} + j_{22} \end{bmatrix}$$

Because this matrix is so small, the lowest eigenvalue of this matrix will be the Full CI energy. If we subtract out the energy of the Hartree-Fock determinant (2h11 + J11), then we will get the correlation energy.

$$H - E_0 1 = \begin{bmatrix} 0 & k_{12} \\ k_{12} & 2\Delta \end{bmatrix}$$

$$2 \Delta = (2h_{22} + J_{22}) - (2h_{11} + J_{11})$$

$$\begin{bmatrix} 0 - E_{corr} & k_{12} \\ k_{12} & 2\Delta - E_{corr} \end{bmatrix} = 0$$

$$-E_{corr}(2\Delta - E_{corr}) - k_{12}^2 = 0$$

$$E_{corr}^{2} - 2\Delta E_{corr} - k_{12}^{2} = 0$$

$$E_{corr} = \frac{2\Delta - \sqrt{4\Delta^2} + 4k_{12}^2}{2}$$

$$E_{corr} = \Delta - \sqrt{\Delta^2} - k_{12}^2$$

So E<sub>corr</sub> is the correlation energy within the basis set.

In general, Full CI [55] [56] is very expensive. The scaling for Full CI is on the order of O(N!), where N is the number of electrons. Full CI is exponential with the number of electrons and also with the basis set size. Generally, both the number of electrons and the number of basis functions affect computational costs, but the number of basis functions is usually the limiting factor. The number of basis functions that we use depends on and scales with the number of atoms and the types of atoms. A small calculation would have 14 basis functions per carbon atom. A big calculation on Chromium might have 93 basis functions per atom.

#### **CHAPTER 4**

# **COMMON FORMATS**

The format in which the matrix is stored in the CPU memory or the GPU memory affects both the performance of the SpMV operation and the amount of memory used. In this section, we will be discussing some of the features of various sparse matrix storage formats that are used for storing sparse matrices on the CPU or the GPU. We will also be discussing the SpMV kernel that is used along with each format. Besides, we will take a look at the pros and cons of each single storage format in terms of performance and the amount of used memory.

# 1. The Compressed Sparse Row (CSR) or Compressed Row Storage (CRS) Format [2][11]:

The CSR format compresses a sparse matrix into three vectors:

- The Value vector: contains all the non-zero entries.

- The Column vector: contains column index of each non-zero entry.

- The RowPtr vector: contains the index of the first non-zero entry of each row in the "Value" vector. We add the number of non-zero entries in the sparse matrix as the last element of the RowPtr vector.

In terms of memory, the CSR format is very powerful and efficient since no zero-padding [7] is needed.

In terms of performance, the CSR format is efficient for SpMV operations implemented on CPUs with multiple cores [2]. On the other hand, on the GPU, the CSR format isn't as efficient as the ELLPACK format and shows a worse throughput than the ELLPACK format when it comes to SpMV due to the lack of coalesced access to global memory on the GPU [2].

## Example:

Consider the following 6 by 5 sparse matrix A, where:

$$A = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 2 & 0 & 3 \\ 0 & 4 & 0 & 0 & 5 \\ 0 & 0 & 6 & 0 & 0 \\ 0 & 0 & 0 & 7 & 0 \\ 0 & 0 & 0 & 0 & 8 \end{bmatrix}$$

The three vectors will be:

Value = 1, 2, 3, 4, 5, 6, 7, 8

Column = 0, 2, 4, 1, 4, 2, 3, 4

RowPtr = 0, 1, 3, 5, 6, 7, 8

Algorithm 1 describes the SpMV kernel for the CSR format.

\_\_\_\_\_

Algorithm 1 is the SpMV kernel for the CSR format.

#### **Input:**

• Value Vector: All the non-zero entries.

- **Column Vector:** The column index of each non-zero entry.

- **Vector:** The vector that the matrix will be multiplied by.

- **RowPtr:** The index of the first non-zero entry of each row in the "Value" array.

#### Output:

• **Result:** The result of the SpMV process

```

\begin{aligned} & \textbf{SpMV\_CSR(Value, Column, Vector, RowPtr, Result)} \\ & \text{for } i \leftarrow 0 \text{ to } \text{ROWS - 1 do} \\ & \text{Start} \leftarrow \text{RowPtr[i]} \\ & \text{End} \leftarrow \text{RowPtr[i + 1]} \\ & \text{for } j \leftarrow \text{Start to End - 1 do} \\ & \text{Temp} \leftarrow \text{Temp} + (\text{Value[j]} * \text{Vector[Column[j]]}) \\ & \text{Result[i]} \leftarrow \text{Temp} \\ & \text{Temp} \leftarrow 0.00 \end{aligned}

```

Algorithm 1. The SpMV kernel for the CSR format

# 2. The ELLPACK (ELL) Format [2]:

In the ELLPACK (ELL) format, each single row will have the same number of elements. If a row contains fewer non-zero elements, then it will be padded with zeros in order to reach the length of the longest non-zero entry row. For example, consider a 10 by 10 diagonal matrix (or an identity

matrix) with the last row full of non-zero entries. In this case, each single row in the matrix except the last row will be padded with 9 zeros in order to reach the length of the longest non-zero entry row. Thus, instead of storing 19 elements in memory, we store 100 elements in memory.

| г1    | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ر0 |

|-------|---|---|---|---|---|---|---|---|----|

| 0     | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  |

| 0     | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0  |

| 0     | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0  |

| 0     | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0  |

| 0     | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0  |

| 0     | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0  |

| 0     | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0  |

| 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0  |

| $L_1$ | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1  |

A 10x10 Identity Matrix with the last row full of non-zero entries

The ELLPACK (ELL) format compresses a sparse matrix into two matrices:

- The NonZerosEntries matrix: All the non-zero entries.

- The Column matrix: The column index of each non-zero entry.

In terms of memory, the ELLPACK format introduces a noticeable redundancy since zero-padding [7] is needed in order to reach the length of the longest non-zero entry row. So, the ELLPACK format is less efficient than the CSR format from the memory standpoint.

In terms of performance, the ELLPACK format achieves better performance on the GPU than on the CPU due to the coalesced access to global memory on the GPU [2]. To ensure coalesced global memory access on the GPU, the number of rows has to be a multiple of the block size. This can be achieved by adding extra rows with zero entries [2].

#### Example:

Consider the following 6 by 5 sparse matrix A, where:

$$A = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 2 & 0 & 3 \\ 0 & 4 & 0 & 0 & 5 \\ 0 & 0 & 6 & 0 & 0 \\ 0 & 0 & 0 & 7 & 0 \\ 0 & 0 & 0 & 0 & 8 \end{bmatrix}$$

The two matrices will be:

NonZerosEntries =

$$\begin{bmatrix} 1 & 0 \\ 2 & 3 \\ 4 & 5 \\ 6 & 0 \\ 7 & 0 \\ 8 & 0 \end{bmatrix}$$

$$Column = \begin{bmatrix} 0 & -1 \\ 2 & 4 \\ 1 & 4 \\ 2 & -1 \\ 3 & -1 \\ 4 & -1 \end{bmatrix}$$

Algorithm 2 describes the SpMV kernel for the ELLPACK format (thread per row) [6].

Algorithm 2 is the SpMV kernel for the ELLPACK format.

#### **Input:**

- NonZerosEntries Matrix: All the non-zero entries.

- Column Matrix: The column index of each non-zero entry.

- **Vector:** The vector that the matrix will be multiplied by.

- **MaxNonZeros:** The length of the longest non-zero entry row.

## **Output:**

• **Result:** The result of the SpMV process.

\_\_\_\_\_

```

\begin{aligned} & \textbf{SpMV\_ELLPACK}(\textbf{NonZerosEntries}, \textbf{Column}, \textbf{Vector}, \textbf{Result}, \textbf{MaxNonZeros}) \\ & \text{for } r_1 \leftarrow 0 \text{ to } \textbf{ROWS} - 1 \text{ do} \\ & \text{for } r_2 \leftarrow 0 \text{ to } \textbf{MaxNonZeros} - 1 \text{ do} \\ & \text{if } \textbf{Column}[r_1][r_2] = -1 \text{ then} \\ & \text{exit loop} \\ & \text{Temp} = \text{Temp} + (\textbf{NonZerosEntries}[r_1][r_2] * \textbf{Vector}[\textbf{Column}[r_1][r_2]]) \\ & \textbf{Result}[r_1] \leftarrow \textbf{Temp} \\ & \textbf{Temp} \qquad \leftarrow 0.00 \end{aligned}

```

Algorithm 2. The SpMV kernel for the ELLPACK format (thread per row)

# 3. The ELLPACK-R (ELL-R) Format:

The performance of the SpMV operation can be further improved by adding an extra vector that includes the number of non-zero entries in each row (NonZerosCount vector). In this case, No iterations will be wasted in the loop since only non-zero entries will be involved in calculations [7].

## Example:

Consider the following 6 by 5 sparse matrix A, where:

$$A = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 2 & 0 & 3 \\ 0 & 4 & 0 & 0 & 5 \\ 0 & 0 & 6 & 0 & 0 \\ 0 & 0 & 0 & 7 & 0 \\ 0 & 0 & 0 & 0 & 8 \end{bmatrix}$$

The three matrices will be:

NonZerosEntries =

$$\begin{bmatrix} 1 & 0 \\ 2 & 3 \\ 4 & 5 \\ 6 & 0 \\ 7 & 0 \\ 8 & 0 \end{bmatrix}$$

$$Column = \begin{bmatrix} 0 & -1 \\ 2 & 4 \\ 1 & 4 \\ 2 & -1 \\ 3 & -1 \\ 4 & -1 \end{bmatrix}$$

RowLength =

$$\begin{bmatrix} 1 \\ 2 \\ 2 \\ 1 \\ 1 \\ 1 \end{bmatrix}$$

Algorithm 3 describes the SpMV kernel for the ELLPACK-R format (thread per row).

\_\_\_\_\_

Algorithm 3 is the SpMV kernel for the ELLPACK-R format.

# **Input:**

- **NonZerosEntries Matrix:** All the non-zero entries.

- **Column Matrix:** The column index of each non-zero entry.

- **Vector:** The vector that the matrix will be multiplied by.

- **NonZerosCount:** The count of the non-zero entries per row.

#### **Output:**

• **Result:** The result of the SpMV process.

```

\begin{aligned} & \textbf{SpMV\_ELLPACK\_R(NonZerosEntries, Column, Vector, NonZerosCount, Result)} \\ & \text{for } r_1 \leftarrow 0 \text{ to } ROWS - 1 \text{ do} \\ & \text{End} \leftarrow \text{NonZerosCount}[r_1] \\ & \text{for } r_2 \leftarrow 0 \text{ to } \text{End} - 1 \text{ do} \\ & \text{Temp} \leftarrow \text{Temp} + (\text{NonZerosEntries}[r_1][r_2] * \text{Vector}[\text{Column}[r_1][r_2]]) \\ & \text{Result}[r_1] \leftarrow \text{Temp} \\ & \text{Temp} \qquad \leftarrow 0.00 \end{aligned}

```

Algorithm 3. The SpMV kernel for the ELLPACK-R format (thread per row)

# 4. The Sliced ELLPACK (Sliced ELL) Format:

The Sliced ELLPACK Format was introduced in order to reduce the redundancy that is inherent in the ELLPACK Format. In this format, the matrix has to be divided first into submatrices (slices) and then each slice is stored in the ELLPACK format. Therefore, the number of extra zero entries (zero-padding) will be determined by the length of the longest non-zero entry row in each slice, rather than in the whole sparse matrix, so we will have less zero-padding, which definitely saves memory.

# Example:

Consider the following 6 by 5 sparse matrix A, where:

$$A = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 2 & 0 & 3 \\ 0 & 4 & 0 & 0 & 5 \\ 0 & 0 & 6 & 0 & 0 \\ 0 & 0 & 0 & 7 & 0 \\ 0 & 0 & 0 & 0 & 8 \end{bmatrix}$$

Slice

$$1 = \begin{bmatrix} 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 2 & 0 & 3 \end{bmatrix}$$

Slice2 =

$$\begin{bmatrix} 0 & 4 & 0 & 0 & 5 \\ 0 & 0 & 6 & 0 & 0 \end{bmatrix}$$

Slice3 =

$$\begin{bmatrix} 0 & 0 & 0 & 7 & 0 \\ 0 & 0 & 0 & 0 & 8 \end{bmatrix}$$

NonZerosEntries1 =

$$\begin{bmatrix} 1 & 0 \\ 2 & 3 \end{bmatrix}$$

$$Column1 = \begin{bmatrix} 0 & -1 \\ 2 & 4 \end{bmatrix}$$

NonZerosEntries2 =

$$\begin{bmatrix} 4 & 5 \\ 6 & 0 \end{bmatrix}$$

$$Column2 = \begin{bmatrix} 1 & 4 \\ 2 & -1 \end{bmatrix}$$

NonZerosEntries3 =

$$\begin{bmatrix} 7 \\ 8 \end{bmatrix}$$

$$Column3 = \begin{bmatrix} 3 \\ 4 \end{bmatrix}$$

Notice that we have one column in matrices, NonZerosEntries3 and Column3 instead of two, in other words, no zero-padding has occurred. Algorithm 4 describes the SpMV kernel for the Sliced ELLPACK format (thread per row).

\_\_\_\_\_

Algorithm 4 is the SpMV kernel for the Sliced ELLPACK format.

### **Input:**

- NonZerosEntries Matrix: All the non-zero entries.

- **Column Matrix:** The column index of each non-zero entry.

- **Vector:** The vector that the matrix will be multiplied by.

- **Rows:** The number of rows in the slice.

- **Cols:** The length of the longest non-zero entry row in the slice.

#### **Output:**

• **Result:** The result of the SpMV process.

```

\begin{aligned} & \textbf{SpMV\_SlicedELLPACK}(\textbf{NonZerosEntries}, \textbf{Column}, \textbf{Vector}, \textbf{Result}, \textbf{Rows}, \textbf{Cols}) \\ & \text{for } r_1 \leftarrow 0 \text{ to } \textbf{Rows} - 1 \text{ do} \\ & \text{for } r_2 \leftarrow 0 \text{ to } \textbf{Cols} - 1 \text{ do} \\ & \text{if } \textbf{Column}[r_1][r_2] = -1 \text{ then} \\ & \text{exit loop} \\ & \textbf{Temp} \leftarrow \textbf{Temp} + (\textbf{NonZerosEntries}[r_1][r_2] * \textbf{Vector}[\textbf{Column}[r_1][r_2]]) \\ & \textbf{Result}[r_1] \leftarrow \textbf{Temp} \\ & \textbf{Temp} \leftarrow 0.00 \end{aligned}

```

Algorithm 4. The SpMV kernel for the Sliced ELLPACK format (thread per row)

# 5. The Sliced ELLPACK-R (Sliced ELL-R) Format:

It's worth mentioning that the Sliced ELLPACK format can be even further extended to be Sliced ELLPACK-R. In this case, the performance of the SpMV operation will be improved by adding an extra vector that counts the number of non-zeros in each row (NonZerosCount vector), just like the ELLPACK-R format. Algorithm 5 describes the SpMV kernel for the Sliced ELLPACK-R format (thread per row).

Algorithm 5 is the SpMV kernel for the Sliced ELLPACK-R format.

#### **Input:**

- NonZerosEntries Matrix: All the non-zero entries.

- Column Matrix: The column index of each non-zero entry.

- **Vector:** The vector that the matrix will be multiplied by.

- NonZerosCount: The count of the non-zero entries per row in the slice.

- **Rows:** The number of rows in the slice.

## **Output:**

• **Result:** The result of the SpMV process.

```

\begin{tabular}{ll} \textbf{SpMV\_SlicedELLPACK\_R(NonZerosEntries, Column, Vector, NonZerosCount, Result, Rows)} \\ for $r_1 \leftarrow 0$ to $Rows - 1$ do \\ End \leftarrow NonZerosCount[$r_1$] \\ for $r_2 \leftarrow 0$ to $End - 1$ do \\ Temp \leftarrow Temp + (NonZerosEntries[$r_1$][$r_2$] * Vector[Column[$r_1$][$r_2$]]) \\ Result[$r_1$] \leftarrow Temp \\ Temp & \leftarrow 0.00 \\ \end{tabular}

```

Algorithm 5. The SpMV kernel for the Sliced ELLPACK-R format (thread per row)

# 6. The Compressed Sparse Blocks (CSB) Format:

The Compressed Sparse Blocks (CSB) format [12] [13] [14] is used for storing sparse matrices. The CSB format partitions the n X n matrix into  $n^2/z^2$  equal-sized z X z square blocks using a block size parameter z. The CSB format consists of the following:

- The **Value** vector: The Value vector is of length nnz. It stored all the non-zero elements of the sparse matrix.

- The **row\_idx** and **col\_idx** vectors: They track the row index and the column index of each non-zero entry inside the Value vector with regard to the block, not the whole entire matrix. So row\_idx and col\_idx range from 0 to z − 1.

- The Block\_ptr vector: It stores the index of the first non-zero entry of each block inside the Value vector.

A comparison among the common formats in terms of memory and performance on the GPU is illustrated in the following table (Table 2). Note that the information in the following table might be different depending on the nature of the matrix and the sparsity pattern of it.

| Format            | Memory                                      | Performance         |

|-------------------|---------------------------------------------|---------------------|

| CSR               | Good                                        | Bad                 |

| ELLPACK (ELL)     | Bad (Zero Padding)                          | Good                |

| ELLPACK-R (ELL-R) | Bad (Zero Padding)                          | Better than ELLPACK |

| Sliced ELLPACK    | Bad (Zero Padding), but better than ELLPACK | Good                |

| Sliced ELLPACK-R  | Bad (Zero Padding), but better than ELLPACK | Better than ELLPACK |

**TABLE 2: Common Formats**

In the proposed model, we stored the CI Reference region, which is more dense in the ELLPACK format instead of the ELLPACK-R format although the ELLPACK-R format is generally faster than the ELLPACK format. We applied the warp technique to the proposed SpMV kernel, we assigned a warp to each single row in the Reference region and in order to efficiently do that, each row has to be a multiple of 32, consequently we padded the rows in the Reference region with zeros in order to achieve that, therefore, we used the ELLPACK format for the Reference region instead on the ELLPACK-R format. We did not use the Sliced ELLPACK format or the Sliced ELLPACK format since there will be an added overhead that is caused by adding the sub-results of the submatrices (slices) in order to get the final result. The Expansion Space region that is extremely sparse, is stored in the CSR format that uses memory very efficiently.

#### **CHAPTER 5**

#### RELATED WORK

SpMV is noticeably a rich area of research that is heavily studied. A lot of work that has been done with regard to SpMV wasn't designed specifically for CI sparse matrices. CI sparse matrices are a special case of sparse matrices in terms of the structure of the sparse matrix as well as the sparsity pattern of the non-zero elements inside the matrix.

In this section, we will review some of the related work to SpMV, some of these studies generally apply to the majority of sparse matrices and others apply to special types of sparse matrices.

F. Vázquez and et al. [22] proposed a new format called ELLR-T. This format is an extension of the ELLPACK-R (ELL-R) format (The ELLPACK-R format was discussed in part 3 of the COMMON FORMATS section). In the ELLR-T format, there is a preprocessing step that has to be performed first [2]. The elements of the NonZerosEntries matrix and the Column matrix are permuted. Also, each row has to be a multiple of 16. In the ELLR-T format, multiple threads (T = 1, 2, 4, 8, 16, 32) operate on single row while executing the SpMV operation. The value T (number of threads per row) can change in order to obtain the best performance with different types of sparse matrices. The ELLR-T format achieves a higher overall performance due to the coalesced and aligned access to global memory.

Due to the fact that SpMV kernels are heavily used in scientific computing, M. M. Baskaran [23] tried to optimize SpMV kernels on GPUs. They tried to evaluate various issues and challenges that deal with and relate to developing robust and high performance kernels for the SpMV operation on NVIDIA GPUs using the CUDA platform. They have proposed a framework that includes both compile-time and run-time optimizations. The compile-time optimizer applies the following optimizations to SpMV kernels that execute on the GPU: exploiting synchronization-free parallelism, optimized thread mapping, optimized global memory access, and exploiting data reuse. There is an optional runtime optimizer. They have created a new blocked storage format for storing and accessing the elements of a sparse matrix in an optimized manner from the GPU

memories. They evaluated their optimizations over two classes of NVIDIA GPU chips, namely, GeForce 8800 GTX and GeForce GTX 280 using a large set of sparse matrices derived from real applications. They compared the performance of their approach with that of existing parallel SpMV implementations. Their optimization techniques resulted in significant performance improvements on both GPUs over existing parallel SpMV implementations by a factor of 2 to 4. Using this framework, they were able to achieve peak SpMV performance that is 70% of the performance observed for SpMV computations using dense matrices stored in sparse format.

M. R. Hugues and et al. [24] proposed an evaluation of several sparse matrix formats that are used by the GPU SpMV kernel. They analyzed the performance when having multiple sparse matrices with a strong distribution of non-zero elements. The sparse matrices that have been used in the study are from the University of Florida. These sparse matrices have different sizes as well as different number of non-zeros. The best results were obtained by using the ELL format for sparse matrices, however various formats that deal with sparse matrices that have a strong distribution of non-zero elements achieve approximately the same performance (2.0 GFLOPS) which is considered poor performance. This study concluded that the performance of SpMV computation depends on the format of the sparse matrix as well as the data structure of the sparse matrix.

B. Neelima and et al. [25] proposed a new format for storing square sparse matrices on the GPU. The newly-developed format can give 2x to 5x performance improvement compared to the CSR format. The CSR format doesn't benefit from global coalescing feature of the GPU. Also, the GPU is underutilized if the number of non-zero elements per row is less than 32 (warp size). The proposed format (CSPR format) reduces the SpMV operation to a constant time and it uses a single data structure (ind vector) as it embeds the row information into column information, hence it can also optimize the memory transfer between the CPU and the GPU. Generally, the CSPR format can be applied to any sparse matrix, but better performance can be achieved when using sparse matrices with a large number of rows with a minimum number of non-zero elements per row and few dense rows distributed in the center. The proposed format can get 2x to 54x performance improvement compared to other sparse matrix formats (CSR, COO, and CSR vector).

A. Monakov and et al. [26] proposed a new storage format that adapts to different sparse matrices in order to improve the performance of the SpMV operation on the GPU. The storage format is called sliced ELLPACK. This format takes parameter S which represents the slice size. The sparse matrix is partitioned into strips (slices or partitions) of length S (S adjacent rows) and each strip is stored in the known ELLPACK format. Sparse matrices that have big variations with regard to the number of non-zero elements per row have less padding (extra zeros) than the ELLPACK format and hence, use less memory. This format uses a single SpMV kernel as opposed to the hybrid ELLPACK/COO format [15], therefore it achieves more performance. The ability to allocate a variable number of threads per row helps to adapt to various different matrices. It's possible to allocate one thread per row in extremely sparse matrices or allocate multiple threads per row.

Some of the developed formats are actually built on one of the conventional (common) formats. For example, J. L. Greathouse and et al. [27] proposed a storage format called the CSR-Adaptive format that is based on the common CSR format (good at memory storage) that maps well to GPUs. The CSR format is frequently used in order to store sparse matrices on the GPU, nonetheless when it comes to the SpMV kernel on the GPU, this format has poor performance because of accessing memory in irregular patterns. The CSR-Adaptive format achieves an average speed up of 14.7x over the conventional CSR format.

F. Vázquez and et al. [28] and J. a Mart and et al. [30] proposes a new storage format for storing sparse matrices on NVIDIA GPUs. This format is called ELLPACK-R. They also implemented the SpMV kernel based on the newly-developed format. The ELLPACK-R format doesn't include conditional branches since it includes the rl (row length) array, in other words the ELLPACK-R format gets rid of useless computations since only non-zero elements of each row in the sparse matrix are considered. They compared the ELLPACK-R format to a variety of other sparse matrix storage formats using different test matrices. Although the performance depends on the pattern of the sparse matrix, the implementation based on ELLPACK-R format achieves noticeable higher performance. The ELLPACK-R format achieves the highest performance when it deals with

matrices of high dimensions, nonetheless the performance gets lower with sparse matrices of small dimensions.

X. Liu and et al. [29] proposed a new SpMV kernel on Intel Xeon Phi Coprocessor that is called Knights Corner (KNC). First, they tested the architecture with a CSR kernel. They got several performance bottlenecks. Then, they designed a new sparse matrix format called ELLPACK Sparse Block (ESB) that is tuned for KNC. The new format adds several features to the ELLPACK format, for example: 1. finite-window sorting in order to improve the SIMD efficiency of the kernel. 2. A bit array to encode nonzero locations to reduce the bandwidth requirement. 3. Column blocking to improve memory access locality. In addition to that, in order to deal with the load balancing problem, they proposed 3 load balancers for the SpMV kernel on KNC. The proposed kernel is 1.85x faster than other kernels that use the CSR format. Speaking of architecture, the SpMV kernel on KNC is 3.52x faster than on dual-socket Intel Xeon Processor E5-2680 and is 1.32x faster than on NVIDIA Tesla K20X.

J. W. Choi and et al. [31] proposed a performance model-driven framework for auto-tuning the SpMV kernel (more specifically, BELLPACK and BCSR kernels) on the GPU. They started out by implementing the blocked CSR (BCSR) format. The BCSR format led them to developing a new sparse matrix storage format called the blocked ELLPACK (BELLPACK) format. Using BELLPACK, they obtained up to 29.0 GFLOP/s in single-precision and 15.7 GFLOP/s in double-precision. Additionally, they worked on tuning the BELLPACK format. They developing a performance model-driven framework for auto-tuning the SpMV kernel for the BELLPACK format using some tuning parameters. This proposed framework is applicable only to matrices with small dense block sub-structures and to BELLPACK and BCSR kernels only.

P. Guo and et al. [32] proposed an auto-tuning framework that can calculate and select CUDA parameters for SpMV kernels in order to attain the optimal performance on the GPU. The proposed framework was tested on GeForce 9500 GTX and GeForce GTX 295 NVIDIA GPUs. The CUDA parameters that they used were the number of threads, the block size, and the warp size. They researched how these parameters can affect the performance of SpMV kernels. The auto-tuning

framework has 237% and 33% performance improvements on average for GeForce 9500 GTX and GeForce GTX 295 GPUs compared to SpMV kernels without the auto-tuning framework.