# **Old Dominion University ODU Digital Commons**

Electrical & Computer Engineering Theses & Disssertations

**Electrical & Computer Engineering**

Summer 2016

# Simulation, Measurement, and Emulation of Photovoltaic Modules Using High Frequency and High Power Density Power Electronic Circuits

Yunas Erkaya Old Dominion University

Follow this and additional works at: https://digitalcommons.odu.edu/ece etds

**Č** Part of the <u>Electrical and Electronics Commons</u>, and the <u>Power and Energy Commons</u>

#### Recommended Citation

Erkaya, Yunas. "Simulation, Measurement, and Emulation of Photovoltaic Modules Using High Frequency and High Power Density Power Electronic Circuits" (2016). Doctor of Philosophy (PhD), dissertation, Electrical/Computer Engineering, Old Dominion University, DOI: 10.25777/nvtx-d822

https://digitalcommons.odu.edu/ece\_etds/7

This Dissertation is brought to you for free and open access by the Electrical & Computer Engineering at ODU Digital Commons. It has been accepted for inclusion in Electrical & Computer Engineering Theses & Disssertations by an authorized administrator of ODU Digital Commons. For more information, please contact digitalcommons@odu.edu.

# SIMULATION, MEASUREMENT, AND EMULATION OF PHOTOVOLTAIC MODULES USING HIGH FREQUENCY AND HIGH POWER DENSITY POWER ELECTRONIC CIRCUITS

by

Yunus Erkaya B.S. June 2010, Istanbul Technical University, Turkey

A Dissertation Submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirements for the Degree of

DOCTOR OF PHILOSOPHY

ELECTRICAL AND COMPUTER ENGINEERING

OLD DOMINION UNIVERSITY August 2016

Approved by:

Sylvain Marsillac (Director)

Isaac Flory (Member)

Shu Xiao (Member)

Christopher Bailey (Member)

Paul Moses (Member)

**ABSTRACT**

SIMULATION, MEASUREMENT, AND EMULATION OF PHOTOVOLTAIC MODULES

USING HIGH FREQUENCY AND HIGH POWER DENSITY POWER ELECTRONIC

**CIRCUITS**

Yunus Erkaya

Old Dominion University, 2016

Director: Dr. Sylvain Marsillac

The number of solar photovoltaic (PV) installations is growing exponentially, and to

improve the energy yield and the efficiency of PV systems, it is necessary to have correct

methods for simulation, measurement, and emulation. PV systems can be simulated using PV

models for different configurations and technologies of PV modules. Additionally, different

environmental conditions of solar irradiance, temperature, and partial shading can be

incorporated in the model to accurately simulate PV systems for any given condition.

The electrical measurement of PV systems both prior to and after making electrical

connections is important for attaining high efficiency and reliability. Measuring PV modules

using a current-voltage (I-V) curve tracer allows the installer to know whether the PV modules

are 100% operational. The installed modules can be properly matched to maximize performance.

Once installed, the whole system needs to be characterized similarly to detect mismatches,

partial shading, or installation damage before energizing the system. This will prevent any

reliability issues from the onset and ensure the system efficiency will remain high.

A capacitive load is implemented in making I-V curve measurements with the goal of

minimizing the curve tracer volume and cost. Additionally, the increase of measurement

resolution and accuracy is possible via the use of accurate voltage and current measurement

methods and accurate PV models to translate the curves to standard testing conditions. A move

from mechanical relays to solid-state MOSFETs improved system reliability while significantly reducing device volume and costs.

Finally, emulating PV modules is necessary for testing electrical components of a PV system. PV emulation simplifies and standardizes the tests allowing for different irradiance, temperature and partial shading levels to be easily tested. Proper emulation of PV modules requires an accurate and mathematically simple PV model that incorporates all known system variables so that any PV module can be emulated as the design requires.

A non-synchronous buck converter is proposed for the emulation of a single, high-power PV module using traditional silicon devices. With the proof-of-concept working and improvements in efficiency, power density and steady-state errors made, dynamic tests were performed using an inverter connected to the PV emulator. In order to improve the dynamic characteristics, a synchronous buck converter topology is proposed along with the use of advanced GaNFET devices which resulted in very high power efficiency and improved dynamic response characteristics when emulating PV modules.

Copyright, 2016, by Yunus Erkaya, All Rights Reserved.

This thesis is dedicated to my family who span the corners of the world.

#### **ACKNOWLEDGMENTS**

I would like to thank Dr. Sylvain Marsillac, my advisor, for his never ending support and guidance throughout my academic career. Never to be forgotten are his contributions in improving my life, my work ethics, and my desire to innovate. I hope to collaborate with him in the future in business and in research to improve the availability of solar energy worldwide. I will never forget his kind and generous nature.

I am grateful for my committee members Dr. Isaac Flory, Dr. Shu Xiao, Dr. Christopher Bailey, and Dr. Paul Moses for their time, their invaluable suggestions and comments. The work presented in this dissertation fell on the shoulders of the committee members quite frequently and I am thankful for the support and brainstorming discussions given.

I would like to thank my colleagues Krishna Aryal, Hareen Sekhar Illa, Tasnuva Ashrafee, Grace Rajan, and Shankar Karki.

I would like to thank my family Hasan Hüseyin Erkaya, Odiléa Rocha Erkaya, Yasin Erkaya, Samir Nepal, Radha Nepal, and Suraksha Nepal.

I would like to thank my wife, Sadiksha Nepal, for rescuing me half-way through my doctoral adventures and standing strong throughout the ups and downs of my education, and always sending me off to research with packs of delicious lunches. Sometimes the quality of the food surpassed the quality of the research, but I digress...

I would like to thank my friends, İlker Cansu, Osman Akif Öztürk, Hamza Fadıl, Kemal Anar, Yusuf Levent Topçu, and Murat Bakırcı for when they talked, I thought about my experiments, and when I talked, I wrote it somewhere in my head to be forgotten later.

I would like to thank the professors in the Electrical and Computer Engineering

Department at Old Dominion University, Dr. Oscar Gonzalez, Dr. Mounir Laroussi, Dr. Hani El-Sayed Ali, Dr. Gon Namkoong, Dr. Youssif Al-Nashif, Dr. Dimitrie Popescu, Dr. Helmut Baumgart, Dr. Khan Iftekharuddin, Dr. Lee Belfore, Dr. Vishnukumar Lakdawala, and Dr. Christian Zemlin.

I would like to thank the people at the Old Dominion University, Mina Samson, Linda Marshall, Deborah Kinney, and Lori Barrett.

I would like to thank Erika Small-Cisco at the Old Dominion University Research Foundation.

I would like to thank Dr. M'hammed Abdous, Dr. Khaled Abul-Hassan, and Dr. Abdelmageed Elmustafa.

I would like to thank Dominion Virginia Power for funding this work and supporting research in the field of photovoltaics.

Finally, I would like to thank the National Science Foundation for the So-LEAP scholarship (National Science Foundation Scholar: Solar Engineering Academic Program).

# TABLE OF CONTENTS

|                                                                      | Page |

|----------------------------------------------------------------------|------|

| LIST OF TABLES                                                       | X    |

| LIST OF FIGURES                                                      | xi   |

| Chapter                                                              |      |

| 1. INTRODUCTION                                                      | 1    |

| 1.1 Introduction                                                     | 1    |

| 1.2 Overview of I-V Curve Tracers                                    | 3    |

| 1.3 Overview of PV Emulators                                         | 14   |

| 1.4 Dissertation Outline                                             | 19   |

| 2. MODELING OF PHOTOVOLTAIC MODULES                                  | 22   |

| 2.1 Introduction                                                     | 22   |

| 2.2 Diode Models                                                     | 23   |

| 2.3 Model Used in Dissertation                                       | 29   |

| 2.4 Conclusions                                                      | 38   |

| 3. I-V CURVE MEASUREMENT OF PHOTOVOLTAIC MODULES                     |      |

| 3.1 Introduction                                                     | 39   |

| 3.2 Generation 1: I-V Curve Tracer Using Mechanical Switches         | 48   |

| 3.3 Generation 1.5: Improvements to Generation 1                     |      |

| 3.4 Generation 2: I-V Curve Tracer Using Solid State Switches        |      |

| 3.5 Conclusions                                                      | 95   |

| 4. EMULATION OF PHOTOVOLTAIC MODULES USING SILICON DEVICES           | 97   |

| 4.1 Introduction                                                     | 97   |

| 4.2 Generation 1: 62.5 kHz Non-Synchronous Buck Converter            | 98   |

| 4.3 Generation 2: 500 kHz Non-Synchronous Buck Converter             |      |

| 4.4 Generation 2.5: Improvements to Generation 2 Dynamic Performance | 126  |

| 4.5 Conclusions                                                      | 129  |

| 5. EMULATION OF PHOTOVOLTAIC MODULES USING GANFET DEVICES            | 131  |

| 5.1 Introduction                                                     |      |

| 5.2 Algorithm Development                                            | 131  |

| 5.3 PV Emulator Circuit Construction                                 | 138  |

| 5.4 Performance under Static and Dynamic Conditions                  | 147  |

| 5.5 Conclusions                                                      |      |

| 6. CONCLUSIONS                                                       | 164  |

| 6.1 Conclusions                                                      | 164  |

|                            | Page |

|----------------------------|------|

| 6.2 Research Contributions | 167  |

| 6.3 Future Work            | 169  |

| REFERENCES                 | 170  |

| VITA                       | 177  |

## LIST OF TABLES

| Table |                                                                                | Page |

|-------|--------------------------------------------------------------------------------|------|

| 1.1.  | Capabilities of different curve tracer topologies                              | 4    |

| 2.1.  | Ideal model initialization parameters                                          | 31   |

| 3.1.  | Comparison of different relays with over 10A current rating                    | 41   |

| 3.2.  | Summary of I-V curve tracing methods explored                                  | 42   |

| 3.3.  | Summary of various charge times for $C_{load} = 4700 \mu F$ for two PV systems | 47   |

| 3.4.  | Bill of materials of the Generation 1.5 curve tracer                           | 59   |

| 3.5.  | Components costs of the curve tracer                                           | 62   |

| 3.6.  | Capacitor charge and discharge times and measurement delay between points      | 67   |

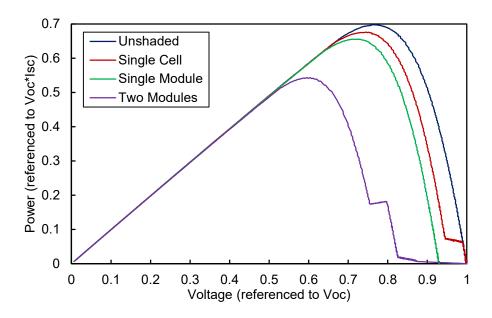

| 3.7.  | Power circuit components                                                       | 75   |

| 3.8.  | Temperature and irradiance measurement circuit components                      | 77   |

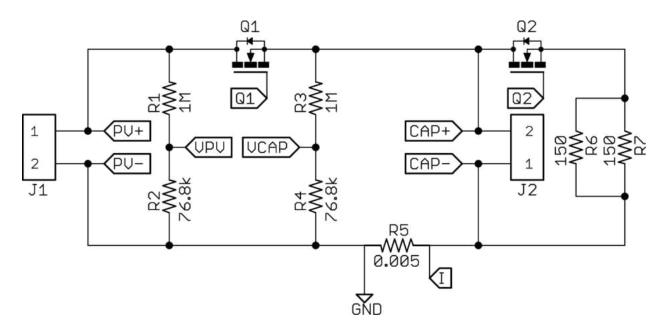

| 3.9.  | Irradiance measurement board circuit components                                | 79   |

| 3.10. | Properties of MOSFETs that fit the selection criteria                          | 85   |

| 3.11. | Component costs per board                                                      | 91   |

| 4.1.  | PV emulator operational parameters                                             | 103  |

| 4.2.  | PV emulator accuracy for various $I_{sc}$ conditions                           | 107  |

| 4.3.  | Hardware components of the photovoltaic emulator                               | 113  |

| 4.4.  | Output Errors of the PV Emulator expressed in RMSD                             | 119  |

| 5.1.  | Properties of the GaN-based PV Emulator                                        | 143  |

## LIST OF FIGURES

| Figure |                                                                                                                                                               | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1.   | Variable resistive load                                                                                                                                       | 4    |

| 1.2.   | Capacitive load                                                                                                                                               | 6    |

| 1.3.   | Electronic load                                                                                                                                               | 9    |

| 1.4.   | Four quadrant power supply                                                                                                                                    | 10   |

| 1.5.   | DC-DC converter                                                                                                                                               | 11   |

| 2.1.   | Single diode model of a solar cell with series and shunt resistances                                                                                          | 24   |

| 2.2.   | Ideal single diode model of solar cell without resistances                                                                                                    | 25   |

| 2.3.   | Two diode model of solar cell with series and shunt resistances                                                                                               | 26   |

| 2.4.   | Comparison of different models when fitting to measured data                                                                                                  | 28   |

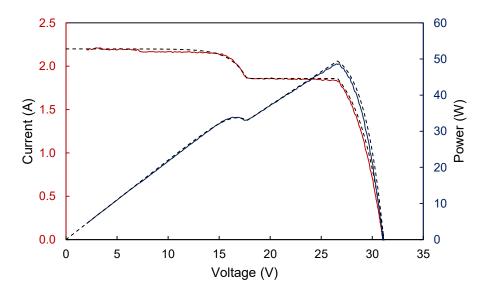

| 2.5.   | Measured (solid line) vs. simulated (dashed line) I-V curves                                                                                                  | 30   |

| 2.6.   | Measured (solid line) vs. simulated (dashed line) P-V curves                                                                                                  | 30   |

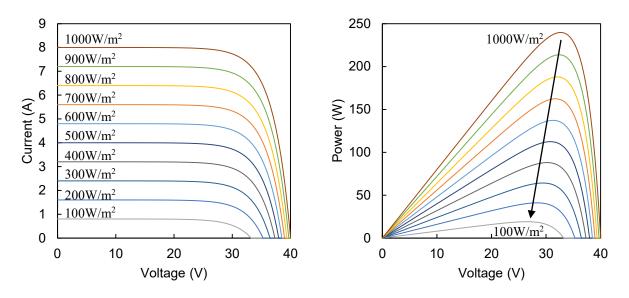

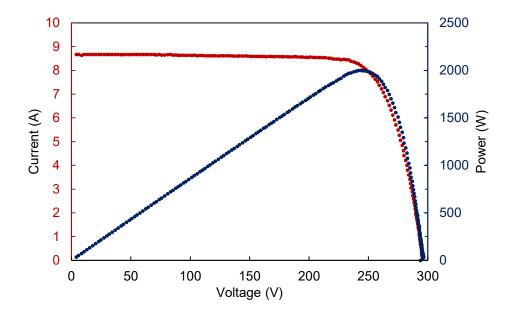

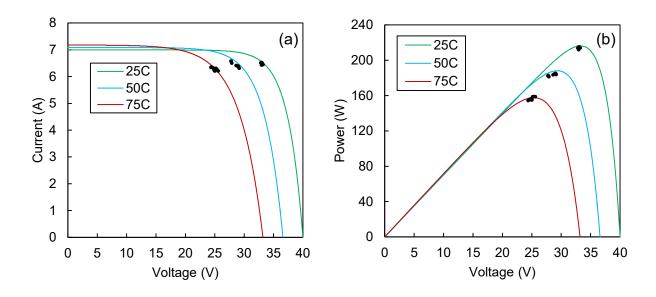

| 2.7.   | I-V and P-V curve dependence on incident irradiance (100-1000W/m²)                                                                                            | 33   |

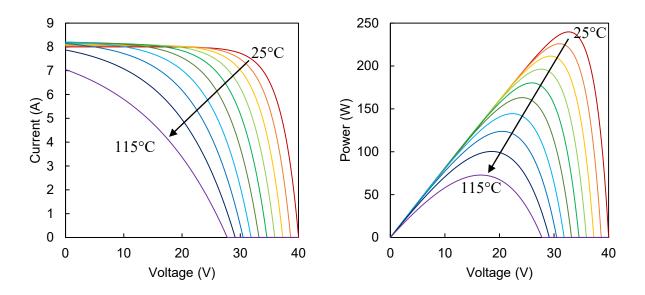

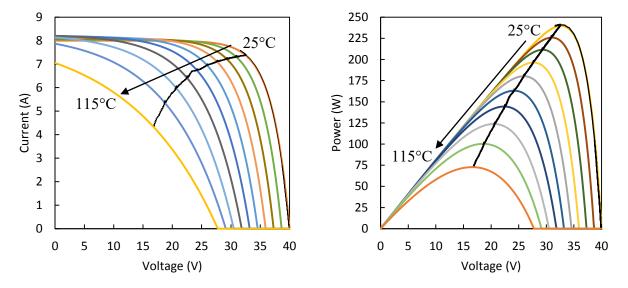

| 2.8.   | I-V and P-V curve dependence on ambient temperature (25-115°C)                                                                                                | 33   |

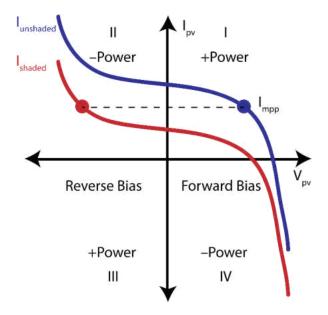

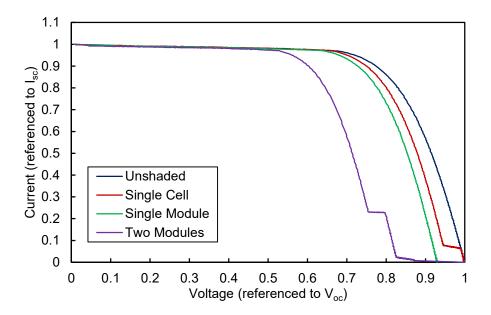

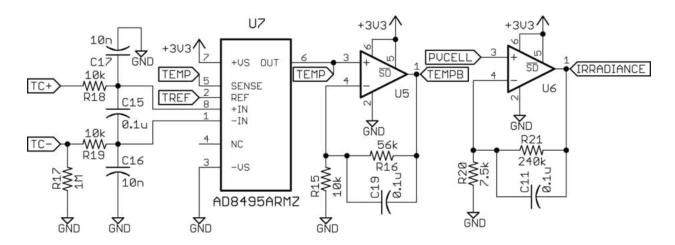

| 2.9.   | PV cell operation regions for unshaded (blue) and shaded cells (red)                                                                                          | 35   |

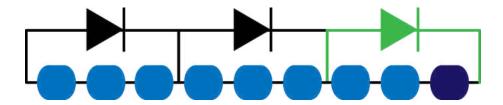

| 2.10.  | Bypass diodes connected across series-connected solar cells                                                                                                   | 36   |

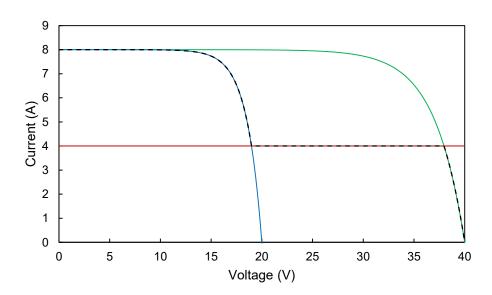

| 2.11.  | Construction of a PV module partial shading model for $V_{oc} = 40\text{V}$ , $I_{sc} = 8\text{A}$ , system shading = 0.5, and shading strength = 0.5         | 36   |

| 2.12.  | Measured (solid lines) and modelled curves (dashed lines) for a partially shaded PV module                                                                    | 37   |

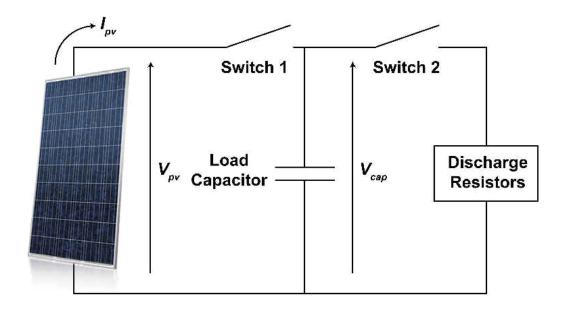

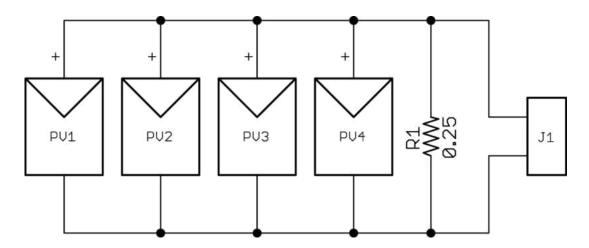

| 3.1.   | Simplified schematic of a curve tracer using a capacitive load                                                                                                | 43   |

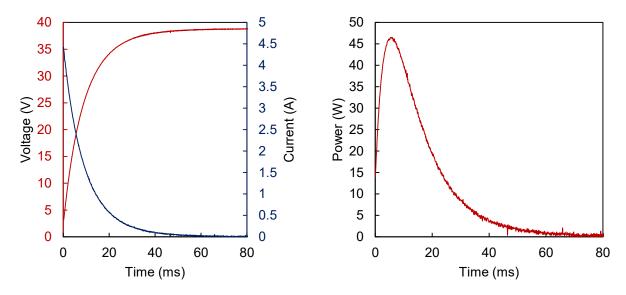

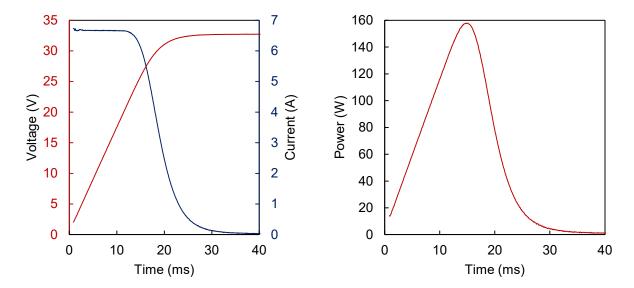

| 3.2.   | Measured voltage, current and power vs. time curves of a capacitor charged with a constant voltage source (38V) and an $8\Omega$ resistor connected in series | 44   |

|       |                                                                                                                                         | Page |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.3.  | Measured voltage, current and power vs. time curves of a capacitor charged with a PV module                                             | 45   |

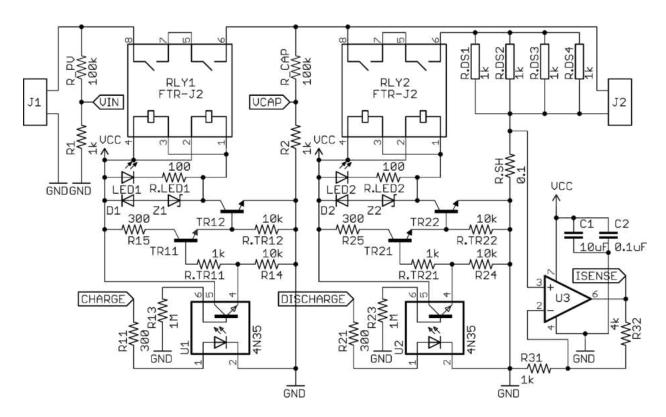

| 3.4.  | Schematic of the first generation I-V curve tracer                                                                                      | 49   |

| 3.5.  | First generation I-V curve tracer board                                                                                                 | 50   |

| 3.6.  | Photograph of the populated first generation I-V curve tracer                                                                           | 51   |

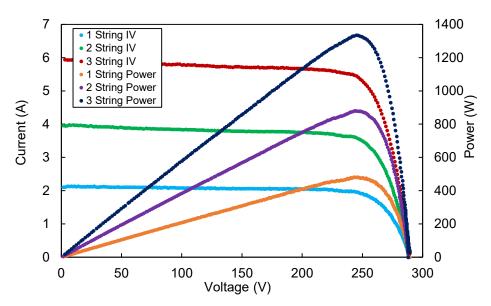

| 3.7.  | Measured I-V and P-V curves for 1, 2, and 3 strings under 25% illumination                                                              | 51   |

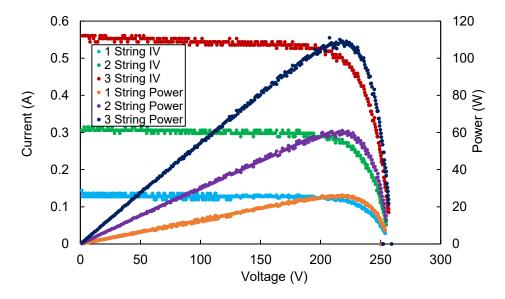

| 3.8.  | Measured I-V and P-V curves for 1-3 strings under 1.75% illumination                                                                    | 52   |

| 3.9.  | Measured I-V and P-V curves for 2 strings under 50% illumination                                                                        | 53   |

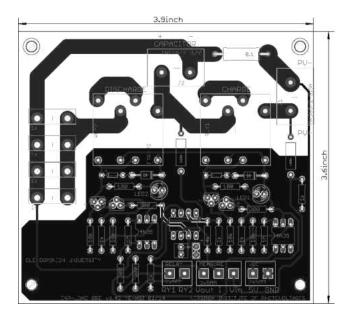

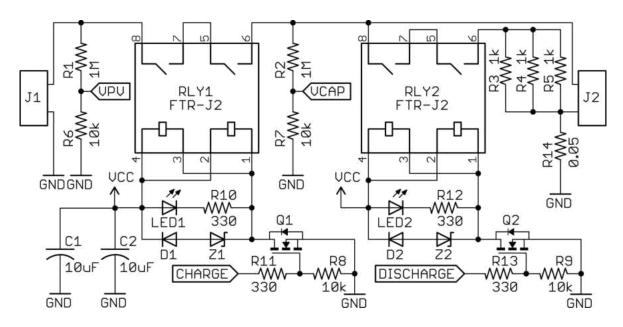

| 3.10. | Schematic of the Generation 1.5 power circuit                                                                                           | 55   |

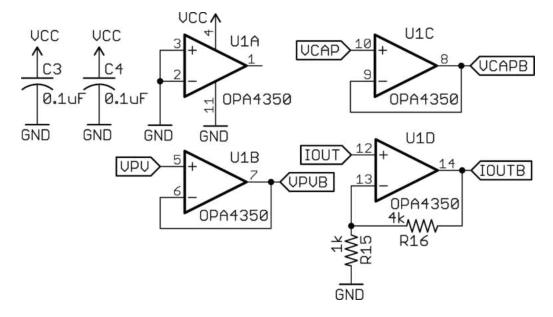

| 3.11. | Schematic of the signal conditioning circuit                                                                                            | 57   |

| 3.12. | Generation 1.5 I-V curve tracer board                                                                                                   | 60   |

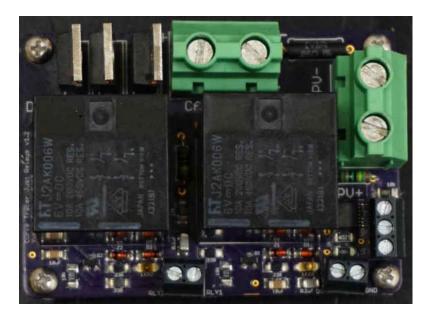

| 3.13. | Photograph of the populated curve tracer                                                                                                | 61   |

| 3.14. | PV load switching enclosure                                                                                                             | 63   |

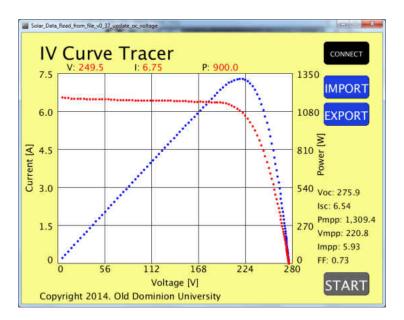

| 3.15. | Custom IV curve tracer software                                                                                                         | 64   |

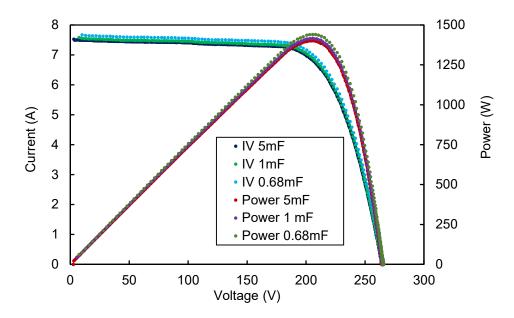

| 3.16. | Measured effect of different capacitor values on I-V and P-V curves                                                                     | 66   |

| 3.17. | Shading arrangement for two shaded PV modules                                                                                           | 68   |

| 3.18. | Measured I-V and P-V curves of an unshaded single string                                                                                | 68   |

| 3.19. | Measured I-V and P-V curves with a single shaded cell                                                                                   | 69   |

| 3.20. | Measured I-V and P-V curves with a single shaded module                                                                                 | 69   |

| 3.21. | Measured I-V and P-V curves with two shaded modules                                                                                     | 70   |

| 3.22. | Measured I-V and P-V curves of a single string charged using Eq. 3.1 with a single shaded panel                                         | 71   |

| 3.23. | Comparison between the normalized measured I-V curves for unshaded, a single shaded cell, asingle shaded module, and two shaded modules | 72   |

|       |                                                                                                                                          | Page |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.24. | Comparison between the normalized measured P-V curves for unshaded, a single shaded cell, a single shaded module, and two shaded modules | 73   |

| 3.25. | Power circuit schematic                                                                                                                  | 75   |

| 3.26. | Temperature and irradiance measurement schematic                                                                                         | 77   |

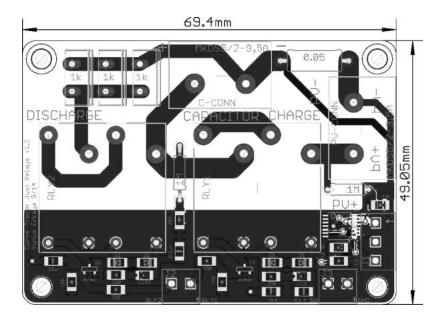

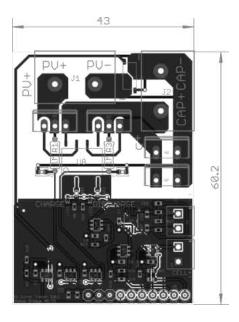

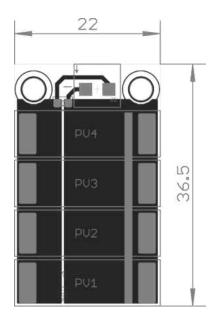

| 3.27. | I-V curve tracer board (dimensions are in mm)                                                                                            | 78   |

| 3.28. | I-V curve tracer board after assembly                                                                                                    | 78   |

| 3.29. | Schematic of the irradiance monitor PCB                                                                                                  | 79   |

| 3.30. | Irradiance monitor board (dimensions are in mm)                                                                                          | 80   |

| 3.31. | MOSFET switching circuit                                                                                                                 | 81   |

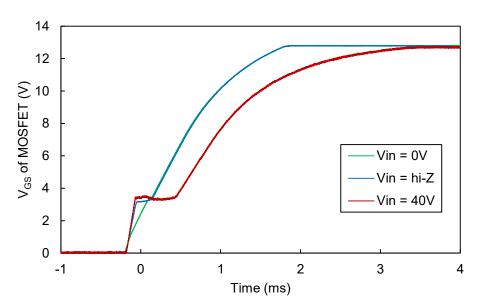

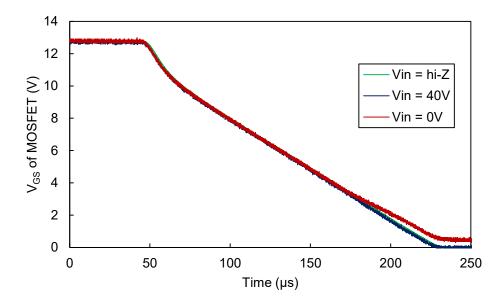

| 3.32. | Measured MOSFET turn-on waveforms for high-impedance, 0V and 40V applied at PV input                                                     | 83   |

| 3.33. | Measured MOSFET turn-off waveforms for high-impedance, 0V and 40V at PV input                                                            | 84   |

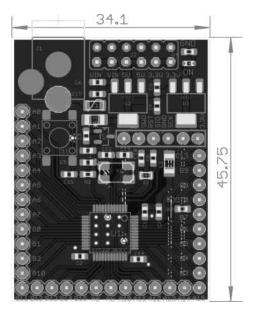

| 3.34. | Microcontroller board (dimensions in mm)                                                                                                 | 87   |

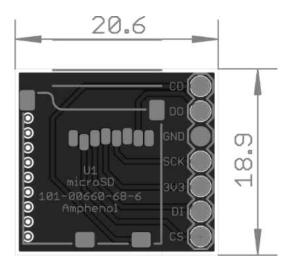

| 3.35. | Micro SD card board (dimensions in mm)                                                                                                   | 88   |

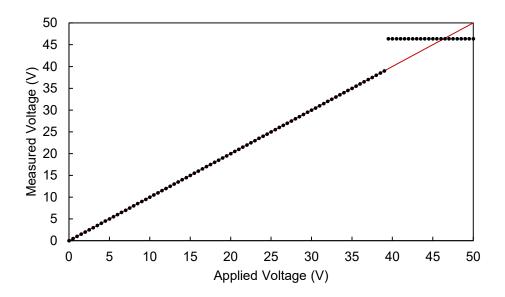

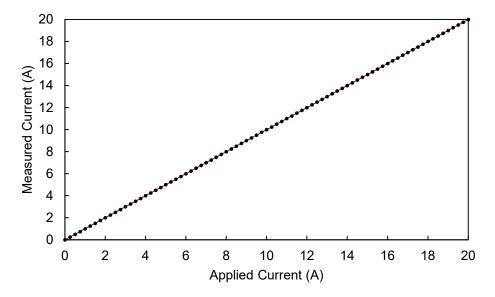

| 3.36. | Applied voltage vs. measured voltage                                                                                                     | 89   |

| 3.37. | Applied current vs. measured current                                                                                                     | 90   |

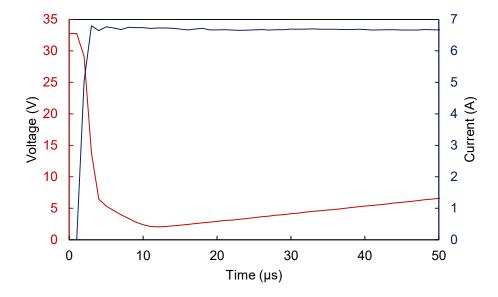

| 3.38. | Measured PV module voltage and current during charging MOSFET turn-on                                                                    | 93   |

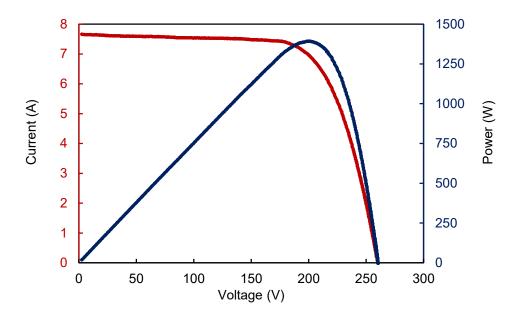

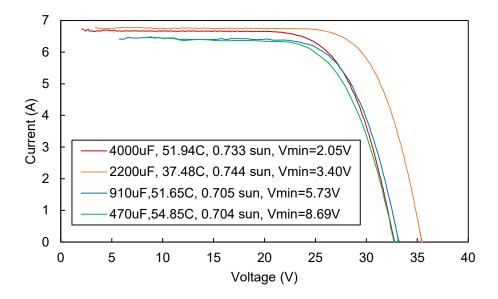

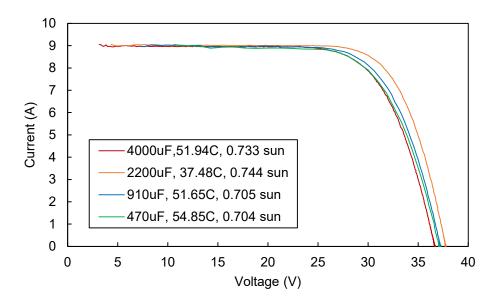

| 3.39. | I-V curve measurements using different capacitors                                                                                        | 94   |

| 3.40. | STC converted I-V curve measurements using different capacitors                                                                          | 94   |

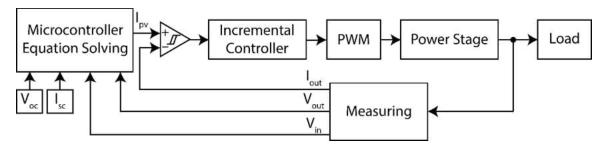

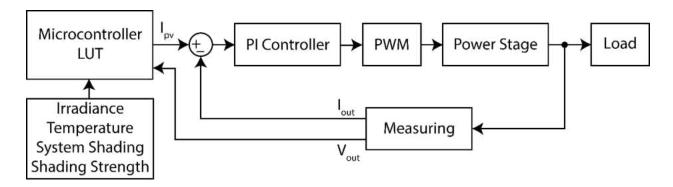

| 4.1.  | Block diagram of the proposed PV module emulator                                                                                         | 99   |

| 4.2.  | Schematic of non-synchronous buck converter                                                                                              | 99   |

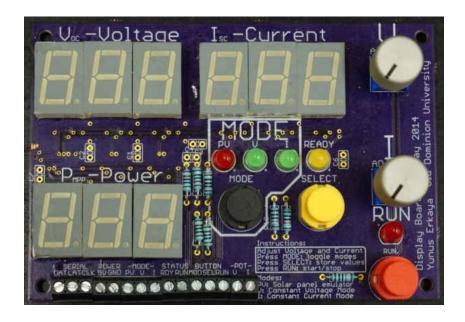

| 4.3.  | Photograph of the PV emulator                                                                                                            | 104  |

| 4.4.  | Photograph of the PV emulator user interface                                                                                             | 104  |

|       |                                                                                                                                                     | Page |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

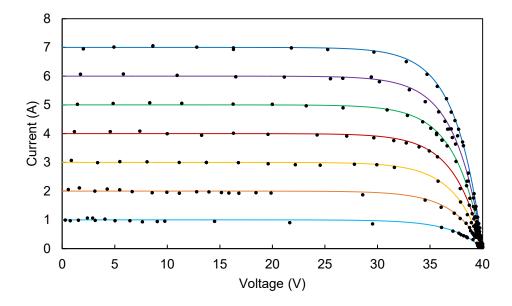

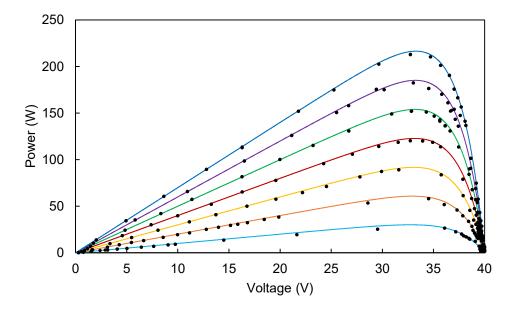

| 4.5.  | Measured operation points over simulated I-V curves of the PV emulator for $V_{oc} = 40$ V and $I_{sc}$ ranging from 1A to 7A                       | 106  |

| 4.6.  | Measured operation points over simulated P-V curves of the PV emulator for $V_{oc} = 40$ V and $I_{sc}$ ranging from 1A to 7A                       | 106  |

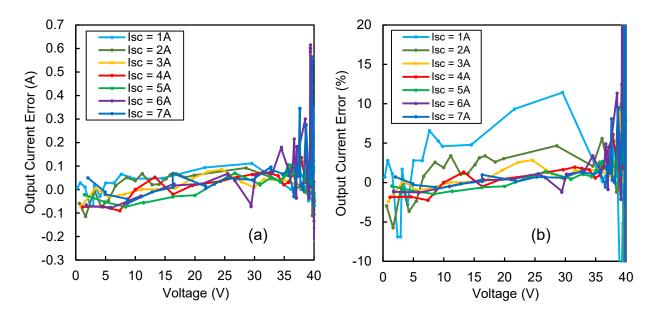

| 4.7.  | Output current error in absolute (a) and percentage (b) vs. output voltage of the PV emulator                                                       | 108  |

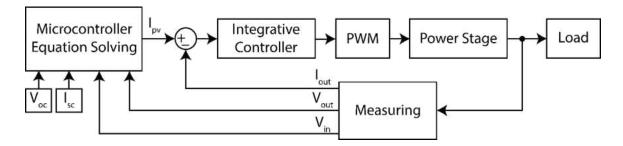

| 4.8.  | Block diagram of the proposed PV module emulator                                                                                                    | 109  |

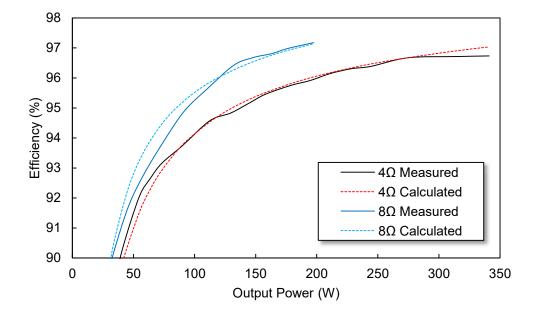

| 4.9.  | Measured and calculated efficiency for $4\Omega$ and $8\Omega$ loads                                                                                | 115  |

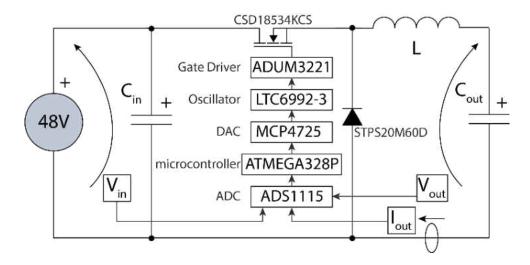

| 4.10. | Circuit schematic with main component blocks of the PV emulator                                                                                     | 116  |

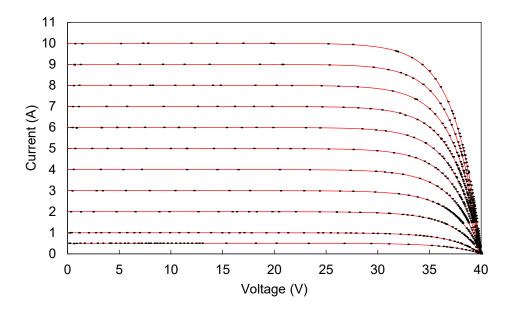

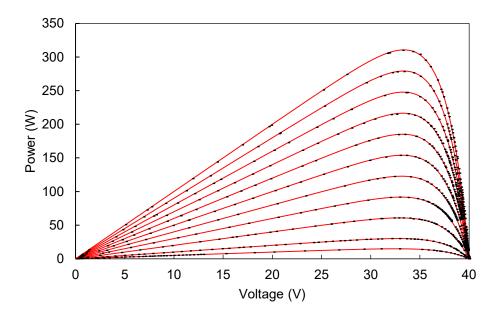

| 4.11. | Experimental I-V curve results, dots are measurements on simulated red lines                                                                        | 118  |

| 4.12. | Experimental P-V curve results, dots are measurements on simulated red lines                                                                        | 118  |

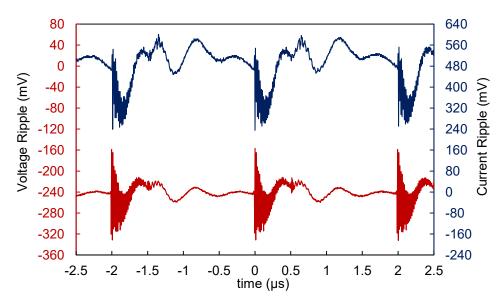

| 4.13. | Voltage and current ripple waveforms at 48V input and 12V output with an $8\Omega$ load using an HP E3631A power supply                             | 120  |

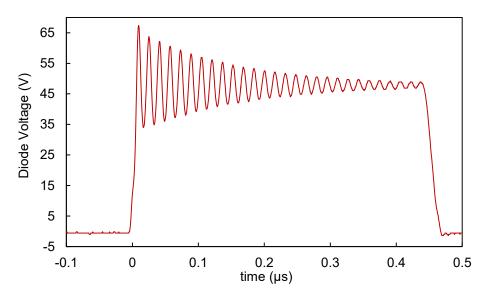

| 4.14. | Voltage ringing across the diode, with an undesired overshoot of 67.25V at a fundamental frequency of 63.2 MHz                                      | 121  |

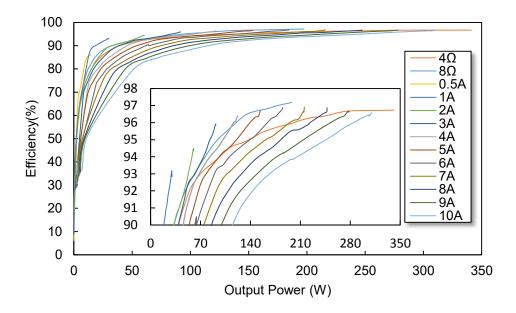

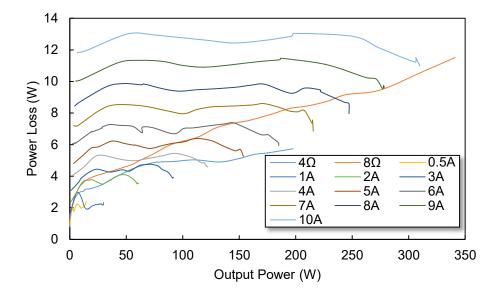

| 4.15. | Efficiency vs. output power of the PV module emulator                                                                                               | 122  |

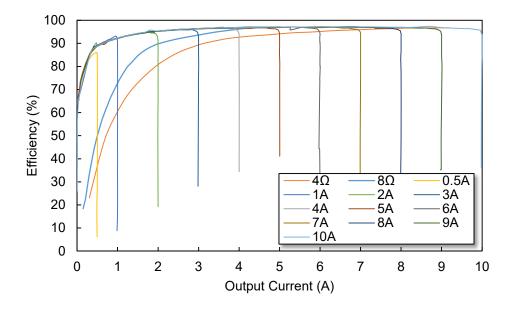

| 4.16. | Efficiency vs. output current of the PV module emulator                                                                                             | 123  |

| 4.17. | Power loss vs. output power of the PV module emulator                                                                                               | 124  |

| 4.18. | Photograph of the second generation PV module emulator                                                                                              | 125  |

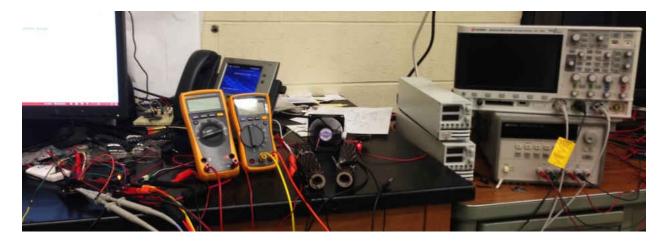

| 4.19. | PV module emulator test setup                                                                                                                       | 126  |

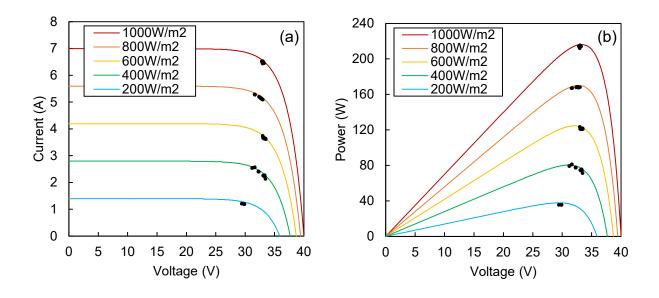

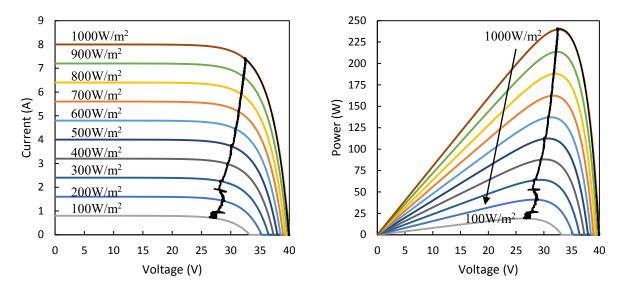

| 4.20. | Measured operation points (black dots) on simulated I-V and P-V curves (color lines) at constant temperature (25°C) for different irradiance values | 128  |

| 4.21. | Measured operation points (black dots) on simulated P-V curves (color lines) at constant irradiance (1000W/m²) for different temperature values     | 128  |

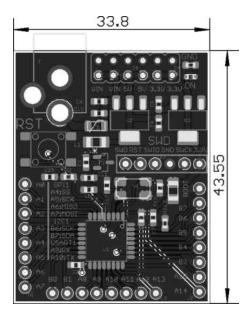

| 5.1.  | STM32F334K8 development board                                                                                                                       | 132  |

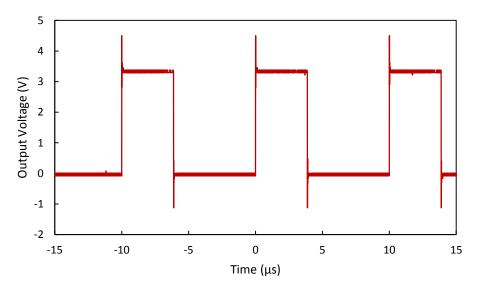

| 5.2.  | Measured SysTick timer interval and algorithm speed                                                                                                 | 137  |

|       |                                                                                                                                  | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------------|------|

| 5.3.  | Block diagram of the proposed PV module emulator                                                                                 | 139  |

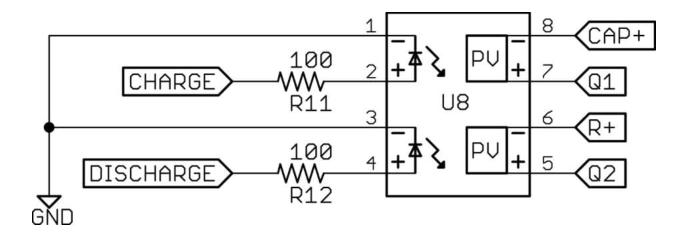

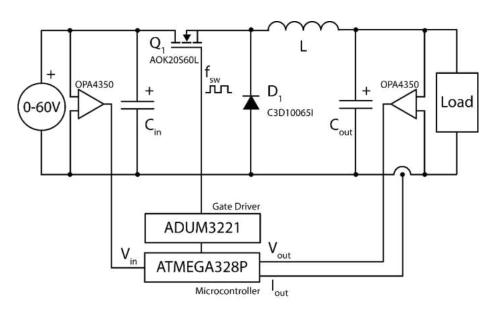

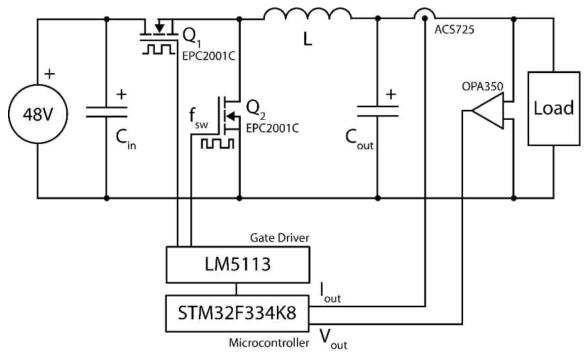

| 5.4.  | Simplified circuit schematic of the proposed PV emulator                                                                         | 140  |

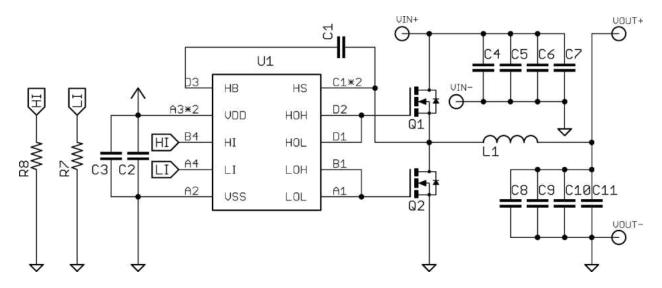

| 5.5.  | Detailed schematic of the power board                                                                                            | 141  |

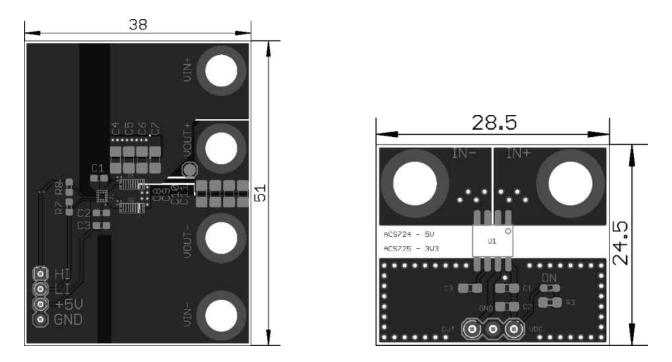

| 5.6.  | Power board (left) and current board (right) design (dimensions are in mm)                                                       | 141  |

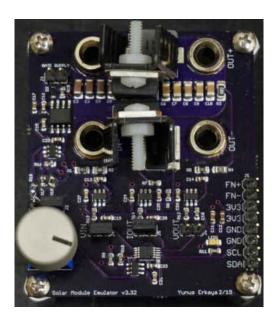

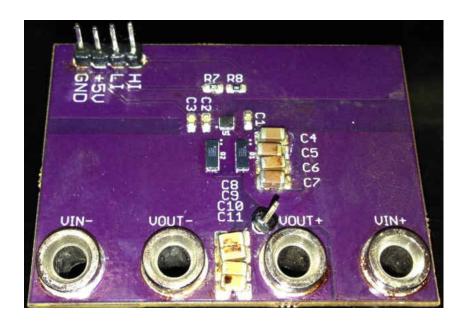

| 5.7.  | Photograph of the populated PV module emulator                                                                                   | 144  |

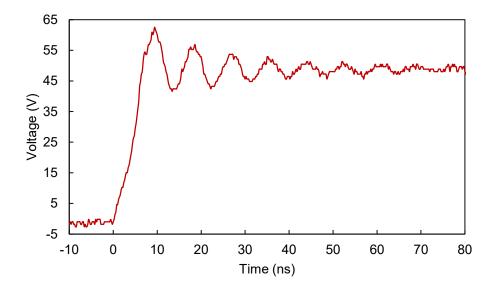

| 5.8.  | Measured switch node voltage at high-side MOSFET turn-on                                                                         | 145  |

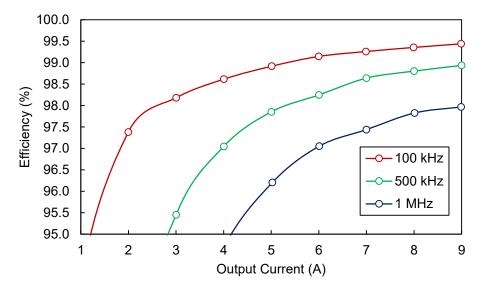

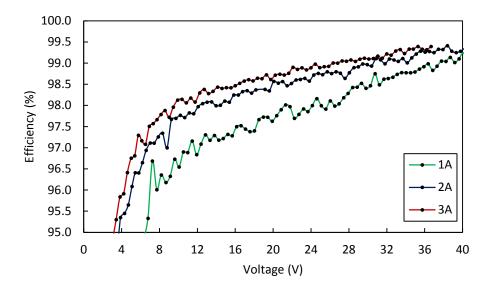

| 5.9.  | Efficiency vs. output current for a $4\Omega$ load                                                                               | 146  |

| 5.10. | Constant voltage electronic load that uses a MOSFET in linear operation                                                          | 148  |

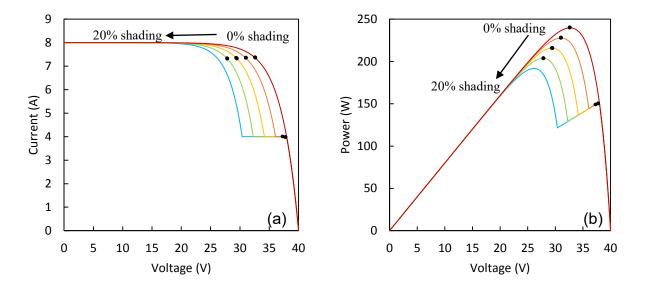

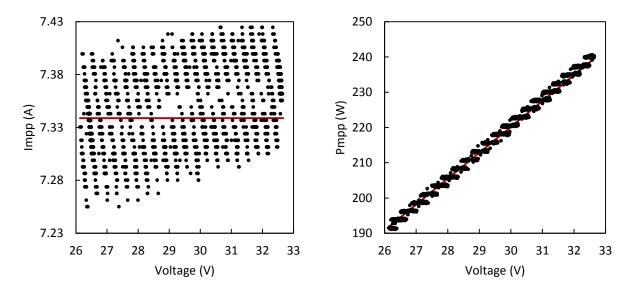

| 5.11. | Inverter MPP (black dots) over simulated I-V (a) and P-V (b) curves (color lines) at different system shading conditions (0-20%) | 149  |

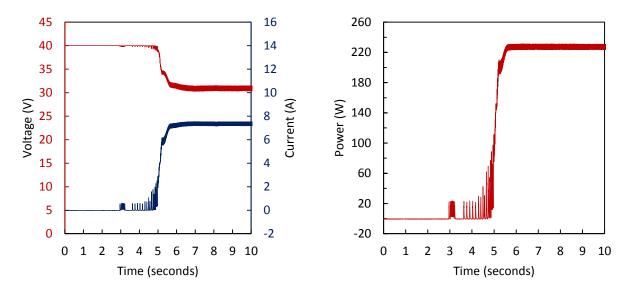

| 5.12. | Inverter startup sequence for 0% system shading                                                                                  | 150  |

| 5.13. | Inverter startup sequence for 5% system shading                                                                                  | 151  |

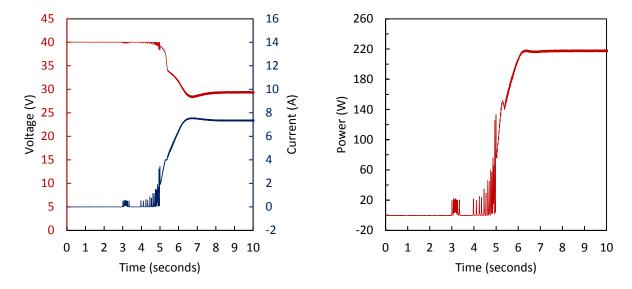

| 5.14. | Inverter startup sequence for 10% system shading                                                                                 | 152  |

| 5.15. | Inverter startup sequence for 15% system shading                                                                                 | 152  |

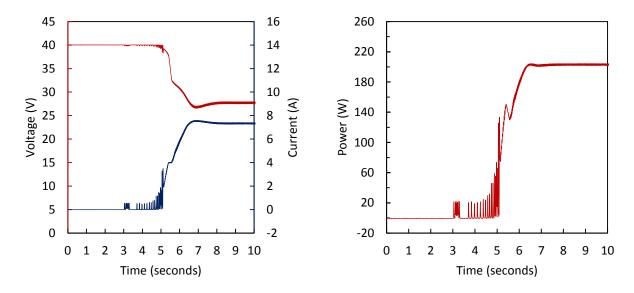

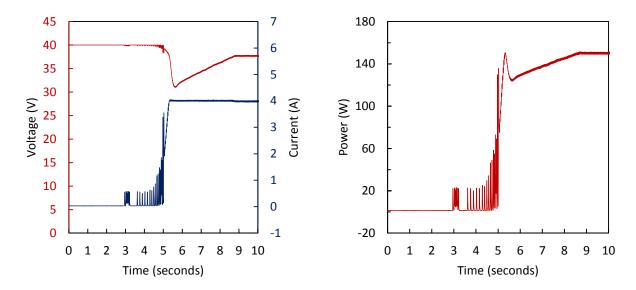

| 5.16. | Measured inverter startup sequence for 20% system shading                                                                        | 153  |

| 5.17. | Detailed view of the inverter operation at 20% shading                                                                           | 154  |

| 5.18. | PV module emulator tested with constant voltage electronic load                                                                  | 154  |

| 5.19. | Current error vs. output voltage for PV emulator operation for $V_{oc} = 40$ V and $I_{sc} = 1$ A                                | 155  |

| 5.20. | Current error vs. output voltage for constant current mode operation for 1A, 2A, and 3A                                          | 156  |

| 5.21. | Efficiency vs. output voltage of the emulator circuit when operating at constant current mode                                    | 157  |

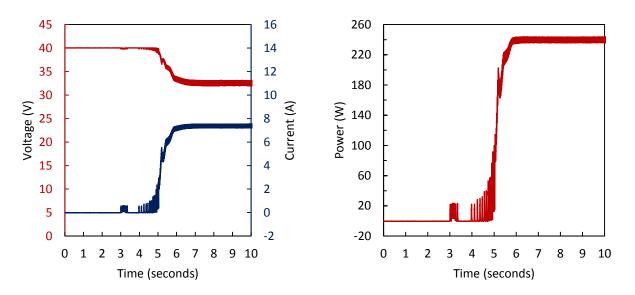

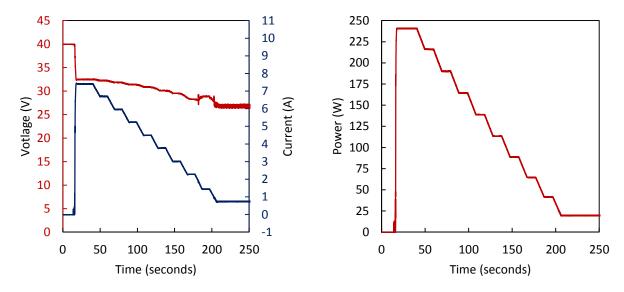

| 5.22. | Voltage/current vs. time and power vs. time for irradiance variation tests                                                       | 158  |

|       |                                                                                                                                                     | Page |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.23. | I-V and P-V curves as a function of irradiance levels (1000W/m² to 100W/m²) along with MPP tracking                                                 | 159  |

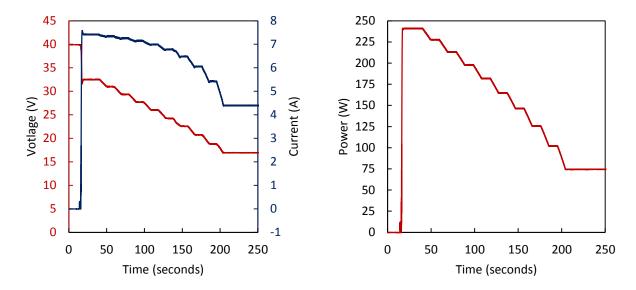

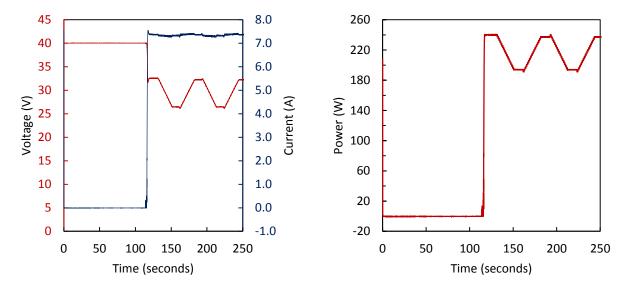

| 5.24. | Voltage/current vs. time and power vs. time for temperature variation test                                                                          | 160  |

| 5.25. | I-V and P-V curves as a function of temperature levels (25°C to 115°C) along with MPP tracking                                                      | 160  |

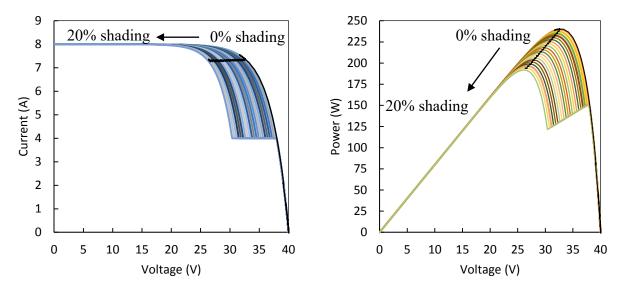

| 5.26. | Voltage/current vs. time and power vs. time for the shading variation test                                                                          | 161  |

| 5.27. | I-V and P-V curves as a function of system shading levels (fixed shading strength of 0.5 and system shading from 0% to 20%) along with MPP tracking | 162  |

| 5.28. | I-V and P-V curves with the detailed view of the MPP tracking algorithm for changing system shading                                                 | 162  |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1. Introduction

There is significant growth in the photovoltaic (PV) market, thanks to the wide availability of low-cost PV modules, good federal and state incentives such as tax credits and feed-in tariffs in the United States [1-4]. With increased numbers in commercial and residential deployments, it becomes important to properly model, measure, characterize, and emulate photovoltaic modules to better utilize PV technology [5-6].

PV models are important to understand and simulate the behavior of PV modules under different conditions and configurations [7]. Such conditions relate to different amounts of sunlight (irradiance), the varying outdoor temperatures and the amount of partial shading (when a section of the PV module receives less light than others) [8-10]. Internal configurations of PV modules include the number of solar cells connected in either series or parallel combinations, and the type of the material i.e. Silicon (Si), Copper Indium Gallium Selenide (CIGS), Cadmium Telluride (CdTe) or Gallium Arsenide (GaAs) [11-15]. External configurations include the number of PV modules in a "string" (a series chain of PV modules) and the number of strings connected together in parallel via a junction box [16].

Measurements of a PV system typically include the open-circuit voltage  $V_{oc}$ , short-circuit current  $I_{sc}$ , voltage, current and power at the maximum power point  $V_{mpp}$ ,  $I_{mpp}$ ,  $P_{mpp}$ , respectively [17]. These measurements, while perfectly representative of PV modules in ideal laboratory conditions and operation at the maximum power point (MPP), fail to properly characterize the PV system throughout its operational region [18].

As one can imagine, testing PV modules requires them to be under sunlight. PV module manufacturers use devices known as solar simulators to shine a calibrated amount of light on the PV module under test, and bin the modules according to power output and provide certain operational parameters in the module datasheets [19-20]. While it is straightforward to test and characterize PV modules under standard testing conditions (1000W/m² irradiance and 25°C ambient temperature), the same testing methods cannot be applied to systems connected to PV modules, such as inverters, protection devices, measurement devices, and cabling and junction boxes [21-25].

In order to test the external electrical hardware "PV electronics" used in PV systems, the tests need to cover all expected operational conditions. The goal of designing PV electronics is to have them work under varying conditions of sunlight, temperature, and partial shading. For fully testing the capabilities and guaranteeing the robustness of PV electronics, the use of actual PV modules is undesirable. Testing high power PV equipment would require enormous and costly testing facilities [26]. Besides costs, problems arise from inconsistent and difficult to predict fluctuating conditions of solar irradiation and ambient temperature [27].

PV module emulators are designed to emulate the output of actual photovoltaic modules using electrical circuits [28-31]. In order to do so, an accurate PV module model is necessary to generate the output curve that correctly represents a PV module [32-35]. Afterwards, the simulated I-V characteristics are input into the electrical circuit control algorithm to control the output of the emulator resulting in an accurate representation of PV module characteristics. The use of PV module emulators provides the flexibility and cost effectiveness required to test all kinds of PV equipment.

#### 1.2. Overview of I-V curve Tracers

I-V curves of photovoltaic strings provide relevant information that ordinary monitoring systems at the inverter level and fault detection systems at combiner level cannot measure. Information about partial shading, PV module mismatch, effects of solar insolation and temperature, shunt resistance, and series resistance can be gathered from the analysis of a typical I-V curve [36-44].

Many topologies are described in the literature regarding I-V curve measurement circuits [45-46]. The main ones in concern can be listed as: variable resistor load, capacitive load, electronic load, four quadrant power supply, and DC-DC converter. Ultimately, the goal of all of these topologies is the same: to measure the I-V curve accurately. The requirements for an I-V curve tracer can be listed as [47]:

- 1. Flexibility,

- 2. Modularity,

- 3. Fidelity,

- 4. Fast response: all points recorded at same climatic conditions,

- 5. Direct display: test results are displayed while running, and

- 6. Cost

Considering the criteria above, all topologies listed have their benefits and drawbacks.

Table 1.1 presents a summary of the most common I-V curve tracer topologies.

| Table 1.1: Capabilities of | different curve tracer topo | logies based on [ | [47]. |

|----------------------------|-----------------------------|-------------------|-------|

|----------------------------|-----------------------------|-------------------|-------|

|                   | Flexibility | Modularity | Fidelity | Response | Display | Cost |

|-------------------|-------------|------------|----------|----------|---------|------|

| Variable Resistor | Medium      | Medium     | Medium   | Low      | No      | Low  |

| Capacitive Load   | Low         | Low        | Medium   | Low      | No      | High |

| Electronic Load   | High        | High       | Medium   | Medium   | Yes     | High |

| 4-quadrant PSU    | Low         | Low        | High     | High     | Yes     | High |

| DC-DC Converter   | High        | High       | High     | High     | Yes     | Low  |

#### 1.2.1. Variable Resistive Load

The simplest and most intuitive way of measuring the I-V curve of a photovoltaic module or array is to use a variable resistive load. The operational point of the module can be varied by altering the value of the load resistance. Two distinct load topologies are possible: a switched load bank that changes the load resistance via automated relays, or a simple rheostat (variable resistance) that can be swept from nearly 0 to a large enough value.

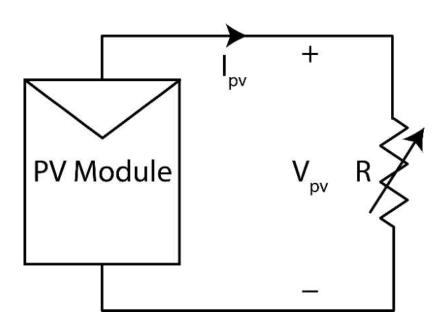

Figure 1.1. Variable resistive load based on [47].

The power consumed by the resistors turns into heat and may destroy the resistors in question. Coupled with the fact that it is difficult to get large power resistors, this circuit topology is only suitable for low power modules and not large power arrays. The measurements tend to be very slow if manually operated and this may lead to the conditions to change during measurements.

Willoughby *et al.* present a simple resistive load to monitor the I-V characteristics of PV modules [48]. Their methodology consists of a 10 minute interval timer that triggers measurements. The counter connected to the timer energizes a sequence of relays connected to high power resistive loads of  $0.1\Omega$  to about  $100\Omega$ . The circuit is an analog design and while claimed to be cost effective due to the low-cost low voltage relays, the authors suggest the use of a single microcontroller to eliminate the timer and counter circuit, and the use of MOSFETs over relays to reduce the relay bouncing effect. The maximum electrical values tested were just below 22V, 3A, and 45W.

Rivai and Rahim investigated a binary-based I-V curve tracer [49]. When compared to a traditional curve tracer with different load resistance values, their resistor selection is optimized to trace many points with the use of only 8 resistors. The circuit is based on a binary counting system with resistors values ranging from  $1\Omega$  to  $128\Omega$  in powers of 2, and through switching the resistors in and out, it is possible for them to change the load resistance from  $1\Omega$  to  $255\Omega$  in  $1\Omega$  increments.

#### 1.2.3. Capacitive Load

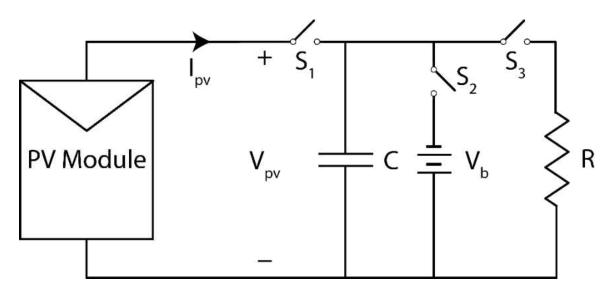

A capacitor is used to bias the module under test in this topology. When S1 is closed in Figure 1.2, the capacitor begins charging. Assuming the capacitor is fully discharged, the initial capacitor voltage will equal to zero. As the capacitor initiates charging, the I-V curve

relationship will be constrained by the PV module and, thus, a highly accurate measurement is made possible.

Figure 1.2. Capacitive load based on [47].

Typical requirements are good quality capacitors with low equivalent series resistor (ESR) values to keep the capacitors from overheating. Since the energy stored in the capacitor is in the form of reactive power, it leads to no heat related issues. Varying the size of the capacitor will vary the stored energy but, generally speaking, there is very little energy transferred to the circuit when compared to other forms of measurement.

The capacitor can also be pre-charged with a reverse voltage (negatively biased) by closing S2 before the measurement takes place. This is an important factor for the measurement of the true-short circuit current, otherwise there will be an absolute minimum measurable voltage that will be greater than zero. This inhibits the measurement of the true short-circuit current.

Finally, the capacitor is discharged via S3 and the capacitor energy is dissipated within the resistor bank. Resistor values above 10W generally yield good thermal characteristics without temperature issues.

The capacitor size is highly dependent on the conditions, which makes this circuit a challenge to accommodate for all circumstances. The capacitor size is directly proportional with  $I_{sc}$  and indirectly proportional with  $V_{oc}$ . That is, a large system consisting of photovoltaic modules in a series array will need a much smaller capacitor than a single module or modules connected in parallel. The capacitor size is still quite important as it should allow for fast enough measurements for the climatic conditions to remain constant and it should be slow enough to overcome the junction capacitance of the modules.

Munoz *et al.* propose a capacitive load with insulated gate bipolar transistors (IGBTs) used as switches for the purposes of tracing the I-V curves of photovoltaic modules connected in a combinational series/parallel array in [50]. The circuit consists of three switches, which serve various functions. The first switch is connected to a shorting diode which allows for making short-circuit current measurements near zero volts. Due to the high system voltage and the high short-circuit current, the diode used is very large and has a large voltage drop, leading to increased losses. Therefore, the authors recommended that a very quick pulse test should be used to confirm the short-circuit current.

The second switch connects the PV modules to the capacitor bank comprised of four capacitors, which can be connected all in parallel or in two-series and two-parallel for doubling the open-circuit voltage capability. The voltage across the capacitors is balanced by two balancing resistors.

A pushbutton located on the panel allows for negatively charging the capacitor bank using a 9V battery before measurements are made to capture the module current at zero volts. The third switch is used for discharging the capacitor bank after measurements are performed through a discharge resistor and blocking diode.

The voltage and current values are measured through a voltage divider and series connected shunt resistor respectively, and there is no data logging capability in the device. Therefore, the aid of an oscilloscope for data acquisition is necessary.

The paper discuss the complex switching and gate drive arrangement, which are part of the largest drawbacks of this design. The gate driver circuit is a complex system consisting of 9V batteries, a DC capacitor, manual trigger pushbuttons, optocouplers, gate resistors, and large package chassis mount IGBTs costing hundreds of dollars.

A human operator is necessary to charge, discharge, and negatively bias the capacitor and no automation is possible. The lack of data storage is also a huge problem. Because the operator comes in contact with the device, the operator is at risk of electrical shock. Other drawbacks include bulky and heavy components weighing a total of 15kg and a high cost over \$1000. The oscilloscope used to capture the data costs about \$2200.

The authors' results show that there is measurement noise coupled into the system, but it performs an adequate sweep from what appears to be 0V to the short-circuit current. The algorithm used to extrapolate to STC appears to be highly questionable due to the wide gap it introduces between  $I_{sc}$  and the measured lowest voltage.

#### 1.2.4. Electronic Load

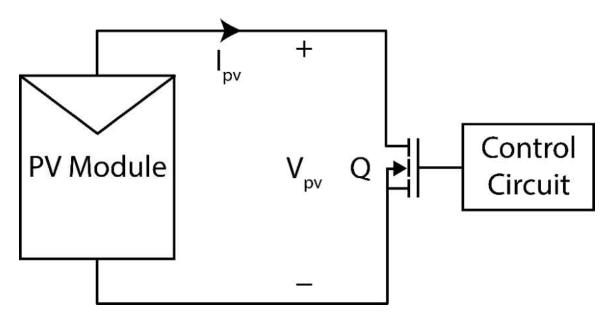

The electronic load topology is a practical and simple method of measurement. Most products sold in the market titled "DC electronic load" work using this operational principle. In

the simplest sense, a transistor will be operated in its cut-off, active and ohmic regions by modulating the gate voltage to vary its resistance. This makes the transistor act like a variable resistor, which is very easy to construct.

Figure 1.3. Electronic load based on [47].

The main challenge of this circuit comes from the fact that the transistor dissipates all the power and large heat sinks and many parallel MOSFETs are required to build a large enough device to carry out measurements for larger systems.

Although technology has vastly improved MOSFETs high frequency capabilities and figures of merit through the reduction of the gate charge and series resistances, the reduced cell areas in the MOSFET structure cause an imbalance of current [51]. During fully-on operation (ohmic region), there certainly is no problem as the resistances are small and similar to each other. But in the saturation region the resistances will be significantly larger than the minimum

resistances possible and this will cause current localization and regions with smaller resistances [52]. With increased temperatures the resistances of the regions will further drop and will cause premature failure [53]. Therefore, older generation devices with larger cells and devices designed especially for linear use are required in the design of an electronic load.

#### 1.2.5. Four Quadrant Power Supply

The four quadrant power supply requires a large power supply which is usually limited to a maximum power of 1 kW to both source and sink current from the PV module under test. This method is the only way of making a 3 quadrant measurement on a photovoltaic module. However, with the capability comes the tremendous costs and difficult switching schemes. The low power limit of this load (mainly from sinking power) disallows large array testing and it is only useful for single module testing.

Figure 1.4: Four quadrant power supply based on [47].

#### 1.2.6. DC-DC Converter

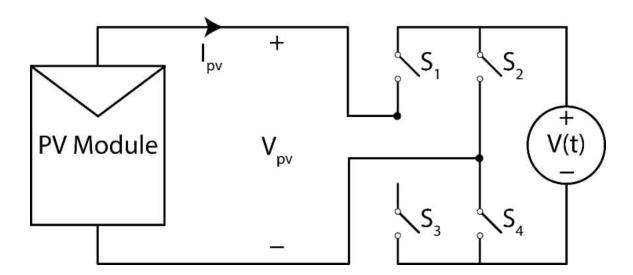

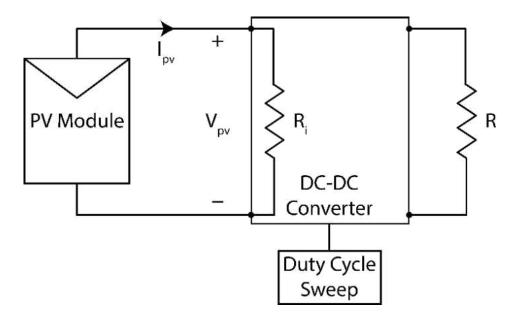

The DC-DC converter shown in Figure 1.5 is a device connected between the PV module and a resistive load that allows for a variable resistor, variable current, and a variable power load to be constructed. The main power electronics topologies for this circuit consist of buck, buckboost, and boost converters operating as DC transformers. The buck converter topology is incapable of emulating a resistive load below the physically connected resistor and therefore is incapable of tracing near  $I_{sc}$ . Conversely, the boost converter cannot emulate a load larger than the physical resistor and it is not capable of making measurements at or near  $V_{oc}$ . The buck-boost converter, on the other hand, is capable of resolving the whole curve. Two other exotic converters such as SEPIC and Cuk converters are good for reduced ripple in the reproduced curves. The current ripple and voltage ripple caused by the switching action reduce the quality of the measured curve and large passive filters are necessary to eliminate noise in the measurements. This method can take single quadrant measurements only.

Figure 1.5: DC-DC converter based on [47].

#### 1.2.7. Industrial I-V Curve Tracers

There are quite a few I-V curve tracers in the market, some of which operate with an electronic load topology, and others with capacitive load topologies. The portable devices are usually capacitive while rack-mount units designed for production testing with a solar simulator are DC electronic load type. Example of devices for portable measurements and their characteristics are given in the following paragraphs.

The MP-11 I-V Checker by Eko Instruments is a portable I-V curve tracer that relies on the capacitive load topology [54]. It is capable of taking voltage measurements in the range of 10-1000V and current measurements in the range of 0.1-30A with a power range of 10W-18kW. It is capable of recording 400 data points and storing 300 I-V curves in the internal memory. The device comes with a pyranometer, a reference cell, and two thermocouples for sensing irradiance and module temperature. The unit dimensions are 23 x 32 x 18 cm<sup>3</sup> with a total weight of 2.5kg for the tester, 0.5kg for the sensor unit, and 0.5kg for the battery box. Power is supplied by 8 x AA batteries or a 9V/1A DC adaptor. The sensor unit runs off a single 9V battery (006P type).

The TRI-KA I-V Curve Tracer from Tritec Energy [55] is capable of measuring 1.0-1000V and 0.1-15A PV systems. The unit includes a sensing unit that measures temperature and irradiance through a direct contact with the face of the PV module and the sensing unit, and a reference silicon cell, respectively. It is recommended to make I-V measurements above 700W/m² irradiance for reliable results per EN 61829 standards [56]. Data points are stored in an SD card, which provides over 1000 measurements per 1 GB. The unit weighs just 0.5kg with dimensions of 21 x 10.5 x 4.1 cm³. The cost of the unit is \$5,595 at Solar-PV-Tester.com

The DS-1000 I-V curve tracer from Daystar is a portable curve tracer weighing 12 kg and measuring 44 x 35 x 20 cm<sup>3</sup> [57]. Each measurement includes 1000 data points and requires a

computer to transfer the data. The unit includes two thermocouple inputs (Type T) and two analog voltage inputs that can be used to connected irradiance sensors. The device has 3 ranges of voltage (10, 100, 1000V) and current (1, 10, 100A).

The Solmetric PVA-1000S PV Analyzer Kit provides a portable solution to I-V curve measurements [58]. In its standard configuration it is capable of measurements of up to 1000V and 20A and for an additional \$600 it can measure up to 30A. The voltage and current resolution are 25mV and 2mA, respectively. The minimum measurements points are 100 and the device uses an external sensor wirelessly connected to the main unit to acquire the irradiance and module temperature. A computer is needed to transmit and receive the data and the unit weighs 12 lb. with dimensions of 15 x 8 x 5 cubic inches. The sensor unit has an irradiance resolution of 1 W/m<sup>2</sup> and a measurement range of 0-1500W/m<sup>2</sup>. The temperature resolution of the sensor unit is 0.1°C with a measurement range of 0-100°C. The sensor unit weights 2 lb. with dimensions of 14 x 4.5 x 3 cubic inches. The total cost of the PVA-1000S as indicated on the manufacturer website is \$5,695 or \$6,295 including the 30A capability.

#### **1.2.8 Summary**

There is limited development in the literature concerning I-V curve tracers. Most of the focus on I-V curves is the extraction of the PV module parameters using novel methods. The capacitive load topology has not been improved upon since it was first proposed in [59]. Most of the research of capacitive topologies is focusing on improving the high power characteristics as shown in [60]. There is a significant issue with size, weight and price when it comes to products both in the market and in literature. The main challenges that have to be overcome are the size and costs of the switches and also the complicated switching circuits need to be simplified.

#### 1.3. Overview of PV Emulators

PV emulators come in different topologies but mostly rely on switching converters for power output capability. Since PV systems are connected to dynamic loads via inverters and maximum power point (MPPT) trackers, there is a lot of work being done to optimize the quality of the emulated output. When selecting or designing a PV emulator, the following attributes carry significant importance:

- 1. The PV emulator should be able to emulate any PV module as long as the outputs lie within the limits of the emulator output;

- 2. Emulate PV module outputs for different irradiance, temperature, and partial shading conditions;

- 3. Be portable;

- 4. Have high efficiency as to not require active cooling;

- 5. Have good dynamic response; and

- 6. Allow testing solar equipment such as inverters and maximum power point trackers.

#### 1.3.1. Circuit Topologies

While generally constructed from switching circuits, it is possible to construct a low power PV module emulator using a linear regulator connected to a DC power supply [61-62]. This approach will give the purest and cleanest DC output of any topology while being extremely inefficient and suitable for only applications lower than 100W.

For high power applications, switching power supplies are preferred for their superior efficiency values. There are two main types of switching power supplies considered for PV module emulation: AC-DC and DC-DC power supplies.

If the PV module emulator in question is designed to be run off the ac grid, it is possible to choose an AC-DC topology such as power factor correction, flyback, or forward converters. On the other hand, if the emulator runs off a DC power supply, then a DC-DC topology such as buck, buck-boost, or boost converters will be more suitable. Examples in the literature include single-phase DC-DC buck converter, three-phase AC-DC voltage source and current source rectifier, and an LLC resonant DC-DC converter [63-65].

In addition to circuit topologies, there are two main ways of generating the current-voltage relationship of the photovoltaic curve: analog-based and digital techniques [66-71]. The analog-based reference generation relies on analog circuits. One example is the use of a physical solar cell to generate the I-V relationship and simply amplify it for higher power output [31]. The digital techniques involve two methods of reference generation. The first method relies on equation solving where the complex equation in the photovoltaic model is used [72-73]. This method requires a sophisticated digital signal processor to make very fast calculations as to not slow down the loop frequency. The second method relies on generating the I-V reference and storing it in memory within a look up table with or without linear interpolation [74-77]. Increasing the number of points allows for greater resolution and accuracy.

The physical cell method relies on the implementation of an actual solar cell with a small amount of light illuminating it. The cell bias is simply the downscaled version of the PV emulator output voltage, and the solar cell current generated at the solar cell is outputted into the load using analog amplifiers. This requires a lighting source and a small circuit and area to accommodate the solar cell.

Equation solving implies that the photovoltaic emulator is calculating the diode equation given in the PV model section between each iteration. This requires the least amount of memory

with the most amount of computational time, and as shown in Chapter 4, does not appear to be fast enough to keep the loop frequency high for dynamic loads.

The look up table (LUT) method is one of the preferable methods since it relies on calculating the operational points before running the tests; therefore, saving tremendous amount of computational time at the expense of memory bandwidth. The points in between the values can be connected in two ways: either a few key points can be set and the program simply performs a linear interpolation between the two adjacent points, or as proposed in Chapter 4, a unique look up table value for each ADC value that eliminates linear interpolation overhead while adding a lot of memory requirements.

#### 1.3.2. Photovoltaic Emulators in Literature

Koran *et al.* propose a PV module emulator device based on an AC-DC topology using the physical cell method [30]. The physical cell reference circuit schematic is based on a single solar cell connected across a MOSFET operating in the saturation region as a constant voltage load. The voltage and current values of the reference cell are measured to drive the control circuit.

The power section is complicated as it utilizes multiple circuits connected in series. The grid voltage is fed into an AC-DC synchronous rectifier and the resulting high DC voltage is filtered via a DC-link capacitor. This output is connected to the input of a DC-DC boost converter to increase the output voltage. The output of the DC-DC boost converter is scaled and fed into the physical reference circuit and the current output is again scaled and fed into a digital PI controller that drives the PWM signal to the boost converter. The output of the PV emulator is capable of emulating PV systems up to 200V and 20A.

The switching frequency of the PV emulator is 33 kHz, leading to unnecessarily large passive components with significant bulk and large volume. The high voltages and the multiple stages make it hard to choose efficient switching devices, which necessitates the usage of large heat sinks with large fans. Multiple boards are connected within a large box with the reference cell and light fixture placed on top.

While the authors have extensive knowledge on power electronics circuit design, the waveforms of the emulated curves do not look particularly good as their fill factors are much lower than the expected 60-80% range. Nevertheless, they were able to emulate a partially shaded PV system with great success. Their use of bulky analog references and low switching frequencies seems to be a problem for robust and high power density designs.

Gonzalez-Medina *et al.* propose quite a different approach in their PV module emulator which is based on a DC-DC converter with a simple non-synchronous buck converter power stage running at 100 kHz switching frequency [29]. Unlike others, the authors use a look up table with 26 strategically selected points, including a higher density of points near the maximum power point, with linear interpolation between two successive points to calculate the output. The authors have elected to use analog PI controllers for their inherent speed advantage at the expense of difficult tuning and large constant variations introduced by large capacitor variations in the PI circuit. The authors simply measure the output voltage and feed it into the look up table, which outputs a voltage through a digital to analog converter that drives the analog PI controller.

Due to the relatively high switching frequency of 100 kHz, the circuit requires smaller passive components and is possible to have it fit over the size of a typical mouse pad. Key advantages are look up table execution, which eliminates the need for a reference cell and challenging illumination and measurement circuits. The analog PI controller is a proven

topology, which gives good results but is being quickly phased out in literature and in the industry for digital controls.

#### **1.3.3. Summary**

Two of the main concerns in power electronic circuits are the power density and power efficiency. While most of the literature on power converters and topologies focuses on these two parameters, when it comes to PV emulators, these values have not been deemed important. One reason being that PV emulators are stationary units and portability is not desirable. Another reason given is that efficiency is not very important because a cooling system can be devised.

While both concerns are true at first thought, a deeper look into the power density and efficiency metrics paints another picture. Having a very high power density circuit allows for improved portability and plug-and-play simplicity that is not common. A high efficiency circuit allows for fanless designs as discussed in Chapters 4 and 5, and also makes long tests possible because heating and local hot spots are not a concern. The emulator can also run in elevated temperature environments to better emulate high ambient temperatures that occur in summer when testing inverters and other equipment.

The industry has been moving towards digital controls in power electronic circuits for a while, and keeping up with this latest trend is important for innovation. Most PV emulators in the literature rely on analog controllers; however, all PV emulators in this dissertation rely on digital controls.

Analog-based I-V reference generation is not very straightforward and easy as it is claimed to be, since it does not allow for easily changing the open-circuit voltage, short-circuit current, fill-factor, operational temperature, irradiance, and partial shading parameters. Digital-based references are capable of much higher flexibility in these regards. With digital references,

it is possible to program changing dynamic conditions of irradiance, temperature and partial shading as well. Therefore, all circuits proposed in this work are based on digital I-V reference generation.

#### 1.4. Dissertation Outline

This dissertation consists of six chapters all geared towards the main objective of this work: improving the capabilities and reducing the volume and price of I-V curve tracers, and improving the power density, efficiency, and dynamic performance of silicon and GaN-based photovoltaic emulators using buck converters. I-V curve tracers allow for the measurement of typical curves for single module and high power PV arrays and PV emulators make possible the use of DC power supplies in emulating PV module characteristics.

Chapter 1 discusses the background of this research, drawing examples from academic literature and industrial products. Different examples of I-V curve tracers and PV module emulators are presented with their merits and drawbacks. The main issue with the I-V curve tracers in literature and market are the high costs and the high volume of the measurement system. These issues will be challenged and overcome as outlined in Chapter 3. The main drawbacks of PV module emulators are the dynamic capabilities, the power density, and the power efficiency. The PV models used in specific literature examples leaves a lot to be desired in producing an accurate emulated output. Work on PV module emulators will be carried out in Chapters 4 and 5.

In the second chapter, suitable PV models will be investigated with a focus on simplicity, accuracy and applicability within I-V measurements and PV emulators. The PV model chosen must model PV modules at different temperature, irradiance and partial shading conditions

accurately. The elimination of the series and shunt resistance parameters will make it possible to simplify the required calculations for the PV emulator. The parameter conversion from arbitrary values to standard testing conditions (STC) will allow the I-V curve tracer to translate the measurements taken to STC conditions with great accuracy.

In Chapter 3, two distinct generations of curve tracers will be proposed with the goal of minimizing volume, costs and increasing measurement accuracy, resolution and the number of data points. Generation 1 will lay the foundation as the proof of concept for capacitive load I-V curve measurements. Generation 1.5 will build upon it with algorithm optimizations to make measurements at different conditions including partial shading. Generation 2 will do away with the mechanical relays from the previous generation and MOSFET switches will be explored with the goal of allowing for a more compact and lower-cost design with improved reliability.

In Chapter 4, new PV module emulator designs is investigated through two distinct generations. While both are buck converters, generation 1 will focus on creating the algorithm and basic circuitry that forms the heart of the PV emulator with the use of a non-synchronous buck converter and an equation solving system. Generation 2 will demonstrate innovation in high switching frequency along with significant reduction in steady-state errors and power losses. In generation 2.5, the dynamic performance of the emulator will be increased to work with dynamic loads. This will be accomplished by moving from an equation solving approach to a look-up table approach. The new approach will reduce the execution time and improve the loop frequency significantly.

Chapter 5 examines the use of novel GaN devices to replace traditional silicon devices in PV module emulators. The impact of GaN MOSFETs for increasing the efficiency, power density and dynamic response of PV module emulators is explored. Static tests using an

electronic load and dynamic tests using an inverter are demonstrated that show the accuracy of emulating both static conditions and temporal changes of irradiance, temperature, and partial shading. The design of the algorithm and the controller are described as well, as they have a significant effect on the loop frequency, and obtaining better dynamic performance to match the dynamic characteristics of actual PV modules.

Chapter 6 summarizes the main contributions of this work and proposes future work and research avenues.

### **CHAPTER 2**

## MODELING OF PHOTOVOLTAIC MODULES

## 2.1. Introduction

Modeling the behavior of photovoltaic modules is important for module characterization, I-V curve measurements, and PV module emulation. The model used must represent photovoltaic modules accurately without prohibitively difficult mathematical operations that make the solutions hard to obtain.

PV module measurements taken outdoors are under an uncontrolled solar irradiance and ambient temperature. For consistent results, these measurements must be converted to standard testing conditions (STC) for proper characterization of PV modules. Similarly, with I-V curve measurements, the measured curves need to be transposed to STC for meaningful and comparable results.

In order to convert the I-V measurements of PV modules to STC, there are only six parameters that can be used towards STC conversion:

- Voltage  $V_{pv}$  and current  $I_{pv}$  output of the module,

- Incident irradiance S, the ambient temperature  $T_{ambient}$ , and

- Temperature coefficient of voltage  $\alpha_V$  and temperature coefficient of current  $\alpha_I$ .

The PV model will have to only work with S and  $T_{ambient}$  variables and rely on the datasheet values of  $\alpha_V$  and  $\alpha_I$  to convert the measurements of  $V_{pv}$  and  $I_{pv}$  from arbitrary conditions to STC. After STC conversions are made, if desired, the values for open-circuit voltage  $V_{oc}$ , short-circuit current  $I_{sc}$ , diode saturation current  $I_o$ , diode ideality factor n, series resistance  $R_{sh}$  and shunt resistance  $R_{sh}$  can be extracted from the I-V curve.

PV module emulation on the other hand, does not require STC conversions and must work with any given values for  $V_{oc}$ ,  $I_{sc}$ ,  $I_o$ ,  $R_s$ ,  $R_{sh}$ , S and  $T_{ambient}$ . The complexity of the PV model can be increased for emulation purposes as the curve is drawn from scratch, unlike the conversion processes used for measurements.

There are two approaches to modeling PV modules, the first of which can be modeled as multiple solar cells connected in series (usually 60) to construct what is known as a high power module with a power rating between 200W and 250W. The second approach, which is the approach taken in this dissertation, is to model the entire PV module as a single solar cell. This has some advantages when working with PV modules, as we do not have to calculate individual solar cell  $V_{oc}$  and factor in the number of cells, which reduces the complexity of the model.

#### 2.2. Diode Models

There are three main ways of modeling photovoltaic modules in the literature: single-diode, ideal single-diode, and dual-diode models. These models slightly differ among themselves in theory, but there is a large discrepancy when it comes to mathematical complexity. Among these, the ideal single diode model provides the simplest mathematical equation that is easily solvable without using iterative methods, which both the single diode and the dual-diode require. In the single and dual-diode models, the presence of photovoltaic current both on the left side of the equation and within an exponential on the right side of the equation calls for the Lambert W method, which significantly increases the mathematical and computational overhead [78].

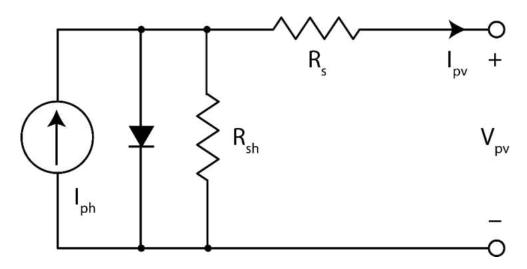

## 2.2.1. Single Diode Model

The single diode model is the most commonly used model in solar cells owing to its relative simplicity and good correlation. The solar cell is modeled as a current source with  $I_{ph}$ , a

series anti-parallel diode, the series resistance  $R_s$  that models the series losses in the device, and the shunt resistance  $R_{sh}$  that models the recombination losses in the device. The schematic of the model is given in Figure 2.1.

Figure 2.1: Single diode model of a solar cell with series and shunt resistances based on [79].

The equation for the single-diode model is given by Equation 2.1,

$$I_{pv} = I_{ph} - I_o \left[ \exp\left( A \left( V_{pv} + R_s I_{pv} \right) \right) - 1 \right] - \frac{V_{pv} + R_s I_{pv}}{R_{sh}}$$

(2.1)

where A combines the diode ideality factor, Boltzmann's constant, cell temperature and electronic charge,

$$A = \frac{q}{nkT} \tag{2.2}$$

For modern PV cells and modules, the effects of  $R_s$  and  $R_{sh}$  are not as significant as they used to be, due to the improvements in manufacturing processes in recent years.

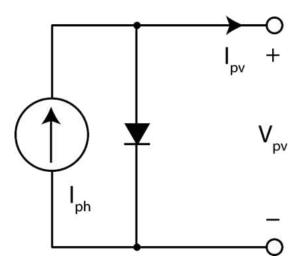

## 2.2.2. Ideal Single Diode Model

The ideal diode model ignores the non-ideal effects of series and shunt resistances and simplifies both the schematic and the equations.

Figure 2.2: Ideal single diode model of solar cell without resistances based on [80].

A few assumptions are made for the ideal single diode model: the series resistance is assumed to be zero, the shunt resistance is assumed to be infinitely large, the photon current  $I_{ph}$  is assumed equal to the short-circuit current  $I_{sc}$  and the exponential term is assumed much larger than one, allowing the removal of the "-1" term. The new equation describing the diode therefore is:

$$I = I_{sc} - I_o \exp(A \cdot V) \tag{2.3}$$

$$I_{sc} = I_o \exp(A \cdot V_{oc}) \tag{2.4}$$

$$I_o = I_{sc} \exp(-A \cdot V_{oc}) \tag{2.5}$$

$$I = I_{sc}(1 - \exp[A \cdot (V - V_{oc})])$$

(2.6)

$$I_{mpp} = I_{sc} \left( 1 - \exp\left[ A \cdot \left( V_{mpp} - V_{oc} \right) \right] \right) \tag{2.7}$$

$$A = \frac{\ln\left(1 - \frac{I_{mpp}}{I_{sc}}\right)}{V_{mpp} - V_{oc}} \tag{2.8}$$

$$I = I_{sc} \left[ 1 - \exp\left(\frac{\ln\left(1 - \frac{I_{mpp}}{I_{sc}}\right)(V - V_{oc})}{V_{mpp} - V_{oc}}\right) \right]$$

$$(2.9)$$

In the end, the current equation can be simply derived from the open-circuit voltage  $V_{oc}$ , the short-circuit current  $I_{sc}$ , the maximum power point voltage  $V_{mpp}$  and the maximum power point current  $I_{mpp}$ . This eliminates the requirement for knowing  $I_o$  and a, values which are not provided by module manufacturers.

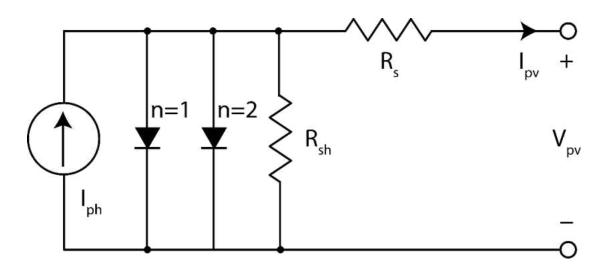

## 2.2.3. Two Diode Model

Both the single diode and the ideal single diode solar cell model assume a fixed value for the diode ideality factor n. This assumption does not hold in reality since the diode ideality factor is dependent on the bias voltage across the solar cell.

Figure 2.3: Two diode model of solar cell with series and shunt resistances based on [81].

When  $V_{pv}$  is large, the recombination of the charge carriers (holes and electrons) is dominated by surfaces and bulk regions, therefore the ideality factor n converges to 1. On the other hand, when the cell voltage  $V_{pv}$  is low, the recombination at the junction dominates and n converges to 2.

The second diode in the two diode model is necessary to account for junction recombination effects. Some drawbacks have been observed in literature, i.e. the recombination is dependent on carrier concentration, the two diode model is challenging to resolve mathematically, small fluctuations in light intensity overwhelm the second diode effects, and the two diode model is more common for dark measurements (without light) [81].

The current equation used in the two diode model is given below,

$$I = I_L - I_{o1} \left( \exp \left[ \frac{q(V + IR_s)}{kT} \right] - 1 \right) - I_{o2} \left( \exp \left[ \frac{q(V + IR_s)}{2kT} \right] - 1 \right) - \frac{V + IR_s}{R_{sh}}$$

(2.10)

For dark measurements (which are more common) the equation becomes,

$$I = I_{o1} \left( \exp \left[ \frac{q(V + IR_s)}{kT} \right] - 1 \right) + I_{o2} \left( \exp \left[ \frac{q(V + IR_s)}{2kT} \right] - 1 \right) + \frac{V + IR_s}{R_{sh}}$$

(2.11)

Ignoring the "-1" term makes analysis much easier under light,

$$I = I_L - I_{o1} \exp\left[\frac{q(V + IR_s)}{kT}\right] - I_{o2} \exp\left[\frac{q(V + IR_s)}{2kT}\right] - \frac{V + IR_s}{R_{sh}}$$

(2.12)

and under dark conditions,

$$I = I_{o1} \exp\left[\frac{q(V + IR_s)}{kT}\right] + I_{o2} \exp\left[\frac{q(V + IR_s)}{2kT}\right] + \frac{V + IR_s}{R_{sh}}$$

(2.13)

## 2.2.4. Comparison of Diode Models

The ideal single diode model provides the easiest method for modeling solar cells. With the inclusion of the series and shunt resistances, the model becomes highly accurate and can approximate the small current reduction from the short-circuit point to maximum power point very well [34]. The two-diode model on the other hand, complicates matters beyond what is generally worth accomplishing; that is to say, the drawbacks far outweigh the benefits.

Mahmoud *et al.* studied different models to model photovoltaic modules accurately [34]. In their paper, they propose the following enhancement to the single diode model:

$$I = I_{ph} - I_s \left( \exp\left[ \frac{\alpha_0 + \alpha_1 V + \alpha_2 V^2 + \alpha_3 V^3}{\frac{N_s kTA}{q}} \right] - 1 \right) - \frac{\alpha_0 + \alpha_1 V + \alpha_2 V^2 + \alpha_3 V^3}{R_{sh}}$$

(2.14)

As shown above, the goal is to eliminate the difficult to calculate "current-within-the-exponent" issue by using a polynomial that approximates the relationships,

$$\alpha_0 = I_{sc} R_s \tag{2.15}$$

$$\alpha_0 + \alpha_1 V_{mpp} + \alpha_2 V_{mpp}^2 + \alpha_3 V_{mpp}^3 = V_{mpp} + I_{mpp} R_s$$

(2.16)

$$\alpha_0 + \alpha_1 V_{oc} + \alpha_2 V_{oc}^2 + \alpha_3 V_{oc}^3 = V_{oc}$$

(2.17)

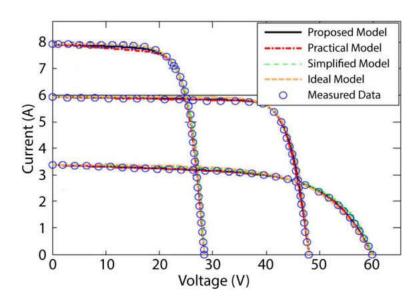

Figure 2.4: Comparison of different models when fitting to measured data based on [34].

Their results show that the computational times decreased at a cost of increased inaccuracy at low irradiance levels. In Figure 2.4, the practical model refers to the single-diode model, the simplified model refers to the single-diode model with the shunt resistance omitted, the ideal model is the ideal single-diode model, and the proposed model is the polynomial fitted model [34]. As clearly shown, all models lie within the measured data circles indicating that regardless of model chosen, they all model PV modules well.

#### 2.3. Model Used in Dissertation

#### 2.3.1. Model selection

The model chosen for the purposes of this work needs to fulfill the following criteria:

- 1. Must be easily solvable,

- 2. Must model irradiance, temperature and shading effects accurately,

- 3. Must allow the input of  $V_{oc}$ ,  $I_{sc}$ ,  $I_o$ , S, T,  $\alpha_V$ ,  $\alpha_I$ , system shading and shading strength,

- 4. Must be highly accurate,

- 5. Must work in any given application, and

- 6. Must model the whole PV module or PV array as a single cell.

After the analysis of different models in the literature and especially looking at Figure 2.4, the ideal single diode model was chosen as the most suitable model for this work. To confirm the validity of our choice, the ideal diode model was then verified with the photovoltaic modules installed on the roof of Kaufman Hall at the Old Dominion University consisting of 8 series connected Bosch c-Si m60 photovoltaic modules. The results are shown in the Figures 2.5 and 2.6 below.

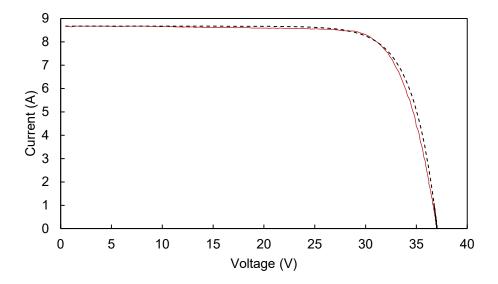

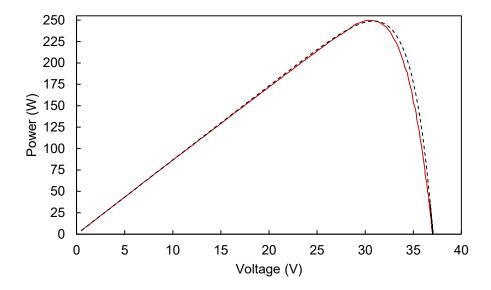

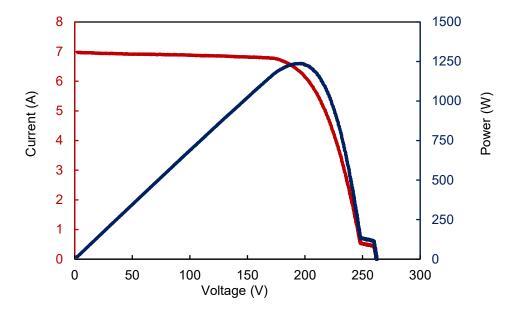

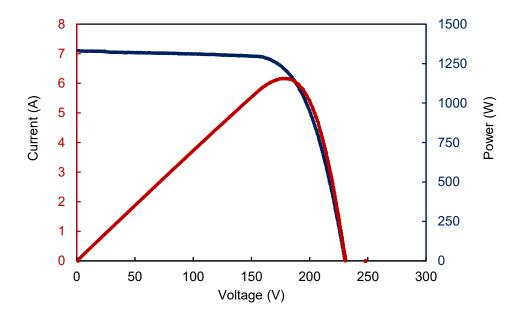

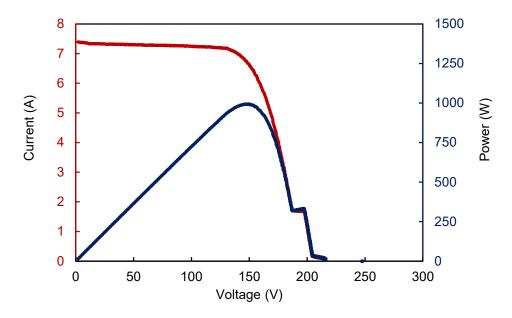

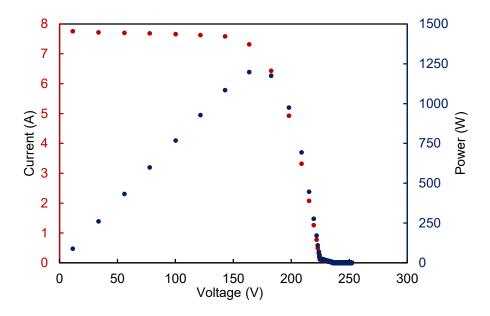

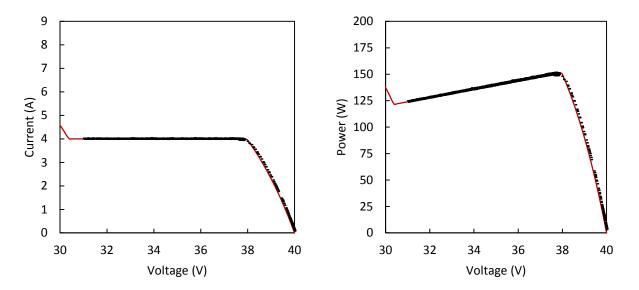

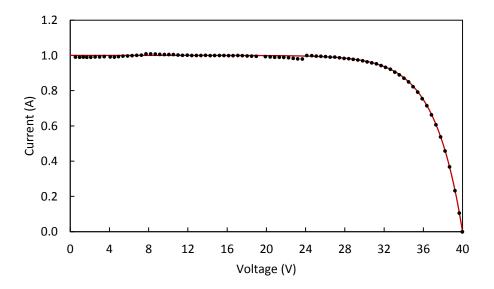

Fig. 2.5: Measured (solid line) vs. simulated (dashed line) I-V curves.

Fig. 2.6: Measured (solid line) vs. simulated (dashed line) P-V curves.

The conditions in Figures 2.5 and 2.6 were  $V_{oc} = 37.03 \text{ V}$ ,  $I_{sc} = 8.67 \text{A}$  and  $I_o = 1 \mu \text{A}$  with a fill factor of 77.8% show suitable correlation between the measured and calculated curves.

# 2.3.2. Modeling Effects of Irradiance and Temperature

The power output of PV modules are dependent on irradiance and temperature. This section discusses the equations used to convert values from STC to different S and T conditions. In Chapter 3, measurements made in arbitrary S and T conditions are converted to STC using similar equations.

The procedure to model effects of irradiance and temperature are as follows. First, the values for the variables shown in Table 2.1 are input. These inputs correspond to the STC values of short-circuit current, open-circuit voltage and dark saturation current, values of irradiance and temperature, the temperature coefficients found in the module datasheet, and the band gap of the PV module material (1.12eV for silicon).

Table 2.1: Ideal model initialization parameters.

| Symbol       | Name                             | Value                              |

|--------------|----------------------------------|------------------------------------|

| $T_{cell}$   | Module temperature               | 25.0°C (user input)                |

| $T_{ref}$    | Reference temperature            | 25.0°C                             |

| $V_{oc,stc}$ | Open-circuit voltage             | 40V (user input)                   |