# Old Dominion University ODU Digital Commons

Electrical & Computer Engineering Theses & Disssertations

**Electrical & Computer Engineering**

Winter 2008

# Design of a High-Speed Architecture for Stabilization of Video Captured Under Non-Uniform Lighting Conditions

Ming Zhu Zhang Old Dominion University

Follow this and additional works at: https://digitalcommons.odu.edu/ece\_etds Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Zhang, Ming Z.. "Design of a High-Speed Architecture for Stabilization of Video Captured Under Non-Uniform Lighting Conditions" (2008). Doctor of Philosophy (PhD), dissertation, Electrical/Computer Engineering, Old Dominion University, DOI: 10.25777/ ac8b-wr03

https://digitalcommons.odu.edu/ece\_etds/192

This Dissertation is brought to you for free and open access by the Electrical & Computer Engineering at ODU Digital Commons. It has been accepted for inclusion in Electrical & Computer Engineering Theses & Dissertations by an authorized administrator of ODU Digital Commons. For more information, please contact digitalcommons@odu.edu.

#### **DESIGN OF A HIGH-SPEED ARCHITECTURE**

# FOR STABILIZATION OF VIDEO

# **CAPTURED UNDER NON-UNIFORM LIGHTING CONDITIONS**

by

Ming Zhu Zhang B.S. December 2004, Old Dominion University M.S. August 2005, Old Dominion University

A Dissertation Submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirement for the Degree of

#### DOCTOR OF PHILOSOPHY

#### ELECTRICAL AND COMPUTER ENGINEERING

OLD DOMINION UNIVERSITY December 2008

Approved by:

Dr. Vijayan K. Asari (Director)

Dr. James Leathrum, Jr. (Member)

Dr. Jiang Li (Member)

Dr. Shunichi Toida (Member)

#### ABSTRACT

# DESIGN OF A HIGH-SPEED ARCHITECTURE FOR STABILIZATION OF VIDEO CAPTURED UNDER NON-UNIFORM LIGHTING CONDITIONS

Ming Zhu Zhang Old Dominion University, 2008 Director: Dr. Vijayan K. Asari

Video captured in shaky conditions may lead to vibrations. A robust algorithm to immobilize the video by compensating for the vibrations from physical settings of the camera is presented in this dissertation. A very high performance hardware architecture on Field Programmable Gate Array (FPGA) technology is also developed for the implementation of the stabilization system. Stabilization of video sequences captured under non-uniform lighting conditions begins with a nonlinear enhancement process. This improves the visibility of the scene captured from physical sensing devices which have limited dynamic range. This physical limitation causes the saturated region of the image to shadow out the rest of the scene. It is therefore desirable to bring back a more uniform scene which eliminates the shadows to a certain extent. Stabilization of video requires the estimation of global motion parameters. By obtaining reliable background motion, the video can be spatially transformed to the reference sequence thereby eliminating the unintended motion of the camera.

A reflectance-illuminance model for video enhancement is used in this research work to improve the visibility and quality of the scene. With fast color space conversion, the computational complexity is reduced to a minimum. The basic video stabilization model is formulated and configured for hardware implementation. Such a model involves evaluation of reliable features for tracking, motion estimation, and affine transformation to map the display coordinates of a stabilized sequence. The multiplications, divisions and exponentiations are replaced by simple arithmetic and logic operations using improved log-domain computations in the hardware modules. On Xilinx's Virtex II 2V8000-5 FPGA platform, the prototype system consumes 59% logic slices, 30% flipflops, 34% lookup tables, 35% embedded RAMs and two ZBT frame buffers. The system is capable of rendering 180.9 million pixels per second (mpps) and consumes approximately 30.6 watts of power at 1.5 volts. With a 1024×1024 frame, the throughput is equivalent to 172 frames per second (fps).

Future work will optimize the performance-resource trade-off to meet the specific needs of the applications. It further extends the model for extraction and tracking of moving objects as our model inherently encapsulates the attributes of spatial distortion and motion prediction to reduce complexity. With these parameters to narrow down the processing range, it is possible to achieve a minimum of 20 fps on desktop computers with Intel Core 2 Duo or Quad Core CPUs and 2GB DDR2 memory without a dedicated hardware.

© 2008 Ming Zhang. All Rights Reserved.

,

# ACKNOWLEDGMENTS

First of all, I would like to thank Dr. K Vijayan Asari for his guidance and efforts as my dissertation director. I am also very grateful for such an opportunity to explore on a broader view of the chosen topic. I would also like to thank Dr. James Leathrum, Jr, Dr. Jiang Li, and Dr. Shunichi Toida for their invaluable time and consideration in serving on my dissertation committee. I greatly appreciate their efforts. Finally, I would like to thank my family and friends for all their support.

# TABLE OF CONTENTS

vi

| List of T | ables | •••••                |             |                                                     | ix  |

|-----------|-------|----------------------|-------------|-----------------------------------------------------|-----|

| List of F | igure | s                    | •••••       |                                                     | X   |

| Chapter   |       |                      |             |                                                     |     |

| 1         | INT   | INTRODUCTION         |             |                                                     |     |

|           | 1.1   |                      |             | e Research                                          |     |

|           | 1.2   |                      |             | e of the Dissertation                               |     |

|           | 1.3   | -                    |             | ons                                                 |     |

|           | 1.4   | Organ                | ization of  | Forthcoming Chapters                                | 8   |

| 2         | ALC   | GORITHMIC BACKGROUND |             |                                                     |     |

|           | 2.1   | Neces                | sity of Ima | age and Video Enhancement                           | 9   |

|           | 2.2   |                      | -           | ood Tracking Features                               |     |

|           | 2.3   |                      |             | otion Parameters                                    |     |

|           | 2.4   | Summ                 | ary         |                                                     | 16  |

|           |       |                      |             |                                                     |     |

| 3         | COI   |                      |             | COMPLEXITY REDUCTION                                |     |

|           | 3.1   |                      |             | the Operator                                        |     |

|           | 3.2   |                      |             | arithmic Domain Computation                         |     |

|           |       | 3.2.1                | -           | ty of Approximation and Its Benefits                |     |

|           |       | 3.2.2                | -           | ment of Precision with Piecewise Straight Lines     |     |

|           |       | 3.2.3                | Bit-level   | Curve Fitting                                       | 24  |

|           |       |                      |             |                                                     | • • |

| 4         |       |                      |             | DEL                                                 |     |

|           | 4.1   |                      |             | y Video Enhancement                                 |     |

|           |       | 4.1.1                |             | orphic Processing in HSV-Domain                     |     |

|           |       | 4.1.2                |             | main Enhancement with Fast Color Space Conversion   |     |

|           | 4.0   | 4.1.3                |             | son of Visual Quality with Relevant Algorithms      |     |

|           | 4.2   |                      |             | n and Tracking                                      |     |

|           |       | 4.2.1                |             | v of the Framework                                  |     |

|           |       | 4.2.2                |             | ormulation                                          |     |

|           |       |                      | 4.2.2.1     | Extraction of $\beta$ Layers of Textures            | 37  |

|           |       |                      | 4.2.2.2     | Weight Matrix for Fusing $\beta$ Layers of Textures | 39  |

|           |       |                      | 4.2.2.3     | Feature Selection                                   | 40  |

|           |       |                      | 4.2.2.4     | Feature Measure                                     | 41  |

|           |       |                      | 4.2.2.5     | Verification and Update of Weight Memory of l2      |     |

|           |       |                      | 4.2.2.6     | Convergence of the Network                          |     |

|           |       | 4.2.3                | Prelimin    | ary Simulation                                      |     |

|           |       |                      | 4.2.3.1     | Automatic Feature Selection                         | 43  |

|           |       |                      | 4.2.3.2     | Feature Tracking                                    | 46  |

|   |            | 4.2.4                | Potential Extension of the Framework                  | 47  |  |  |

|---|------------|----------------------|-------------------------------------------------------|-----|--|--|

|   |            | 4.2.5                | Simplification                                        | 48  |  |  |

|   |            |                      | 4.2.5.1 Single Trivial Layer of Texture               | 48  |  |  |

|   |            |                      | 4.2.5.2 Sub-feature Representation                    |     |  |  |

|   | 4.3        | Estima               | ation of Motion by Consistency of Motion Parameters   |     |  |  |

|   |            | 4.3.1                | Estimation of Inlier Motion                           |     |  |  |

|   |            | 4.3.2                | Estimation of Intended Motion                         |     |  |  |

|   |            | 4.3.3                | Simplification by Order of Search                     | 56  |  |  |

|   |            | 4.3.4                | Algorithmic Simulation of the Stabilization Prototype | 58  |  |  |

|   | 4.4        | Summ                 | ary                                                   | 61  |  |  |

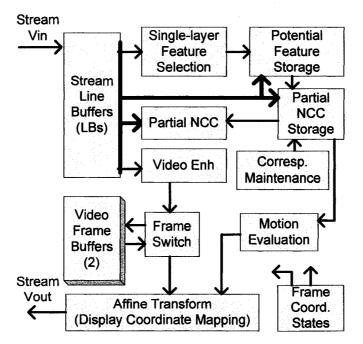

| 5 | DES        | IGN O                | F HIGH PERFORMANCE ARCHITECTURE                       | 63  |  |  |

|   | 5.1        | Overv                | iew                                                   | 63  |  |  |

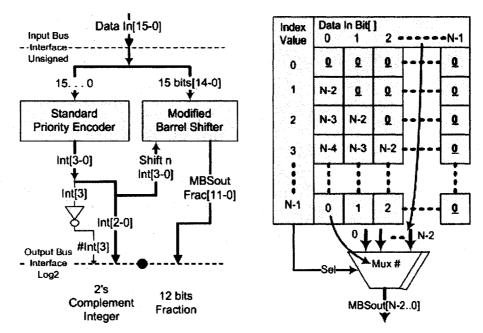

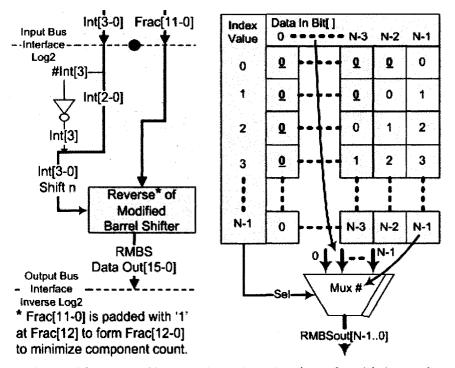

|   | 5.2        | Logari               | ithmic Domain Computation                             | 65  |  |  |

|   |            | 5.2.1                | Architecture of Log <sub>2</sub> Module               |     |  |  |

|   |            | 5.2.2                | Architecture of iLog <sub>2</sub> Module              | 67  |  |  |

|   |            | 5.2.3                | Error Correction                                      | 69  |  |  |

|   | 5.3        | Video                | Enhancement Module                                    |     |  |  |

|   |            | 5.3.1                | Overview of Computational Sequence                    |     |  |  |

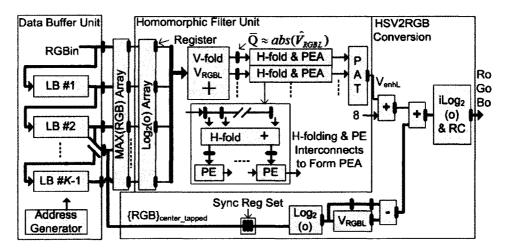

|   |            | 5.3.2                | Tightly Coupled System Architecture                   |     |  |  |

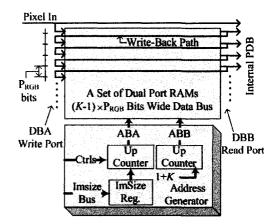

|   |            | 5.3.3                | Data Buffer Unit                                      |     |  |  |

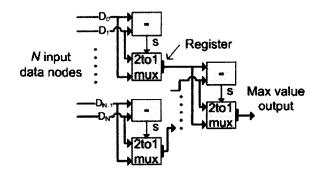

|   |            | 5.3.4                | Extraction of V-component                             |     |  |  |

|   |            | 5.3.5                | Architecture of Homomorphic Filter                    |     |  |  |

|   |            | 5.3.6                | Fast HSV to RGB Color Space Conversion                |     |  |  |

|   | 5.4        | <u> </u>             | Layer Feature Selection                               |     |  |  |

|   |            | 5.4.1                | Overview of Feature Selection & Storage               |     |  |  |

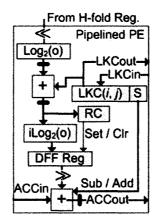

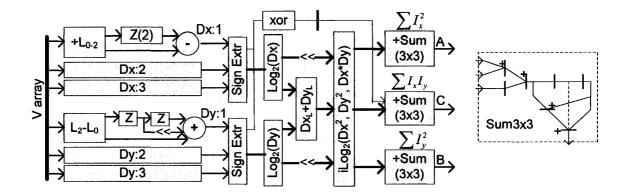

|   |            | 5.4.2                | Components of Auto-correlation Matrix                 |     |  |  |

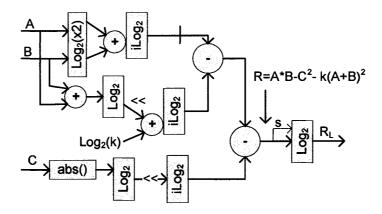

|   |            | 5.4.3                | Logarithmic Corner-ness Response                      |     |  |  |

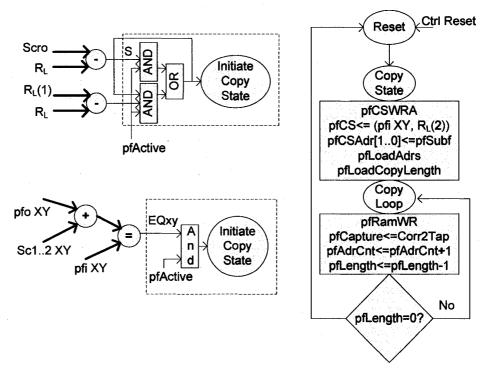

|   |            | 5.4.4                | Storage of Potential Features                         |     |  |  |

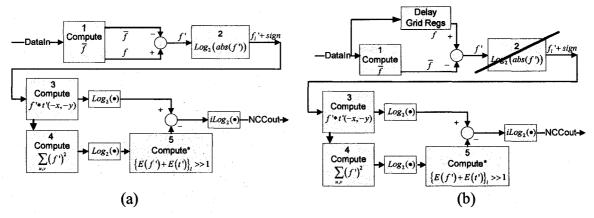

|   | 5.5        |                      | re Measure & Tracking with Improved NCC Architecture  |     |  |  |

|   |            | 5.5.1                |                                                       |     |  |  |

|   |            | 5.5.2                | Partial NCC as Parallel Filters                       |     |  |  |

|   |            |                      | 5.5.2.1 Architecture of Normalizing Factors           |     |  |  |

|   |            |                      | 5.5.2.2 2D Integral Summation                         |     |  |  |

|   |            | 553                  | 5.5.2.3 2D Correlation                                |     |  |  |

|   | 5.6        | 5.5.3<br>Correct     | Storage Layout                                        |     |  |  |

|   | 5.0<br>5.7 |                      | spondence Management<br>n Evaluation Module           |     |  |  |

|   | 5.8        |                      | r Transformation                                      |     |  |  |

|   | 5.9        |                      | ary                                                   |     |  |  |

| 6 | סדס        |                      |                                                       | 00  |  |  |

| 0 |            | RESULTS AND ANALYSIS |                                                       |     |  |  |

|   | 6.1<br>6.2 | 6                    |                                                       |     |  |  |

|   | 0.2        | 6.2.1                | Logarithmic Approximation                             |     |  |  |

|   |            | 6.2.1                | Video Enhancement                                     |     |  |  |

|   |            | 0.2.2                | 6.2.2.1 Fine-tuning Transfer Function                 |     |  |  |

|   |            |                      |                                                       | 10/ |  |  |

|          | 6.2.3 Video Stabilization                           | 108 |

|----------|-----------------------------------------------------|-----|

| 6.3      | Performance Analysis and Resource Utilization       | 112 |

|          | 6.3.1 Log <sub>2</sub> /iLog <sub>2</sub> Modules   | 112 |

|          | 6.3.2 Comparison of Video Enhancement Architectures | 113 |

|          | 6.3.3 Video Stabilization Subsystems                | 117 |

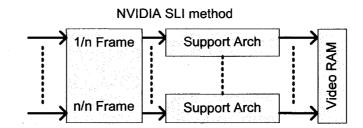

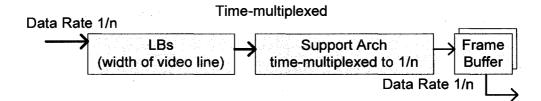

| 6.4      | Scalability of the System                           | 119 |

|          | 6.4.1 Feature Measure                               |     |

|          | 6.4.2 Frame Size and Rate                           | 121 |

|          | 6.4.3 Technological Advancement                     | 124 |

| 6.5      | Power Consumption                                   |     |

| 6.6      | Summary                                             |     |

| 7 CO     | NCLUSION & FUTURE WORK                              | 128 |

| EFERENCE | ES                                                  | 133 |

| ТТА      |                                                     | 139 |

# List of Tables

| Table                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1: Example of $\log_2$ converter with 5-bit integers and the index $k = 4$                                                                                                                                                                                                        |

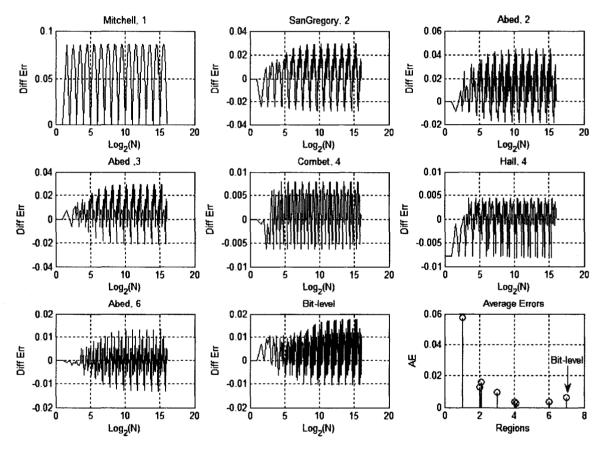

| 2: Comparison of the error range and average magnitude with other designs103                                                                                                                                                                                                      |

| 3: Average errors of feature selection and measure subsystems                                                                                                                                                                                                                     |

| 4: Performance and resource utilization for Log <sub>2</sub> module113                                                                                                                                                                                                            |

| 5: Performance and resource utilization for iLog <sub>2</sub> module113                                                                                                                                                                                                           |

| 6: Hardware resource utilization for various sizes of the kernels with<br>corresponding throughput rate114                                                                                                                                                                        |

| <ul> <li>7: Comparison of the proposed work with other implementations most relevant to reflectance-illuminace model. Note that 256 × 256 frame size (should be power of 2) is employed so the performance is not penalized for [16] and [72] to utilize FFT and IFFT.</li> </ul> |

| 8: Resource allocation and the performance of subsystems                                                                                                                                                                                                                          |

| 9: Comparison of conventional method and sub-feature representation                                                                                                                                                                                                               |

| 10: Power consumption of subsystems at 180.9 MHz system clock                                                                                                                                                                                                                     |

| 11: Power consumption of the system by FPGA resources126                                                                                                                                                                                                                          |

# List of Figures

| Figu | re                                                                                                                                                                                                                                                                                         | Page |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | 1: Decomposition and structural representation of the dataset.                                                                                                                                                                                                                             | 4    |

|      | 2: Mitchell's log <sub>2</sub> approximation (a) and the difference error (b).                                                                                                                                                                                                             | 22   |

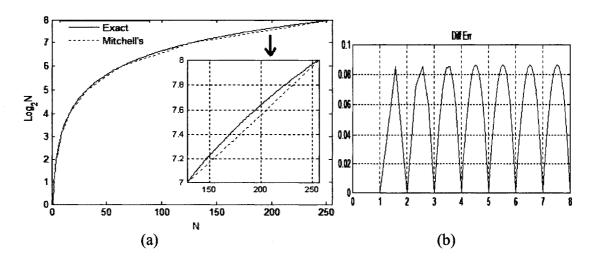

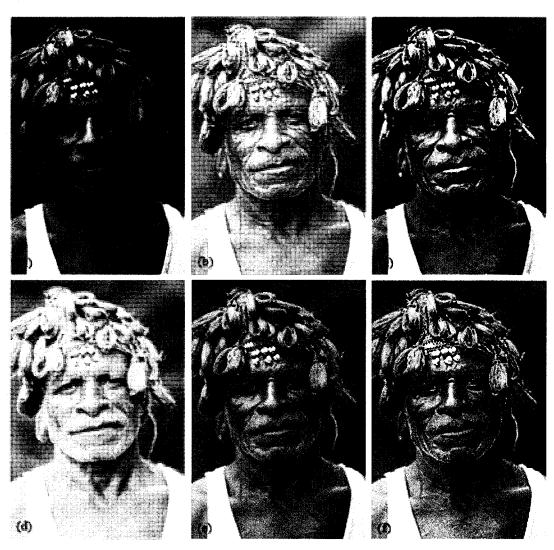

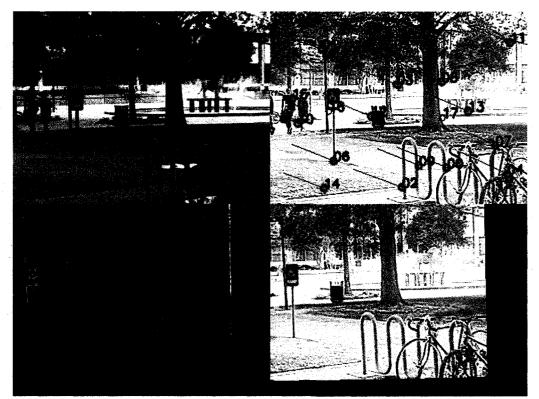

|      | 3: Algorithm simulation: (a) original, (b) enhanced (c) conical representation<br>of HSV color space. No useful color information can be obtained with V<br>component too close to the tip of the cone. Hence the excessively dark<br>regions appear pale in the enhanced image.           | 33   |

|      | 4: Algorithm Comparison: (a) original image taken from [15], (b) enhanced<br>Separate RGB channels without color correction, (c) enhanced by MSR<br>with color correction [15], (d) enhanced with LDNE [20] [21], (e)<br>enhanced with RR [5] [6] [19], (f) enhanced with the approach we  |      |

|      | proposed                                                                                                                                                                                                                                                                                   | 35   |

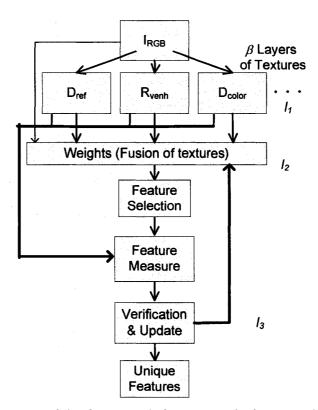

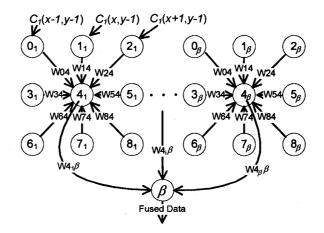

|      | 5: Block diagram of the framework for automatic feature selection for tracking.                                                                                                                                                                                                            | 37   |

|      | 6: Architecture of interconnects for fusing $\beta$ layers of textures                                                                                                                                                                                                                     | 40   |

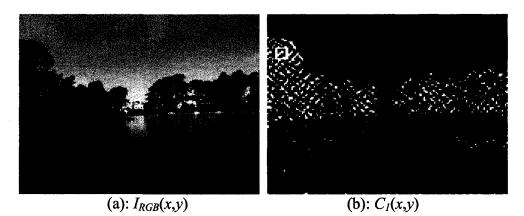

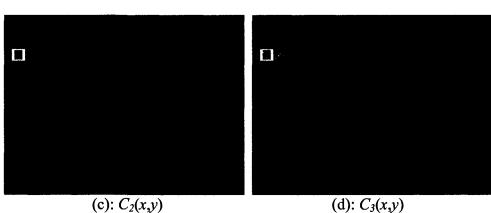

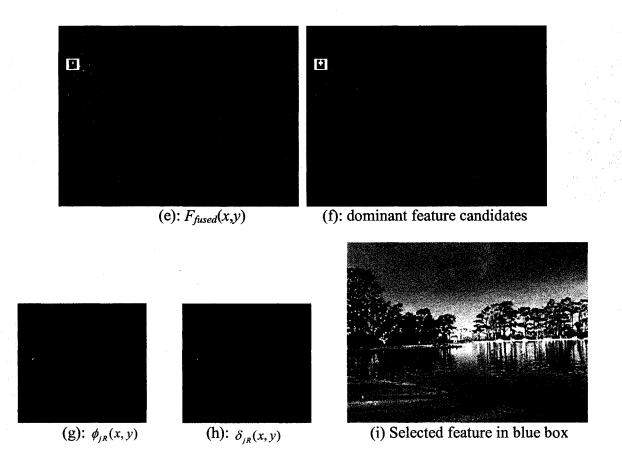

|      | 7: Input color image and the outputs of the network at different stages are illustrated in (a)-(i). White dot in (f) shows initial dominate candidate with uniqueness test ( $\upsilon$ =1 according to (4.2.12)) shown in (h). Pink dots are important corner features evaluated by [62]. | 45   |

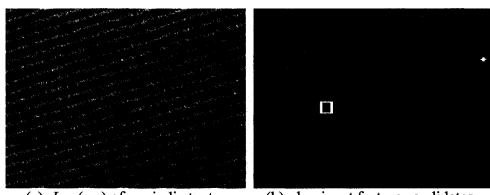

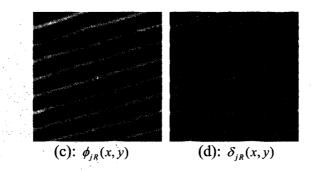

|      | 8: An example of input data with periodic textures where no feature is reliable for tracking confirmed by large $v$ computed from (d)                                                                                                                                                      | 46   |

|      | 9: Results from feature tracking after automatic feature selection scheme.<br>Shown from top-left to bottom-right are snapshots at frames 1, 56, 78, 102, 135, 161, 180, 220, and 237.                                                                                                     |      |

|      | <ul><li>10: Representation of full feature by texturally optimal sub-features in a constellation. (a) A start constellation constructed to encapsulate the spatial relationship of sub-features. (b) A straight line structure to simplify hardware realization.</li></ul>                 | 52   |

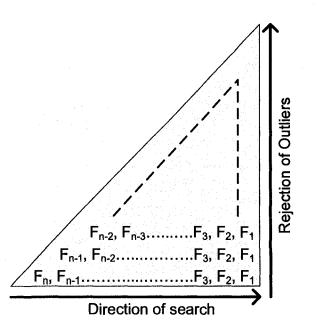

|      | 11: Triangular order of search to minimize the number of calculations and to identify the inlier and reject the outliers.                                                                                                                                                                  | 57   |

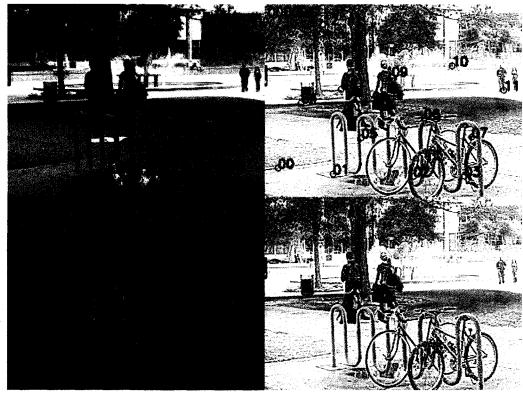

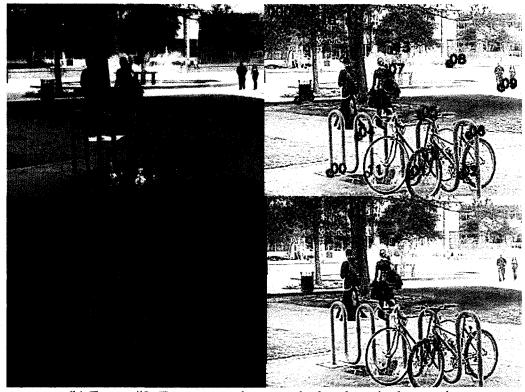

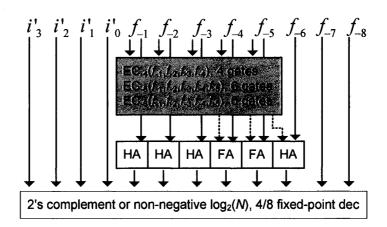

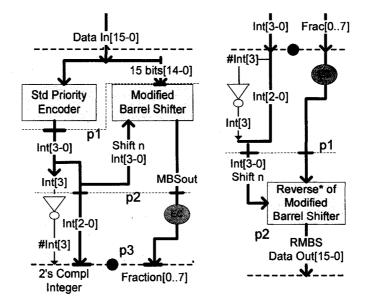

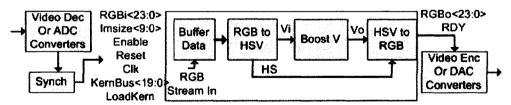

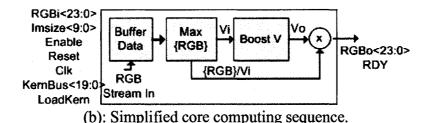

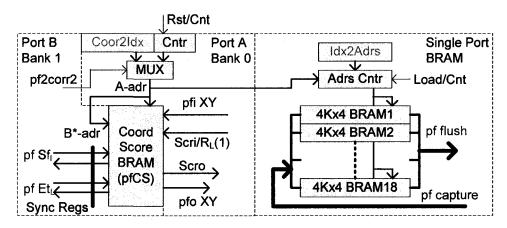

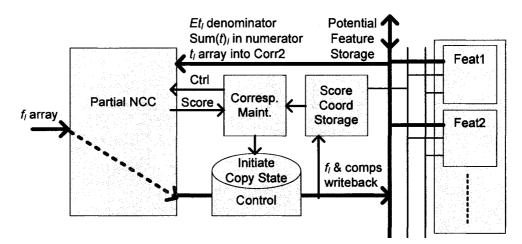

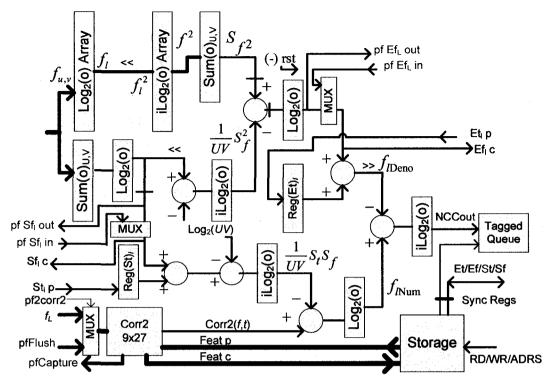

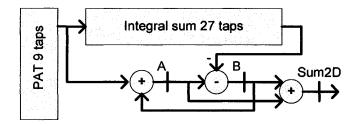

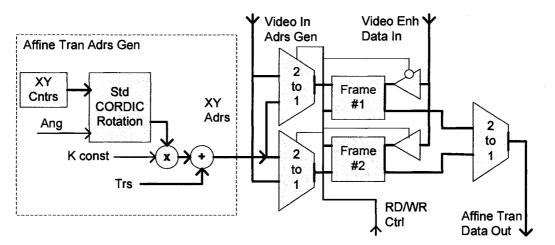

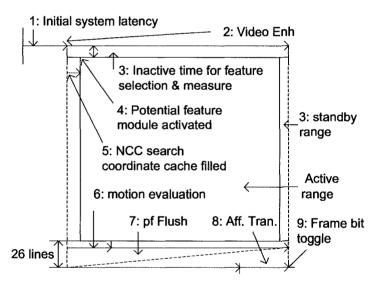

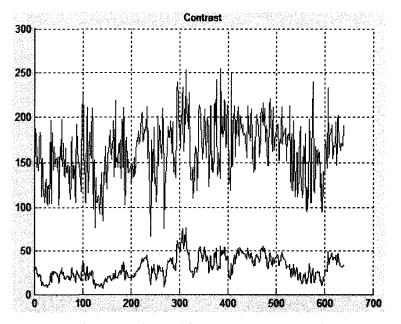

12: Snapshots of enhanced video and stabilized sequence to show different stages of the event......60 17: Fully optimized architectures of Log<sub>2</sub> and iLog<sub>2</sub> with error correction 18: Block diagram illustrates the overall sequence of computation alone with simplification......72 19: System architecture illustrates the coupling of three main units to achieve 20: Detail architecture of the DBU shown in Fig 19. The data bus of (K-1)  $\times P_{RGB}$  bits wide is grouped into a number of 24-bit paths to form effective 21: Elementary architecture of the max filter is used to extract the Vcomponent. K elements of 3-to-1 max filters are needed in the MAX(RGB) Array as shown in Fig 19.....74 24: Architecture for calculation of A, B, and C components of M matrix......80 25: Architecture for calculation of the response in  $\log_2$  scale to reduce word

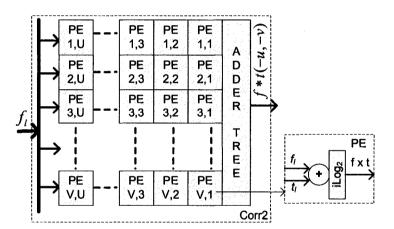

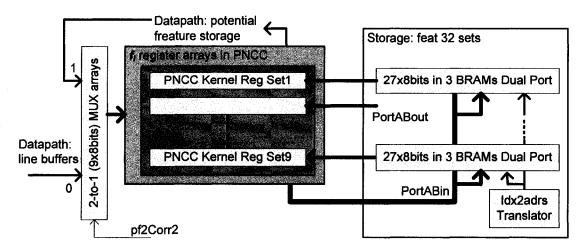

| 32: Storage layout of the NCC architecture9                                                                                                                                                                                                                                                                                                    | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

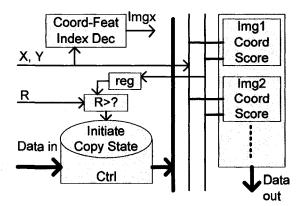

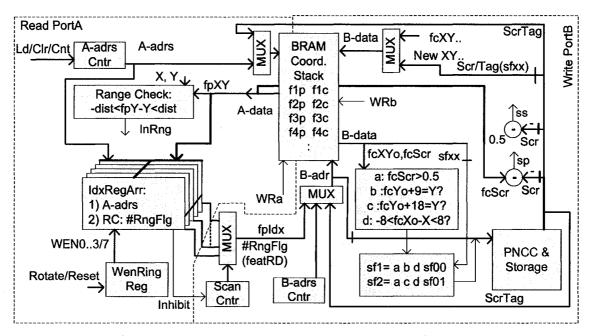

| 33: NCC correspondence management subsystem                                                                                                                                                                                                                                                                                                    | 13 |

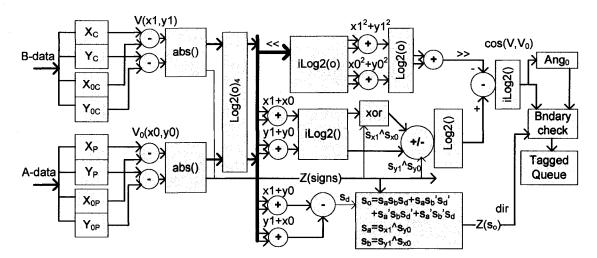

| 34: Architecture of inlier motion evaluation subsystem                                                                                                                                                                                                                                                                                         | 15 |

| 35: Affine transformation to map the display coordinates9                                                                                                                                                                                                                                                                                      | 6  |

| 36: Timing events within the video frame                                                                                                                                                                                                                                                                                                       | 19 |

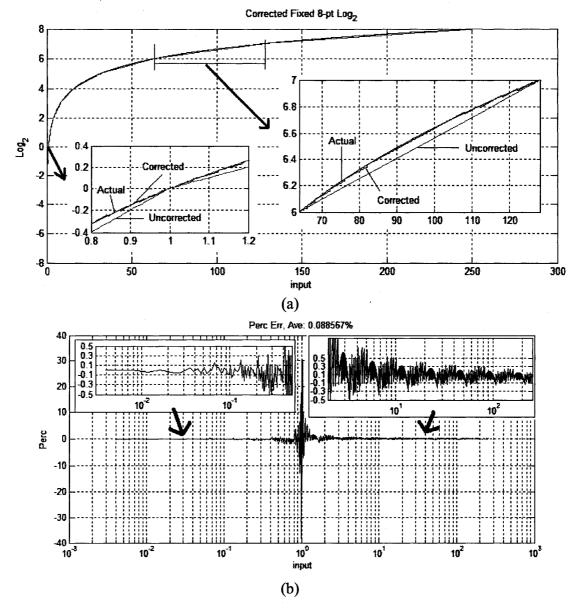

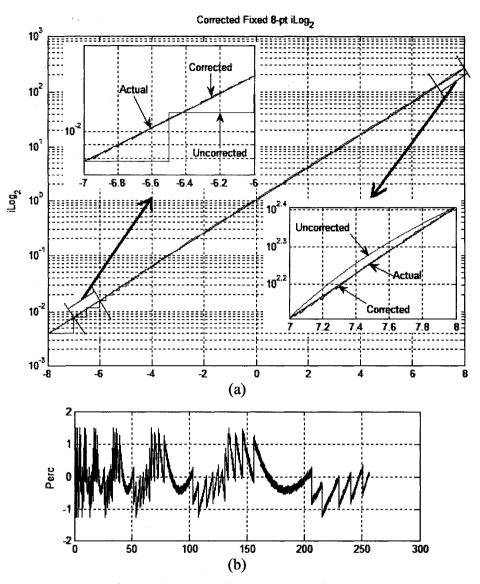

| <ul><li>37: Plot of double precision, uncorrected and corrected log<sub>2</sub> calculations are shown in (a) with the percentage error in (b) for 8-bit fixed point decimals10</li></ul>                                                                                                                                                      | )0 |

| 38: Comparison of difference errors with 5 other designs10                                                                                                                                                                                                                                                                                     | 12 |

| <ul><li>39: Plot of 8-bit fixed point (4-bit integer and 8-bit fraction in 2's complement) iLog<sub>2</sub> (a) and its percentage error (b)10</li></ul>                                                                                                                                                                                       | )4 |

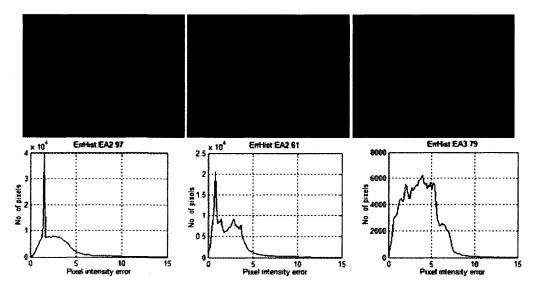

| 40: Images shown on 1 <sup>st</sup> row are the test color images with non-uniform darkness. Results from software and hardware simulations are illustrated on 2 <sup>nd</sup> and 3 <sup>rd</sup> rows, respectively                                                                                                                          | )6 |

| 41: Error characteristics: The errors introduced for utilizing fast conversion factor are illustrated on the 1 <sup>st</sup> row (50x). Error histograms are graphed on the 2 <sup>nd</sup> row with average errors of 2.97, 2.61, and 3.79 pixel intensities10                                                                                | )6 |

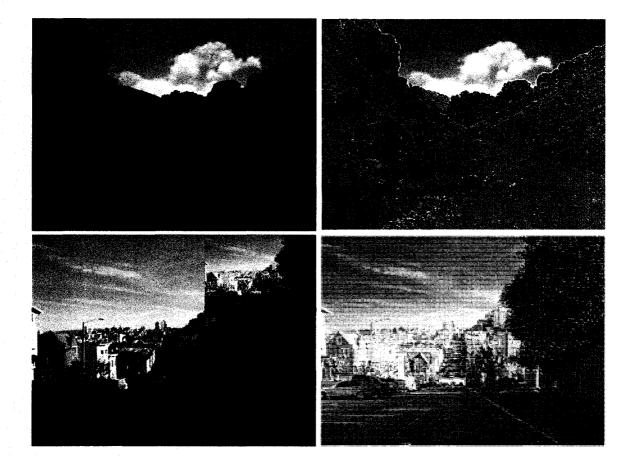

| 42: Examples showing the flexibility of fine-tuning the transfer function for visually more clear view of the scenes                                                                                                                                                                                                                           | 18 |

| 43: The kernel registers of the architecture can also be fine-tuned to enhance the contrast (sharpness) component of the image as illustrated10                                                                                                                                                                                                | 18 |

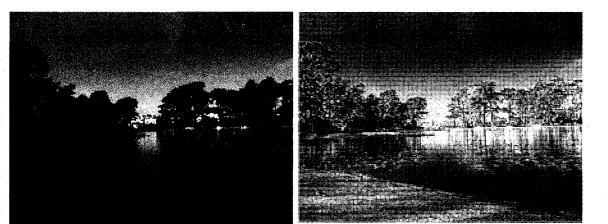

| 44: A short sequence of stabilized frames from the algorithm (1 <sup>st</sup> column) and the hardware simulation (2 <sup>nd</sup> column)11                                                                                                                                                                                                   | 0  |

| 45: Design error in earlier implementation of NCC architecture                                                                                                                                                                                                                                                                                 | 2  |

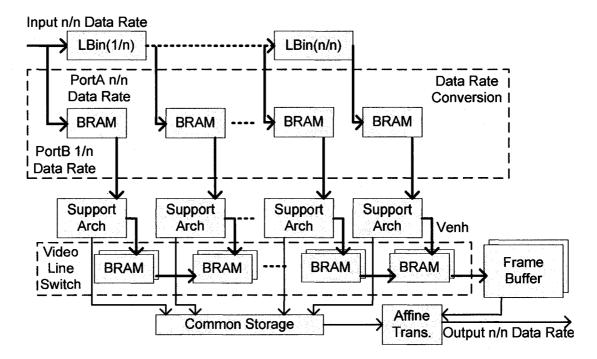

| 46: Scalability of frame size and rate: (a) NVIDIA method to increase the size<br>with constant rate, (b) reduced size or rate with multiplexed architecture to<br>cut back resource, (c) larger size or higher rate with de-multiplexed<br>support to obtain proper data rate from the stream video and sustain same<br>frame performance (c) | 22 |

#### **CHAPTER 1**

#### **INTRODUCTION**

The theme of this dissertation focuses on reducing the complexity of certain calculations in video stabilization by decomposition and the structural representation of the dataset into smaller sub-features. This methodology enables us to overcome the drawback of conventional performance-resource trade-off in hardware designs by concentrating the computation on the most distinct sub-feature and sustaining a one-on-one throughput rate. The main contributions of this dissertation are listed in section 1.3 followed by the organization of this book in section 1.4.

#### **1.1 Motivation of the Research**

Video Stabilization is an essential part of the video processing technology for scenes captured under shaky conditions. From the perspective of an audience, extraction of information from such a video source can be distracting, thus making it very difficult to concentrate and exhausting to track the target of interest from the scenes. In extreme cases, it is impossible to identify the details from such a scene with large variations when the frames are averaged through our eyes' perception. However, the vibrative motion of the camera is not the only problem. Videos captured under non-uniform lighting conditions are mainly contributed from the limitation of physical sensing devices. Due to the limited dynamic range of the sampling circuitry, the brighter region of the image

Format of this dissertation is IEEE Transactions on Computers

saturates the photo site of sensing elements, causing the device to compensate itself and shadow out slightly darker parts of the scene. While there are several image enhancement algorithms available, the method which is capable of simultaneous rendering of the luminance and contrast components of the color images is not currently available for efficient design of the architecture.

The motivation of this dissertation is to find a robust algorithm to immobilize the video by compensating for the background motion of the camera. Another objective is to develop a high performance system architecture in FPGA technology for the stabilization of video sequences captured under non-uniform lighting conditions. In this research, we apply a reflectance-illuminant model for video enhancement to improve the visibility and quality of the scene. With fast color space conversion, the computational complexity is reduced to a minimum, further simplifying the hardware design. The basic video stabilization model is formulated and simplified for implementation. Such a model involves evaluation of reliable features to track, feature measure and tracking, motion estimation, and affine transformation to map the display coordinates of stabilized sequences. Novel architectures for performing these calculations are also proposed in this dissertation. With improved log-domain computation, all multiplications, divisions and exponentiations are replaced by simple arithmetic and logic operations. On a Xilinx's Virtex II 2V8000-5 FPGA platform, the prototype system consumes 59% logic slices, 30% flip-flops, 34% lookup tables, 35% embedded RAMs and two ZBT frame buffers. The system is capable of rendering 180.9 million pixels per second (mpps) and consumes approximately 30.6 watts of power at a 1.5 volt internal operating voltage. With a  $1024 \times 1024$  maximum frame, the throughput is equivalent to 172 frames per second (fps).

#### **1.2 Proposed Theme of the Dissertation**

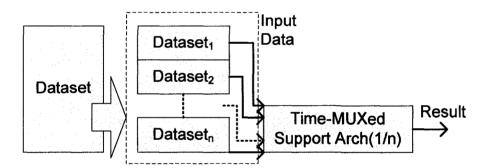

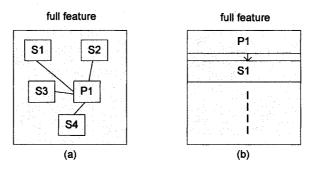

We often face the decision of performance-resource optimization due to hardware constraints and the performance needs of specific applications. The performance parameter usually has an inverse relationship with the amount of assisting hardware necessary to achieve certain calculations within a given time. To minimize the resource, conventional methods usually compute the partial results on a timeslot shared architecture and construct a set of distributed queues to hold the partial results which are accumulatively combined to produce a more complete output. This concept can readily be illustrated in Fig 1a. A dataset is first uniformly divided into *n* subsets, where *n* is the reduction factor of computing elements, 1/n is the throughput parameter. The subsets are fetched into the support architecture at a clock cycle. The partial results are properly saved to the distributed queues to be accumulated in subsequent cycles. It requires *n* clock cycles to complete the evaluation of an entire dataset.

To sustain the peak performance of a system while reducing hardware complexity, we propose to represent the dataset by sub-features in a structured constellation as shown in Fig 1b. The full dataset is first decomposed into a primary sub-feature,  $P_1$ , and a set of secondary sub-features,  $S_{2..n}$ . The criteria of evaluating the sub-features are application dependent; however, the general rule is to extract the most distinctive characteristics for the primary sub-feature and select sub-optimal regions to be secondary sub-features. With the coordinates of the sub-features obtained from the process of feature decomposition, these sub-features form the distance and angle relationships with the primary sub-feature in a structure which identifies the complete dataset. The support architecture for partial evaluation is similar to the time-multiplexed architecture in Fig 1a. Nonetheless, only  $P_1$ is being evaluated at all time with respect to the region of interest. With the successful evaluation of the primary sub-feature, subsequent measure of secondary sub-features is enabled at the proper spatial locality predetermined by the structure representing the dataset. The secondary sub-features,  $S_{2..n}$ , are evaluated only once for every valid measure of  $P_1$ . A successful measure of all sub-features contributes to a correct

(a) Time-multiplexed evaluation of a complete dataset.

(b) Distinctive characteristics oriented partial evaluation with sub-feature representation.

Figure 1: Decomposition and structural representation of the dataset.

evaluation of the dataset. This method allows us to evaluate a larger dataset on a dedicated hardware with limited computing elements and at the same time provides roughly a one-on-one system performance.

### **1.3 Main Contributions**

The main contributions of this dissertation can be summarized as follows:

1. Model of feature representation by constellation. The sub-feature methodology decomposes a feature into sub-features based on the criteria of distinctive characteristics (textural optimality in our case) of the dataset. A region with the most distinctive characteristics is assigned as primary sub-feature along with a set of non-overlapped secondary sub-features having sub-optimal regions. A brute force evaluation of the complete feature is eliminated with the computational power concentrated on the primary sub-feature. For every successful measure of the primary sub-feature, the secondary sub-features are evaluated to confirm the existence of such structure which represents the complete feature. By representing the full feature in primary sub-feature and a set of secondary sub-features, the amount of necessary calculations can be dramatically reduced. For hardware design, it is not necessary to build a huge architecture to evaluate the complete feature; instead, one only needs to implement a support system for the sub-feature dimension. The model also encapsulates the spatial deformation or distortion of the full feature through the angle and distance relationships among the subfeatures within the constellation. With further extension, this idea can be readily applied for adaptive tracking of rigid objects.

- 2. Design of various subsystems for video stabilization, namely, the potential feature selection, feature measure and tracking, and the angle calculation for inlier motion estimation. The single most important component, however, is the feature measure which involves the computation of 2D normalized cross correlation (NCC). The first step to reduce complexity is to perform a partial measure of NCC on primary sub-features. Another important aspect of NCC architecture is its ability to sustain the peak performance without the performance-resource trade-off. With the assistance of sub-feature measures, the representation of the full feature served as confirmation of primary sub-features; the NCC architecture virtually appears to handle much larger feature templates. It is interesting to note that such a design is the direct extension of our previous research based on the generic architecture of 2D convolution.

- 3. Design of low complexity architecture for video enhancement. While we already have several implementations of various algorithms, the architecture presented in this dissertation has the lowest complexity of all previous approaches. The idea of generalized 2D convolution with quadrant symmetry property from master thesis has also proven to be very flexible in deploying the concept to various image enhancement architectures. Virtually all image processing algorithms involve some kind of filtering operations that often has quadrant symmetric kernels.

- 4. Design of improved logarithmic modules. A simple bit-level error correction is introduced to increase the precision of Log<sub>2</sub> and iLog<sub>2</sub> modules with improved pipelining. The hardware complexity for 32-bit numbers is also further reduced while maintaining only 8-bit fixed point for the fractions. The research done from

6

the master thesis, "A multiplier-less architecture for high speed computation of multi-dimensional convolution", has proven log-domain computation to be very useful for reducing the complexity in hardware designs.

- 5. Global motion evaluation with triangular order of search. By calculating the angles between the vectors alone, we can quickly estimate the background motion. It is accomplished by searching, without any redundant calculation, for the most outstanding element within a collection of motions. The outstanding element can be applied to further narrow down the motions of subsequent video frames, hence, forming a star constellation based on the stability of the outstanding element in relation to other nodes within itself.

- 6. Basic model of feature evaluation based on different types of textures. Due to hardware related issues, only a single layer of texture already available from the literature has been selected. The uniqueness of the features proved to be least useful as the required processing bandwidth can become highly non-uniform which is not very suitable for hardware implementation.

- Application of fast color space conversion to speed up the video enhancement on desktop computers to 30 fps with 3.2GHz Intel P4H processor and 1.5GB DDR1 memory.

Future work should not focus on further improving the performance of hardware system since the throughput is already excessively high; however, it should optimize the performance and the resource to meet the specifics based on the nature of the applications. Future development should also extend the great potential of the model into finer grains for extraction and adaptive tracking of moving objects as our model inherently encapsulates the attributes of spatial distortion and motion prediction to reduce complexity. With these parameters to narrow down the processing range, it is possible to achieve a minimum of 20 fps on desktop computers with Intel Core 2 Duo or Quad Core CPUs and 2GB DDR2 memory without dedicated hardware.

### **1.4 Organization of Forthcoming Chapters**

The remainder of this dissertation is organized as the following. A brief survey of image enhancement, feature evaluation and motion estimation is discussed in chapter 2 regarding the fundamental problems involved with the stabilization. Chapter 3 introduces the issues of complexity of certain operations commonly applied in image processing. Chapter 4 addresses the theoretical model formulation and the simplification toward designing hardware efficient high-speed architecture. The design of different subsystem modules is illustrated in-depth in chapter 5. The simulation results and error analysis along with the parameters of performance and resource allocation are given in chapter 6. The conclusion and the comments regarding future development of the video stabilization system are presented in chapter 7.

### **CHAPTER 2**

# ALGORITHMIC BACKGROUND

In this chapter, we briefly describe the fundamental issues involved with the task of stabilizing the video sequence. One of the issues is video enhancement for which one must compensate the visual quality of the scenes captured from cameras with limited dynamic range. The second issue requires the detection of reliable features to establish the correspondence between the video frames. Various approaches for estimation of background motion are addressed for derivation of parameters necessary for stabilization.

#### 2.1 Necessity of Image and Video Enhancement

Physical limitations exist in the sensor arrays of imaging devices, such as CCD and CMOS cameras. Often the videos captured by these devices cannot properly represent scenes that have both very bright and dark regions. The sensor cells are commonly compensated with the amount of saturation from bright regions fading out the details in the darker regions. Image enhancement algorithms [1], [2], [3], [4] provide good rendering to bring out the details hidden due to dynamic range compression of the physical sensing devices. For applications in color images these algorithms may fail to preserve the color relationship among RGB channels which result in distortion of color information after enhancement. Thus, there is still room for improvement. The recent development of a fast converging neural network based learning algorithm called Ratio Rule [5], [6] provides an excellent solution for natural color restoration of the image after gray-level image enhancement. Hardware implementation of such algorithms is absolutely essential to

parallelize the computation and deliver real time throughputs for color images or video processing containing extensive transformations and a large volume of pixels. Implementation of window related operations such as convolution, summation, and matrix dot products which are common in enhancement architectures demands enormous amount of hardware resources [7], [8]. Often a large number of multiplications/divisions is needed [9]. Some designs compromise this issue by effectively adapting the architectures to very specific forms [7], [8], [10] and cannot operate on different sets of properties related to the operation without the aid of dynamic reconfiguration in an FPGA based environment. We proposed the concept of log-domain computation in [11] to solve the problem of multiplication and division in the enhancement system to significantly reduce the hardware requirement while providing a high throughput rate.

Algorithms developed under the reflectance-illuminance category of the image processing models are not unique. The theorization of such a model for visual representation originated in the early 1970's [12] with stochastic image processing in [13] to reduce the salt-and-pepper noise (black and white dots imposed from poor quality sensing device available at the time). In classical approaches, homomorphic processing operates exclusively on the grayscale images. Recently the concept has become popular for adapting the model to color image representation. Although the concepts for a number of exotic approaches are generalized by Kimmel *et al* [14], dedicated architectures for such algorithms are generally unavailable; thus, comparison is limited to existing designs relevant to the subject. One of the few well explored and adapted techniques (in both hardware and software) in this category is Multi-Scale Retinex (MSR) related model

developed by Jobson's research team [2], [3], [15]. By the nature of the algorithmic procedure, MSR is suitable for DSP based implementation discussed in [16] where the fast Fourier transform (FFT) and inverse FFT (IFFT) may be readily plugged in from the DSP library [17], [18]. Further improvement on MSR can be made for better color consistency to minimize the influence from background color. Within the same category, we presented a hardware-efficient architecture in [19] for enhancement of the digital color images with non-uniform darkness using a Ratio learning algorithm [5] [6] for color distortion correction. We also proposed the nonlinear enhancement architecture in [20] based on [21] which results with similar quality on the output images. As far as efficiency is concerned, tweaking of the enhancement processes needs to be further exploited for potential speed up and hardware reduction.

# 2.2 Evaluation of Good Tracking Features

Modeling of artificial neural networks (ANN) to solve real-world problems is inspired by biological neural systems. Such systems are simplified for ANN where the neurons are characterized solely by the biologic machinery but the ability to adapt, learn, and generalize in response to given types of information within the network architectures are governed by certain learning rules. The successors of such models mimic the biological functionality of the systems quite well. Virtually all forms of modification of the synaptic weights between neurons are in some ways variations of Hebbian or Delta rule in ANN whether the networks are feed-forward or recurrent [22]. While feed-forward architectures such as perceptron and adaline [23] [24] [25] have strict limitation where no feed-back or back-propagation exists for error correction, recurrent networks significantly increase the dynamics of the network. One of those earliest recurrent networks was introduced by Anderson and Kohonen in [26] [27] and generalized by Hopfield in 1982 [28] with primary applications for associative memory which remembers the patterns and pattern recognition. Examples of applications include optimization in power systems [29]. For classification, the unsupervised Fuzzy Adaptive Resonance Theory, Fuzzy-ART, neural network, introduced in 1976 by biological phenomena [30] can be useful. Fuzzy-ART is capable of clustering documents with the ability to mine data and discover knowledge dynamically by a wide variety of techniques [31]. It can also be applied for rapid stable learning to categorize and recognize the patterns [32]. The supervised Fuzzy-ART called Fuzzy ARTMAP can learn incrementally for category recognition with new minima learning rule [33].

Inspired by the concepts of adaptive resonance theory based neural networks and Hopfield recurrent network, a new neural architecture is desirable to fuse different characteristics [34] for automatic extraction and selection of a set of unique features from a video stream. The same network should also be able to track the features to maintain the correspondence between video frames and minimize iterative error measures. Such features would be useful for estimation of motion parameters. While the ANN has the capacity to support pattern related classes of applications, the iterative nature of the process itself imposes the bottleneck of non-constant bandwidth access of the storage components in dedicated high performance system architectures. Nonetheless, the specific textures can be considered reliable for tracking. In general, good features are characterized by the distinctiveness of different types of textures.

Scale invariant feature templates (SIFT) can be very helpful for object detection [34][74]. To identify the correspondent coordinates of a feature in another picture, the image must be re-sampled into different resolutions to construct a pyramid of images. Within each resolution, feature selection is performed based on certain criteria. The most consistent features of the pyramid are extracted as the scale invariant templates for subsequent processing. In conjunction with rotation invariant features through affine normalization, the multi-resolution feature extraction has proven to be vital for the construction of image descriptors and the accumulation of its database for autonomous object detection [75]. Our main focus, however, is to identify reliable features with respect to a current video frame under the legitimate assumption that variation of scale and rotation are gradual within a video sequence. Hence, it is not necessary to represent the features according to image descriptors with scale and histogram orientation of certain key points.

#### **2.3 Evaluation of Motion Parameters**

Evaluation of the features alone may seem insignificant; however, such a step is crucial when combined with a variety of motion analysis and estimation. Motion estimation (ME) is a process of evaluating the relationship between the frames such that the contents of the frames are approximately stationary with respect to the reference frame through transformation of motion parameters. Global motion estimation (GME) is an instance of ME which involves the monitoring of background or dominant motion. ME has a very broad applications in video processing technology. In video compression, the ability to accurately estimate the motions, not necessarily global motion alone, determines the compression ratio, resulting in smaller video files [35]. In segmentation, motion information helps in distinguishing between moving objects from the background [36]. In registration and mosaicing applications, motion vectors contribute to the key components in identifying orientation for stitching the frames into a more complete scene [37].

ME search algorithms can be divided into three categories based on their complexity. The full search algorithms (FSA) contribute to the most optimal match yet impractical with overwhelmed complexity O(n), where *n* is the search range. The cost for block search is O(n/m), where *m* is the block range, and may be as low as  $O(\log(n))$  with logarithmic search [38]. In video compression the blocks are usually divided into macroblocks to further reduce the search range with a trade off of increasing the distortion and the assumption of block-wise uniform motion [39]. The hybrid search serves to balance the complexity and accuracy [40].

The class of gradient/differential based ME algorithms is commonly modeled by (2.1), where  $I_t(\mathbf{x})$  is the current frame with coordinate vector  $\mathbf{x}=[\mathbf{x},\mathbf{y}]^T$ ,  $I_{t-1}$  is previous frame or reference, G function is the affine transformation by motion vector **M**, and err(**x**) is the error. The coefficients  $a_i$  and  $b_i$  are the rotation and scale of affine parameters while  $d_x$  and  $d_y$  are the displacement or translational motion between the frames. Two well

known cost functions for error measure defined in (2.2) are mean absolute error (MAE) and mean square error (MSE) [41] for which **M** has the solution of least squares regression.

The error minimization has a first order Taylor expansion of (2.3). The resolution pyramid is often constructed to iteratively estimate the motion parameter for convergence from course to fine resolutions. Such differential techniques assume that the intensity of the images is conserved reducing its reliability to subtle change by noise and illumination. Higher orders of Taylor expansion further assumes that the subsequent gradients be conserved which implies the ill-posed problems to rotation, scaling as well as sources of noise [42]. The approach essentially becomes less stable as the constraint is overly specified. A more troublesome part of the gradient descending ME is that the search algorithm fails when trapped into local minima [43]. Lucas introduced weighting to error measure defined in (2.4) to give more influence to centre pixel under the window [44]. This concept can be extended to increase the reliability of selected regions for motion measure. Such confidence factor can be modeled with Bayesian statistics through observation over time to enhance regions with low noise and small aperture problems or suppressing otherwise [45]. Multi-frame buffering and frame sub-sampling are usually required for ME with differential techniques. They translate to greater memory usage with added complexity to buffer flow in hardware realization. The potential of measuring global motion can be explored through consistency of motions to avoid iterative error measure and minimize frame buffering. Once the motion parameters are sustained and compensated by intended motion, standard affine transforms may be performed to

minimize shakiness of the scene, hence, stabilizing the video. While the motion parameters may be estimated through measure of residues with respect to the reference frame, we should examine the basic properties of calculating the coherence of different motions.

$$I_{t}(\mathbf{x}) = I_{t-1} \left( G(\mathbf{x}, \mathbf{M}) \right) + err(\mathbf{x})$$

$$G(\mathbf{x}, \mathbf{M}) = \begin{bmatrix} a_{1} & a_{2} \\ b_{1} & b_{2} \end{bmatrix} \begin{bmatrix} x \\ y \end{bmatrix} + \begin{bmatrix} d_{x} \\ d_{y} \end{bmatrix}, or$$

$$\begin{bmatrix} x & y & 1 & 0 & 0 & 0 \\ 0 & 0 & x & y & 1 \end{bmatrix} \times \begin{bmatrix} a_{1} & a_{2} & d_{x} & b_{1} & b_{2} & d_{y} \end{bmatrix}^{T}$$

$$= \mathbf{C}(\mathbf{x}) \times \mathbf{M}$$

$$(2.1)$$

$$err(\mathbf{x}) = \arg\min_{\mathbf{M}} \left\{ E\left( \left| I_{t}(\mathbf{x}) - I_{t-1}\left(G(\mathbf{x}, \mathbf{M})\right) \right| \right) \right\}$$

$$err(\mathbf{x}) = \arg\min_{\mathbf{M}} \left\{ E\left( I_{t}(\mathbf{x}) - I_{t-1}\left(G(\mathbf{x}, \mathbf{M})\right) \right)^{2} \right\}$$

(2.2)

$$I_{t}(\mathbf{x}) = I_{t-1} + \sum_{i} \frac{\partial I_{t-1}}{\partial M_{i}} M_{i}$$

(2.3)

$$\sum_{\mathbf{x}\in\Omega} W(\mathbf{x})^{2} \left[ \nabla I(\mathbf{x},t) \cdot \mathbf{M} + I_{t}(\mathbf{x},t) \right]^{2}$$

(2.4)

# 2.4 Summary

In this chapter, we discussed the fundamental limitation of physical sensing devices for which the cameras had narrow dynamic range. Saturation in part of the image tended to shadow out the details in other regions of the scene. Different image enhancement algorithms often required several separate operations for contrast improvement, luminance enhancement, color correction and color restoration. We found it necessary to apply a simpler model and at the same time eliminate color correction and

restoration. Such a model should minimize the number of multiplications to reduce complexity while produced reasonable image quality to improve the visibility of the scene. Moreover, we intended to design an enhancement subsystem capable of finetuning certain parameters to meet the need. In computer vision, most feature evaluation concepts available in the literature often model the scale, rotation and orientation as part of the efforts to recognize certain invariant features. It required a significant degree of computation frequently too difficult to implement in hardware. The processing nature of certain calculations would be highly non-linear, therefore, extremely difficult to implement. Our interest would be to only evaluate reliable features with respect to current conditions within the scene. It is desirable to derive a simple model for feature evaluation which has low complexity with minimum storage space. Hence the evaluation technique has to support feature extraction on the fly. A class of gradient based motion evaluation techniques was also evaluated in this chapter. These approaches are iterative nature in the process of obtaining motion parameters. The assumption of conservative image intensity further poses the ill nature in the presence of noise. Similar to the feature evaluation these techniques often require the storage of entire video frames for which certain prediction must be iteratively measured by means of residual errors. In theory, if the feature evaluation works well, it is not mandatory to extract motion parameters from the entire frames. In the forthcoming chapters, a simpler mean of video enhancement, feature evaluation and motion estimation suitable for hardware realization are analyzed for the stabilization of video sequence.

#### CHAPTER 3

#### **COMPUTATIONAL COMPLEXITY REDUCTION**

In advance to in-depth discussion of the theory behind the algorithm, let us begin by a briefing on the fundamental problems of the complexity itself regarding most commonly used operators such as division, multiplication, exponentiation and some form of summation equivalent to window/kernel based operations such as matrix multiplication.

#### **3.1 Redundancy of the Operator**

As introduced in chapter 2, window based operations are very common in video processing technology such as generalized 2D convolution. Often, coefficients associated with these kernels are non-arbitrary and exhibit interesting properties. It is a waste of the computational power and resource allocation from hardware designers' perspective to not take advantage of certain symmetries within the kernels. Such symmetries are very common in the design of digital filters. In particular, we utilize the quadrant symmetry (QS) of the kernels to support convolution operations (digital filtering). This preprocessing ideally saves close to 75% of the multiplications in addition to the replacement of the hardware multipliers discussed in [46]. Such optimization results with the architecture that is neither too specific nor generic while focusing the essential computation to a single quadrant. It maintains the flexibility of redefining the filter characteristics at run-time (soft upgrade) by external systems. Examples of the filters

qualified for QS property include both separable [47] and non-separable kernels. QS also encapsulates circularly symmetric kernels such as Gaussians and Laplacian of Gaussians used for smoothing and edge detection, respectively. In summary, one can minimize the computational power by simply exploiting the redundant properties of certain operators. The reliance on redundancy alone, however, is insufficient for hardware implementation of the dedicated architectures which demand relatively complex calculations.

#### **3.2** Concept of Logarithmic Domain Computation

This section describes the basics of logarithmic approximation. A common technique which relies on piecewise straight lines for error correction to various precisions is also illustrated in the subsections. We propose bit-level curve fitting as a mean to generate the correcting coefficients and achieve similar precision compared to other approaches.

#### **3.2.1** Simplicity of Approximation and Its Benefits

Multiplications and divisions become additions and subtractions with logarithmic transformations logically defined by (3.1) which require significantly less computational power. A number to the power *n* becomes a matter of arithmetic shift operation achievable within single clock cycle for *n* equals to power of two, or multiplication operation for any finite *n* in general. Eq. (3.1) states that the log<sub>2</sub> scale of *V* can be calculated by concatenating the index  $I_V$  of leading 1's in *V* with the fractions (remaining bits after  $I_V$ <sup>th</sup> bit). The reversed process holds true as well, except the leading 1's and fractions,  $L_f$ , are shifted to the left by  $L_i$  (integer of *L*) bits as shown in (3.1). This definition is generalized

to integer values as well as fraction numbers. For example,  $\log_2(0000.0110)$  binary becomes -1.5 or (-2 + 0.5) in decimal since the position of  $I_{\nu}$  is -2 (two places after decimal point) with fraction 0.10 in binary. The correct value should be -1.415 which results with 6% error from the approximation for worst case scenario. Application of this concept eliminates most costly components just described for hardware designs. Thus, it is crucial to implement efficient logarithmic estimation modules in such a way that is very compact in its design, reduces large amount of hardware resource, and provides very high throughput rate [11] [19]. Designs based on the concept presented in [48] which employees unrolled pipeline architectures such as [20], [49] and [50] may not be efficient for replacement of multiplications and divisions in window related architectures for FPGA based implementation. Particularly in filters, such architectures usually require a large number of multiplications and the amount of hardware resource allocated for the unrolled pipeline stages usually can come close to the cost of the multipliers on FPGA technology. Our implementation of the estimation modules packs the resolution-dependent unrolled pipeline style design into a few stages regardless of its resolution and at the same time optimizes the component count, power and speed. It is about 10 times reduction in the resource and 170% performance boost in FPGA environment. We generalized the modules to support both integer and fraction numbers without introducing hardware complexity. These modules are also insensitive to the bit-resolution that exists in hardware multipliers in which the performance is inversely proportional to the number of bits in the multipliers. We have demonstrated the use of log domain computations in [19], [46] for image processing applications with a figure of 60% hardware reduction in addition to the

applicable QS based architecture. The error correction to enhance such approximation is discussed in next section.

$$\log_2(V) \cong \{I_V\} + \{(V - I_V) \gg I_V\} \Leftrightarrow \log_2^{-1}(L) \cong \{1 \ll L_i\} + \{L_f \ll L_i\}$$

(3.1)

#### 3.2.2 Improvement of Precision with Piecewise Straight Lines

Mitchell's logarithmic converter proposed in [48] was derived based on binary representation of a number N in

$$N = \sum_{i=j}^{k} b_i 2^i \tag{3.2}$$

as a summation of binary coefficients,  $b_i$  with respect to the placement,  $2^i$ . The k is an index (aka characteristic of log<sub>2</sub>N) for which the most significant bit (MSB) of N in binary equals to 1's. Given  $b_k=1$ , the term  $2^k$  can be factored out to simplify (3.2) by

$$N = 2^{k} (1+f)$$

(3.3)

where f is the fraction of the remaining terms of (3.2). The log<sub>2</sub> scale of (3.3) is defined by

$$\log_2 N = k + \log_2(1+f)$$

(3.4)

and can be approximated by

$$\log_2 N' = k + f', \tag{3.5}$$

with the slop of line equal to one between consecutive points of exactly power of two. A different perspective to the approximation using power series can eventually reach the same conclusion for fix-point N in addition to strictly integer values [46]. The error is measured by the difference between exact  $\log_2 N$  and approximated  $\log_2 N'$ :

$$Err(N) = \log_2 N - \log_2 N'.$$

(3.6)

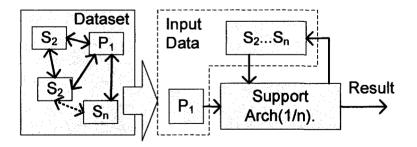

Eq (3.5) only requires arithmetic addition and may be implemented completely free of any multiplication. Mitchell demonstrated the design with counter and shift register in serial form which requires minimum hardware resources at the expense of the largest number of clock cycles necessary. The result of Mitchell's approximation is shown in Fig 2a along with the difference error in Fig 2b, which is quite symmetrical with x-axis in log<sub>2</sub> scale. The periodic nature of the difference error makes it possible for bit-level error correction as an alternative to piece-wise linear approaches [49][50][51][52][53].

Figure 2: Mitchell's log<sub>2</sub> approximation (a) and the difference error (b).

In general, piecewise linearly corrected logarithmic converters maintain the following form:

$$\log_2 N' = k + f + \left(f \times \sum c_R + \sum d_R\right), \qquad (3.7)$$

where  $c_R$  is the single-bit slop in power of two to eliminate real multiplications and minimize error, and R denotes the divided regions for such linearization. The number of binary coefficients in  $\sum c_R$  is determined to be fewest possible for realization of low complexity circuitry. In 1999, SanGregory proposed the two-region piecewise linear correcting factor [52]. The single-bit coefficient was selected by minimizing root-mean-square error. His correction algorithm can be summarized as follows:

$$\log_2 N' = k + f + \begin{cases} 2^{-2} f_{4MSB}, & \text{for } 0 \le f < 1/2 \\ 2^{-2} \overline{f}_{4MSB}, & \text{for } 1/2 \le f < 2/2 \end{cases},$$

(3.8)

where  $\overline{f} \approx 1$ -f, or the descending part of the error curve in Fig 2b. The difference error with  $0 \le f < 1$  is approximately symmetrical around the midway in linear scale. SanGregory chose to only incorporate 4 MSBs of the fraction to generate a three bits correcting factor to improve accuracy yet maintain very low hardware overhead. Dated back to 1965, Combet also improved Mitchell's algorithm with a four region error correction in serial architecture with increased circuit complexity [51]. His algorithm was based on trial and error in selecting the straight lines and can be defined as:

$$\log_2 N' = k + f + \begin{cases} (2^{-2} + 2^{-4})f, & \text{for } 0 \le f < 1/4 \\ 2^{-4} + 2^{-6}, & \text{for } 1/4 \le f < 2/4 \\ 2^{-3} \overline{f} + 2^{-6} + 2^{-7}, & \text{for } 2/4 \le f < 3/4 \\ 2^{-2} \overline{f}, & \text{for } 3/4 \le f < 4/4 \end{cases}$$

(3.9)

Hall also adapted Combet's idea with more coefficients for better accuracy yet seemed to defeat the desire for solutions with a simple hardware requirement [54]. In 2003, Abed refined the work done in [52] and extended the piecewise straight line approach to offer two, three, and six region error correction algorithms for 32-bit integer numbers. His formulation for the implementation presented in [53] can be summarized as follows with two, three, and six-bit correcting factors, respectively:

$$\log_2 N' = k + f + \begin{cases} 2^{-2} f_{3MSB}, & \text{for } 0 \le f < 1/2 \\ 2^{-2} \overline{f}_{3MSB}, & \text{for } 1/2 \le f < 2/2 \end{cases},$$

(3.10a)

$$\log_2 N' = k + f + \begin{cases} 2^{-2} f_{4MSB}, & \text{for } 0 \le f < 1/4 \\ 2^{-4} + 2^{-6}, & \text{for } 1/4 \le f < 3/4 \\ 2^{-2} \overline{f}_{4MSB}, & \text{for } 3/4 \le f < 4/4 \end{cases},$$

(3.10b)

$$\log_2 N' = k + f + \begin{cases} 2^{-2} f_{6MSB}, & for \ 0 \le f < 1/16 \\ 2^{-2} f_{6MSB} + 2^{-6}, & for \ 1/16 \le f < 4/16 \\ 2^{-4} + 2^{-7} + 2^{-8}, & for \ 4/16 \le f < 6/16 \\ 2^{-4} + 2^{-6} + 2^{-7}, & for \ 6/16 \le f < 10/16 \\ 2^{-4} + 2^{-7}, & for \ 10/16 \le f < 12/16 \\ 2^{-2} \overline{f}_{6MSB}, & for \ 12/16 \le f < 16/16 \\ \end{cases}$$

(3.10c)

In general, increasing the number of regions results with smaller approximation error defined in (3.6) at the cost of additional logic gates and adder cells. In the case of six-region method, two cascaded adder arrays are needed which can reduce the overall performance of the logarithmic converters. We now present the idea of bit-level curve fitting to generate a three-bit correcting factor. Furthermore, we apply it beyond integer values to include fixed-point representation, given consideration of the precision.

# 3.2.3 Bit-level Curve Fitting

The process of calculating inverse- $\log_2$  is to undo the  $\log_2$  conversion which has the following relationship:

$$\log_2(N) \cong \{k_N\} + \{(N-2^{k_N}) \gg k_N\} \Leftrightarrow \log_2^{-1}(L) \cong \{(1+L_{\text{frac}}) \ll L_{\text{int}}\},$$

(3.11)

where  $\gg$  and  $\ll$  denote the opposite data bus shifting operation. Note that neither (3.5) nor (3.11) restricted us from defining negative index, k < 0; however, only the integer portion (assuming non-negative k) has been exploited in the literature to our best knowledge. For a fixed-point decimal of 8/8 (8-bit integer and 8-bit fraction), the same

rule holds true. We need to find a mechanism to express the k in two's complement. By using the standard priority encoder, we found that the single bit-inversion of the MSB at the output of the encoder does the trick. A single bit of inverter logic generalizes the architecture to accept both integer and decimal values. By including fraction values, it may seem to complicate the problem that shifting operation of (3.11) can go either way depending on the sign of k; the logic shift remains unidirectional in the implementation. To avoid real computation and minimize delay in realizing high speed parallel architectures, one is often left with very few choices. Besides the linear methods of (3.8) to (3.10), curve fitting at the logic level can also achieve a high degree of precision without introducing complex circuits.

Rather than applying piecewise straight lines, we examined the dataset of the difference error shown in Fig 2b to determine a close fit for generating such correcting factor. At the same time, the correction should not be dependent on all fraction bits to minimize circuit complexity. Examples of binary logarithmic conversion are shown in Table I for 5-bit integers with index value k = 4. On the rightmost column is the error pattern without the correcting factor. Given a finite set of data points and the coherent near-symmetric error bits, one can utilize a large ROM table to correct the error to its best precision. Although not entirely impractical, such an approach does not work well in its scalability as the size of ROM storage exponentiates with the increasing resolution of input integers. It is therefore wise to focus solely on the bits which contribute to the largest magnitudes of error. Based on the simulation analysis at higher precision with consideration of rounding, it was determined that the last five bits of fraction coefficients

can provide sufficient improvement for 8-bit fixed-point representation. Furthermore, optimization on highlighted bits of the error coefficients, EC, (on last column of Table I) shows best trading of higher precision with a reasonably small set of logic gates. Unlike piecewise straight line methods discussed in previous section, bit-level curve fitting needs to be optimized at a much higher resolution for more accurate representation by logic gates.

| Input_bin | Log2_dec | Log2_bin     | Log2appx_bin                 | Log2 - appx         |

|-----------|----------|--------------|------------------------------|---------------------|

| 10000:    | 4        | 100.00000000 | 100. <u>00000</u> 000        | 0.000 <u>000</u> 00 |

| 10001:    | 4.0875   | 100.00010110 | 100. <u>00010</u> 000        | 0.000 <u>001</u> 10 |

| 10010:    | 4.1699   | 100.00101011 | 100. <u><b>00100</b></u> 000 | 0.000 <u>010</u> 11 |

| 10011:    | 4.2479   | 100.00111111 | 100. <u>00110</u> 000        | 0.000 <u>011</u> 11 |

| 10100:    | 4.3219   | 100.01010010 | 100. <b>01000</b> 000        | 0.000 <u>100</u> 10 |

| 10101:    | 4.3923   | 100.01100100 | 100. <u><b>01010</b></u> 000 | 0.000 <u>101</u> 00 |

| 10110:    | 4.4594   | 100.01110101 | 100. <b>01100</b> 000        | 0.000 <u>101</u> 01 |

| 10111:    | 4.5236   | 100.10000110 | 100. <u>01110</u> 000        | 0.000 <u>101</u> 10 |

| 11000:    | 4.585    | 100.10010101 | 100. <u>10000</u> 000        | 0.000 <u>101</u> 01 |

| 11001:    | 4.6439   | 100.10100100 | 100. <u>10010</u> 000        | 0.000 <u>101</u> 00 |

| 11010:    | 4.7004   | 100,10110011 | 100. <u>10100</u> 000        | 0.000 <u>100</u> 11 |

| 11011:    | 4.7549   | 100.11000001 | 100. <u>10110</u> 000        | 0.00010001          |

| 11100:    | 4.8074   | 100.11001110 | 100. <b>11000</b> 000        | 0.000 <u>011</u> 10 |

| 11101:    | 4.858    | 100.11011011 | 100. <u><b>11010</b></u> 000 | 0.000 <u>010</u> 11 |

| 11110:    | 4.9069   | 100.11101000 | 100. <u>11100</u> 000        | 0.000 <u>010</u> 00 |

| 11111:    | 4.9542   | 100.11110100 | 100. <b>11110</b> 000        | 0.000 <u>001</u> 00 |

Table 1: Example of  $\log_2$  converter with 5-bit integers and the index k = 4.

The binary logic fitting analysis of precision-circuit trading pinpoints to the generation of EC<sub>4</sub> to EC<sub>6</sub> depending on the fraction bits  $f_{-1}$  to  $f_{-5}$  and the potential rounding of EC itself. Based on the results, it was concluded that the following simple logic equations reduce the average magnitude of error to approximately one tenth of Mitchell's estimation:

$$EC_{-4}(f) = (\overline{f}_{-1} \vee \overline{f}_{-2}) \wedge (f_{-1} \vee f_{-2} \vee f_{-4}) \wedge (f_{-1} \vee f_{-2} \vee f_{-3})$$

$$EC_{-5}(f) = (\overline{f}_{-3} \vee \overline{f}_{-4}) \wedge (\overline{f}_{-1} \vee f_{-2}) \wedge (\overline{f}_{-2} \vee f_{-1}) \wedge (\overline{f}_{-1} \vee \overline{f}_{-3} \vee \overline{f}_{-5})$$

$$\wedge (f_{-2} \vee f_{-3} \vee f_{-4})$$

$$EC_{-6}(f) = (f_{-1} \vee f_{-2} \vee \overline{f}_{-4}) \wedge (f_{-2} \vee \overline{f}_{-3} \vee \overline{f}_{-4}) \wedge (\overline{f}_{-1} \vee \overline{f}_{-2} \vee \overline{f}_{-4} \vee \overline{f}_{-5})$$

$$\wedge (f_{-1} \vee f_{-3} \vee f_{-4} \vee f_{-5}) \wedge (\overline{f}_{-1} \vee \overline{f}_{-2} \vee \overline{f}_{-3} \vee f_{-4} \vee f_{-5})$$

$$(3.12)$$

The range of error is expected to be  $^{-2.5f_{-8}} < Err < 3.5f_{-8}$  for 8-bit integers comparing to double precision  $\log_2$  values. Since the meaningful precision is limited to 8-bit fixed-point for the fraction, it is also subjected to additional bit of error from rounding for N with greater bit resolution. The analysis also shows that the precision-circuit optimized logic equations reduced the range of approximation error to [-0.0096, 0.0128] with an average error 11.8 times smaller than Mitchell's for 8-bit integers.

Given eight-bit fixed point fraction,  $f_{-1}$  to  $f_{-8}$ , it is obvious that appending any fraction beyond an eighth bit contributes very little to improve the precision with dominant source of error in higher significant bits. Hence, the log<sub>2</sub> converter can be simplified further to reduce hardware components. Instead of the full one-to-one mapping from input to the output, one only needs to construct the data paths relevant to eight output nodes, whether it be 8, 16 or 32-bit resolution. The same concept applies to inverse-log<sub>2</sub> converter. In summary, we replace the portion of piecewise lines with three-bit coefficients to improve the precision with eight bits fraction while in logarithmic scale:

$$\log_2 N' = k^* + f_{_{8MSB}} + EC \tag{3.13a}$$

$$\log_2^{-1} L' = 2^{k^*} \left( 1 + f_{8MSB} - EC' \right), \tag{3.13b}$$

where k\* is specific to the input of either integer or fixed-point decimal(2's complemented k). In next chapter, we discuss the theoretical model for video stabilization and illustrate how redundancy and log-domain computation help reduce complexity of the design.

# **CHAPTER 4**

# **THEORETICAL MODEL**

Improvement of visibility, evaluation of reliable features and estimation of motion parameters are inseparable integral of the effort to formulate the model for stabilization of video sequence captured under non-uniform lighting conditions. The theory underneath these three subjects are discussed to the fullest extend in this chapter. At the end of each topic, the relevant part of the model should be simplified to the point that is reasonably achievable for realization of such hardware architecture.

# 4.1 Low Complexity Video Enhancement