Electronic Theses and Dissertations, 2004-2019

2014

## Shop Scheduling In The Presence Of Batching, Sequencedependent Setups And Incompatible Job Families Minimizing Earliness And Tardiness Penalties

Patricia Buchanan University of Central Florida

Part of the Industrial Engineering Commons

Find similar works at: https://stars.library.ucf.edu/etd

University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Buchanan, Patricia, "Shop Scheduling In The Presence Of Batching, Sequence-dependent Setups And Incompatible Job Families Minimizing Earliness And Tardiness Penalties" (2014). *Electronic Theses and Dissertations*, 2004-2019. 3018.

https://stars.library.ucf.edu/etd/3018

# SHOP SCHEDULING IN THE PRESENCE OF BATCHING, SEQUENCE-DEPENDENT SETUPS AND INCOMPATIBLE JOB FAMILIES MINIMIZING EARLINESS AND TARDINESS PENALTIES

by

#### PATRICIA C. BUCHANAN

B.S. Industrial Engineering, University of Florida, 2003 M.S. Industrial Engineering, University of Florida, 2006

A dissertation submitted in partial fulfillment of the requirements

for the degree of Doctor of Philosophy

in the Department of Industrial Engineering and Management Systems

in the College of Engineering and Computer Science

at the University of Central Florida

Orlando, Florida

Spring Term 2014

Major Professor: Christopher D. Geiger

#### **ABSTRACT**

The motivation of this research investigation stems from a particular job shop production environment at a large international communications and information technology company in which electro-mechanical assemblies (EMAs) are produced. The production environment of the EMAs includes the continuous arrivals of the EMAs (generally called jobs), with distinct due dates, degrees of importance and routing sequences through the production workstations, to the job shop. Jobs are processed in batches at the workstations, and there are incompatible families of jobs, where jobs from different product families cannot be processed together in the same batch. In addition, there are sequence-dependent setups between batches at the workstations. Most importantly, it is imperative that all product deliveries arrive on time to their customers (internal and external) within their respective delivery time windows. Delivery is allowed outside a time window, but at the expense of a penalty. Completing a job and delivering the job before the start of its respective time window results in a penalty, i.e., inventory holding cost. Delivering a job after its respective time window also results in a penalty, i.e., delay cost or emergency shipping cost. This presents a unique scheduling problem where an earlinesstardiness composite objective is considered.

This research approaches this scheduling problem by decomposing this complex job shop scheduling environment into bottleneck and non-bottleneck resources, with the primary focus on effectively scheduling the bottleneck resource. Specifically, the problem of scheduling jobs with unique due dates on a single workstation under the conditions of batching, sequence-dependent

setups, incompatible job families in order to minimize weighted earliness and tardiness is formulated as an integer linear program. This scheduling problem, even in its simplest form, is NP-Hard, where no polynomial-time algorithm exists to solve this problem to optimality, especially as the number of jobs increases. As a result, the computational time to arrive at optimal solutions is not of practical use in industrial settings, where production scheduling decisions need to be made quickly. Therefore, this research explores and proposes new heuristic algorithms to solve this unique scheduling problem. The heuristics use order review and release strategies in combination with priority dispatching rules, which is a popular and more commonly-used class of scheduling algorithms in real-world industrial settings. A computational study is conducted to assess the quality of the solutions generated by the proposed heuristics. The computational results show that, in general, the proposed heuristics produce solutions that are competitive to the optimal solutions, yet in a fraction of the time. The results also show that the proposed heuristics are superior in quality to a set of benchmark algorithms within this same class of heuristics.

To my loving husband

#### ACKNOWLEDGMENTS

I would first like to thank my advisor, Dr. Christopher D. Geiger, for his guidance and support during the development of my dissertation. He is a great teacher, mentor, and friend. His knowledge, patience, and dedication to guiding students helped to make this possible.

I would also like to thank Dr. Dima Nazzal who helped me develop my idea and the beginning stages of my research and phases. It was a pleasure working with her. I would also like to thank Dr. Mansooreh Mollaghasemi, Dr. Jennifer Pazour and Dr. Cheryl Xu for their insights, advice, and for serving on my doctoral dissertation committee.

I would also like to thank my former boss Phillip Burroughs, who constantly supported my continued education and was instrumental in helping me balance my work/life schedule. His constant encouragement and advice was one of the drivers that helped me succeed.

I would like to express my gratitude to all my friends and family for all their constant and loving support. They offered words of encouragement, guidance, a shoulder to lean on, babysitting, and reassurance in my ability to successfully finish this journey.

I especially thank my three children. Their smiles, hugs, and love helped me through my rough times. They were truly patient and understanding when mom had to study. They were my constant reminder why I was working so hard.

Most importantly, I would like to say thank you to my best friend and husband. He was incredibly supportive, encouraging, and was my sounding board when I needed to talk about ideas. This journey was as much his as it was mine.

#### TABLE OF CONTENTS

| LIST OF FIGURES                                                                  | x    |

|----------------------------------------------------------------------------------|------|

| LIST OF TABLES                                                                   | xiii |

| CHAPTER 1 : INTRODUCTION                                                         | 1    |

| 1.1. Background of the Industrial Setting Motivating This Research Investigation | 1    |

| 1.1.1 The Importance of On-Time Delivery                                         | 2    |

| 1.1.2 The Coating Room                                                           | 3    |

| 1.1.3 Process Characteristics within the Coating Room                            | 5    |

| 1.2 Description of the General Problem                                           | 7    |

| 1.2.1 Job and Resource Characteristics                                           | 8    |

| 1.2.2 Processing Characteristics                                                 | 9    |

| 1.2.3 The Performance Objective                                                  | 12   |

| 1.3 Decomposition of the Problem – The Bottleneck                                | 13   |

| 1.4 Objectives of This Research Investigation                                    | 14   |

| 1.5 Expected Contribution of This Research Investigation                         | 15   |

| 1.6 Organization of This Document                                                | 15   |

| CHAPTER 2 REVIEW OF THE EXISTING LITERATURE                                      | 17   |

| 2.1 Introduction                                                                 | 17   |

| 2.2 Job Shop Scheduling                                                          | 17   |

| 2.2.1 Heuristic Approaches to the Job Shop Scheduling Problem                    | 18   |

| 2.3 Batching and Sequence-Dependent Setups                                       | 19   |

| 2.3.1 Exact Approaches                                                           | 20   |

| 2.3.2 Heuristic Approaches                                                                                                                            | 21 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.3.3 Sequence-Dependent Setups                                                                                                                       | 23 |

| 2.4 Unplanned Disruptions                                                                                                                             | 24 |

| 2.5 Minimizing the Earliness and Tardiness Performance Objectives                                                                                     | 26 |

| 2.5.1 Approaches for Minimizing Tardiness                                                                                                             | 26 |

| 2.5.2 Approaches for Minimizing Earliness-Tardiness                                                                                                   | 28 |

| 2.6 Summary                                                                                                                                           | 31 |

| CHAPTER 3 : RESEARCH APPROACH                                                                                                                         | 32 |

| 3.1 Introduction                                                                                                                                      | 32 |

| 3.2 Phase 1: Single Batch Workstation with Sequence-Independent Setups and Equivolent Weights                                                         |    |

| 3.3 Phase 2: Single Batch Workstation with Sequence-Independent Setups and Unweights                                                                  |    |

| 3.4 Phase 3: Single Batch Workstation with Sequence-Dependent Setups and Unequ                                                                        |    |

| CHAPTER 4 : MATHEMATICAL MODEL FORMULATION AND COMPUTATION PERFORMANCE REQUIREMENTS                                                                   |    |

| 4.1 Phase 1: Single Batch Machine Scheduling with Sequence-Independent Setup Equal Earliness and Tardiness Penalties                                  | -  |

| 4.2 Computational Requirements of the Single Batch Machine Scheduling Problem Sequence-Independent Setups and Equal Earliness and Tardiness Penalties |    |

| CHAPTER 5 : HEURISTIC SOLUTION PROCEDURES                                                                                                             | 45 |

| 5.1 Introduction                                                                                                                                      | 45 |

| 5.2 Proposed Solution Heuristics                                                                                                                      | 45 |

| 5.2.1 Apparent Tardiness and Earliness Cost (ATEC) Heuristic                                                                                          | 45 |

| 5.2.2 Batching Incompatible Families with Earliness Tardiness Cost (BIFET) Heuristic 47                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.2.2.1 The Family Batch Constraint (FBC) Parameter                                                                                                          |

| 5.3 Computational Study                                                                                                                                      |

| 5.3.1 Benchmark Heuristics                                                                                                                                   |

| 5.3.2 Experimental Design                                                                                                                                    |

| 5.4 Discussion of Computational Results                                                                                                                      |

| CHAPTER 6: THE SINGLE BATCH WORKSTATION WITH UNEQUALLY-WEIGHTED PENALTIES AND VARYING BATCH SIZES AND INCOMPATIBLE FAMILIES AND SEQUENCE-INDEPENDENT SETUPS  |

| 6.1 Introduction                                                                                                                                             |

| 6.2 Phase 2: Single Batch Workstation with Sequence-Independent Setups and Unequal Job Weights                                                               |

| 6.2.1 Experimental Design                                                                                                                                    |

| 6.2.2 Performance Results of Varying Maximum Batch Sizes                                                                                                     |

| 6.2.3 Unequal Weights83                                                                                                                                      |

| 6.3 Integrating Order Review and Release Strategies                                                                                                          |

| 6.3.1 Experimental Design with ORR Strategies                                                                                                                |

| 6.4 Results with ORR Strategies 90                                                                                                                           |

| CHAPTER 7 : THE SINGLE BATCH WORKSTATION WITH UNEQUALLY-WEIGHTED PENALTIES AND VARYING BATCH SIZES AND INCOMPATIBLE FAMILIES AND SEQUENCE-DEPENDENT SETUPS95 |

| 7.1 Introduction                                                                                                                                             |

| 7.2 Mathematical Model                                                                                                                                       |

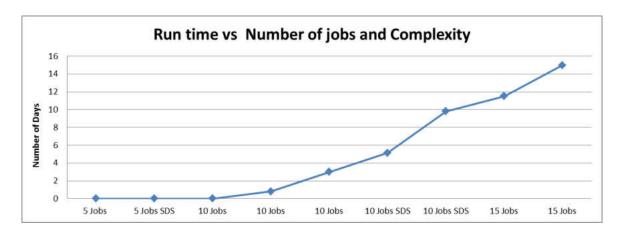

| 7.2.1 Computational Time of the Mathematical Model vs the Proposed and Benchmark Heuristics                                                                  |

| 7.2    | .2  | Experimental Design                                                         | 103 |

|--------|-----|-----------------------------------------------------------------------------|-----|

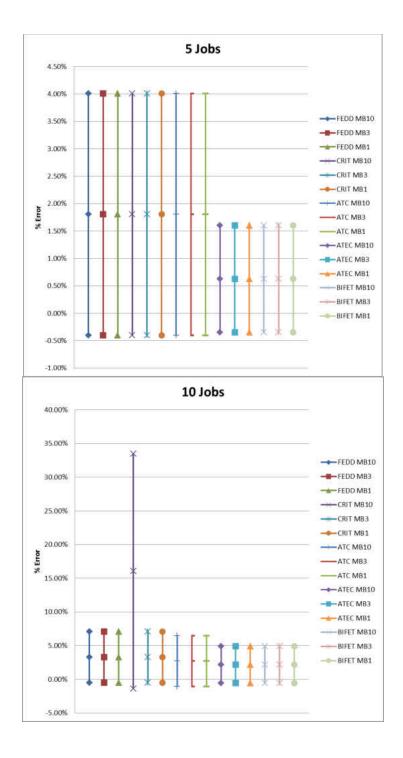

| 7.3    | D   | iscussion of the Performance Results                                        | 104 |

| 7.3    | .1  | Batch Size Impact                                                           | 104 |

| 7.3    | .2  | Effects of Weighted the Earliness and Tardiness Penalties                   | 105 |

| 7.3    | .3  | Overall Performance of Dispatching Rules and ORR versus Proposed Heuristics | 109 |

| СНАРТ  | ΈR  | 8 : SUMMARY AND FUTURE RESEARCH DIRECTIONS                                  | 119 |

| 8.1    | Sı  | ummary                                                                      | 119 |

| 8.2    | Fu  | uture Research Directions                                                   | 120 |

| 8.2    | .1  | Modeling Multiple Serial Machines in a Flow shop                            | 120 |

| 8.2    | .2  | Modeling Multiple Parallel Machines                                         | 121 |

| 8.2    | .3  | Machine scheduling with Job Preemption                                      | 123 |

| 8.2    | .4  | Due Date Time Windows                                                       | 124 |

| APPEN  | DIX | A: EQUAL WEIGHTS                                                            | 126 |

| APPEN  | DIX | X B: EARLY PENALY =10/TARDY PENALTY =1                                      | 157 |

| APPEN  | DIX | C: TARDY PENALTY=10/EARLY PENALTY = 1                                       | 188 |

| LIST O | FRI | FFFRENCES                                                                   | 218 |

#### LIST OF FIGURES

| Figure | 1.1. General product flow through the Coating Room 4                                                                                                                                                   |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 2.1. Summary of existing solution methodologies (modified from Mathirajan et al. 2006)                                                                                                                 |

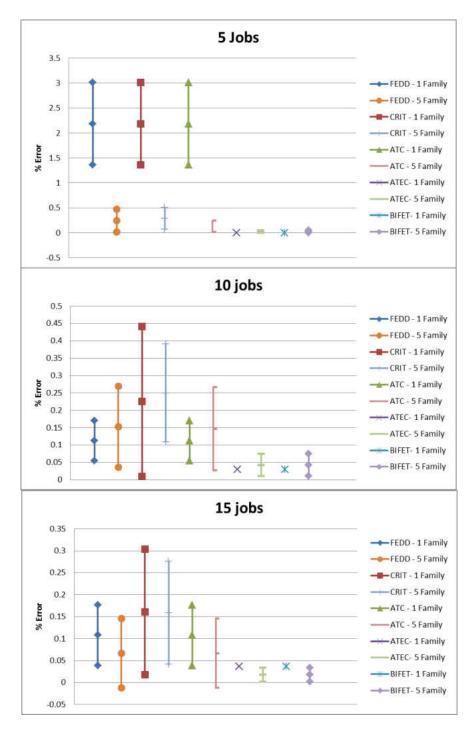

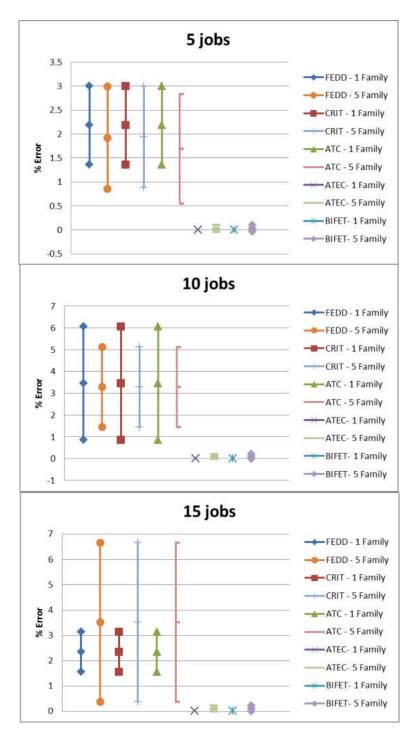

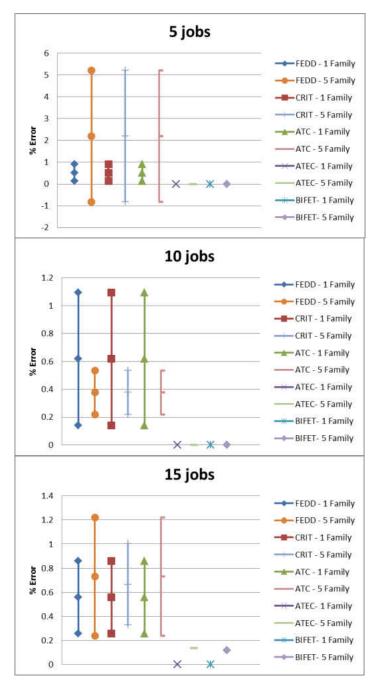

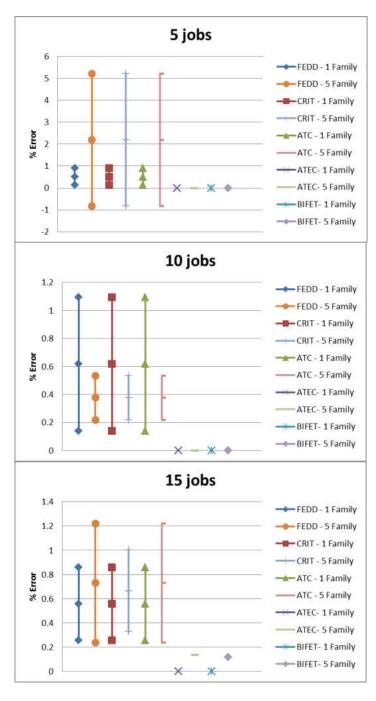

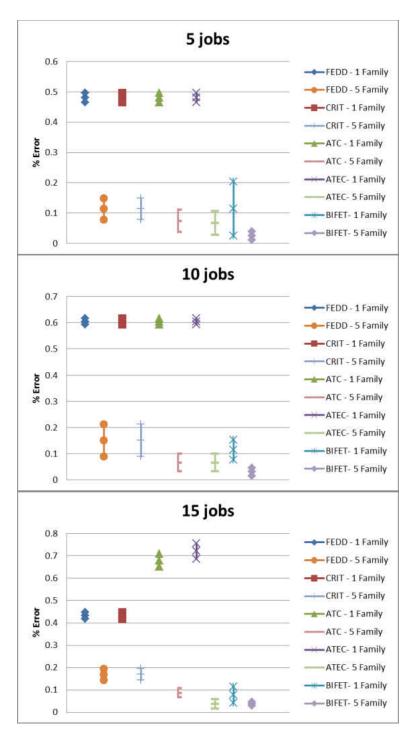

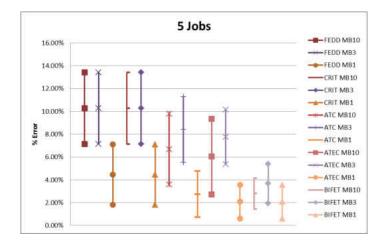

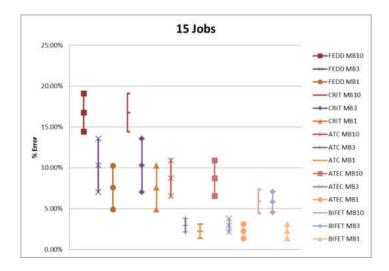

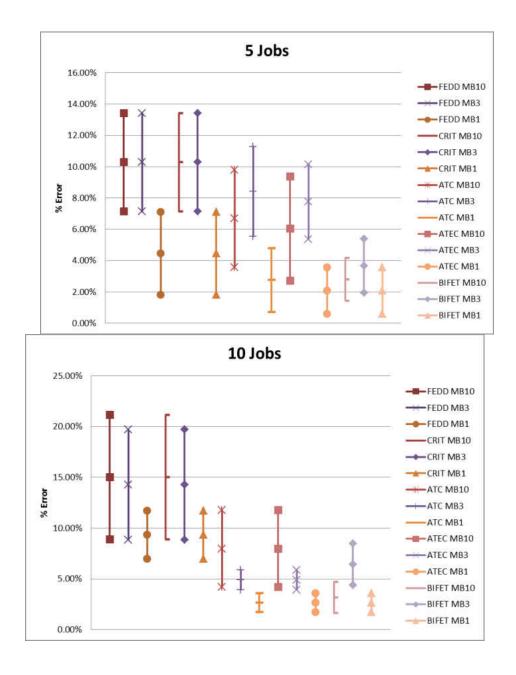

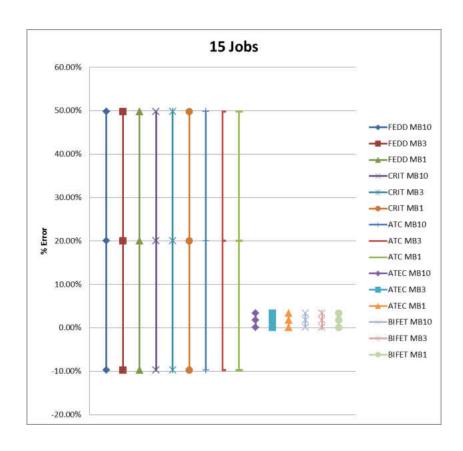

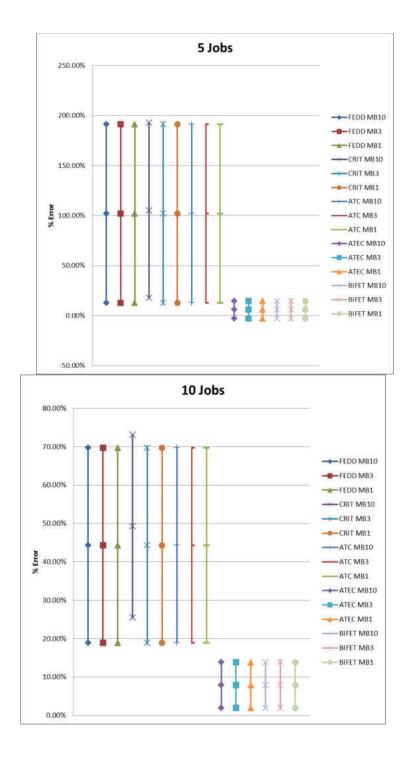

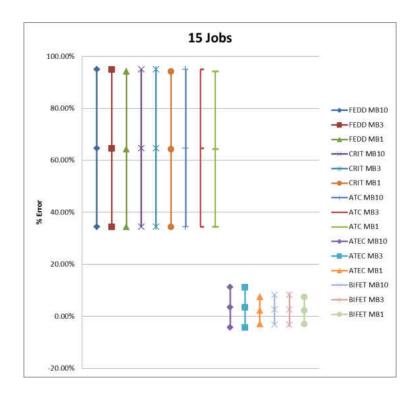

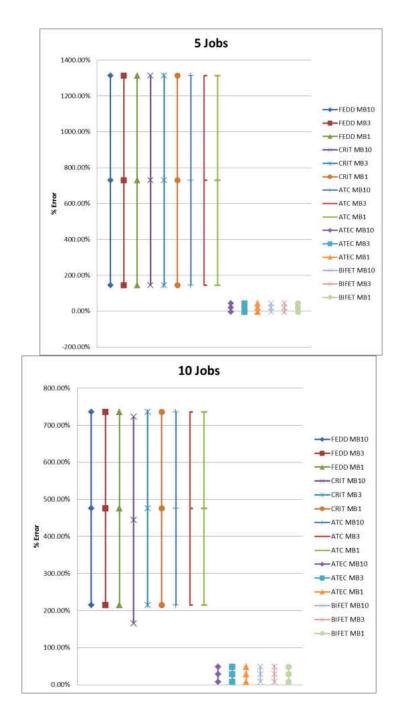

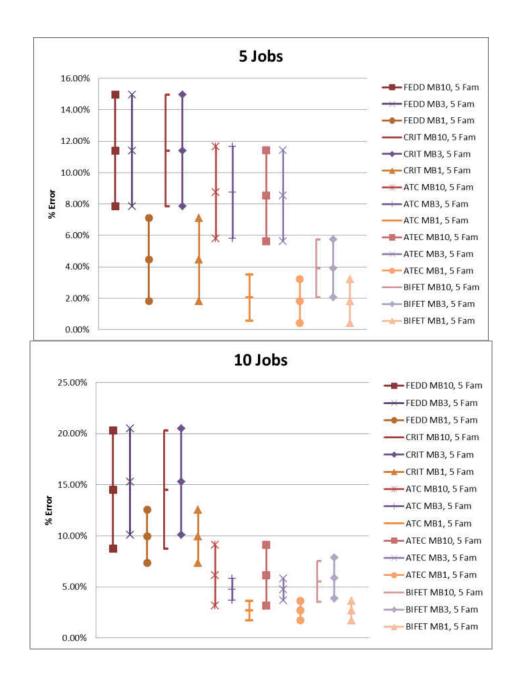

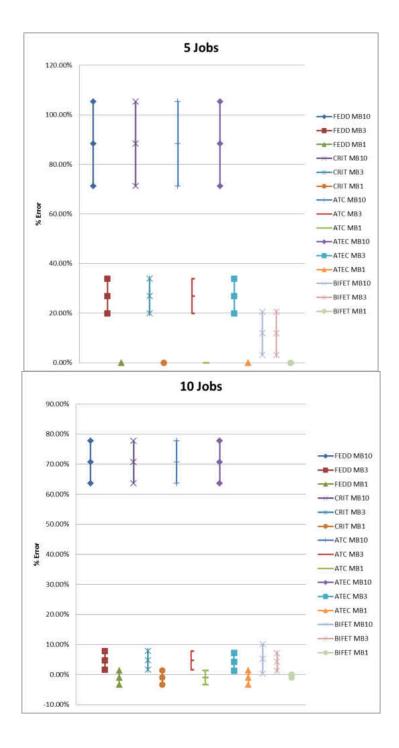

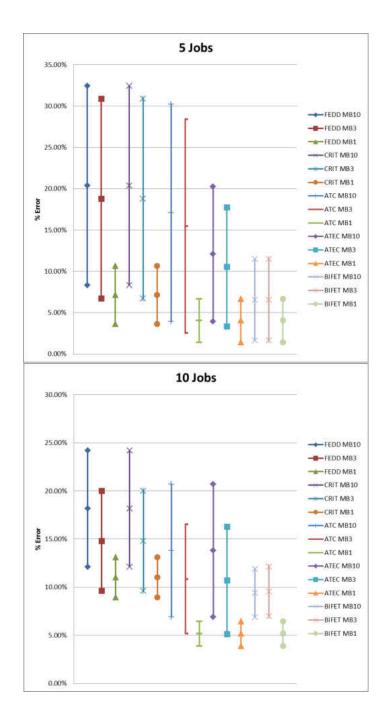

| Figure | 5.1. 95% confidence intervals on the performance results for 1 family and 5 families, tight due dates, and high traffic intensity                                                                      |

| Figure | 5.2. 95% confidence intervals on the performance results for 1 family and 5 families, tight due dates, and medium traffic intensity                                                                    |

| Figure | 5.3. 95% confidence intervals on the performance results for 1 family and 5 families, tight due dates, low traffic intensity                                                                           |

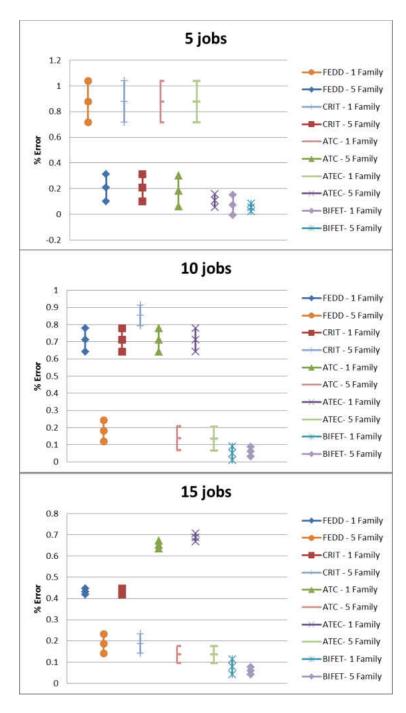

| Figure | 5.4. 95% confidence intervals on the performance results for 1 family and 5 families, loose due dates, and low traffic intensity                                                                       |

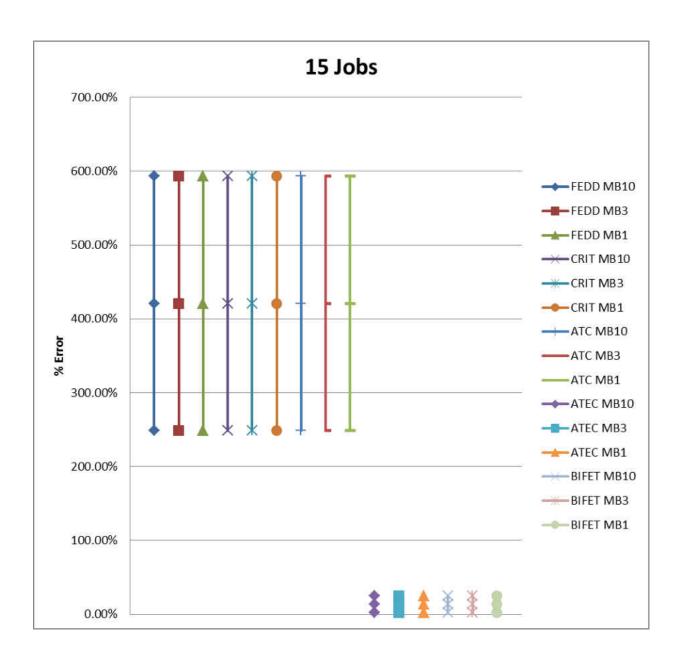

| Figure | 5.5. 95% confidence intervals on the performance results for 1 family and 5 families, tight due dates, and low traffic intensity                                                                       |

| Figure | 5.6. 95% confidence intervals on the performance results for 1 family and 5 families, loose due dates, and high traffic intensity                                                                      |

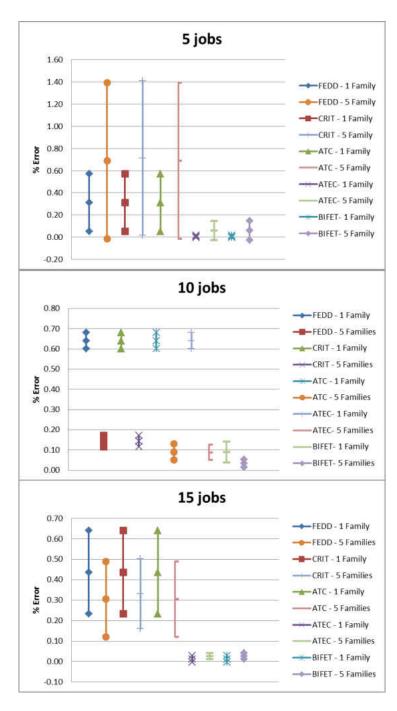

| Figure | 5.7. 95% confidence intervals on the performance results for 1 family and 5 families, tight due dates, and all jobs arriving simultaneously                                                            |

| Figure | 5.8. 95% confidence intervals on the performance results for 1 family and 5 families, loose due dates, and all jobs arriving simultaneously                                                            |

| Figure | 5.9. 95% confidence intervals on the performance results for 1 family and 5 families, tight due dates, and medium traffic intensity                                                                    |

| Figure | 5.10. 95% confidence intervals on the performance results for 1 family and 5 families, loose due dates, and medium traffic intensity                                                                   |

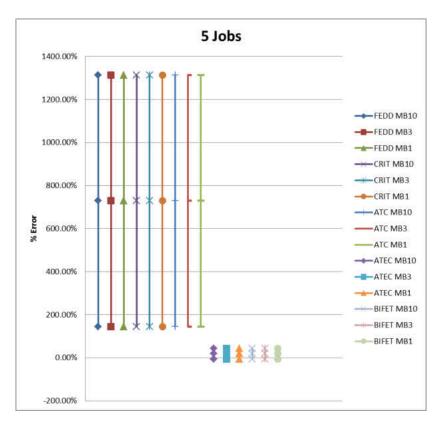

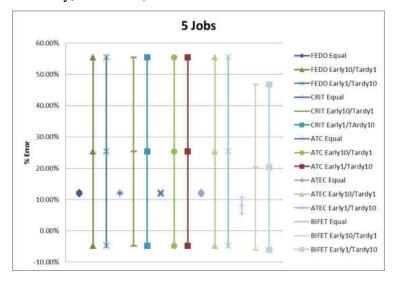

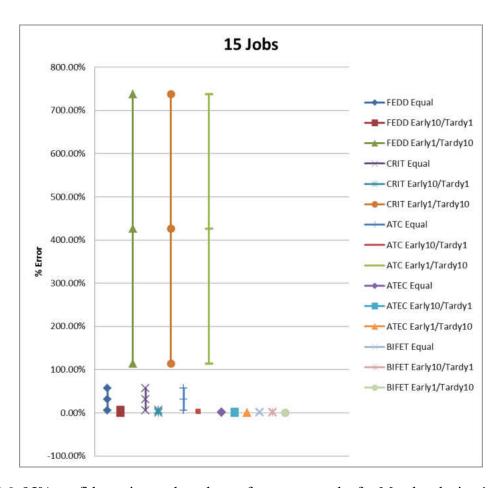

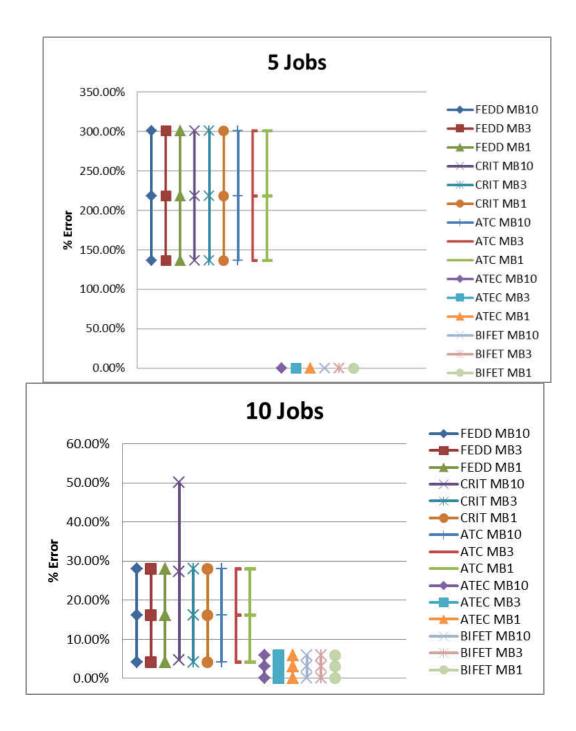

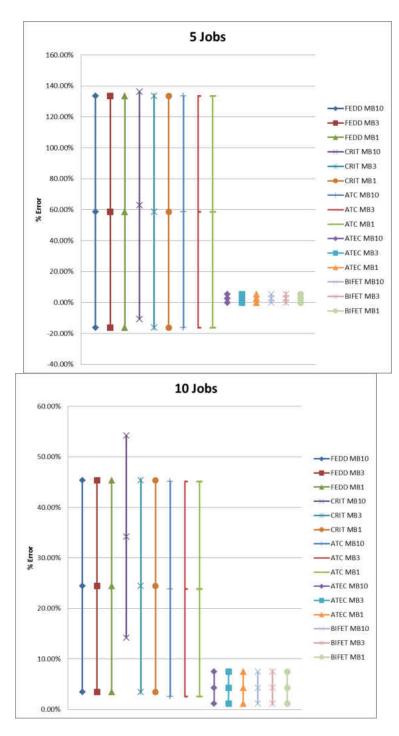

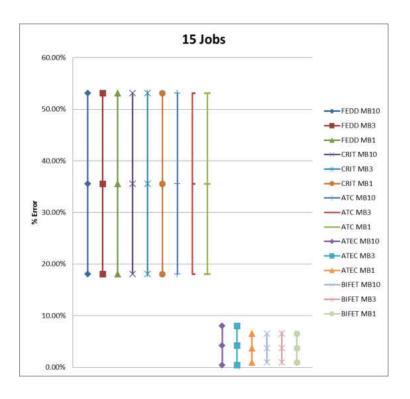

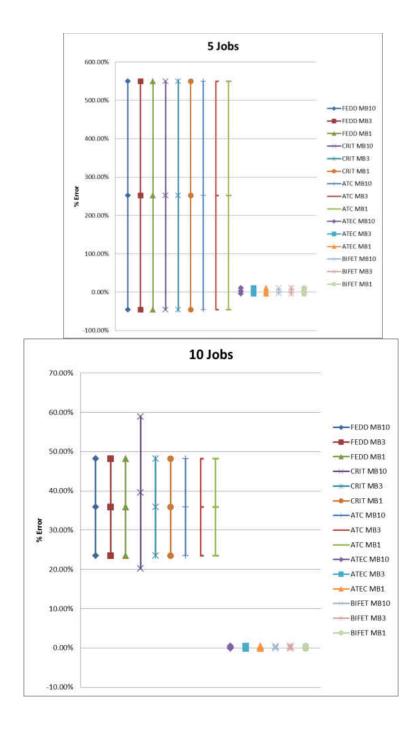

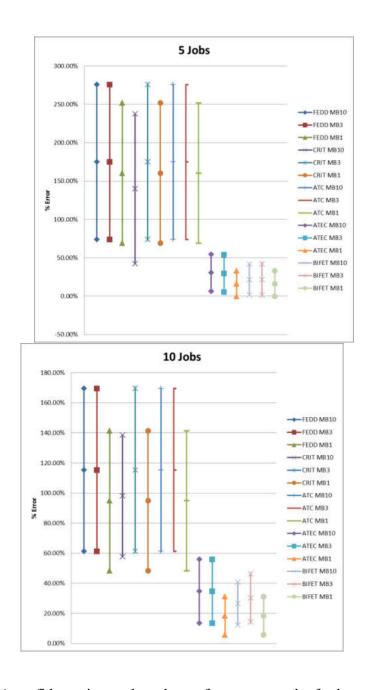

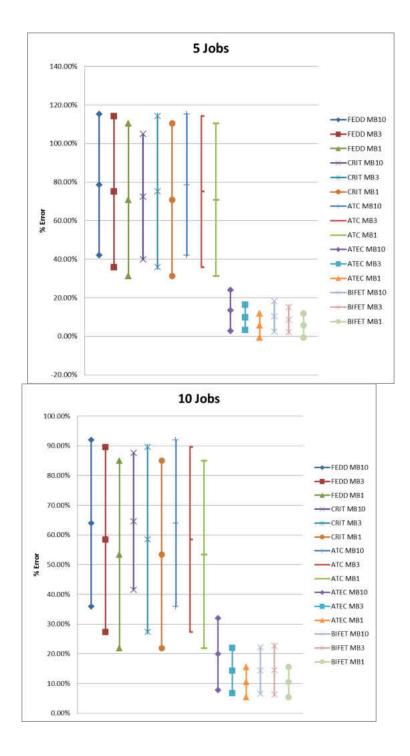

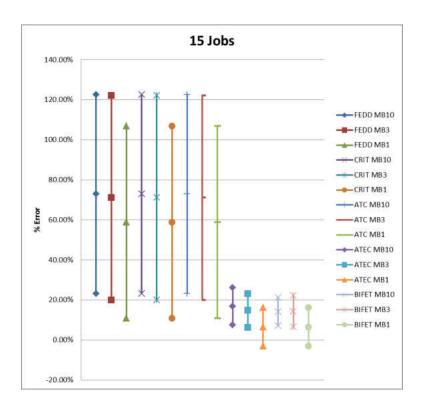

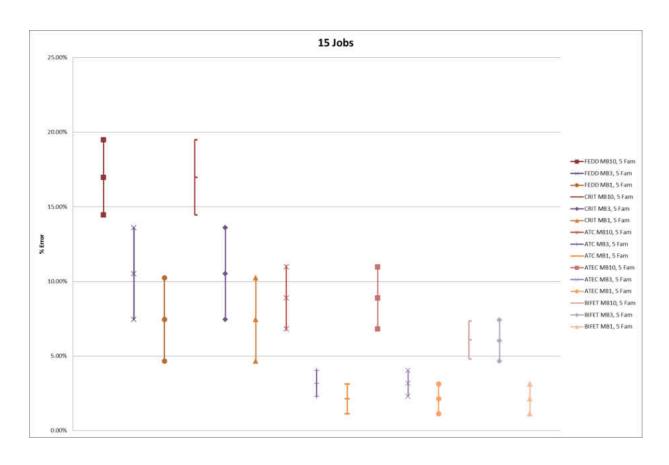

| Figure | 6.1. 95% confidence interval on the performance results with varying batch sizes for tight due dates, all jobs arrive simultaneously, 5 families, and earliness penalty = 10 and tardiness penalty = 1 |

| Figure | 6.2. 95% confidence interval on the performance results with varying batch sizes for tight due dates, all jobs arrive simultaneously, 5 families, and earliness penalty = 1 and tardiness penalty = 10.                                          |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 6.3. 95% confidence interval on the performance results with varying batch sizes for tight due dates, medium traffic intensity, 5 families, earliness penalty = 10 and tardiness penalty = 1.                                                    |

| Figure | 6.4. 95% confidence interval on the performance results for tight due dates, low traffic intensity, 5 families, and maximum batch size 10                                                                                                        |

| Figure | 6.5. 95% confidence interval on the performance results for tight due dates, jobs arrive simultaneously, 1 family, and maximum batch 3                                                                                                           |

| Figure | 6.6. 95% confidence interval on the performance results for Max batch size 1, tight due dates, medium traffic intensity, and 1 family.                                                                                                           |

| Figure | 6.7. 95% confidence interval on the performance results for equal earliness and tardiness penalties, tight due dates, all jobs arriving simultaneously, and 5 families                                                                           |

| Figure | 6.8. 95% confidence interval on the performance results for equal earliness and tardiness penalties, tight due dates, all jobs arriving simultaneously, and 5 families                                                                           |

| Figure | 6.9. 95% confidence interval on the performance results for equal earliness and tardiness penalties, tight due dates, high traffic intensity, 1 family, dispatching rules compared with ORR strategies combined with dispatching rules           |

| Figure | 6.10. 95% confidence interval on the performance results for equal earliness and tardiness penalties, tight due dates, low traffic, 1 family, dispatching rules compared with ORR strategies combined with dispatching rules.                    |

| Figure | 6.11. 95% confidence interval on the performance results for earliness penalty=10 and tardiness penalty=1, for tight due dates, high traffic intensity, 1 family, dispatching rules compared with ORR strategies combined with dispatching rules |

| Figure | 6.12. 95% confidence interval on the performance results for earliness penalty=1 and tardiness penalty=10, loose due dates, high traffic, 5 families, dispatching rules compared with ORR strategies combined with dispatching rules             |

| Figure | 7.1. Computational time for CPLEX to arrive at a solution as problem complexity increases in terms of the number of jobs.                                                                                                                        |

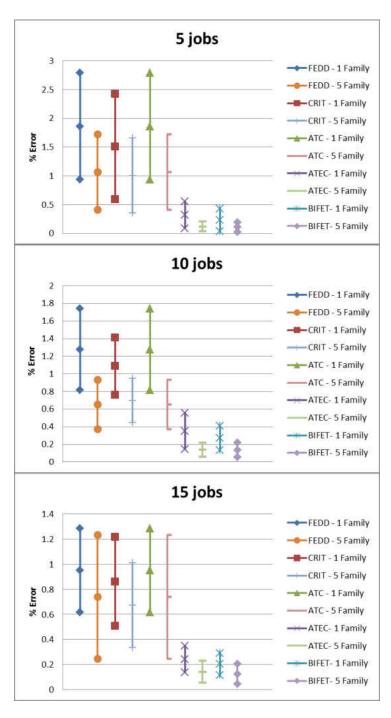

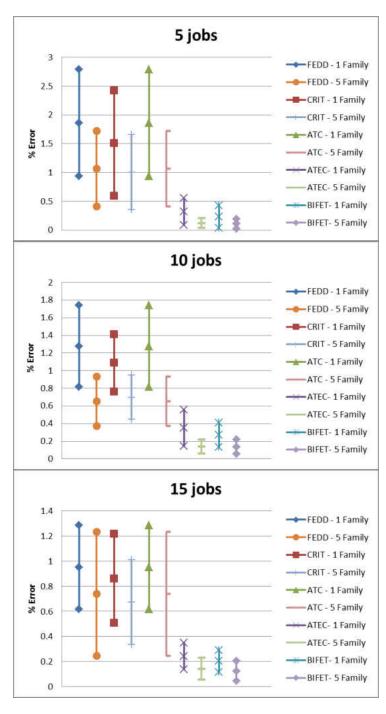

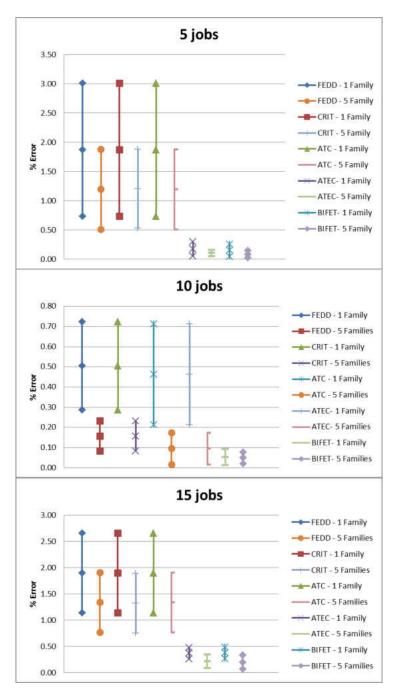

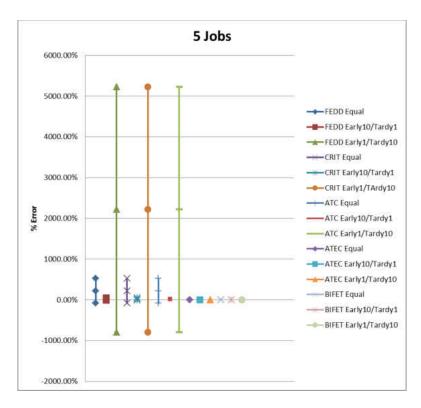

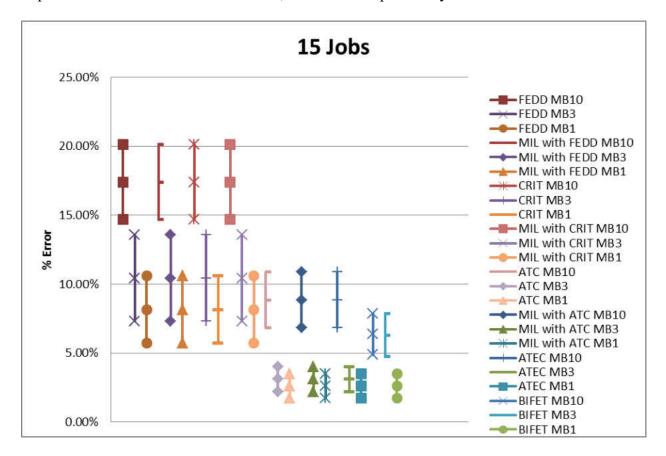

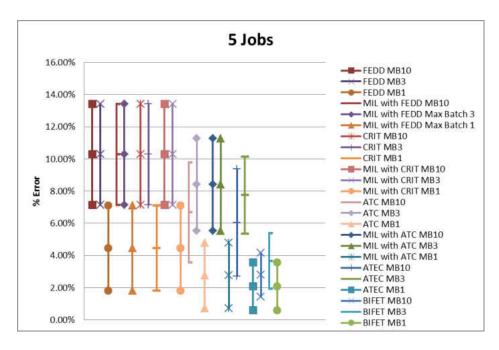

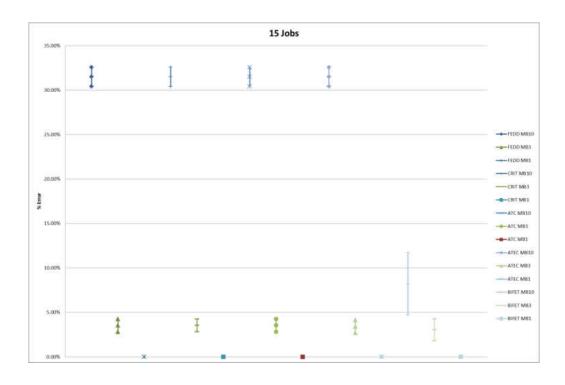

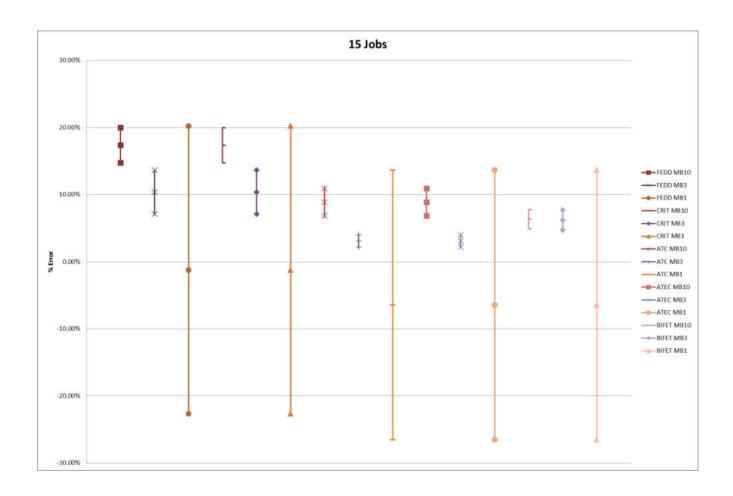

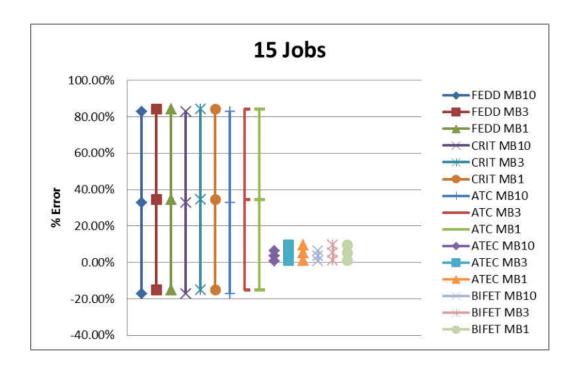

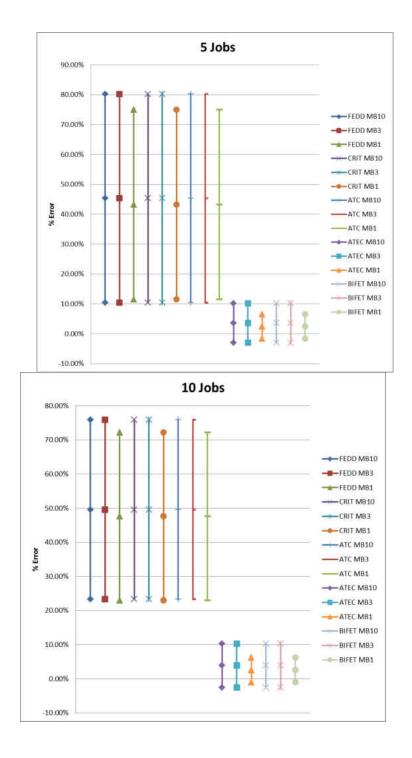

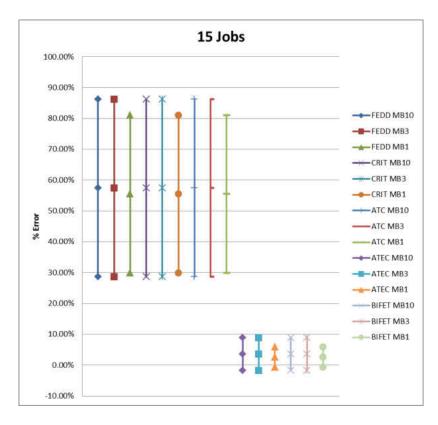

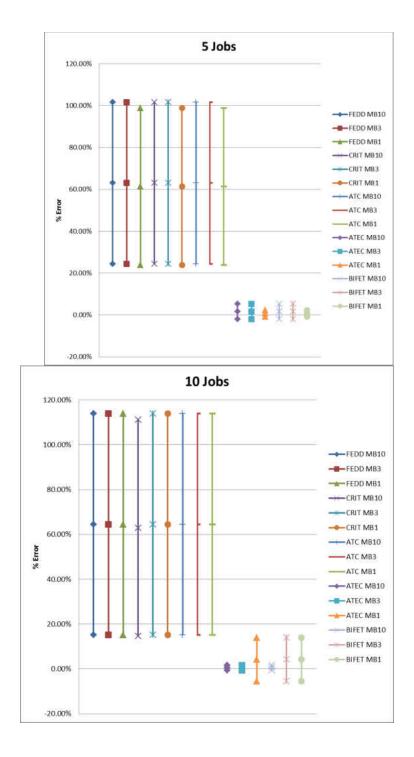

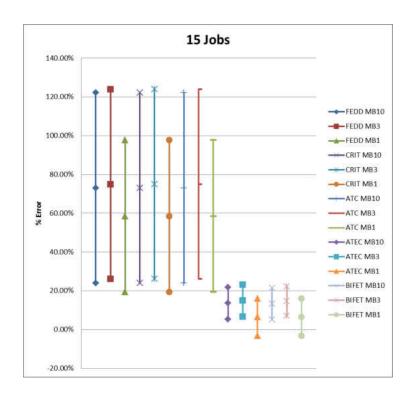

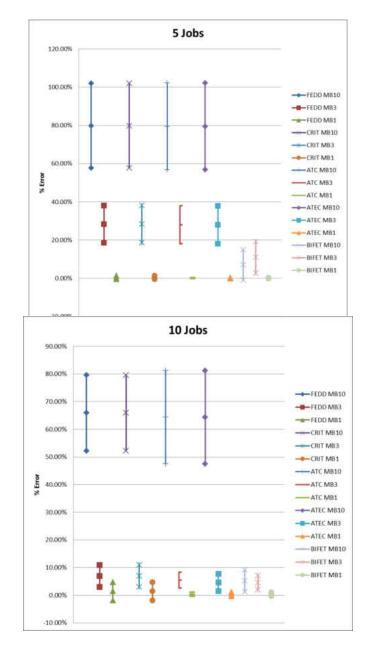

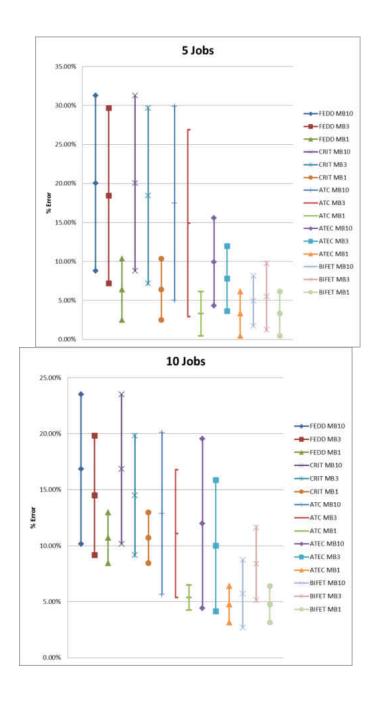

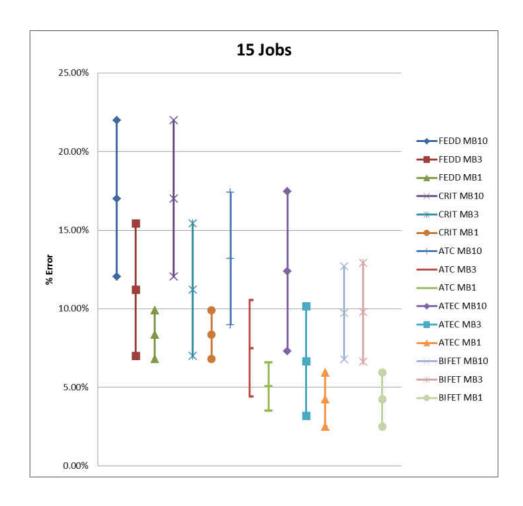

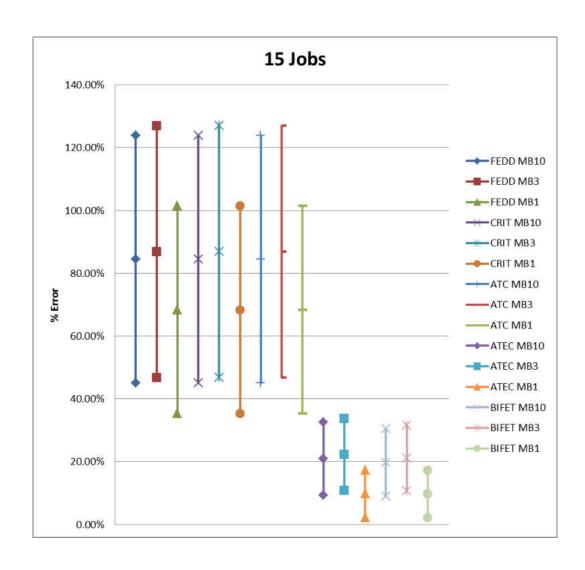

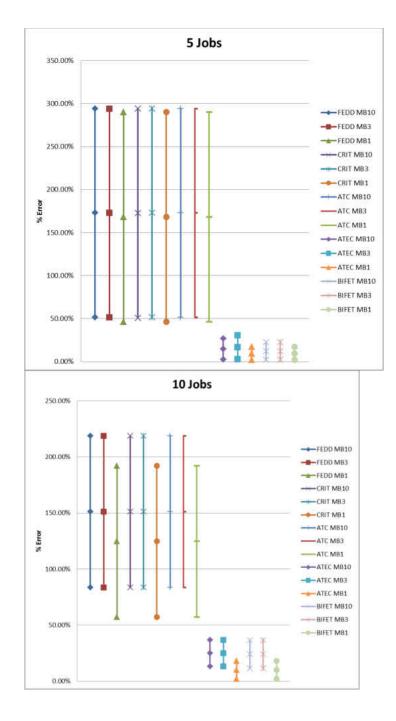

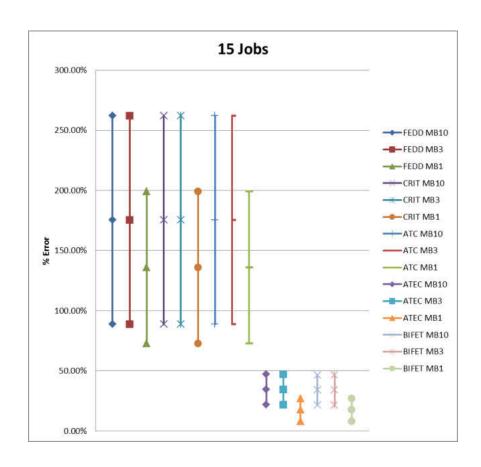

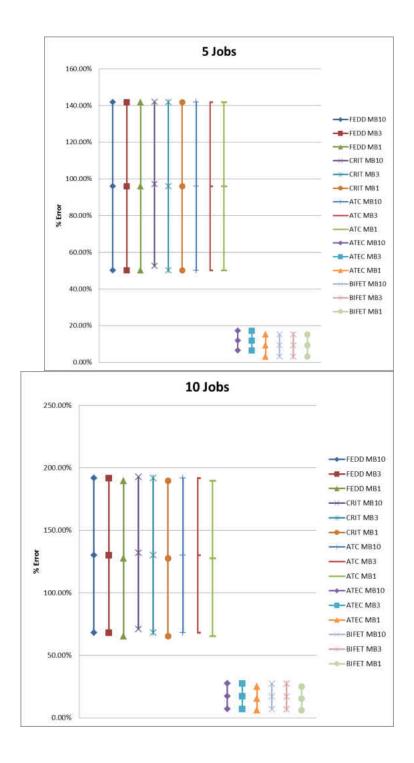

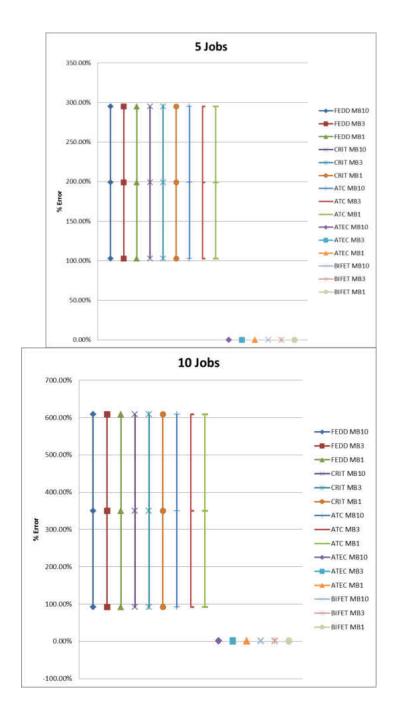

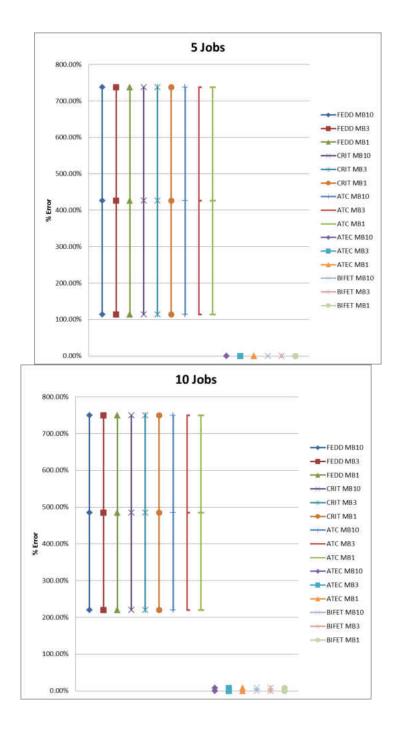

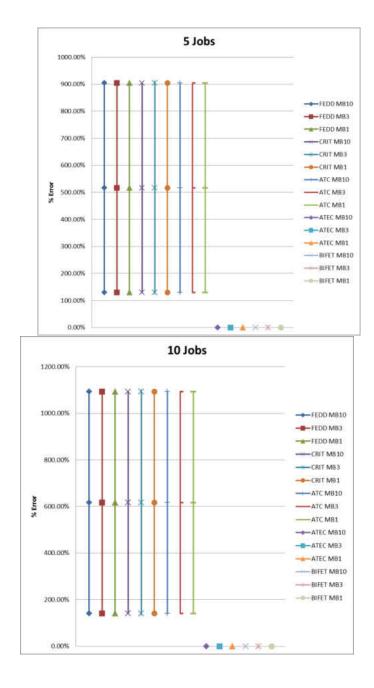

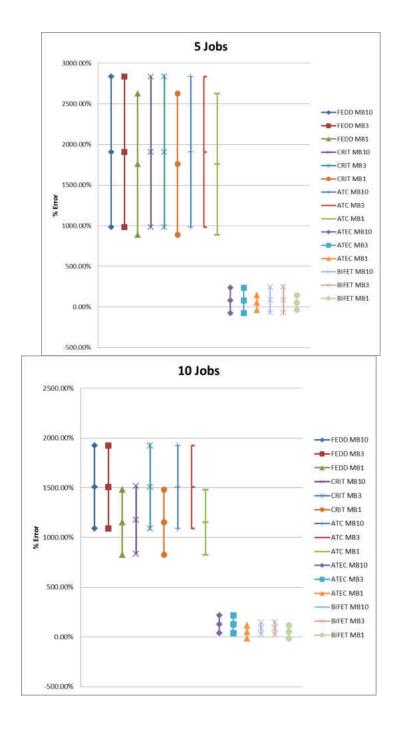

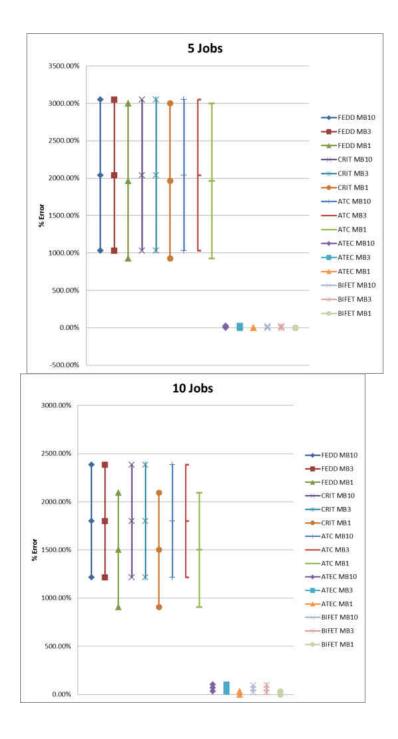

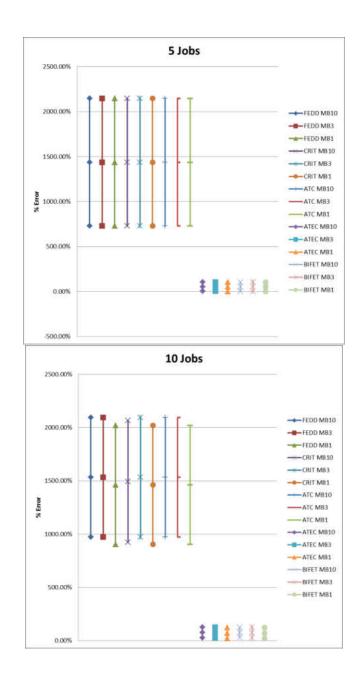

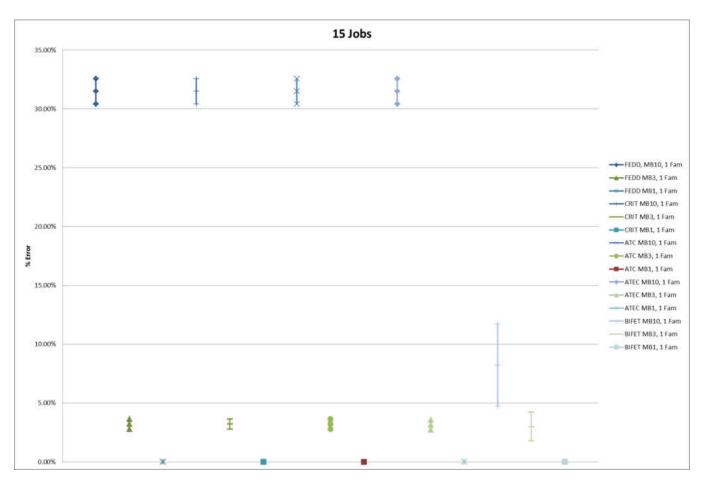

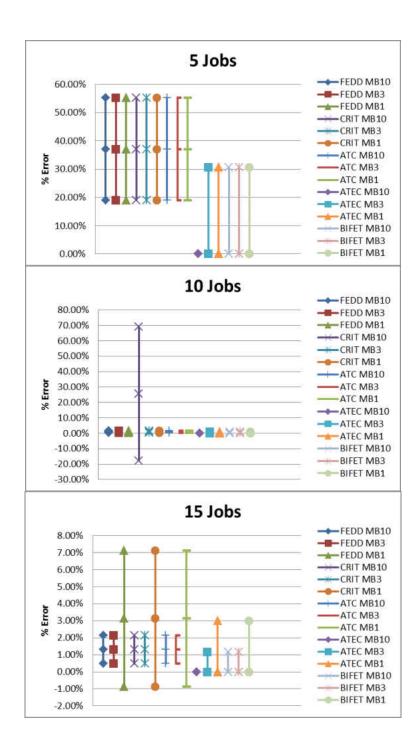

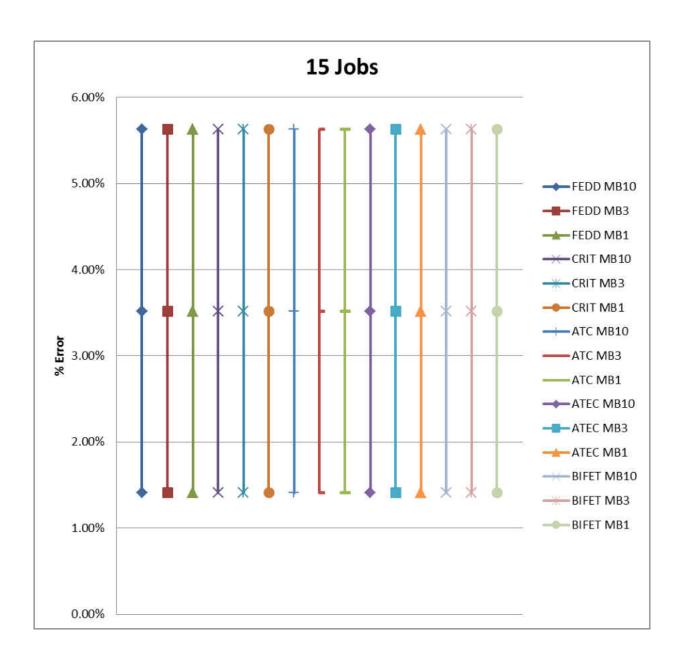

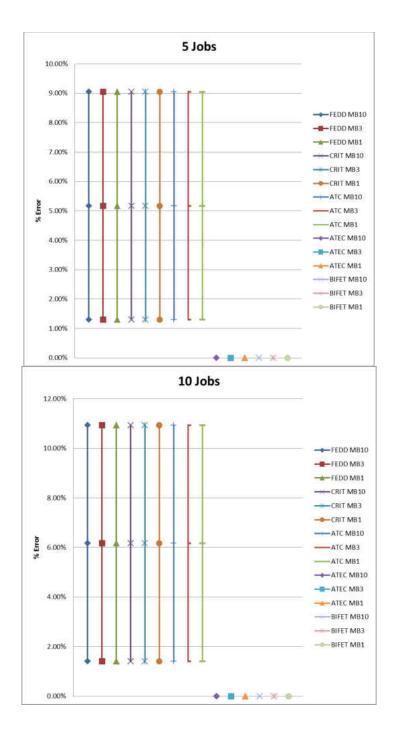

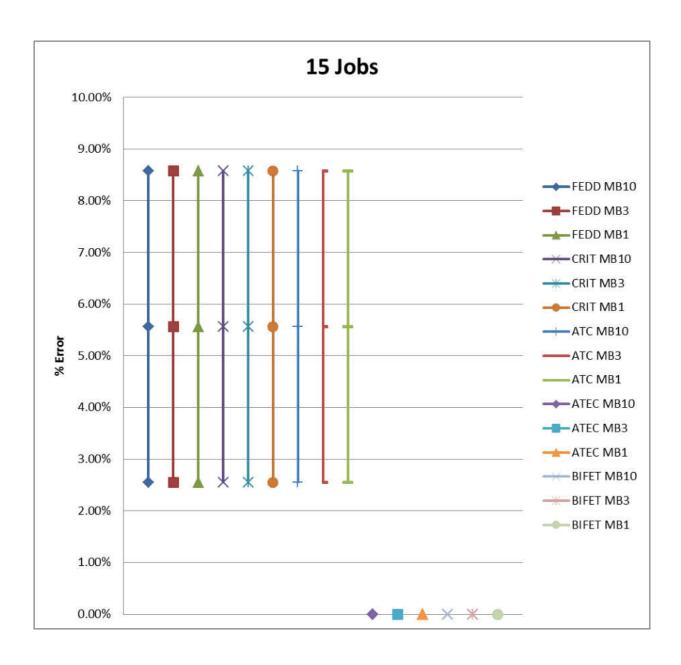

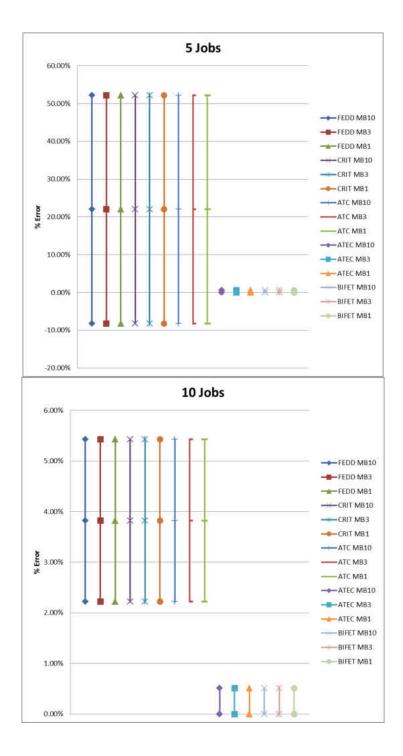

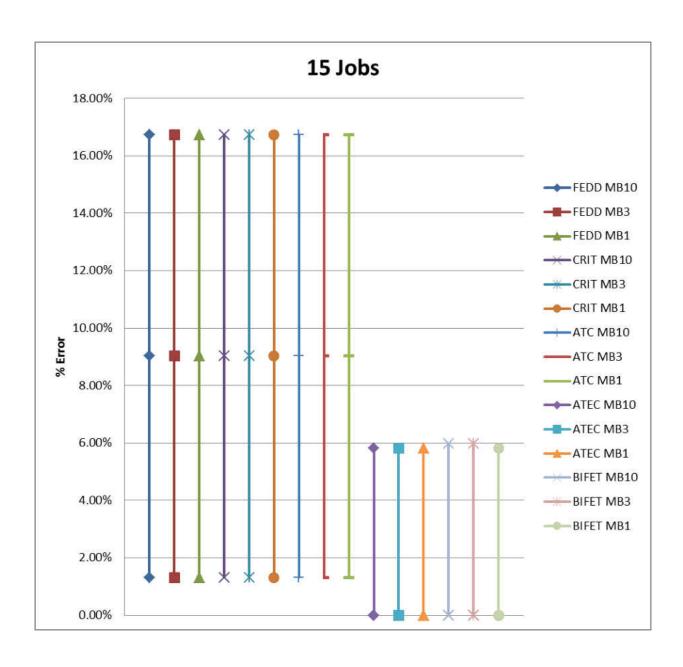

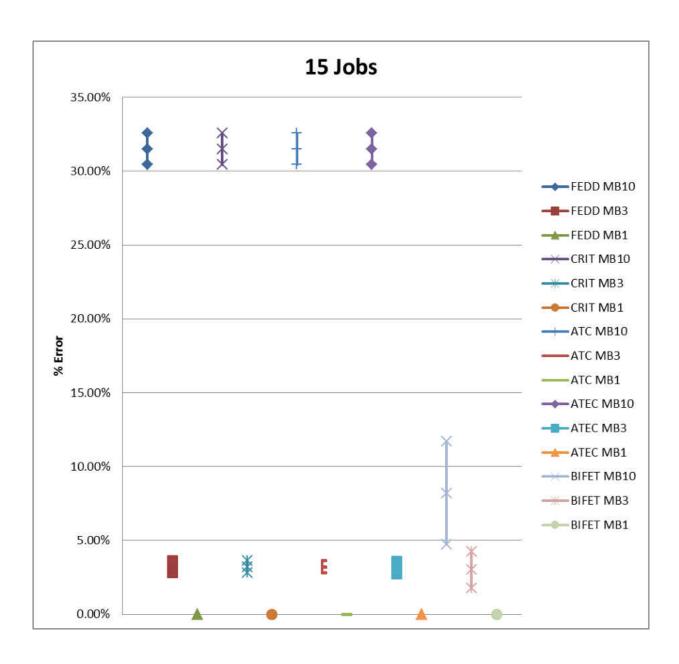

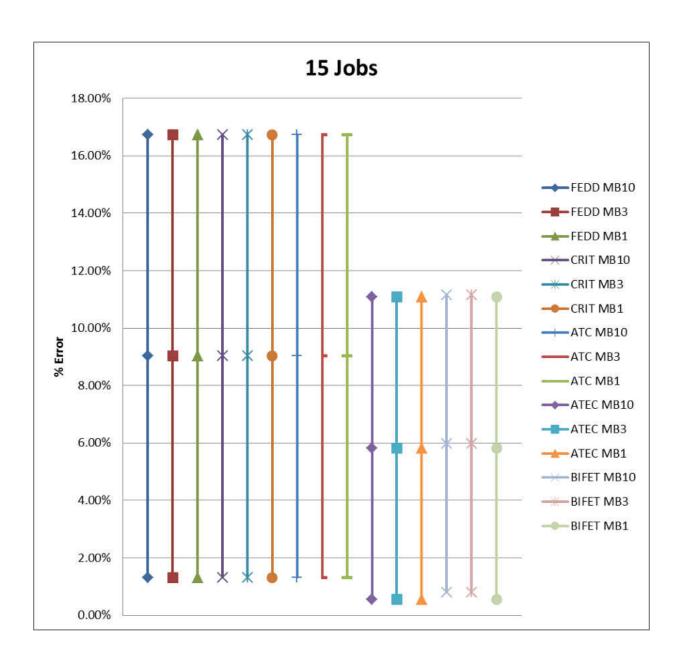

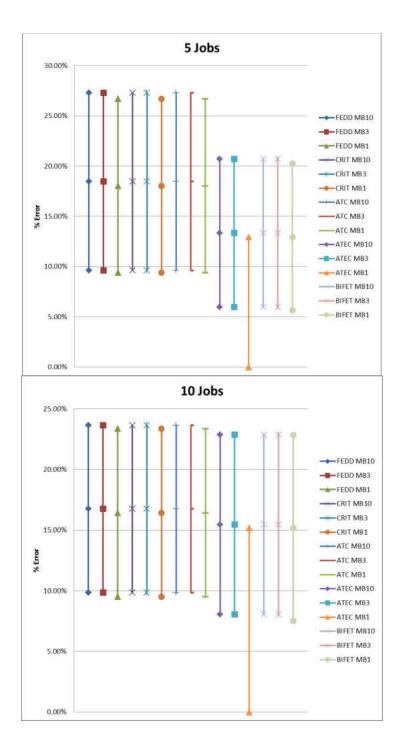

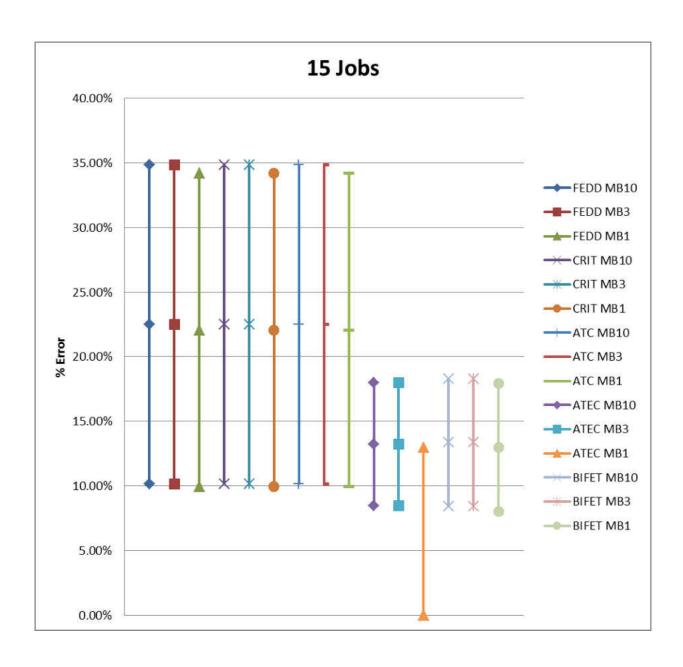

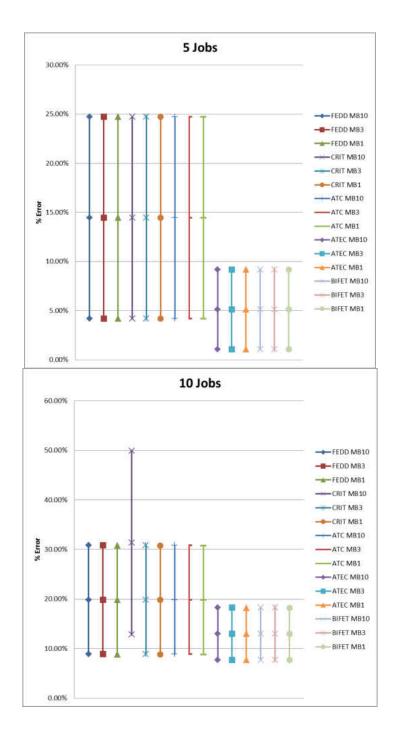

| Figure | 7.2. 95% confidence interval on the performance results for equal earliness and tardiness penalties, tight due dates, and high traffic intensity, dispatching rules compared with ORR strategies combined with dispatching rules          |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

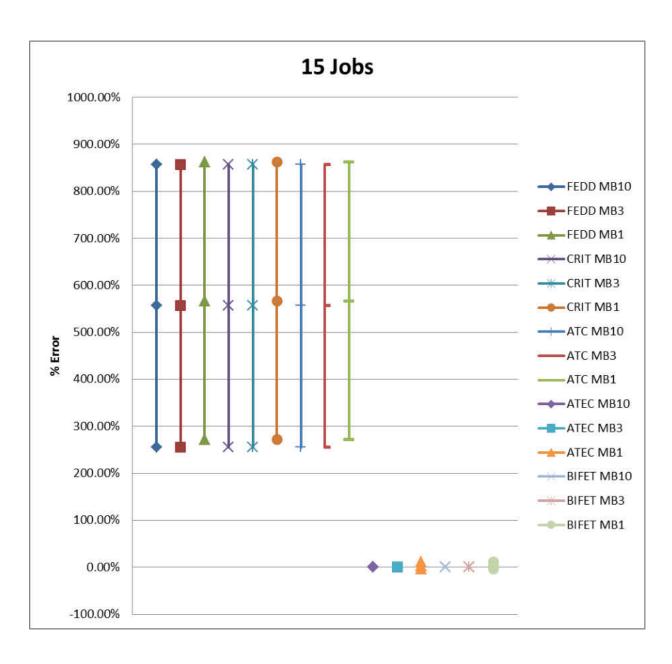

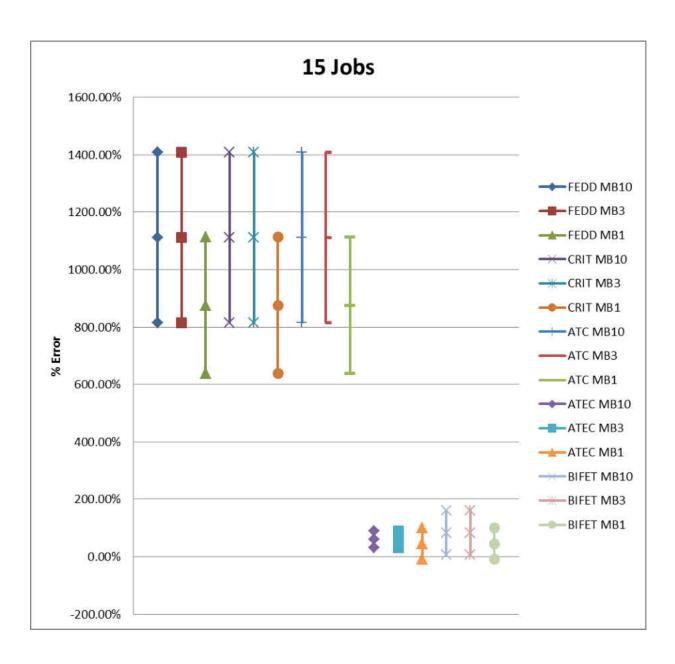

| Figure | 7.3. 95% confidence interval on the performance results for earliness penalty =10 and tardiness =1, tight due dates, and low traffic intensity, dispatching rules compared with ORR strategies combined with dispatching rules            |

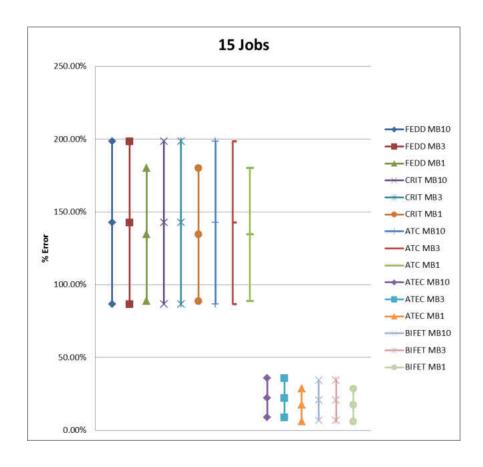

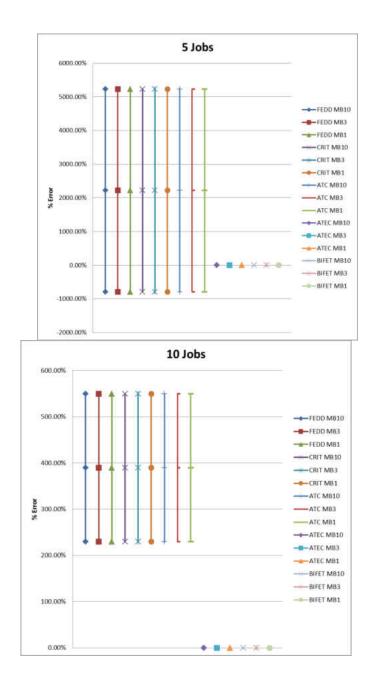

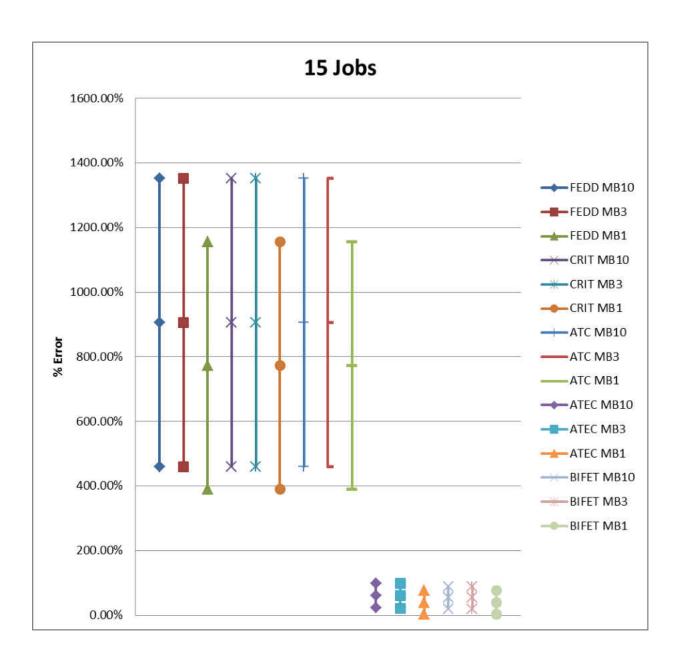

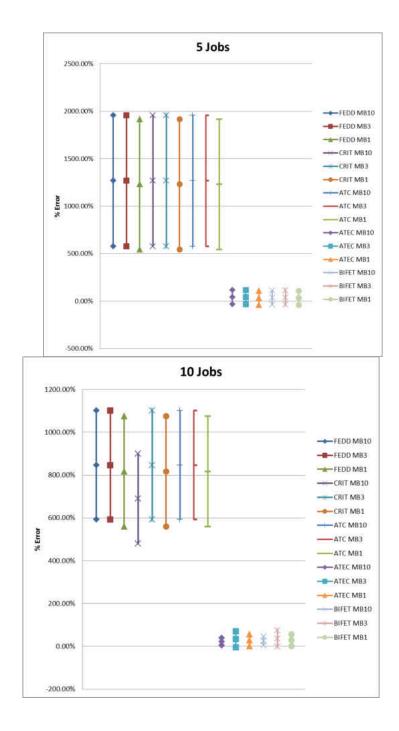

| Figure | 7.4. 95% confidence interval on the performance results for tardiness penalty =10, and earliness penalty = 1, loose due dates, and high traffic intensity, dispatching rules compared with ORR strategies combined with dispatching rules |

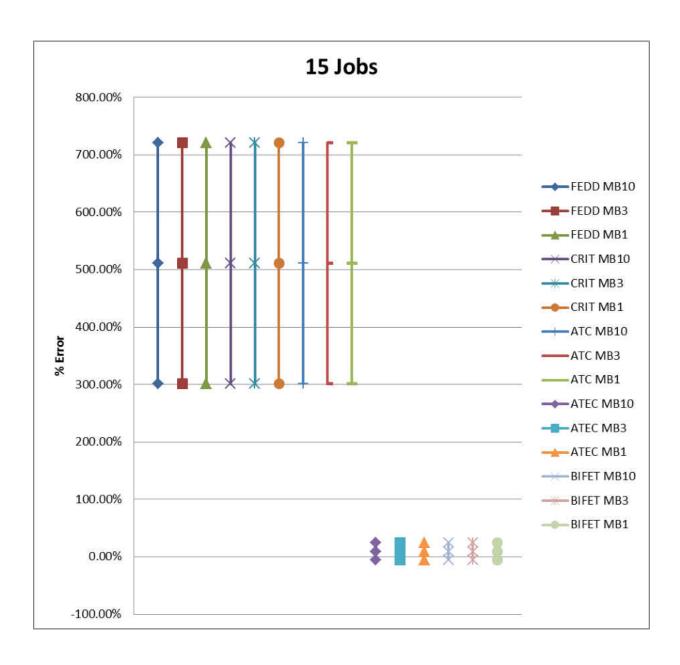

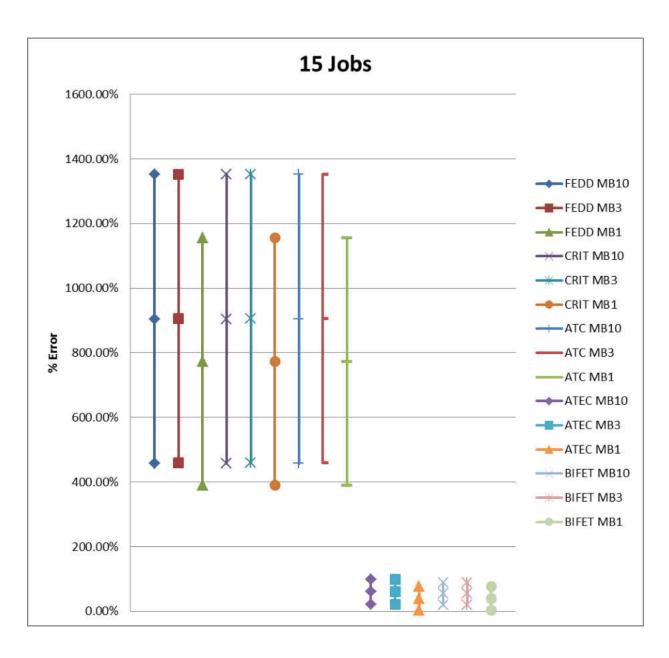

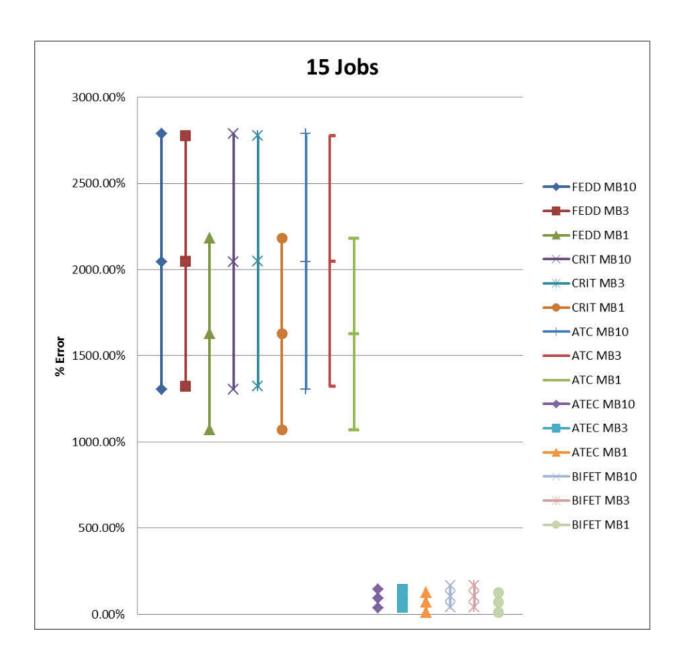

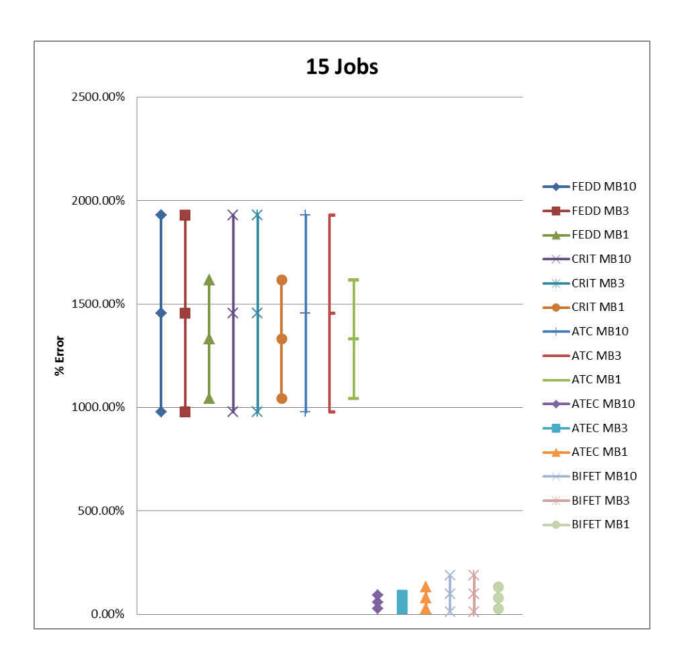

| Figure | 7.5. 95% confidence interval on the performance results for equal earliness and tardiness penalties, loose due dates, high traffic, dispatching rules compared with ORR strategies combined with dispatching rules.                       |

| Figure | 7.6. 95% confidence interval on the performance results for tardiness penalty =1, and earliness penalty = 10, loose due dates, high traffic, dispatching rules compared with ORR strategies combined with dispatching rules.              |

| Figure | 7.7: 95% confidence interval on the performance results for earliness penalty =1 and tardiness =10, loose due dates, high traffic, dispatching rules compared with ORR strategies combined with dispatching rules                         |

### LIST OF TABLES

| Table 4.1. Summary of CPLEX solution times in order to reach an optimal solution                                            | 44 |

|-----------------------------------------------------------------------------------------------------------------------------|----|

| Table 5.1. Experimental design for phase 1: single batch workstation with sequence-independent setups and equal job weights |    |

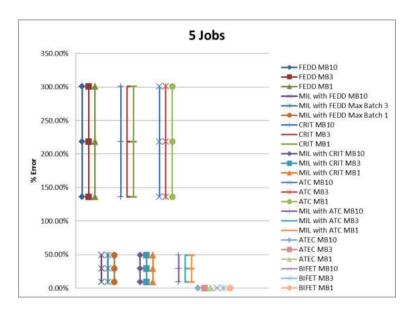

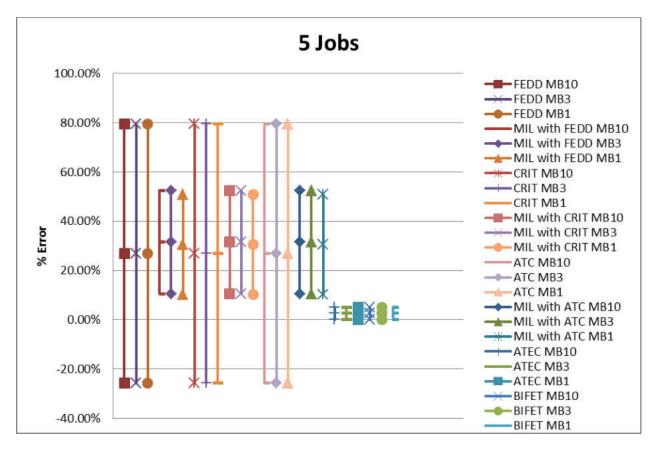

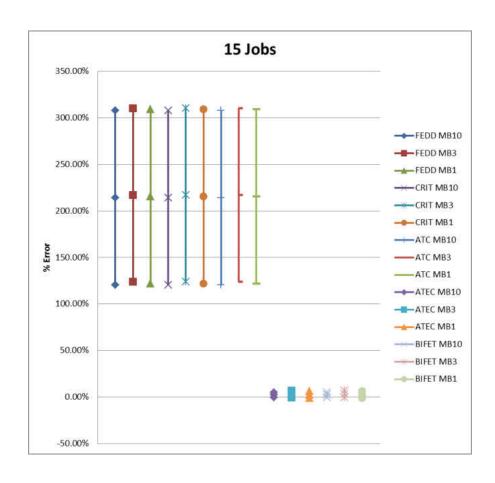

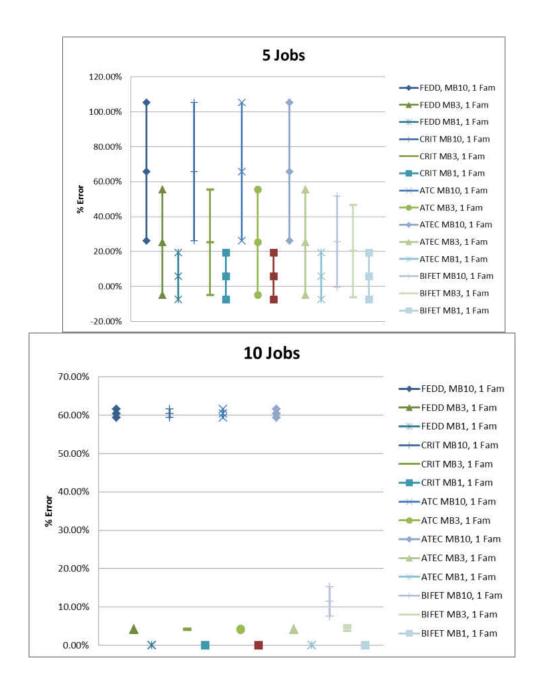

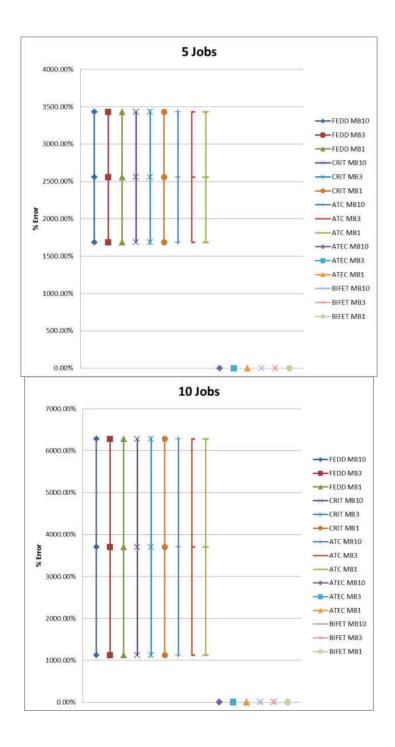

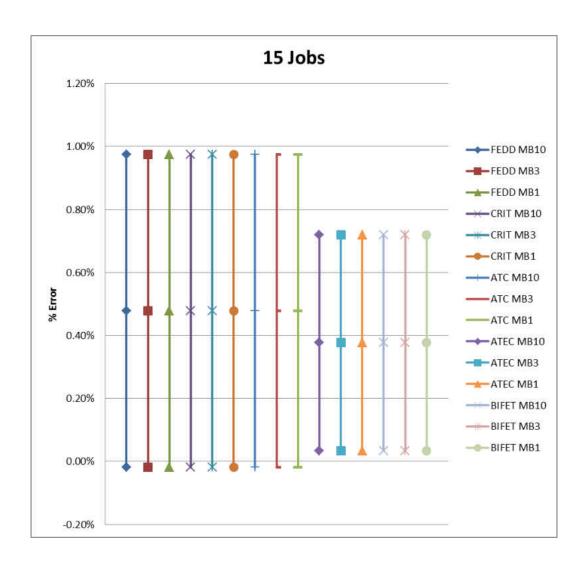

| Table 5.2. Performance results for 5 jobs with tight due dates results.                                                     | 54 |

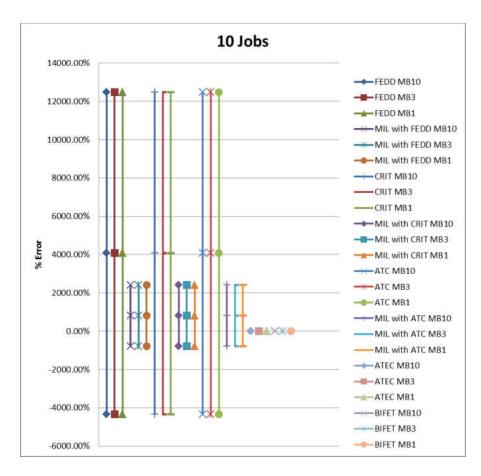

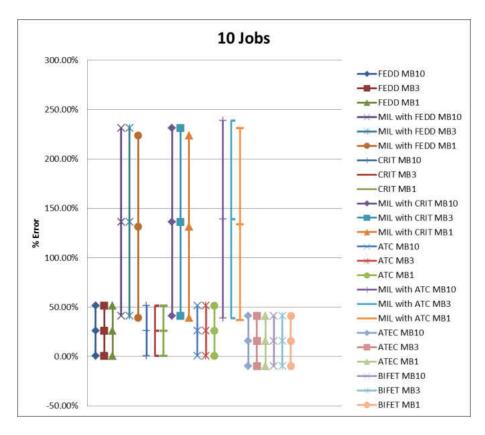

| Table 5.3. Performance results for 10 jobs with tight due date results                                                      | 54 |

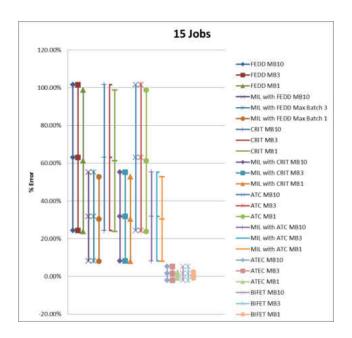

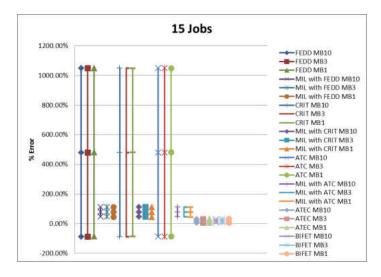

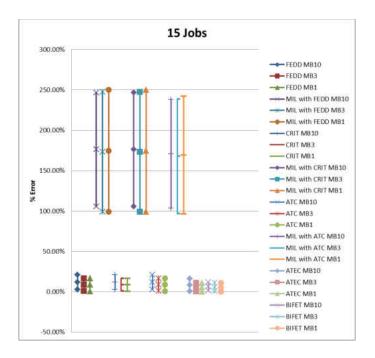

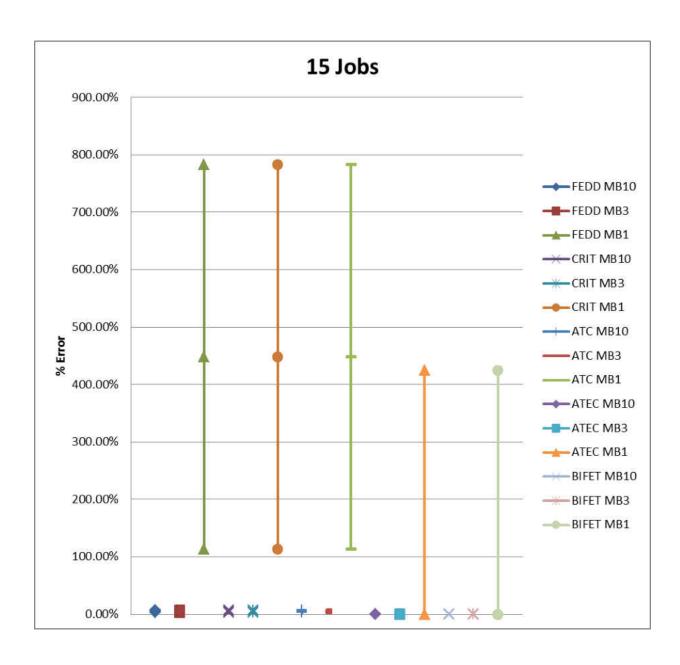

| Table 5.4. Performance results for 15 jobs with tight due dates                                                             | 55 |

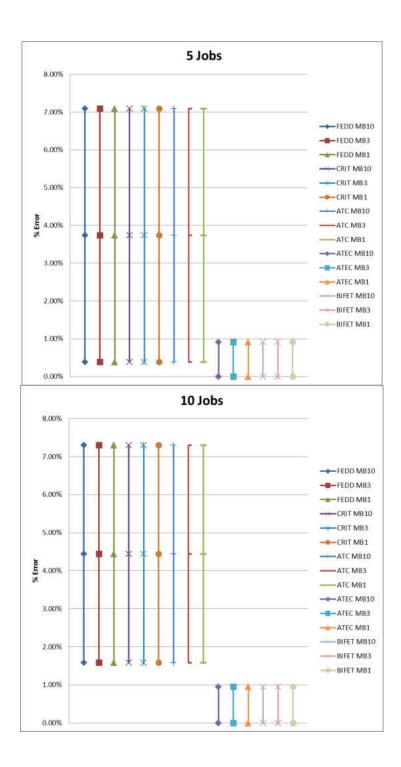

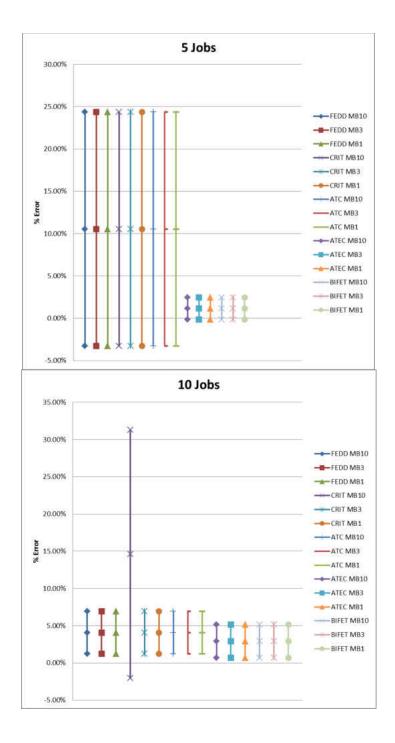

| Table 5.5. Performance results for 5 jobs with loose due dates                                                              | 56 |

| Table 5.6. Performance results for 10 jobs with loose due dates                                                             | 56 |

| Table 5.7. Performance results for 15 jobs with loose due dates                                                             | 56 |

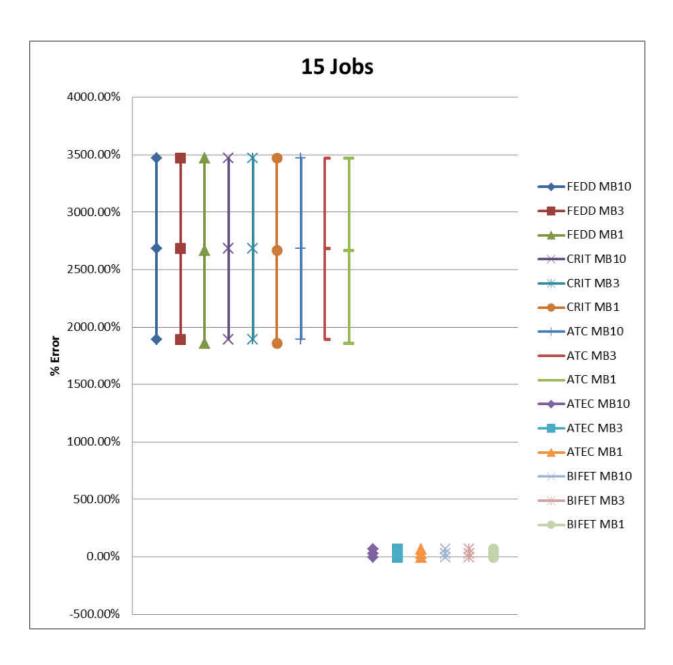

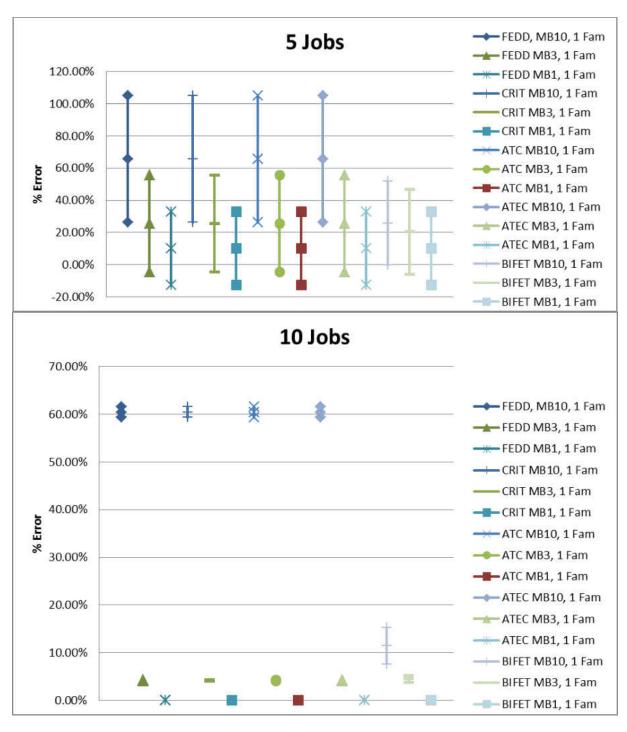

| Table 5.8. Performance results for 5 jobs that arrive simultaneously                                                        | 57 |

| Table 5.9. Performance results for 10 jobs that arrive simultaneously                                                       | 58 |

| Table 5.10. Performance results for 15 jobs that arrive simultaneously                                                      | 58 |

| Table 5.11. Performance results for 5 jobs with high traffic intensity.                                                     | 59 |

| Table 5.12. Performance results for 10 jobs with high traffic intensity.                                                    | 59 |

| Table 5.13. Performance results for 15 jobs with high traffic intensity.                                                    | 60 |

| Table 5.14. Performance results for 5 jobs with medium traffic intensity                                                    | 61 |

| Table 5.15. Performance results for 10 jobs with medium traffic intensity                                                   | 61 |

| Table 5.16. Performance results for 15 jobs with medium traffic intensity                                                   | 62 |

| Table 5.17. Performance results for 5 jobs with low traffic intensity                                                       | 62 |

| Table 5.18. Performance results for 10 jobs with low traffic intensity                                                      | 63 |

| Table 5.19. Performance results for 15 jobs with low traffic intensity                                                      | 63 |

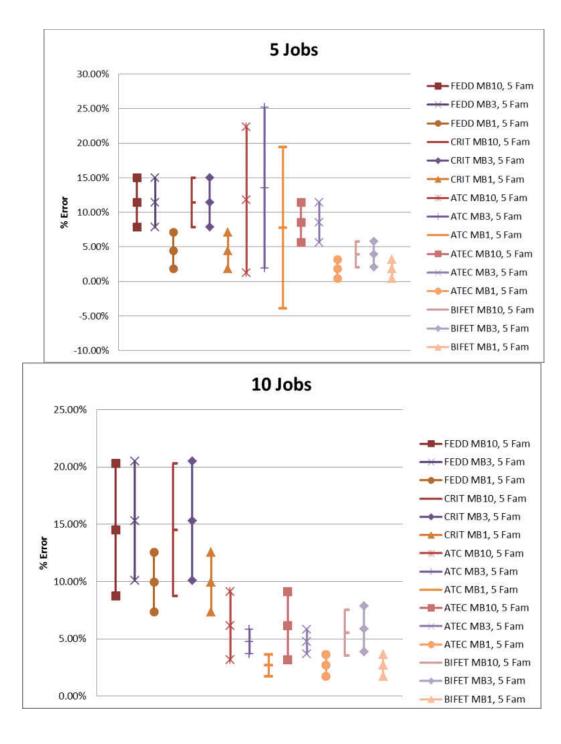

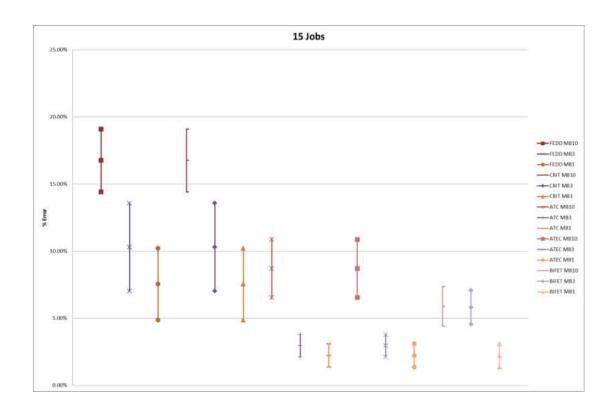

| Table 6.1. Experimental design with emphasis on unequal job weights and varying batch sizes.77                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 6.2. Comparison of ATC and ATEC performance of percent error with varying batch sizes and equal earliness and tardiness weights                                                      |

| Table 6.3. Comparison of ATC and BIFET performance of percent error with varying batch sizes and unequal earliness and tardiness weights where earliness is more important than tardiness. |

| Table 6.4. Comparison of ATC and ATEC performance of percent error with varying batch sizes and unequal earliness and tardiness weights where tardiness is more important than earliness   |

| Table 6.5. Comparison of FEDD and BIFET performance of percent error when varying penalties at a maximum batch size of 10                                                                  |

| Table 7.1. Experimental design with emphasis on unequal job weights and sequence-dependent setups                                                                                          |

| Table 7.2. Comparison of MIL with ATC and BIFET performance of percent error when varying batch sizes                                                                                      |

| Table 7.3. Comparison of MIL with ATC and BIFET performance of percent error when varying penalties                                                                                        |

| Table 7.4. Average percent error for heuristics                                                                                                                                            |

| Table 7.5. Comparison of rule performance for ATC against MIL with ATC for equal penalties and earliness penalty=10/tardiness penalty=1                                                    |

| Table 7.6. Comparison of rule performance for ATEC against MIL with ATC for equal penalties and earliness penalty=10/tardiness penalty=1                                                   |

| Table 7.7. Comparison of rule performance for BIFET against MIL with ATC for equal penalties and earliness penalty=10/tardiness penalty=1                                                  |

| Table 7.8. Comparison of rule performance for MIL ATC against ATC for earliness penalty =1/tardiness penalty =10                                                                           |

| Table 7.9. Comparison of rule performance for ATEC against ATC for earliness penalty =1/tardiness penalty =10                                                                              |

| Table | 7.10. | Comparison    | of rule | performance | for | <b>BIFET</b> | against | ATC | for | earliness | penalty |

|-------|-------|---------------|---------|-------------|-----|--------------|---------|-----|-----|-----------|---------|

|       | =1/ta | rdiness penal | ty = 10 |             |     |              |         |     |     |           | 118     |

#### **CHAPTER 1: INTRODUCTION**

#### 1.1. Background of the Industrial Setting Motivating This Research Investigation

The motivation of this research investigation stems from a particular production environment at large international communications and information technology company serving both the government and commercial markets. This company specializes in government contracts that provide funding to the company to produce various complex electro-mechanical assembly systems that support communications systems. These communication systems are typically installed on avionics, space, and ground systems such as radios, reflectors, ground system radars, etc. Often, the assemblies start with the production of circuit card assemblies (CCAs). These CCAs are later assembled into a chassis using mechanical subassemblies.

The typical customers for these products are the United States military, foreign militaries and industries, and commercial customers. The requirements of a government contract constitute what is called a manufacturing program, where the program has unique hardware requirements, quantities for the electro-mechanical assemblies (EMAs), and a unique customer. The work for a program includes the effort of designing and manufacturing a set of products or systems for that customer. Each EMA can contain one or multiple CCAs, and there can be multiple types (or families) of CCAs built for one program.

#### 1.1.1 The Importance of On-Time Delivery

The Master Production Schedule (MPS) outlines the manufacturing start time (or release date) of each assembly within a program (or within multiple programs), expected manufacturing completion dates, and customer due dates. Strict adherence to the MPS for a contract is the primary objective, and the MPS is often fixed. The metric often used to measure on-time delivery performance of a program is the Schedule Performance Index (SPI). SPI is the ratio of what is completed versus what was scheduled to be completed. An SPI value equal to 1.0 means the program is on-schedule for delivery. An SPI value less than 1.0 means the program is behind schedule.

Strict adherence to the fixed schedule is necessary for several reasons. Firstly, some assemblies must be loaded onto cargo ships that arrive at local loading docks at specific times during the year, and typically, there is a one-week window during which these ships are docked. The assemblies must be delivered to and arrive at the loading dock during this one-week window in order to be loaded onto the cargo ship. Therefore, it is imperative that all deliveries arrive on time.

Secondly, missing a delivery date could result in a loss of an award fee to the company. Typically, programs are financially compensated when they reach certain performance goals. One of these performance goals is on-time delivery performance. The award fees are given when the program meets each delivery milestone. The award fee is another incentive for the manufacturing completion dates of programs to be aligned to the MPS.

Finally, finishing a program's production ahead of schedule incurs a penalty in the form of rework costs. If production jobs are finished ahead of schedule (or, early), and there is an engineering change order that requires a change to the design of the product, or if it is found that a component is not performing to its full capability and needs to be removed and replaced by a superior component, then the finished inventory will have to be reworked and retested.

#### 1.1.2 The Coating Room

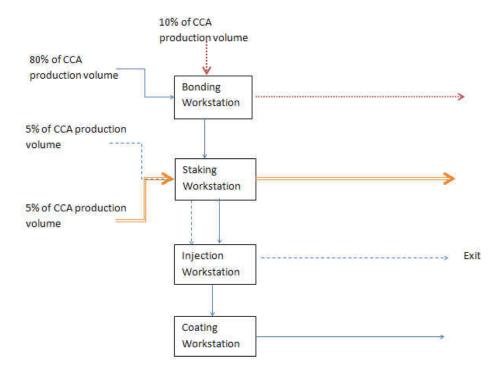

The particular area of interest within the subject manufacturing facility is the Coating Room, which is a key area in the production of circuit card assemblies. This area is classified as a low-volume, high product variety job shop. Virtually all programs completed in the facility require at least one or more process steps performed in the Coating Room, which results in a large variety of CCAs that visit the Room. The Coating Room has several functional areas such as Bonding, Staking and Coating (see Figure 1.1.).

Figure 1.1. General product flow through the Coating Room.

Each process involves the application of chemicals and chemical adhesives to the assemblies. The assemblies require these additional processes for structural reinforcement, moisture protection, foreign object damage protection, and thermal protection to enhance heat transfer away from assembly sub-components, especially those that are critical to the functionality, durability and useful life to the CCAs. A single assembly can require one or multiple processes and can enter the Coating Room multiple times during the production of a circuit card. The type of processes and chemicals the assemblies require depend on the operating environment (i.e., ground, flight, and/or space) of the final assembly product.

The chemicals in the Coating Room are applied manually to the assemblies by Coating Room technicians and have long process times associated with them. More specifically, the chemicals and chemical adhesives must be given time not only to be applied to the assemblies but also to cure and harden after being applied.

#### 1.1.3 Process Characteristics within the Coating Room

#### 1.1.3.1 Batch Processing and Machine Changeovers

CCAs are typically processed in batches based on product type (or, family). A family of CCAs is a group of assemblies that share the same underlying architecture and are closely related in production and process requirements. CCAs of different families cannot be batched and processed together. The size of the batches varies depending upon processing requirements and CCA availability at the time of processing at a particular machine or set of machines.

Batching of assemblies is performed at different process steps and is due to the often long times that occur when changing a machine's current production setup to another. Machine changeover is needed when processing batches of jobs both within a CCA product family and between different CCA product families. As such, there are two types of machine changeovers – minor changeover and major changeover. As a result, there are two types of machine setup times associated with the changeover types. A minor changeover incurs a minor setup time, and a major changeover incurs a major setup time. A minor changeover at a machine takes place between two successive batches of jobs from the same family. Therefore, minor setup times tend

to be relatively short in length. A major changeover at a machine takes place between two successive batches of CCAs from different product families. The major setup time includes the time to clean the machine, to apply electronic devices to the batch of assemblies prior to the use of the new chemicals, and to mix and weigh those chemicals. Therefore, major setup times tend to be significantly longer than minor setup times.

#### 1.1.3.2 <u>Sequence-Dependent Setups</u>

The length of the machine setup times between CCA product families (i.e., major setup times) varies depending upon the sequence in which the product families are processed at the machines. In other words, a machine's setup time for a batch from a particular CCA product family is determined not only by that batch's product family but also by the previous CCA product family for which the machine is currently setup.

#### 1.1.3.3 <u>Disruptions in the Production Schedule</u>

Planned and unplanned disruptions in the MPS occur in the Coating Room and often threaten the on-time delivery of assemblies to the customer. By disruptions, it is meant that the scheduled completion of the CCAs within the Coating Room is delayed due to an expected or unexpected event. As a result, the delivery of the EMAs awaiting the installation of the CCAs is also delayed.

Unplanned disruptions are more commonplace in this particular job shop, and there are two main types of unplanned disruptions in the Coating Room. The first is the unexpected arrival of high priority (or "hot") CCAs to the Room, or the unexpected elevation of priority of CCAs currently in process in the Room.

The second type of unplanned disruption is the availability of the chemicals and chemical adhesives, which have varying shelf lives and varying work lives. The shelf life of a chemical is the length of time that it can remain in its packaging or container before it expires prior to the container and packaging of the chemical being opened and the chemical being mixed. The work life is the amount of time the chemical is usable once it is mixed or once it is out of its container. Each chemical needs to be mixed prior to applying it to assemblies belonging to a family not currently being processed. When the chemicals expire according to the shelf life, the processing of the awaiting CCAs is delayed because the chemicals need to be recertified, in which the shelf life of the unusable chemicals is extended.

#### 1.2 Description of the General Problem

In this section, the shop floor configuration and the general problem that underlie the industrial problem motivating this research investigation, as explained in Section 1.1, is described.

#### 1.2.1 Job and Resource Characteristics

In the fundamental problem, there is an index set **J** of n jobs (i.e.,  $i = \{1, ..., n\}$ ) to be processed through an index set **W** of m workstation resources (i.e.,  $j = \{1, ..., m\}$ ) during a certain planning horizon T.

A job, in this context, refers to a single circuit card assembly unit and is generally referred to as job i. Jobs arrive on a continuous basis to the shop floor during planning horizon T, and each job i has a release date,  $r_i$ , at which the job is initially made available for processing on the shop floor. Each job i has a due date,  $d_i$ , by which the job is due to an internal or external customer and a weight,  $w_i$ , which indicates the priority of the job. Depending upon customer requirements, some jobs have a higher priority than others, and have to meet internal and/or external due dates. It is important to note that the due date  $d_i$  of each job i has a lower bound and upper bound,  $L_i$  and  $U_i$ , respectively. These bounds create a non-relaxable delivery time window for each job.

A workstation resource in this context consists of a single machine or a number of parallel identical machines. The *m* workstations are arranged by function in a low-volume, high-mix job shop. Job shops, by definition, are production systems that are configured by function to produce a number of different job types. Each type has a unique routing and a different processing time on each machine visited.

#### 1.2.2 Processing Characteristics

#### 1.2.2.1 Batching and Incompatible Job families

A machine in the production shop floor underlying the industrial problem processes a number of jobs simultaneously as a batch. Specifically, the jobs traverse the shop floor in transfer batches, and they are processed at the machine individually. A batch consists of a finite number of circuit card assembly units. A batch does not move on to the next station in its routing until all jobs in the batch have been processed.

Batch splitting, where a batch is divided into sub-batches and each sub-batch is process simultaneously across multiple resources, does not occur. In other words, once a batch is formed, it is permanent and is processed as a single unit. Batch preemption, however, does occur. Batch preemption occurs when a single batch is in process at a machine and another batch with higher priority arrives at that machine and interrupts the batch currently in process. After completing the higher priority batch that arrived, the preempted batch resumes processing until it is completed unless another higher priority batch arrives before it completes processing, and so on.

The set **J** of n jobs awaiting processing can be partitioned into F different families and each job within a family f is denoted as job  $i^f$ . The number of jobs in family f is denoted by  $n^f$ . The processing times of all jobs belonging to family f are equal to a common processing time,  $p_j^f$ , for each machine j. It is important to note that the F product families are incompatible, in that jobs from different families cannot be batched together in the same batch. This is due to the

various chemical and chemical adhesive requirements. Therefore, each batch k is made up  $n_k^f$  jobs belonging to a single product family.

Batch sizes within a product family are not fixed and can vary across the different product families. In other words, a batch k of  $n_k^f$  jobs is processed of family f, and a batch l of  $n_l^g$  jobs of another family g can be processed next. Each machine is capable of processing up to  $B_{\max}^f$  jobs from the same family f simultaneously as a batch and each machine can begin processing a batch when there are at least  $B_{\min}^f$  jobs from the same family f available simultaneously at the machine.

The processing time of a batch k is equal to the sum of the processing times of its jobs. More succinctly, the processing time of a batch k is equal to the number of jobs in batch k times the common processing time for the family, i.e.,  $p_k^f = n_k^f \times p_j^f$ .

#### 1.2.2.2 <u>Sequence-Dependent Setup Times</u>

A common machine setup time precedes the processing of the first batch of family g after completing processing of the last batch of family f, and the setup times at the machines are influenced by the sequence in which product families are processed. In other words, the setup time to change over a machine f after processing the last in a sequence of batches of jobs belonging to family f in order to process the first in a sequence of batches of jobs belonging to family g is denoted by  $g_{f}$ . Therefore, the sequence-dependent setup times for the f families can be stored in an f-by-f matrix. Note that the setup time to change over a machine from family g

back to family f can be different. Also, it is important to note that a changeover is needed at a machine j between two batches of the same family, i.e.,  $\forall f: s_{jff} \neq 0$ . In other words, the diagonal entries of the F-by-F matrix of setup times are non-zero.

#### 1.2.2.3 Unplanned Disruptions

There are high priority, or "hot", jobs that arrive unexpectedly to the shop floor. Also, due to the finite work life and finite shelf life of the chemicals and chemical adhesives, the perishability of materials is a prominent feature of the general problem.

First, consider the unexpected arrival of hot jobs during planning horizon T. Upon the arrival of a hot job i to the first machine in its routing, p represents the number of jobs impacted by job i's arrival and need to be rescheduled and these p jobs make up the subset of jobs  $J_i$ , where  $J_i \subset J$ . There is a subset of workstations that process that particular job along its routing and along the routing of the other p jobs that need to be rescheduled. Let q represents the number of workstations to be rescheduled in the subset of workstations  $W_i$  for hot job i and the other p impacted jobs, where  $W_i \subset W$ .

Second, in addition to the unexpected arrival of hot jobs, jobs must arrive to workstations before the expiration of the shelf and work lives of the chemicals required for processing. This expiration time can be represented using a time window at the different workstations in each arriving job's process routing. Therefore, similar to that which is discussed in Section 1.2.3, delivery to each workstation is allowed outside the time window, but at the expense of an

associated penalty. When a job arrives to a workstation before the start of its respective time window for the chemicals results in a penalty, e.g., inventory holding/storage cost. If a job's estimated completion time at a workstation is after its respective time window for the chemicals, this also results in a penalty, e.g., delay cost due to chemical remixing and recertification. However, this penalty is much more severe than that incurred when a job arrives to a workstation before the start of its respective time window, and thus should be avoided.

#### 1.2.3 The Performance Objective

Recall that strict adherence to the fixed Master Production Schedule is necessary for several reasons, and there is a one-week time window during which jobs must be delivered and loaded onto cargo ships. Therefore, it is imperative that all product deliveries arrive on time within the delivery time windows. Delivery is allowed outside the time window, but at the expense of an associated penalty. The process of manufacturing these electro-mechanical assemblies are very lengthy and complex. Completing a job and delivering the job before the start of its respective time window result in a penalty, i.e., inventory holding cost. Delivering a job after its respective time window also results in a penalty, i.e., delay cost or emergency shipping cost. In summary, completing shipments too early or too late is disadvantageous, and no penalty is incurred when a job is completed and delivered during its respective delivery time window. As a result, the performance objective for the general problem is a composition of performance measures  $E_i$  and  $T_i$ , where

$$E_i = \max\{L_i - c_i, 0\} \ i = 1, ..., n, \text{ and}$$

(1.1)

$$T_i = \max\{c_i - U_i, 0\} \ i = 1, ..., n.$$

(1.2)

Hence, the performance objective for the general problem is to minimize

$$Z = \sum_{i=1}^{n} \left( \theta_{1i} E_i + \theta_{2i} T_i \right), \tag{1.3}$$

where  $c_i$  is the actual completion/delivery time of job i,  $\theta_{1i}$  is the cost per unit time of completing job i before the beginning of the delivery time window, and  $\theta_{2i}$  is the cost per unit time of completing job i after the end of the delivery time window.

To summarize, the general problem considered in this research investigation is expressed using the widely adopted three-field scheduling notation  $\alpha \mid \beta \mid \gamma$  (Blazewicz *et al.*, 1996) as Jm |  $r_i$ , batch, prmp,  $s_{ij} \mid \sum_{i=1}^{n} (\theta_{li} E_i + \theta_{2i} T_i)$ .

#### 1.3 Decomposition of the Problem – The Bottleneck

In the industry problem, the overall performance of the Coating Room is greatly inhibited by the bottleneck – the Bonding Station, and approximately 80% of the jobs visit the Bonding Station. Therefore, this research can make inroads to the industry problem by focusing on the effective scheduling of this one workstation, which would, in turn, improve the overall performance of the entire production system.

#### 1.4 Objectives of This Research Investigation

Hence, the primary objectives of this research investigation are to:

- 1. Model the scheduling problem for one workstation in the presence of batching, incompatible job families and sequence-dependent setup times. The definition and modeling of this scheduling problem,  $1 \mid r_i$ , batch,  $s_{ij} \mid \sum_{i=1}^{n} (\theta_{1i} E_i + \theta_{2i} T_i)$ , is a contribution in and of itself. The definition discusses the characteristics and challenges of this interesting problem and the subsequent model of the general problem presents valuable insights to solving it; and

- 2. Develop effective heuristic solution approaches for the  $1 \mid r_i$ , batch,  $s_{ij} \mid \sum_{i=1}^{n} (\theta_{1i}E_i + \theta_{2i}T_i)$ , scheduling problem in the presence of batching, incompatible job families, and sequence-dependent setup times. It is well-known that the single batch resource scheduling problem for all but very few special situations is NP-hard. In other words, a polynomial-time algorithm that solves this problem optimally does not exist. Therefore, researchers and practitioners seek and develop heuristic approaches to address this problem. The proposed solution approaches can serve as the initial effort to address this unique problem and other problems similar in structure.

#### 1.5 Expected Contribution of This Research Investigation

The contribution of this research is two-fold. First, the general scheduling problem underlying the industrial problem motivating this research investigation is known to be NP-hard. Therefore, any effective solution approaches to this problem, not only for some simple, smaller special cases but also for cases that align with more realistically-sized job shop scheduling problems, will contribute significantly to the research body of knowledge in operations/production scheduling. Second, this investigation explores new approaches that should help shop floor production supervisors and managers effectively manage and schedule jobs in order to minimize the deviation of actual job delivery dates from scheduled delivery dates. Further, it should lead to the development of better proactive scheduling policies in job shops where sequence-dependent setups and batching are present.

#### 1.6 <u>Organization of This Document</u>

The remainder of this document is organized as follows. Chapter 2 discusses the previous literature related to the primary areas of this research investigation, which include job shop scheduling, batching with sequence-dependent setups and incompatible job families. An overview of past solution approaches is also presented. Chapter 3 describes the research approach of this investigation in detail. Chapter 4 summarizes the proposed mathematical formulation of the scheduling problem, followed by Chapter 5, which presents the proposed heuristics and the benchmark heuristics to which the proposed heuristics are compared. Chapter 6 summarizes sensitivity analyses, where the weights of the earliness and tardiness measures and

limits of batch sizes are varied. The effects of these changes on the performance of the proposed heuristics and the benchmark heuristics are presented and discussed. This chapter also introduces the use of Order Review and Release strategies. Chapter 7 increases the complexity of the problem formulation by introducing sequence-dependent setups and updates the previous mathematical formulation to include this problem characteristic. Chapter 8 summarizes this research investigation as well as directions for future research.

# CHAPTER 2 REVIEW OF THE EXISTING LITERATURE

#### 2.1 Introduction

This chapter presents a review of the literature covers the job scheduling problem along with various approaches to solve this problem. The chapter is divided into several sections. The first major section summarizes existing literature on job shop scheduling problems. The second section discusses scheduling problems that include the batching of jobs and sequence-dependent setups. The third discusses existing methods for scheduling due to unplanned disturbances in the manufacturing flow. The chapter concludes with a review of the research gaps that are addressed during this investigation.

#### 2.2 <u>Job Shop Scheduling</u>

A job shop is a facility that typically has many product families, but low volumes, and units visit multiple workstations during their production. The job shop scheduling problem is a well-researched problem and has been studied for many decades. One of the first to explore this problem is the research of Balas (1969). As a result, it is impractical to review all the research that addresses the general job shop scheduling problem and its variants. Therefore, the interested reader is encouraged to review the following works, which provide detailed background on this well-studied problem – Mellor (1966), Rodammer and White (1988), Blazewicz et al. (1996), Jain and Meeran (1999), Pinedo (2002), and Parveen and Ullah (2010). It has been concluded in

the open literature that the job shop scheduling problem, even in its simplest form, is proven to be NP-hard and no polynomial-time algorithm exists to solve this problem to optimality (see, for example, Muth and Thompson (1963), Garey et al. (1976), Kan (1976), Sotskov and Shakhlevich (1995)).

#### 2.2.1 Heuristic Approaches to the Job Shop Scheduling Problem

Since the job shop scheduling problem is NP-hard, researchers typically pursue heuristic solution approaches instead of exact approaches. Other heuristic approaches that are applied to the job scheduling problems and perhaps have greater appeal, especially to practitioners, are order review and release (ORR) strategies and dispatching rules. These methodologies are shown to be effective in controlling the amount of work-in-process inventory on the floor as well as provide the best sequencing of jobs with respect to the desired performance criterion or set of criteria (e.g., Philipoom et al. 1993; Sabuncuoglu and Karapinar 2000; Chiang and Fu 2009; Lu et al. 2011).

Job shop scheduling problems involving batching and/or sequence-dependent setups are quite common in scheduling research literature (e.g., Gentile 2009; Vinod and Sridharan 2009; Zhang and Gu 2009). The next section discusses these problem features and methodologies proposed to solve scheduling problems with these features.

#### 2.3 Batching and Sequence-Dependent Setups

There are different approaches in solving scheduling problems when batching and sequence-dependent setups are present. These solution approaches range from exact methodologies to heuristic methodologies. These various solution approaches can be used in order to improve performance metrics such as number of tardy jobs, maximum lateness and deviation from job due dates.

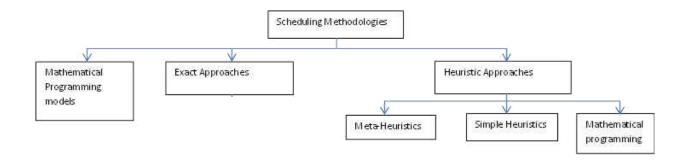

Batching is typically done when machine changeovers (or, setups) are required, in order to improve machine utilization, especially when the machine is a shared resource across product families. One industry in which the use of shared resources is common is the semiconductor manufacturing industry. This is due to the complex nature of the product being manufactured. This environment is similar to the industrial setting motivating this research investigation, with the exception that batch processors in a semiconductor manufacturing environment can process multiple units simultaneously. Scheduling of batch processors in a semiconductor industry has been studied for many years (e.g., Kim et al. 1998, Min and Yih 2003, Mathirajan et al. 2006, Lee et al. 2009, Senties et al. 2009). Mathirajan et al. (2006) identify three primary categories of methods to address these problems: mathematical programming models, exact approaches and heuristic approaches (see Figure 2.1).

Figure 2.1. Summary of existing solution methodologies (modified from Mathirajan et al. 2006).

Many researchers address batch scheduling in other production environments, e.g., the automotive industry (e.g., Gokhale and Mathirajan 2010) and the fruit canning industry (e.g., Parthanadee and Buddhakulsomsiri 2010). These researchers explore different approaches, such as dispatching rules, to address their particular problem in their respective industries.

#### 2.3.1 Exact Approaches

Pott et al. (2000) review batch scheduling and identify past research from Rinnooy Kan (1976) that considers the  $1|s_{ij}|\Sigma C_i$  problem, which is the minimization of total job completion time on a single machine where there are job families and sequence-dependent family setup times. This problem is unary NP-hard for an arbitrary number of product families F. This research is interested in preventing late deliveries, and as a result, one of the objectives of interest is to minimize job maximum lateness, or  $L_{\text{max}}$ .

Solving this problem for an arbitrary number of product families has been found to be NP-hard by Bruno and Downey (1978), and, as a response, Hariri and Potts (1997) develop a

branch and bound algorithm to solve such a problem using the Earliest Due Date (EDD) dispatching rule. A review of Pott et al. (2000) and Cheng et al. (2001) reveals that scheduling with batching is an NP-hard problem, and heuristics are better suited at solving a scheduling problem when batching is present. Cheng et al. (2001) show that single batch processor scheduling problems with multiple product families, setup times, and focusing on due date objectives, such as minimizing maximum lateness, is strongly NP-hard.

## 2.3.2 Heuristic Approaches

Given the computational complexity results of the batch scheduling problem, researchers, such as Mathirajan and Sivakkumar (2006), Geiger and Uzsoy (2008), Gokhale et al. (2010), explore the effects batching have on scheduling. Geiger and Uzsoy (2008) extend their previous work Geiger et al. (2006) of utilizing a bio-inspired genetic learning approach and apply it to more complex batch processing environments. They are able to evaluate this approach over a range of single batch processor scheduling problems under different production conditions to identify the robustness and performance of their proposed learning approach against other known heuristics such as Greedy Earliest Due Date (GREDD) (Uzsoy 1995) and Batch Apparent Tardiness Cost (BATC) (Mehta and Uzsoy 1998).

Gokhale et al. (2010) look at the problem of scheduling a batch processor in presence of unequal release times, incompatible job families and non-identical job sizes with job splitting to minimize the total weighted tardiness. The batch processor can process multiple compatible jobs at one time. The focus of their research is on the bottleneck of an automobile gear manufacturer.

In order to solve this problem, Gokhale et al. (2010) develop three heuristic algorithms (HAs): Weighted tardiness based HA, Weighted job score based HA, and Weighted family score and job score based HA. All three heuristics are tested on smaller-sized problems and then later on larger problems, and prove to be relatively effective.

Another approach to solving scheduling problems with batching is with the use of order review and release (ORR) strategies and dispatching rules. The combination of these two scheduling strategies have been shown to be effective in reducing work-in-process (WIP) inventory in order to improve the overall performance of the shop floor (e.g., Gronalt 2002 and Gentile 2009).

Batch preemption can occur when a machine is processing a job of an in-process batch and that processing is often interrupted by a batch (or single job) of higher priority. That machine then processes the interrupting higher priority batch (or single job) to completion, then resumes processing the previously interrupted job and completes the in-process batch. An assumption of many researchers used to solve scheduling problems is to not allow batch or machine preemptions (e.g., Mathirajan 2006, Chiang and Fu 2007, Geiger and Uzsoy 2008, Gokhale and Mathirajan 2010). Scheduling problems in which batch preemption occurs is NP-hard when the number of machines m is 2 (Monma and Potts 1993). Therefore, heuristic approaches are appropriate when solving batch scheduling problems with preemption.

## 2.3.3 Sequence-Dependent Setups

Zhu and Wilhelm (2005) summarize recent results in the existing literature for scheduling problems with sequence-dependent setups. Most research considers the reduction of setup costs and inventory holding costs. This research shows that any scheduling problem that has sequence-dependent setups any performance objective (e.g., minimize makespan, minimize total flow time, minimize maximum lateness, etc.) is NP-hard (see, for example, Monma and Potts 1989, Ghosh 1994, Pinedo 2002). As a result, even though some researchers have pursued exact approaches for simplified versions of scheduling problems with sequence-dependent setups, more commonly, heuristic solution approaches have been developed in order to address problems with sequence-dependent setups, including genetic algorithms, dispatching rules and simulation, to name a few.

## 2.3.3.1 Exact Approaches

A scheduling problem involving sequence-dependent setups is well-known to be similar to that of the Traveling Salesperson problem (TSP), which is known in literature to be NP-hard (see, for example, Kan 1976, Pinedo 2002, Zhu and Wilhlem 2006). The traveling salesperson problem is a widely-studied mathematical problem for which the ultimate goal is to find the optimal path given a set of distances. This problem has been applied to many other fields such as logistics, planning and manufacturing. A literature review by Allahverdi et al. (2008) shows that scheduling problems, with sequence-dependent setups, regardless if there is or isn't batching, are NP-hard.

## 2.3.3.2 <u>Heuristic Approaches</u>

Mathematical programming models, simulation models and metamodels, etc. all have been used to address scheduling problems in various environments (e.g., Ruiz 2008, Vinod and Sridharan 2009, Salmas et al. 2010, Fernandes et al. 2011).

Various heuristic scheduling approaches have been used and tested in order to improve shop floor performance. One of these approaches is the Similar Setup (SIMSET) rule (Vinod and Sridharan 2009, Fernandes et al. 2011), which has proven to be effective especially in the case of sequence-dependent setups.

Another popular strategy for solving scheduling problems with sequence-dependent setups is the integration of both order review and release (ORR) strategies and dispatching rules. Missbauer (1996), Lee (1997) and Gentile (2008) evaluate the performance of these strategies in a job shop and show the effectiveness of these strategies in reducing production costs and reducing work-in-process inventory. Missbauer (1996) create an analytical model as well as a simulation model. The author tests and analyzes the performance of these rules and determines the most suitable combination of ORR strategies and dispatching rules.

### 2.4 Unplanned Disruptions

In a manufacturing environment, it is often difficult to plan or predict the performance of the manufacturing system due to random disturbances, which can alter the originally intended schedule. Many theories have been suggested to identify the best planning strategies and identify when there are dangers of missed deliveries. One of the planning strategies that can be utilized is dispatching rules.

Dispatching rules identify priorities of jobs waiting to be processed on a machine and can be based on various criteria. New research has suggested using simulation in order to select dispatching rules as the manufacturing conditions change (e.g., disruptions occur, unanticipated orders arrive, etc.). Interruptions such as machine failures, process yield and rework are some issues that impact the dispatching rules in the study performed by Min and Yih (2003). Their objective is to utilize scheduling rules to minimize work-in-process inventory, improve throughput. They researchers develop a simulation-based scheduler that provides real-time dispatching decisions.

A successful approach to dealing with unexpected changes in the system is to modify dispatching rules in real-time (e.g., Jeong and Kim 1998, Wu et al. 1999, Min and Yih 2003, Parthanadee and Buddhakulsomsiri 2010). Parthanadee and Buddhakulsomsiri (2010) successfully apply dispatching rules to a fruit canning facility's bottleneck. The desired outcomes of Parthanadee and Buddhakulsomsiri (2010)'s research are to:

- 1. identify the dispatching rules for scheduling, which are performed real-time;

- 2. use simulation modeling to analyze the dispatching rule performance.

Dynamically changing dispatching rules to account for these unforeseen changes, such as variable job arrival patterns, urgent jobs, or unplanned machine downtime, has been studied throughout the years (e.g., Jeong and Kim 1998, Min and Yih 2003, Upsani and Uzsoy 2008). For each significant disruption, the dispatching rules are analyzed and the best fit is selected.

Some authors' works involve testing different rules in order to determine the rules that provide the best performance (e.g., Joeng and Kim 1998). Other authors propose a more complex solution in which dispatching rules are adjusted in order to meet pre-determined acceptable levels in the performance metrics (e.g., Min and Yih 2003). Upsani and Uzsoy (2008) focus on how the dispatching rules impact the lateness of the product. Ishii and Talavage (1991) use simulation to analyze dispatching rules to identify the rule that provides the best solution to reduce work-in-process inventory, reduce costs and improve profit in a flexible manufacturing system. The authors assert that a dispatching rule selected at different periods in time greatly improves production performance. They assert that no one dispatching rule produces optimal performance in all cases.

## 2.5 Minimizing the Earliness and Tardiness Performance Objectives

#### 2.5.1 Approaches for Minimizing Tardiness

It is reported that the single machine total tardiness problem is NP-hard in the ordinary sense, and its weighted counterpart is NP-hard in the strong sense (Pinedo 2002). As the tardiness problem increases in complexity, the tractability of the problem does not improve. Therefore, researchers and practitioners pursue approximate approaches to address this performance objective.

A successful and popular heuristic approach to addressing the tardiness objective is the Apparent Tardiness Cost (ATC) sequencing heuristic proposed by Rachamadugu and Morton

(1981). ATC calculates an index value for each job i in a set of jobs to be processed and arranges those jobs in decreasing order ATC index value. ATC works in a similar fashion as the weighted shortest processing time dispatching rule that processes a set of jobs in increasing order of the  $w_i$  /  $p_i$  index value, where  $w_i$  is the weight (or importance) of job i and  $p_i$  is the processing time of job i. However, ATC considers the "apparent cost" of the remaining jobs awaiting processing and scales the slack in accordance with the remaining number of competing jobs awaiting processing. The calculation of the ATC index value for job i is as follows:

$$ATC(i) = \frac{w_i}{p_i} \exp\left(-\left[\frac{[d_i - p_i - t]^+}{kp}\right]\right)$$

(2.1)

where:

$p_i$  processing time for job i

$d_i$  due date for job i

p average processing time of the waiting jobs

$w_i$  weight of job i

k look-ahead parameter (user-defined for the problem at hand)

The k parameter is a look-ahead parameter related to the number of competing jobs, and k is a decision parameter whose specific value is determined by the user for the scheduling problem at hand. Appropriate values of the k-value range from  $1.5 \le k \le 4.5$ , according to the empirical analyses of Ow (1985) and Rachamadugu (1982).

Vepsalainen and Morton (1987) evaluate the ATC rule against several standard rules including First Come First Serve (FCFS), Earliest Due Date (EDD), Slack per Remaining

Processing Time (S/RPT), Weighted Shortest Processing Time (WSPT), and Weighted Cost over Time (COVERT), in a job shop environment with 10 machines and jobs arriving at a continuous Poisson arrival rate. ATC is shown to outperform the standard rules and the COVERT dispatching rule. In fact, Rachamadugu and Morton (1981) and Vepsalainen and Morton (1987) find that ATC outperforms several other heuristics for the tardiness and weighted tardiness objectives. It is found to generate near-optimal performance for single machine scheduling problems when tardiness and weighted tardiness are the performance objectives.

#### 2.5.2 Approaches for Minimizing Earliness-Tardiness

Baker and Scudder (1990) discuss that there are several formulations of the earliness-tardiness scheduling problem. One formulation is that jobs have a common due date (see, for example, Gordon et al. 2002). Another formulation is that each job has a distinct due date, which is a generalization of the previous formulation. Yet, another formulation of the earliness-tardiness scheduling problem is to derive a due date that will ultimately help to optimize the sequence of jobs with respect to both objectives simultaneously. Each of these types of problems requires different solutions approaches in order to minimize earliness-tardiness.

For instance, Wan and Yen (2002) develop a tabu search method for the single machine problem with individual jobs having distinct due dates, and jobs are assumed to be all available at time t = 0. In order to consider the earliness portion of the objective, they allow for idle time to be inserted into the master production schedule. Their problem allows for time windows in which the job due dates fall. Batching, incompatible job families, sequence-dependent setups are

not considered. The authors' solution to this problem involves two algorithms: optimal timing and optimal sequencing. The optimal timing algorithm identifies the best completion time that corresponds to a particular job's due window. Forced idle time is inserted and jobs are shifted in order for their completion time to fall within their respective time windows.

Mazzini and Armentano (2001) approach the problem by proposing a heuristic in which idle times are inserted during the construction of the schedule rather than determining a schedule using a priority rule and then inserting idle times in order to optimize the schedule. The authors are able to compare the results of the heuristic against optimal solutions but only for 12 jobs or less. The authors show that it is computationally-expensive to reach a solution for more than 12 jobs. Therefore, their heuristic is compared to other known heuristic priority rules for problems greater than 12 jobs. Their results suggest that, if the job is going to be inevitably tardy, then the job would start at its ready time  $r_i$ ; however, if the job is early, the start would be the difference between the due date  $d_i$  and its processing time  $p_i$ . After the start time  $s_i$  is determined for each job i, the heuristic looks to see if any jobs have overlapping times, in which the feasibility procedure of their heuristic shifts jobs either to the left or to the right to ensure no overlapping and reduce overall earliness-tardiness. Their heuristic performs well when compared to the optimal solution and a benchmark set of standard heuristic priority rules.

Rabadi et al. (2004), Rabadi et al. (2006), and Sourd (2005) all address scheduling problems with sequence-dependent setups. Both the research of Rabadi et al. (2004) and Sourd (2005) focuses on a scheduling problem with one machine and no preemptions; however, Rabadi et al. (2004) assumes one common due date for all jobs and attempts to minimize the total

amount of earliness and tardiness, while Sourd (2005) assigns each job a due date and works to minimize earliness-tardiness and setup costs. Rabadi et al. (2004) attempts to minimize overall earliness and tardiness by scheduling jobs using the longest processing time first (to minimize earliness) until the due date is approached. Once jobs are considered tardy, shortest processing time is used to schedule the remaining jobs in order to minimize tardiness. In order to make the scheduling problem more manageable, Rabadi et al. (2004) sum the processing and setup times in a matrix as the adjusted processing time or  $AP_{ij}$ , where  $AP_{ij} = S_{ij} + P_{j}$ . The authors utilize a branch and bound algorithm and compare their solutions to those generated from a mixed integer programming (MIP) model by proposed by Coleman (1992). Sourd (2005) use a similar approach in that a MIP model is formulated, and then use a branch and bound algorithm approach to solve the MIP. Sourd (2005) also proposes a heuristic to solve the problem, and the solutions generated by the proposed heuristic are compared to those generated from the branch and bound algorithm. It is found that the branch and bound algorithm performs well; however, it is only suitable when the number of jobs is limited to less than 20. For larger-scale scheduling problems where the number of jobs is greater than or equal to 20, the heuristic approach is more suitable.

## 2.6 Summary

As concluded by most researchers in the existing literature, job shop scheduling problems in which batching and sequence-dependent setups are present are NP-hard. Therefore, in order to provide a solution to this problem, heuristic solution methods are pursued. There are many solution approaches to preventing late deliveries to customers considering some of these problem characteristics. However, currently there is no research regarding the scheduling problem encompasses all of these problem characteristics as described and defined in Section 1.2.

## CHAPTER 3 : RESEARCH APPROACH

### 3.1 Introduction

Job shop scheduling with batching, incompatible job families, and sequence-dependent setups have all been addressed independently or in some combination. However, the open literature shows that there is no current work that identifies a methodology to solve the problem when all three features are present simultaneously and while minimizing both earliness and tardiness. As a result of the computational complexity results for this (and variants of this) problem, heuristics are the desired approach to solve this problem.

Recall that an objective of this research investigation is to formulate a special case of the general problem. Specifically, this research focuses on the effective scheduling of the bottleneck workstation, which would, in turn, improve the overall performance of the entire production system. In order to do this, the general multi-workstation problem is simplified through a series of assumptions that are systematically relaxed in a three-phased approach. The final phase involves modeling the problem  $1 \mid r_i$ , batch,  $s_{ij} \mid \sum (\theta_1 E_i + \theta_2 T_i)$ . The following three sections detail the relevant assumptions of each phase.

## 3.2 <u>Phase 1: Single Batch Workstation with Sequence-Independent Setups and Equal Job Weights</u>

Phase 1 of this research involves the following problem with the simplifying assumptions.

- The number of workstations m is 1, i.e.,  $|\mathbf{W}| = 1$ ;

- The number of machines in the workstation is 1;

- The number of jobs n arrives individually to the workstation and are placed in batches before being processed;

- There is no restriction on queue length for jobs and batches awaiting processing at the workstation;

- Jobs within a batch are processed one at a time at the workstation;

- Jobs depart the workstation in batches;

- No batch preemption. Once a batch has begun processing at a workstation, it cannot be

interrupted due to the arrival of higher priority jobs (or batches of jobs) before the

processing of that batch has been completed;

- No batch splitting. Once a batch has been created, it cannot be divided into smaller subbatches of jobs. It is treated as a single entity;

- Incompatible job families. Jobs from different families cannot be processed together in the same batch;

- Machine setups occur between processing batches of jobs, regardless of the job family process prior; in other words, a machine's setup time for a batch from a family is

determined by that batch's product family not by the previous family for which the machine is currently setup, i.e., machine setups are batch sequence-independent; and

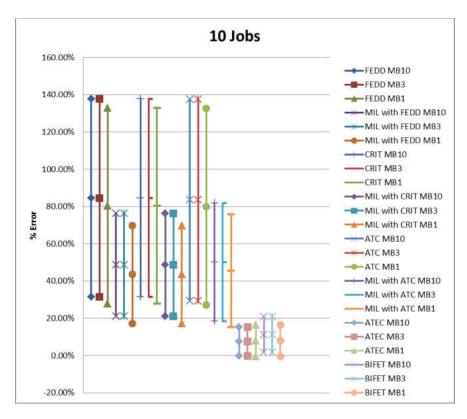

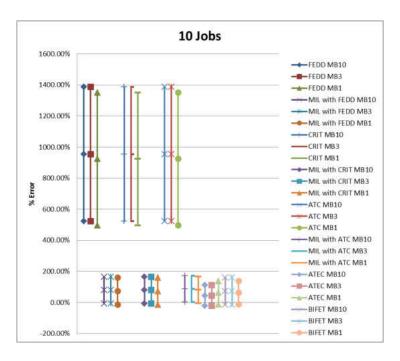

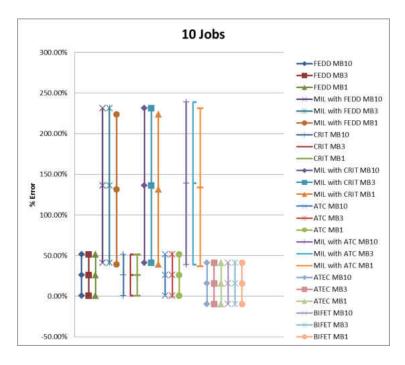

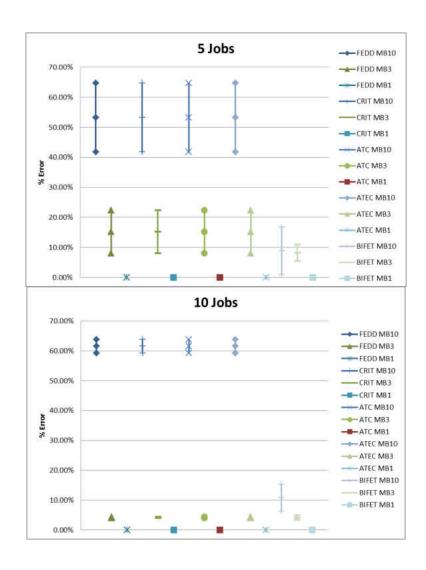

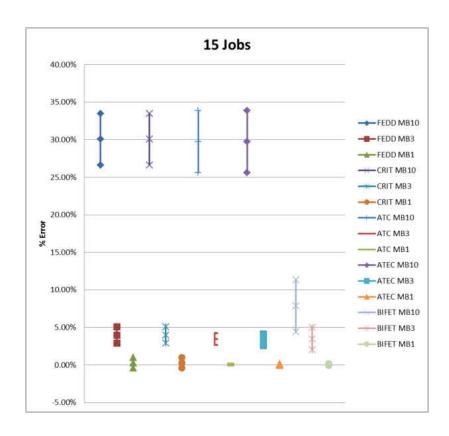

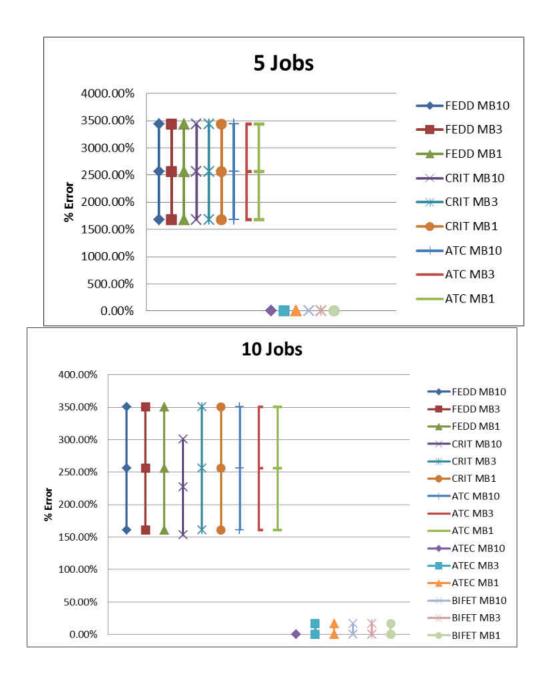

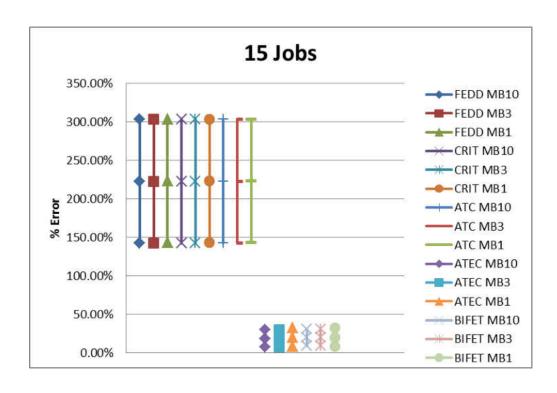

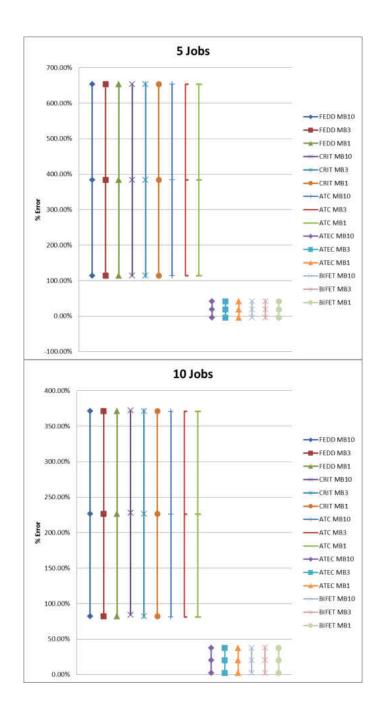

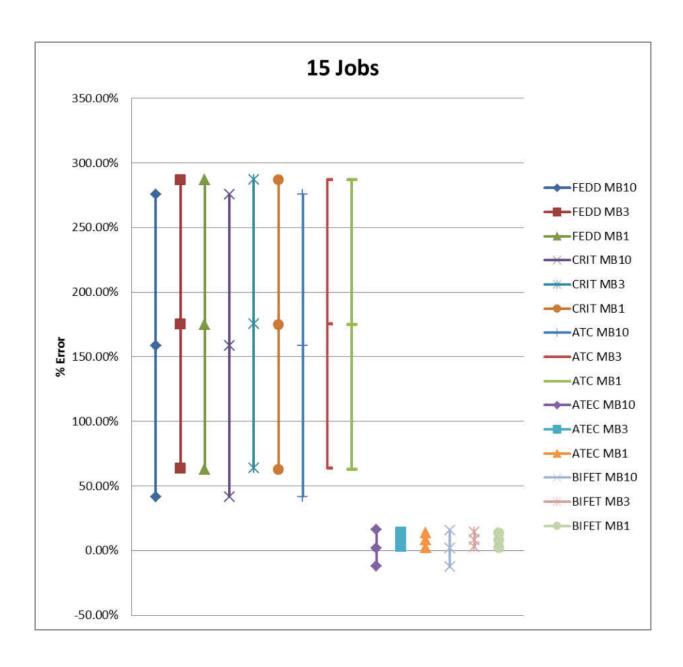

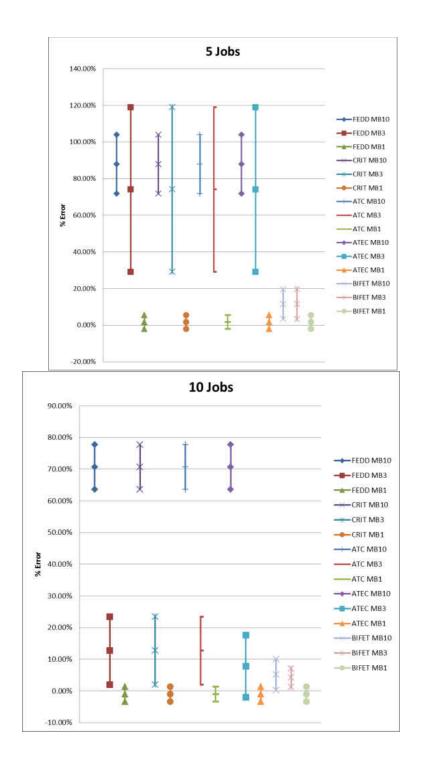

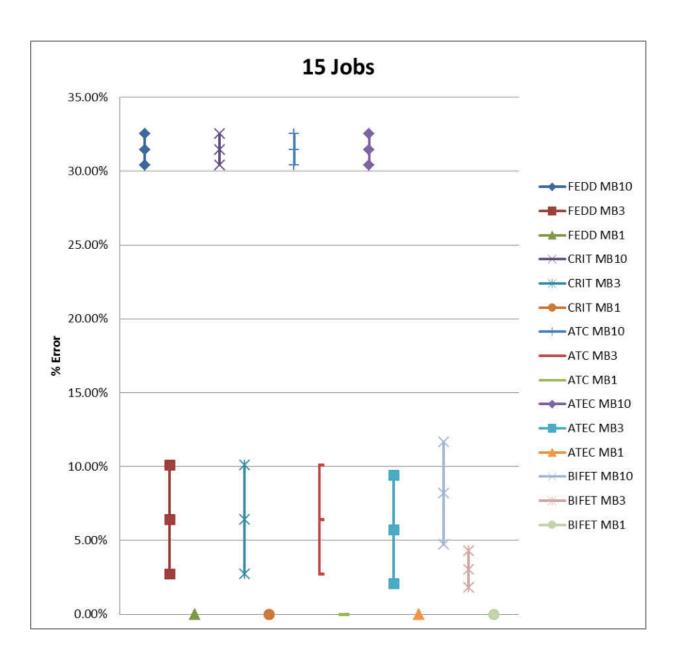

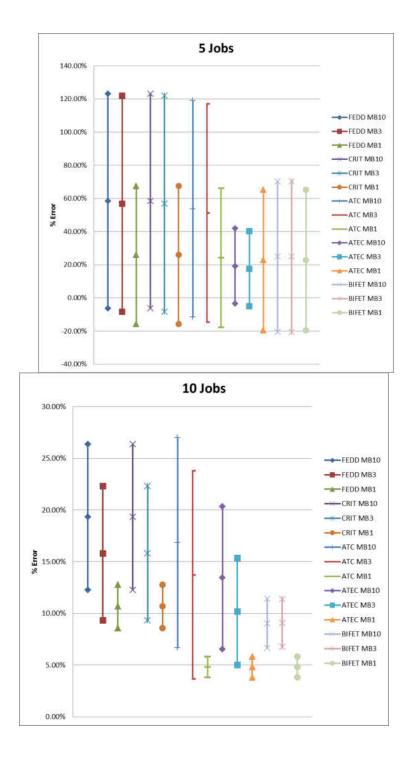

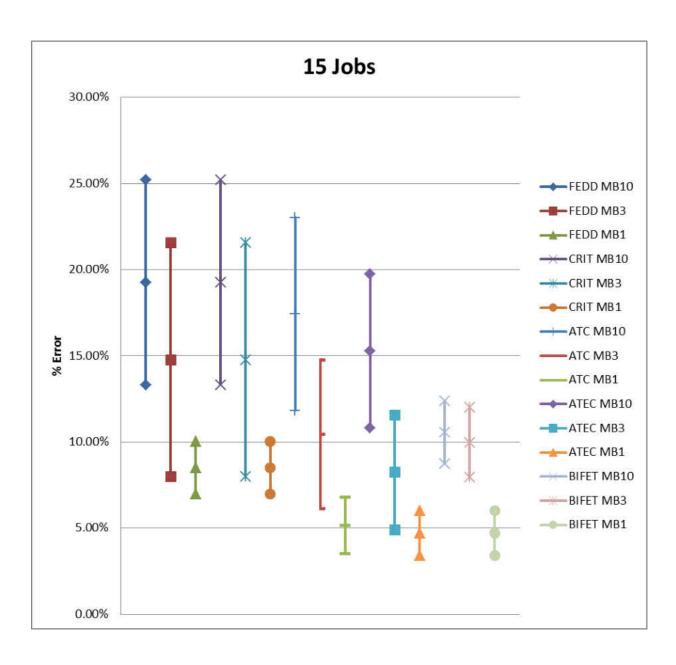

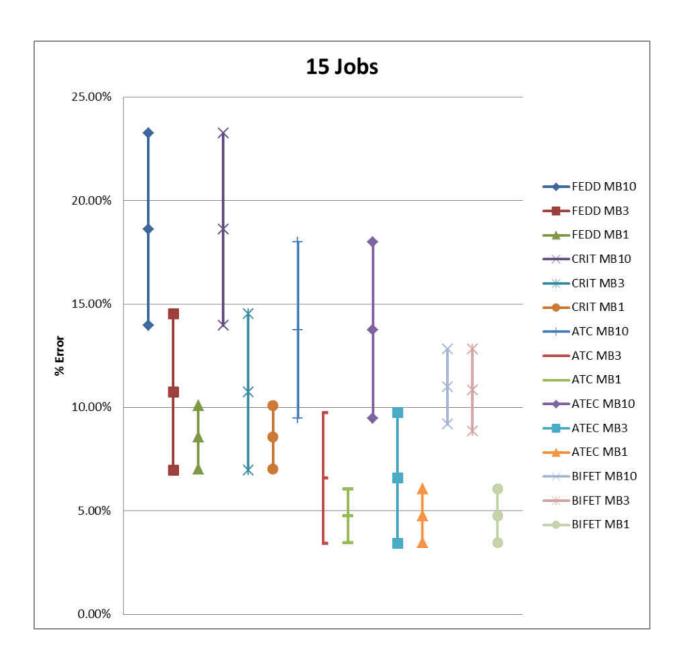

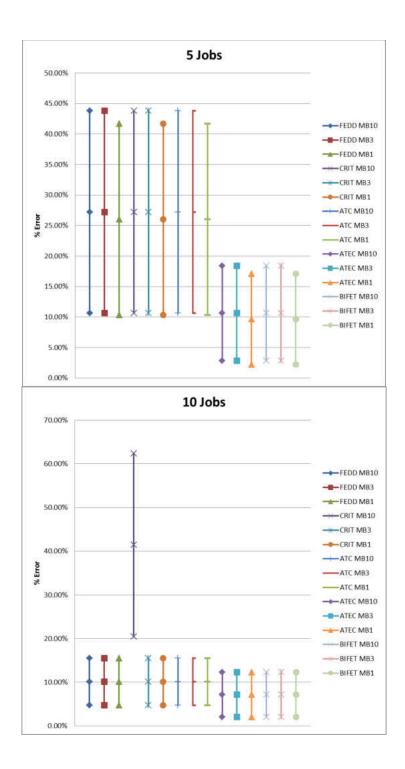

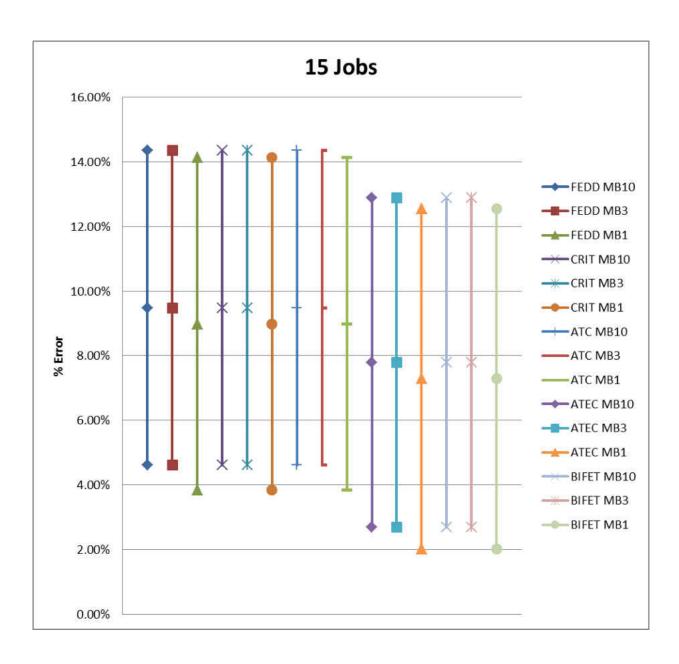

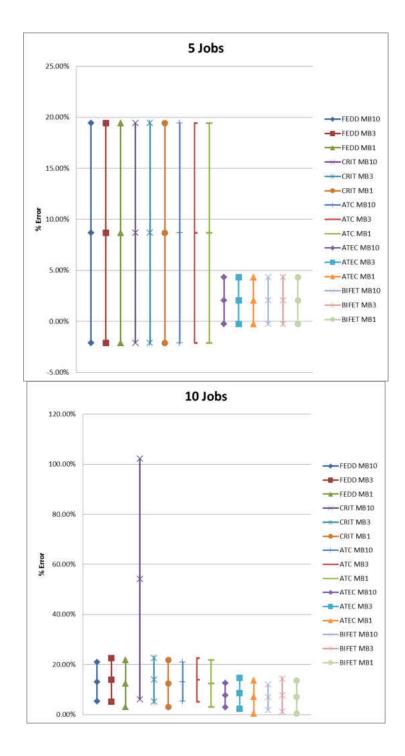

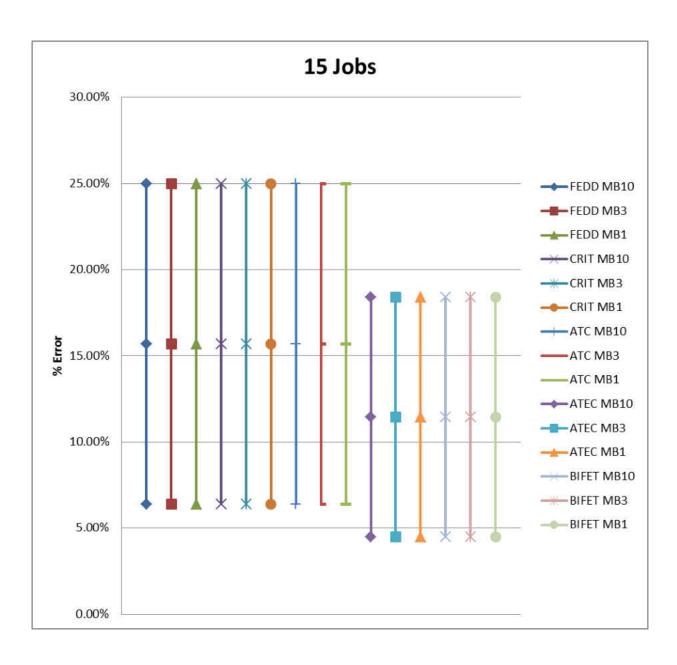

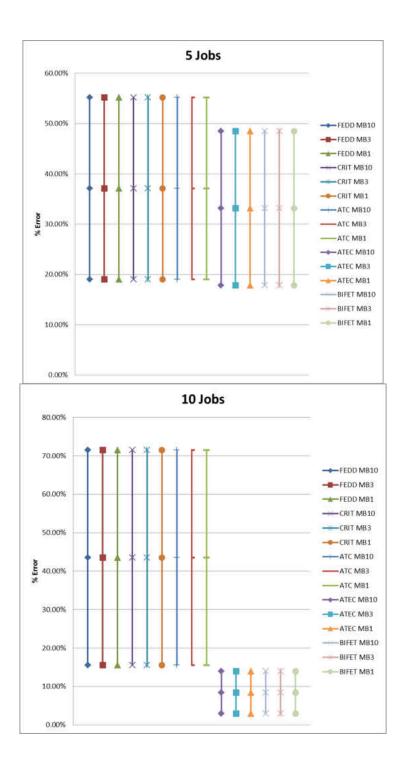

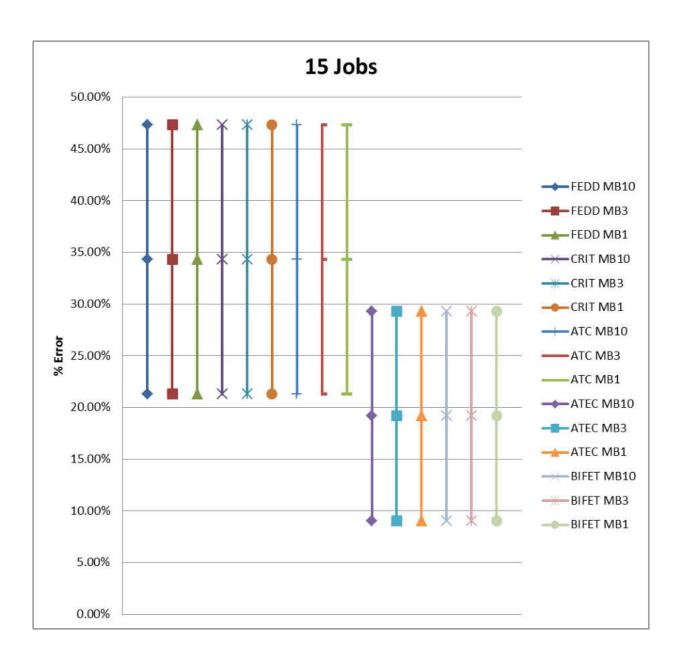

The earliness penalty per unit time per job and the tardiness penalty per unit time per job are equal.