Electronic Theses and Dissertations, 2004-2019

2014

# Investigation of Dual-Stage High Efficiency and Density Micro Inverter for Solar Application

Lin Chen University of Central Florida

Part of the Electrical and Electronics Commons

Find similar works at: https://stars.library.ucf.edu/etd University of Central Florida Libraries http://library.ucf.edu

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations, 2004-2019 by an authorized administrator of STARS. For more information, please contact STARS@ucf.edu.

#### **STARS Citation**

Chen, Lin, "Investigation of Dual-Stage High Efficiency and Density Micro Inverter for Solar Application" (2014). *Electronic Theses and Dissertations, 2004-2019*. 4657. https://stars.library.ucf.edu/etd/4657

# INVESTIGATION OF DUAL-STAGE HIGH EFFICIENCY &DENSITY MICRO INVERTER FOR SOLAR APPLICATION

by

LIN CHEN B.S. TONGJI University, 1999

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical Engineering and Computer Science in the College of Engineering and Computer Science at the University of Central Florida

Orlando, Florida

Spring Term 2014

Major Professor: Issa Batarseh

© 2014 Lin Chen

#### **ABSTRACT**

Module integrated converters (MIC), also called micro inverter, in single phase have witnessed recent market success due to unique features (1) improved energy harvest, (2) improved system efficiency, (3) lower installation costs, (4) plug-N-play operation, (5) and enhanced flexibility and modularity. The MIC sector has grown from a niche market to mainstream, especially in the United States. Due to the fact that two-stage architecture is commonly used for single phase MIC application. A DC-DC stage with maximum power point tracking to boost the output voltage of the Photovoltaic (PV) panel is employed in the first stage, DC-AC stage is used for use to connect the grid or the residential application. As well known, the cost of MIC is key issue compared to convention PV system, such as the architecture: string inverter or central inverter. A high efficiency and density DC-DC converter is proposed and dedicated for MIC application. Assuming further expansion of the MIC market, this dissertation presents the micro-inverter concept incorporated in large size PV installations such as MW-class solar farms where a three phase AC connection is employed. A high efficiency three phase MIC with two-stage ZVS operation for grid tied photovoltaic system is proposed which will reduce cost per watt, improve reliability, and increase scalability of MW-class solar farms through the development of new solar farm system architectures. This dissertation presents modeling and triple-loop control for a high efficiency three-phase four-wire inverter for use in grid-connected two-stage micro inverter applications. An average signal model based on a synchronous rotation frame for a three-phase four-wire inverter has been developed. The inner current loop consists of a variable frequency bidirectional current mode (VFBCM) controller which regulates output filter inductor current thereby achieving ZVS, improved system response, and reduced grid current THD. Active

damping of the LCL output filter using filter inductor current feedback is discussed along with small signal modeling of the proposed control method.

Since the DC-link capacitor plays a critical role in two-stage micro inverter applications, a DC-link controller is implemented outside of the two current control loops to keep the bus voltage constant. In the end, simulation and experimental results from a 400 watt prototype are presented to verify the validity of the theoretical analysis.

#### **ACKNOWLEDGMENTS**

I would like to express my sincere gratitude to my advisors Dr. Issa Batarseh for their tremendous supports and continuous inspirations to my research works throughout my Ph.D. studies. What I have learned from him is not only the spirit of doing research but also the ability to think independently. I would also like to thank Dr. Nasser Kutkut for his precious and patient guidance during his supervision of Florida Energy Systems Consortium (FESC) in UCF. I am greatly grateful for my other dissertation committee members, Dr. Thomas Xinzhang Wu, Dr. Wasfy Mikhael and Dr. Aman Behal for their valuable guidance and kind suggestions.

I would like to express my deep appreciation to Mr. Chalres Jourdan, who kindly gave me insightful suggestions for my academic research, and carefully edited my transactions on power electronics.

It is a great honor for me to be part of the Florida Power Electronics Center (FPEC) at the University of Central Florida. My study and research life in FPEC was full of joy and hard work, which is an unforgettable and precious memory to me. I would like to thank all my fellow colleagues for the inspiration and the support. I especially appreciate the generous help from Dr. Haibing Hu, Dr. Qiang Zhang and Dr. Changsheng Hu.

In the end, many appreciations are also for my family. It is a given that without the sacrifices and support of my father and mother, I would never have started on this path I am finishing with this work.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                                                  | viii |

|------------------------------------------------------------------------------------------------------------------|------|

| LIST OF TABLES                                                                                                   | x    |

| CHAPTER ONE: INTRODUCTION                                                                                        | 1    |

| 1.1 Background and Challenges                                                                                    | 1    |

| 1.2 Objectives and Outline                                                                                       | 8    |

| CHAPTER TWO: DC-DC STAGE CONVERTER                                                                               | 10   |

| 2.1 Background and Motivation.                                                                                   | 10   |

| 2.2 Principle of Operation                                                                                       | 14   |

| 2.3 BMFFC Steady State Analysis                                                                                  | 26   |

| 2.4 ZVS Condition Discussion                                                                                     | 30   |

| 2.5 Design Guidelines                                                                                            | 38   |

| 2.5.1 Design of Turns Ratio of the Transformer (N <sub>2</sub> /N <sub>1</sub> &N <sub>3</sub> /N <sub>1</sub> ) | 38   |

| $2.5.2$ Design of the Magnetizing Inductance $L_{\rm m}$ , and Output Inductance $L_{\rm l}$                     | 39   |

| 2.5.3 Design of the Resonant Components in Snubber Circuit, C <sub>sb</sub> and L <sub>sb</sub>                  | 40   |

| 2.5.4 Design of the Output Capacitor C <sub>2</sub>                                                              | 41   |

| 2.6 Experimental Results Verification                                                                            | 44   |

| 2.7 Summary                                                                                                      | 58   |

| CHAPTER THREE: DC-AC STAGE CONVERTER                                                                             | 59   |

| 3.1 Introduction                                                                                                 | 59   |

| 3.2 Operation principle                                                                                          | 60   |

| 3.3 Modeling of three-phase four-wire grid-connected inverter                                                    | 62   |

| 3.4 Small signal model                                                                                           | 64   |

| CHAPTER FOUR: CONTROL DESIGN OF DC/AC STAGE                                                                      | 67   |

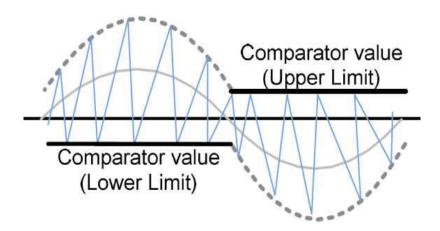

| 4.1 Inner current loop control of the inverter side inductor                                                     | 69   |

| 4.1.1 Implementation of the VFBCMC                                                                               | 69   |

| 4.1.2 Small signal modeling of the VFBCMC for one phase of the half bridge inverter                              | 72   |

| 4.1.3 Complete Model with VFBCMC for one Inverter Phase                                                          | 79   |

| 4.2 Controller design of the grid current loop                                                                   | 80   |

| 4.3 Controller Design of the Bus Voltage Loop            | 83  |

|----------------------------------------------------------|-----|

| CHAPTER FIVE: PARAMETERS CALCULATION OF PASSIVE COMPON   | 85  |

| 5.1 DC-Link Capacitance Calculation                      | 85  |

| 5.2 Input Capacitance Calculation for LLC Resonant Stage | 88  |

| CHAPTER SIX: SIMULATION & EXPERIMENTAL RESULTS           | 91  |

| 6.1 Simulation results                                   | 91  |

| 6.2 Experimental results                                 | 92  |

| CHAPTER SEVEN: CONCLUSIONS AND FUTURE WORK               | 99  |

| 7.1 Conclusions                                          | 99  |

| 7.2 Future work                                          | 100 |

| LIST OF PUBLICATIONS                                     | 101 |

| LIST OF REFERENCES                                       | 104 |

# LIST OF FIGURES

| Figure 1.1 A typical PV system configuration for appliances [1]                                                                        | 1    |

|----------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.2 Diagram of central inverter architecture                                                                                    | 2    |

| Figure 1.3 Diagram of string inverter based architecture                                                                               | 3    |

| Figure 1.4 Maximum power tracking for each panel                                                                                       | 4    |

| Figure 1.5 Configuration of micro-inverter for solar application                                                                       | 4    |

| Figure 1.6 Three-phase micro-inverter based architecture for solar farm                                                                |      |

| Figure 2.1 Simplified block diagram of two-stage MIC                                                                                   |      |

| Figure 2.2 BMFFC with efficient active LC snubber circuit                                                                              |      |

| Figure 2.3 Operational intervals of ZVS Forward Flyback converter. (Interval 1) [t0-t1]. (Interval 2) [t1-t2]. (Interval 2)            | rval |

| 3) [t2-t3]. (Interval 4) [t3-t4]. (Interval 5) [t4-t5]. (Interval 6) [t5-t6]. (Interval 7) [t6-t7]. (Interval 8) [t7-t8]. (Interval 7) |      |

| 9) [t8-t0]                                                                                                                             |      |

| Figure 2.4 Theoretical waveforms of the BMFFC with efficient LC snubber circuit                                                        |      |

| Figure 2.5 Continuous conduction mode CCM/DCM operation region of BMFFC                                                                |      |

| Figure 2.6 DC gain of BMFFC as a function of duty ratio                                                                                |      |

| Figure 2.7 DC gain of BMFFC as a function of load                                                                                      |      |

| Figure 2.8 Key waveforms of BMFFC during off time                                                                                      |      |

| Figure 2.9 ZVS condition as a function of the input voltage and turns ratio (N3/N1)                                                    |      |

| Figure 2.10 Three-Dimensional plot of the ratio $\lambda$ (L1/Lm)                                                                      |      |

| Figure 2.11 The ratio $\lambda$ (L1/Lm) as a function of input voltage and turns ratio N (N2/N1)                                       |      |

| Figure 2.12 Voltage and current ripple in the output capacitor                                                                         |      |

| Figure 2.13 Photograph of the hardware prototype of BMFCC with 200W                                                                    |      |

| Figure 2.14 Measured waveforms of the BMFFC at 200W with 25V input                                                                     |      |

| Figure 2.15 Measured waveforms of the BMFFC with 200W output and 50V input                                                             |      |

| Figure 2.16 Measured waveforms of the BMFFC with 20W output and 25V input                                                              |      |

| Figure 2.17 Measured waveforms of the BMFFC at 20W with 50V input                                                                      |      |

| Figure 2.18 Measured waveforms of the BMFFC at 60W with 43V input                                                                      |      |

| Figure 2.19 Measured waveforms of an efficient active LC snubber circuit                                                               |      |

| Figure 2.20 Sum of output current from Forward and Flyback sections                                                                    |      |

| Figure 2.21 Transformer construction of BMFFC                                                                                          |      |

| Figure 2.22 Measured efficiency of BMFFC according to the variation of the input voltage and output power                              |      |

| Figure 2.23 Measured efficiency of BMFFC according to the variation of the input voltage and output power                              |      |

| Figure 2.24 Measured waveforms of the BMFFC without LC snubber circuit at 200W with 25V                                                |      |

| Figure 2.25 Efficiency comparison (with/without snubber circuit) with different output power at 25V input                              |      |

| Figure 2.26 Transformer construction of QRFC (Np=6 Parallel in primary, Ns=36 series connection in secondary                           | _    |

| Figure 2.27 Efficiency comparison with different output power between BMFFC and QRFC at 35V                                            |      |

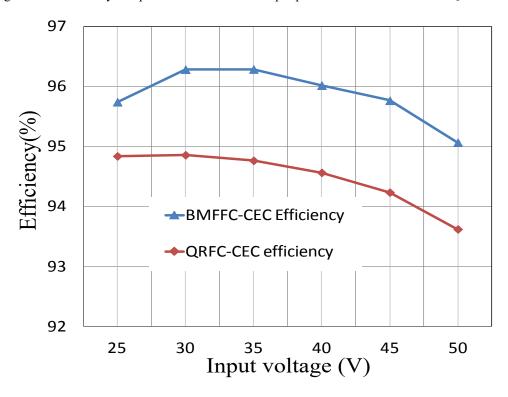

| Figure 2.28 BMFFC CEC weight efficiency comparison with QRFC                                                                           |      |

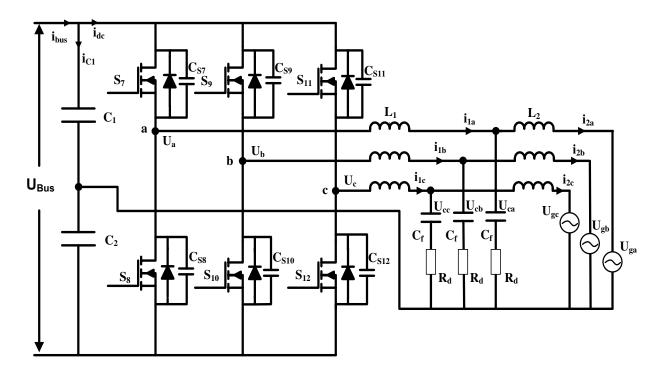

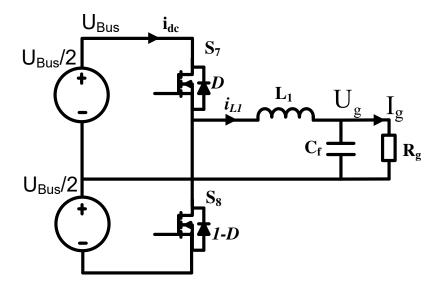

| Figure 3.1 Three-phase four-wire DC/AC grid-connected converter                                                                        |      |

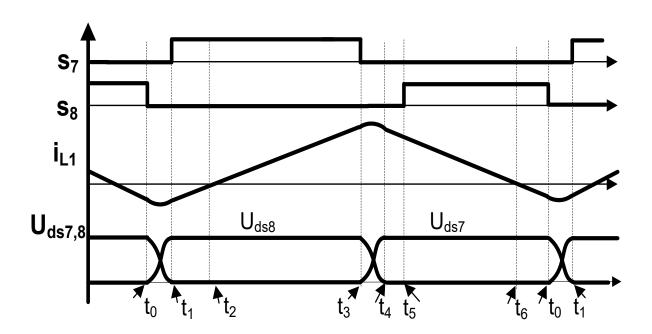

| Figure 3.2 Theoretic Waveforms and Operating Intervals of a Single Phase DC/AC Converter                                               |      |

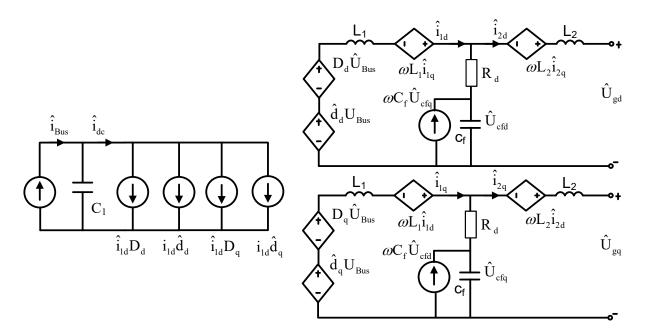

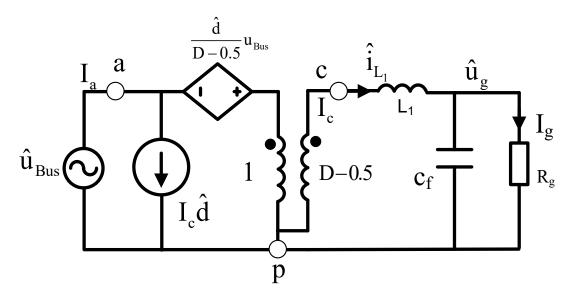

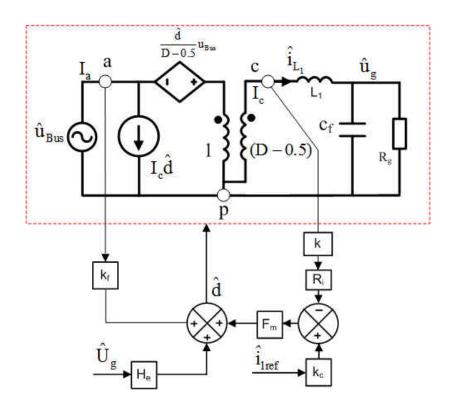

| Figure 3.3 Equivalent circuit based on small signal modeling                                                                           |      |

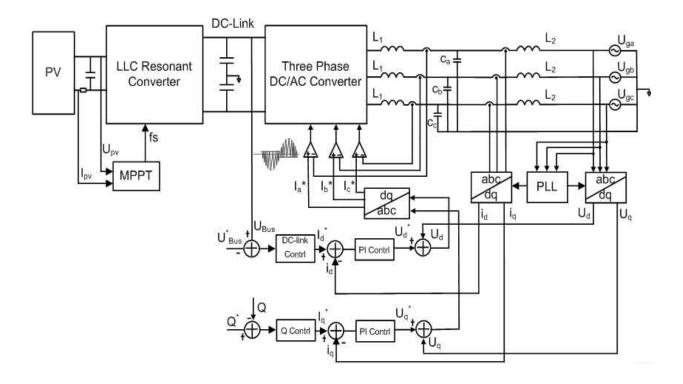

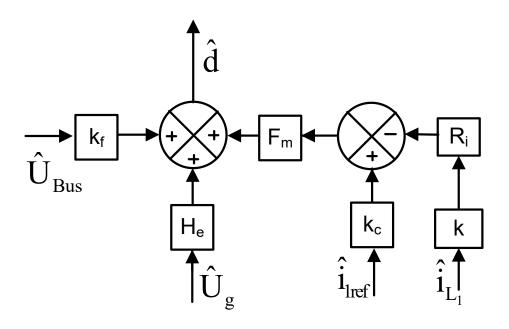

| Figure 4.1 Overall control diagram of a two stage three-phase grid-tie inverter system                                                 |      |

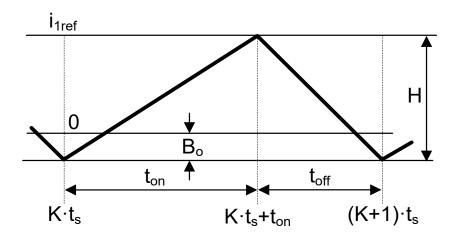

| Figure 4.2 VEDCM of high fraguency inductor L1                                                                                         |      |

| Figure 4.3 VFBCM of high frequency inductor L1                                                                                         |      |

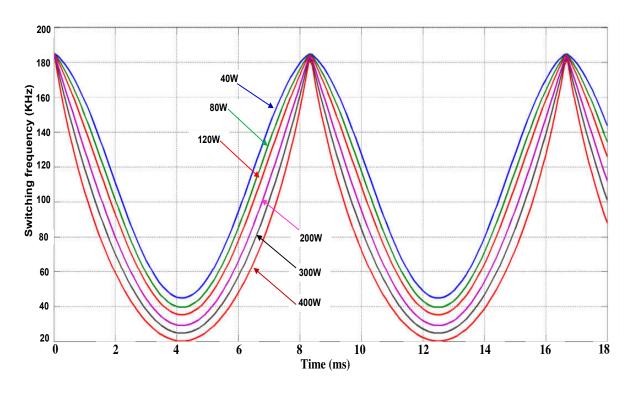

| Figure 4.4 Switching frequency versus load range variation at a line period of output current                                          | / I  |

| Figure 4.5 Half bridge topology of one inverter phase                                                         | 73 |

|---------------------------------------------------------------------------------------------------------------|----|

| Figure 4.6 The equivalent circuit based on switch model for one inverter phase                                | 74 |

| Figure 4.7 The extended instantaneous inductor current waveform                                               | 75 |

| Figure 4.8 A small signal model diagram of the VFBCMC                                                         | 78 |

| Figure 4.9 The inner current loop diagram of one inverter phase with VFBCMC                                   | 79 |

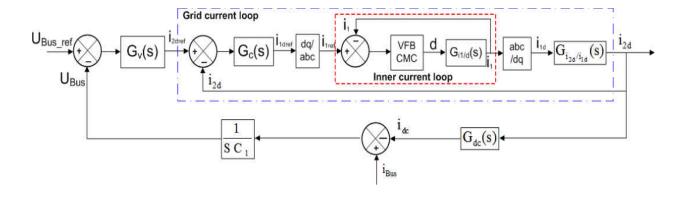

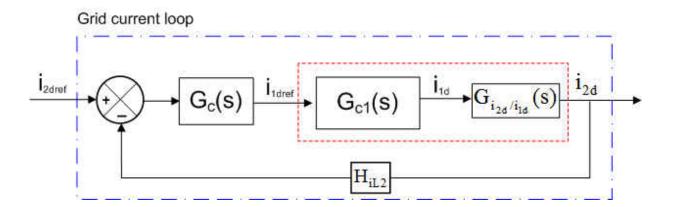

| Figure 4.10 The grid current control diagram in d-axis                                                        | 80 |

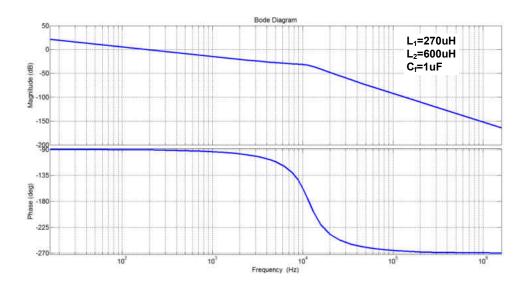

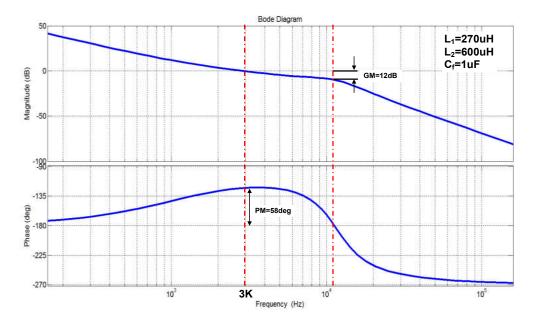

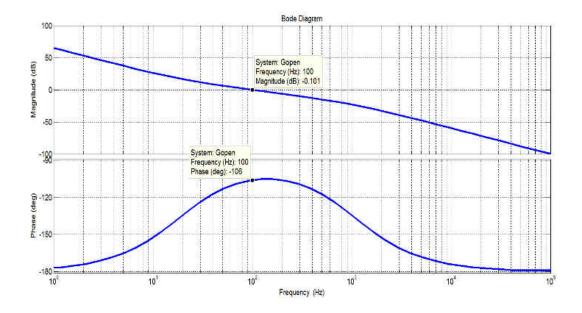

| Figure 4.11 Bode plot of current control loop without controller                                              | 82 |

| Figure 4.12 Bode plot of current control loop with PI controller: PM=580 at fc=3kHz                           | 82 |

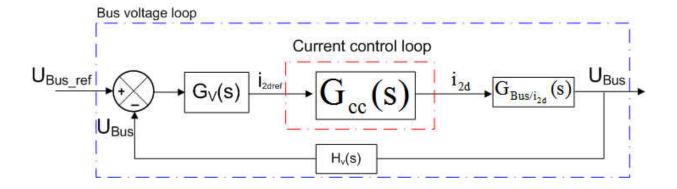

| Figure 4.13 Outer bus voltage control loop diagram                                                            | 83 |

| Figure 4.14 Bode plot of outer bus voltage loop with PI compensation: PM=740 at fc=100Hz                      | 84 |

| Figure 5.1 Simplified block diagram of two-stage MIC                                                          | 87 |

| Figure 5.2 Input capacitor current with various switching frequency at 400W output and different input voltag |    |

| fs=fr; (b)fs>fr; (c)fs <fr< td=""><td>89</td></fr<>                                                           | 89 |

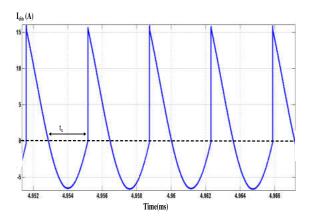

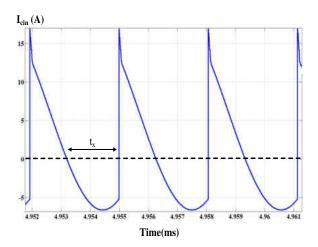

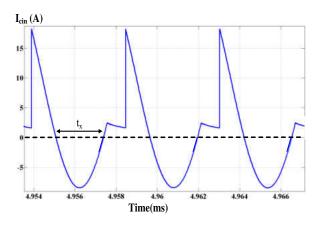

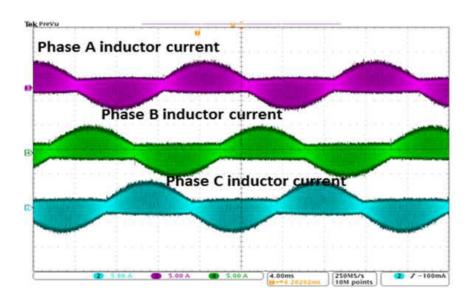

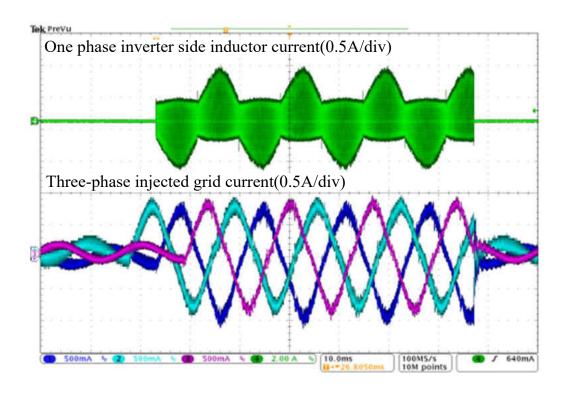

| Figure 6.1 The inductor current waveform and injected grid current in the inverter stage                      | 91 |

| Figure 6.2 The inductor current waveform and injected grid current in the inverter stage                      | 93 |

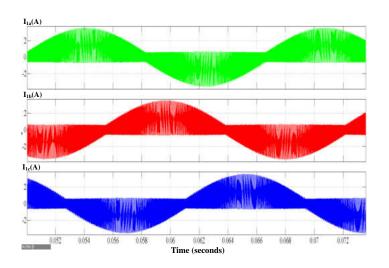

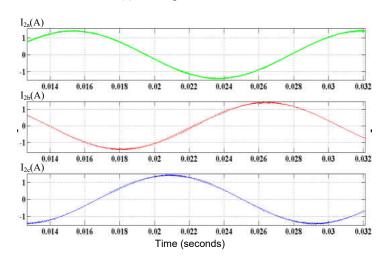

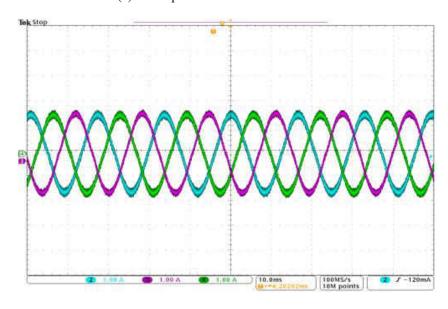

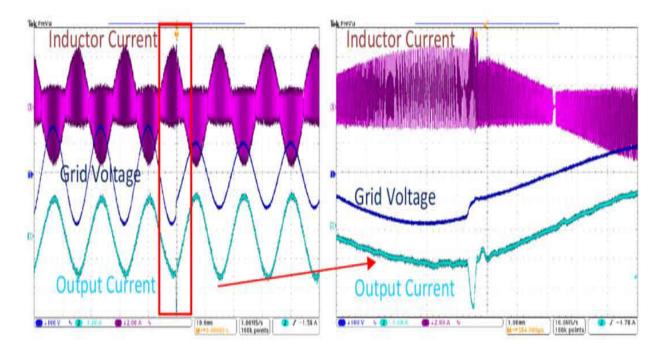

| Figure 6.3 The injected grid current with different power levels                                              | 94 |

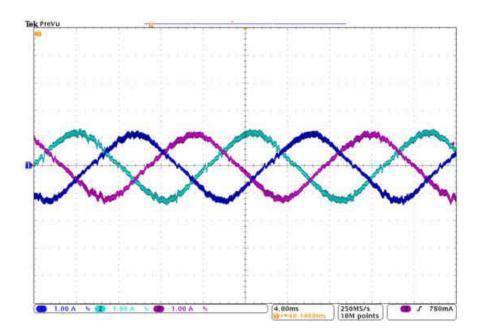

| Figure 6.4 The load dynamic response of the inverter to a step change 0 to 50% rated output power             | 96 |

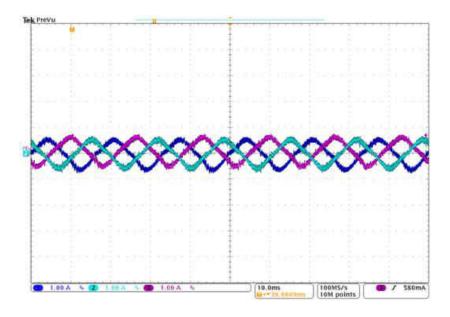

| Figure 6.5 Dynamic response to a step change in the grid voltage from 120V to 80V                             | 96 |

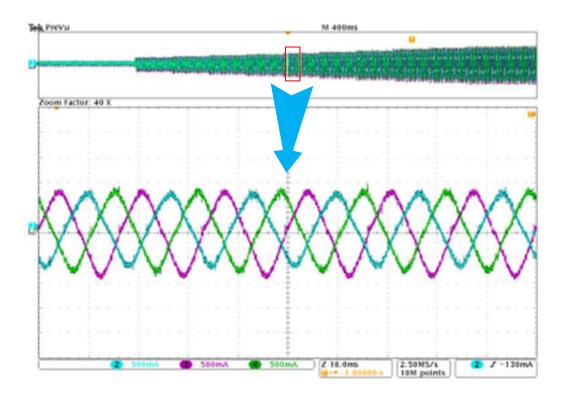

| Figure 6.6 Soft start function of the three-phase four-wire grid-connected inverter (0.5A/div)                | 97 |

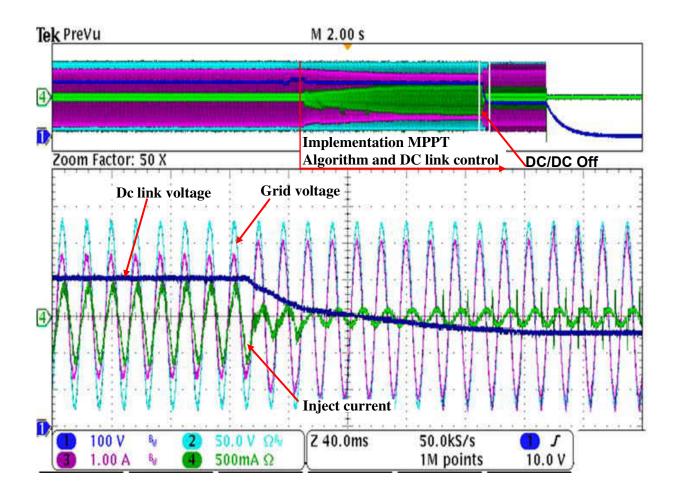

| Figure 6.7 The experimental waveform of overall system with grid-connected                                    | 98 |

# LIST OF TABLES

| Table 1 Key parameters of a 200 W prototype                                                  | 44 |

|----------------------------------------------------------------------------------------------|----|

| Table 2 Three-phase unbalanced dips due to different fault types and transformer connections |    |

| Table 3 Key parameters of the experimental prototype                                         | 92 |

# **CHAPTER ONE: INTRODUCTION**

# 1.1 Background and Challenges

With ever dwindling natural resources and increasing demands for power, the need to seek out viable alternative sources of renewable energy is not just acute but urgent. Due to the fact that solar energy offers extraordinary merits including environmentally neutral, unlimited availability and low cost capable of competing with conventional sources with technology advances and mass production in the coming few years. The photovoltaic (PV) industry has seen over 25% growth on an average over the last 10 years [1].

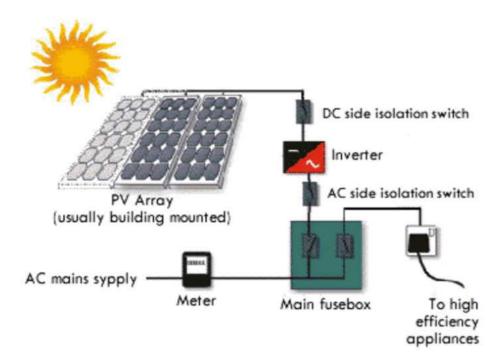

Figure 1.1 A typical PV system configuration for appliances [1]

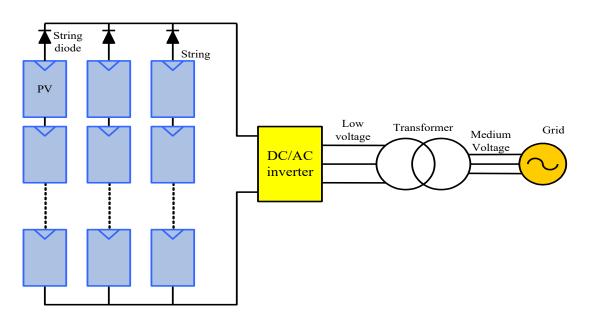

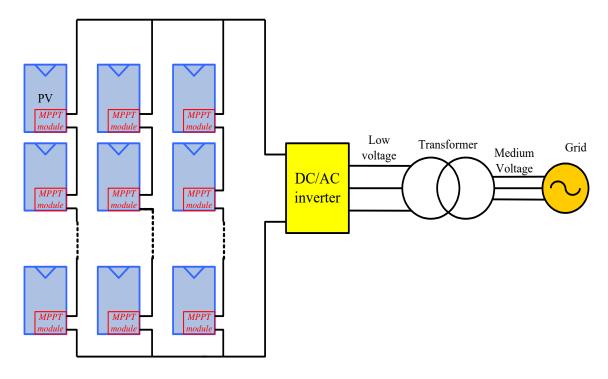

Figure 1.1 shows a typical grid-connected PV system configuration for appliances application. The PV array is consisted with a couple of individual PV modules connected together to generate the required power with a suitable alternating current and voltage through a DC/AC converter. Other than the PV panel itself, the inverter is the most critical device in a PV system both for offgrid or grid-connection applications. Currently, PV system architectures can be categorized into three basic classes with respect to the types of grid-tied inverter: Central inverter, String or Multi-string inverter, and Module Integrated Converter (MIC), also called Micro-inverter [2] [3] [4]. Although the Central inverter as shown in Figure 1.2 can operate at high efficiency with only one DC/AC power conversion stage, this structure has some disadvantages: (1) Each PV module may not operate at its maximum power point which results in less energy harvested. (2) Additional losses are introduced by string diodes and junction box; (3) Single point of failure and mismatch of each string or PV panel affects the PV array efficiency greatly.

Figure 1.2 Diagram of central inverter architecture

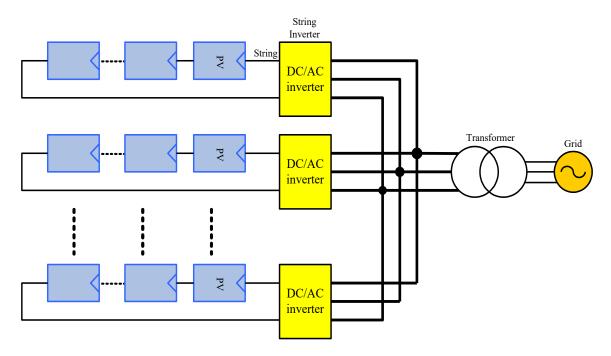

Figure 1.3 shows a diagram of the String inverter that is a modified version of the Central inverter. It partially overcomes the issues arising in Central inverters however it still suffers some of the disadvantages of the central inverter. In an effort to maximize the power from each PV panel, a new approach was recently proposed which can be applied to either Central or String inverter architectures. A power maximizer (usually in the form of a DC/DC converter) is shown in figure 1.4, which is attached to each PV panel to implement maximum power tracking. Although the architecture maximizes power from each PV panel at the cost of additional DC/DC module, it still suffers from drawbacks such as high voltage hazard, single point failure, and difficulty in maintenance.

Figure 1.3 Diagram of string inverter based architecture

Figure 1.4 Maximum power tracking for each panel

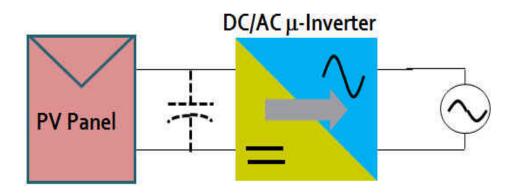

Figure 1.5 Configuration of micro-inverter for solar application

Module integrated converters (MIC) in single phase as shown in figure 1.5 have witnessed recent market success due to unique features (1) improved energy harvest, (2) improved system efficiency, (3) lower installation costs, (4) plug-N-play operation, (5) and enhanced flexibility and modularity. The MIC sector has grown from a niche market to mainstream, especially in the United States.

Assuming further expansion of the MIC market, this dissertation presents the micro-inverter concept incorporated in large size PV installations such as MW-class solar farms where a three phase AC connection is employed. A high efficiency three phase MIC with two-stage ZVS operation for grid tied photovoltaic system is proposed which will reduce cost per watt, improve reliability, and increase scalability of MW-class solar farms through the development of new solar farm system architectures.

The MIC typically used in distributed PV systems is a small grid-tie inverter of 150-400W that converts the output of a single PV panel to AC. The MIC AC outputs are connected in parallel and routed to a common AC coupling point. No series or parallel DC connections are made leaving all DC wiring at a relatively low voltage level of a single panel (typically <60Vdc). The MIC can be further integrated into PV modules to realize a true Plug-and-Play solar AC PV generation system. Thus, AC PV modules with integrated MIC, have significant advantages over traditional PV systems since they allow Maximum Peak Power Tracking (MPPT) on each solar panel to maximize energy harvesting, and offer distributed and redundant system architecture. In addition, MIC and AC PV systems greatly simplify system design, eliminate safety hazards, and reduce installation costs [3][5][6]. With these advantages, the AC module has become the trend for future PV system development. Although MIC and AC PV modules have witnessed recent market success, MIC still has many technical challenges remaining such as high efficiency, high reliability at module level, low cost and high level control issues. To date, research of the MIC has mainly focused on isolated topologies for the following two reasons: (1) from reported literature, most topologies with a few exceptions cannot meet the dual grounding requirement without transformer isolation according to the UL1741 standard. (2) Using transformer is the

best way to boost the low input voltage to high output voltage for AC grid with high efficiency. Since line transformers are bulky and costly, this architecture is not practical for MIC. This paper mainly focuses on the architecture employing a high frequency transformer.

The MIC with its high frequency transformer can be grouped into three architectures based on the DC-link configurations: DC-link, pseudo DC-link and high frequency AC [3] [4] [5]. Usually the MIC just pumps the power from PV to AC grid with unidirectional power flow. However, with the presence of the power decoupling capacitor, MIC can support the AC grid not only as an AC power source, but as a VAR and possibly a harmonics compensator as well [5]. For the latter two cases, bidirectional power flow is needed between AC grid and the power decoupling capacitor requiring MIC with bidirectional power flow capability.

For applications with power levels under several kilo-watts, the single phase connection is commonly used. However, the single phase connection has the disadvantage that the power flow to the grid is time varying, while the power of the PV panel must be constant for maximizing energy harvest, which results in instantaneous input power mismatch with the output instantaneous AC power to the grid. Therefore, energy storage elements must be placed between the input and output to balance (decouple the unbalance) the different instantaneous input and output power. Usually, a capacitor is used to serve as a power decoupling element [2]. However, the lifetime of different types of capacitors varies greatly, e.g. Electrolytic capacitors typically have a limited lifetime of 1000~12,000 hours at 105°C operating temperature [7]. Although some researchers have developed various methods of reducing the required capacitance in single phase MICs in order to allow use of longer lifespan film capacitors [9][11]-[15], these approaches have the drawbacks of either complicating the inverter topology and control or reducing the overall

efficiency. Most presently available commercial MICs still use electrolytic capacitors as power decoupling storage elements due to their large capacitance, low cost, and volumetric efficiency. This tends to limit the lifespan of these MICs [7] [8].

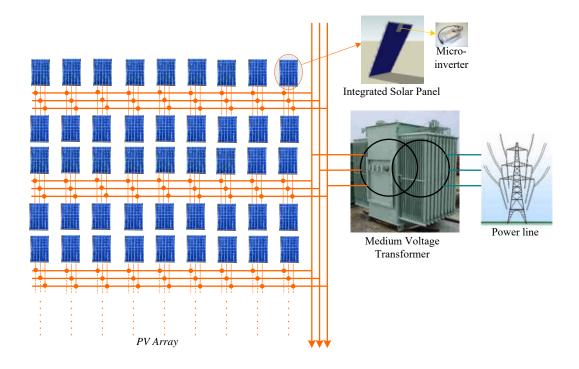

The Distributed PV system, whether used in large-scale solar farms, tens of kilowatt installations, or even down to a single PV panel, will be a trend for future solar PV deployment due to its remarkable merits: (a) Easy modularization and scalability; (b) Elimination of single point failure; (c) Simple installation and maintenance; (d) High efficiency and low cost. FPEC (Florida Power Electronics Center) which is a research arm of UCF has first developed system architecture for a PV solar farm based on three-phase MICs with film capacitor shown in figure 1.6. A three-phase MIC (Micro-inverter) is attached or integrated directly into each PV panel. The outputs of each MIC are directly connected to low voltage three-phase grid and then through medium voltage transformer boost the low three phase voltage to high voltage at power transmission line side. Each MIC operates independently regardless of the failure of other MICs. This architecture will reduce the cost per watt, improve system reliability, and provide more cost effective and efficient power distribution. FPEC also commissioned market research that confirmed the viability of this PV system architecture.

Figure 1.6 Three-phase micro-inverter based architecture for solar farm

Reference [10] shows that the most common commercial building electric service in North America is 120/208 volt wye (three-phase four-wire) which is used to power 120 volt plug loads, lighting, and smaller HVAC systems. In larger facilities the voltage is 277/480 volt and used to power single phase 277 volt lighting and larger HVAC loads. A large number of PV panels with MICs can be located on the roof of a commercial building or adjacent structure and the three phase AC outputs combined to supplement the building electrical service.

# 1.2 Objectives and Outline

The objective of this paper is to provide research background and motivation for use of a three phase topology in larger residential and small to medium solar farm applications. Since the MIC

is a critical component of any such system, this dissertation will present the design and implementation of a two stage high efficiency three phase MIC which uses no electrolytic capacitors. A two-stage micro inverter design suitable for high efficiency DC/AC conversion from a low-voltage (25-50V) DC input to a three-phase 308V AC grid-tied PV system will be discussed in this dissertation. The organization of this dissertation is classified as follows: The first chapter gives the background introduction of the PV system architecture for solar energy generation.

In Chapter 2, a high efficiency DC-DC stage configuration to interface with PV panel is proposed to boost high voltage from low voltage DC input. The specific design of the MPPT controller will not be discussed here due to focusing on the design of topology. Operating modes of the proposed ZVS three-phase four-wire DC/AC converter along with an average modeling is illustrated in Chapter 3. A control strategy for overall system based on trip-loop design will be presented in Chapter 4. As a relatively large area close to half the full prototype is occupied by passive components, such as dc link capacitor, output filter to connect grid while we take a view from the prototype, Chapter 5 will provide a design procedure to minimize the passive components size along with the value calculation based on the prototype's specification. Experimental results are verified using a 400 watt prototype that is shown in Chapter 6. The conclusion is given at the end.

# **CHAPTER TWO: DC-DC STAGE CONVERTER**

#### 2.1 Background and Motivation

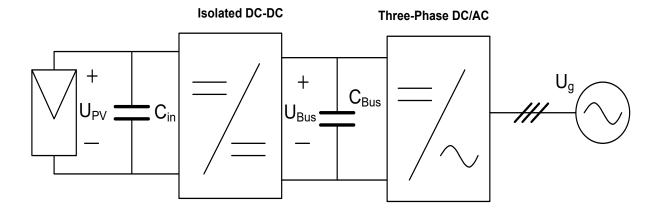

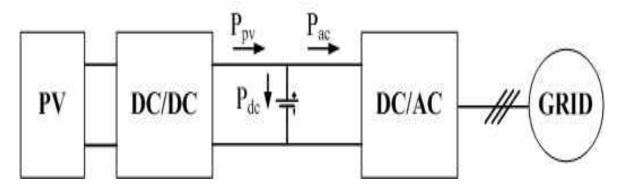

Single panel PV array output voltages are relatively low and vary over a wide range under different operating conditions. A high step up dc-dc converter is typically required to boost this voltage to a value high enough for use in two stage grid-connected power applications [18] [22] which is shown in figure 2.1.

Many non-isolated topologies have been devised to obtain high step-up voltage gain in the past decade [19]-[25]. However, non-isolated converters are not discussed in this paper because most of them cannot meet the dual grounding requirement, thereby possibly losing the grid-connected opportunities [26]. In order to provide galvanic isolation, various isolated converters for high step up applications have been proposed [27]-[42]. In general, the topologies with galvanic isolation suitable for this application can be categorized into two groups: single switch topologies and multi-switch topologies. Single switch topologies mainly include fly-back and forward converters. Multiple-switch topologies include half bridge and full bridge.

Figure 2.1 Simplified block diagram of two-stage MIC

Recently, LLC resonant topology has become attractive due to its desirable characteristics such as high efficiency and natural ZVS/ZCS commutation. This topology is widely utilized in front end DC/DC converters, PC power supplies, flat panel TV's, telecom, and many other commercial, military, and industrial applications. [27-29], [69]. Unfortunately, conventional LLC resonant topology is rarely chosen as the first stage of a PV step-up DC-DC converter due to its difficultly in maintaining high efficiency over a wide input range with varying load conditions. Hybrid operation of a LLC half bridge resonant converter by paralleling an auxiliary transformer with the resonant inductor was proposed by Liang [30]. In addition, a modified LLC converter with two transformers in series was also introduced to increase voltage gain [31]. Although these methods are effective in retaining the merits of LLC resonant topology while extending the input voltage range, the transition between operating modes is a function of input voltage and output power and is not smooth. In addition, control complexity increases which may negatively impact cost and reliability.

Since the power rating of a single PV panel is approximately 200 Watts, single switch flyback and forward topologies are good candidates for step-up DC-DC converter applications due to their simplicity, low cost, and good efficiency over a wide operating voltage range [32-36]. Note that the isolated flyback converter requires only one magnetic component since the transformer's magnetizing inductance serves as the energy storage element and this stored energy is transferred to the load during the transistor's off period [37]. Since energy is stored in the core air gap during the on time, The more the energy stored, the larger the air gap requirement. Thus, a flyback converter is not the best choice at higher power levels according to the general formula-core selection for different topologies [36, 43]. In addition, the value of output capacitor is

relatively high due to discontinuous output current resulting in a physically larger DC link capacitor in two-stage micro inverter applications. It is also difficult to handle the high peak current in the primary that is present with a typical PV panel voltage of less than 30V. Overall, the size of the flyback converter is a major concern especially when the power rating exceeds 100 Watts. Alternately, the energy in a forward converter is transferred to the load during the transistor's on time enabling more power to be delivered to the load for the same core size. Output voltage ripple is much smaller than that of a flyback due to the output filter inductor. However, the forward converter does need additional circuits or an auxiliary winding to reset the magnetizing current of the transformer.

The Forward-Flyback topology that merges the merits of each has been studied by many researchers over the past several decades [37-42]. A circuit that combines direct energy transfer with a wide operating range would have advantages over a forward or flyback converter by itself [37]. This topology (usually running in continuous current mode) is widely used for high input voltage and low output voltage application. In order to achieve zero voltage switching (ZVS) of the primary switch, an auxiliary switch such as an active clamp circuit is necessary but it has the aforementioned problems [41]. Recently, a Series-Connected Forward-Flyback converter that achieves high step-up conversion gain was published in [42], however the voltage balance on the output capacitors should be considered due to the series structure. Publications released over the last decade indicate that Forward-Flyback efficiency is still a major impediment to its widespread application.

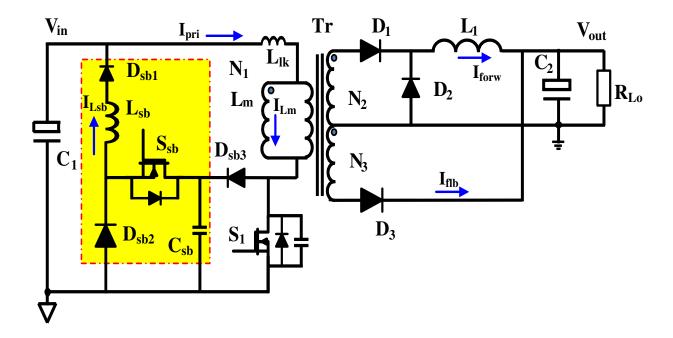

In this chapter, a BMFFC with an efficient active LC snubber circuit is proposed as shown in Figure 2.2. This simple ZVS control scheme is utilized without increasing hardware cost. The

switching loss is greatly reduced since there is no reverse recovery current in the output rectifier diodes. In addition, a low voltage MOSFET can be used by selecting the proper transformer turns ratio. Due to rapid advances in the semiconductor industry, low voltage MOSFET on resistance has been significantly reduced. For example, the on resistance of a 150V MOSFET is less than 10 milliohms for D<sup>2</sup>PAK package. With this in mind there is little difference in conduction losses between Continuous Current Mode (CCM) and Boundary Current Mode (BCM) operation. Energy stored in the transformer leakage inductance causes high voltage spikes in the MOSFET due to BCM, requiring a higher voltage (higher RDSon) MOSFET thereby reducing system efficiency. In order to suppress this voltage spike, an efficient active LC snubber circuit is employed. Although it has several discrete components, these can be low cost surface mount parts due to the small root mean square (RMS) current through the LC snubber circuit and low voltage stress. The gate signal of S<sub>sb</sub> is the same as S<sub>1</sub>; a pulse transformer is inserted between S<sub>1</sub> driver and S<sub>sb</sub>. According to the parameters of a 200W experimental prototype in Table I, the total cost of the LC snubber circuit is \$0.78 based on 10k PCS. Thus, there is very little impact on the system cost.

Figure 2.2 BMFFC with efficient active LC snubber circuit

# 2.2 Principle of Operation

In order to simplify analysis of the operating principle, the following assumptions are made over one switching period:

- 1) Capacitors  $C_1$ ,  $C_2$  are large enough thus  $V_{in}$  and  $V_{out}$  are regarded as a constant voltage source.

- 2) All passive components are considered to be ideal which implies the ESRs of inductors and capacitors are neglected.

- Active switches and all diodes are regarded as ideal that are linearly on or off and the converter is operating in steady state.

- 4) Parasitic inductors, capacitors, and resistors of circuit traces are neglected.

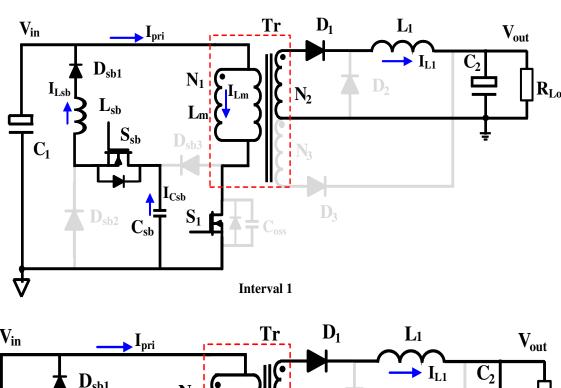

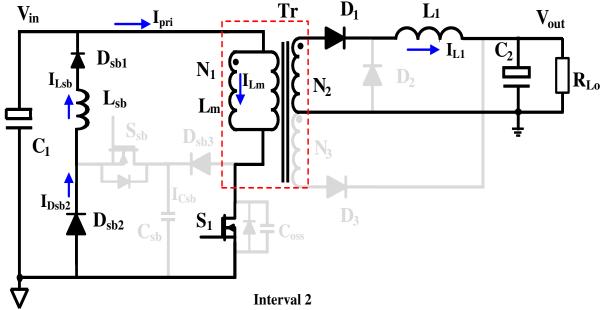

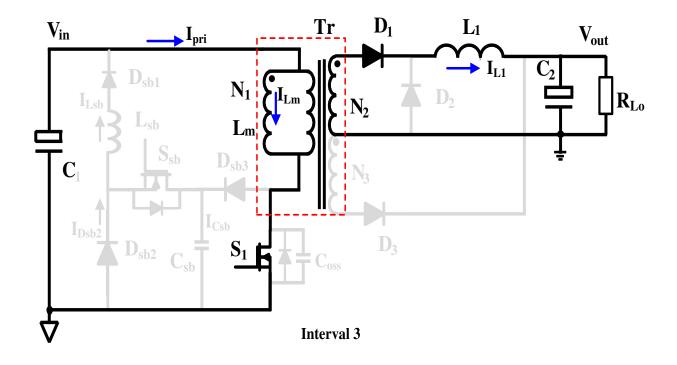

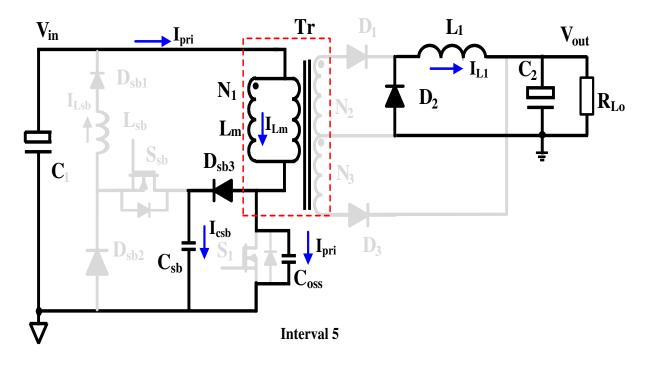

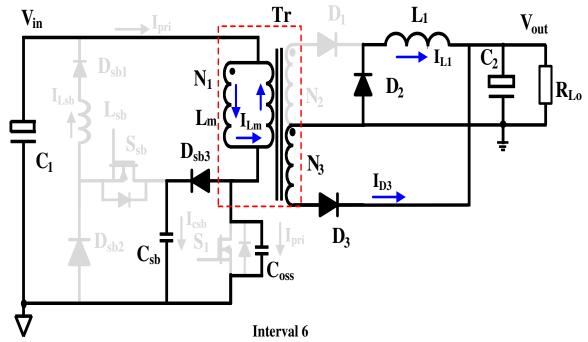

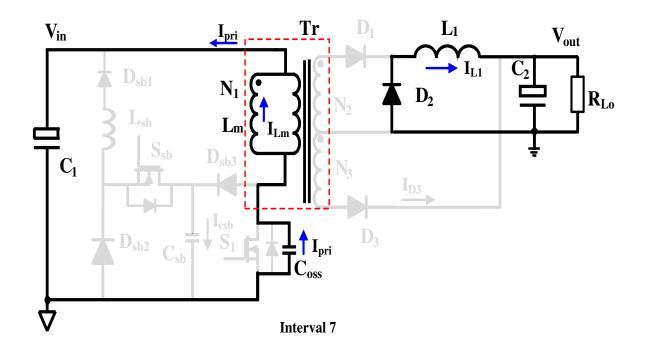

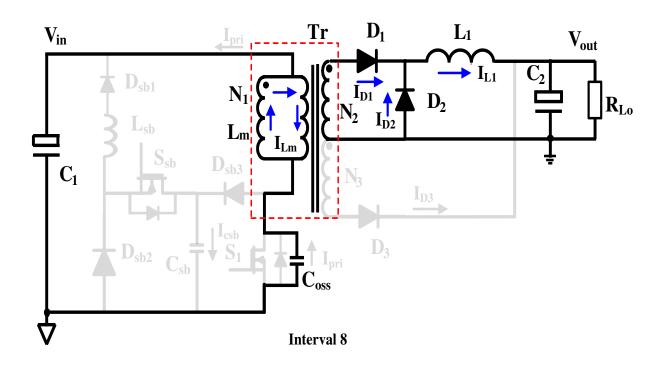

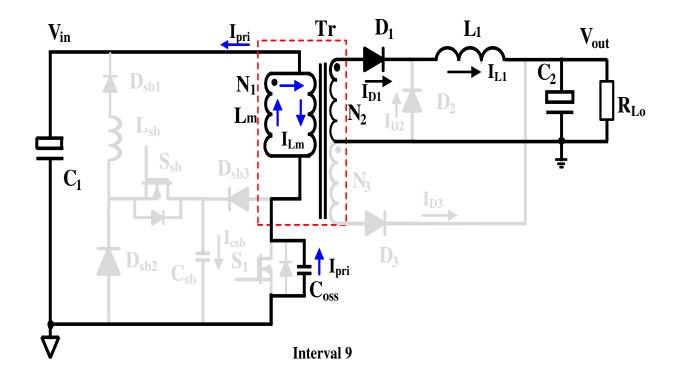

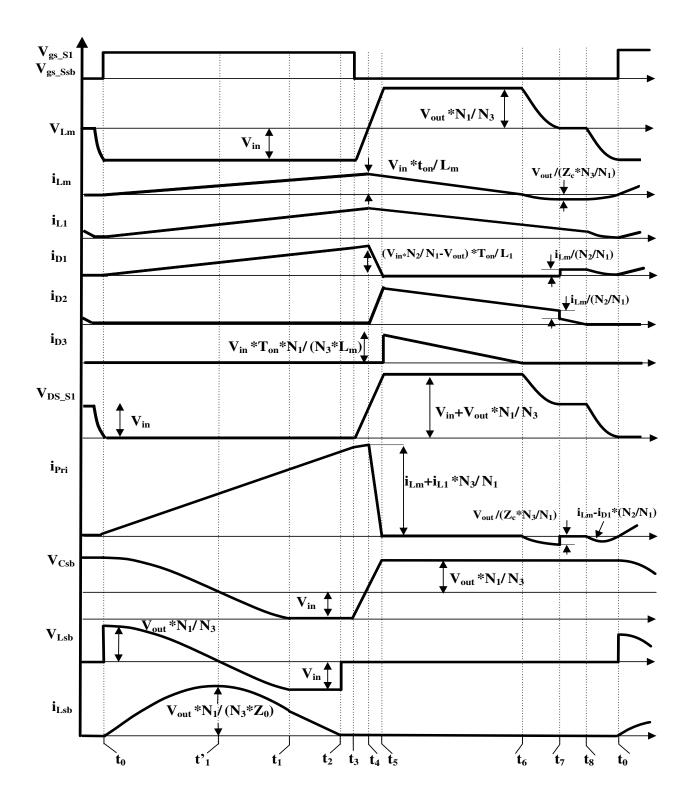

The equivalent circuits of the BMFFC in different operating intervals are introduced in Figure 2.3. Figure 2.4 shows the theoretical waveforms of the BMFFC with an active LC snubber circuit. The operation of the converter within one switching cycle can be divided into nine intervals.

Prior to  $t_0$ , the main switch  $S_1$  and the auxiliary switch  $S_{sb}$ , are both off. At  $t_o$ ,  $S_1$  and  $S_{sb}$  are simultaneously turned on. One portion of the energy from the input source is stored in the transformer, similar to a conventional flyback converter. Meanwhile, another portion of the energy is directly transferred to the load through the transformer and the output inductor  $L_1$ , similar to conventional forward converter operation.

Since the voltage across  $C_{sb}$  is deliberately designed to be at least as high as twice the input voltage,  $C_{sb}$  resonates with  $L_{sb}$  to discharge the energy stored in the snubber capacitor  $C_{sb}$  back to the input source. The voltage across the snubber capacitor  $V_{C_{sb}}$ , and the current through snubber inductor  $I_{L_{sb}}$ , can be represented respectively by:

$$V_{C_{sb}}(t) = V_{in} + V_{out} \frac{N_1}{N_3} \cos(\omega_0 t - \omega_0 t_0)$$

(2.1)

$$i_{L_{sb}}(t) = -\frac{V_{out}}{z_0} \frac{N_1}{N_3} \sin(\omega_0 t - \omega_0 t_0)$$

(2.2)

Where:

$\omega_0 = \frac{1}{\sqrt{L_{sb}*C_{sb}}}$ : the resonant angular frequency

$z_0 = \sqrt{\frac{L_{sb}}{C_{sb}}}$ : the characteristic impedance of the snubber circuit resonant tank

$N_1$  = number of turns in the transformer primary

$N_3$  = number of turns in the secondary flyback section

While the voltage across  $C_{sb}$  equals to Vin, the current  $I_{L_{sb}}$  reaches the maximum value  $\frac{V_{out}}{z_0} \frac{N_1}{N_3}$  at  $t'_1$ . After  $t'_1$ , the current  $I_{L_{sb}}$  is gradually decreasing due to the polarity change of the voltage across  $L_{sb}$ . This interval ends once the voltage across  $C_{sb}$  drops to zero. The duration of the resonance is given by (2.3).

$$\Delta t_1 = t_1 - t_0 = \cos^{-1}(-\frac{V_{in}}{V_{out}} \frac{N_3}{N_1}) \sqrt{L_{sb} * C_{sb}}$$

(2.3)

From (2.3), the length of this interval depends on input voltage after output voltage, turns ratio of transformer, and resonant parameters are determined. The maximum duration of  $\Delta t_1$  is at  $\pi \sqrt{L_{sb}*C_{sb}}$  while  $\frac{V_{in}}{V_{out}} \frac{N_3}{N_1}$  equals one. Combining (2.2) and (2.3), we can see the current  $I_{Lsb}$  doesn't drop to zero if  $\frac{V_{in}}{V_{out}} \frac{N_3}{N_1}$  is less than 1 at  $t_1$  with input voltage decrease. Because  $V_{csb}$  is already equal to zero at  $t_2$ ,  $D_{sb2}$  is turned on if  $L_{sb}$  still has current. As a result,  $I_{Lsb}$  continues to decrease linearly due to input voltage across  $L_{sb}$ . The blocking diode  $D_{sb1}$  is turned off with ZCS when  $I_{Lsb}$  equals zero at  $t_2$ . The action of the non-dissipative LC snubber circuit is completed at  $t_2$ .  $S_1$  continues to conduct during this interval.

The main switch  $S_1$  is still on in this interval as it was in the previous two operating intervals. The magnetizing current  $I_{Lm}$  and the current through the output inductor  $I_{L1}$  continue to ramp up. The current  $I_{Lm}$ ,  $I_{L1}$  and  $I_{pri}$  at  $t_3$  can be calculated by:

$$i_{Lm}(t_3) = \frac{V_{in}}{L_m} \cdot (t_3 - t_0) + i_{Lm}(t_0)$$

(2.4)

$$i_{L1}(t_3) = \frac{V_{In} \cdot \frac{N_2}{N_1} - V_{out}}{L_1} \cdot (t_3 - t_0) + i_{L1}(t_0)$$

(2.5)

$$I_{pri}(t_3) = i_{Lm}(t_3) + i_{L1}(t_3) * \frac{N_2}{N_1}$$

(2.6)

Where:

$L_m$  = the value of the primary magnetizing inductance

$L_1$ = the value of the output inductor

$N_2$  = the winding turns in secondary side of forward section

$i_{Lm}(t_0)$ ,  $i_{L1}(t_0)$ : the initial current of L<sub>m</sub> and L<sub>1</sub> is zero at t<sub>0</sub>

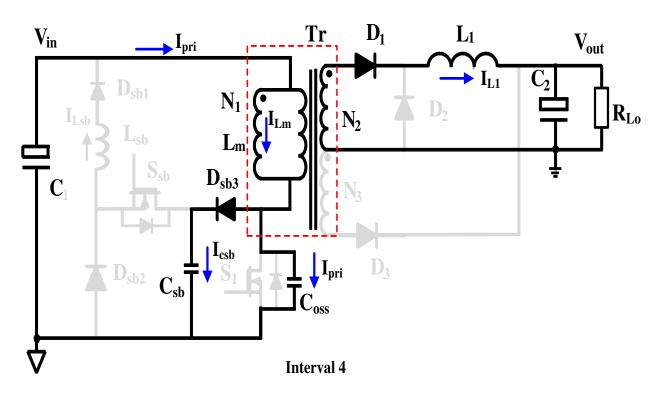

At  $t_3$ ,  $S_1$  and  $S_{sb}$  are simultaneously turned off. The parasitic output capacitor of the MOSFET  $C_{oss}$  in parallel with the snubber capacitor  $C_{sb}$  is immediately charged by the primary current  $I_{pri}$ . The voltage across  $S_1$  and  $C_{sb}$  is increasing quickly due to high charging current  $I_{pri}$ . This period ends when the voltage across  $S_1$  is equal to  $V_{in}$ .

When the voltage across  $S_1$  is greater than input voltage  $V_{in}$  from  $t_4$ , the rectifier  $D_1$  is blocked and  $D_2$  is turned on since it is forward biased. Due to the output voltage across  $L_1$ ,  $I_{L1}$  is freewheeling via  $D_2$ . Consequently, the energy stored in  $L_1$  is released to the load. At this time, the parallel combination of  $C_{oss}$  and  $C_{sb}$  is charged solely by the magnetizing current  $I_{Lm}$ . Since  $D_1$  is off, the load current is not reflected in the primary side. The current through the MOSFET is far smaller than that through the snubber capacitor due to the fact that the value of  $C_{sb}$  is more than 10 times of  $C_{oss}$ . Thus, the turn off loss in the MOSFET is greatly reduced. This interval ends at  $t_5$  when the voltage across the MOSFET is equal to input voltage  $V_{in}$  plus the output voltage divided by the turns ratio of  $N_3/N_1$ .

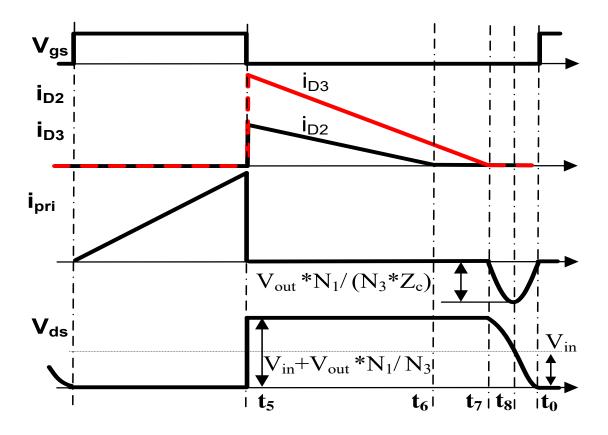

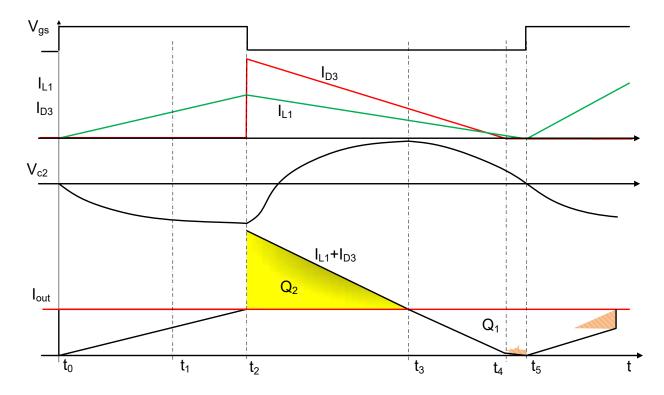

At  $t_5$ , the secondary side rectifier  $D_3$  of the flyback section starts to conduct. The energy stored in the transformer is delivered to the load similar to a conventional flyback converter and the magnetizing current decreases linearly. Meanwhile, the current  $I_{L1}$  continues to decrease linearly. The total output current is summed up by the output current of the forward and flyback converter sections which can be represented by:

$$I_{D3}(t) = i_{Lm}(t_5) \frac{N_1}{N_3} - \frac{V_{out}}{L_{m*} \left(\frac{N_3}{N_1}\right)^2} (t - t_5)$$

(2.7)

$$I_{L1}(t) = i_{L1}(t_5) - \frac{V_{out}}{L_1}(t - t_5)$$

(2.8)

$$I_{out}(t) = I_{D3}(t) + I_{L1}(t) (2.9)$$

This interval begins at  $t_6$ , when the current through  $D_3$  decays to zero. In this case,  $D_3$  is turned off under ZCS. As soon as  $D_3$  is blocked, a primary side resonant circuit consisting of  $C_{oss}$  and  $L_m$  is formed and the voltage across  $S_1$  decreases. The blocking diode  $D_{sb3}$  is reverse biased once the voltage across  $C_{oss}$  ( $V_{ds\_S1}$ ) is less than the voltage across  $C_{sb}$ , whose voltage will maintain unchanged until  $S_{sb}$  turns on at the next switching cycle. In the secondary, the energy stored in  $L_1$  is being transferred to the output. During this time, the voltage across  $C_{oss}$ , and the current in the primary side can be represented respectively by:

$$V_{ds_{-}s_{1}}(t) = V_{in} + V_{out} \frac{N_{1}}{N_{3}} \cos \omega_{c}(t - t_{6})$$

(2.10)

$$i_{pri}(t) = -\frac{V_{out} \frac{N_1}{N_3}}{z_c} \sin \omega_c(t - t_6)$$

(2.11)

Where:

$\omega_c = \frac{1}{\sqrt{L_m * C_{oss}}}$ : the resonant angular frequency

$z_c = \sqrt{\frac{L_m}{c_{oss}}}$ : the characteristic impedance of the resonant tank in the primary side

When the voltage across  $S_1$  decreases to the input voltage  $V_{in}$ , it will be clamped to Vin due to the fact that the current through  $L_1$  will be conducted through rectifiers  $D_1$  and  $D_2$  shorting the transformer secondary. Therefore, the current in the primary magnetizing inductance remains constant in this interval and is transferred to the load via  $D_1$ . Meanwhile, the current through  $D_2$

continues to decrease due to the output voltage across  $L_1$ . This interval ends when the current through  $D_2$  reaches zero. The currents flowing through the primary winding,  $D_1$  and  $D_2$  can be calculated respectively by:

$$i_{Lm}(t) = \frac{V_{out} \frac{N_1}{N_3}}{z_c} \tag{2.12}$$

$$i_{D1}(t) = \frac{V_{out} \frac{N_1}{N_3}}{z_c} \cdot \frac{N_1}{N_2}$$

(2.13)

$$i_{D2}(t) = I_{L1}(t) - i_{D1}(t) (2.14)$$

Once the current through  $D_2$  reaches zero, the transformer is no longer shorted by output rectifiers  $D_1$  and  $D_2$ . Thus, the current through the magnetizing inductor will change with the variation of voltage across the primary winding of the transformer. Because  $D_1$  is still turned on during this time, the current through  $C_{oss}$  ( $I_{pri}$ ) is equal to that of the magnetizing current  $I_{Lm}$  minus the reflected current of  $D_1$  in the primary winding of the transformer. Consequently, the voltage across the MOSFET is decreasing due to the action of  $I_{pri}$ . As the resonant cycle progresses, the voltage across  $C_{oss}$  continues to decrease untill it reaches zero. After that, the body diode of the MOSFET  $S_1$  conducts and the voltage across switch  $S_1$  remains zero which produces zero-voltage switching. According to the Kirchhoff's Circuit Laws in this interval, the corresponding differential equations of current  $I_{pri}$ ,  $I_{lm}$ ,  $I_{D1}$  and voltage ( $V_{ds}$ ) across  $C_{oss}$  can be represented by:

$$\begin{cases} L_{m} \frac{di_{Lm}(t)}{dt} + V_{ds}(t) = V_{in} \\ i_{Lm}(t) = \frac{N_{2}}{N_{1}} \cdot i_{D1}(t) + i_{Pri}(t) \\ i_{Pri}(t) = C_{oss} \frac{dV_{ds}(t)}{dt} \\ \frac{di_{D1}(t)}{dt} = \frac{-[V_{in} - V_{ds}(t)] \cdot \frac{N_{2}}{N_{1}} + V_{out}}{L_{1}} \end{cases}$$

(2.15)

Figure 2.3 Operational intervals of ZVS Forward Flyback converter. (Interval 1) [t0-t1]. (Interval 2) [t1-t2]. (Interval 3) [t2-t3]. (Interval 4) [t3-t4]. (Interval 5) [t4-t5]. (Interval 6) [t5-t6]. (Interval 7) [t6-t7]. (Interval 8) [t7-t8]. (Interval 9) [t8-t0].

Figure 2.4 Theoretical waveforms of the BMFFC with efficient LC snubber circuit

# 2.3 BMFFC Steady State Analysis

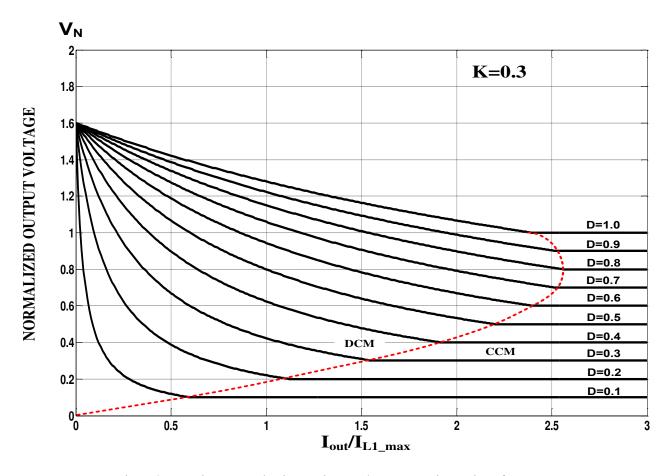

Since both parts supply load current and are forced to have the same duty cycle, they are not independent [37]. Though we deliberately design BMFFC operates at boundary mode, the flyback and forward both have two operation regions of BCM and DCM with wide variation of input voltage. In order to analyze the steady state BMFFC characteristics, the normalized voltage ratio  $V_{out}/(N^*V_{in})$  at DCM is derived in this section. Followed the similar individual derivation of voltage ratio for the flyback converter and forward converter in [43], the average current from flyback and forward part is calculated as, respectively.

$$I_{fb_{avg}} = \frac{V_{in}}{2 \cdot L_m} \cdot \frac{N_1}{N_3} \cdot D \cdot T_s \cdot \frac{V_{in} \cdot D}{\frac{V_{out}}{N_3}}$$

(2.16)

$$I_{fw_{avg}} = \frac{V_{in_{N_1}}^{N_2} - V_{out}}{2 \cdot L_1} \cdot D \cdot T_s \cdot \frac{V_{in_{N_1}}^{N_2}}{V_{out}} \cdot D$$

(2.17)

Combining equations (2.16) and (2.17), the total output current ( $I_{out}$ ) is the sum of both part's average current as

$$\frac{V_{in}}{2 \cdot L_m} \cdot \frac{N_1}{N_3} \cdot D \cdot T_S \cdot \frac{V_{in} \cdot D}{\frac{V_{out}}{N_1}} + \frac{V_{in} \frac{N_2}{N_1} - V_{out}}{2 \cdot L_1} \cdot D \cdot T_S \cdot \frac{V_{in} \frac{N_2}{N_1}}{V_{out}} \cdot D = I_{out}$$

(2.18)

And from [43] the output current of the forward converter and flyback converter required for a continuous conduction mode is maximum at D=0.5, then we get  $I_{Lo\_max} = \frac{V_{in}T_S}{8*L_1} \frac{N_2}{N_1}$  and  $I_{LB\_max} = \frac{V_{in}T_S}{8*L_m*\frac{N_3}{N_L}}$ .

Substituting  $I_{Lo\_max}$  and  $I_{LB\_max}$  into (2.18), the normalized voltage ratio Vout/(N\*Vin) of BMFFC can be expressed as (2.19).

$$V_N = \frac{V_{out}}{N * V_{in}} = \frac{1 + k}{\frac{I_{out}}{4 \cdot I_{Lo,max}} + D^2} \cdot D^2$$

(2.19)

Where,

$$k = \frac{\frac{N_3}{N_2}I_{LB,max}}{I_{L1,max}} = \frac{L_1}{L_m} \frac{N_1^2}{N_2 \cdot N_3}$$

and  $N = \frac{N_2}{N_1}$

The normalized voltage ratio is plotted, shown in Figure 2.5, as a function of  $I_{out}/I_{L1\_max}$  for various values of duty ratio using (2.19), when k is selected as 0.3 from the parameters in Table I. The boundary between CCM and DCM is shown in Figure 2.5 by a dashed red line.

Figure 2.5 Continuous conduction mode CCM/DCM operation region of BMFFC

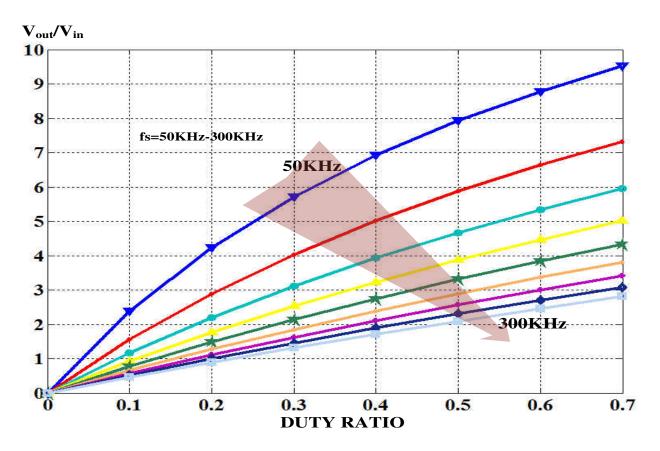

In order to intuitively see the variation of voltage ratio of BMFFC along with switching frequency, duty ratio, and output power change, a specific quantitative analysis as an example is provided based on the specification in Table I. The voltage ratio of BMFFC is rewritten while we

consider interval 7 and interval 9. The average output current of BMFFC is given by combining (2.6) and (2.7):

$$\begin{cases} I_{out} = i_{forward} + i_{flyback} = \frac{V_{in} \cdot \frac{N_2}{N_1} - V_{out}}{2L_1} \cdot t_{on} \cdot \frac{T_s - \tau}{T_s} + \frac{V_{in}}{2L_m} \cdot \frac{N_1}{N_3} \cdot t_{on} \cdot \frac{T_s - \tau - t_{on}}{T_s} \\ t_{on} = t_3 - t_0 = DT_s \\ \tau = \pi \sqrt{L_m C_{oss}} \end{cases}$$

(2.20)

From the load aspect, the output current can be also expressed by  $I_{out} = \frac{V_{out}}{R_L}$ . Then, voltage ratio can be derived by:

$$M = \frac{V_{out}}{V_{in}} = \frac{\left(\frac{N_2}{L_1 N_1} + \frac{N_1}{N_3 L_m} - \frac{N_1 D}{N_3 L_m}\right) - \frac{\tau}{T_S} \left[\frac{N_2}{L_1 N_1} + \frac{N_1}{N_3 L_m}\right]}{\frac{T_S - \tau}{T_S L_1} + \frac{2}{R_L D T_S}}$$

(2.21)

Let

$$\alpha=\frac{N_2}{L_1N_1}$$

,  $\beta=\frac{N_1}{N_3L_m}$ ,  $\gamma=\frac{T_S-\tau}{T_SL_1}$  ,  $\delta=\frac{\tau}{T_S}$

$$M = \frac{\alpha + \beta(1 - D) - \delta(\alpha + \beta)}{\gamma + \frac{2}{R_L DT_S}}$$

(2.22)

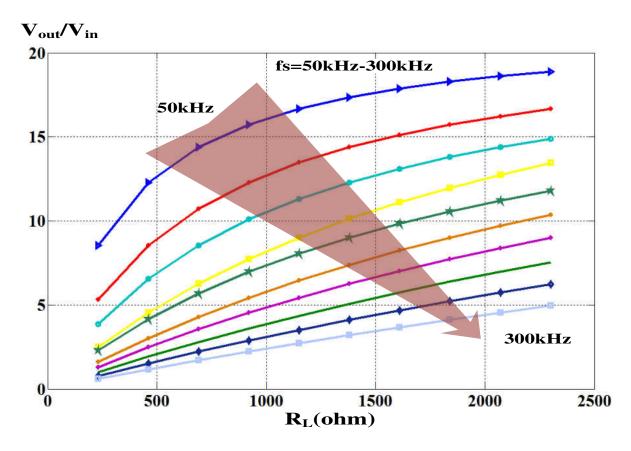

Figure 2.6 DC gain of BMFFC as a function of duty ratio

Figure 2.7 DC gain of BMFFC as a function of load

Using (2.20), the voltage gain of the BMFFC varies with duty ratio and switching frequency. The gain from 50 kHz to 300 kHz is plotted in Figure 2.6. Under this condition according to Table I:  $R_L$ =230ohm,  $\alpha = 37037$ ,  $\beta = 11122$ ,  $\gamma = 3518$ ,  $\delta = 0.05$ . Figure 2.7 shows that the voltage gain varies with loads from 10% to 100% with a switching frequency between 50 kHz to 300 kHz.

# 2.4 ZVS Condition Discussion

Achieving ZVS depends heavily on the currents through  $D_3$  and  $L_1$ . Based on whether current of  $D_3$  reaches zero first or not in Interval 6, two ZVS conditions exist. For these two conditions the

ZVS design considerations are different. In this section, two ZVS conditions will be explored and circuit parameter constraints will be derived for each.

# 2.4.1 Output inductor current $I_{l1}$ reaches zero first

The key waveforms are shown in Figure 2.8. This is the same as a conventional boundary mode flyback converter so the voltage across MOSFET can be expressed by (2.23).

$$V_{ds}(t) = V_{in} + V_{out} \frac{N_1}{N_3} \cos \omega_c (t - t_7)$$

(2.23)

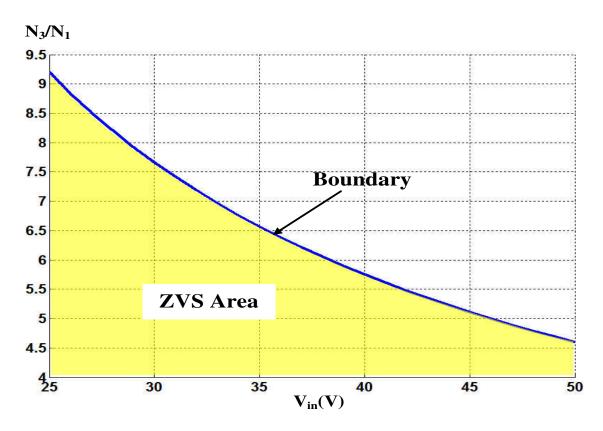

If the turns ratio of  $N_3/N_1$  is selected so that  $V_{DS}$ =0 in (2.23), and  $\cos \omega_c(t-t_7)$  is equal to -1 after half of the resonant period, we can derive the ZVS condition from (2.23) in terms of the turns ratio of  $N_3/N_1$  and the ratio of output voltage to input voltage as shown in (2.24).

$$\frac{N_3}{N_1} \le \frac{V_{\text{out}}}{V_{\text{in}}} \tag{2.24}$$

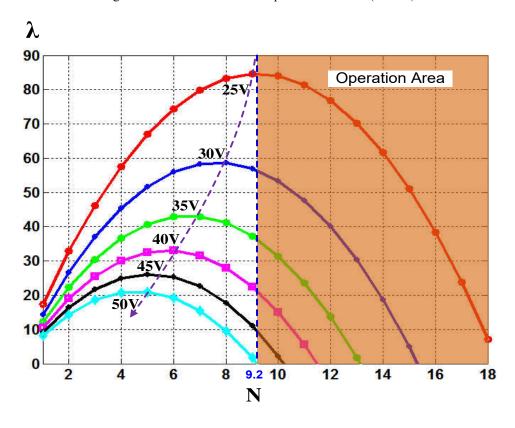

Using (2.24) and the design specifications from Table I, the boundary of ZVS can be plotted as shown Figure 2.9. The range of turns ratio  $(N_3/N_1)$  required to achieve ZVS is indicated by the yellow area with a maximum of 9.2 at 25V input and 4.6 at 50V input.

Figure 2.8 Key waveforms of BMFFC during off time

Figure 2.9 ZVS condition as a function of the input voltage and turns ratio (N3/N1)

# 2.4.2 Current $I_{D3}$ reaches zero first

Before the  $I_{D3}$  reaches zero and when the voltage across the  $S_1$  resonates to  $V_{in}$ , the primary magnetizing current transfers to the secondary due to shorting of the secondary winding via  $D_1$  and  $D_2$ . The voltage across  $S_1$  remains at  $V_{in}$  during this time. Once the current  $I_{D3}$  reaches zero, the resonance resumes and the ZVS condition can be calculated using (2.25). Per the description of Interval 9 in Section 2.2, and considering the leakage inductance of the transformer, the differential equation to describe the principle of operation can be represented by:

$$\begin{cases} L_{lk} \frac{di_{Pri}}{dt} + L_m \frac{di_{Lm}}{dt} + V_{ds} = V_{in} \\ i_{Lm} = \frac{N_2}{N_1} \cdot i_{D1} + i_{Pri} \\ i_{Pri} = C_{oss} \frac{dV_{ds}}{dt} \\ \frac{di_{D1}}{dt} = \frac{-(V_{in} - V_{ds}) \cdot \frac{N_2}{N_1} + V_{out}}{L_1} \end{cases}$$

(2.25)

Simplify (2.25) and the differential equation can be expressed by (2.26):

$$\frac{(L_m + L_{lk})C_{oss}}{\left[1 + \frac{L_m}{L_1} \left(\frac{N_2}{N_1}\right)^2\right]} \frac{dV_{ds}^2}{dt^2} + V_{ds} = V_{in} - \frac{\frac{L_m}{L_1} \frac{N_2}{N_1}}{\left[1 + \frac{L_m}{L_1} \left(\frac{N_2}{N_1}\right)^2\right]} V_{out}$$

(2.26)

Let

$$V_{pri}' = \frac{\frac{L_m, N_2}{L_1, N_1}}{\left[1 + \frac{L_m}{L_1} \left(\frac{N_2}{N_1}\right)^2\right]} V_{out}$$

(2.27)

By combining (2.26) and (2.27), the solution of the differential equation can be calculated in (2.28):

$$\begin{cases} V_{ds}(t) = V_{in} - V_{pri}' - \left[ V_{in} - V_{pri}' - V_{ds}(t_8) \right] \cdot \cos \omega_{c1}(t - t_8) + z_{c1} \cdot i_{pri}(t_8) \sin \omega_{c1}(t - t_8) \\ i_{pri}(t) = C_{oss} \cdot \omega_{c1} \cdot \left[ V_{in} - V_{pri}' - V_{ds}(t_8) \right] \cdot \sin \omega_{c1}(t - t_8) + C_{oss} \cdot z_{c1} \cdot \omega_{c} \cdot i_{pri}(t_8) \cdot \cos \omega_{c1}(t - t_8) \\ where \qquad \omega_{c1} = \frac{1}{\sqrt{\frac{(L_m + L_{lk})Coss}{L_1 \left( \frac{L_m}{N_1} \right)^2}}}; z_{c1} = \sqrt{\frac{(L_m + L_{lk})}{Coss}} \end{cases}$$

(2.28)

And according to the initial condition at t<sub>8</sub>:

$$\begin{cases} i_{Lm}(t_8) = -\frac{V_{out}\frac{N_1}{N_3}}{z_c} \\ V_{ds}(t_8) = V_{in} \\ i_{Pri}(t_8) = 0 \end{cases}$$

(2.29)

Then substituting (2.29) into (2.28), we get both functions of the voltage across  $S_1$  and the current ( $i_{pri}$ ) through  $C_{oss}$ :

$$\begin{cases} V_{ds}(t) = V_{in} - V_{pri}' + V_{pri}' \cos \omega_{c1}(t - t_8) \\ i_{pri}(t) = -C_{oss} \cdot \omega_{c1} \cdot V_{pri}' \cdot \sin \omega_{c1}(t - t_8) \end{cases}$$

(2.30)

From (2.30), ZVS condition can be expressed by (2.31) if the voltage across  $S_1$  reaches zero:

$$V_{in} - V_{pri}' + V_{pri}' \cos \omega_{c1}(t - t_8) = 0$$

(2.31)

Thus, after a half resonant period:  $\omega_{c1}(t-t_8)=\pi$ :

$$V_{in} - V_{pri}' - V_{pri}' = 0 (2.32)$$

Plug (2.27) into (2.32) and simplify, we get (2.33):

$$\frac{\frac{L_{m}, N_{2}}{L_{1}}}{\left[1 + \frac{L_{m}}{L_{1}} \left(\frac{N_{2}}{N_{1}}\right)^{2}\right]} \cdot V_{out} \ge \frac{V_{in}}{2}$$

(2.33)

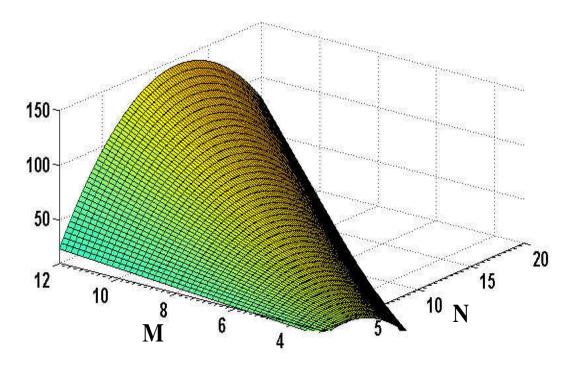

Let  $\lambda = \frac{L_1}{L_m}$ ,  $N = \frac{N_2}{N_1}$ ,  $M = \frac{V_{out}}{V_{in}}$ , then substitute  $\lambda$ , N, M into (2.33)

$$\frac{\frac{N}{\lambda}}{1+\frac{N^2}{\lambda}} \cdot V_{out} \ge \frac{V_{in}}{2} \tag{2.34}$$

Simplify (2.34)

$$\lambda \le 2NM - N^2 \tag{2.35}$$

Figure 2.10 Three-Dimensional plot of the ratio  $\lambda$  (L1/Lm)

Figure 2.11 The ratio  $\lambda$  (L1/Lm) as a function of input voltage and turns ratio N (N2/N1)

In this case, the ZVS range is closely related to the ratio  $\lambda$ , the voltage gain M, and the turns ratio N<sub>2</sub>/N<sub>1</sub> as illustrated in Figure 2.10. To clearly demonstrate the relationship between  $\lambda$  and turns ratio N with input voltage from 25V to 50V and a 230V output voltage, a 2-D graph is plotted in Figure 2.11. It can be seen from this that the region of parameter selection to achieve ZVS gradually decreases as input voltage increases which indicates ZVS is easier to achieve at low input voltages. Referring to the design specifications in Table I, the shaded operating ZVS area shows that the minimum turns ratio N (N<sub>2</sub>/N<sub>1</sub>) is 9.2 from (2.38). As shown in Figure 2.11, although ZVS will be lost at high input voltage, the efficiency at high input voltage generally is higher than low input voltage for most step-up DC-DC converters. Efficiency at the minimum input voltage determines the magnetic core selection, thermal design, and ultimately the size of the whole prototype. Therefore, the overall performance will be improved if the efficiency at low input voltage is significantly increased by trade-off design between high voltage and low voltage through the unique feature of BMFFC.

# 2.5 Design Guidelines

The key parameters in design of the BMFFC are discussed in this section with the following specifications:

Input voltage  $V_{in} = 25\text{V}-50\text{V}$

Output voltage  $V_{out} = 230 \text{V}$

Output power  $P_{out} = 200$ W

Minimum switching frequency  $f_s = 50 \text{ kHz}$

### 2.5.1 Design of Turns Ratio of the Transformer $(N_2/N_1 \& N_3/N_1)$

In order to use 150V MOSFETs, the voltage stress across  $S_1$  should be limited to 120V to provide some margin. Therefore, the turns ratio of  $N_2/N_1$  should yield to (2.36) according to the voltage stress equation in Table I:

$$V_{in\_max} + \frac{N_1}{N_3} V_{out} < 120 \tag{2.36}$$

The turns ratios of  $N_3/N_1$  can be simplified as:

$$\frac{N_3}{N_1} > \frac{V_{out}}{120 - V_{in\_max}} \tag{2.37}$$

Based on the specification: Vin\_max=50V, Vout=230V, and the turns ratio of  $N_3/N_1$  is selected as 3.3.

From the ZVS range analysis in section IV, the turns ratio  $N_2/N_1$  strongly affects the ZVS condition with the variation of input voltage and  $\lambda$ . According to the plot in Figure 2.11, it is easier to achieve ZVS over the full input voltage range with a low turns ratio of  $N_2/N_1$ . Thus we need to choose the turns ratio of  $N_2/N_1$  as small as possible. But according to the specification,

the lower limit of the turns ratio yielded by (2.38) is at the minimum input voltage of 25V. Therefore, the turns ratio of  $N_2/N_1$  should greater than 9.2.

$$V_{in\_min} \cdot \frac{N_2}{N_1} > V_{out} \tag{2.38}$$

In general, efficiency increases with higher input voltages in a step-up DC/DC converter. With this in mind and referring to Figure 2.11, N=10 and  $\lambda$ =10 are chosen. Turn-on loss is still very small due to ZCS when compared to CCM hard switching even though ZVS is lost once the input voltage exceeds 43V.

# 2.5.2 Design of the Magnetizing Inductance $L_m$ , and Output Inductance $L_1$

To simply the design, we assume the power converted from flyback operation and from forward operation is equal at the minimum input voltage and rated output power. The mathematical expressions can be given as:

$$\begin{cases} i_{forward} = i_{flyback} \\ l_{out} = i_{forward} + i_{flyback} \end{cases}$$

(2.39)

Considering load condition, the maximum output current is expressed by:

$$I_{out} = \frac{P_{out}}{V_{out}} \tag{2.40}$$

Substituting (2.40) and (2.39) into (2.20), we can derive the following constraints:

$$\frac{V_{in}}{2 \cdot L_m} \cdot \frac{N_1}{N_3} \cdot t_{on} \cdot \frac{T_S - \tau - t_{on}}{T_S} = 0.5 \cdot I_{out}$$

$$(2.41)$$

Simplify (2.41),

$$L_m = \frac{V_{in}}{I_{out}} \cdot \frac{N_1}{N_3} \cdot t_{on} \cdot \frac{T_s - \tau - t_{on}}{T_s}$$

(2.42)

As the current  $I_{L1}$  reaches zero first at 25V input, the DC gain of BMFFC can be expressed by  $M_{Flyb} = \frac{N_3}{N_1} \frac{D}{1-D}$ . Thus, the duty ratio is 0.736 and the turns ratio  $N_3/N_1 = 3.3$  is inserted in  $M_{Flyb}$ . Using (2.42) the designed value of the magnetizing inductance of the transformer  $L_m$  is 27uH with a switching frequency is 50 kHz at 25V input. Since  $\lambda$  (the ratio of  $L_1$  to  $L_m$ ) was chosen to be 10, the designed value of the output inductor  $L_1$  is 270uH.

# 2.5.3 Design of the Resonant Components in Snubber Circuit, $C_{sb}$ and $L_{sb}$ .

As we know, the voltage spike across MOSFET is caused by transferring the energy in the leakage inductor ( $L_{lk}$ ) to the capacitor. Based on the law of conservation of energy, the resonant snubber capacitor value can be calculated by (2.43) under worst case conditions of maximum input voltage and full power:

$$\frac{1}{2} \cdot C_{sb} \cdot \left(V_{peak}^2 - V_{in\_max}^2\right) \ge \frac{1}{2} \cdot L_{lk} \cdot \left[i_{pri_{peak}}\right]^2 \tag{2.43}$$

Simplify (2.43):

$$C_{sb} = \frac{L_{lk}}{V_{peak}^2 - V_{in\ max}^2} \cdot \left[i_{pri_{peak}}\right]^2 \tag{2.44}$$

In addition, the average input current is derived in (2.45) according to the specification:

$$\begin{cases} I_{in-avg} = \frac{1}{2}i_{pri_{peak}} \cdot \frac{t_{on}}{T_S} = \frac{1}{2}i_{pri_{peak}} \cdot D \\ I_{in-avg} = \frac{P_{in}}{V_{in}} = \frac{P_{out}}{\eta \cdot V_{in}} \end{cases}$$

(2.45)

Simplify (2.45) and the peak current can be expressed by (2.46):

$$i_{pri_{peak}} = \frac{2 \cdot P_{out}}{\eta \cdot V_{in} \cdot D} \tag{2.46}$$

Then substitute (2.46) into (2.44):

$$C_{sb} = \frac{L_{lk}}{V_{peak}^2 - V_{in max}^2} \cdot \left(\frac{2 \cdot P_{out}}{\eta \cdot V_{in} \cdot D}\right)^2 \tag{2.47}$$

With D=0.46 from  $M_{Flyb}$ , voltage spike ( $V_{peak}$ ) should not exceed 130V if we want to maintain a 20V margin for the 150V MOSFET. If an efficiency  $\eta$ =0.97 at 50V input is assumed at  $P_{out}$ =230W and  $L_{lk}$ =252nH from Table I, the calculated value of the resonant snubber capacitor  $C_{sb}$  using (35) is 8.48nF. The final value was chosen to be 9.4nF by paralleling two 4.7nF capacitors.

As analyzed in Section II, the interval from  $t_0$  to  $t_2$  is one half of the resonant period of the snubber capacitor  $C_{sb}$  and Lsb, which should be less than the minimum conduction time at the worst case condition of input voltage (50V) and output power (20W).

$$\pi \cdot \sqrt{L_{sb} \cdot C_{sb}} \le t_{on} \tag{2.48}$$

Combining (2.6), (2.46) and (2.48), we get (2.49):

$$L_{sb} = \left(\frac{\frac{\frac{2 \cdot P_{out}}{\eta \cdot V_{in} \cdot D \cdot \pi}}{\frac{V_{in} \cdot N_2}{2 \cdot L_1} + \frac{V_{in}}{L_m}}\right)^2 \cdot \frac{1}{C_{sb}}$$

(2.49)

Thus, the calculated value of the resonant snubber inductor Lsb is 27.8uH. The known values of  $L_1$ ,  $L_m$ ,  $N_2$ ,  $N_1$  and D can be inserted into (37).

# 2.5.4 Design of the Output Capacitor C2

Neglecting the interval shown in Figure 2.4 from  $t_3$  to  $t_5$  and from  $t_6$  to  $t_0$ , voltage and current ripple of the output capacitor  $C_2$  for one switching cycle is shown in Figure 2.12. The output

capacitor  $C_2$  is charged by the sum of  $I_{L1}$  and  $I_{D3}$  during the period  $t_2$ - $t_3$ . The output capacitor is discharging after  $t_3$  while the load current ( $I_{out}$ ) is greater than the sum of  $I_{L1}$  and  $I_{D3}$ .

Figure 2.12 Voltage and current ripple in the output capacitor

The electric charge  $(Q_2)$  of the output capacitor from  $t_2$  to  $t_3$  can be represented by (2.50):

$$Q_{2} = \int_{t_{2}}^{t_{3}} \left[ i_{L1_{peak}} - \frac{V_{out}}{L_{1}} \cdot t + i_{D3_{peak}} - \frac{V_{out}}{\left(\frac{N_{3}}{N_{1}}\right)^{2} \cdot L_{m}} \cdot t - I_{out} \right] dt$$

(2.50)

The equation after integration is:

$$Q_{2} = \left(i_{L1\_peak} + i_{D3\_peak} - I_{out}\right) \cdot t \Big|_{t_{2}}^{t_{3}} - \frac{1}{2} \left[\frac{V_{out}}{L_{1}} + \frac{V_{out}}{\left(\frac{N_{3}}{N_{1}}\right)^{2} \cdot L_{m}}\right] \cdot t^{2} \Big|_{t_{2}}^{t_{3}}$$

(2.51)

Where:

$$t_3 - t_2 = \frac{\left(i_{L1\_peak} + i_{D3\_peak} - I_{out}\right)}{\frac{V_{out}}{L_1} + \frac{V_{out}}{\left(\frac{N_3}{N_1}\right)^2 L_m}}$$

(2.52)

Substitute (2.52) into (2.51) and we get (2.53):

$$Q_{2} = \frac{1}{2} \cdot \left[ \left( i_{L1\_peak} + i_{D3\_peak} - I_{out} \right) \cdot \frac{\left( i_{L1\_peak} + i_{D3\_peak} - I_{out} \right)}{\frac{V_{out}}{L_{1}} + \frac{V_{out}}{\left( \frac{N_{3}}{N_{1}} \right)^{2} L_{m}}} \right]$$

(2.53)

Then according to the equation  $Q_2 = C \cdot \Delta V$ , the capacitance can be calculated by (2.54):

$$C = \frac{Q_2}{\Delta V} = \frac{1}{2 \cdot \Delta V} \cdot \left[ \left( i_{L1\_peak} + i_{D3\_peak} - I_{out} \right) \cdot \frac{\left( i_{L1\_peak} + i_{D3\_peak} - I_{out} \right)}{\frac{V_{out} + V_{out}}{L_1} \left( \frac{N_3}{N_1} \right)^2 L_m} \right]$$

(2.54)

The output capacitor value is selected based on the current ripple through  $C_2$  in one switching cycle and can be calculated as (2.55) for a resistive load.

$$C = \frac{Q_2}{\Delta V} = \frac{1}{2 \cdot \Delta V} \cdot \left[ \left( i_{L1\_peak} + i_{D3\_peak} - I_{out} \right) \cdot \frac{\left( i_{L1\_peak} + i_{D3\_peak} - I_{out} \right)}{\frac{V_{out}}{L_1} + \frac{V_{out}}{\left( \frac{N_3}{N_1} \right)^2 L_m}} \right]$$

(2.55)

Given  $i_{L1_{peak}} = 1A$ ,  $i_{D3\_peak} = 3.9A$ ,  $I_{out} = 1A$ , and a desired output voltage ripple of 0.5V, the calculated value of output capacitor  $C_2$  is 9.3uF. A value of 11uF was chosen by paralleling five 2.2uF ceramic capacitors.

# 2.6 Experimental Results Verification

Following the design guidelines in section 2.5, a 200W prototype was constructed to verify the performance of the BMFFC with non-dissipative LC snubber circuit. The specifications of the prototype are listed in Table I.

Table 1 Key parameters of a 200 W prototype

| Input voltage                    | 25V-50V               | Rated output power                               | 200W      |

|----------------------------------|-----------------------|--------------------------------------------------|-----------|

| Output voltage                   | 230V                  | Switching frequency                              | 50-220KHz |

| Turns number $N_1:N_2:N_3$       | 6:60:20               | Magnetizing inductance                           | 27uH      |

| Leakage inductance               | 252nH                 | Output inductor L <sub>1</sub>                   | 270uH     |

| Primary Mosfet S <sub>1</sub>    | FDB075N15A (2PCS)     | Output rectifier D <sub>1</sub> , D <sub>2</sub> | STTH312S  |

| Output capacitor C <sub>2</sub>  | C2220C225MAR2C (5PCS) | Output rectifier D <sub>3</sub>                  | STTH310S  |

| Trans Core Size                  | RM14                  | Snubber Capacitor C <sub>sb</sub>                | 9.4nF     |

| Snubber Inductor L <sub>sb</sub> | CDRH127NP-270MC       | Snubber switch S <sub>sb</sub>                   | FDD7N20   |

| Dsb1                             | B380                  | Dsb2,Dsb3                                        | ES2D      |

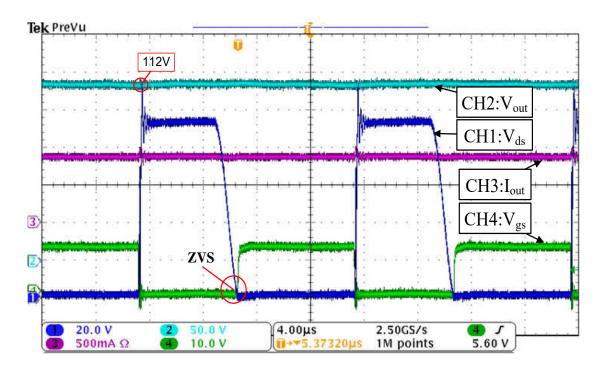

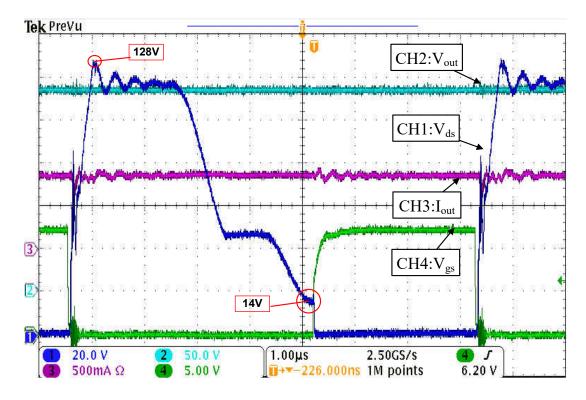

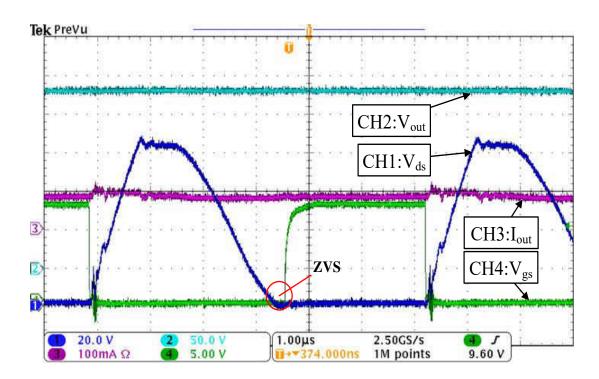

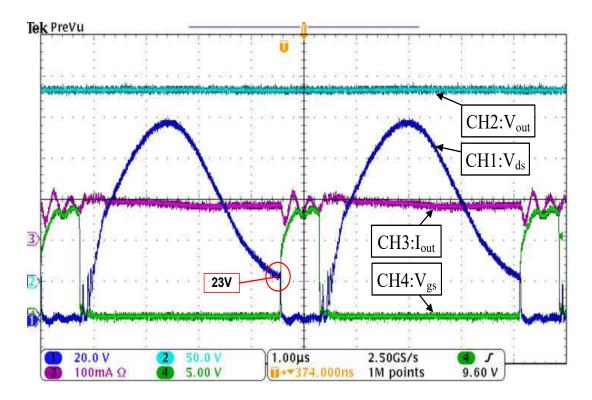

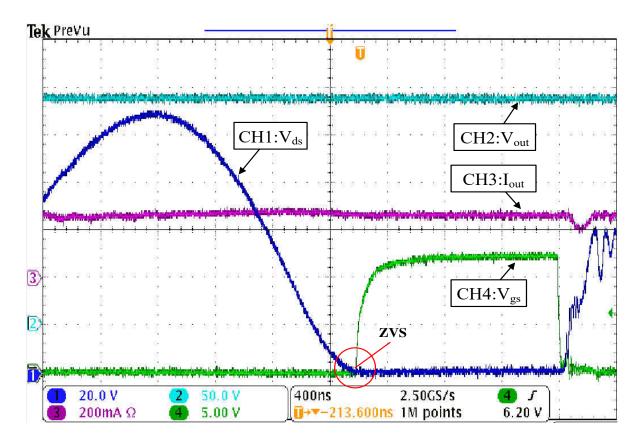

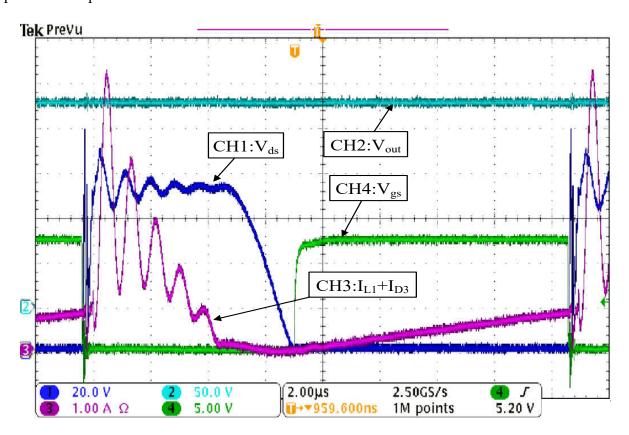

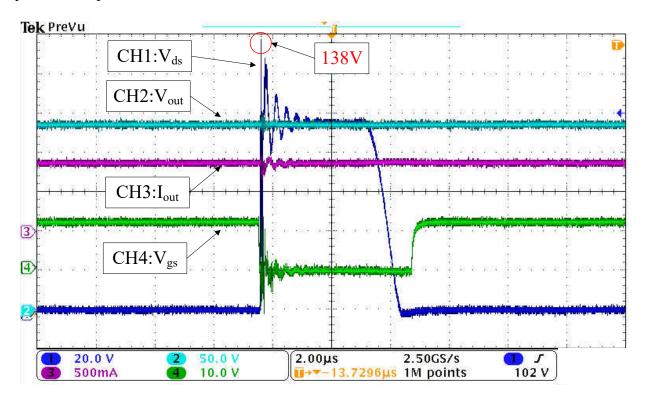

A photograph of the laboratory prototype with 200W is shown in Figure 2.13. The experimental waveforms of BMFFC with different input voltages and power outputs are shown in Figure 2.14 through Figure 2.18. (CH1: voltage stress across  $S_1$ , CH2: output voltage 230V, CH3: output current, CH4: gate signal of MOSFET, the voltage and current scale is shown in the figures). Referring to Figure 2.14, with 25V input and 200W output, ZVS is achieved before the gate signal turns on. The voltage spike across  $S_1$  is limited to 112V due to the effect of the LC snubber circuit. With the maximum input of 50V and 200W output, the voltage spike across  $S_1$  is 128V as shown in Figure 2.15. The voltage across  $S_1$  decreases to 14V at full power output

before the switch is turned on which reduces turn-on loss due to the fact that the current through MOSFET is already very small.

# 67.5mm

Figure 2.13 Photograph of the hardware prototype of BMFCC with 200W

Figure 2.14 Measured waveforms of the BMFFC at 200W with 25V input

Figure 2.15 Measured waveforms of the BMFFC with 200W output and 50V input

Figure 2.16 Measured waveforms of the BMFFC with 20W output and 25V input

Figure 2.17 Measured waveforms of the BMFFC at 20W with 50V input

Figure 2.18 Measured waveforms of the BMFFC at 60W with 43V input

Figure 2.16 and Figure 2.17 show measured waveforms at 10% of rated power output at minimum and maximum input voltages. As seen in Figure 2.16, ZVS is still achieved at 10% of full load. Figure 2.17 shows experimental waveforms at maximum input voltage. The voltage across S<sub>1</sub> decreases to 23V at 20 watts output. Consequently, the turn-on loss of the BMFFC at light load is reduced. Figure 2.18 shows ZVS is still achieved even at 60 watts output with 43 input.

Figure 2.19 Measured waveforms of an efficient active LC snubber circuit

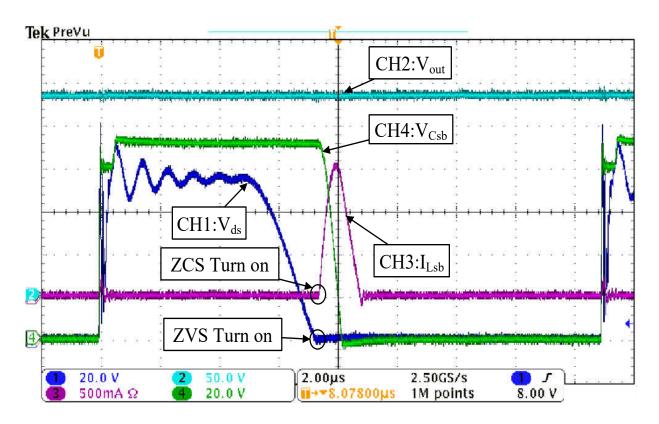

Figure 2.19 (CH1: voltage stress across  $S_1$ , CH2: output voltage 230V, CH3: the current  $i_{Lsb}$  through the snubber inductor  $L_{sb}$ , CH4: voltage stress across snubber capacitor  $C_{sb}$ ) shows the measured voltage waveforms across the snubber capacitor  $C_{sb}$  and current waveform through the snubber inductor  $L_{sb}$ . As shown in Figure 2.19, the auxiliary switch  $S_{sb}$  is turned on with ZCS so its turn-on loss is small. The drive signal of  $S_{sb}$  is the same as that of  $S_1$  and its current decreases to zero after a half of the sinusoidal resonant period so the turn-off loss in  $S_{sb}$  is also small. Figure 2.20 shows the measured output current which is the sum of  $i_{L1}$  and  $i_{D3}$  at 200W output with 25V input. Referring to Figure 2.20, the peak output current reaches 6.2A which is caused by energy stored in the leakage inductance of the transformer when  $D_3$  starts to conduct.

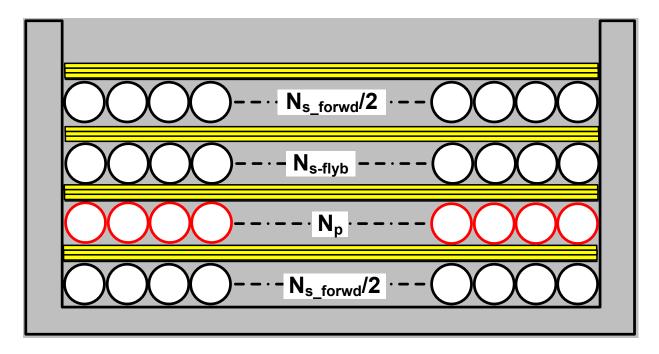

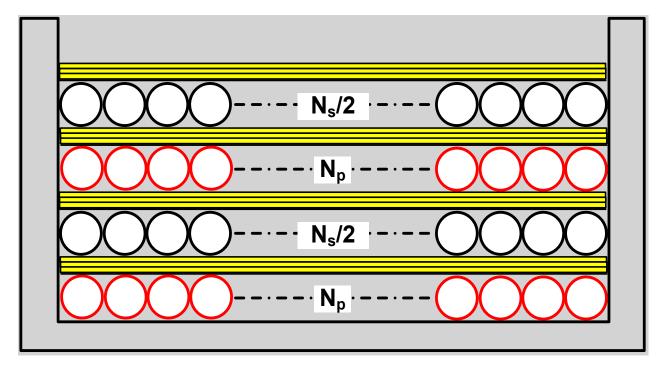

Although the method of sandwich winding for BMFFC is employed as shown in Figure 2.21, the leakage inductance is still 252nH due to the separated forward and flyback windings in the secondary. Although an efficient LC snubber circuit is employed, efficiency is negatively impacted by transformer leakage inductance. Therefore, it is very important to minimize this parameter in production.

Figure 2.20 Sum of output current from Forward and Flyback sections

Figure 2.21 Transformer construction of BMFFC

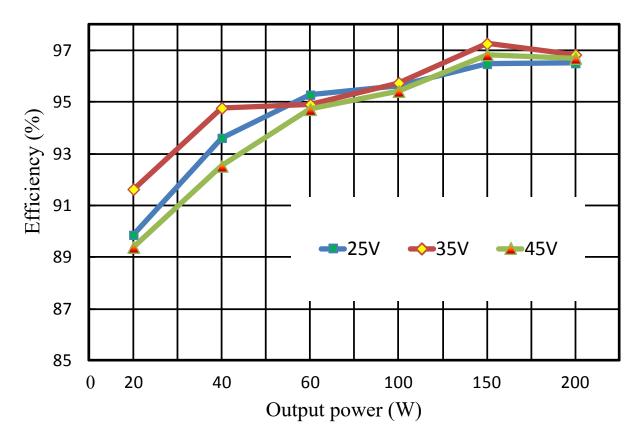

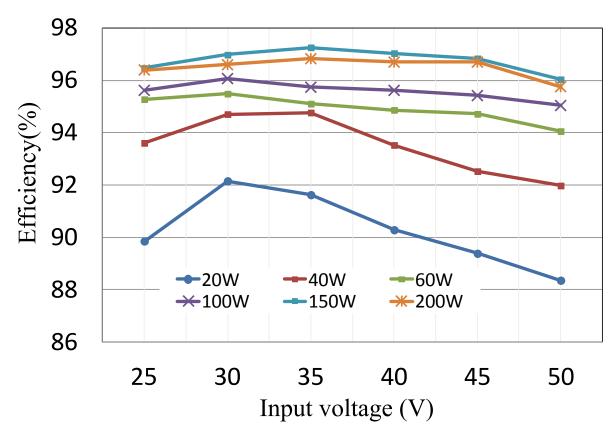

The measured efficiency of the tested 200W prototype with different input voltages is shown in Figure 2.22. With 35V input voltage, the maximum efficiency is 97.2% and the efficiency at full load is over 96.5%. The efficiency at full load with 45-V input voltage is 96.7%. Even the input voltage is decreased to 25 V. The maximum efficiency of the tested prototype is still higher than 96.5%. According to the experimental data, peak efficiency is achieved at 35V instead of 50V. The interesting phenomena emerged because a variable switching frequency control scheme is employed over the entire range of input voltage and output power. The higher the input voltage, the higher the switching frequency is. Figure 2.23 shows measured efficiency of BMFFC with varying input voltage and output power.

Figure 2.22 Measured efficiency of BMFFC according to the variation of the input voltage and output power

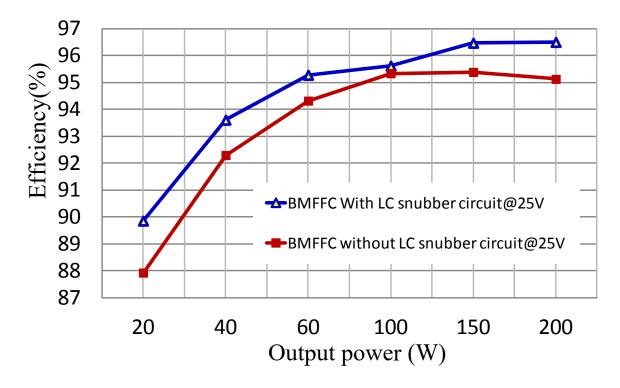

Figure 2.23 Measured efficiency of BMFFC according to the variation of the input voltage and output power. In order to observe the performance of an active LC snubber circuit, Figure 2.24 shows the measured waveforms of BMFFC without snubber circuit. As shown in Figure 2.24, the voltage spike across the MOSFET is 138V at 25V input and 200W output. Compared to Figure 2.14 with LC snubber circuit, the voltage spike is only 112V at the same condition. In addition, oscillation without the LC snubber circuit at turn off is worse than with LC snubber circuit. With the same transformer, MOSFET, and test bed, efficiency without the snubber circuit at 25V input and various power levels is shown in Figure 2.25. Note that 150V MOSFET should be changed to a higher voltage part if we want to measure efficiency without snubber circuit over the whole range of input voltage and output power. Obviously, the overall efficiency without the LC snubber circuit will drop due to conduction loss increase when a higher voltage MOSFET is used.

As mentioned previously, the efficiency at the minimum input voltage is a key factor in determining the size of the prototype. As shown in Figure 2.25, the overall efficiency without the LC snubber circuit is 0.5-1 percentage points less than with the LC snubber circuit. Therefore, it can be concluded that an active LC snubber circuit improves efficiency even though we select a point of comparison at 25V.

Figure 2.24 Measured waveforms of the BMFFC without LC snubber circuit at 200W with 25V

Figure 2.25 Efficiency comparison (with/without snubber circuit) with different output power at 25V input

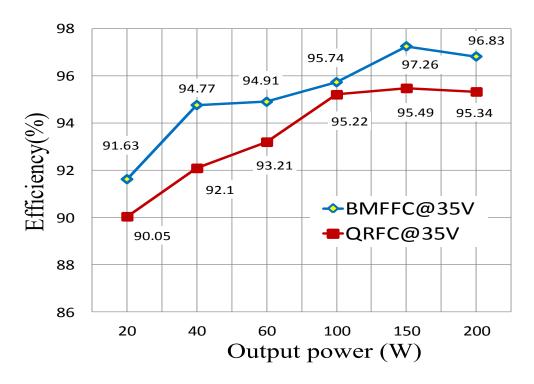

In order to see the superior performance of BMFFC, a conventional quasi-resonant flyback converter (QRFC) with the same MOSFET and diode was built for comparison purposes. Since the RM14 core can't deliver 200W at 50KHz and 25V input in the QRFC topology, a larger PQ40 core was selected for comparison with the BMFFC. Leakage inductance greatly impacts the conversion efficiency for flyback converter so an interleaved winding technique was employed as shown in Figure 2.26, where the main primary winding is paralleled, and the secondary winding is in series. This resulted in approximately 12nH of primary leakage inductance. The primary peak current is 27A at 25V input and 200W output. A conventional RCD snubber circuit was employed to suppress the MOSFET drain voltage spike. Using [36], the parameters of RCD circuit are R=1K, C=4.7nF, and MUR460. Figure 2.27 shows the

efficiency with varying output power of the BMFFC and conventional QRFC at 35V input. The efficiency of BMFFC and QRFC at 35V input is measured with different output power, respectively. As seen in Figure 2.27, the peak efficiency of the BMFFC at 35V is 1.77 percent points higher than QRFC with the same power level. In addition, the CEC (California Energy Commission) weighted efficiency is also plotted in Figure 2.28 at different input voltage because CEC efficiency is widely accepted as a key index to evaluate the performance of micro-inverter [44]. The BMFFC CEC efficiency with varying input voltage is obviously 1-1.5 percent points higher than QRFC, even though a larger PQ40 core is used for the QRFC.

Figure 2.26 Transformer construction of QRFC (Np=6 Parallel in primary, Ns=36 series connection in secondary)

Figure 2.27 Efficiency comparison with different output power between BMFFC and QRFC at 35V

Figure 2.28 BMFFC CEC weight efficiency comparison with QRFC

# 2.7 Summary

A Forward-Flyback converter with boundary mode operation to achieve ZVS has been proposed in this chapter 2. To further improve the efficiency through reducing turning-off losses, an active LC snubber is employed to suppress the voltage spike across the primary MOSFET switch and to recycle energy stored in the transformer leakage inductance. The operation of the converter is analyzed and a detailed design procedure is given to facilitate optimal design of the converter. A 200W BMFFC prototype was built and tested. The measured maximum efficiency reached 97.2%. The experimental results demonstrating better efficiency of the BMFFC over full range operation not only validate the operation of the converter but also confirm the superiority of the BMFFC over the conventional Forward-Flyback converter for low power applications.

### **CHAPTER THREE: DC-AC STAGE CONVERTER**

### 3.1 Introduction

For the three-phase DC/AC converter in the second stage, a variety of active soft switching topologies have been proposed in last three decades [45]-[58]. Most of them can be divided into three groups: auxiliary resonant commutated pole (ARCP) group [47]-[50], resonant DC-link inverter (RDCLI) group [51]-[56], and resonant AC-link converter (RACLC) [57] [58]. The ARCP can be applied broadly for the voltage-source-type single-phase or three-phase inverters but it requires a large number of auxiliary components. Compared to the ARCP, the RDCLI has the advantages of fewer auxiliary switches and a simpler circuit. Several soft switching topologies in [55]-[57] were proposed to achieve the minimum number of extra components. However, the driving signals of the auxiliary switches are very sensitive to the noise from the main circuit. Since the RACLC can achieve voltage boosting and electrical isolation at the same time, it is highly preferred for renewable energy power generation. Unfortunately, the control circuit for the RACLC is complex and bi-directional switches are required. In fact, auxiliary components are unavoidable for all of the soft switching topologies mentioned above.