Wayne State University Dissertations

January 2020

# Securing Arm Platform: From Software-Based To Hardware-Based **Approaches**

Zhenyu Ning Wayne State University

Follow this and additional works at: https://digitalcommons.wayne.edu/oa\_dissertations

Part of the Computer Sciences Commons

#### **Recommended Citation**

Ning, Zhenyu, "Securing Arm Platform: From Software-Based To Hardware-Based Approaches" (2020). Wayne State University Dissertations. 2393.

https://digitalcommons.wayne.edu/oa\_dissertations/2393

This Open Access Dissertation is brought to you for free and open access by DigitalCommons@WayneState. It has been accepted for inclusion in Wayne State University Dissertations by an authorized administrator of DigitalCommons@WayneState.

# SECURING ARM PLATFORM: FROM SOFTWARE-BASED TO HARDWARE-BASED APPROACHES

by

## **ZHENYU NING**

## **DISSERTATION**

Submitted to the Graduate School, of Wayne State University,

Detroit, Michigan

in partial fulfillment of the requirements

for the degree of

# **DOCTOR OF PHILOSOPHY**

| 2020            |         |

|-----------------|---------|

| MAJOR: COMPUTER | SCIENCE |

| Approved By:    |         |

| Advisor         | Date    |

# **DEDICATION**

To my wife and all my family.

### **ACKNOWLEDGEMENTS**

I wish to express my appreciation to those who supported and encouraged me in one way or another during the last five years.

First of all, I would like to express my gratefulness to my advisor, Dr. Fengwei Zhang, for his valuable guidance and continuous support during my Ph.D. study at Wayne State University. Dr. Zhang led me into the way of academic research and showed me the essentials of a researcher. His enthusiasm for research has encouraged me to achieve the degree. During the tough times in the Ph.D. pursuit, he showed me great patient and offered numerous hours to discuss with me, without which I cannot succeed.

I am also very grateful to Prof. Weisong Shi, Prof. Dongxiao Zhu, and Prof. Anyi Liu for serving as my dissertation committee and giving valuable suggestions on the dissertation. Your attitude on research helps me not only in the dissertation but also in my career.

Moreover, I would like to thank all the group members in COMPASS lab. Especially for Dr. Saeid Mofrad, Dr. Lei Zhou, and Dr. Jinghui Liao, we have had many brilliant ideas and exciting discussions.

Also, I deeply appreciate the support and love from my wife Qian Jiang. You give me light in the darkness and always make me hopeful. Thanks to my mother Weiping Zhu and my father Guoqiang Ning, I really hope you could see it.

# TABLE OF CONTENTS

| Dedicat   | 10n .  |                                                      | 11  |

|-----------|--------|------------------------------------------------------|-----|

| Acknow    | ledgen | nents                                                | iii |

| List of T | Tables |                                                      | ix  |

| List of F | igures |                                                      | X   |

| Chapter   | 1 Iı   | ntroduction                                          | 1   |

| Chapter   | 2 B    | Background                                           | 5   |

| 2.1       | Dalvik | x, Android Runtime, and Android Java Bytecode        | 5   |

| 2.2       | ARM 7  | TrustZone and Trusted Firmware                       | 6   |

| 2.3       | ARM I  | Debugging Architecture                               | 6   |

| 2.4       | Advan  | aced Transportation Controller and Roadside Cabinets | 7   |

|           | 2.4.1  | Malfunction Management Unit and Cabinet Monitor Unit | 8   |

| Chapter   | 3 R    | Reassembleable Bytecode Extraction on Android        | 10  |

| 3.1       | Introd | luction                                              | 10  |

| 3.2       | Relate | ed Work                                              | 12  |

|           | 3.2.1  | Static Analysis Tools                                | 12  |

|           | 3.2.2  | Dynamic Analysis Tools                               | 13  |

|           | 3.2.3  | Hybrid Analysis Tools                                | 13  |

|           | 3.2.4  | Unpacking and Reassembling in Traditional Platforms  | 14  |

| 3.3       | System | n Overview                                           | 15  |

|           | 3.3.1  | Bytecode and Data Collection                         | 15  |

|           | 3.3.2  | DEX File Reassembling                                | 16  |

|           | 3.3.3  | Code Coverage Improvement Module                     | 17  |

| 3.4     | Desigi | n and Implementation                               | 17 |

|---------|--------|----------------------------------------------------|----|

|         | 3.4.1  | Bytecode Collection                                | 18 |

|         | 3.4.2  | Bytecode Reassembling                              | 24 |

|         | 3.4.3  | Data Collection and DEX Reassembling               | 26 |

|         | 3.4.4  | Handling Reflection                                | 27 |

|         | 3.4.5  | Force Execution                                    | 27 |

| 3.5     | Evalua | ation                                              | 29 |

|         | 3.5.1  | RQ1: Test with Open-source Apps and Public Packers | 29 |

|         | 3.5.2  | RQ2: Test with Existing Tools                      | 30 |

|         | 3.5.3  | RQ3: Test with Real-world Packed Applications      | 35 |

|         | 3.5.4  | RQ4: Code Coverage                                 | 36 |

|         | 3.5.5  | RQ5: Performance                                   | 37 |

| Chapter | r 4 T  | Transparent Malware Analysis on ARM                | 40 |

| 4.1     | Introd | luction                                            | 40 |

| 4.2     | Relate | ed Work                                            | 41 |

|         | 4.2.1  | Transparent Malware Analysis on x86                | 41 |

|         | 4.2.2  | Dynamic Analysis Tools on ARM                      | 43 |

|         | 4.2.3  | TrustZone-related Systems                          | 44 |

| 4.3     | Systen | m Architecture                                     | 45 |

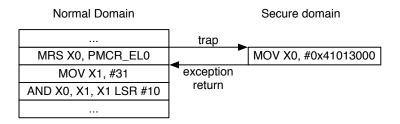

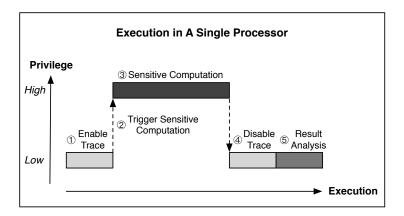

|         | 4.3.1  | Reliable Domain Switch                             | 46 |

|         | 4.3.2  | The Trace Subsystem                                | 46 |

|         | 4.3.3  | The Debug Subsystem                                | 47 |

| 4.4     | Design | n and Implementation                               | 48 |

|         | 4.4.1  | Bridge the Semantic Gap                              | 48 |

|---------|--------|------------------------------------------------------|----|

|         | 4.4.2  | Secure Interrupts                                    | 51 |

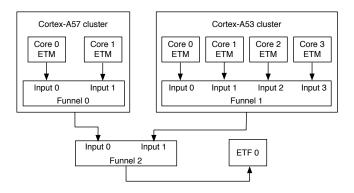

|         | 4.4.3  | The Trace Subsystem                                  | 51 |

|         | 4.4.4  | The Debug Subsystem                                  | 54 |

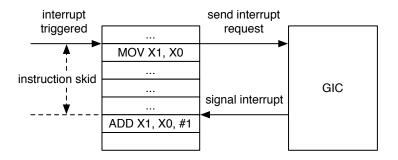

|         | 4.4.5  | Interrupt Instruction Skid                           | 57 |

| 4.5     | Transp | parency                                              | 58 |

|         | 4.5.1  | Footprints Elimination                               | 59 |

|         | 4.5.2  | Defending Against Timing Attacks                     | 61 |

| 4.6     | Evalua | ntion                                                | 63 |

|         | 4.6.1  | Output of Tracing Subsystem                          | 64 |

|         | 4.6.2  | Tracing and Debugging Samples                        | 64 |

|         | 4.6.3  | Transparency Experiments                             | 66 |

|         | 4.6.4  | Accessing Memory Mapped Interface                    | 67 |

|         | 4.6.5  | Performance Evaluation                               | 68 |

|         | 4.6.6  | Skid Evaluation                                      | 70 |

| Chapter | 5 U    | Inderstanding the Security of ARM Debugging Features | 72 |

| 5.1     | Introd | uction                                               | 72 |

| 5.2     | Securi | ty Implications of the Debugging Architecture        | 75 |

|         | 5.2.1  | Non-invasive Debugging                               | 75 |

|         | 5.2.2  | Invasive Debugging                                   | 76 |

|         | 5.2.3  | Summary                                              | 80 |

| 5.3     | Debug  | Authentication Signals in Real-World Devices         | 82 |

|         | 5.3.1  | Target Devices                                       | 83 |

|         | 5.3.2  | Status of the Authentication Signals                 | 85 |

|---------|--------|------------------------------------------------------|----|

|         | 5.3.3  | Management of the Authentication Signals             | 86 |

|         | 5.3.4  | Summary                                              | 88 |

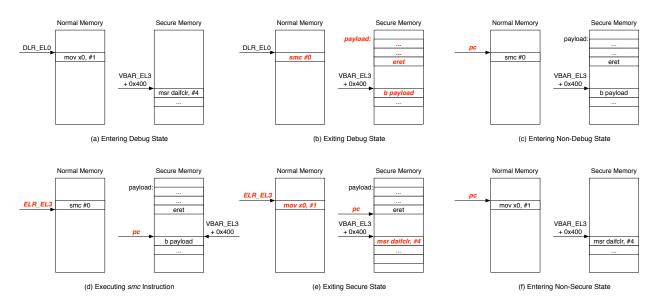

| 5.4     | Nailgu | ın Attack                                            | 89 |

|         | 5.4.1  | Threat Model and Assumptions                         | 89 |

|         | 5.4.2  | Attack Scenarios                                     | 90 |

| 5.5     | Count  | ermeasure                                            | 99 |

|         | 5.5.1  | Disabling the Signals?                               | 99 |

|         | 5.5.2  | Comprehensive Countermeasure                         | 01 |

| Chaptei | r 6 R  | desearch on Trusted Execution Environment            | 06 |

| 6.1     | Truste | d Execution Environments                             | 06 |

|         | 6.1.1  | Ring 3 TEEs via Memory Encryption                    | 06 |

|         | 6.1.2  | Ring -2 TEEs via Memory Restriction                  | 08 |

|         | 6.1.3  | Ring -3 TEEs via Co-Processors                       | 10 |

| 6.2     | Challe | enges Towards Securing Hardware-assisted TEEs        | 12 |

|         | 6.2.1  | Introduction                                         | 12 |

|         | 6.2.2  | TEE-based Systems                                    | 13 |

|         | 6.2.3  | Challenges and Directions                            | 18 |

| 6.3     | Prelim | ninary Study of TEEs on Heterogeneous Edge Platforms | 24 |

|         | 6.3.1  | Introduction                                         | 24 |

|         | 6.3.2  | Evaluation with Intel Fog Node                       | 25 |

|         | 6.3.3  | Evaluation with ARM Juno Board                       | 29 |

|         | 634    | Evaluation with AMD EPYC CPU                         | 32 |

| Chapter   | 7 Research on Traffic Signal Infrastructure        |

|-----------|----------------------------------------------------|

| 7.1       | Introduction                                       |

| 7.2       | Related Work                                       |

| 7.3       | Attack Surface Analysis                            |

|           | 7.3.1 Access to the Traffic Signal System          |

|           | 7.3.2 Traffic Signal Control                       |

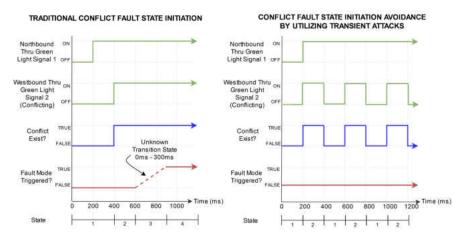

|           | 7.3.3 Conflict Status Control                      |

|           | 7.3.4 Troubleshooting of the Traffic Signal System |

| 7.4       | Attacks Implementation and Testing                 |

|           | 7.4.1 Environment Setup                            |

|           | 7.4.2 Thread Model                                 |

|           | 7.4.3 Attack Scenarios                             |

| Chapter   | 8 Conclusion and Future Work                       |

| 8.1       | Conclusion                                         |

| 8.2       | Future Work                                        |

| Reference | es                                                 |

| Abstract  |                                                    |

| Autobiog  | graphical Statement                                |

# LIST OF TABLES

| Table 1  | Test Result of Different Packers                                       |

|----------|------------------------------------------------------------------------|

| Table 2  | Analysis Result of Static Analysis Tools                               |

| Table 3  | Analysis Result of Packed Samples                                      |

| Table 4  | Analysis Result of Dynamic Analysis Tools and DexLego                  |

| Table 5  | Analysis Result of Packed Real-world Applications                      |

| Table 6  | Samples from F-Droid                                                   |

| Table 7  | Code Coverage with F-Droid Applications                                |

| Table 8  | Time Consumption of DexLego                                            |

| Table 9  | Comparing with Other Tools                                             |

| Table 10 | The TS Performance Evaluation Calculating 1 Million Digits of $\pi$ 68 |

| Table 11 | The TS Performance Evaluation with CF-Bench 69                         |

| Table 12 | Instructions in the Skid Shadow with Representative PMU Events 70      |

| Table 13 | Debug Authentication Signals on Real Devices                           |

| Table 14 | Context Switching Time of Intel SGX on the Fog Node ( $\mu s$ )        |

| Table 15 | Time Consumption of MD5 ( $\mu$ s)                                     |

| Table 16 | Performance Score by GeekBench                                         |

| Table 17 | Context Switching Time of ARM TrustZone ( $\mu$ s)                     |

| Table 18 | Time Consumption of MD5 ( $\mu$ s)                                     |

| Table 19 | Performance Score by GeekBench                                         |

| Table 20 | Time Consumption of MD5 ( $\mu$ s)                                     |

| Table 21 | Performance Score by GeekBench                                         |

# LIST OF FIGURES

| Figure 1  | Overview of DexLego                                                           | 14 |

|-----------|-------------------------------------------------------------------------------|----|

| Figure 2  | Just-in-Time Collection                                                       | 15 |

| Figure 3  | Data Structure Storing All Instructions in a Method During a Single Execution | 21 |

| Figure 4  | Iterative Force Execution                                                     | 28 |

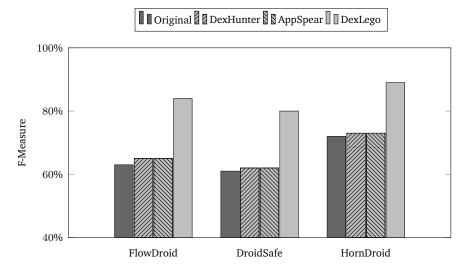

| Figure 5  | F-measures of Static Analysis Tools                                           | 34 |

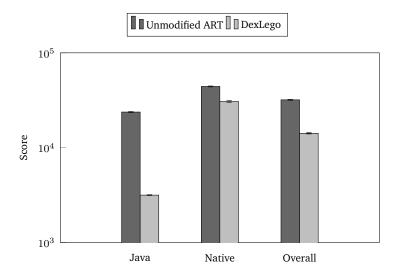

| Figure 6  | Performance Measured by CF-Bench                                              | 38 |

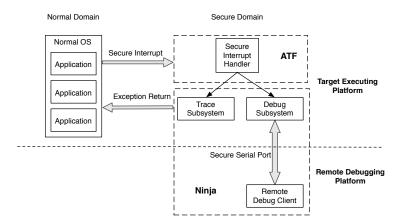

| Figure 7  | Architecture of Ninja                                                         | 45 |

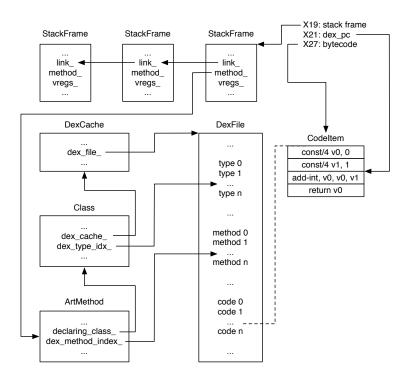

| Figure 8  | Semantics in the Function ExecuteGotoImpl                                     | 49 |

| Figure 9  | ETM in Juno Board                                                             | 52 |

| Figure 10 | Interrupt Instruction Skid                                                    | 58 |

| Figure 11 | Protect the PMCR_ELO Register via Traps                                       | 59 |

| Figure 12 | Accessing System Instruction Interface                                        | 66 |

| Figure 13 | Memory Mapped Interface                                                       | 67 |

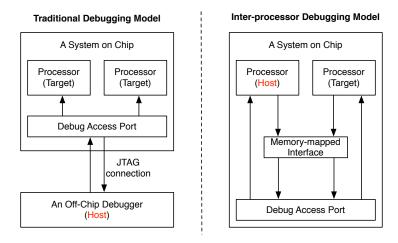

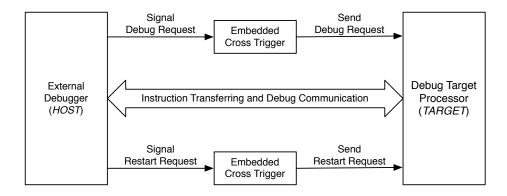

| Figure 14 | Debug Models in ARM Architecture                                              | 73 |

| Figure 15 | Invasive Debugging Model                                                      | 77 |

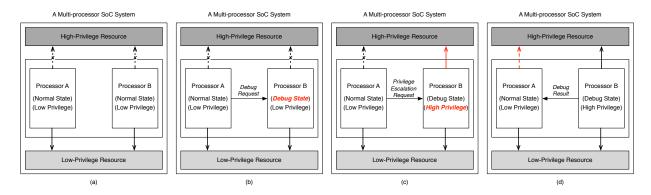

| Figure 16 | Violating the Isolation via Non-Invasive Debugging                            | 80 |

| Figure 17 | Privilege Escalation in A Multi-processor SoC System via Invasive Debugging.  | 81 |

| Figure 18 | Retrieving the AES Encryption Key                                             | 92 |

| Figure 19 | Executing Arbitrary Payload in the Secure State                               | 94 |

| Figure 20 | Executing Payload in TrustZone via an LKM                                     | 96 |

| Figure 21 | Fingerprint Image Leaked by Nailgun from Huawei Mate 7                        | 98 |

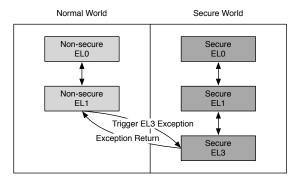

| Figure 22 | Processor Modes with ARM TrustZone                                          |

|-----------|-----------------------------------------------------------------------------|

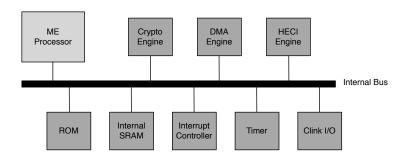

| Figure 23 | Architecture of Intel ME                                                    |

| Figure 24 | Datakey LCK4000 Microwire Flasher                                           |

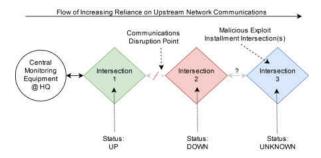

| Figure 25 | Diversionary Cabinet Access Tactic                                          |

| Figure 26 | Traffic Signal System in the Municipality Test Lab                          |

| Figure 27 | Traffic Signal System of TS-2 Standard                                      |

| Figure 28 | CMU-212 Display Unit                                                        |

| Figure 29 | All-direction Green Lights Being Displayed on Traffic Signal Test Equipment |

| Figure 30 | Transient Avoidance Attack Tactic                                           |

## CHAPTER 1 INTRODUCTION

ARM architecture has been wildly adopted in smart mobile phones and Internet of Things (IoT). In recent years, smart mobile phones and IoT devices become prevalent and important to our daily life. Unfortunately, these devices suffers from a variety of malware threats and internet attacks. According to the latest McAfee threats report, more than 1.5 million new malware samples on mobile device has been detected during the third quarter of 2018 [161]. To defend against these malware attacks, researchers need to analyze these samples to understand their behavior so that effective defenses can be developed.

As the most representative platform for mobile phones and IoT devices, Android dominate the mobile operate system market with more than 75% market share by the end of 2018 [238]. The dominative market also attracts the attentions of malicious developers and security researchers. To avoid of being detected by the analysis systems designed by the security researchers, the malicious developers play with the special Java virtual machine deployed in Android and adopt various techniques to hide the malicious behavior in the application [5, 42, 48, 113, 114, 151, 198, 248]. Specifically, these techniques aim to obfuscate the bytecode inside the application and mislead the analysis systems.

Other than the special techniques for Android, the traditional evasion trick helps the malware escape from being detected by the malware analysis system on ARM platforms. For example, some of the malware analysis systems on ARM platforms [73, 245, 277] are based on emulation or virtualization technology, and a series of anti-emulation and anti-virtualization techniques [131, 193, 258] have been developed to challenge them. To address this challenge, researchers study the malware on bare-metal devices via modify-

ing the system software [85, 194, 244, 294] or leveraging OS APIs [55, 295] to monitor the runtime behavior of malware. Although bare-metal based approaches eliminate the detection of the emulator or hypervisor, the artifacts introduced by the analysis tool itself are still detectable by malware. Moreover, privileged malware can even manipulate the analysis tool since they run in the same environment. How to build a transparent malware analysis system on ARM platform is still a challenging problem.

This transparency problem has been well studied in the traditional x86 architecture, and milestones have been made from emulation-based analysis systems [15, 234] to hardware-assisted virtualization analysis systems [76, 77, 147], and then to bare-metal analysis systems [140, 141, 236, 285]. As the state-of-the-art solution to the transparency problem on x86 architecture, [285] provide us a insight that the hardware-based design brings a better transparency for the analysis system.

The goal of our work it to provide a practical solution for the security-related problems on the ARM platforms. As the first attempt, we design a novel program transformation system that reveals the hidden code in Android applications to analyzable pattern via instruction-level extracting and reassembling. With this transformation, the hidden code protected by the aforementioned evasion techniques on Android (i.e., packing, reflection, dynamic loading and self-modifying) would be detectable for existing static analysis tools. Our system collects bytecode and data when they are executed and accessed, and reassembles the collected result into a valid DEX file for static analysis tools. One of the key challenges in our system is to reassemble the instructions into a valid and accurate DEX file. Hence, we design a novel reassembling approach to construct the entire executed control flows including self-modifying code. Additionally, we implement the first prototype of

force execution on Android and use it as our code coverage improvement module. Since we extract all executed instructions, our system is able to uncover the malicious behavior of the applications equipped with Android-specific evasion technique.

Next, to handle the traditional evasion techniques, we present a transparent malware analysis framework on ARM platform by leveraging hardware features including TrustZone technology, Performance Monitoring Unit (PMU), and Embedded Trace Macrocell (ETM). We implement a prototype of the framework that embodies a trace subsystem with different tracing granularities and a debug subsystem with a GDB-like debugging protocol on ARM Juno development board. In the prototype, we also protect the system registers via hardware traps and memory protection to keep the analysis system transparent to the target application.

Due to the heavy use of the hardware debugging features, we also dig into the ARM debugging architecture to acquire a comprehensive understanding of the debugging features. Although the debugging architecture has been presented for years, its security is under-examined by the community since it normally requires physical access to use these features. However, the real security aspects of the debugging architecture remains unclear. During the analysis, we find that physical access is not actually required to make use of the hardware debugging features. Consequently, we summarize a series of the security implications that is caused by the assumption of physical access. By exploiting these implications, we craft a novel attack scenario that works on a processor running in a low-privileged mode and accesses the high-privileged content of the system without restriction via the misusing the hardware debugging features.

The revealed privilege escalation vulnerability has raised our concern on the security

of the Trusted Execution Environment (TEE) and Cyber-physical Systems (CPS). For the security of TEE, we conduct an analysis on the widely deployed TEEs and summarize the challenges in securing these TEEs. A study of the deploying the TEEs on edge platform is also presented. For the security of CPS, we also perform an analysis on the real-world traffic signal systems to understand their security problems.

## **CHAPTER 2 BACKGROUND**

In this section, we introduce the basic concepts used in this paper. First, we explain the Java virtual machines deployed in Android. Then, I describe the design of ARM TrustZone and trusted firmware. The ARM debugging architecture is also explained.

# 2.1 Dalvik, Android Runtime, and Android Java Bytecode

Dalvik is a special Java virtual machine running in the Android system. It is used to interpret Android specified bytecode format since the first release of Android. To improve the performance, Google has introduced Just-In-Time (JIT) compilation and Ahead-Of-Time (AOT) compilation since Android 2.2 and Android 4.4, respectively. The JIT compilation continually compiles frequently executed bytecode slices into the machine code. As an upgrade, the AOT compilation compiles most bytecode in the application into the machine code during the installation. Dalvik equipped with AOT compilation is renamed to Android Runtime (ART). Since Android 5.0, Dalvik has been completely replaced by ART.

In both Dalvik and ART, the Java source code is compiled to Dalvik Executable (DEX) files which includes the bytecode for the Android Java virtual machine. The bytecode in DEX files is organized in units of methods. The minimum code unit for JIT and AOT compilation is a method, indicating that a single method cannot contain both bytecode and machine code. Methods such as constructors and abstract methods require the bytecode interpreter even in ART. Moreover, a single method or the entire ART can be configured to run in the interpreter mode.

The Java bytecode in Android is chained by instructions. Each instruction contains an opcode and arguments related to the opcode. The opcodes are different from the ones in

regular Java bytecode and the bit-length of an instruction varies according to the opcode. In the interpreter, instructions are listed in an array of 16-bit (2 bytes) units. An instruction occupies at least one unit with a maximum number of units up to five.

### 2.2 ARM TrustZone and Trusted Firmware

ARM TrustZone technology [31] introduces a hardware-assisted security concept that divides the execution environment into two isolated domains, i.e., secure domain and non-secure domain. Due to security concerns, the secure domain could access the resources (e.g., memory and registers) of the non-secure domain, but not vice versa. In ARMv8 architecture, the only way to switch from normal domain to secure domain is to trigger a secure exception [20], and the exception return instruction eret is used to switch back to the normal domain from the secure domain after the exception is handled.

ARM Trusted Firmware [30] (ATF) is an official implementation of secure domain provided by ARM, and it supports an array of hardware platforms and emulators. While entering the secure domain, the ATF saves the context of the normal domain and dispatches the secure exception to the corresponding exception handler. After the handler finishes the handling process, the ATF restores the context of the normal domain and switches back with eret instruction. ATF also provides a trusted boot path by authenticating the firmware image with several approaches like signatures and public keys.

# 2.3 ARM Debugging Architecture

The ARM architecture defines both invasive and non-invasive debugging features [18, 20]. The invasive debugging is defined as a debug process where a processor can be controlled and observed, whereas the non-invasive debugging involves observation only

without the control. The debugging features such as breakpoint and software stepping belong to the invasive debugging since they are used to halt the processor and modify its state, while the debugging features such as tracing (via the Embedded Trace Macrocell) and monitoring (via the Performance Monitor Unit) are non-invasive debugging.

The invasive debugging can be performed in two different modes: the halting-debug mode and the monitor-debug mode. In the halting-debug mode, the processor halts and enters the debug state when a debug event (e.g., a hardware breakpoint) occurs. In the debug state, the processor stops executing the instruction indicated by the program counter, and a debugger, either an on-chip component such as another processor or an off-chip component such as a JTAG debugger, can examine and modify the processor state via the Debug Access Port (DAP). In the monitor-debug mode, the processor takes a debug exception instead of halting when the debug events occur. A special piece of software, known as a monitor, can take control and alter the process state accordingly.

# 2.4 Advanced Transportation Controller and Roadside Cabinets

The traffic signals in the intersections are controlled by the Advanced Transportation Controller (ATC). The ATC makes logical decisions based on its inputs and configuration settings to implement traffic patterns. This configuration, based upon what is called the signal timing plan [257], holds parameters such as what duration to run which traffic patterns along with the minimum and maximum times to run the pattern.

According to the ATC standard [2] released by American Association of State Highway and Transportation Officials (AASHTO) [1], Institute of Transportation Engineers (ITE) [124], and National Electrical Manufacturers Association (NEMA) [171], the ATC

is built upon a Linux kernel with BusyBox integration, supporting a capable networking stack and access to most typical Linux shell operations such as FTP and SSH. On top of the kernel, the actual control logic is left to the individual software running in the ATC, and the municipalities may use different software according to their specific requirements and existing infrastructure.

The ATC is normally placed in a roadside cabinet. There are mainly two standards for the cabinet, i.e., the TS-2 standard [170] designed by NEMA and the Intelligent Transportation System (ITS) standard [115] developed by ITE.

The TS-2 Cabinet Standard [170] is a traffic signal cabinet standard that was initially commissioned by NEMA in 1998. The core feature of the modern TS-2 cabinet is its use of a single IBM SDLC serial bus for inter-device communications within the cabinet. The ITS Cabinet standard [115] is designed to supersede the NEMA TS-2 standard. By effectively using two serial buses, the ITS Cabinet maintains separation between the control plane of the traffic signal's relays and the supervisory bus shared between the traffic controller unit and fail-safe unit. Since the control planes (failure handling, signal control, environmental sensing) is separated into different buses, the congestion and latency on the bus are reduced.

### 2.4.1 Malfunction Management Unit and Cabinet Monitor Unit

As specified in the NEMA TS-2 Cabinet specification, the Malfunction Management Unit (MMU) is designed to accomplish the detection of, and response to, improper and conflicting signals. If an MMU detects that any monitoring parameter is out-of-range or in disagreement with the expectation, the MMU will override the control of the ATC, and the intersection is placed into a known-safe state called "conflict flash". Conflict flash is a state

in that all intersection operations are halted and individual traffic signal will be instructed to strobe their red lights. In order to return the operation of an intersection to a normal state, the MMU must be manually reset by a technician on-site.

The functionality of the Cabinet Monitor Unit (CMU) in the ITS cabinet is similar to the MMU in the TS-2 cabinet. The ITS Cabinet specification states that the minimum functionality of CMU is as least that provided by the NEMA TS-2 MMU. Additionally, the CMU offers enhanced monitoring and logging capabilities for items such as electrical voltages seen on cabinet peripherals, operating temperatures, and access controls.

# CHAPTER 3 REASSEMBLEABLE BYTECODE EXTRACTION ON ANDROID

## 3.1 Introduction

For a better understanding of the malware behaviors on Android, a series of static analysis tools [33, 58, 98, 148, 265] and dynamic analysis tools [85, 244, 245, 277, 294] are designed. However, these tools suffer from some common disadvantages.

First, static analysis tools identify the malicious behavior of an application by investigating bytecode in Dalvik Executable (DEX) files, which is compiled from the Java source code and embedded in the Android Package (APK) file of the application. Due to the popular usage of the public packing platforms [5, 42, 114, 151, 198, 248], the original DEX file of the application may be encrypted and replaced by another shell DEX file, while the shell DEX file would decrypt the original DEX file and release it at runtime. In this case, static analysis tools are completely unarmed as they can only fetch the shell DEX file but not the encrypted original DEX file. Existing solutions [278, 293] to the packing technique assume that there is a point when all original code is unpacked in memory, which is not held with sophisticated adversaries [48, 113]. Moreover, the Java reflection and dynamic loading code are still a challenging task for the static analysis tools [33, 58, 98].

Second, although the dynamic analysis tools [85, 244, 245, 277, 294] do not suffer from the aforementioned techniques, they have their own drawbacks. The automatic dynamic taint flow analysis tools [85, 244, 294] cannot handle implicit taint flows while static analysis tools [148, 265] can solve them. Moreover, the huge performance overhead makes it difficult to implement a complicated analysis mechanism, so there is a trade-off between the accuracy and performance. Meantime, the code coverage problem also

threatens the accuracy of the dynamic analysis tools [245, 277, 294].

We present DexLego, a novel program transformation system that reveals the hidden code in Android applications to analyzable pattern via instruction-level extracting and reassembling. DexLego collects bytecode and data when they are executed and accessed, and reassembles the collected result into a valid DEX file for static analysis tools. Since we extract all executed instructions, our system is able to uncover the malicious behavior of the packed applications or malware with self-modifying code. One of the key challenges in DexLego is to reassemble the instructions into a valid and accurate DEX file. Hence, we design a novel reassembling approach to construct the entire executed control flows including self-modifying code. Additionally, we implement the first prototype of force execution on Android and use it as our code coverage improvement module.

Moreover, our system helps static analysis tools improve the analysis accuracy on reflection samples. The Java reflection obscures the control flows of the application by replacing the direct function call or field access with a call to the reflection library functions which take the name string of the function or field as parameter. Previous reflection solutions [45] and static analysis tools [33, 58, 98] on Android assume that the name strings of the reflectively invoked method and its declaring class are reachable. However, the name string can be encrypted in some cases [204] and the advanced malware could even use reflective method calls without involving any string parameter [83]. A solution on traditional Java platform [49] requires load-time instrumentation which is not supported in Android [33]. Thus, DexLego implements a similar idea in Android and replaces the reflective call with direct call.

We evaluate DexLego on real-world packed applications and DroidBench [83]. The

evaluation result shows DexLego successfully unpack and reconstruct the behavior of the applications. The F-measures (i.e., analysis accuracy) of FlowDroid [33], DroidSafe [98], and HornDroid [58] on DroidBench increase 33.3%, 31.1%, and 23.6%, respectively. Moreover, static analysis tools with the help of DexLego provide a better accuracy than existing dynamic analysis systems TaindDroid [85] and TaindART [244]. The code coverage experiments on open source samples from F-Droid [86] show that our force execution module helps to improve the coverage of dynamic analysis and increases the coverage of state-of-the-art fuzzing tool, Sapienz [158], from 32% to 82%.

## 3.2 Related Work

# 3.2.1 Static Analysis Tools

FlowDroid [33] is a static taint-analysis tool for Android applications, and it achieves a high accuracy by mitigating the gaps between lifecycle methods and callback methods. Amandroid [265] and IccTA [148] aim to resolve the implicit control flows during intercomponent communication. EdgeMiner [59] links the callback methods with their registration methods to facilitate the static analysis tools in gaining more precise results. Droid-Safe [98] implements a simplified model of the Android system and solves native code in the Android framework by manually analyzing the source code and writing stubs for them in Java. HornDroid [58] generates Horn clauses from the bytecode of application and performs both value-sensitive and flow-sensitive analysis on the clauses. HSOMiner [189] uses machine learning algorithms to discover the hidden sensitive operations by analyzing the branch instructions and their related conditional branches.

### 3.2.2 Dynamic Analysis Tools

DroidScope [277] provides an instrumentation tool to monitor the executed bytecode and native instructions to help analysts learn the malware manually. VetDroid [294] executes the Android applications by a custom application driver and performs a permission usage behavior analysis. CopperDroid [245] traces the system calls and reconstructs the behavior of the target application. TaintDroid [85] and TaintART [244] are taint flow analysis system on different Android Java virtual machines. They track the information flow of the target application at runtime and report the data leakage from sink methods. DexHunter [293] focuses on how to dump the whole DEX file from memory at a "right timing". AppSpear [278] leverages the key data structures in Dalvik to reassemble the DEX file and claims that these data structures are reliable. Both DexHunter and AppSpear assume that there is a clear boundary between the unpacking code and the original code. However, the unpacking code and malicious code may intersperse with each other. Moreover, advanced malware can modify bytecode and data in the DEX file at runtime, and thus the previous dump-based unpacking systems will miss the content modified after the dump procedure.

### 3.2.3 Hybrid Analysis Tools

Harvester [204] collects runtime values and injects these values into the DEX file for the accuracy improvement of analysis tools. However, some limitations still exist. Firstly, marking logging points and backward slicing are based on the original DEX file. If packing is considered, Harvester loses its target like other static analysis tools. In contrast, DexLego does not analyze the original DEX file. Additionally, Harvester greatly facilitates

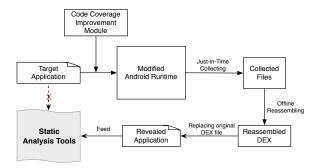

Figure 1: Overview of DexLego.

static analysis tools on solving reflections as they reduce the parameters back into constant strings. However, malware can use advanced reflection code to evade the analysis. Since DexLego replaces the reflective call with direct call, we do not care about how the adversaries use reflection.

# 3.2.4 Unpacking and Reassembling in Traditional Platforms

Ugarte et al. [256] present a summary of recent unpacking tools and develop an analysis framework for measuring the complexity of a large variety of packers. CoDisasm [50] is a dissembler tool that takes memory snapshot during execution and disassembles the captured memory. Uroboros [264] aims to disassemble binaries with a reassembleable approach. Their reassembling method is based on the disassembling output of Uroboros. DexLego is different from these systems as we do not disassemble the binary or monitor memory. [276] collects the instruction trace at runtime and performs taint analysis on the trace. Unlike [276], DexLego aims to facilitate the other static analysis tools and outputs a standardized DEX file, which could be used for state-of-the-art static analysis tools to perform different kinds of analysis including taint analysis.

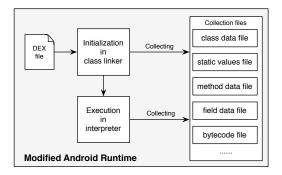

Figure 2: Just-in-Time Collection.

# 3.3 System Overview

As Figure 1 shows, instead of directly feed the target application to static analysis tools, we firstly execute the target application with DexLego. In executing, we use Just-in-Time (JIT) collection to extract data/instructions and output them to files right before used by ART. In the meantime, we use a code coverage improvement module to increase the code coverage. Next, we reassemble the collected files to a DEX file and use the reassembled DEX file to replace the one in the original APK. Finally, the new APK file is fed to the static analysis tools. The architecture of DexLego contains three main components:

1) the collecting component that collects bytecode and data, 2) the offline reassembling component that reassembles a new DEX file based on the collection result, and 3) the code coverage improvement module that helps DexLego to achieve a high code coverage. Next, we will discuss the three components respectively.

# 3.3.1 Bytecode and Data Collection

Figure 2 shows the JIT collection we used in DexLego. During the execution of an application, ART firstly extracts the DEX file from the original APK file and passes it to the class linker. The class linker then loads and initializes the classes in the DEX file, and

our JIT collection method collects the metadata of the class (e.g., super class) at this point. Next, when a method is invoked, ART extracts its bytecode from the DEX file, and leverages the interpreter to execute them. The interpreter fetches the entire bytecode (organizing in a 16-bit array) of the method and executes the bytecode instructions one by one. Thus, according to our JIT policy, we collect the executed instructions of the method and their related objects (e.g., string) via instruction-level extracting. Note that the execution of the code in the dynamic loaded DEX file also follows the same flow.

The state-of-the-art static analysis tools do not accept machine code as their input. However, ART executes most methods based on the machine code, and the translation from the machine code to the bytecode is a challenging task. To simplify the task, DexLego configures all methods in the application to be executed by the interpreter.

# 3.3.2 DEX File Reassembling

After the collecting, all the output files are reassembled to a new DEX file offline following the format of a DEX file, and we replace the DEX file in the original APK file with the reassembled one. The modified APK file is finally fed to static analysis tools to study the malicious behavior.

This reassembling is not trivial, and we consider this is the key contribution of this work. In the DEX file format, each method contains only one instruction array. However, due to different control flows (e.g., execution is led to different branches of a branch statement) or self-modifying code, one method may contain different instruction arrays in the collection stage. To correctly combine the collected instructions, we thus design a tree model and a novel collecting and reassembling mechanism. More details are discussed in Section 3.4.1 and Section 3.4.2.

# 3.3.3 Code Coverage Improvement Module

To improve the code coverage of dynamic analysis systems, there already exists a series of tools or theories like: 1) Input generators or fuzzing tools [6, 41, 97, 105, 157], 2) Symbolic or concolic execution [12, 57, 166, 204, 270, 279] based systems, 3) Force execution [75, 139, 191] based systems. Our code coverage improvement module can be one of them or a combination of them. Note that most of the systems mentioned in 1) and 2) are implemented in Android, and we can directly use them to conduct the execution of the target application with little engineering effort. However, to the best of our knowledge, the idea of force execution has not been applied on Android platform. Thus, we implement a prototype of force execution as a supplement of our code coverage improvement module.

To use force execution in DexLego, we identify the Uncovered Conditional Branches (UCB) and calculate the path to each UCB. By monitoring and manipulating the branch instructions in the interpreter, we force the control flow to go along the calculated path to reach each UCB.

# 3.4 Design and Implementation

We implement DexLego in an LG Nexus 5X with Android 6.0. Based on the Android Open Source Project [94] (AOSP), we build a customized system image and flash it into the device by leveraging a third-party recovery system [247].

A DEX file consists of data structures that represent different data types used by the interpreter [96]. DexLego collects these data structures directly from memory while they are used by ART at the runtime. Moreover, we leverage instruction-level tracing to collect executed instructions and reassemble them back to a method structure. In this section, we

```

package com.test;

public class Main extends Activity {

private static final String PHONE = "800-123-456";

protected void onCreate(Bundle savedInstanceState) {

advancedLeak();

8

9

10

public void advancedLeak() {

String a = getSensitiveData(); // source

11

for (int i = 0; i < 2; ++i) {

13

normal(a);

bytecodeTamper(i);

14

15

16

17

public void normal(String param) {

18

// do something normal

19

20

21

public void sink(String param) {

// send param through text message.

23

24

SmsManager.getDefault().sendTextMessage(PHONE, null, param, null, null); // sink

25

26

27

/* While i = 0:

* modify Line 11 to String a = "non-sensitive data"

28

modify Line 13 to sink(a)

* While i = 1:

30

31

modify Line 11 to String a = getSensitiveData()

modify Line 13 to normal(a) */

32

public void native bytecodeTamper(int i);

33

34

```

Code 1: An Example of Self-Modifying Code.

discuss 1) bytecode collection, 2) bytecode reassembling, 3) data collection, and 4) DEX file reassembling separately. The approaches to handle reflection and force execution are also discussed in this section.

# 3.4.1 Bytecode Collection

In ART, after the instruction array of a method is passed to the interpreter, the interpreter executes the instructions one by one following the control flow indicated by them. To expose the behavior of the method, DexLego aims to collect all instructions executed in the method. However, existing systems [278, 293] that use method-level collection cannot defend against dynamic bytecode modification, and the detailed limitation is described as below.

Inadequacy of Method-level Collection. Consider Code 1 as an example. While entering the method advancedLeak, the small code <sup>1</sup> of the method is represented by Code 2. After the first execution of the native method bytecodeTamper, the code of the method advancedLeak is modified to Code 3. In Code 3, the native method has modified the bytecode to hide the source (Lines 2-4 are changed from Code 2 to Code 3), but the sensitive data is already stored in the register v0. During the second execution of the for loop, the sensitive data in the register v0 is leaked through the method sink (Lines 9-10 in Code 3). Then, the native method resumes the code back to Code 2. The instruction array of the method advancedLeak in memory is either Code 2 or 3 at any time point (e.g., before and after JNI code), which means that the method-level collection (e.g., DexHunter [293] and AppSpear [278]) can only collect Code 2 or 3 even when multiple collections are involved. However, in the static taint flow analysis, the red lines in Code 2 (Lines 2-4) represent a source, but the data fetched from the source are sent to the blue lines (Lines 9-10) which are not a sink. In Code 3, the red lines (Lines 9-10) are a sink, but the received data are obtained from the blue lines (Lines 2-4) which are not a source. Thus, the leak of the sensitive data can be identified from neither Code 2 nor Code 3, and the key reason is that the code representing the source and sink are modified on purpose to hide the taint flow. AppSpear claims that it implements an instruction-level tracing mechanism, however, as we will explain below, simply tracing the instructions does not satisfy the requirement of static analysis tools.

**Instruction-level Collection and Tree Model.** In light of the shortcoming of method-level collection as described above, the DexLego leverages instruction-level collection to defend

<sup>&</sup>lt;sup>1</sup>The smali code is a more readable format of the bytecode.

```

.method public advancedLeak()V

invoke-virtual p0 , \setminus

Lcom/test/Main;->getSensitiveData()Ljava/lang/String;

3

move-result-object v0

const/4 v1, 0

: 1.0

const/4 v2, 2

if-ge v1, v2, :L1

invoke-virtual p0, v0 , \

9

10

Lcom/test/Main; ->normal(Ljava/lang/String;)V

invoke-virtual { p0, v1 }, \

11

Lcom/ecspride/Main;->bytecodeTamper(I)V

add-int/lit8 v1, v1, 1

13

14

goto :L0

15

:L1

return-void

17 .end method

```

Code 2: Small representation of the method advancedLeak while entering and leaving it.

against self-modifying code such as Code 1. One simple approach for instruction-level collection is to list all the executed instructions one by one; however, this approach leads to a code scale issue. Take the loop as an example, since the instructions in a loop are executed for multiple times, the simple approach would lead to a large number of repeating instructions. Moreover, the branch statements and self-modifying code make it possible that different executions of a single method lead to different instruction sequences. However, the format of the DEX file [96] allows only one instruction sequence for a single method.

```

1 .method public advancedLeak()V

const-string v0, "non-sensitive data"

nop

const/4 v1, 0

:L0

6

const/4 v2, 2

8

if-ge v1, v2, :L1

invoke-virtual p0, v0 , \

10

Lcom/test/Main;->sink(Ljava/lang/String;)V

invoke-virtual { p0, v1 }, \

11

Lcom/ecspride/Main; ->bytecodeTamper(I)V

13

add-int/lit8 v1, v1, 1

14

goto :L0

15

:L1

return-void

16

17 .end method

```

Code 3: Small representation of the method advancedLeak after the first execution of the method bytecodeTamper.

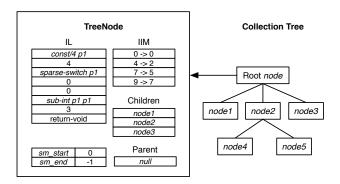

Figure 3: Data Structure Storing All Instructions in a Method During a Single Execution. The right tree structure shows the collection result for a method during a single execution. The left rectangle describes the data structure of each tree node. For each execution of a method, we generate a collection tree.

To address the code scale issue, DexLego eliminates repeating instructions by comparing the instructions with same indices. As mentioned above, the bytecode of a method is organized in a 16-bit unit array and passed to the interpretation functions (ExecuteSwitchI-mpl and ExecuteGotoImpl functions). In these functions, the interpreter uses a variable dex\_pc to represent the index of the executing instruction in the array. In light of this, we identify repeating instructions by comparing the executing instructions with the same dex\_pc values. Moreover, the self-modifying code can also be identified by the comparison. Different instructions with the same dex\_pc value actually indicate a runtime modification.

Algorithm 1 illustrates the comparison-based instruction collection algorithm, and Figure 3 shows the related data structures. We consider the first execution of an instruction as a baseline and any different instructions with the same dex\_pc value as a divergence branch. Thus, each divergence branch indicates a piece of self-modifying code. Note that self-modifying code might also exist in the divergence branch (like multiple layers of self-modifying). The divergence branches in a method then form a tree structure. The right part of Figure 3 shows an example of the final collecting result. Nodes 1-3 represent three

## **Algorithm 1** Bytecode Collection Algorithm

```

1: procedure BytecodeCollection

create node root

current = root

3:

for each executing instruction ins do

4:

let index of ins be dex pc

5:

if dex pc exists in current.IIM then

6:

pos\ in\ IL = current.IIM.get(dex\_pc)

7:

old\_ins = current.IL.get(pos\_in\_IL)

if !SameIns(ins, old ins) then

9:

create a child node child

10:

child.parent = current

11:

child.start\ pos = dex\ pc

12:

current = child

13:

else

14:

continue

15:

end if

16:

else if current has a parent then

17:

parent = current.parent

18:

if dex pc exists in parent.IIM then

19:

pos\ in\ IL = parent.IIM.get(dex\ pc)

20:

old\ ins = parent.IL.qet(pos\ in\ IL)

if SameIns(ins, old ins) then

22:

current.end pos = dex pc

current = parent

24:

continue

end if

26:

end if

end if

28:

pos\ in\ IL = current.IL.size()

29:

current.IL.add(ins)

30:

current.IIM.push(pair(dex\_pc, pos\_in\_IL))

31:

end for

33: end procedure

```

pieces of self-modifying code on the root node, and Nodes 4-5 represent two pieces of self-modifying code on Node 2. The left rectangle in Figure 3 shows the TreeNode structure which represents a node in the tree structure. The Instruction List (IL) in the structure includes the list of executed instruction and their metadata. The instructions in IL are recorded by the order of their first execution and the IL plays the role of baseline in the node. The dex\_pc value of an instruction may be different from its index in IL due to branch statements, and we use an Instruction Index Map (IIM) to maintain the mapping

between the instruction's dex\_pc value and its index in IL for further comparison. sm\_start and sm\_end indicate the starting and ending dex\_pc value of the divergence branch, while parent and children represent the parent and all children of the node, respectively. With the tree structure, DexLego records all executed instructions in a single execution of a method and maintains the code size similar to the original instruction array.

In Algorithm 1, we only update one node during the execution of a single instruction, and this node is considered as the current node. DexLego creates an empty root node as the current node while entering a method. Once an instruction is executed, we check IIM of the current node to find whether the dex\_pc value of this instruction has been recorded. If it does not exist in IIM, DexLego pushes the instruction into IL and updates IIM. If the dex\_pc value already exists in IIM, we add a check procedure to find whether the instruction is the same as the one we recorded before. A positive result means that the same instruction in the same position is executed again, and DexLego does not record it. In contrast, the negative result indicates that modification has occurred to this instruction since its last execution. Then, we create a child node of the current node to represent the divergence branch, and the new node becomes the current node. After that, DexLego treats the instruction as a new instruction and pushes it into IL of the current node. In a divergence branch, another check procedure is added to each instruction, and this check procedure aims to identify whether the current divergence branch converges to its parent. If the same instruction with the same dex\_pc value has been found in the parent's IL, we consider that the divergence branch converges back to its parent (e.g., current layer of self-modifying code ends) and make the parent node to be the new current node.

Listing 1 shows a high-level semantic view of the collection result of the method

advancedLeak in Code 1. When Line 13 in Code 1 is executed for the first time, an invocation of the method normal is recorded. Then, in the second run, an invocation of the method sink is detected. However, by comparing with the recorded instructions, DexLego finds that it is a divergence point. A child node is forked and the instruction is pushed into the IL of the child node. Furthermore, a convergence point is found when Line 14 is executing. Thus, the collection tree contains a root node and a child node, and the child node contains only one instruction. With the tree, the executed instructions and the control flows in the method are well maintained. Note that the modification to the Line 11 is ignored since the modified instructions are never executed.

```

Root Node:

String a = getSensitiveData();

for (int i = 0; i < 2; ++i) {

normal(a);

bytecodeTamper(i);

}

Child Node: (Line 13 in Code 1)

sink(a);</pre>

```

Listing 1: High-level Semantic View of the Collection Result of the Method advancedLeak in Code 1.

For the issue of multiple instruction sequences for a single method, we generate multiple collection trees for multiple executions of the method and keep only the unique trees. The trees are further combined together with the approach detailed in Section 3.4.2.

### 3.4.2 Bytecode Reassembling

The offline reassembling-phase merges the collected trees into a DEX file while holding all the executed instructions and control flows. There are two steps in this phase: 1) converting each tree into an instruction array. 2) merging instruction arrays into the DEX file.

```

String a = getSensitiveData();

for (int i = 0; i < 2; ++i) {

if (Modification.com_test_Main_advancedLeak_0) {

normal(a);

} else {

sink(a)

}

bytecodeTamper(i);

}</pre>

```

Code 4: Reassembled Result of the Method advancedLeak in Code 1.

Converting a Tree into an Instruction Array. Each node in the collection tree generated from the collection phase contains an independent Instruction List (IL), and the goal of this phase is to combine the ILs in the nodes together without losing any control flows or instructions. To simplify the combination process, we traverse the nodes with the bottom-up fashion since the leaf nodes contain no child node.

To merge a single leaf to its parent, DexLego inserts an additional branch instruction in the divergence point (indicated by sm\_start, self-modifying start, as defined in the above subsection 3.4.1), with one branch of the instruction pointing to the leaf. To make both conditional branches reachable, the conditional expression of the added branch instruction is calculated based on a static field of an instrument class with random values. Note that the random value produces indeterminacy problem on the additional branch instruction, and we consider it acceptable since the static analysis tool will take both branches of the instruction as reachable.

Once the leaf nodes are recursively merged into their parents, the root node becomes a complete set of the collected instructions including different control flows triggered during the execution.

Code 4 demonstrates the reassembled result of Listing 1. The static field com\_test\_Main\_advancedLeak\_0 in our instrument class Modification indicates the divergence point in Line 13 of Code 1. When this result is fed to static analysis tools, they treat both normal and sink as reachable and detect the taint flow from sensitive data to text message in Code 1.

**Merging Instructions Arrays.** For each executed method, the previous phase outputs unique instruction arrays which indicate different executions of the method. Similar to the approach discussed above, we create a method variant for each instruction array and use additional branch instructions to cover different method variants.

# 3.4.3 Data Collection and DEX Reassembling

As mentioned in Section 3.3.1, besides bytecode instructions, DexLego uses JIT collection to collect the metadata of DEX file. The collected data is written into collection files and further used to reassemble a new DEX file offline.

In Code 1, before any method or field in Main is accessed, the class Lcom/example/Main; is loaded and initialized. During the process, we firstly store string Lcom/example/Main; into a string structure and record the index of this string structure. Then with the index, a type structure is constructed and stored. Finally, a corresponding class structure related to the type is extracted. The collection occurs again when the class is initialized. The initialization procedure links the methods and fields to the class, and initializes the static fields. In Code 1, methods onCreate, advancedLeak, normal, and sink are linked to the class. While the static field PHONE is initialized, DexLego stores its name PHONE, type Ljava/lang/String; and initial value 800-123-456. Lastly, a field structure is created and recorded. The method structures and the bytecode inside them are collected before and during the execution of the methods, respectively.

After the collection process, all collection files including bytecode are combined offline

according to the format of the DEX file. Finally, we leverage the Android Asset Packaging Tool integrated with Android SDK to replace the DEX file in the original APK file with the reassembled one. To verify the soundness of our extracting and reassembling algorithm, we perform extensive tests against real-world applications, and the evaluation results in Section 3.5.1, Section 3.5.2, and Section 3.5.4 show that the reassembled DEX file retains the semantics of the real-world application and can be correctly processed by the state-of-the-art static analysis tools.

# 3.4.4 Handling Reflection

Currently, reflection is a serious obstacle for static analysis tools, and even the state-of-the-art static analysis tools [33, 58, 98, 204] cannot provide a precise result when reflection is involved in an application. FlowDroid [33], DroidSafe [98], and HornDroid [58] can solve the reflection only when the parameters are constant strings. However, the name string can be encrypted in some cases [204], and advanced malware can use reflection without involving any string parameter [83].

The TamiFlex [49] system on traditional Java platform uses load-time instrumentation to log reflective method calls and transform them to direct calls at offline. However, the required load-time instrumentation class <code>java.lang.instrument</code> is not supported in Android [33]. Meanwhile, since the target of the reflective method calls is parsed in ART at runtime, DexLego actually knows the target of each reflection. Thus, we apply the similar idea in ART by replacing the reflection calls with direct calls in the collecting stage.

#### 3.4.5 Force Execution

As a supplement of the code coverage improvement module, we implement a prototype of force execution which executes the target application in an iterative fashion. Note that

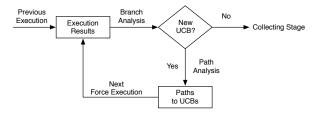

Figure 4: Iterative Force Execution.

our force execution starts from the execution result of the previous execution, and the previous execution could be any kind of execution like fuzzing, symbolic execution, another force execution, or simply open the application and close. Figure 4 shows the workflow of the iterative force execution. In each iteration, we first use branch analysis to identify the Uncovered Conditional Branch (UCB) from the result of the previous execution. Next, we calculate the control flow path to each UCB. A path to an UCB consists of branch instructions and the offsets of the conditional branches leading to the UCB. We save each path into a file and use these files as the input of the next iteration together with the original application. Finally, in the interpretation functions, the outcome of the corresponding conditional expression is automatically manipulated at runtime following the path files. With this approach, DexLego ensures that the runtime control flow goes along the path to the UCB. If no more new UCB are generated after the iteration, we terminate the execution and continue the collecting stage. Otherwise, the next iteration is scheduled.

Since the idea of force execution breaks the normal control flow of the original application, the application may crash due to the control flow falls to an infeasible path [139, 191]. To avoid crash triggered by force execution, we monitor the unhandled exception in the interpreter and tolerate it by directly clear the exception. This strategy helps us to avoid terminations due to infeasible paths while does not affect our runtime bytecode and

data collection.

### 3.5 Evaluation

In this section, we evaluate DexLego with DroidBench [83] and real-world applications downloaded from Google Play and other application markets. In particular, we aim to answer five research questions:

- **RQ1.** Can we correctly reconstruct the behavior of apps?

- **RQ3.** How is DexLego compared with other tools?

- **RQ4.** Can DexLego work with real-world packed apps?

- **RQ5.** What is the coverage of our force execution prototype?

- **RQ6.** What is the runtime performance overhead?

### 3.5.1 RQ1: Test with Open-source Apps and Public Packers

To verify the correctness of the reassembled result, we pick up four open source applications (i.e., HTMLViewer, Calculator, Calendar, and Contacts) from AOSP [94] and use DexLego to reveal them. By manually comparing the instructions and control flows in each method, we ensure that the instructions and control flows in the source code are completely included in the reassembled result. In regard to Calendar and Contacts, we use Soot framework [143] to build a complete call graph since the numbers of instructions (78,598 and 103,602 instructions, respectively) are too large for a manual analysis. By examining the call graph, we confirm that the control flows in these two applications are properly maintained in the reassembled DEX.

Next, to check the functionality against packers, we use different public packing platforms to pack these applications and then use DexLego to reveal them again. Table 1

Table 1: Test Result of Different Packers.

| Applications      | HTMLViewer                       | Calculator     | Calendar     | Contacts     |  |

|-------------------|----------------------------------|----------------|--------------|--------------|--|

| # of Instructions | 217                              | 2,507          | 78,598       | 103,602      |  |

| 360 [198]         | <b>√</b>                         | <b>√</b>       | <b>√</b>     | <b>√</b>     |  |

| Alibaba [5]       | $\checkmark$                     | $\checkmark$   | $\checkmark$ | $\checkmark$ |  |

| Tencent [248]     | $\checkmark$                     | $\checkmark$   | $\checkmark$ | $\checkmark$ |  |

| Baidu [42]        | $\checkmark$                     | $\checkmark$   | $\checkmark$ | $\checkmark$ |  |

| Bangcle [44]      | $\checkmark$                     | $\checkmark$   | $\checkmark$ | $\checkmark$ |  |

| NetQin [179]      | The service is offline now       |                |              |              |  |

| APKProtect [14]   | Unresponsive to packing requests |                |              |              |  |

| Ijiami [114]      | Samples are rej                  | ected by human | agents       |              |  |

shows the result of the experiments. For the packers including 360 [198], Alibaba [5], Tencent [248], Baidu [42], and Bangcle [44], DexLego succeeds in both collection and reassembling stages. By using the same approach described above, we ensure that DexLego correctly rebuilds the behavior of each application. Note that NetQin packer [179] mentioned in AppSpear [278] is no longer available. The APKProtect [14] is unresponsive to the packing requests, and there are no logs of the occurred errors. The packing service provided by Ijiami [114] requires manual audits by their agents, and they reject our applications for the reason that the applications are not actually developed by us.

### 3.5.2 RQ2: Test with Existing Tools

# **Static Analysis Tools**

DroidBench [83] is a set of open-source samples that leak sensitive data in various ways. It is considered as a benchmark for Android application analysis and widely used among recent analysis tools [33, 58, 98, 148, 265]. The latest release of DroidBench contains 119 applications, including both leaky and benign samples. The leaky samples leak a variety of sensitive data fetched from sources (API calls that fetch sensitive information)

Table 2: Analysis Result of Static Analysis Tools. The columns in "Original" represent the analysis result of the original samples, and the columns in "DexLego" represent that of the samples reassembled by DexLego. The column "TP" and "FP" indicate the number of true positives and false positives of the analysis result, respectively.

|                                  | # of       | # of       | Orig     | Original |            | DexLego |  |

|----------------------------------|------------|------------|----------|----------|------------|---------|--|

|                                  | Samples    | Malware    | TP       | FP       | TP         | FP      |  |

| FlowDroid [33]                   | 134        | 111<br>111 | 81       | 10       | 95<br>105  | 4       |  |

| DroidSafe [98]<br>HornDroid [58] | 134<br>134 | 111        | 95<br>98 | 9        | 105<br>106 | 4       |  |

to sinks (API calls that may leak information), and the benign samples contain no such information flows. As a supplement, we contribute another 15 samples involving usage of advanced reflection (5 samples), dynamic loading (3 samples), self-modifying (4 samples), and unreachable taint flows (3 samples). Current static analysis tools [33, 58, 98] cannot precisely analyze these newly added samples. Besides this benchmark, we choose three representative static analysis tools (FlowDroid [33], DroidSafe [98], and HornDroid [58]) to conduct the experiments.

Our experiment involves 134 samples (119 samples in the newest release plus 15 samples we contributed) in DroidBench. Since the lines of code in DroidBench samples are small, we simply choose the state-of-the-art fuzzing tool Sapienz [158] to generate the inputs for the execution. We first use the static analysis tools to analysis the original samples and the samples processed by DexLego, and the result is shown in Table 2. The table shows that DexLego increases more than 8 true positives by resolving advanced reflections, extracting self-modifying code and dynamic loading code. Moreover, The JIT collection ensures that the extracted data reflects the performed behavior of the target application. Thus, at least 5 false positives introduced by dead code blocks are removed. Next, with-

out losing generality, we use one of the most popular packers tested in Section 3.5.1, 360 packer, to pack the original samples and process the packed samples with DexLego, DexHunter [293], and AppSpear [278], respectively. The analysis result of the processed samples is shown in Table 3. Note that DexHunter and AppSpear lead to the same result since they can extract the original DEX files and the result is same as analyzing the original DEX. Compared to DexLego, they fail to deal with self-modifying code and reflection. As shown in the table, DexLego provides more than 5 true positives and reduces more than 5 false positives than DexHunter and AppSpear. We note that DexLego fails to cover taint flow in only one application among all samples. In this sample, sensitive data only leaks in the tablet, and it cannot be detected as we execute it in a mobile phone.

$$Sensitivity = \frac{tp}{tp + fn}, \ Specificity = \frac{tn}{tn + fp},$$

$$F-Measure = 2 \times \frac{Sensitivity \times Specificity}{Sensitivity + Specificity}$$

(3.1)

The F-Measure [58] is a standard measure of the performance of a classification, and it is calculated by Formula (3.1). Figure 5 illustrates the changes of F-Measures after involving DexHunter, AppSpear, and DexLego. Once DexLego is involved, the F-Measure of FlowDroid increases from 63% to 84% on DroidBench, and that of DroidSafe increases from 61% to 80%. In regard to the most recent static analysis tool, HornDroid, the F-Measure increases from 72% to 89%. The percentages of incremental values are 33.3%, 31.1%, and 23.6%, respectively. In the meantime, the improvement introduced by DexHunter and AppSpear is less than 3%.

Table 3: Analysis Result of Packed Samples. The columns in "DH", "AS", and "DexLego" represent the analysis result of the samples processed by DexHunter [293], AppSpear [278], and DexLego, respectively. The column "TP" and "FP" indicate the number of true positives and false positives of the analysis result, respectively.

|                | # of    | # of    | DH [29: | DH [293] / AS [278] |     | ego |

|----------------|---------|---------|---------|---------------------|-----|-----|

|                | Samples | Malware | TP      | FP                  | TP  | FP  |

| FlowDroid [33] | 134     | 111     | 84      | 10                  | 95  | 4   |

| DroidSafe [98] | 134     | 111     | 98      | 12                  | 105 | 7   |

| HornDroid [58] | 134     | 111     | 101     | 9                   | 106 | 4   |

### **Dynamic Analysis Tools**

Dynamic analysis tools can be circumvented through implicit taint flows, and a recent work [204] shows that a representitive dynamic analysis tool, TaintDroid [85], misses leakage on some samples of DroidBench. We pick these samples and analyze them with both TaintDroid and another recent dynamic analysis tool TaintART [244]. Next, we use DexLego to analyze it again. The reassembled result is fed to HornDroid, the most recent static analysis tool, for comparison.

Table 4 shows the taint flow analysis results of TaintDorid, TaintART, and combing DexLego and HornDroid. As shown in Table 4, the static analysis result of reassembled APK file by DexLego detects the taint flows and is more precise than dynamic analysis tools. In Button1 and Button3, the sensitive data are leaked via callback methods, and we solve it properly while the dynamic analysis tools miss it. As TaintDroid executes applications on emulator, the sample EmulatorDetection1 evades the analysis. Both TaintDroid and TaintART cannot detect the implicit taint flows in ImplicitFlow1, and using HornDroid with DexLego provides a precise analysis result. One of the taint flows in PrivateDataLeak3 leaks the sensitive data through writing/reading an external file, and all tested tools fail to

Figure 5: F-measures of Static Analysis Tools.

Table 4: Analysis Result of Dynamic Analysis Tools and DexLego. The columns "TD" and "TA" represent the taint flows detected by TaintDroid [85] and TaintART [244], respectively. The last column shows the detected taint flows by feeding the revealed result of DexLego to HornDroid [58].

| Samples            | Leak # |         | # of Leak | Detected          |

|--------------------|--------|---------|-----------|-------------------|

| bampies            | Lean " | TD [85] | TA [244]  | DexLego + HD [58] |

| Button1            | 1      | 0       | 0         | 1                 |

| Button3            | 2      | 0       | 0         | 2                 |

| EmulatorDetection1 | 1      | 0       | 1         | 1                 |

| ImplicitFlow1      | 2      | 0       | 0         | 2                 |

| PrivateDataLeak3   | 2      | 1       | 1         | 1                 |

detect this flow since they do not take this case into account. Note that these missed taint flows are not caused by code coverage issue, but due to the weakness of dynamic analysis tools on implicit taint flows.

Note that DexLego is not a dynamic analysis tool. We believe we should not directly compare DexLego with dynamic analysis tools, and the dynamic analysis tools have their advantages. However, the experiment conducted in this subsection is to show that DexLego can help static analysis tools make up some deficiencies of dynamic analysis tools.

# 3.5.3 RQ3: Test with Real-world Packed Applications

A previous work [259] has downloaded more than one million applications from Google Play by a crawler in 2014, and we select the packed applications from this set. Since the DEX file in an application packed by the public packing platforms contains only the classes needed to unpack the original DEX file, the number of the classes in the DEX file is less compared to normal applications. In light of this, we perform a coarse-grain analysis to screen the applications which contains less than 50 classes from the top rated 10,000 applications. Next, we select the first 9 applications from the screened result by manually checking and reverse engineering. Without loss of generality, we download the latest version of these applications from three different popular application markets: 1) Google Play [93] (denoted as set A), 2) 360 Application Market [199] (denoted as set B), and 3) Wandoujia Application Market [261] (denoted as set C).

For these real-world packed applications, we use FlowDroid to provide a quick scan on the original applications, and then execute them with DexLego for 5 minutes. Next, the reassembled APK file is analyzed again by FlowDroid. Table 5 shows the result of our experiment. Although no taint flow can be detected from the original samples, FlowDroid detects several taint flows from these revealed applications. From the analysis result, we find that all of these applications send device ID (IMEI number) to remote servers. Moreover, three of them leak location information and two of them leak SSID. This result also shows that DexLego successfully reveals the latest packed real-world applications.

Table 5: Analysis Result of Packed Real-world Applications. The column "Sample Set" is defined in Section 3.5.3, which indicates the source of the application. The column "# of Installs" shows the installation number provided by the application markets. The column "Original" represents the number of detected taint flows in the original application while the column "Revealed" is the number of detected taint flows in the revealed APK file.

| Package Name               | Version   | Sample Set | # of Installs | Original | Revealed |

|----------------------------|-----------|------------|---------------|----------|----------|

| com.lenovo.anyshare        | 3.6.68    | Α          | 100 million   | 0        | 4        |