### University of Nebraska - Lincoln DigitalCommons@University of Nebraska - Lincoln

Theses, Dissertations, and Student Research from Electrical & Computer Engineering

Electrical & Computer Engineering, Department of

Fall 10-28-2010

# A Single-Chip Ultra-Wideband Based Wireless Sensor Network Node

Nathan R. Schemm University of Nebraska at Lincoln, nathan.schemm@huskers.unl.edu

Follow this and additional works at: http://digitalcommons.unl.edu/elecengtheses Part of the <u>Electrical and Electronics Commons</u>, and the <u>VLSI and Circuits</u>, <u>Embedded and</u> <u>Hardware Systems Commons</u>

Schemm, Nathan R., "A Single-Chip Ultra-Wideband Based Wireless Sensor Network Node" (2010). *Theses, Dissertations, and Student Research from Electrical & Computer Engineering*. 10. http://digitalcommons.unl.edu/elecengtheses/10

This Article is brought to you for free and open access by the Electrical & Computer Engineering, Department of at DigitalCommons@University of Nebraska - Lincoln. It has been accepted for inclusion in Theses, Dissertations, and Student Research from Electrical & Computer Engineering by an authorized administrator of DigitalCommons@University of Nebraska - Lincoln.

#### A SINGLE-CHIP ULTRA-WIDEBAND BASED WIRELESS SENSOR NETWORK NODE

by

Nathan Schemm

#### A DISSERTATION

Presented to the Faculty of

The Graduate College at the University of Nebraska

In Partial Fulfilment of Requirements

For the Degree of Doctor of Philosophy

Major: Engineering

(Electrical Engineering)

Under the Supervision of Professor Sina Balkır and Professor Michael W. Hoffman

Lincoln, Nebraska

December, 2010

#### A SINGLE-CHIP ULTRA-WIDEBAND BASED WIRELESS

#### SENSOR NETWORK NODE

Nathan Schemm, Ph. D. University of Nebraska, 2010

Advisers: Sina Balkır and Michael W. Hoffman

This dissertation presents the design of a next-generation wireless sensor network node. The node incorporates many new and innovative technologies such as an ultra-wideband radio which allows very low-energy communication, a low-power radiation detection front end, and an efficient implementation of dynamic voltage scaling which improves the energy efficiency of the integrated processor. The complete design is integrated on a single chip for maximum power savings and minimal size.

The ultra-wideband transceiver includes many novel techniques to produce a receiver with low power consumption and fast and accurate packet acquisition and reception. These include the use of a standard symmetric inductor in a non-standard way as a T-coil load which extends the bandwidth of RF amplifiers, and a novel baseband architecture which relies on parallel analog processing to achieve both low power and fast and accurate signal acquisition and tracking.

Other features include a very low power interface to radiation detection detectors which uses an architecture in which the ADC only samples when an event occurs. This decreases the power over a conventional continuous-sampling scheme. A low-power charge sensitive amplifier is designed for the front end while the peak detection is done in the analog domain before an ADC converts the peak value to digital.

An efficient implementation of dynamic voltage scaling allows for unmatched computational power consumption combined with good sleep mode power. This is achieved through the integration of two buck converters which have high efficiency even at light loads.

The complete design was integrated on a single chip using a 0.18  $\mu$ m CMOS process with a total die area of 3×4.5 mm. The fabricated chip was tested and the measured results show that the chip does indeed achieve low power consumption. The measured results validate the approaches chosen, and field tests show the system is useful when interfaced to a variety of sensors for detecting various types of radiation.

#### ACKNOWLEDGMENTS

There are many people who without their assistance, this dissertation would not be possible. I would like to thank Professor Sina Balkır from whom I learned much about analog VLSI design and other life topics such as human relations and middle east politics, and to Professor Michael W. Hoffman who was in invaluable resource for any non-circuits knowledge. I would like to thank Professor Mark Bauer for his friendship and advice in many areas and for assisting me with some chip testing.

I would like to thank my friends and fellow graduate students for their support and encouragement during my tenure at Lincoln. Your support and friendship made my life at Lincoln infinitely more enjoyable.

Finally, I would like to thank my parents, Richard and Sue Schemm, and my sisters Hannah, Naomi, and Rachel for their loving support over the years. I would particularly like to thank my Dad for "teaching me everything he knew about electricity in five minutes" when I was very young (to his credit, it took him many years), and for always allowing me to add one more piece of broken-down, taken-apart junk to his basement workshop whenever I was able to acquire one. Without such an upbringing, I would not be where I am today.

#### GRANT INFORMATION

This work has been funded by a DOE grant entitled "All Solid-State Wireless Sensor Network for Nuclear Proliferation Detection."

# Contents

| Contents |                     |         |                                   |    |  |  |  |

|----------|---------------------|---------|-----------------------------------|----|--|--|--|

| Li       | ist of Figures xiii |         |                                   |    |  |  |  |

| Li       | ist of Tables xx    |         |                                   |    |  |  |  |

| No       | omen                | clature |                                   | 1  |  |  |  |

| I        | Int                 | roduc   | tion                              | 4  |  |  |  |

| 1        | Ove                 | rview   |                                   | 5  |  |  |  |

|          | 1.1                 | Contril | outions                           | 6  |  |  |  |

|          | 1.2                 | Organi  | zation                            | 9  |  |  |  |

| 2        | Mot                 | ivation |                                   | 10 |  |  |  |

|          | 2.1                 | Sensor  | Networks                          | 10 |  |  |  |

|          |                     | 2.1.1   | Applications                      | 11 |  |  |  |

|          |                     | 2.1.2   | Lifetime                          | 12 |  |  |  |

|          | 2.2                 | Digital | Power Consumption                 | 13 |  |  |  |

|          | 2.3                 | Radiat  | ion Detection Methods             | 17 |  |  |  |

|          |                     | 2.3.1   | Neutron Detection Methods         | 17 |  |  |  |

|          |                     | 2.3.2   | Gamma Ray Detection Methods       | 18 |  |  |  |

|          |                     | 2.3.3   | Charge Sensitive Amplifier Design | 20 |  |  |  |

|          | 2.4                 | Radio   |                                   |    |  |  |  |

|          |                     | 2.4.1   | UWB Communication                 |    |  |  |  |

|          |                     |         | 2.4.1.1 MB-OFDM vs. Impulse Radio | 23 |  |  |  |

|          |                     |         | 2.4.1.2 Coherent Designs          | 24 |  |  |  |

|     |        | 2.4.1.3    | Non-Coherent Designs  | 5 |

|-----|--------|------------|-----------------------|---|

|     |        | 2.4.1.4    | Coding                | 7 |

|     |        | 2.4.1.5    | Design Considerations | 7 |

|     | 2.4.2  | Narrowb    | and Communication     | 8 |

| 2.5 | Single | -Chip Solu | ution                 | 9 |

| 2.6 | Chip C | Generation | s                     | 0 |

| 2.7 | Conclu | usion      |                       | 1 |

### II Design

32

| 3 | Cha                | rge Sensi                                                                               | itive Amplifier Front End                                                                                                                                                                                                              | 33                                                       |

|---|--------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|   | 3.1                | Diode-B                                                                                 | Biasing DAC                                                                                                                                                                                                                            | 35                                                       |

|   | 3.2                | CSA .                                                                                   |                                                                                                                                                                                                                                        | 38                                                       |

|   |                    | 3.2.1                                                                                   | CSA Core                                                                                                                                                                                                                               | 38                                                       |

|   |                    | 3.2.2                                                                                   | Peak Detector and ADC Control Functions                                                                                                                                                                                                | 43                                                       |

|   | 3.3                | ADC .                                                                                   |                                                                                                                                                                                                                                        | 46                                                       |

|   |                    | 3.3.1                                                                                   | Comparator                                                                                                                                                                                                                             | 47                                                       |

|   |                    | 3.3.2                                                                                   | Implementation                                                                                                                                                                                                                         | 49                                                       |

|   | 3.4                | Microco                                                                                 | ntroller Interface                                                                                                                                                                                                                     | 51                                                       |

|   | 3.5                | DACs                                                                                    |                                                                                                                                                                                                                                        | 52                                                       |

|   | 3.6                | Conclus                                                                                 | ion                                                                                                                                                                                                                                    | 53                                                       |

|   |                    |                                                                                         |                                                                                                                                                                                                                                        |                                                          |

| 4 | Digi               | tal Core                                                                                | Design                                                                                                                                                                                                                                 | 55                                                       |

| 4 | 0                  | tal Core                                                                                | 5                                                                                                                                                                                                                                      | <b>55</b><br>57                                          |

| 4 | <b>Digi</b><br>4.1 | Design I                                                                                | Flow $\ldots$                                                                                                                                         | 57                                                       |

| 4 | 0                  | Design I<br>4.1.1                                                                       | Flow                                                                                                                                                                                                                                   | 57<br>57                                                 |

| 4 | 0                  | Design I<br>4.1.1                                                                       | Flow                                                                                                                                                                                                                                   | 57<br>57<br>58                                           |

| 4 | 0                  | Design I<br>4.1.1 \$<br>4.1.2 I                                                         | Flow                                                                                                                                                                                                                                   | 57<br>57<br>58<br>59                                     |

| 4 | 0                  | Design I<br>4.1.1 \$<br>4.1.2 I<br>4.1.3 I                                              | Flow                                                                                                                                                                                                                                   | 57<br>57<br>58<br>59<br>60                               |

| 4 | 0                  | Design I<br>4.1.1 2<br>4.1.2 1<br>4.1.3 1<br>4.1.4 0                                    | Flow                                                                                                                                                                                                                                   | 57<br>57<br>58<br>59<br>60<br>62                         |

| 4 | 0                  | Design I<br>4.1.1 2<br>4.1.2 1<br>4.1.3 1<br>4.1.4 0<br>4.1.5 1                         | Flow                                                                                                                                                                                                                                   | 57<br>57<br>58<br>59<br>60<br>62<br>64                   |

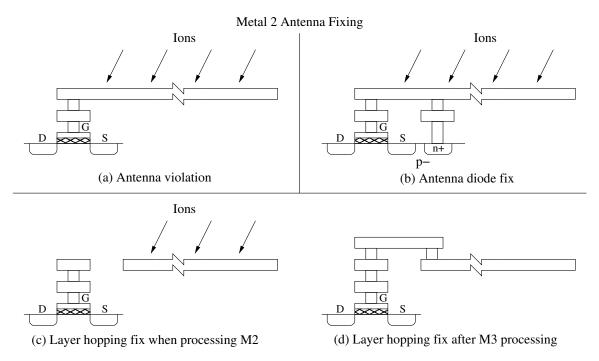

| 4 | 0                  | Design H<br>4.1.1 2<br>4.1.2 1<br>4.1.3 1<br>4.1.4 0<br>4.1.5 1                         | Flow    Flow      Source Files    Source Files      4.1.1.1    Memory IP      Logic Synthesis    Source      Placement    Source      Clock Tree Synthesis    Source      Routing    Source      4.1.5.1    Process Antenna Violations | 57<br>57<br>58<br>59<br>60<br>62<br>64<br>64             |

| 4 | 4.1                | Design H<br>4.1.1 \$<br>4.1.2 H<br>4.1.3 H<br>4.1.4 (<br>4.1.5 H<br>4.1.6 \$            | Flow                                                                                                                                                                                                                                   | 57<br>57<br>58<br>59<br>60<br>62<br>64<br>64<br>64       |

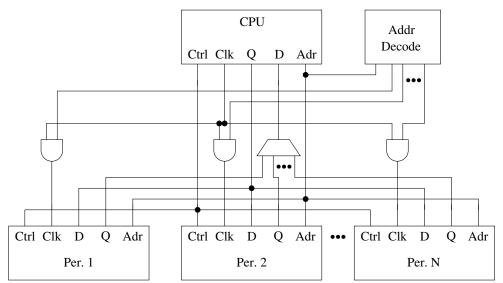

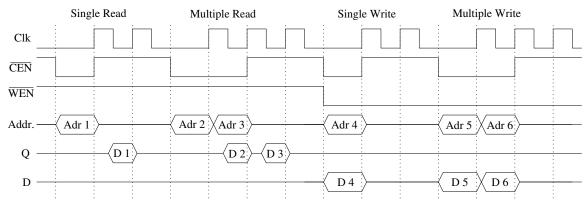

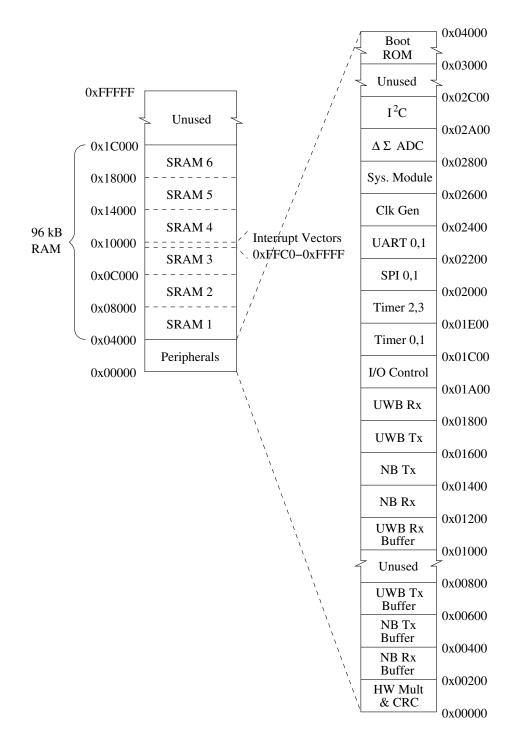

| 4 | 0                  | Design H<br>4.1.1 2<br>4.1.2 H<br>4.1.3 H<br>4.1.4 0<br>4.1.5 H<br>4.1.6 S<br>Bus Inter | Flow    Flow      Source Files    Source Files      4.1.1.1    Memory IP      Logic Synthesis    Source      Placement    Source      Clock Tree Synthesis    Source      Routing    Source      4.1.5.1    Process Antenna Violations | 57<br>57<br>58<br>59<br>60<br>62<br>64<br>64<br>66<br>66 |

|      | 4.3.1   | Registers                             |

|------|---------|---------------------------------------|

|      |         | 4.3.1.1 Status Register               |

|      |         | 4.3.1.2 Constant Generator            |

|      | 4.3.2   | Addressing Modes                      |

|      | 4.3.3   | Interrupts                            |

|      | 4.3.4   | Instruction Set                       |

|      | 4.3.5   | SIMD                                  |

|      | 4.3.6   | Instruction Encoding                  |

|      |         | 4.3.6.1 Extension Word                |

|      | 4.3.7   | Implementation                        |

| 4.4  | CRC N   | Aodule                                |

| 4.5  | Hardw   | are Multiplier                        |

| 4.6  | Timers  |                                       |

| 4.7  | SPI.    |                                       |

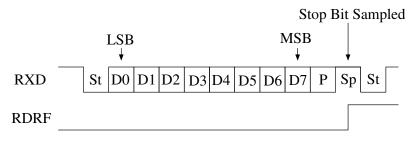

| 4.8  | UART    |                                       |

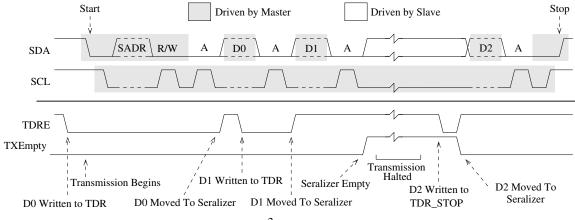

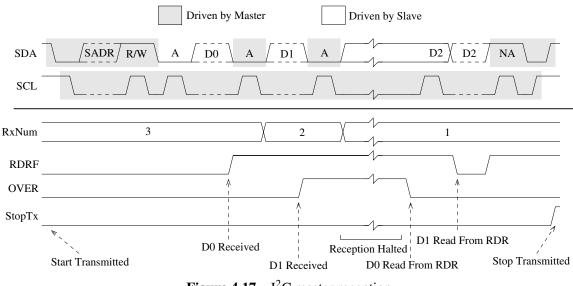

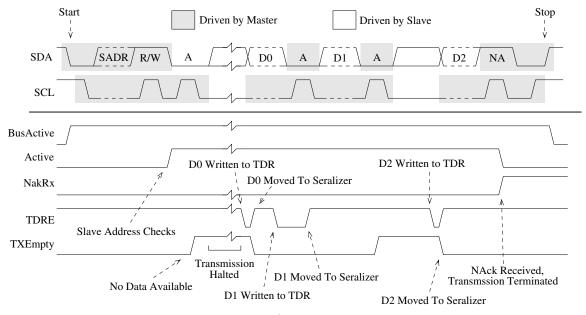

| 4.9  | $I^2C$  |                                       |

|      | 4.9.1   | Transfer Format                       |

|      |         | 4.9.1.1 Clock Stretching/Flow Control |

|      | 4.9.2   | $I^2C$ Master                         |

|      |         | 4.9.2.1 Bus Arbitration               |

|      |         | 4.9.2.2 Transmit Mode                 |

|      |         | 4.9.2.3 Receive Mode                  |

|      | 4.9.3   | $I^2C$ Slave                          |

|      |         | 4.9.3.1 Transmit Mode                 |

|      |         | 4.9.3.2 Receive Mode                  |

| 4.10 | Conclu  | usion                                 |

| UW   | B Trans | sceiver Design 110                    |

| 5.1  |         | ecture                                |

|      | 5.1.1   | Modulation Format                     |

|      | 5.1.2   | Packet Format                         |

| 5.2  | Convo   | lutional Code                         |

|      | 5.2.1   | Fundamentals                          |

|      |         | 5.2.1.1 Performance Measurement       |

5

|   |      | 5.2.2    | Code Selection                         | 116 |

|---|------|----------|----------------------------------------|-----|

|   |      | 5.2.3    | Chosen Code                            | 118 |

|   |      | 5.2.4    | Implementation                         | 121 |

|   |      |          | 5.2.4.1 Encoder                        | 122 |

|   |      |          | 5.2.4.2 Decoder                        | 123 |

|   | 5.3  | Interlea | aver                                   | 124 |

|   | 5.4  | CRC .    |                                        | 126 |

|   | 5.5  | Transn   | nitter                                 | 126 |

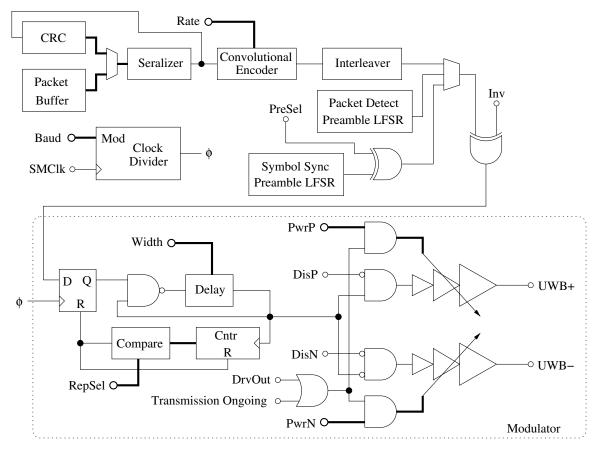

|   |      | 5.5.1    | Digital Architecture                   | 126 |

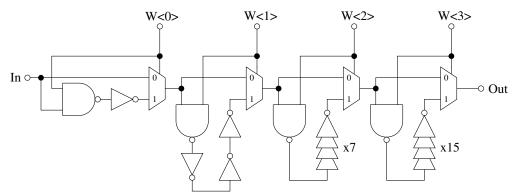

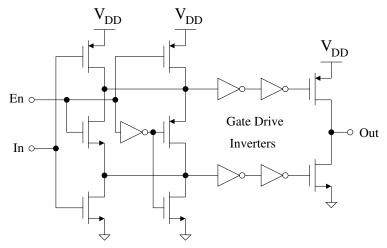

|   |      | 5.5.2    | Modulator Output Stage                 | 129 |

|   | 5.6  | Receiv   | er RF Front End                        | 131 |

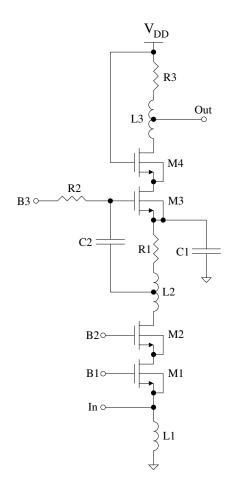

|   |      | 5.6.1    | LNA                                    | 131 |

|   |      |          | 5.6.1.1 Preliminaries                  | 131 |

|   |      |          | 5.6.1.2 Design                         | 134 |

|   |      | 5.6.2    | Gain Stages                            | 136 |

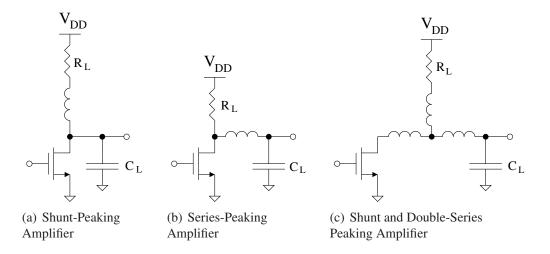

|   |      |          | 5.6.2.1 Multi-Peak Response Flattening | 137 |

|   |      | 5.6.3    | Self-Mixer                             | 138 |

|   |      | 5.6.4    | AGC                                    | 140 |

|   |      | 5.6.5    | Front End Oscillation                  | 143 |

|   | 5.7  | Packet   | Detection                              | 144 |

|   |      | 5.7.1    | Packet Detection Performance           | 146 |

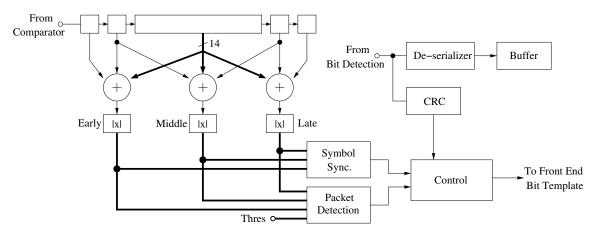

|   | 5.8  | Bit De   | tection                                | 150 |

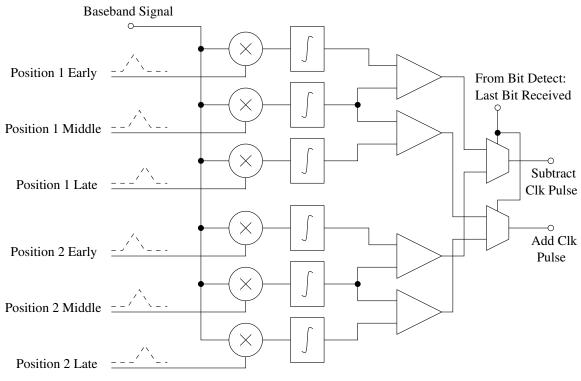

|   | 5.9  | Symbo    | I Synchronization                      | 152 |

|   |      | 5.9.1    | Symbol Synchronization Waveforms       | 154 |

|   | 5.10 | UWB .    | Antenna                                | 157 |

|   | 5.11 | Conclu   | ision                                  | 158 |

| 6 | Narr | owban    | d Transceiver Design                   | 159 |

|   | 6.1  | Archite  | ecture                                 | 160 |

|   | 6.2  | Transn   | nitter                                 | 161 |

|   |      | 6.2.1    | Digital Section                        |     |

|   |      | 6.2.2    | Power Amplifier                        |     |

|   | 6.3  | Receiv   | er                                     |     |

|   |      |          | RF Front End                           |     |

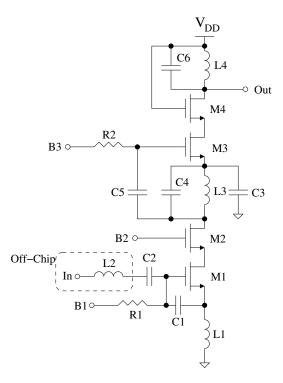

|   |     |         | 6.3.1.1 LNA                                      | 64         |

|---|-----|---------|--------------------------------------------------|------------|

|   |     |         | 6.3.1.2 Gain Stages                              | 5          |

|   |     |         | 6.3.1.3 Self-Mixer                               | 57         |

|   |     |         | 6.3.1.4 AGC                                      | 57         |

|   |     | 6.3.2   | Analog Baseband                                  | 68         |

|   |     | 6.3.3   | Digital Baseband                                 | <u>i</u> 9 |

|   | 6.4 | Conclu  | usion                                            | 0          |

| 7 | Sup | porting | Circuitry 17                                     | ′1         |

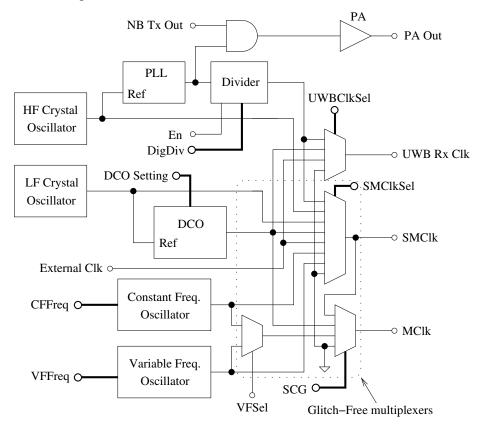

|   | 7.1 | Clock   | Generator                                        | '1         |

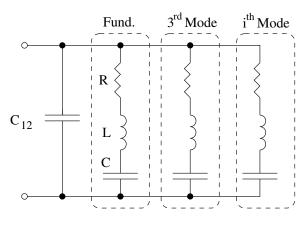

|   |     | 7.1.1   | Crystal Oscillators                              | '3         |

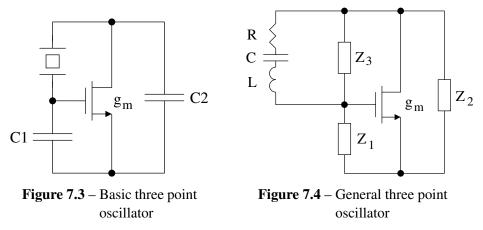

|   |     |         | 7.1.1.1 Theory                                   | '3         |

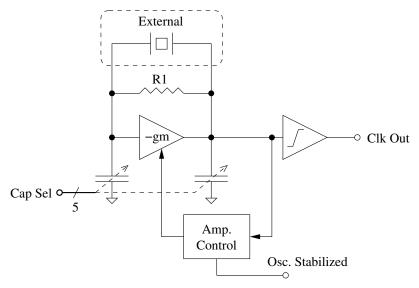

|   |     |         | 7.1.1.2 Overview                                 | 5          |

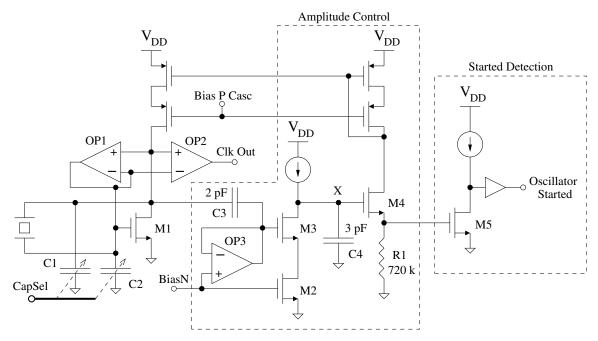

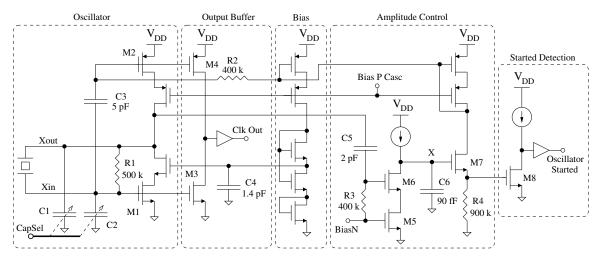

|   |     |         | 7.1.1.3 Low-Frequency Oscillator Implementation  | 7          |

|   |     |         | 7.1.1.4 High-Frequency Oscillator Implementation | 60         |

|   |     | 7.1.2   | PLL                                              | 51         |

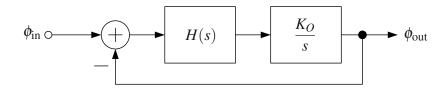

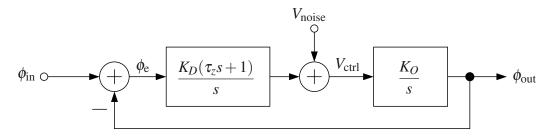

|   |     |         | 7.1.2.1 Theory                                   | 51         |

|   |     |         | 7.1.2.2 PLL Implementation                       | \$4        |

|   |     |         | 7.1.2.3 VCO                                      | 5          |

|   |     |         | 7.1.2.4 Phase-Frequency Detector                 | 57         |

|   |     |         | 7.1.2.5 Loop Filter                              | 8          |

|   |     |         | 7.1.2.6 UWB Receiver Pulse Generator             | ;9         |

|   |     |         | 7.1.2.7 PLL Lock Detect                          | 0          |

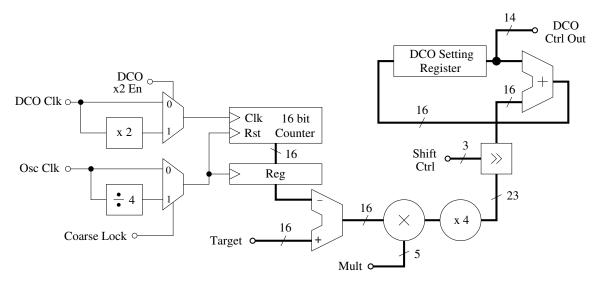

|   |     | 7.1.3   | Digitally-Controlled Oscillator                  | 1          |

|   |     |         | 7.1.3.1 DCO Stabilization                        | 13         |

|   |     | 7.1.4   | Digital-Supply Oscillators                       | 95         |

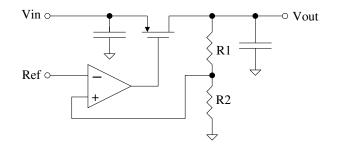

|   | 7.2 | DVS-0   | Capable Power Supply                             | 6          |

|   |     | 7.2.1   | Introduction                                     | 17         |

|   |     | 7.2.2   | DVS Theory                                       | 18         |

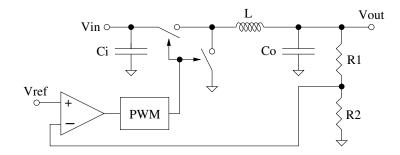

|   |     | 7.2.3   | Buck Regulator                                   | 19         |

|   |     | 7.2.4   | Buck Regulator Design                            | 12         |

|   |     |         | 7.2.4.1 Simulations                              | )7         |

|   | 7.3 | Delta-  | Sigma ADC                                        | 19         |

|   | 7.4 | EFuse   |                                                  | 3          |

| 7.5 | Biases and References | 14 |

|-----|-----------------------|----|

| 7.6 | Conclusion            | 15 |

### **III Results**

### 216

| 8  | Test | Setup                                           | 217 |

|----|------|-------------------------------------------------|-----|

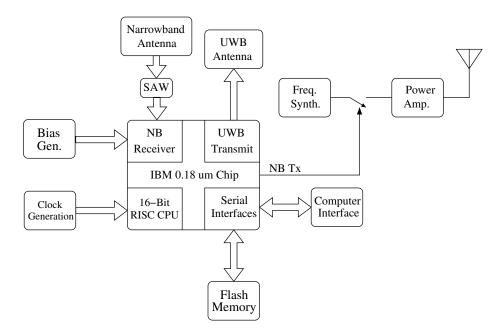

|    | 8.1  | First Chip                                      | 218 |

|    | 8.2  | Second Chip                                     | 221 |

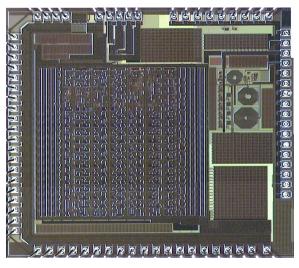

|    | 8.3  | Third Chip                                      | 224 |

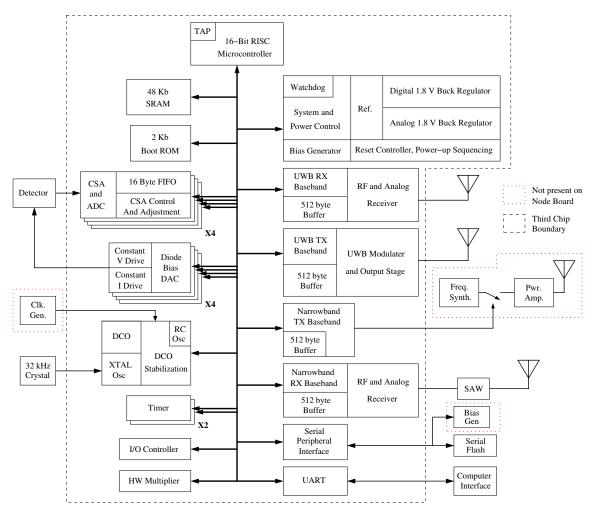

|    | 8.4  | Fourth Chip                                     | 227 |

|    | 8.5  | <i>Forth</i> System                             | 231 |

|    | 8.6  | Conclusion                                      | 232 |

| 9  | CSA  | Results                                         | 233 |

|    | 9.1  | Lab Test Results                                | 233 |

|    | 9.2  | GdHf Diode Results                              | 237 |

|    | 9.3  | Gamma Detection Results                         | 240 |

|    |      | 9.3.1 Detector Operation                        | 241 |

|    |      | 9.3.2 Gamma Isotope Identification              | 242 |

|    |      | 9.3.3 Performance                               | 244 |

|    | 9.4  | Conclusion                                      | 246 |

| 10 | RF 1 | <b>Fransceiver Results</b>                      | 247 |

|    | 10.1 | UWB Transmitter Results                         | 247 |

|    | 10.2 | UWB Receiver                                    | 253 |

|    |      | 10.2.1 Receiver RF Front End                    | 254 |

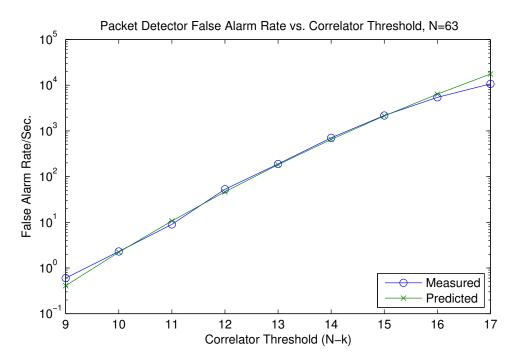

|    |      | 10.2.2 Packet Detection                         | 256 |

|    |      | 10.2.3 Bit Detection and Symbol Synchronization | 258 |

|    |      | 10.2.4 Conclusion                               | 265 |

|    | 10.3 | Narrowband Transmitter                          | 265 |

|    | 10.4 | Narrowband Receiver                             | 270 |

| 11 | Over | call System Results                             | 275 |

|    | 11.1 | Digital Core                                    | 275 |

|    | 11.2 | Support Circuitry                               | 280 |

|     | 11.2.1 Power Supply                  | 281 |

|-----|--------------------------------------|-----|

|     | 11.2.2 Clock Generator               | 284 |

|     | 11.3 Overall Sensor Mote Comparisons | 287 |

|     | 11.4 Conclusion                      | 290 |

| 12  | Conclusions And Future Work          | 291 |

|     | 12.1 Future Work                     | 291 |

|     | 12.1.1 Hardware                      | 291 |

|     | 12.1.2 Software                      | 293 |

|     | 12.2 Conclusion                      | 294 |

| Bib | liography                            | 296 |

| A   | Fourth Chip Pin-out                  | 305 |

# **List of Figures**

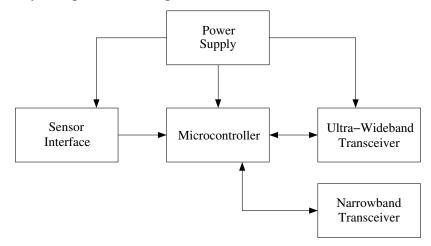

| 1.1  | WSN node architecture presented in this dissertation.                    | 6  |

|------|--------------------------------------------------------------------------|----|

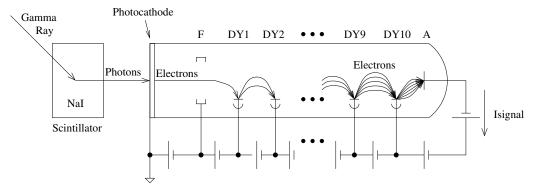

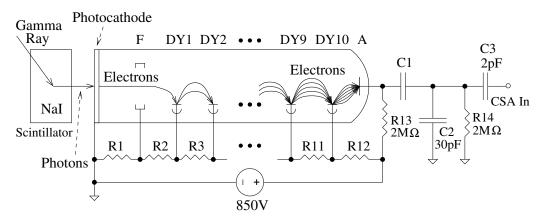

| 2.1  | Scintillation-based gamma detection                                      | 19 |

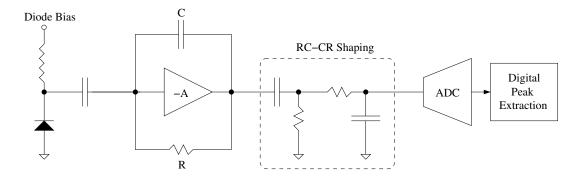

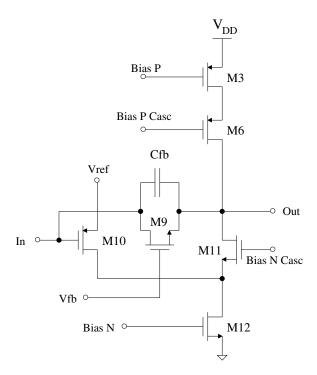

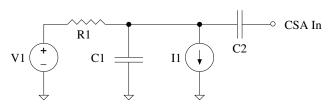

| 2.2  | Conventional charge sensitive signal chain                               | 21 |

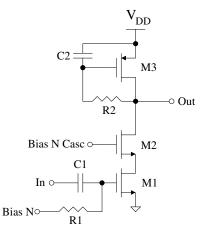

| 2.3  | Conventional folded cascode CSA                                          | 22 |

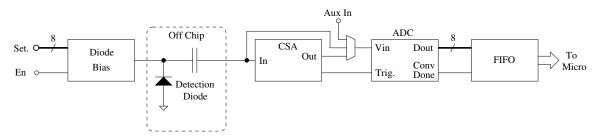

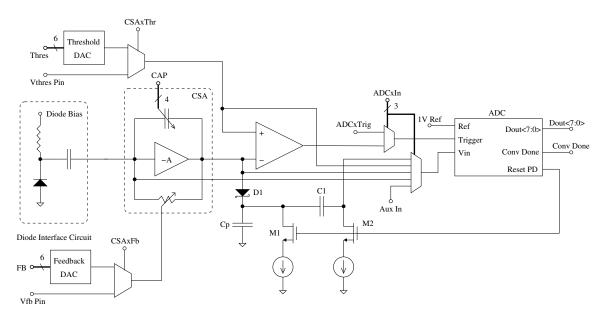

| 3.1  | Sensor interface section enclosed in red box.                            | 33 |

| 3.2  | Detection signal chain showing the diode bias, CSA, ADC and microcon-    |    |

|      | troller interface                                                        | 34 |

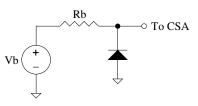

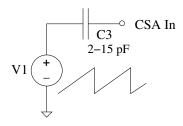

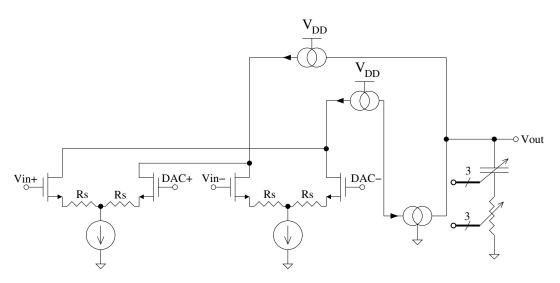

| 3.3  | Standard diode biasing scheme                                            | 35 |

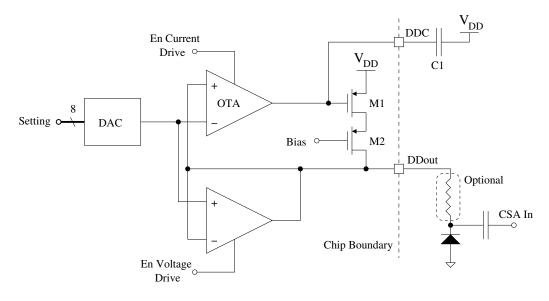

| 3.4  | Diode DAC architecture                                                   | 36 |

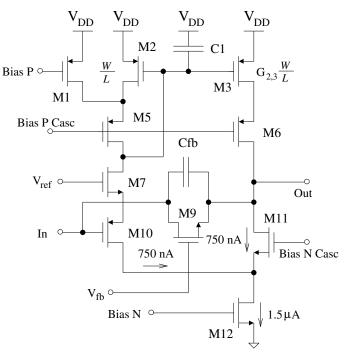

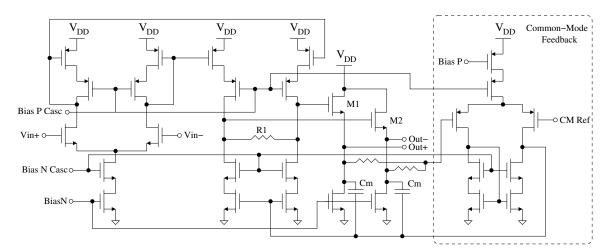

| 3.5  | CSA schematic.                                                           | 38 |

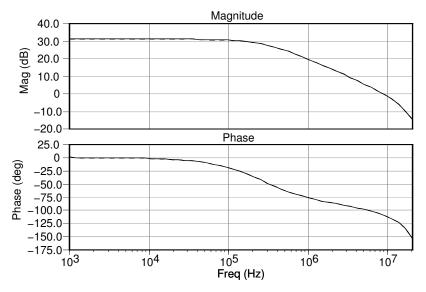

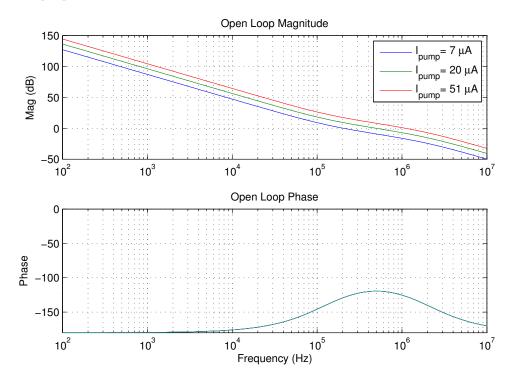

| 3.6  | Open-loop AC response of the feedback circuit.                           | 40 |

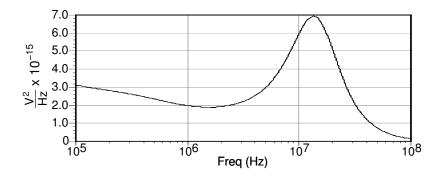

| 3.7  | Output noise spectral density in $V^2$ /Hz                               | 41 |

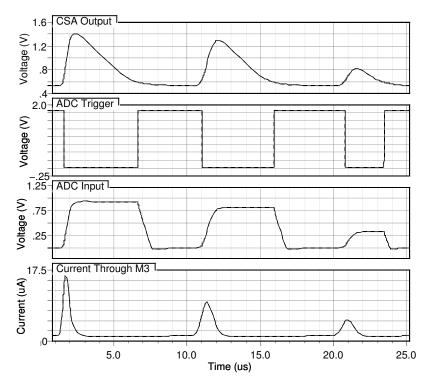

| 3.8  | Front end simulation. From top to bottom:                                |    |

|      | CSA Output, ADC Trigger, ADC Input, Current through M3                   | 42 |

| 3.9  | Simulation diode model                                                   | 43 |

| 3.10 | Differentiator circuit                                                   | 43 |

| 3.11 | Front end architecture implemented in a 0.18 $\mu$ m CMOS process with a |    |

|      | Schottky diode option                                                    | 43 |

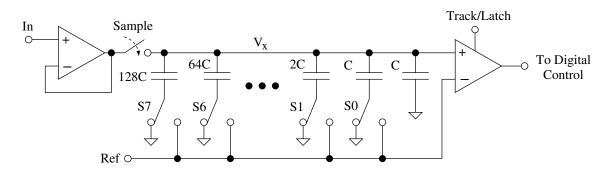

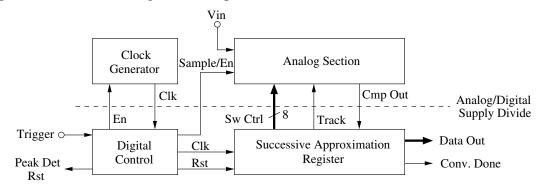

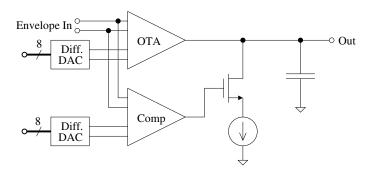

| 3.12 | ADC architecture                                                         | 46 |

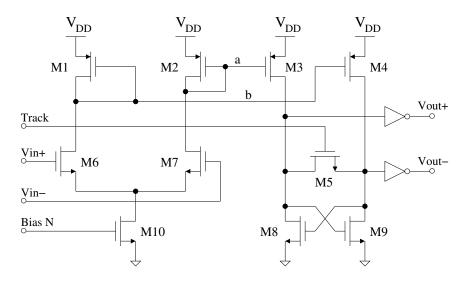

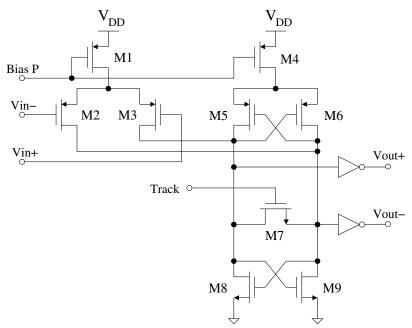

| 3.13 | Track and latch comparator present in the first chip                     | 48 |

| 3.14 | Fixed track and latch comparator used in the third and fourth chip       | 48 |

| 3.15 | Functional diagram of the ADC.                                           | 49 |

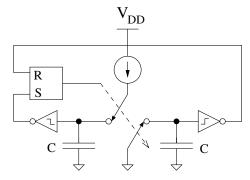

| 3.16 | Functional diagram of the ADC clock generator.                           | 50 |

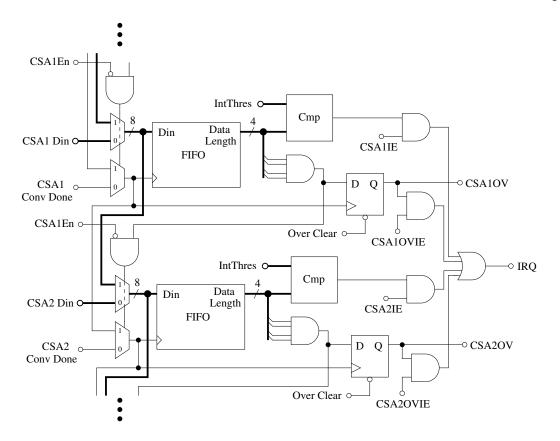

| 3.17 | Schematic of two FIFOs for the ADC interface.                            | 52 |

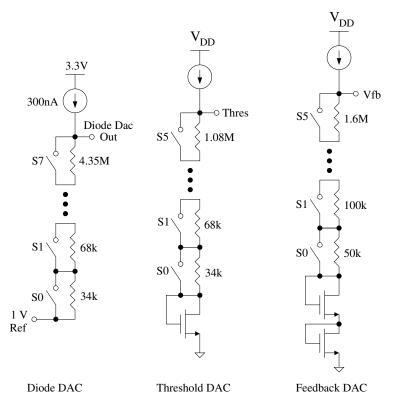

| 3.18 | Schematics for the three DACs                                                  | 54  |

|------|--------------------------------------------------------------------------------|-----|

| 4.1  | Digital section enclosed in red box.                                           | 55  |

| 4.2  | Digital section final placement.                                               | 56  |

| 4.3  | Digital section floorplan showing memory placement and soft placement guide-   |     |

|      | lines                                                                          | 61  |

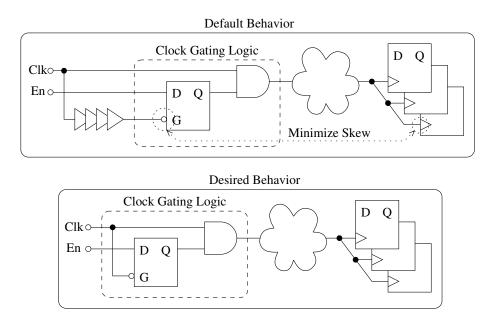

| 4.4  | Clock tree synthesis clock gating showing the default handling and the desired |     |

|      | handling.                                                                      | 63  |

| 4.5  | (a) Antenna violation, (b) Antenna diode, (c) and (d) Layer hopping fix        | 65  |

| 4.6  | Bus architecture                                                               | 67  |

| 4.7  | Bus read and write.                                                            | 68  |

| 4.8  | Device memory map                                                              | 69  |

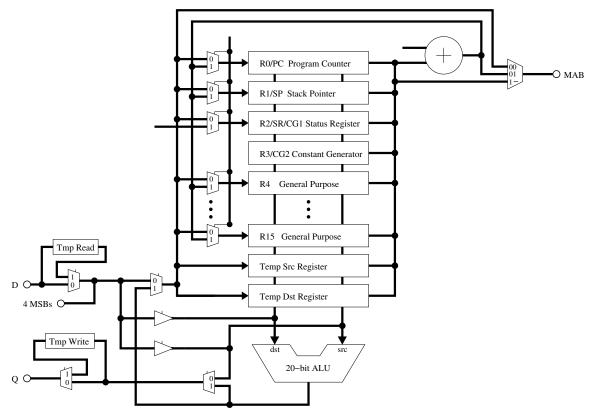

| 4.9  | MSP430X Datapath                                                               | 90  |

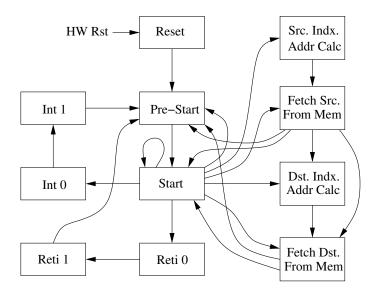

| 4.10 | CPU control section state diagram.                                             | 92  |

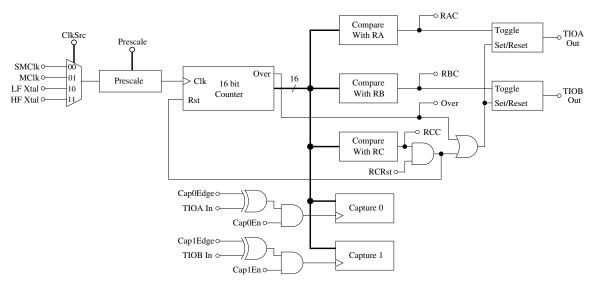

| 4.11 | Timer functional diagram                                                       | 97  |

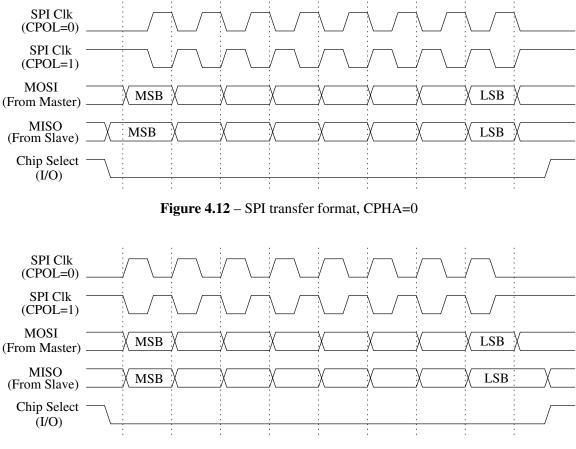

| 4.12 | SPI transfer format, CPHA=0                                                    | 100 |

| 4.13 | SPI transfer format, CPHA=1                                                    | 100 |

| 4.14 | UART receive byte                                                              | 101 |

| 4.15 | $I^2C$ transfer format                                                         |     |

| 4.16 | I <sup>2</sup> C master transmission                                           | 106 |

| 4.17 | $I^2C$ master reception                                                        | 107 |

| 4.18 | $I^2C$ slave transmission                                                      | 108 |

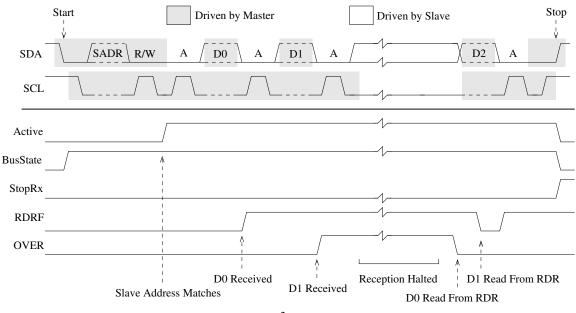

| 4.19 | $I^2C$ slave reception                                                         | 109 |

| 5.1  | UWB transceiver enclosed in red box                                            | 110 |

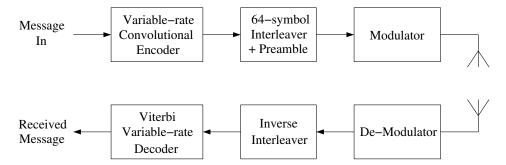

| 5.2  | Overall UWB communication system architecture                                  | 111 |

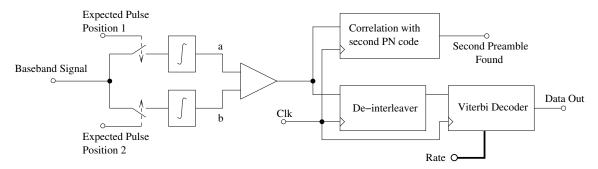

| 5.3  | Architecture of the de-modulator                                               | 112 |

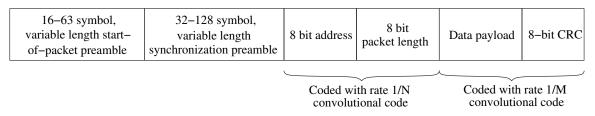

| 5.4  | UWB packet structure, N and M are run-time adjustable integers from 2-10       | 113 |

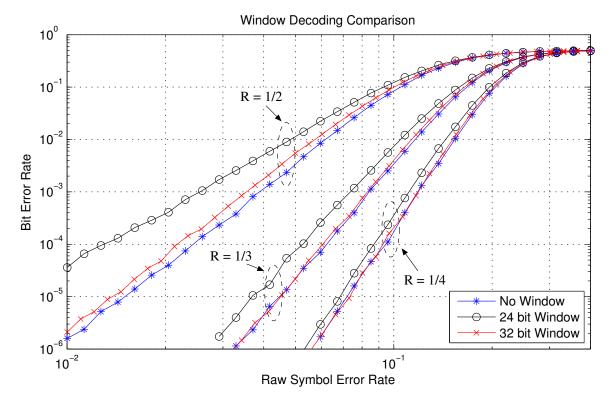

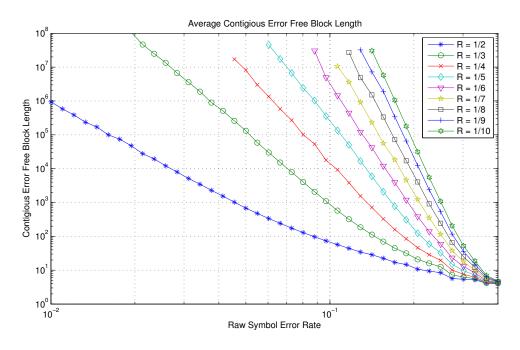

| 5.5  | Effect of window length on performance                                         | 119 |

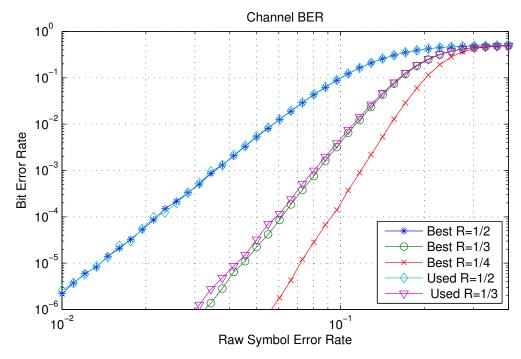

| 5.6  | Code comparison with best known codes, window=32 bits                          | 120 |

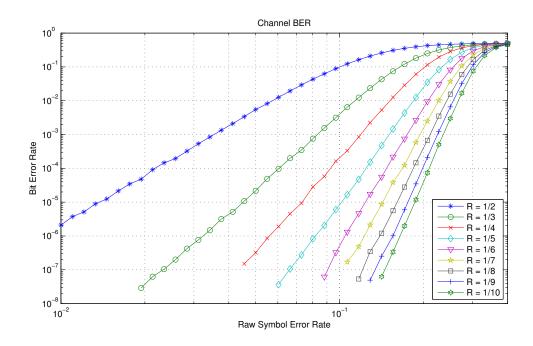

| 5.7  | Code performance, window=32 bits                                               | 121 |

| 5.8  | Error free data bit block length, window=32 bits                               | 122 |

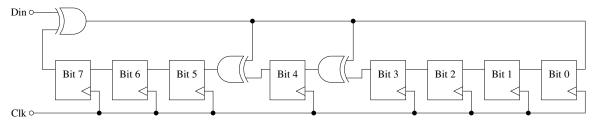

| 5.9  | Convolutional encoder schematic.                                               | 123 |

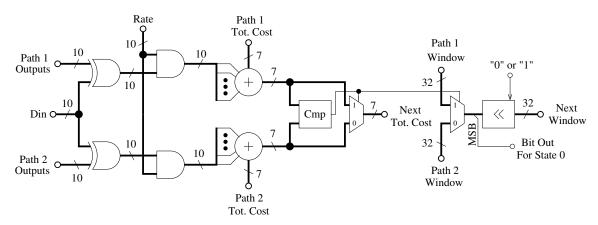

| 5.10 | Add-compare-select unit for the Viterbi decoder.                               | 123 |

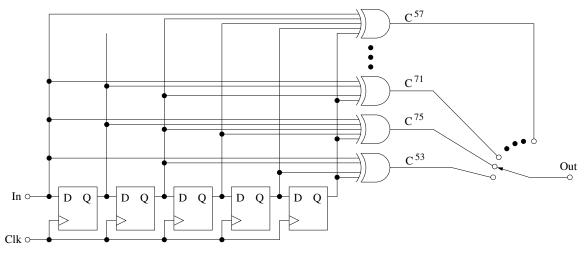

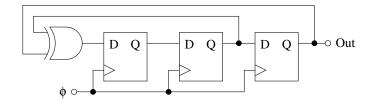

| 5.11 | 8-Bit CRC schematic                                                            | 126 |

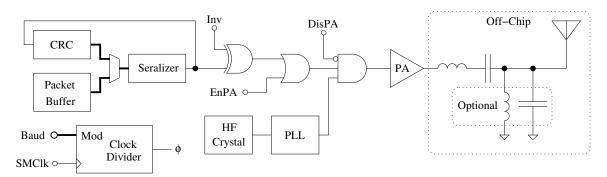

| 5.12 | UWB transmitter architecture                                                     | . 127 |

|------|----------------------------------------------------------------------------------|-------|

| 5.13 | Packet detection LFSR schematic.                                                 | . 128 |

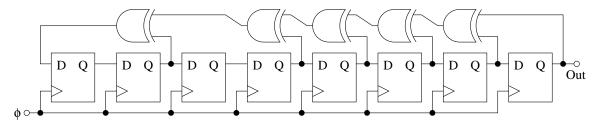

| 5.14 | Symbol synchronization preamble LFSR                                             | . 128 |

| 5.15 | UWB transmitter adjustable delay                                                 | . 129 |

| 5.16 | Single UWB output stage                                                          | . 130 |

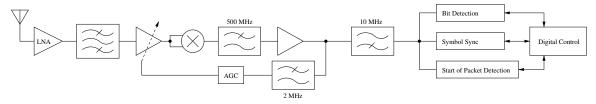

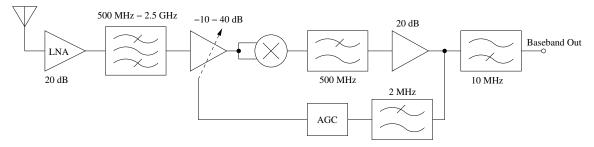

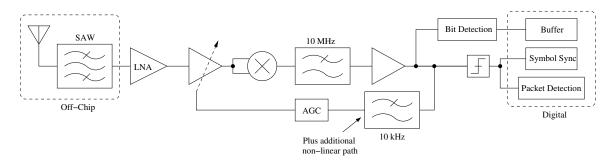

| 5.17 | UWB receiver front end                                                           | . 131 |

| 5.18 | Bandwidth enhancement techniques                                                 | . 133 |

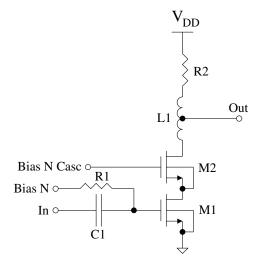

| 5.19 | Stacked LNA schematic.                                                           | . 135 |

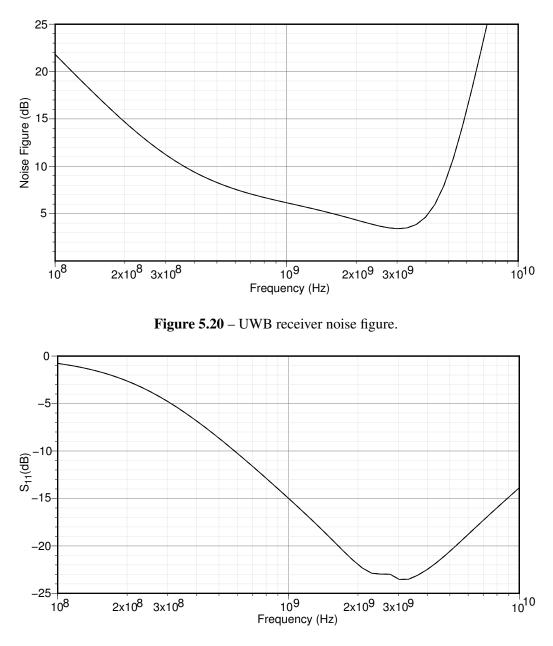

| 5.20 | UWB receiver noise figure.                                                       | . 136 |

| 5.21 | UWB receiver input matching.                                                     | . 136 |

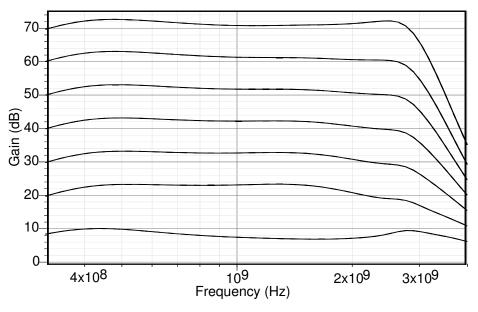

| 5.22 | UWB gain stage.                                                                  | . 137 |

| 5.23 | Outputs of each stage                                                            | . 138 |

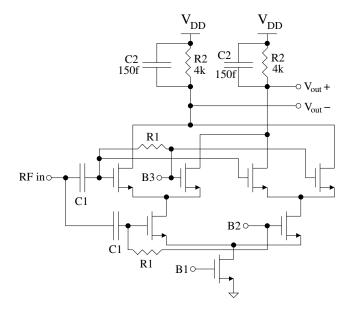

| 5.24 | UWB self-mixer schematic                                                         | . 138 |

| 5.25 | UWB baseband gain                                                                | . 139 |

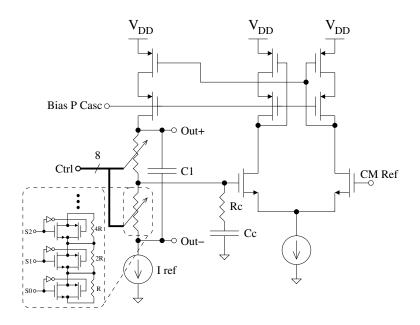

| 5.26 | Differential DAC                                                                 | . 141 |

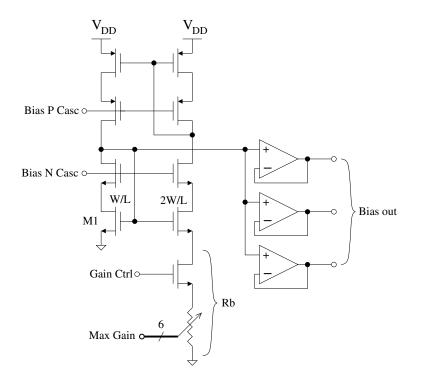

| 5.27 | UWB AGC amplifier and loop compensation                                          | . 141 |

| 5.28 | UWB gain stage bias control                                                      | . 142 |

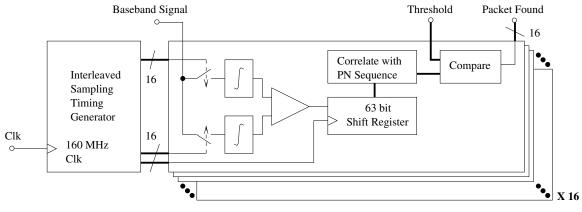

| 5.29 | Packet detection circuitry                                                       | . 145 |

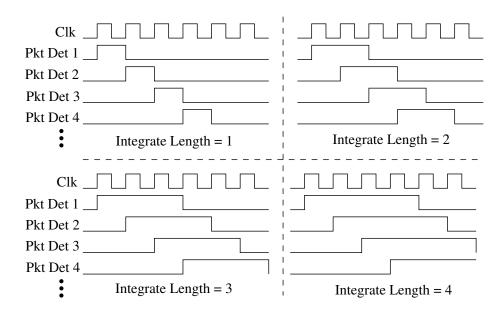

| 5.30 | Packet detect integrator waveforms with varying integration length               | . 146 |

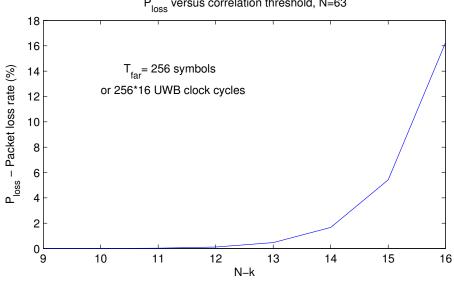

| 5.31 | $P_{loss}$ versus N-k with N=63                                                  | . 148 |

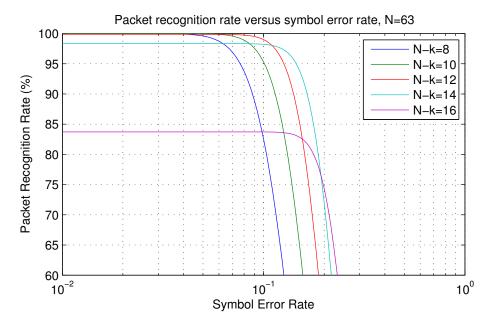

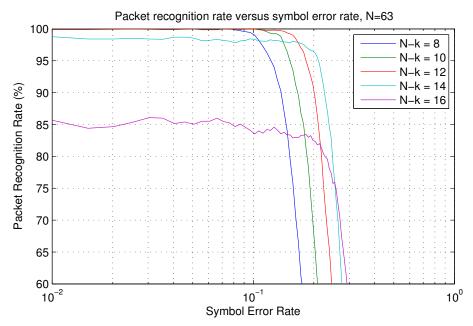

| 5.32 | Packet recognition rate versus symbol error rate for varying values of $N - k$ . | . 149 |

| 5.33 | Simulation of packet recognition rate versus symbol error rate for various       |       |

|      | values of $N-k$ .                                                                | . 150 |

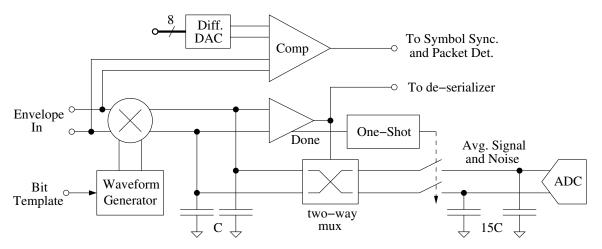

| 5.34 | Bit detection block diagram                                                      | . 151 |

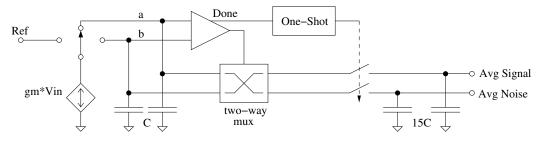

| 5.35 | Average signal and noise computation                                             | . 152 |

| 5.36 | Symbol synchronization block diagram                                             | . 153 |

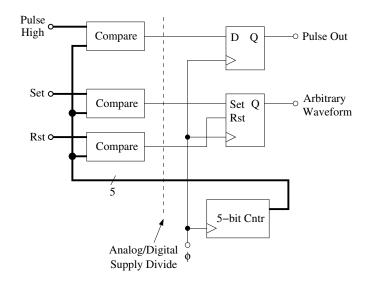

| 5.37 | Symbol synchronization waveform generation circuitry                             | . 155 |

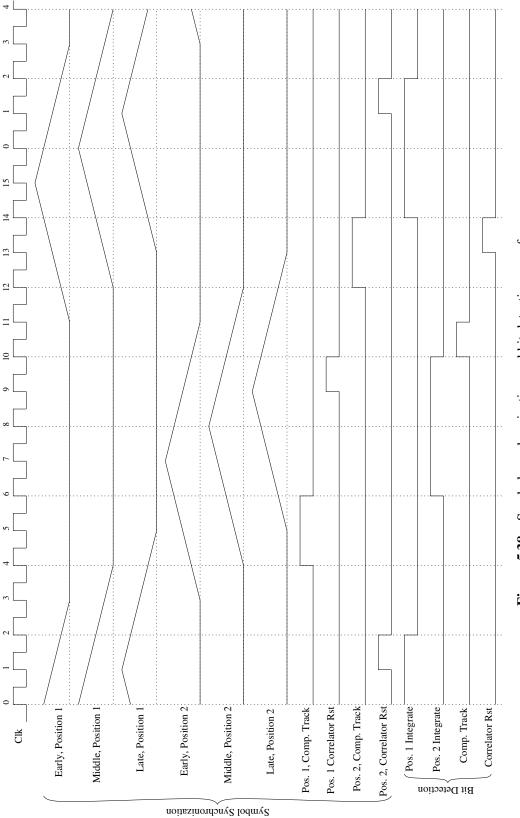

| 5.38 | Symbol synchronization and bit detection waveforms                               | . 156 |

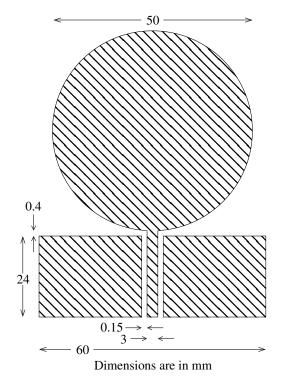

| 5.39 | UWB antenna dimensions (not to scale)                                            | . 157 |

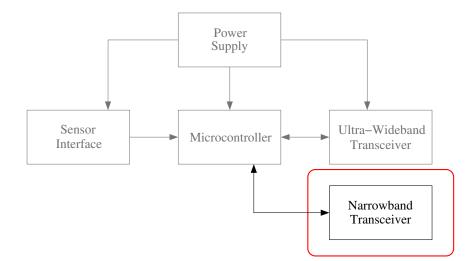

| 6.1  | Narrowband transceiver section enclosed in red box                               | . 159 |

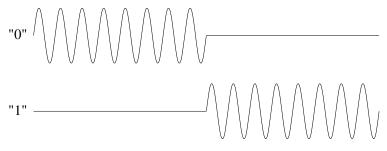

| 6.2  | Narrowband Manchester-encoding scheme                                            | . 160 |

| 6.3  | Narrowband packet format                                                         | . 161 |

| 6.4  | Narrowband transmitter architecture                                              | . 161 |

| 6.5  | Narrowband receiver architecture                                                 | . 164 |

| 6.6  | Narrowband LNA schematic                           |

|------|----------------------------------------------------|

| 6.7  | Un-tuned narrowband gain stage                     |

| 6.8  | Narrowband AGC amplifier with accelerator          |

| 6.9  | Narrowband baseband circuits                       |

| 6.10 | Narrowband digital architecture                    |

| 7.1  | Overall clock system                               |

| 7.2  | Crystal model                                      |

| 7.3  | Basic three point oscillator                       |

| 7.4  | General three point                                |

|      | oscillator                                         |

| 7.5  | Crystal oscillator                                 |

| 7.6  | Low-frequency crystal oscillator schematic         |

| 7.7  | High-frequency crystal oscillator schematic        |

| 7.8  | Linearized PLL model                               |

| 7.9  | Second-order linearized PLL model with noise input |

| 7.10 | PLL and supporting circuitry                       |

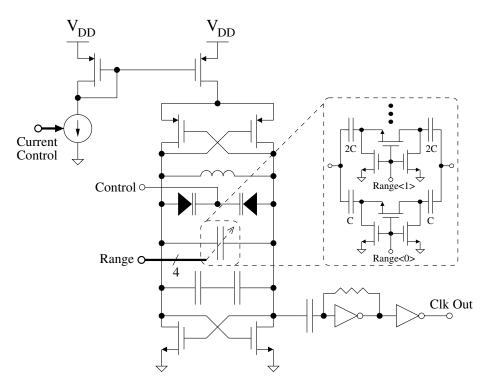

| 7.11 | Differential LC VCO                                |

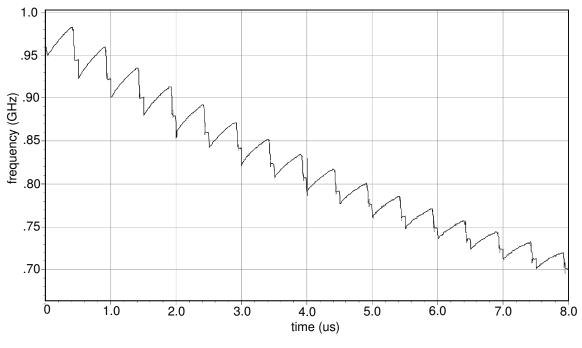

| 7.12 | VCO frequency ranges                               |

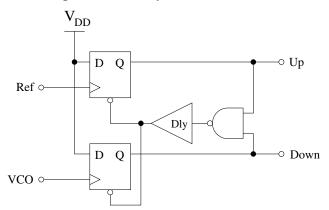

| 7.13 | Phase-frequency detector                           |

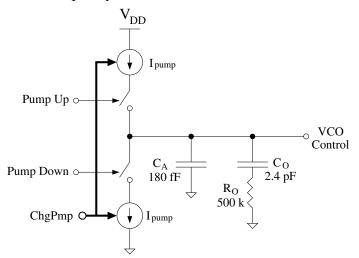

| 7.14 | Charge pump and loop filter                        |

| 7.15 | Loop filter open-loop response                     |

| 7.16 | Oscillator architecture                            |

| 7.17 | DCO core schematic                                 |

| 7.18 | DCO current DAC                                    |

| 7.19 | DCO stabilization functional diagram               |

| 7.20 | Power section enclosed in red box                  |

| 7.21 | Architecture of a low-dropout regulator            |

| 7.22 | Architecture of a buck regulator                   |

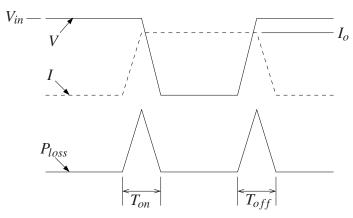

| 7.23 | Switching losses in a buck regulator               |

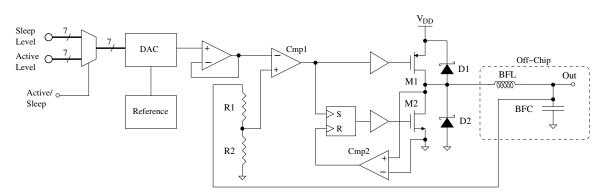

| 7.24 | Architecture of the buck regulator                 |

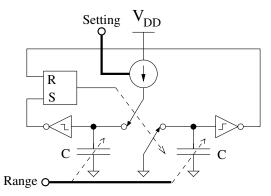

| 7.25 | Ripple voltage adjustment                          |

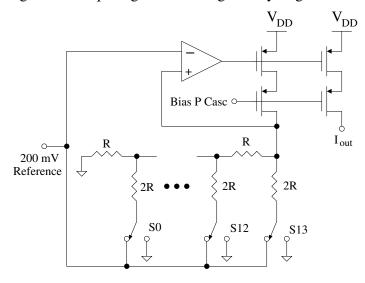

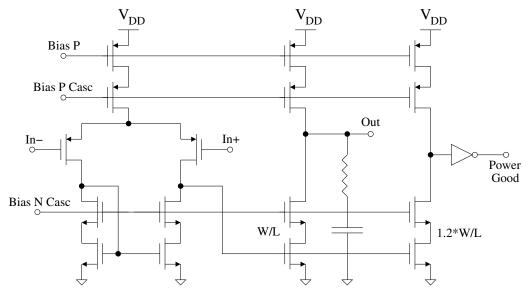

| 7.26 | Schematic of the reference/DAC buffer              |

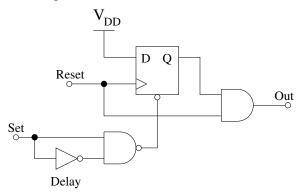

| 7.27 | Schematic of the SR flip-flop                      |

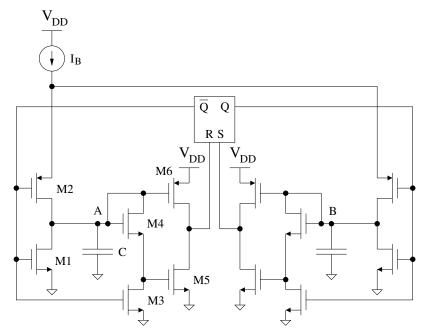

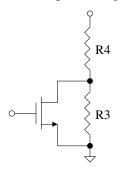

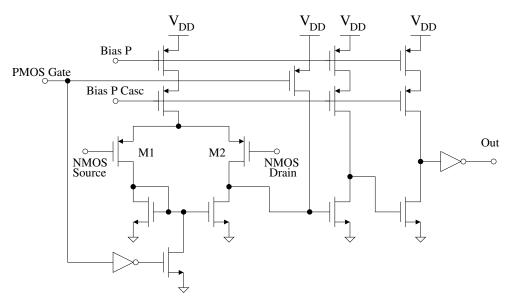

| 7.28 | Schematic of zero-current comparator               |

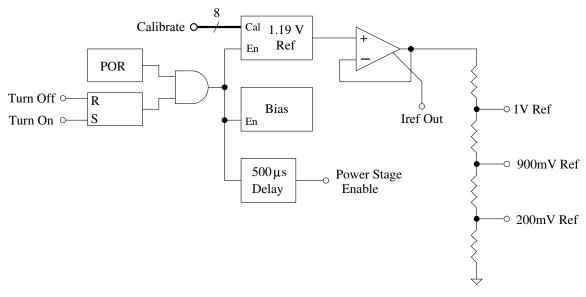

| 7.29 | Reference and supporting circuitry                                                                                    | . 207 |

|------|-----------------------------------------------------------------------------------------------------------------------|-------|

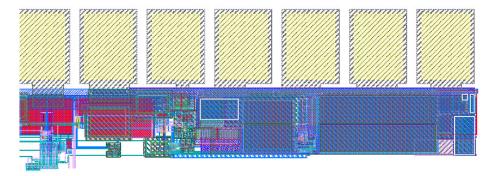

| 7.30 | Layout                                                                                                                | . 208 |

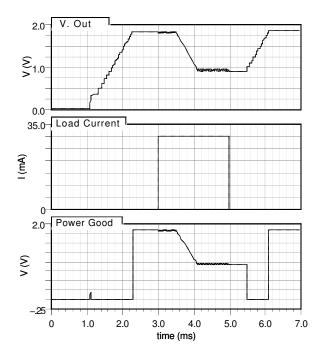

| 7.31 | Simulation with changing load current and dynamic voltage scaling                                                     |       |

|      | BFC = 20 $\mu$ F BFL = 100 $\mu$ H Vin = 3.3 V                                                                        | . 209 |

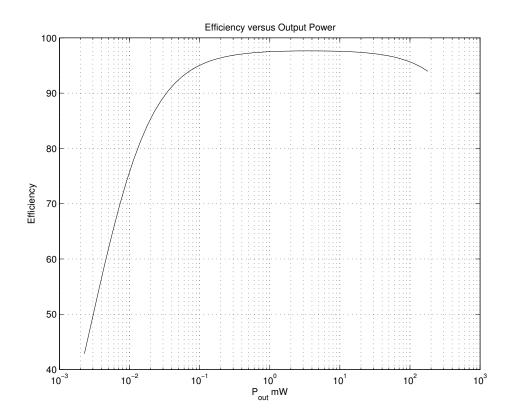

| 7.32 | Simulation showing efficiency as a function of output power                                                           |       |

|      | BFC = 20 $\mu$ F BFL = 100 $\mu$ H Vin = 3.3V Vout = 1.8V                                                             | . 210 |

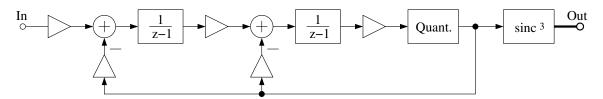

| 7.33 | Delta-Sigma ADC converter architecture showing the second-order modula-                                               |       |

|      | tor and the digital sinc <sup>3</sup> filter. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | . 210 |

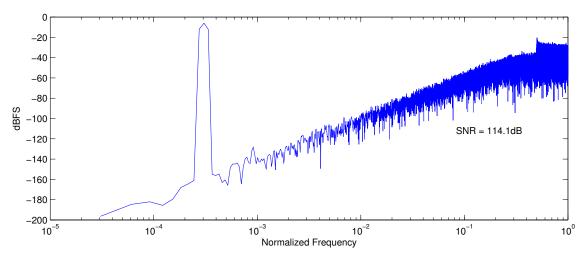

| 7.34 | Delta-Sigma modulator simulation.                                                                                     | . 211 |

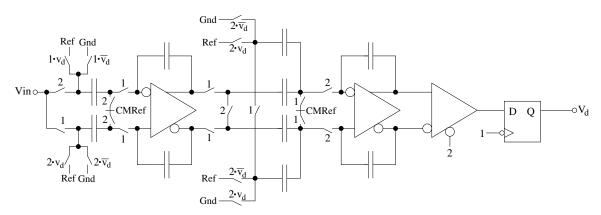

| 7.35 | Delta-Sigma switched-capacitor modulator implementation                                                               | . 211 |

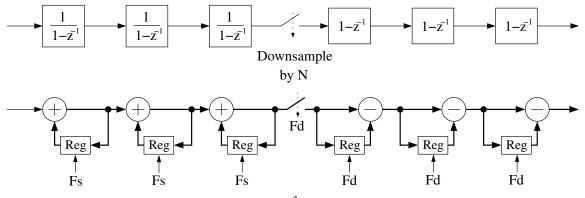

| 7.36 | Sinc <sup>3</sup> filter architecture.                                                                                | . 212 |

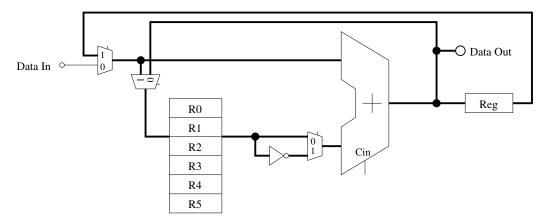

| 7.37 | $Sinc^3$ filter implemented datapath                                                                                  | . 213 |

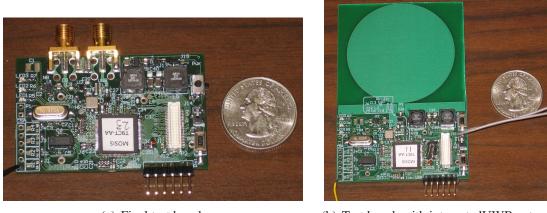

| 8.1  | First AMS 0.35 $\mu$ m chip and testbed architecture                                                                  | . 219 |

| 8.2  | First chip layout and die photo                                                                                       | . 219 |

| 8.3  | First AMS 0.35 $\mu$ m chip testbed                                                                                   | . 220 |

| 8.4  | Second IBM 0.18 $\mu$ m chip and testbed architecture                                                                 | . 221 |

| 8.5  | Second IBM 0.18 $\mu$ m die photo                                                                                     | . 222 |

| 8.6  | Second chip test board                                                                                                | . 222 |

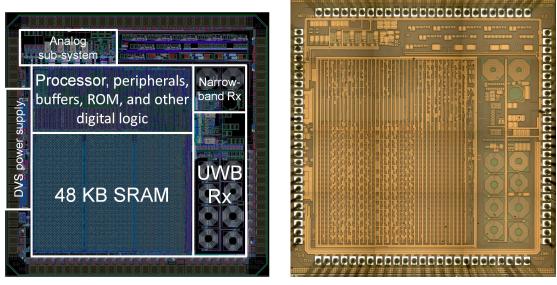

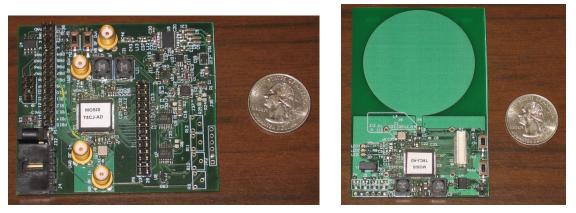

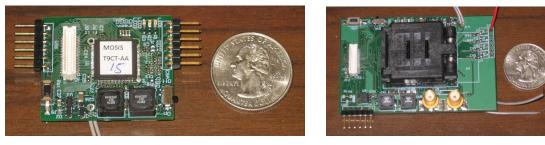

| 8.7  | Third IBM 0.18 $\mu$ m chip and testbench architecture                                                                | . 224 |

| 8.8  | Third chip layout and die photo                                                                                       | . 225 |

| 8.9  | Two testing boards for the third chip                                                                                 | . 226 |

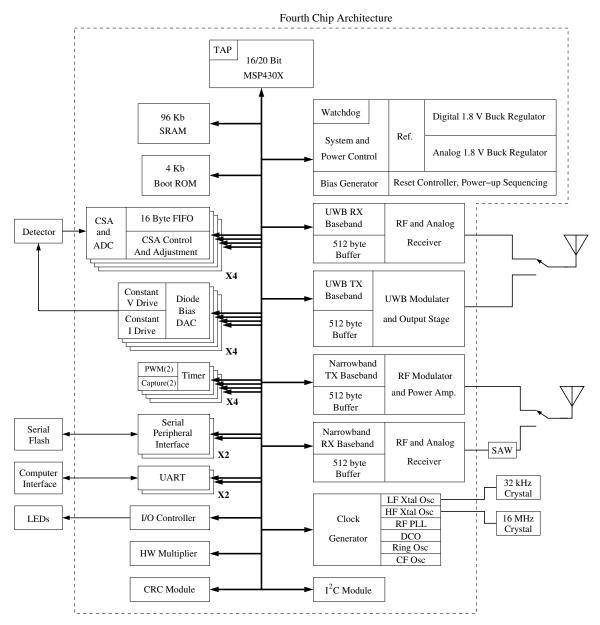

| 8.10 | Fourth IBM 0.18 $\mu$ m chip and testbench architecture                                                               | . 228 |

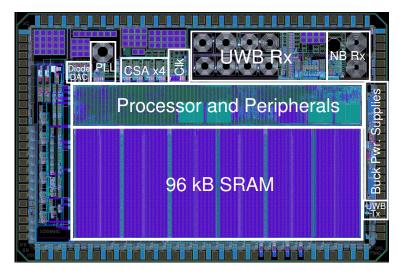

| 8.11 | Fourth chip layout and die photo                                                                                      | . 229 |

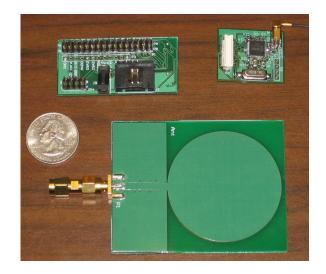

| 8.12 | A number of fourth chip test boards.                                                                                  | . 230 |

| 8.13 | Fourth chip test boards accessories                                                                                   | . 231 |

| 8.14 | Test equipment used in testing the chips                                                                              | . 231 |

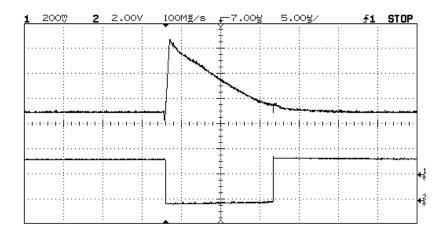

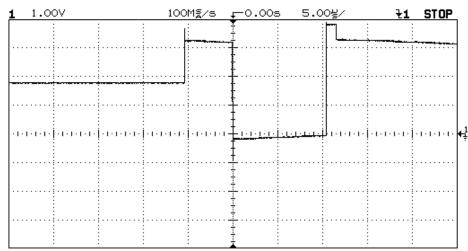

| 9.1  | Measured CSA output and the ADC trigger line                                                                          | . 234 |

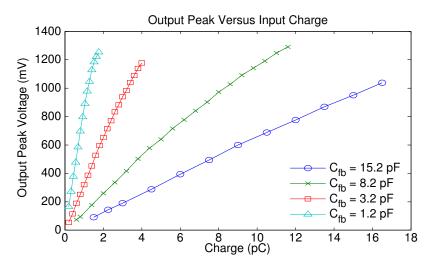

| 9.2  | CSA output peak versus charge input                                                                                   | . 234 |

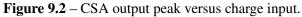

| 9.3  | ADC DNL and INL measurements                                                                                          | . 235 |

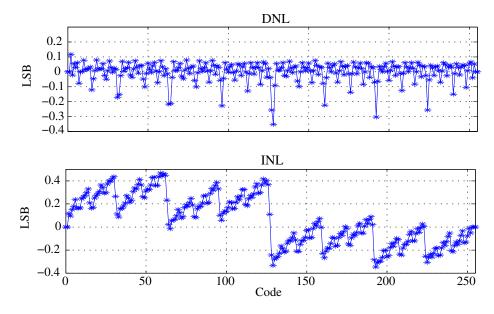

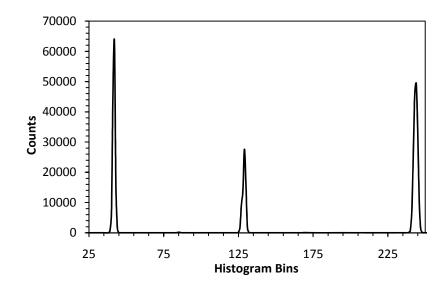

| 9.4  | A sample histogram acquired with a function generator producing three dis-                                            |       |

|      | tinct charge pulse sizes                                                                                              | . 236 |

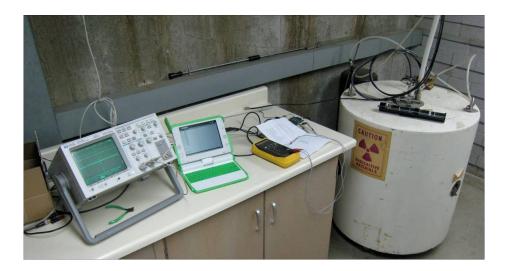

| 9.5  | Field test setup                                                                                                      | . 238 |

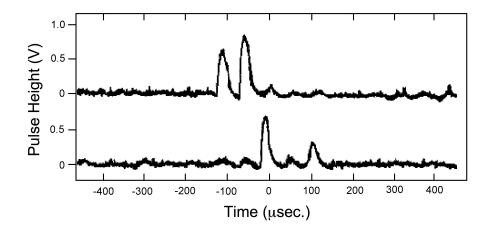

| 9.6  | Charge sensitive amplifier output waveforms.                                                                          | . 239 |

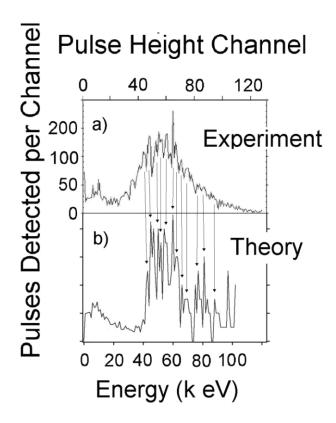

| 9.7   | The pulse height spectra of 15% Gd doped $HfO_2$ on n-type Si(100) with ther-             |       |

|-------|-------------------------------------------------------------------------------------------|-------|

|       | malized neutrons from a PuBE source.                                                      | . 240 |

| 9.8   | Gamma detector schematic.                                                                 | . 241 |

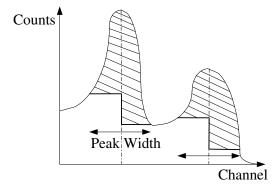

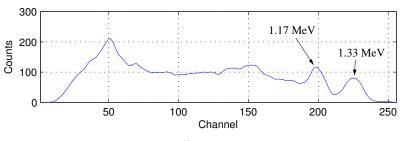

| 9.9   | <sup>133</sup> Ba, <sup>65</sup> Zn, and <sup>137</sup> Cs combined gamma energy spectrum | . 243 |

| 9.10  | Area calculation example                                                                  | . 244 |

| 9.11  | <sup>60</sup> Co smoothed spectrum                                                        | . 245 |

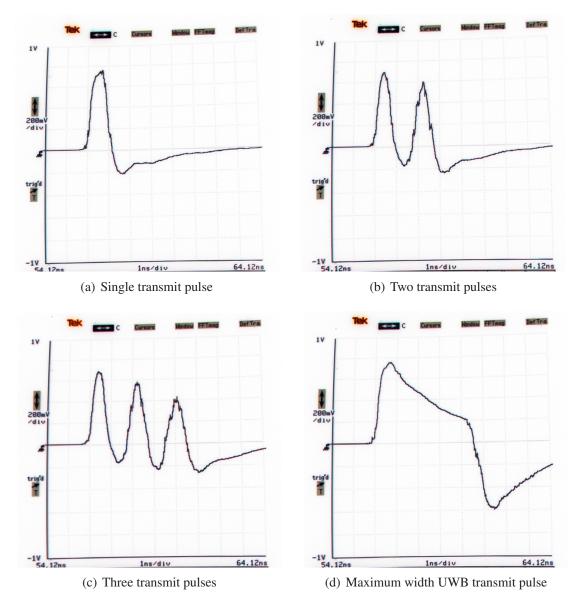

| 10.1  | Various transmitter waveforms.                                                            | . 249 |

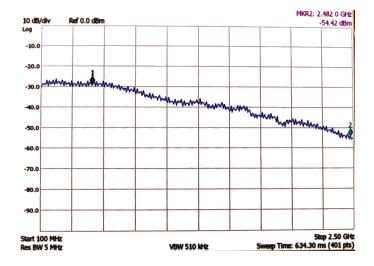

| 10.2  | Spectrum of unfiltered UWB pulses.                                                        | . 250 |

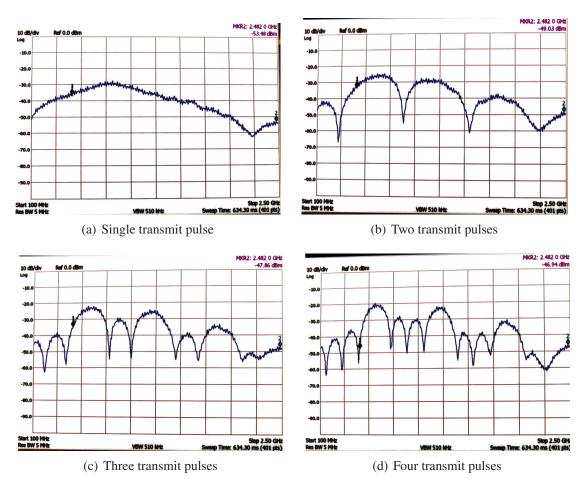

| 10.3  | Spectra for transmitted filtered signal                                                   | . 251 |

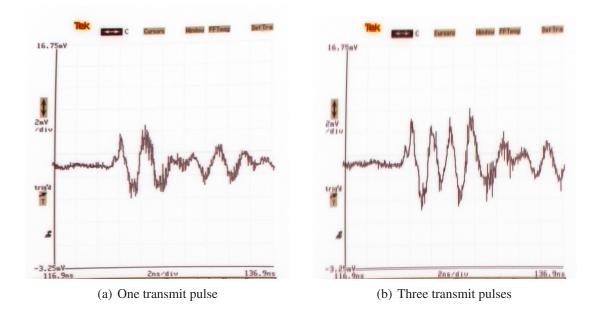

| 10.4  | Received waveforms in the anechoic chamber                                                | . 252 |

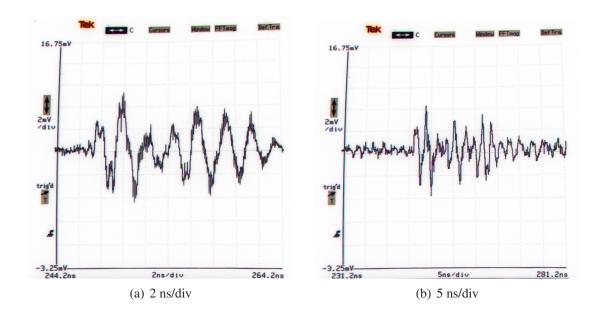

| 10.5  | Received waveforms in the lab, one pulse transmitted                                      | . 252 |

| 10.6  | UWB baseband signal with different conditions.                                            | . 255 |

| 10.7  | False alarm rate versus correlator threshold                                              | . 257 |

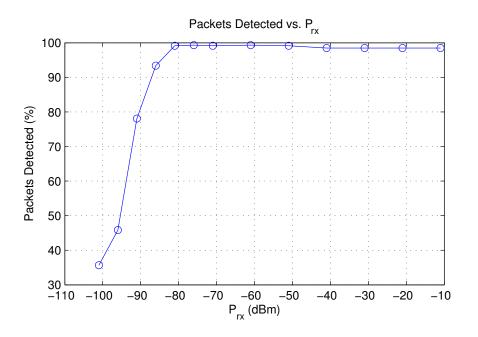

| 10.8  | Packet detection results versus received power.                                           | . 259 |

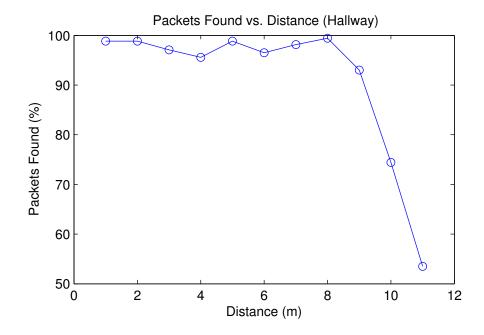

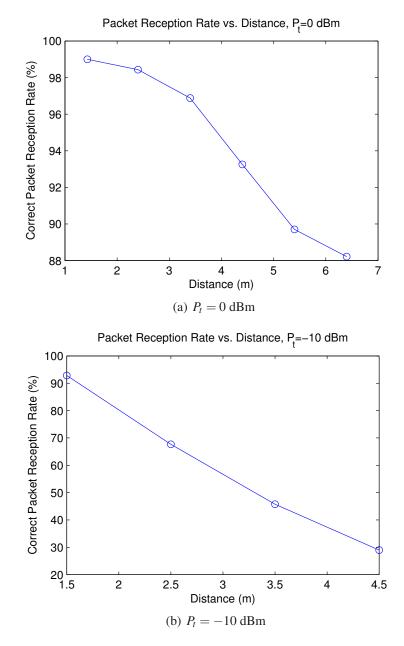

| 10.9  | Packet detection results versus distance.                                                 | . 259 |

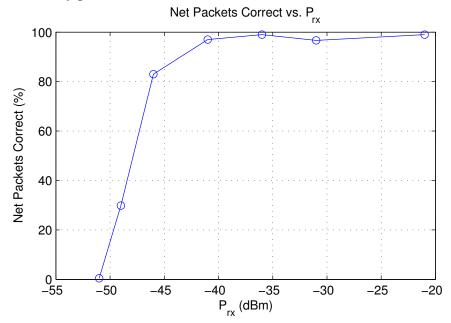

| 10.10 | Correct packet reception versus received signal power with symbol synchro-                |       |

|       | nization enabled                                                                          | . 260 |

| 10.11 | Percent of packets received correctly vs. distance with no synchronization                |       |

|       | enabled                                                                                   | . 261 |

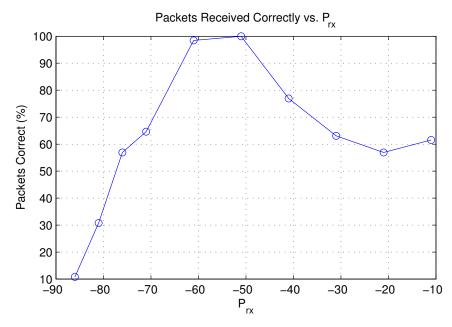

| 10.12 | Percent of packets received correctly vs. received signal power with no syn-              |       |

|       | chronization enabled.                                                                     | . 262 |

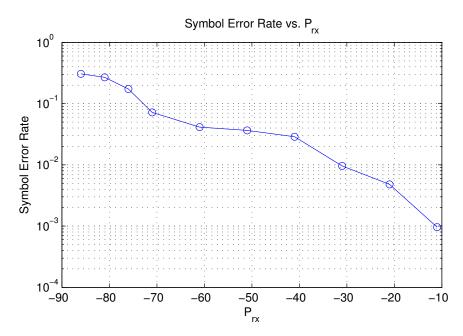

| 10.13 | Symbol error rate vs. received signal power.                                              | . 263 |

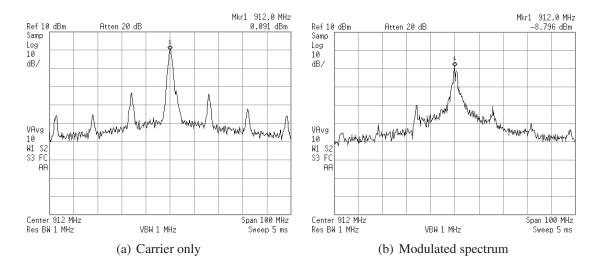

| 10.14 | Narrowband transmitter spectrum.                                                          | . 267 |

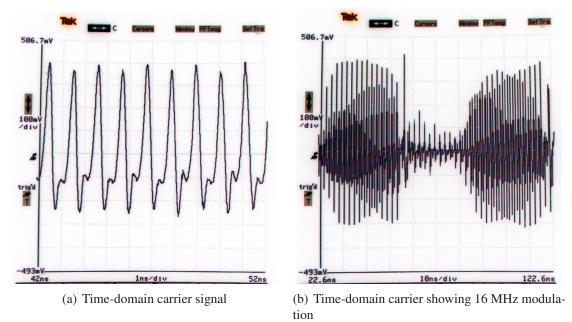

| 10.15 | Narrowband transmitter time-domain signal.                                                | . 267 |

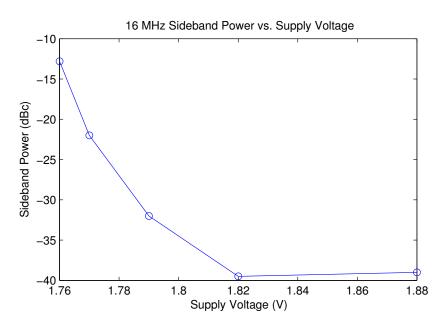

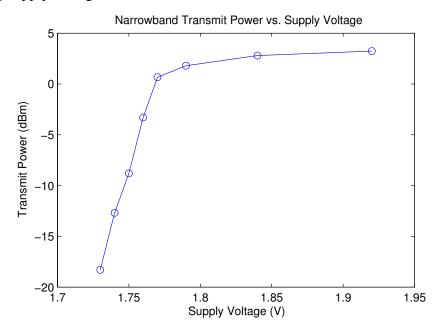

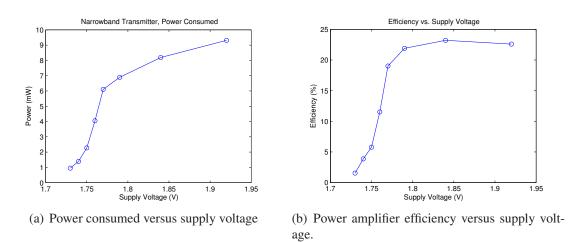

| 10.16 | Narrowband 16 MHz sideband power versus supply voltage                                    | . 268 |

| 10.17 | Narrowband transmitter power output versus supply voltage                                 | . 269 |

| 10.18 | Narrowband transmitter power consumed and efficiency                                      | . 269 |

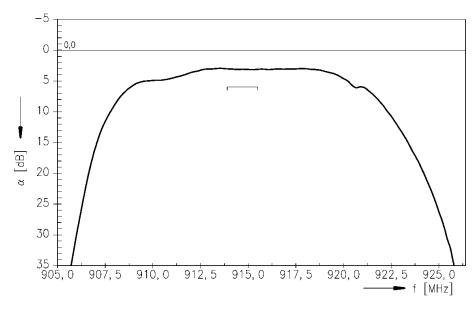

| 10.19 | Narrowband receiver SAW filter response.                                                  | . 271 |

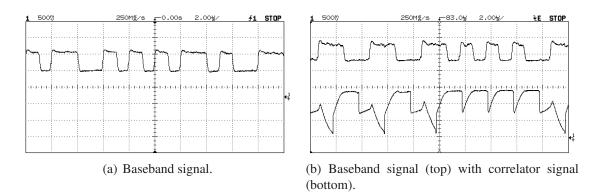

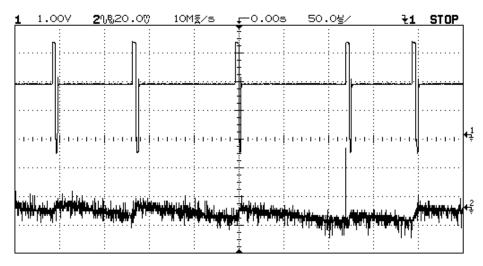

| 10.20 | Narrowband receiver baseband and correlator signals.                                      | . 271 |

| 10.21 | Baseband signal (bottom) and AGC control voltage (top) showing sudden                     |       |

|       | gain fluctuation.                                                                         | . 273 |

| 10.22 | Correct packet reception versus distance-anechoic chamber                                 | . 274 |

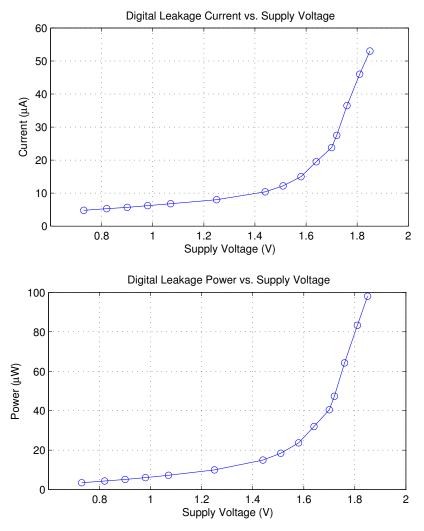

| 11.1 | Measured leakage current and power consumption versus supply voltage for      |

|------|-------------------------------------------------------------------------------|

|      | the fourth chip                                                               |

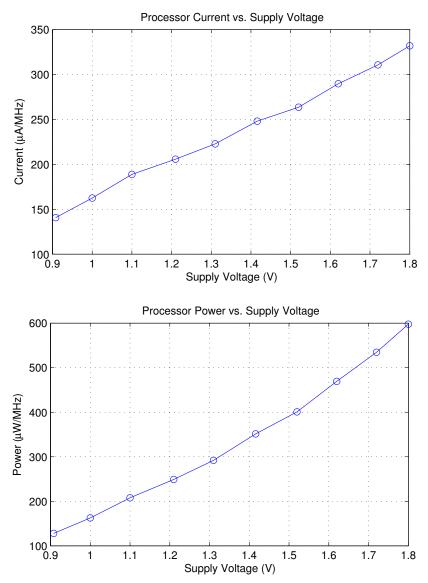

| 11.2 | Measured processor dynamic current and power consumption versus supply        |

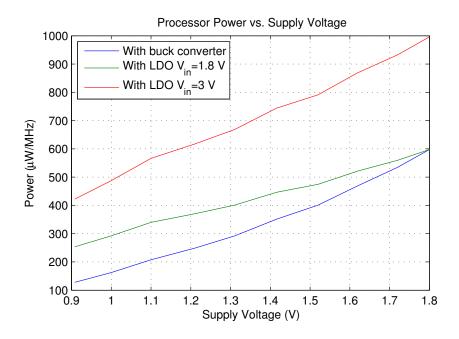

|      | voltage for the fourth chip                                                   |

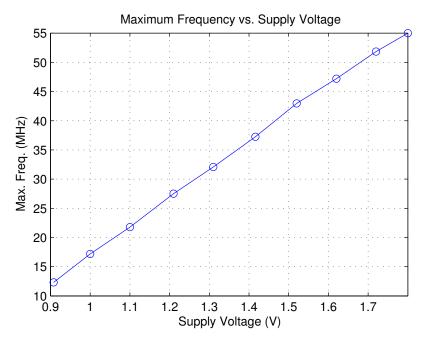

| 11.3 | Maximum frequency versus supply voltage for the fourth chip                   |

| 11.4 | Comparison between using an LDO and buck regulator to power the digital       |

|      | core                                                                          |

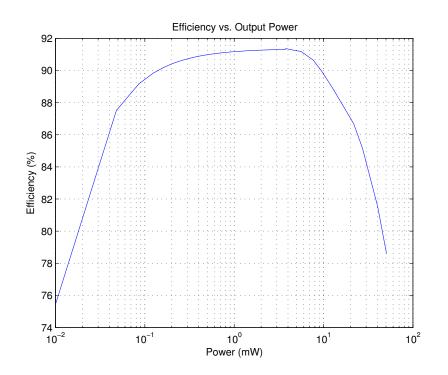

| 11.5 | Measured efficiency as a function of output power.                            |

|      | BFC = 20 $\mu$ F BFL = 330 $\mu$ H Vin = 3.3V Vout = 1.8V                     |

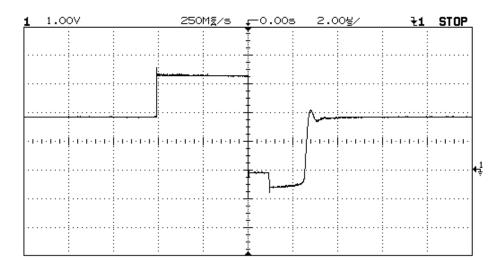

| 11.6 | Switching event when the lower MOSFET turns off too quickly                   |

| 11.7 | Switching event when the lower MOSFET turns off too slowly                    |

| 11.8 | Switching events (top) and output voltage ripple (bottom)                     |

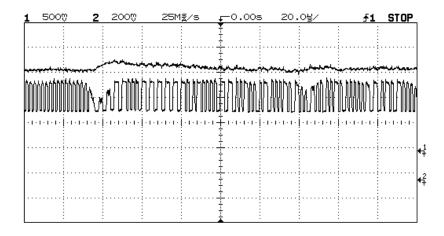

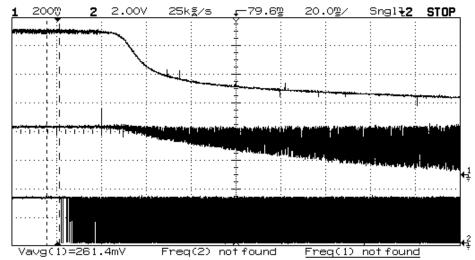

| 11.9 | Low frequency crystal oscillator starting, top (500 mV/div) is the amplitude  |

|      | control voltage, middle (200 mV/div) is the amplitude of the oscillator, bot- |

|      | tom (2 V/div) is the digital output                                           |

# **List of Tables**

| 2.1  | Detection Technologies                       |

|------|----------------------------------------------|

| 4.2  | Constant generator                           |

| 4.3  | Addressing modes                             |

| 4.4  | Interrupt Sources                            |

| 4.5  | MSP430X Instructions                         |

| 4.6  | Instruction encoding                         |

| 4.7  | Single-operand instruction op-codes          |

| 4.8  | Jump conditions                              |

| 4.9  | Double-operand instruction op-codes          |

| 4.10 | Non-register mode extension word             |

| 4.12 | CPU control logic states                     |

| 4.13 | State Transitions                            |

| 4.14 | Hardware multiplier register function select |

| 5.1  | Convolutional Code Polynomials               |

| 5.2  | Forward and reverse interleaver functions    |

| 5.3  | LFSR Initial Conditions                      |

| 7.1  | Loop-filter response                         |

| 7.2  | Circuit Specifications                       |

| 8.1  | Chip Comparison                              |

| 9.1  | Measured Gain                                |

| 9.2  | CSA Specifications                           |

| 9.3  | Front End Detailed Power Measurements        |

| 9.4  | Comparison with Related Work                 |

| 9.5   | Gamma Detection Code Specifications                                                                        |

|-------|------------------------------------------------------------------------------------------------------------|

| 9.6   | Gamma Classification Results                                                                               |

| 10.1  | UWB Transmitter Circuit Area                                                                               |

| 10.2  | UWB Transmitter Power Consumption, $F_{\text{symbol}} = 10 \text{ Meg}$ , $V_{\text{dig}} = 1.4 \dots 248$ |

| 10.3  | Transmitted Power                                                                                          |

| 10.4  | UWB Receiver Circuit Area                                                                                  |

| 10.5  | UWB Receiver Power Consumption, $F_{\text{symbol}} = 10 \text{ Meg}, V_{\text{dig}} = 1.4 \dots 254$       |

| 10.6  | RF Front End Noise                                                                                         |

| 10.7  | Packet Detection Correlator Systematic Bias                                                                |

| 10.8  | UWB Receiver Comparison                                                                                    |

| 10.9  | Narrowband Transmitter Specifications                                                                      |

| 10.10 | Narrowband Receiver Specifications                                                                         |

| 11.1  | Digital Section Area                                                                                       |

| 11.2  | Clock Peak-to-Peak Jitter                                                                                  |

| 11.3  | Clock Current Consumption                                                                                  |

| 11.4  | Mote Hardware Comparison                                                                                   |

| A.1   | Pinout                                                                                                     |

## Nomenclature

- ADC Analog to digital converter

- AGC Automatic gain control

- ALU Arithmetic and logic unit

- AWGN Additive white Gaussian noise

- ECC Error correcting code

- CDMA Code division multiple access

- CMOS Complementary metal-oxide semiconductor

- COTS Commercial off the shelf

- CRC Cyclic redundancy check

- CSA Charge sensitive amplifier

- CTS Clock tree synthesis

- DAC Digital to analog converter

- DCO Digitally controlled oscillator

- DNL Differential non-linearity

- DRC Design rule check

- DVS Dynamic voltage scaling

- FFT Fast Fourier transform

- FIFO First in first out

- FIR Finite impulse response

- GPS Global positioning system

- I<sup>2</sup>C Inter-IC bus

- IIR Infinite impulse response

- IP Intellectual property

- INL Integral non-linearity

- ISM Industrial medical scientific

- ISR Interrupt service routine

- I/O Input/Output

- LDO Low-dropout voltage regulator

- LNA Low noise amplifier

- LO Local oscillator

- LSB Least significant byte/bit

- LVS Layout versus schematic

- MSB Most significant byte/bit

- NMI Non-maskable interrupt

- OFDM Orthogonal frequency division modulation

- OOK On-off keying

- OTA Operational transconductance amplifier

- p-cell Parameterized Cell

- PFD Phase-frequency detector

- PFM Pulse-frequency modulation

- PLL Phase-locked loop

- PMT Photomultiplier tube

- PN Pseudorandom noise

- PPM Pulse-position modulation

- PSK Phase-sift keying

- PVT Process voltage temperature

- PWM Pulse-width modulation

- QAM Quadrature amplitude modulation

- RAM Random access memory

- RF Radio frequency

- RMS Root mean squared

- ROM Read only memory

- RTL Register transfer level

- SAW Surface acoustic wave

- SNR Signal to noise ratio

- SPI Serial Peripheral interface

- SRAM Static RAM

- UART Universal asynchronous receiver/transmitter

- UWB Ultra-wideband

- VCO Voltage controlled oscillator

- VHDL VHSIC hardware description language; VHSIC—very-high-speed integrated circuit

- WSN Wireless sensor network

Throughout the dissertation references may be made to registers and specific bits within the registers. These registers define the user interface which a program uses to interact with the hardware. When referenced, the register names and bit names are denoted with an different font, for example the HFEn bit in the OSC\_CR register enables the crystal oscillator.

For full definitions of all the registers and bits within them, see the supporting chip datasheet.

Assembly instructions for the integrated processor are denoted with a fixed-width font, for example mov r4,r5.

# Part I

# Introduction

## Chapter 1

# Overview

The miniaturization of electronics and sensors in recent years had led to the development of wireless sensor networks (WSN). These consist of a number of small nodes, called motes, which have one or more sensors of some type and wireless connectivity to other motes. The motes may be deployed over an area to monitor a physical quantity of interest. Wireless sensor networks have many exciting applications in diverse fields ranging from habitat monitoring to medical applications to defense systems. The one theme in WSNs have in common is extremely stringent energy requirements. Simultaneously, many new applications are not feasible with today's power consumption, but with lower energy requirements, a vast array of exciting applications could be enabled.

The power consumption of today's motes allow battery lifetimes in the order of weeks to months, however many applications only become feasible with much longer battery lifetimes of years. To achieve this the average power consumption of a mote must be dramatically decreased from the 3-20 mW consumed on average by today's motes to 100-500  $\mu$ W for battery lifetimes of up to 5 years from two AA batteries.

To achieve this power consumption, revolutionary new hardware is required which decreases the power consumed in all areas of the system. This dissertation presents the design of an ultra-wideband (UWB) based single-chip wireless sensor network node. The presented sensor node has many advanced features which allows a substantial improvement over present state-of-the-art designs in virtually every aspect. The presented hardware will allow the permeation of wireless sensor networks into a variety of new applications that are not practical with today's technology.

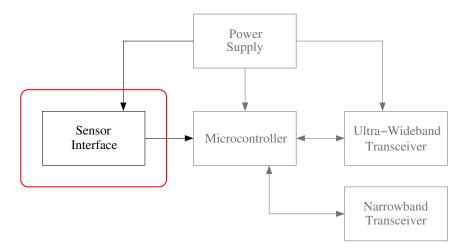

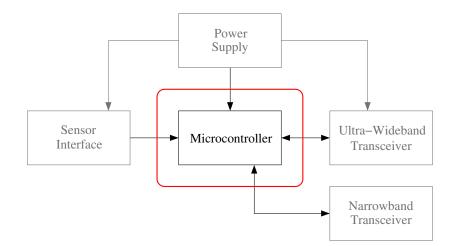

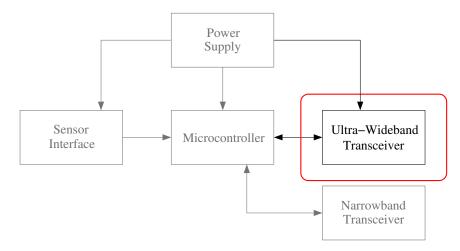

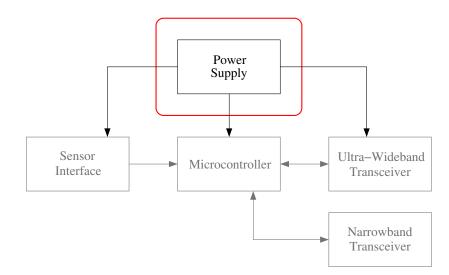

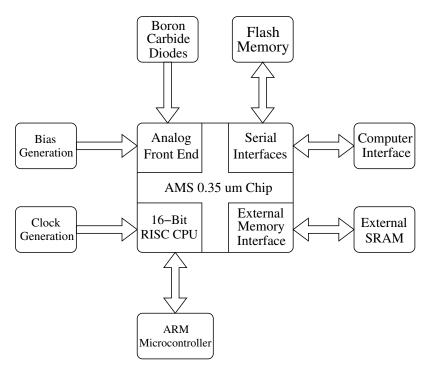

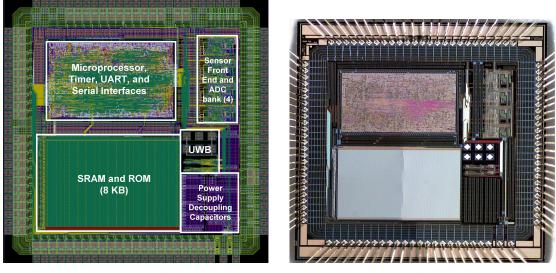

The architecture for the design is shown in Figure 1.1. This is a standard architecture with the exception of the dual RF transceivers present on this design. Each of the parts

will be discussed in later chapters. The power consumption of each must be minimized to minimize total system power consumption.

Figure 1.1 – WSN node architecture presented in this dissertation.

### **1.1 Contributions**

The sensor network node designed has many improvements over existing nodes in each of the major sub-systems shown in Figure 1.1. The main contributions of this work include a number of low-power innovations targeted at many different sub-systems within a wireless sensor network. To dramatically decrease the system power consumption, the power of each of the individual blocks within a WSN must be decreased. Combining these numerous low power innovations can decrease the power consumption of future wireless sensor networks. These innovations include:

<u>A low-power event driven charge-sensitive amplifier front end for sensor interface applications.</u> The front end measures the size of the charge pulse. The presented front end has much lower power consumption than any in the literature. This is achieved through two methods. One is by utilizing a low-power architecture for the initial charge sensitive amplifier. The novel architecture allows the bias currents in the amplifier to be scaled to very low values while still maintaining good performance. Further power savings is achieved through the use of an event-driven front end where the charge pulse amplitude is measured in the analog domain before being converted to digital. This decreases the sample rate of the ADC to simply the count rate as

opposed to the Nyquist rate for a conventional front end, thus saving power. Overall, the CSA power consumption is as low as  $4 + 0.075R \mu W$  where *R* is the particle rate in thousands of particles per second.

- <u>A low-power digital core for processing the sensor data and mote control functions.</u> The low power consumption is achieved through the use of dynamic voltage scaling which is in turn implemented with extremely low-power integrated buck power converters. The buck converters also support a sleep voltage which is lower than the operating voltage to save leakage power. The buck converters are designed to have a high efficiency even when the output current is very small by using a pulse-frequency modulation scheme. Using buck converters instead of the alternative linear regulators allows high efficiency, even with a low output voltage. The digital sleep power consumption of the system can be as low as 3  $\mu$ W while the computational power can be as low as 140  $\mu$ W/MHz.

- <u>A low-power UWB transceiver for use in short range wireless sensor networks.</u> The simple analog architecture consumes much less power than competing designs, and is one of the few complete UWB transceivers in the published literature. The design includes a novel wideband amplifier in the front end which uses a standard symmetrical inductor as a transformer to extend the bandwidth of an amplifier while still only requiring the area of one inductor. The baseband architecture contains many parallel analog correlators which simultaneously allow both low power and accurate and reliable signal acquisition, even in poor channel conditions. Furthermore, unlike other designs, it includes a variable rate hardware error control code to simultaneously maximize reliability, range, and datarate. The UWB transmitter uses 0.46-2.3 nJ/bit to transmit the data while the UWB receiver consumes 3.52-17.6 nJ/bit to receive the data. This is much lower than any narrowband communication power by at least an order of magnitude.

- <u>A simple low-power narrowband transceiver</u>. This can can be used in applications where power consumption is critical and the associated negative aspects of the receiver can be accommodated.

- <u>A single-chip solution</u>. The single chip solution allows lower cost, higher performance, and lower power over multi-chip solutions.

Both the UWB and narrowband transceivers have a much lower energy/bit than conventional transceivers. The UWB transceiver can be low power due to the wide bandwidth usage, while the narrowband receiver can be low power simply due to its simple architecture.

All the required active circuitry, except for the flash memory for program storage, are integrated on a single die. This provides many benefits for sensor networks. First, with sufficient volume, it can decrease the price of a sensor network node. Furthermore, it can also decrease the physical size of the electronics. Finally, the high integration allows for power savings which can be gleaned from the efficiency that comes with high integration. As an example, consider a COTS sensor node such as the MicaZ mote, where there are separate processor and radio transceiver chips connected by a serial bus. The serial bus connecting the two operates at a couple mega-baud. This means that when a radio packet needs to be transferred between the two chips, it takes some time for this to occur. Not only does this slow down the maximum throughput of the transceiver, it also requires much processing by the microcontroller to individually send or receive the bytes to/from the radio chip. This requires the processor to execute many more instructions than in the presented design where the overhead of communicating with the transceiver is negligible.

Four separate chips were designed for the the dissertation, one on a 0.35  $\mu$ m process, and the other three on a 0.18  $\mu$ m process. The final chip is the culmination of all previous chips, the design of which will be discussed in Part II of this dissertation. The final chip area is  $3 \times 4.5 \text{ mm}^2$  and has many impressive specifications. The dynamic digital power consumption consumes up to an order of magnitude less power than the widely available commercial-off-the-shelf (COTS) solutions, the UWB transmitter consumes two orders of magnitude less power consumption, while the UWB receiver consumes one order of magnitude less power. Furthermore, the processing frequency can be many times greater than similar COTS products. Combined, this should allow wireless sensor networks to find uses in many new applications where previously not possible.

The design was funded by the DOE grant titled "All Solid-State Wireless Sensor Network for Nuclear Proliferation Detection" In this grant, it was specified that the target topology is a simple star, where all nodes have direct communication with a less-powerconstrained sink. Furthermore, it was also specified that the communication from the sink to the nodes use a narrowband technique, due to the possibility of a simple low-power receiver at the node, and the communication from the nodes to the sink use a UWB technology due to the possibility of a simple low-power transmitter. This dictated the requirement for both a UWB and narrowband functionality.

Per the grant, the node only needs to integrate the UWB transmitter and the narrowband receiver, while the sink may implement the UWB receiver and narrowband transmitter however it likes, even with high power components. However, when deciding how to make the UWB receiver, it was determined to fully integrate this on the chip, and the same was done for the narrowband transmitter. Therefore, the fabricated sensor node has two complete transceivers and thus could support a multi-hop sensor network with the addition of a suitable protocol.

### 1.2 Organization

This dissertation is divided into three parts. Part I which contains chapters 1 and 2 is the introduction and overview of the dissertation. This presents some background information and outlines the major contributions of this work.

Part II which contains chapters 3-7 presents the design of the individual parts of the presented sensor network. Chapter 3 presents the charge sensitive amplifier front end and the event-driven ADC. Chapter 4 presents the digital core. This is a standard MSP430X microcontroller with a few small modifications. Chapter 5 presents the ultra-wideband transceiver. This includes the convolutional code used, the transmitter, and the receiver. Chapter 6 presents the the low-power narrowband transceiver. Finally, chapter 7 presents some supporting circuitry including the power supply and clock system.

Part III which contains chapters 8-12 presents the measured results of the various chips. Chapter 8 presents the test boards and software used to test the chips. Chapter 10 presents the measured results from the UWB and narrowband transceivers. Chapter 11 presents the measured results for the processor core and provides a comparison of the complete system with other WSN platforms. Finally, chapter 12 concludes the dissertation.

## Chapter 2

## Motivation

This chapter gives some background information and motivation for this work. Section 2.1 discusses the applications, requirements, and principles behind wireless sensor networks and the specific hardware requirements which need to be addressed. Section 2.2 gives background information to the problem of power consumption in digital circuits and what approaches have been taken to address it. Section 2.3 discusses a number of techniques which are used to detect radiation and the benefits of each. This section also discusses the conventional detection electronics used with these detectors. Section 2.4 discusses UWB technology and the presently used designs. Section 2.5 presents the merits of a single-chip solution and how this can provide better performance than a multi-chip solution. Section 2.6 presents a brief overview of the various chips where were designed and fabricated for the project.

### 2.1 Sensor Networks

Recent advances in microelectronics and sensors have enabled the development of miniaturized low-power sensor systems which can be networked in a wireless manner for longduration wide area monitoring. They cover a vast array of applications with each application having different requirements [1, 2]. Each application generally has different constraints on power, weight, communication range, battery life, and cost, so many different architectures exist to fit many different needs.

#### 2.1.1 Applications

Wireless sensor networks have been used for many different applications, each with different requirements. Nonetheless, the hardware for many different applications uses a similar base unit with different sensors attached.

One important application is habitat and wildlife monitoring. In [3] a wireless sensor network was used to monitor the presence of petrel birds on Great Duck Island off the coast of Maine. In this application the wireless sensor network allows for monitoring of the bird's burrows without disturbing them. A similar application is presented in [4] except they are monitoring rare or endangered plants instead of animals. In [5] the sensor networks were carried on the animals, Zebras in this case, and the authors studied how to handle the mobile and constantly changing nature of the network. In this case each sensor has GPS capabilities to record the movement pattern of the individual Zebras. A similar, but more advanced work is also being carried on by researchers here at UNL on tracking whooping cranes [6]. This is more challenging due to the very severe weight constraints.

Wireless sensor networks can also be used to monitor environments which may pose a danger to prolonged human presence such as hurricanes or volcanoes. In [7] a wireless sensor network was designed to monitor infrasonic signals during volcano eruptions.

Wireless sensor networks have also found application in agricultural contexts. In [8] a wireless sensor network was designed to determine what parasites may be present in a vineyard and determine the need for an insecticide. In this case the focus was on the sensor node processing the local data and making its decision. [9–11] investigates the properties and feasibility of placing the sensors underground and the effect this has on the wireless channel.

Wireless networks also have many applications in the medical field. In [12] a system was made to monitor patients' vital signs and report to medical health professionals for assistance in diagnosis.

A multitude of military applications also exist for sensor networks. In [13] a WSNbased system was built to determine the location of a sniper based on the time of arrival.

Though there exist a number of different applications, some unifying themes can be found in them. First, and most importantly, the sensors are generally small, cheap and power constrained. Due to their small size and cost sensitivity, large batteries cannot be used, so power consumption is of the utmost concern in sensor networks. This one factor is the main driving force for much of the research being done in the field, and is also the main factor impeding the deployment of sensor networks to a much larger set of applications than they are used for today.

Other defining characteristics of wireless sensor networks include a much higher deployment density than traditional ad hoc wireless networks, nodes which may be prone to failure, and many times the network connectivity is not static but can change with time due to either node mobility, node failure, or wireless channel conditions.

#### 2.1.2 Lifetime

The lifetime of a sensor network is dependent upon the power it consumes and the size of the battery. To achieve a low-power system, the power must be decreased at all levels in both hardware and software [14]. The energy consumed in the wireless sensor network depends somewhat on the application, but in many applications it is dominated by the power consumed by the radio. The computational power and the leakage power are also significant in some applications. Finally, the sensing power varies greatly from application to application. In some applications it is negligible, however in others it can be dominating depending on the sensor modality [15].

The power consumption of the radio must be attacked from many angles to successfully decrease the power. This can include circuit-level design improvements, transceiver architecture level improvements, modulation and coding changes, radio technology and band used, and higher software-level functions such as medium-access protocol.

One method of decreasing the power is using a flexible modulation scheme which changes depending on the channel conditions [16]. For example, using a larger constellation size when the channel is good (i.e. high SNR) results in lower power consumption. Changing the code strength on the link depending on the channel conditions can also save power.

Various radio architectures can be used, but narrowband communication architectures presently dominate the field. However ultra-wideband radios can theoretically allow much higher data rate at much lower power when compared to conventional radio because the transmission bandwidth can be traded off for power and data rate.

At a higher network-level, the energy consumption can be decreased by a number of factors [17]. Some factors which can be optimized are area coverage, request spreading and data aggregation. Some methods focus on either decreasing the coverage or providing the same coverage with fewer nodes to allow some nodes to sleep and save power [18]. The authors in [19] analyze the precision and resolution requirements and use data aggregation.

gation at nodes to decrease the amount of data to transmit and save energy. Finally, the nodes within a network must attempt to spread out the network traffic between the nodes otherwise certain commonly-used nodes will run out of battery more quickly which may bring down the complete network [20].

WSNs generally use batteries, however energy scavenging can also be used [21]. Solar is the most common method, and can be used indoors with much lower power levels [22]. Solar generally requires some low-power maximum power point tracking circuit [23] to maximize the energy harvested. Mechanical energy harvesting focuses on kinetic and vibrational energy and can be harvested either by piezoelectric capacitors or a mass-spring-magnet system. In [24] a system was built with piezoelectric vibration harvesters. For worn sensors, energy can be harvested from the environment as in [25] where energy from walking was used.

The power consumed in the digital part of the chip includes the static digital leakage power and the dynamic power. Both of which may be significant depending on the application. The following section discusses the digital power consumption in more detail.

### 2.2 Digital Power Consumption

Both leakage power and dynamic power may be important depending on the application. A number of different methods can be used to decrease both static and/or dynamic power.

Leakage power is the power consumed when no digital switching activity is taking place. At any given instant, the vast majority of the logic in the system is not switching, so it is only dissipating leakage power. This power does not depend on switching frequency. It originates as sub-threshold leakage current across a transistor which is nominally off, but may leak a small amount. The leakage current for the classic long-channel approximation is [26]

$$I_{ds} \approx \frac{W}{L} I_s e^{\frac{Vgs - V_{th}}{a(kT/q)}}.$$

(2.1)

The amount of leakage is determined by a number of factors. First, it is an exponential function of  $V_{gs} - V_{th}$ . If we assume  $V_{gs} = 0$ , then this becomes a exponential function of  $V_{th}$ . As technology is scaled, the supply voltage is also generally scaled, and to maintain performance, the  $V_{th}$  must also be scaled. This means that smaller processes have higher leakage currents. The leakage also depends on the W/L of the transistor as well as process parameters  $I_s$  and a.

The long-channel approximation does not mention  $V_{ds}$  however for short-channel devices, the leakage also scales with  $V_{ds}$  due to a number of reasons [27]. For a static CMOS inverter,  $V_{ds}$  is the same voltage as  $V_{dd}$ . The most significant leakage is drain-induced barrier lowering (DIBL) in which the source injects carriers into the channel due to the high E-field present in the channel. A lower drain voltage decreases the injection. Other less-significant short-channel leakage effects include gate-oxide tunneling, hot-carrier injection, gate-induced drain leakage (GIDL), and punchthrough leakage [27].

One way of combating leakage power consumption is to use a larger process with a higher threshold and supply voltage, however this negatively affects dynamic power. A second way is to use high threshold transistors in a smaller process, however the higher-threshold transistors are slower than their normal-threshold counterparts. With an advanced digital design flow, it is possible to mix regular  $V_t$  and high  $V_t$  transistors so that the logic on the critical path is regular  $V_t$  while the remaining logic is high  $V_t$ . Another technique is using back-biasing of the substrate to dynamically change the threshold voltage allowing higher threshold voltages when the circuit is sleeping and lower threshold voltages when the circuit is active. The main drawback of this is the need for specialized IP which supports the separate substrate biasing. This IP requires more area for the same circuit to generate the back-bias voltage.