# University of Nebraska - Lincoln DigitalCommons@University of Nebraska - Lincoln

Theses, Dissertations, and Student Research from Electrical & Computer Engineering

Electrical & Computer Engineering, Department of

Summer 8-10-2012

# MODELING OF POWER SEMICONDUCTOR DEVICES

Tanya Kirilova Gachovska *University of Nebraska-Lincoln*, tgachovska@yahoo.com

Follow this and additional works at: http://digitalcommons.unl.edu/elecengtheses

Part of the Electrical and Electronics Commons, Electronic Devices and Semiconductor

Manufacturing Commons, and the Power and Energy Commons

Gachovska, Tanya Kirilova, "MODELING OF POWER SEMICONDUCTOR DEVICES" (2012). Theses, Dissertations, and Student Research from Electrical & Computer Engineering. 38. http://digitalcommons.unl.edu/elecengtheses/38

This Article is brought to you for free and open access by the Electrical & Computer Engineering, Department of at DigitalCommons@University of Nebraska - Lincoln. It has been accepted for inclusion in Theses, Dissertations, and Student Research from Electrical & Computer Engineering by an authorized administrator of DigitalCommons@University of Nebraska - Lincoln.

#### MODELING OF POWER SEMICONDUCTOR DEVICES

by

Tanya Kirilova Gachovska

#### **A DISSERTATION**

Presented to the Faculty of

The Graduate College at the University of Nebraska

In Partial Fulfillment of Requirements

For Degree of Doctor of Philosophy

Major: Electrical Engineering

Under the Supervision of Professor Jerry Hudgins

Lincoln, Nebraska

December 2012

MODELING OF POWER SEMICONDUCTOR DEVICES

Tanya Kirilova Gachovska, Ph. D

University of Nebraska, 2012

Adviser: Jerry L. Hudgins

One of the requirements for choosing a proper power electronic device for a converter is that it must possess a low specific on-resistance. The specific on-resistance

of a bipolar device is related to the base width and doping concentration of the lightly

doped drift region. This means that the doping concentration and the width of the low-

doped base region in a bipolar device must be carefully considered to achieve a desired

avalanche breakdown voltage and on-resistance. In order to determine the technological

parameters of a semiconductor device, a one dimensional analysis is used to calculate the

minimum depletion layer width,  $W_{min}$ , for a given breakdown voltage,  $V_{BD}$ , in Si, SiC and

GaN  $p^+n^-n^+$  structures. Further investigation is done to determine the optimum width of

associated depletion layers for different blocking voltages to achieve a minimal forward

conduction voltage drop.

The complete one-dimensional model for calculation of the minimum depletion

layer width,  $W_{min}$ , for a given breakdown voltage,  $V_{BD}$ , of a  $p^+n^-n^+$  structure is developed

and used to calculate the optimum width of the depletion layer for different blocking

voltages to achieve a minimal forward drop. The results show that the calculations of the

lightly doped drift region thicknesses, and associated breakdown voltages and forward

voltage drops, lead to incorrect solutions when applied to high voltage  $p^+n^-n^+$  structures using the simplified model equations for a  $p^+n$  structure. These results also indicate a minimal impurity doping concentration for  $p^+n^-n^+$  structures, below which little improvement in breakdown capability can be had. The analysis shows for example that optimization of the doping concentration to minimize  $V_F$  in a 5 kV Si diode could result in more than a 12% decrease in the forward drop, while for SiC and GaN this decrease is insignificant; typically less than 1%. Therefore, an optimization of the forward voltage drop by using the optimal doping concentration for corresponding breakdown voltages is necessary for proper design of a Si diode, while for wide band gap material devices this optimization is not necessary.

The second part of the dissertation presents a physics-based model of a SiC BJT and verification of its validity through experimental testing. The Fourier series solution is used to solve the ambipolar diffusion equation (ADE) in the transistor collector region. The model is realized using MATLAB® and Simulink®. The experimental results of static operation and also the simulated and experimental results of switching waveforms are given.

From the experimental and simulated results it is concluded that the model represents the static and switching characteristics of the SiC BJT quite well. From the experimental measurement results are calculated the switching losses of the BJT. The differences between simulated and measured switching losses during the turn-on and turn-off are 6.28% and 3.52%, respectively.

To my mother, Tsvetanka Dyulgerova (Цветанка Дюлгерова), she never missed to call and encourage me.

Thank you mom!

#### **ACKNOWLEDGEMENT**

First, I would like to thank my advisor, Dr. Jerry Hudgins, for his significant guidance throughout my Ph.D. study. He was always smiling and encouraging me, ready to share his in-depth knowledge. His advice and feedback have been invaluable for me.

I would also like to thank, Dr. Angus Bryant, from the School of Engineering, University of Warwick, Coventry, and Dr. Bin Du for their advice on the modeling of power semiconductor devices.

I also want to thank Dr. Enrico Santi, from the University of South Carolina, Dr. Alan Mantooth, from the University of Arkansas, and Dr. Anant K. Agarwal at Cree for their useful discussions and help.

My particular appreciation and thanks are also sent to my doctoral committee members, Dr. Dean Patterson, Dr. Natale Ianno, and Dr. Jinsong Huang, for their time and constructive suggestions.

I would like to thank Dr. Nathan Schemm for his help and advices.

I would like to thank Mrs. Patricia Worster for editing and proofreading my thesis.

I would also like to extend my thanks to all of my friends, especially Mr. Fabio Parigi, Mrs. Kimberly J. Bay, Mr. Arindra Guha, Mr. Paul Franco, Mr. Joel Jacobs, Dr. Jessica

Colton, Dr. Liqin Ni, and Dr. Ufuk Parali. I am very appreciative of their help, support and friendship.

Special thanks to my Bulgarian friend living in Lincoln, NE, Angel Velichkov, for his support and jokes about semiconductors. (This year I defended for semiconductors, next year I will do conductors.)

I am especially grateful to my family for their continuous encouragement, their love, and their support. Finally, I would like to thank my daughter Anna, without whom I would never have started this Ph.D. study.

#### **NOMENCLATURE**

A Active device area, cm<sup>2</sup>

$A_i$ ,  $b_i$ , and  $m_i$  Amplitude parameter (cm<sup>-1</sup>), ionization energy parameter (V/cm),

and fit parameter

BV Breakdown voltage, kV

$BV_{CEO}$  Maximum open base breakdown voltage of BJT, kV

C,  $C_n$ , and  $C_p$  Auger coefficients, cm<sup>6</sup>/s

d Length from junction to case, cm

$d_1$ , W, and  $d_2$  Depletion region thicknesses of each section of  $N^+NP^+$  regions,

respectively, cm

D Ambipolar diffusivity, cm<sup>2</sup>s<sup>-1</sup>

$D_n$  and  $D_p$  Electron and hole diffusivities, cm<sup>2</sup>s<sup>-1</sup>

$D_{N}^{-}$  Electron diffusivity in  $N^{-}$  region, cm<sup>2</sup>s<sup>-1</sup>

$E_G$  Band gap energy, eV

$h_n$  and  $h_p$  Recombination parameters, cm<sup>-4</sup>s<sup>-1</sup>

$I_n$  and  $I_p$  Electron and hole currents, A

$I_{n0}$ ,  $I_{n1}$ , and  $I_{n2}$  Electron current at junctions  $J_0$ ,  $J_1$ , and  $J_2$ , A

$I_{p0}$ ,  $I_{p1}$ , and  $I_{p2}$  Electron current at junctions  $J_0$ ,  $J_1$ , and  $J_2$ , A

$I_{disp1}$  and  $I_{disp2}$  Displacement currents, A

$J_{n(N^+N^-)}$ ,  $J_{n(PN^-)}$  Electron carrier densities at the  $N^+N^-$  and  $PN^-$  junctions, Acm<sup>-2</sup>

k and n Harmonic indexes for CSR carrier density of Fourier series

representation

k Boltzmann's constant  $(1.381 \times 10^{-23} \text{ J/K})$

K Coefficient

$K_{FV}$  Feedback constant

M Number of the terms of the Fourier series

$N_{D1}$  Doping concentration in the lightly-doped *n*-base, cm<sup>-3</sup>

$N_{D2}$ ,  $N_{DI}$ ,  $N_A$  Doping concentration in the  $N^+N^-P^+$  regions, respectively, cm<sup>-3</sup>

$N_N$  Doping concentration in the N region, cm<sup>-3</sup>

$N_{\rm S}$  Number of effectively available states per unit volume

*n* Electron carrier concentration, cm<sup>-3</sup>

$n_i$  - Intrinsic carrier concentration, cm<sup>-3</sup>

$n_0 \dots n_7$  Nodes in lumped-charge model

$N_A$  Acceptor doping concentration, cm<sup>-3</sup>

$N_D$  Donor doping concentration, cm<sup>-3</sup>

*p* Hole carrier concentration, cm<sup>-3</sup>

p(x) Ambipolar carrier density as a function of position, cm<sup>-3</sup>

p(x; t) Ambipolar carrier density as a function of position and time, cm<sup>-3</sup>

$p_0(t)$  DC Fourier series component of the carrier storage region (CSR)

carrier density profile, cm<sup>-3</sup>

$p_k(t)$ ,  $p_n(t)$  - k- or  $n^{-th}$  Fourier series component of CSR carrier density profile, cm<sup>-3</sup>

$p_{x1}$  and  $p_{x2}$  Excess carrier concentrations at the two boundaries of the drift

region, cm<sup>-3</sup>

$p_{TI}$ ,  $p_{T2}$ , and  $p_{TI}$  Carrier densities of the two points of a segment and the carrier

density of the segment, cm<sup>-1</sup>

q Unit electrical charge ( $\cong 1.6 \times 10^{-19}$ )

$R_{SRH}$  Shotkley-Read-Hall carrier recombination rate, cm<sup>-3</sup>s<sup>-1</sup>

$R_{AUG}$  Auger recombination rate, cm<sup>-3</sup>s<sup>-1</sup>

$R_{SP\_ON}$  Specific on-resistance, mΩ.cm<sup>2</sup>

$R_{th-jc}$  Junction-to-case thermal resistance,  $\Omega$

T Absolute temperature, K

$V_{br}$  Breakdown voltage, V

$V_{d1}$  and  $V_{d2}$  Depletion layer voltages, V

$V_N^-$  - N Drift region voltage drop, V

$V_{i0}$ ,  $V_{i1}$ , and  $V_{i2}$  Voltage drop at junctions  $J_0$ ,  $J_1$  and  $J_2$ , V

$v_{sat}$  Saturation velocity, cm s<sup>-1</sup>

$V_{seg}$  Voltage drop of a segment, V

$V_T$  Thermal voltage, V

$W_1$ ;  $W_2$ ; W Widths of the depletion region on the  $N^-$  and P sides of the

junction and total depletion layer, cm

$W_{d1}$  and  $W_{d2}$  Depletion widths, cm

$W_I$  Intrinsic layer width, cm

$W_{min}$  Minimum width of the depletion layer of N-base, cm

$x_1$  and  $x_2$  Boundary positions of the carrier storage region, cm

$\alpha_{i}$ , and  $\alpha_{eff}$  General ionization coefficient, effective ionization coefficient, cm<sup>-1</sup>

$\beta$  Common-emitter gain

$\mathcal{E}$  Electric field strength, V/cm

$\mathcal{E}_C$  Critical electric field strength, V/cm

$\varepsilon$  Material permittivity, Fcm<sup>-1</sup>

λ Thermal conductivity, W/cm.K

$\mu_n$ , and  $\mu_p$  Electron and hole mobilities, (cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>)

$au_n, au_p$ , and  $au_{HL}$  Electron, hole and high-level injection lifetimes, s

$\tau_N^-$  Electron lifetime in  $N^-$  region, cm<sup>2</sup>s<sup>-1</sup>

$\psi$  Potential, V

AC Alternating current

ADE Ambipolar diffusion equation

BJT Bipolar junction transistor

C Carbon

CS Carrier storage

CSR Carrier storage region

CTE Coefficient of thermal expansion

DC Direct current

GaN Gallium nitride

Ge Germanium

GTO Gate turn-off thyristor

ICM Integral charge control model

IGBT Insulated gate bipolar transistor

IGCT Integrated gate-commutated thyristor

JFET Junction field-effect transistors

MCT MOS-controlled thyristors

MOS Metal-oxide-semiconductor

MOSFET Metal-oxide-semiconductor field-effect transistor

MTO MOS turn-off thyristor

NO Nitric oxide

NPT Non-punch-through

PT Punch-through

RC Resistor-capacitor

SCR Silicon controlled rectifier

Si Silicon

SiC Silicon carbide

SiO<sub>2</sub> Silicon dioxide

SRH Shockley-Read-Hall

VJFET Vertical junction gate field-effect transistors

## TABLE OF CONTENTS

| ACKNOWLEDGEMENT                               | iv |

|-----------------------------------------------|----|

| NOMENCLATURE                                  | vi |

| Chapter 1 – Background                        | 1  |

| 1.1 Background of Power Semiconductor Devices | 1  |

| 1.2 Lightly Doped Drift Region Thickness      | 13 |

| 1.3 Overview of Models                        | 17 |

| 1.3.1 Level 0 Model                           | 18 |

| 1.3.2 Level 1 Model                           | 18 |

| 1.3.3 Level 2 Model                           | 19 |

| 1.3.4 Level 3 Model                           | 20 |

| 1.3.5 Level 4 Model                           | 20 |

| 1.3.6 Level 5 Model                           | 21 |

| 1.4 Power BJT Models                          | 21 |

| Chapter 2 – Silicon Carbide Material          | 24 |

| 2.1 Introduction                              | 24 |

| 2.2 History of Silicon Carbide                | 24 |

| 2.3 Silicon Carbide Polytypes                 | 26 |

| 2.3.1 Silicon Carbide Physical Properties     | 28 |

|                                                             | xiv |

|-------------------------------------------------------------|-----|

| 5.5 Realization of a Power SiC BJT Model in Simulink        | 91  |

| 5.6 Simulation Results of the Switching Losses of a SiC BJT | 98  |

| 5.7 Measurement and Simulation Results of SiC BJT           | 103 |

| 5.8 Validation of the SiC BJT Model                         | 105 |

| Conclusions                                                 | 109 |

| Appendix                                                    | 129 |

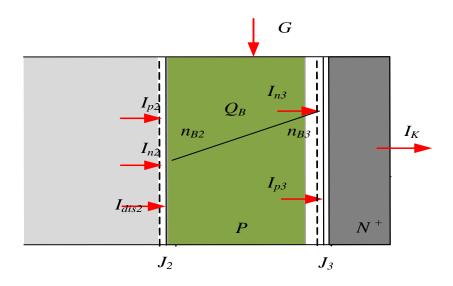

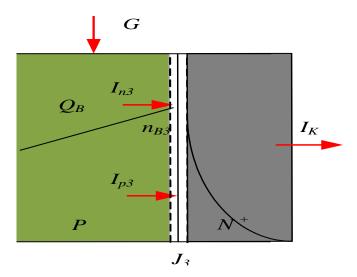

| 1. Modeling of a power SiC GTO                              | 129 |

| P <sup>+</sup> emitter region                               | 129 |

| N Buffer Layer                                              | 130 |

| N - Drift Region                                            | 133 |

| P Base Region                                               | 137 |

| N <sup>+</sup> Emitter Region                               | 138 |

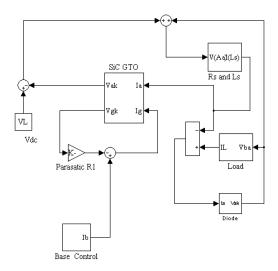

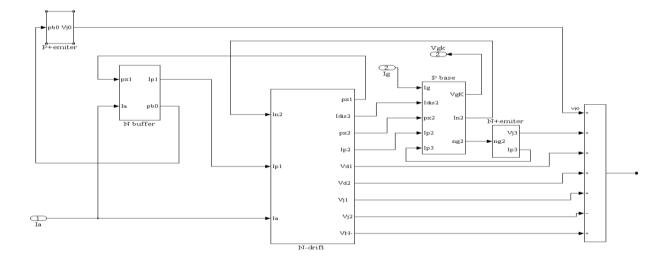

| Realization of Power GTO Model in Simulink                  | 140 |

#### LIST OF FIGURES

| Figure 1.1. Most of the important power semiconductor devices on the market (8) (along                       |

|--------------------------------------------------------------------------------------------------------------|

| with SiC power devices) have been developed and studied in various semiconductor                             |

| laboratories in recent years                                                                                 |

| Figure 2.1. The tetragonal bonding of a carbon atom with the four nearest silicon                            |

| neighbors (111)                                                                                              |

| Figure 2.2. Illustration of common SiC polytypes 3C, 4H, and 6H (112)27                                      |

| Figure 2.3. Band structure of 4H-SiC (120)                                                                   |

| Figure 2.4. Theoretical, specific on-state resistance of the blocking regions in function of                 |

| the breakdown voltages for Si and 4H-SiC (122)                                                               |

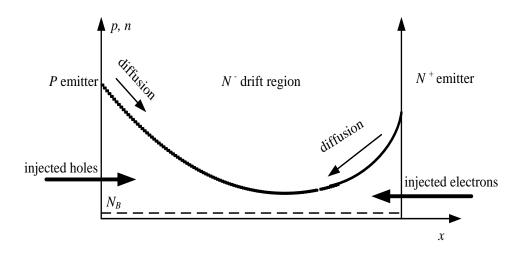

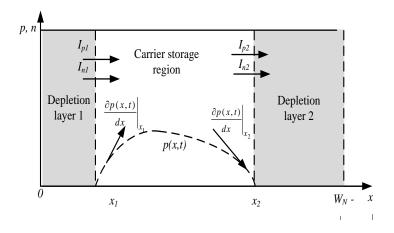

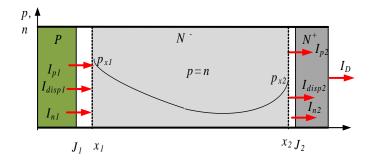

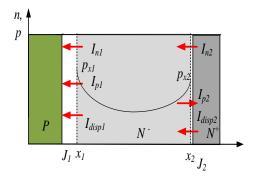

| Figure 3.1. Typical carrier distribution in the $N$ <sup>-</sup> - drift region during high level injection. |

|                                                                                                              |

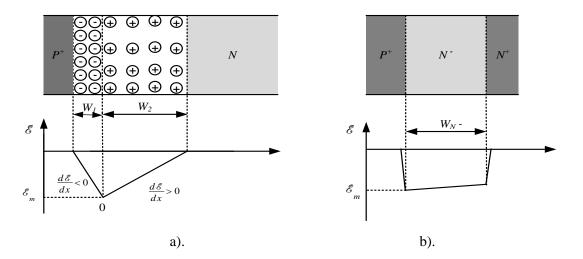

| Figure 3.2. The electrical field within: a) $P^+N$ structure; b) $P^+N^-N^+$ structure 42                    |

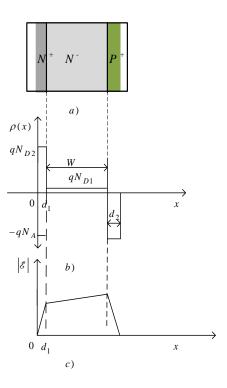

| Figure 4.1. The general arrangement of the carrier storage region and depletion layers in                    |

| the lightly doped $N^-$ - drift region. 47                                                                   |

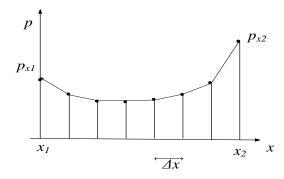

| Figure 4.2. The carrier distribution in CSR during the on-state                                              |

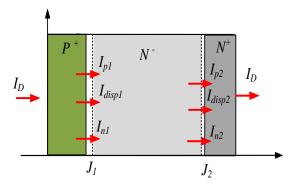

| Figure 4.3. Schematic structure of a $P^+N^-N^+$ power diode                                                 |

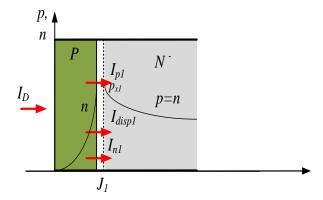

| Figure 4.4. Schematic structure of the $P^+$ emitter region of a power diode during                          |

| the on-state.                                                                                                |

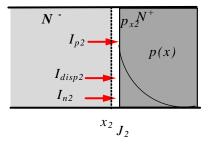

| Figure 4.5. Schematic structure and carrier concentrations of lightly doped drift region of                  |

| a power diode during the on state                                                                            |

| Figure 4.6. Schematic structure of the $N^+$ emitter region of a power diode during the on               |

|----------------------------------------------------------------------------------------------------------|

| state                                                                                                    |

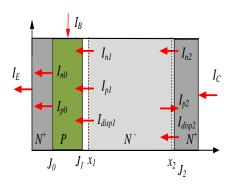

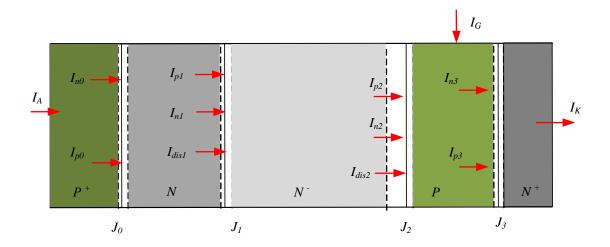

| Figure 4.7. One-dimensional cross-section used for modeling the power BJT showing the                    |

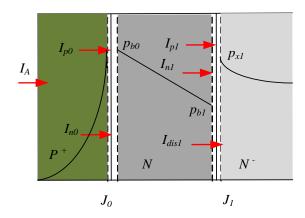

| hole and electron currents in each region. 62                                                            |

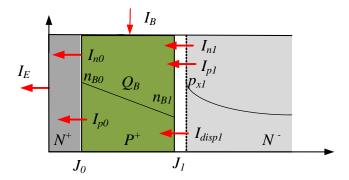

| Figure 4.8. Charge distribution and boundary current components in <i>P</i> base                         |

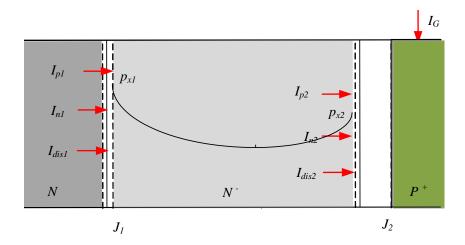

| Figure 4.9. Charge distribution and boundary current components in $N$ - collector 66                    |

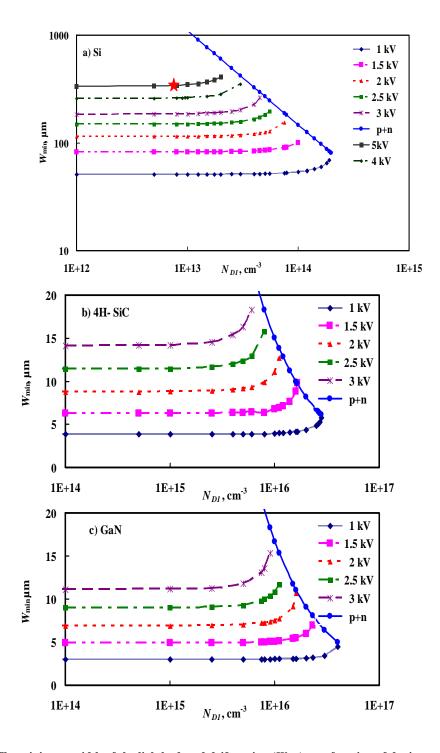

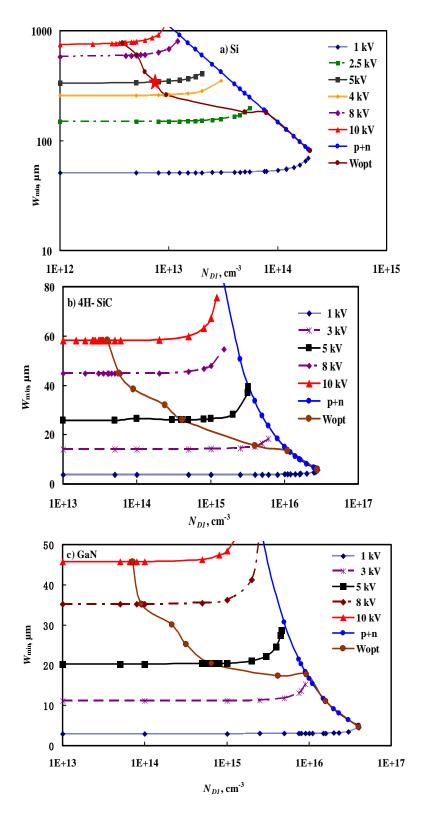

| Figure 5.1 The minimum width of the lightly doped drift region $(W_{min})$ as a function of              |

| doping concentration $(N_{DI})$ for a $P$ $^+N$ diode and a $P$ $^+N$ $^-N$ $^+$ structure for different |

| applied voltages and different semiconductor materials a) Si, b) 4H-SiC and c) GaN 73                    |

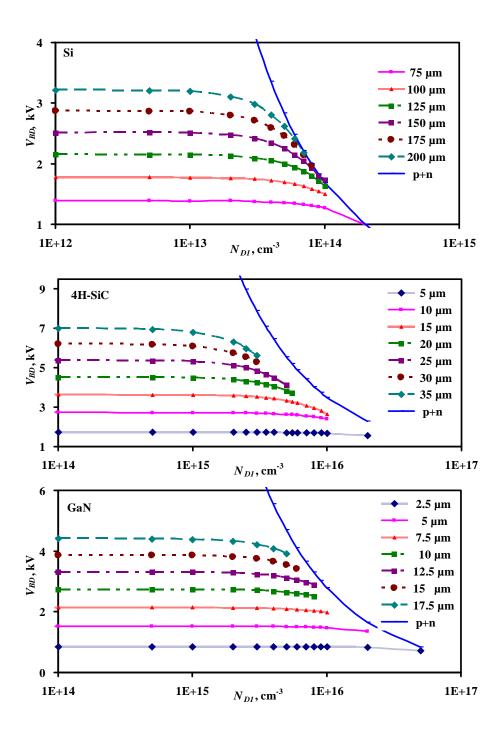

| Figure 5.2. The breakdown voltage as a function of doping concentration $(N_{Dl})$ for a $P^+N_{Dl}$     |

| diode and a $P^+N^-N^+$ structure for different $N^-$ base widths and different semiconductor            |

| materials: a)Si, b)4H-SiC and c)GaN                                                                      |

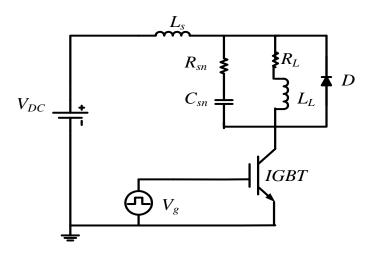

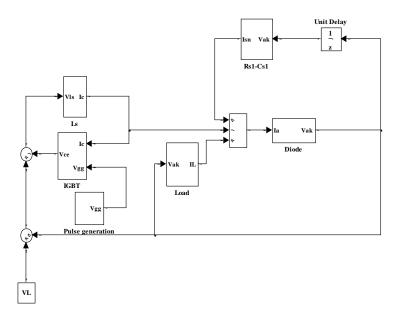

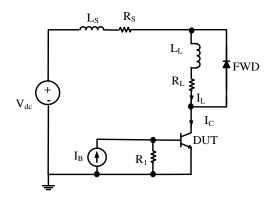

| Figure 5.3. IGBT under an inductive load switching with free-wheeling diode, D 78                        |

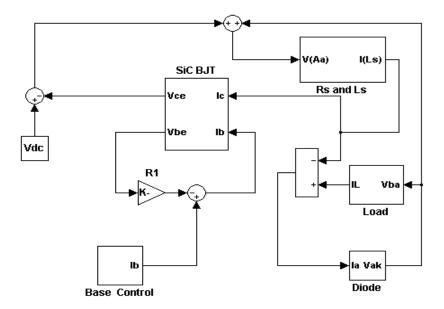

| Figure 5.4. The electrical circuit (Figure 5.3) of the IGBT under clamped inductive                      |

| switching realized in the Matlab/Simulink environment                                                    |

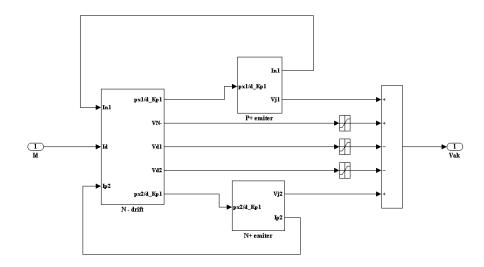

| Figure 5.5. Diode subsystem implemented on Simulink                                                      |

| Figure 5.6. Diode subsystem implemented on Simulink                                                      |

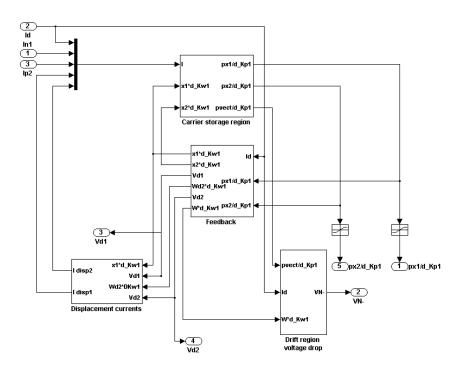

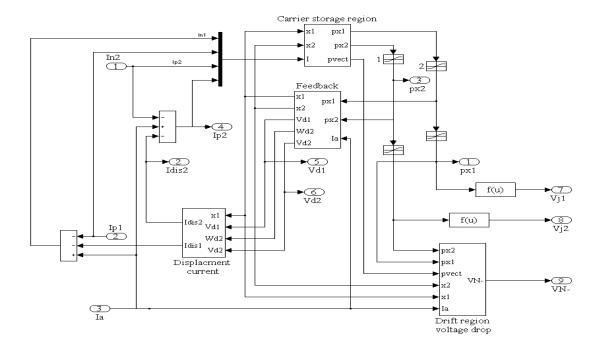

| Figure 5.7. Carrier storage subsystem                                                                    |

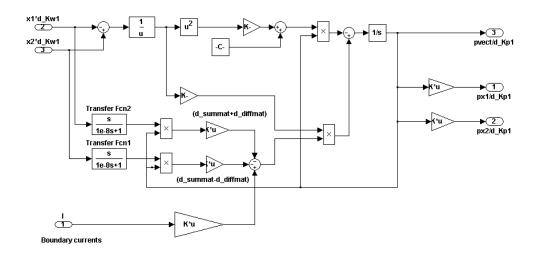

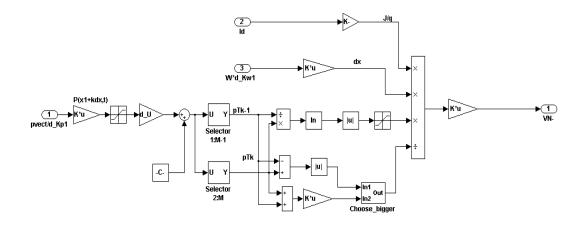

| Figure 5.8. Drift region voltage drop subsystem                                                          |

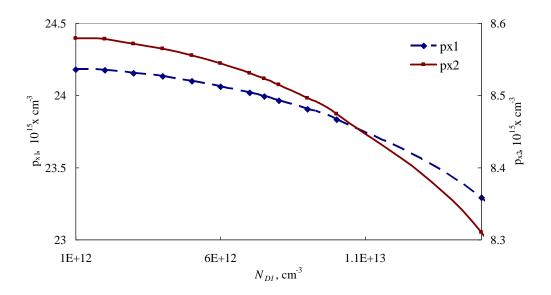

| Figure 5.9. The boundary carrier densities, $p_{x1}$ and $p_{x2}$ , of the lightly doped drift region as |

| a function of the doping concentration, $N_{D1}$ , for a 5 kV $P^+N^-N^+$ structure during the on-       |

| state                                                                                                    |

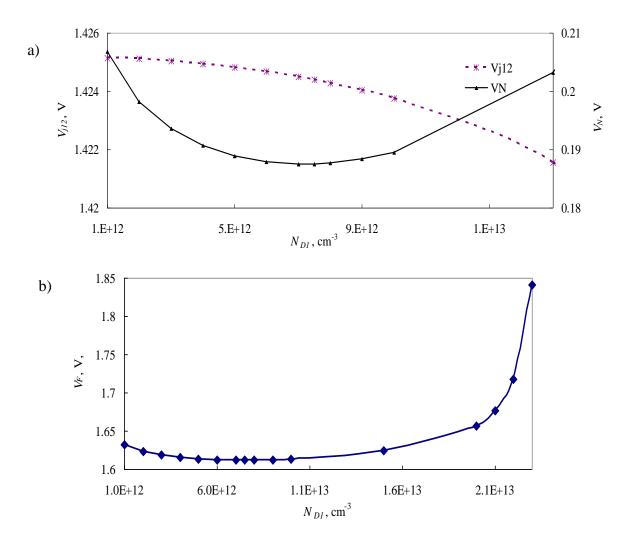

| Figure 5.10. The simulation results of a Si $P^+N^-N^+$ structure for a designed breakdown                     |

|----------------------------------------------------------------------------------------------------------------|

| voltage of 5 kV: a) the total junction voltage and the voltage drop across the $N^-$ drift                     |

| region as a function of the doping concentration of the lightly doped drift region; b) the                     |

| total forward voltage drop as a function of the doping concentration                                           |

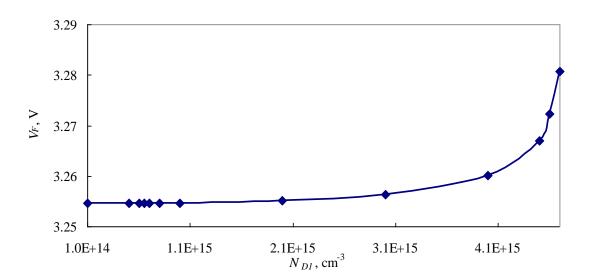

| Figure 5.11. The simulation results for the total forward voltage drop as a function of the                    |

| doping concentration of a GaN $P^+N^-N^+$ structure for a designed breakdown voltage of 5                      |

| kV                                                                                                             |

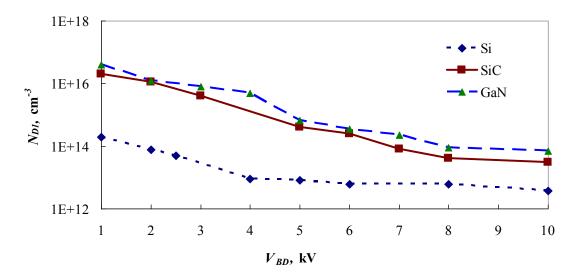

| Figure 5.12. The optimized doping concentration of the lightly doped drift region as a                         |

| function of the designed breakdown voltage that results in a minimum forward voltage                           |

| drop                                                                                                           |

| Figure 5.13. Simulated results of the minimum base width of the lightly doped drift                            |

| region $(W_{\min})$ as a function of doping concentration $(N_{DI})$ for a $P^+N$ diode and a $P^+N^-N$        |

| $^+$ structure and the optimum width $(W_{ m opt})$ of a $P$ $^+N$ $^-N$ $^+$ structure for different designed |

| breakdown voltages that minimize the forward voltage drop in different semiconductor                           |

| materials: a) Si, b) 4H-SiC, and c) GaN                                                                        |

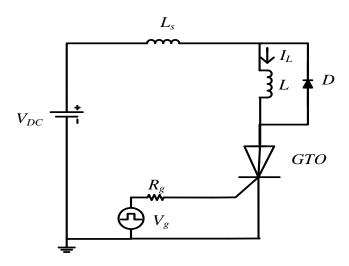

| Figure 5.14. Schematic of switching test circuit used for experiments and simulation 92                        |

| Figure 5.15. The switching test circuit used for experiments of a SiC BJT (Figure 5.14)                        |

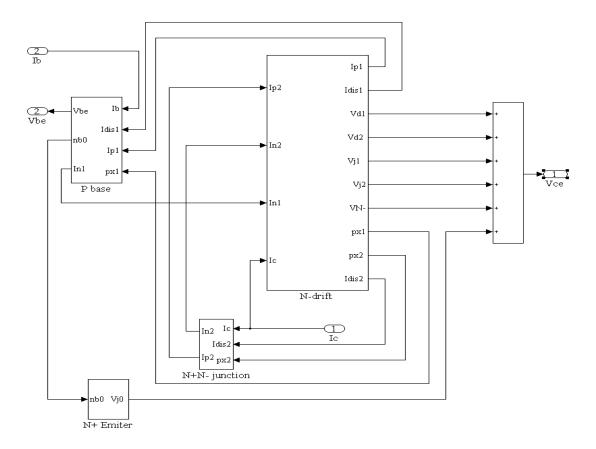

| implemented on Simulink. 94                                                                                    |

| Figure 5.16. SiC BJT subsystem implemented on Simulink                                                         |

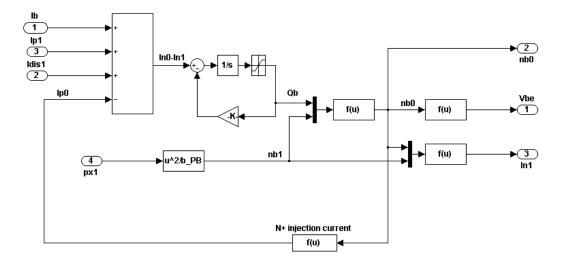

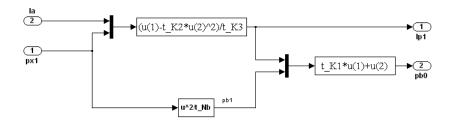

| Figure 5.17. <i>P</i> - base subsystem implemented on Simulink                                                 |

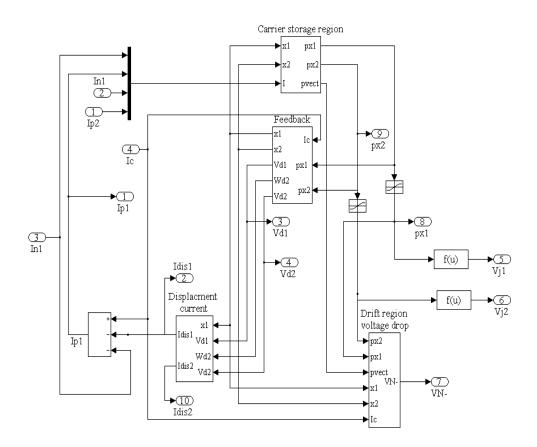

| Figure 5.18. $N^-$ drift region subsystem of the SiC BJT model                                                 |

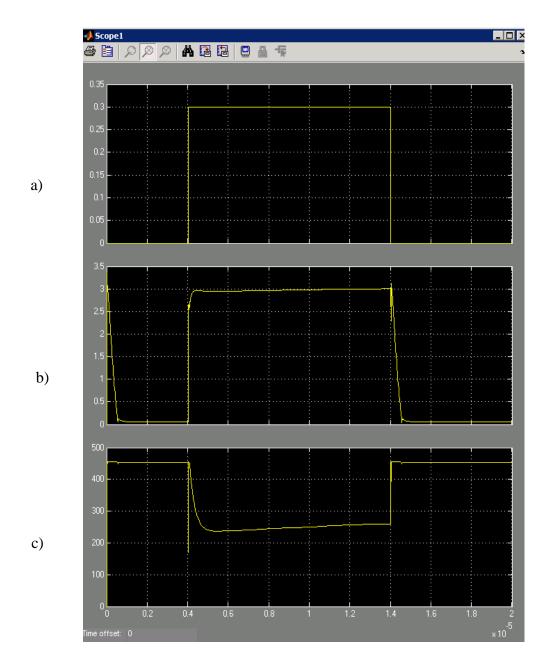

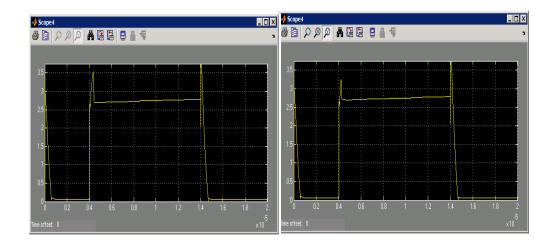

| Figure 5.19. Simulation results of a SiC BJT: a) base current, $I_B$ ; b) collector current, $I_C$ ;           |

| c) collector emitter voltage $V_{CE}$ 100                                                                      |

| Figure 5.20. Simulation results of the collector current of a BJT for different minority         |

|--------------------------------------------------------------------------------------------------|

| carrier lifetimes: a) $0.2~\mu s;$ b) $0.1~\mu s.$ 101                                           |

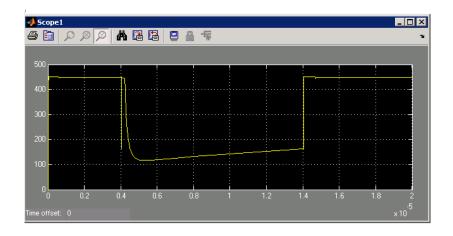

| Figure 5.21. Simulation results of the depletion regions voltage $V_{dI}$                        |

| Figure 5.22. Simulation results of the collector emitter voltage, $V_{CE}$                       |

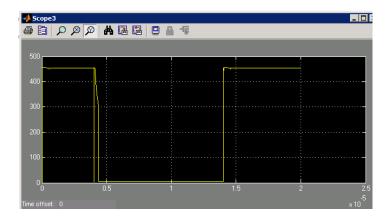

| Figure 5.23. Common emitter I-V curve of SiC BJT at room temperature: a) $V_{CE} = 0.2$          |

| V; b) $V_{CE} = 0-10$ V                                                                          |

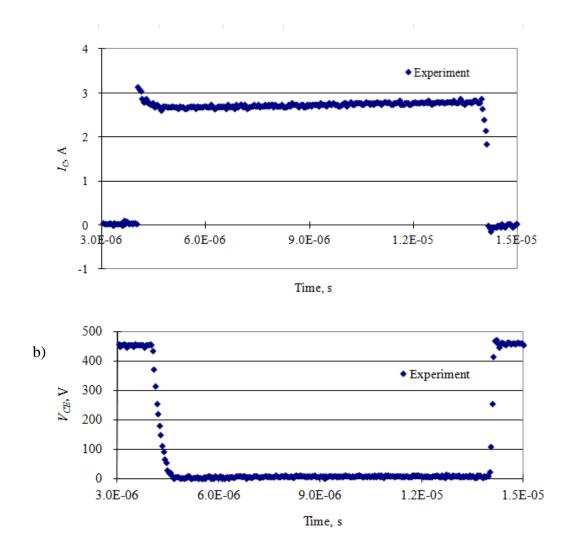

| Figure 5.24. Measurement results of a SiC BJT: a) collector current $I_C$ ; b) collector         |

| emitter voltage $V_{CE}$                                                                         |

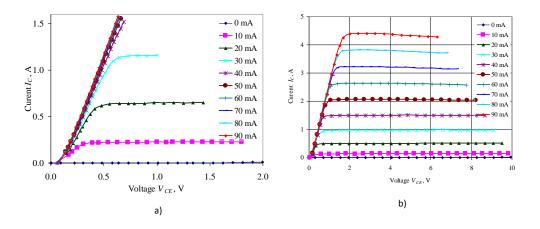

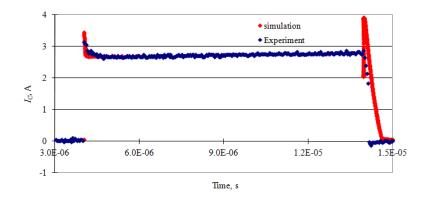

| Figure 5.25. Experimental and simulation results of collector current $I_C$ of SiC BJT           |

| during the inductive switching tests                                                             |

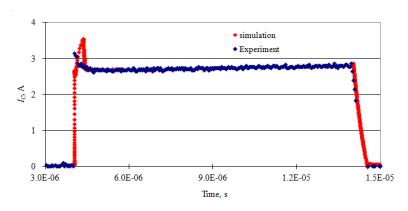

| Figure 5.26. Experimental and simulation results of collector current, $I_C$ , of SiC BJT        |

| during the inductive switching tests after removing the disturbance during turn-off 106          |

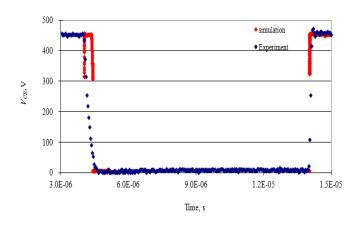

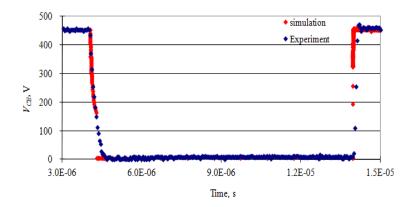

| Figure 5.27. Experimental and simulation results of collector emitter voltage, $V_{CE}$ , of SiC |

| BJT during the inductive switching tests                                                         |

| Figure 5.28. Experimental and simulation results of the collector emitter voltage, $V_{CE}$ , of |

| SiC BJT during the inductive switching tests removing the disturbance during turn-off.           |

|                                                                                                  |

## LIST OF TABLES

| Table 1.1. Parameters of SiC BJTs developed in the past few years     | 7  |

|-----------------------------------------------------------------------|----|

| Table 1.2. Parameters of SiC MOSFETSs developed in the past few years | 9  |

| Table 2.1. Physical properties for various semiconductors.            | 28 |

| Table 5.1 Average ionization coefficients.                            | 71 |

| Table 5.2 Simulation parameters.                                      | 78 |

| Table 5.3 Circuit parameters for simulations                          | 78 |

| Table 5.4. BJT parameters.                                            | 92 |

| Table 5.5. Circuit parameters for experiments and simulation          | 92 |

# **Chapter 1 – Background**

## 1.1 Background of Power Semiconductor Devices

Power semiconductor devices are key components of power electronics technology, used primarily as switches or rectifiers in circuits and systems. Currently, more than 70% of all electrical energy consumed is processed by power electronics. The main function of power electronics is to control and transfer the flow of electrical energy from one form to another and in a form that is suitable to the user. Semiconductor devices are widespread and can be found in almost every electrical and electronic device. Their power range depends on the application and can be from milliwatts to megawatts. Power devices have a significant impact on the economy as they determine system cost and efficiency.

The invention of the bipolar junction transistor in 1947 by Shockley, Bardeen, and Brattain (1), (2) was the beginning of semiconductor electronics and allowed direct solid-state control of electricity for the first time. However, the application of transistors for controlling electrical power was limited until the invention of the thyristor in 1957 (3). Although the thyristor has limited switching capability, it cannot be turned off by external control. Thyristors have been used for the design of different applications, such as control of DC motors. The first power bipolar junction transistor (BJT) with substantial power handling capabilities was introduced in the 1960s. The device overcame some of the limitations of the thyristor, because it can be switched on or off by applying an external signal.

Further developments of the thyristor led to the realization of a fully controllable switching device, a thyristor that can be turned off using a gate (GTO) (4). This enables the GTO to be used in more complex power conversion technology capable of controlling power more directly and efficiently. This significant development greatly enhanced power electronics technology.

The metal-oxide-silicon field-effect transistor (MOSFET) was the next major device introduced in the 1970s (5). It has minimal drive requirements due to its insulated gate. Also, the MOSFET is a voltage-controllable device having high input impedance and fast switching response. MOSFETs are unipolar majority carrier devices which gives them a faster switching speed than the BJT or thyristor. On the other hand, the power handling capabilities of the MOSFET are lower compared to the thyristor because of high on-state resistance associated with high blocking voltage.

In the early 1980s, a new process technology was developed allowing MOSFET and BJT technology to be integrated on the same chip (6), (7). A new device, the insulated gate bipolar transistor (IGBT), was introduced. IGBTs possess the advantages of both devices: faster switching (inherited from MOSFET) and lower specific on-state resistance (from the *PNP* BJT). Improvements in design and technology have made IGBTs popular replacements for BJTs and low to medium power thyristor technology. The IGBT is presently the dominating semiconductor device for most medium power applications.

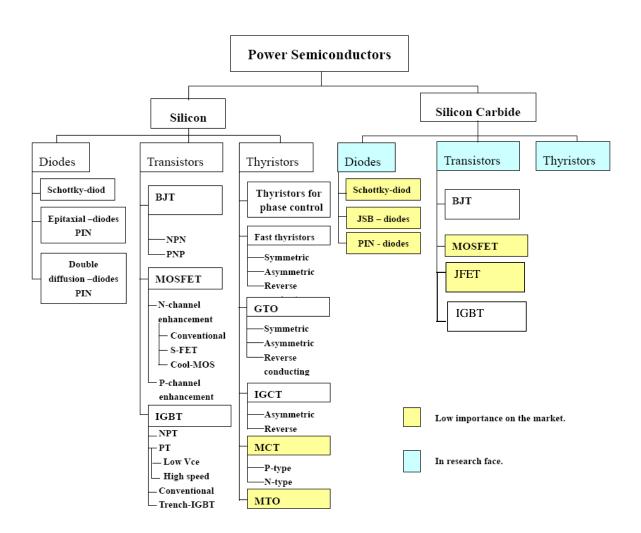

Figure 1.1 summarizes the most important power semiconductor devices on the market (8) along with silicon carbide (SiC) power devices that have been developed and studied in recent years in various semiconductor laboratories. Due to poorly established technology for production of large area wafers without defects for SiC, silicon (Si) is still the most used element for production of power semiconductor devices.

Figure 1.1. Most of the important power semiconductor devices on the market (8) (along with SiC power devices) have been developed and studied in various semiconductor laboratories in recent years.

The devices can be classified as diodes, transistors, and thyristors based on their structure. Schottky diodes are typically used for high switching frequencies at low voltage,  $BV \le 100$  V, the fast switching epitaxial PIN diodes are used for  $BV \le 600$  -1200 V, and double diffused PIN diodes are applied at higher voltages  $BV \ge 1000$  V.

BJTs have been completely replaced by MOSFETs and IGBTs. By introducing an extra P doping region in the MOSFET drift region, a high breakdown voltage can be achieved with much higher drift doping, which results in a drastic reduction (5-10 times) in specific on-resistance for the same chip area in a voltage range of BV = 600-1000 V.

Large-area Si devices capable of handling thousands of amperes and kilovolts are now available on the market. MOS gate devices, such as IGBTs, are designed using two different structures: punch-through (PT) and non-punch-through (NPT). Both types of IGBTs can handle voltage up to 3.3 kV and current up to 1.2 kA (9). IGBT modules for 6.5 kV and 0.6 kA are also available.

Si GTOs and thyristors are still widely used for very high power applications. FMCC Group is currently selling asymmetric GTO thyristors for 4.5 kV and 26 kA (10). The devices are optimized for low conduction losses, and the switching frequency is in the range of 200-500 Hz for most applications. All GTOs require the use of snubbers for protection during turn-on and turn-off switching. Significant improvement to the GTO structure, including a gate driver, an integrated inverse diode, and better packaging, resulted in a new semiconductor device, the integrated gate-commutated thyristor

(IGCT). The IGCTs have much faster turn-off times compared to GTOs. This allows them to operate at higher frequencies - up to several kHz - for very short periods of time. However, the typical IGCT operating frequency is up to 500 Hz because of high switching losses at higher frequencies. Asymmetric IGCTs, optimized for snubberless turn-off, can operate at 6.5 kV and 4.2 kA. MOS-controlled thyristors (MCTs) and MOS turn-off thyristors (MTOs) have been proposed, but the market demand for these devices is very low at this time (8).

The need for high-voltage, high power density devices operating at high frequencies and junction temperatures higher than 150 °C is growing, especially for advanced power electronics. Silicon-based devices are not able to meet these requirements without connecting, in series and in parallel, to a large number of devices using costly active or passive snubbers and expensive cooling systems (11). For this reason, the limitations of Si material properties for power devices are currently being debated; and wide band gap semiconductors, such as SiC and gallium nitride (GaN), have attracted considerable attention.

Significant research into SiC as a material for semiconductor devices has been carried out during the last 20 years. The wide and indirect band gap enables the devices to operate at elevated temperatures (600 °C), and they still have low leakage current. The higher breakdown strength for a given blocking voltage of SiC results in ten times smaller drift layers as compared to Si. This reduces the storage of the minority carriers and the associated switching losses at a given switching frequency. Also, the switching frequency can be increased to 50-100 kHz with acceptable switching losses, which will significantly reduce the size of the magnetic components in power electronic systems.

Regardless of the advantages that SiC possesses, it has not been adopted for manufacturing of the entire range high-power devices. Difficulty with SiC crystal growth, the presence of crystal defects, such as micropipes and dislocations, and absence of abundant wafer suppliers have all contributed to a lack of progress in the fabrication of SiC power devices by the commercial sector (12). Several industrial research groups and universities have been working on the development of SiC power devices and on improving the material properties. In September 2001, two companies advertised the commercial availability of SiC Schottky diodes: Infineon (600 V up to 6 A or 300 V up to 10 A) and Microsemi (100-200-480 V, 1A) (13).

In 2001, a high-voltage PIN diode in SiC capable of blocking over 19 kV was reported (14). The diode has a forward voltage drop of 6.5 V at 100 A/cm<sup>2</sup>. Also in 2002, the design, fabrication, and high temperature characteristics of 4H-SiC PIN rectifiers with 5, 6, and 10 kV blocking voltage were reported (15). For the 10 kV rectifier, a forward voltage drop of less than 4.8 V was observed at 100 A/cm<sup>2</sup> in the entire 25 to 200 °C temperature range. It has also been reported in the literature that Schottky and PIN SiC diodes have significantly less reverse current compared to the conventional fast or ultrafast Si diode (16). Now, Cree Inc. is announcing the world's first commercially available 1700 V and 10 A and 25 A silicon carbide Schottky diodes (17).

Power BJTs in SiC are very attractive for power switching applications due to their very low specific on-resistance and high-temperature operation with high power densities (18). The common emitter gain,  $\beta$ , the specific on-resistance,  $R_{SP\_ON}$ , and the open-base breakdown voltage,  $BV_{CEO}$ , are important parameters that should be accounted for in the optimization of SiC BJTs (19). Different SiC BJTs developed in the last several years are

listed in Table 1.1. Considerable work has been done to improve device performance. One of the main challenges is to increase the low current gain, because BJTs are driven by base currents (20). The current gain of 4H-SiC BJTs is limited by the surface recombination (21). Reducing the surface recombination current by optimizing the surface passivation improves the current gain (22). Also, the common emitter current gain can be improved by increasing the minority carrier lifetime in the base and emitter regions (23). The maximum current gain for high-voltage SiC BJTs that has been reported in the literature is 110 (24).

Table 1.1. Parameters of SiC BJTs developed in the past few years.

|      | $R_{SP\_ON}$ , | $BV_{CEO}$ ,kV |           |

|------|----------------|----------------|-----------|

| β    | $m\Omega.cm^2$ |                | Reference |

| 3    | 28.3           | 6              | (25)      |

| 18.8 | 2.9            | 0.757          | (26)      |

| 20   | 10.8           | 1.8            | (27)      |

| 20   | 28             | >3.2           | (28)      |

| 24.8 | 8.4            | 1.75           | (29)      |

| 31   | 11.2           | 1.3            | (30)      |

| 32   | 17             | >1             | (19)      |

| 38   | 14             | 0.48           | (31)      |

| 42   | 9              | 1.75           | (32)      |

| 44   | 8.1            | 3.2            | (33)      |

| 44.3 | 8.7            | 5.5            | (34)      |

| 60   | 5.2            | 1.2            | (20)      |

| 110  | 3.7            | 0.27           | (24)      |

To increase the blocking voltage, the growth of high-purity SiC homoepitaxial thin films on SiC single crystal wafers is required to form  $NN^+$  wafer structures (35). The maximum open base breakdown voltage,  $BV_{CEO}$ , for SiC BJT was reported to be 6 kV (25). From the data presented in Table 1.1, it can be seen that the BJT having the highest current gain has the smallest open breakdown voltage and vice versa. Further work is

necessary to improve the design and to develop a new processing technology so that an increase in  $BV_{CEO}$  can be achieved without sacrificing the current gain of the transistor.

For Si power MOSFETs (breakdown voltage higher than 200 V), the on-resistance becomes dominated by the drift region resistance leading to an increase in the on-state voltage drop and conducting losses. Novel Si structures have allowed the breakdown voltage to extend to 600 V, but the specific on-resistance is still reasonably large which limits high frequency operation. Theoretically, the much lower drift region resistance in SiC would allow development of power MOSFETs with high breakdown voltages and smaller switching and conducting losses.

Since the introduction of the first SiC power double MOSFET (DMOSFET) in 1996 (36), different devices have been designed, characterized, and studied to improve their performances. In **Error! Reference source not found.** are presented some SiC MOSFETs developed since then. Over this period, blocking voltages have increased from 0.76 to 14 kV. For a long period of time, the power MOSFET structures developed in Si could not be directly employed for SiC devices due to the following reasons.

The first reason is that in low voltage devices, the on-resistance is caused by the low mobility of inversion electrons at the SiO<sub>2</sub>/4H-SiC interface. Electrical quality of the interface can be improved dramatically by post-oxidation annealing in nitric oxide (NO) which leads to an increase in inversion layer electron mobility and a corresponding reduction in channel resistivity (37). Also, the introduction of a self-aligned process reduces the channel resistance; and therefore, the specific on-resistance of a well-fabricated power device is no longer limited by the channel resistance (38).

The second reason is that a high electric field occurring in the isolator (silicon dioxide (SiO<sub>2</sub>) of a silicon carbide MOSFET can cause the device to fail during the blocking mode. The problem is aggravated at the trench corners leading to rupture of the gate oxide at higher drain voltages (39), thus restricting the maximum operating voltage. It can be solved by using a buried  $P^+$  layer to shield the channel region (40). As a result, the electrical field in the gate oxide will reduce, increasing the reliability of the SiC MOSFETs.

Table 1.2. Parameters of SiC MOSFETSs developed in the past few years.

| BV,<br>kV | $R_{SP\_ON}$ , m $\Omega$ .cm <sup>2</sup> | Reference |

|-----------|--------------------------------------------|-----------|

|           |                                            |           |

| 0.76      | 66                                         | (36)      |

| 0.95      | 220                                        | (41)      |

| 0.95      | 8.7                                        | (42)      |

| 1         | 6.95                                       | (43)      |

| 1.1       | 74@100 °C                                  | (44)      |

| 1.3       | 7                                          | (45)      |

| 1.4       | 313                                        | (46)      |

| 1.6       | 27                                         | (47)      |

| 1.8       | 8                                          | (48)      |

| 2         | 10.3                                       | (49)      |

| 2.6       | 200                                        | (50)      |

| 3.06      | 121                                        | (51)      |

| 3.36      | 199                                        | (51)      |

| 10        | 236                                        | (52)      |

| 10        | 133                                        | (53)      |

| 10        | 123                                        | (54)      |

| 10        | 111                                        | (55)      |

| 14        | 228                                        | (56)      |

The third reason is that the injection of electrons into the oxide can take place when the electrons in the semiconductor gain sufficient energy to surmount the potential barrier between the SiC and SiO<sub>2</sub>. This can cause shifting of the threshold voltage of the MOSFET leading to reliability problems.

To make further progress in the design of MOSFETs, all limiting factors should be addressed simultaneously, especially the quality of the oxide-semiconductor interface which must be improved to allow good control over the channel mobility and threshold voltage. Despite the problems mention above, a new12 kV SiC MOSFET was ready for production and presented by Cree Inc. at the ECCE 2011 Phoenix conference.

Other unipolar power switching devices, junction gate field-effect transistors (JFETs), have also been intensively investigated. They are free of gate oxide reliability issues and are the most promising candidates for high-temperature operation since only pn-junctions are involved in the active device structure. The SiC power JFETs are still the most mature SiC devices that are close to commercialization and available as restricted samples (57). In October 2009, SemiSouth Laboratories in Starkville, MS, USA, which designs and manufactures SiC-based discrete electronic power devices, claimed the first SiC JFET (normally-off, 1.2 kV, 100 m-Ohm) used in the audio amplifier market for a new audiophile-quality power amplifier (58).

Some JFETs with high blocking voltage and low specific on-resistance reported by different research groups in the last few years are: a vertical JFET (VJFET) with a blocking voltage of 3.5 kV and less than 30 m $\Omega$ -cm<sup>2</sup> on-resistance (59); a VJFET with a blocking voltage of 4 kV and 45 m $\Omega$ -cm<sup>2</sup> on-resistance (60); a static expansion channel JFET, a normally off type with 5.3 kV blocking voltage and 69 m $\Omega$ -cm<sup>2</sup> specific on-

resistance (61); and a normally off 11.1 kV TI-VJFET (trenched-and-implanted vertical JFET) with 124 m $\Omega$ -cm<sup>2</sup> specific on-resistance (62).

One disadvantage of JFETs is that they are normally-on devices which require a negative gate voltage to be turned off. Using a cascode device comprised of a SiC JFET and a series-connected, low-voltage Si MOSFET will result in a normally-off device having a behavior very similar to a conventional MOSFET (63). The first cascode based on a SiC VJFET was reported with a blocking voltage of 4.5 kV and an on-resistance of 1.2  $\Omega$  (64). Although using a cascode makes a JFET operate as a normally-off device, there are several limitations. The maximum operating temperature of the cascode is limited by the Si MOSFET. The conduction losses increase, because the two devices are connected in series, which should be taken into consideration during the design of a power application.

As was mentioned, the rapid improvement in 4H- SiC material quality and maturing of SiC device processing have enabled the development of high-voltage SiC power devices (MOSFETs and JFETs) in recent years. However, the on-resistance of SiC MOSFETs and JFETs rapidly increases as the blocking voltage and operating junction temperature increase. This makes the conduction loss of the unipolar devices unacceptable for applications with a blocking voltage higher than 10 kV. For these applications, bipolar devices are preferred, because they have shown a small voltage drop at elevated temperatures due to strong conductivity modulation in their drift region (65).

Simple gate drive interfaces make 4H-SiC IGBTs attractive devices. Both *N*- and *P*-channel SiC IGBTs have been demonstrated with higher than 10 kV blocking voltage.

The first 10-kV P-IGBT on SiC was reported in 2005 (66). Since then, 12-kV P- channel IGBTs with 14 m $\Omega$ .cm<sup>2</sup> on-resistance (67), 13 kV N- channel IGBTs with 22 m $\Omega$ .cm<sup>2</sup> on-resistance (68), and 20 kV self-aligned P-channel DMOS-IGBTs have been reported (69). The 20 kV P- channel IGBT has a less than 15 times smaller voltage drop at 31 A/cm<sup>2</sup> current density compared to a theoretical MOSFET with the same blocking voltage (69).

A 4H-SiC thyristor is capable of higher current densities than an IGBT, because the physical mechanism for conductivity modulation is more effective in the thyristor compared to the IGBT. However, the thyristor requires more complex external circuitry as it is a current-controlled device. The first SiC symmetrical thyristors (700 V with a rated current of 6 A and a forward drop of 3.9 V) were demonstrated by Cree, Inc. (70). Since then, scientists from Cree have designed and fabricated different asymmetrical *NPNP* devices. The thyristors are made on  $N^+$  4H-SiC substrates, because  $P^+$  substrates have higher resistance compared to the  $N^+$ . The limitations of the epilayer thickness and device footprint have been the main obstacles to increasing the blocking voltage and the current passing through the devices.

Different scientific groups have worked on the design, fabrication, and characterization of SiC thyristors. Some of the parameters of thyristors reported in the last few years are: 1.77 kV blocking voltage with 4 V voltage drop at 100 A and 200 °C (71); 2.6 and 3.1 kV blocking voltage and 6.5 V voltage drop at 12 A (72); 7 kV blocking voltage with a voltage drop of 3.66 V at a current density of 300 A/cm<sup>2</sup> at room temperature and a forward voltage drop of 3.1 V at 300 A/cm<sup>2</sup> at 224 °C (73); 4.5-kV SiC *P*-type GTO prototype with forward voltage drop of 4.6 V at a current density of 25

A/cm<sup>2</sup> and a turn-off energy loss of 9.88 mJ (74); 4H-SiC 7.8 kV thyristors with a graded, etched junction termination extension with forward voltage drop of 3.9 V at a current density of 100 A/cm<sup>2</sup> and specific on-state resistance of 5.3 m $\Omega$ -cm<sup>2</sup> (75); and a 12.7 kV SiC commutated GTO with leakage current less than 1 x 10<sup>-3</sup>A/cm<sup>2</sup> at 9 kV and 250°C and onstate voltage drop at 100 A/cm<sup>2</sup> is 6.6 V (76).

From the literature review, it can be concluded that rapid progress (blocking voltage increasing, on-state voltage dropping, and leakage current decreasing) in the design, fabrication, and characterization of SiC power-switching devices has been made. Several SiC devices have demonstrated better performance compared to the existing comparable Si devices. SiC technology has not matured yet and has some limitations. The same limitations existed for Si when it was thought that it could replace germanium (Ge); and today, few remember the initial processing problems of Si. The SiC advantages lead many scientists to continue work on improving the quality of the material and device design. Power electronics based on SiC devices will bring a renaissance in power electronics in the future, particularly in the high power area.

# 1.2 Lightly Doped Drift Region Thickness

One of the requirements for choosing a proper power electronic device for a converter is that it must possess a low specific on-resistance. The specific on-resistance of a bipolar device is related to the width and doping concentration of the lightly doped drift region (N-base). This means that the doping concentration and the width of the low-doped base region in a bipolar device must be carefully considered to achieve a desired avalanche breakdown voltage and on-resistance (conduction characteristics).

The avalanche breakdown voltage,  $V_{BD}$ , for an abrupt parallel plate junction is a function of the background doping and the semiconductor properties, such as dielectric constant, energy band gap, and impact ionization coefficient. Breakdown occurs when the carrier multiplication becomes greater than unity. Impact ionization coefficients empirically describe the exponential relationship of the applied electric field and associated charge carrier creation. The impact ionization coefficients for electrons and holes have different values, and values for semiconductor materials of interest are obtained empirically. The general ionization coefficient has been determined to have a theoretical form that is exponential and represented by (77):

$$\alpha_i = A_i e^{-\left(\frac{b_i}{\mathcal{E}}\right)^{m_i}} \tag{1.1}$$

where  $\mathscr{E}$  is the electrical field (V/cm),  $A_i$  is the amplitude parameter (cm<sup>-1</sup>),  $b_i$  is the ionization energy parameter related to the mean free path between collisions (V/cm), and  $m_i$  is an additional fit parameter for use with a multitude of semiconductor materials (77) (78). These parameter values depend on the semiconductor material, and they are different for electrons or holes. For Si, 6H-SiC, and GaN,  $m_i$  has been determined to be 1 for both electrons and holes (77), (78).

Near the breakdown condition, a small error is introduced by equating the impact ionization coefficients of electrons and holes to an effective ionization coefficient,  $\alpha_{eff}$ . In this case, the breakdown voltage is defined as the applied voltage at which the summed effects described by the ionization coefficient acting over the depletion width, W, create more free charge carriers. The boundary at breakdown is when the integral (1.2) achieves

a value of unity (79). The associated breakdown condition in terms of the effective ionization coefficient is:

$$\int_{0}^{W} \alpha_{eff} dx = 1 \tag{1.2}$$

Evaluation of this integral using Equation (1.1) is very difficult; and no analytical expressions result, thus limiting its usefulness for device design. However, a simplified (and purely empirical) polynomial expression for the ionization coefficient in terms of the electric field is widely used (79):

$$\alpha_{eff} = K \mathcal{E}^7 \tag{1.3}$$

The two previous fit parameters,  $A_i$  and  $b_i$ , are absorbed into the prefactor, K. The coefficient, K, is expressed in terms of new parameters, A, b, and m, that are averages of the previous  $A_i$ ,  $b_i$ , and  $m_i$  values, expressed in Equation (1.1) for holes and electrons (78):

$$K = 9 \times 10^{-38} \frac{A216^m}{b^{0.85} E_G^{15}}$$

(1.4)

where  $E_G$  is the band gap energy (eV) for the semiconductor material of interest.

For a one-sided abrupt  $P^+$ -N junction, the electrical field and the voltage across the lightly doped region are functions of the depletion distance and depend on the impurity doping concentration,  $N_{D1}$ , in the lightly doped N-base and the depleted N-base width, W.

The electric field and voltage relations are presented in Equations (1.5) and (1.6), respectively.

$$\mathscr{E}(x) = \frac{q}{\varepsilon} N_{D1}(W - x) \tag{1.5}$$

$$V(x) = \frac{q}{2\varepsilon} N_{D1} (W - x)^2$$

(1.6)

The maximum electrical field is observed at junction (x = 0). Using this and substituting Equation (1.5) in Equation (1.3) and then substituting into the integral (1.2), one can obtain the minimum width of the depletion layer,  $W_{\min}$ , at breakdown (78).

$$W_{\min} = \left(\frac{K}{8} \frac{q^7}{\varepsilon^7} N_{D1}^7\right)^{-\frac{1}{8}} \tag{1.7}$$

The corresponding breakdown voltage can then be determined from Equation (1.6) as:

$$V_{BD} = \left(2K\frac{q^3}{\varepsilon^3}N_{D1}^{3}\right)^{-1/4}$$

(1.8)

It should be noted that the permittivity is correctly placed in the denominator in Equation (1.8), not in the numerator as was presented in the expressions from (78).

To reduce the lightly doped region width and maintain the same breakdown voltage requires the addition of a highly-doped  $N^+$  buffer layer at the end of the drift (N-base) region to create a  $P^+N^-N^+$  structure. This will modify the expressions for the minimum width of the depletion layer,  $W_{\min}$ , and the corresponding breakdown voltage,  $V_{\text{BD}}$ .

Reducing the width of the base region will decrease the effective on-resistance during conduction and reduce the volume of stored charge, thus decreasing the turn-off (and turn-on) time.

Anantharam and Bhat, 1980, calculated the breakdown voltage as a function of the thickness of the intrinsic layer,  $W_I$ , by solving the ionization integral. It was assumed that the PT voltage of the purely intrinsic region was equal to zero, and the breakdown voltage was given by (80):

$$BV = \frac{W_I^6}{A}. ag{1.9}$$

The first objective of this dissertation is to extend the concepts for the breakdown voltage of the PT diodes with abrupt junctions using the theory of the average ionization coefficient and investigate the modifications due to the PT structure.

#### 1.3 Overview of Models

The rapid developments in semiconductor technology over the past few years have led to a remarkable increase in interest in device modeling. It is necessary to understand the detailed operation of the devices and to optimize their design. This implies that device modeling now plays an essential role in modern technology. As the scale of the semiconductor devices decreases and the complexity of the physical structure increases, the modeling concepts become more complicated. Also, the difficulty connected with measuring some of the semiconductor device's parameters means that the results obtained from the theoretical characteristics must be highlighted. Modeling also allows new device structures to be accurately investigated prior to fabrication.

In (81) there are six proposed model levels that can be adapted for categorization of the device models in any circuit simulator or finite element (or finite difference) simulator. The categorization of the levels begins with simple behavioral models and then moves to more complex physics-based models. Different model levels have been developed using different programing languages. A brief review of these six model levels is presented below.

#### 1.3.1 Level 0 Model

The Level 0 model is a behavioral model that does not have a real physical representation. In other words, this model can be considered as an ideal electrical switch with two stages: no current flow, when the device is in blocking condition, and no forward voltage drop, when it is in conducting condition. In order to assist numerical convergence during the simulation, the commutation time may either be zero (instantaneous) or finite. Thermal or power loss data cannot be obtained with this model. For the model to work, some parameters, such as maximum forward or reverse blocking voltages and maximum forward current, and the current and voltage directions should be specified. The model allows fast, rough simulation and can be used in the early stages of the design process. One of the applications of the Level 0 model is for simulation of many switching cycles.

#### **1.3.2** Level 1 Model

A Level 1 model is a behavioral model, suitable for basic system-level modeling where the circuit methodologies are tested, validated, and compared. It models only the

basic properties of the devices: forward voltage drop as a function of forward current and temperature, and turn-on and turn-off switching losses as a function of current and voltage. This model does not calculate triggering losses. Breakdown voltage limits, maximum forward conduction-current limits, and maximum junction-temperature limits are imposed. The junction temperature of the device is estimated by the simple multisection resistor-capacitor (RC) equivalent network.

#### 1.3.3 Level 2 Model

Level 2 models predict the same basic physical properties and behavior as the switching characteristics of semiconductor devices. They are one dimensional and are a simplified physical-properties-based system. These models include all of the features of the Level 1 model, but they are not behavioral models. They accurately describe the dynamic characteristic within the device except the operating area. An example of a Level 2 model is a lumped-charge model.

The lumped-charge modeling technique was first introduced by P.O. Lauritzen and C.L. Ma in 1991 (82). The technique is based on Linvill's lumped-parameter approach and the standard charge control method. It has been successfully used to create diode (82), BJT (83), Si controlled rectifier (SCR) (84), GTO (85), MCT (86), and MOSFET (87) models. The basic idea is to divide the device into several critical regions; each of these regions contains one charged storage node and up to two connection nodes. The electron and hole values of the charge at each node are equal to the product of the region volume and carrier concentration at each node. Then, the charge nodes are linked using a set of equations related by semiconductor physics and circuit theory.

Based on the physical equations, the injected carrier distribution inside the device is determined with a given external circuit condition. The voltage drops across each segment are calculated based on the carrier distribution at different nodes. The lumped-charge model captures some of the physical behavior of the device, but it does not provide adequate detail for the carrier distribution profile in the base and low-doped drift regions. The models are not easy to adapt to incorporate all thermal dependencies and implementation for use in circuit simulators.

#### **1.3.4 Level 3 Model**

Level 3 models are typically full physics-based models. Beside the external electrical characteristics, internal physical and electrical information, such as the junction temperature and carrier distribution in different regions of the device, can be obtained. This requires solving the Ambipolar Diffusion Equation (ADE) by using some of the numerical algorithms: Fourier series, Laplace transformation, internal approximation, or difference methods. In most cases, due to high level injection, the ADE is assumed to be one dimensional, which is valid for the power semiconductor devices.

The Level 3 models using Fourier series solutions for solving the ADE in the lightly doped drift region have been developed for Si diodes, IGBTs (88), (89), and IGCTs (90).

#### 1.3.5 Level 4 Model

This is a complete, complex physical-properties-based model that captures all of the relevant physical parameters of the device, such as the motion of charge carriers and the

associated electrical fields. The models are process based and should be able to have full two- or three-dimensional representation of the device design. They can also give information about the failure behavior of the device during operation outside of the safe operation area. The models could be implemented by using finite-element techniques; but due to their complexity, no analytical models exist.

#### **1.3.6 Level 5 Model**

These models have the ability to precisely simulate degradation effects that occur in the device during long periods of operation. The models take long-term radiation and degradation into account as well as any effects due to power or thermal cycling. Such models can be used to predict a failure of the device due to degradation. Because of their complexity, very few Level 5 models for power semiconductor devices exist (81).

#### 1.4 Power BJT Models

Since the invention of BJT in 1947, scientists have attempted to describe the behavior of the BJT by using different models. The coupled diode model, developed by Ebers and Moll in 1954 (91), is one of the first BJT models and is widely used in simulating the static behavior of bipolar transistor circuits. A main advantage of the model is its mathematical simplicity; but the disadvantages are that the model neglects various phenomena that can occur in transistors, such as high injection in the base, emitter crowding, breakdown, space-charge-limited flow in the collector, appreciable net recombination in junction transition regions, etc. In 1970, a compact bipolar transistor model (integral charge control model (ICM)) was developed by Gummel and Poon (92). It basically includes many high-level effects, such as conductivity modulation, base push-

out effect, Early effect, and impact ionization. Most SPICE simulators use the Gummel-Poon model for modeling of signal BJTs, but it is inaccurate for modeling of power BJTs (93).

The power BJT models published to 1992 describe the static characteristics, for instance, the quasi-saturation effect, without considering the recombination (94) (95) or giving some dynamic characteristics; but they only take into account the quasi-static behavior of the charge in the collector layer (96), (97). These models do not include the charge in the lightly doped collector which is substantial for determining the dynamic behaviors of a power BJT. A power BJT model, including the charge in the lightly doped collector layer, was proposed by Xu and Schröder in 1992 (98). The model uses an empirical solution to the diffusion equation and sometimes has convergence problems during the transistor switching. Goebel et al., 1993 (99), presented a unified method for modeling power devices based on a hybrid algorithm that solves the equations describing the semiconductor part numerically and part analytically. The method is more exact but requires higher computation time.

Bayer et al., 1994, presented a circuit model of a BJT based on the calculation of the charge carrier distribution in the base and the lightly doped collector region by approximation of the time derivatives (100). Two years later, Talwalkar et al., 1996, proposed a lumped-charge method for modeling a BJT using simplified forms of Poisson's equation, the continuity equation, and the Boltzmann relation (83). It is a Level 2 model that includes all physical effects, such as base widening, recombination in the base, emitter, and collector and base conductivity modulation.

It was mentioned in Section 1.1 that power BJTs have been completely replaced by MOSFETs and IGBTs. This can also be seen on the modeling side. No more models have been proposed for power Si BJTs since then. Now, the new technology, using SiC for the power BJT, requires the development of more precise power BJT physics-based models. The models should provide all of the external electrical characteristics and internal physical and electrical information for the BJT.

Most of the research groups have used some old, already-developed models for Si power BJTs and have only changed the properties of Si to SiC. An example worth mentioning is the modeling of dc gain performance of 4H-SiC BJTs by using a 2D device simulator, PISCES-IIB (101).

The second objective of this work is to develop a new physics-based Level 3 model to model the transient processes in 4H-SiC BJT using the Fourier series for solving the ADE in the lightly doped collector region. The model should be realized using Matlab and Simulink.

# **Chapter 2 – Silicon Carbide Material**

# 2.1 Introduction

This chapter includes an introduction to SiC as a material for power electronic devices. The chapter starts with a brief history of the material, including the very first reported discovery of SiC, right up to the latest existing semiconductor technology. Then, it is followed by details of the physical characteristics of SiC, in parallel with highlights on the advantageous properties from electrical and thermal perspectives.

# 2.2 History of Silicon Carbide

Silicon carbide is one of the oldest compounds in the universe. It is older than our solar system, and it has been floating around the Milky Way for billions of years as stardust that was generated in the atmospheres of carbon-rich red giant stars (102). In 1924, a Swedish chemist, Jöns Jacob Berzelius, discovered SiC while trying to make a diamond. The material was first used as an alternative to diamond for cutting and polishing. Sixty-seven years after Berzelius' discovery, Eugene G. Acheson of Monongahela, Pennsylvania, melted coke and silica in a furnace and found a crystalline product characterized by great hardness. The mineral produced could substitute for diamond as an abrasive and cutting material. It was called "carborundum" from Al<sub>2</sub>O<sub>3</sub>, which is called "corundum." Later, it was found that the new compound was made up of silicon and carbon; however, SiC is still known as "carborundum." The first commercial process to synthesize SiC in the form of a polycrystalline powder was the Acheson process developed and patented in 1893.

In 1905, Moissan found the first natural SiC crystal in a meteorite. Because of this discovery, mineralogists refer to natural SiC as "moissanite" (103). Two years later, a British experimenter, H.J. Round of Marconi Labs, discovered electroluminescence by using a crystal of SiC and a cat's-whisker detector (104). In 1913, Baumhauer used the word "polytype" to describe the ability of SiC to crystallize into different forms varying only in their stacking mode (105). Since then, the research in SiC did not progress far until J.A. Lely at Philips Research Labs in Einhoven (1955) developed a small-scale sublimation technique for growing high purity, good crystallinity SiC crystals for semiconductor purposes (106). This significantly increased the interest in SiC as a semiconductor material, with it becoming even more popular than Si and Ge. The first SiC conference was held in Boston in 1958. However, the initial interest was diverted from SiC to Si because of the advances in silicon processing technology. During the silicon era, there was still some SiC research going on, especially in the former Soviet Union.

In 1978, Tairov and Tsvetkov developed the seeded sublimation process (107) which marked the start of the second stage in the SiC evolution as semiconductor material (102). The first commercial move into SiC growth for semiconductor devices was evident after heteroepitaxial growth of cubic silicon carbide on foreign substrates was introduced in 1981 (108). The interest in SiC technology started again when researchers realized that Si technology had peaked and new semiconductor materials were required with capabilities beyond that of Si.

In 1987, Cree Research was founded. The introduction of 25 mm single crystal wafers of 6H-SiC by Cree in 1990 activated and initiated SiC research and gave new life

to the use of SiC in device development. At present, 35 mm diameter wafers of both 4H and 6H SiC are commercially available from Cree Research (Durham, NC, USA) and Advanced Technology Materials, Inc. (Danbury, CT, USA). Wafers 75 mm in diameter have been prototyped by both Cree and Westinghouse (now Northrup Grumman). Cree was the first to sell devices and quality SiC substrates, and they continue to research ways to surmount the limitations connected with SiC technology. In August 2011, Bridgestone reported that the company had developed a 5-inch SiC wafer. The company is currently working on the development of 6-inch SiC wafers and is planning to bring them to market during the latter half of 2012 (109).

# 2.3 Silicon Carbide Polytypes

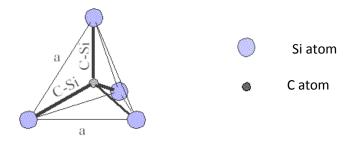

SiC is known as a classical polytypic substance existing in more than 250 polytypes; and the common polytypes are 6H, 15R, 4H, and 3C (110). All polytypes have a hexagonal frame with a carbon atom positioned at the center of the mass of the tetragonal structure outlined by the four neighboring Si atoms, and the distance between a carbon (C) atom to each of the Si atoms is the same (111). Figure 2.1 shows a tetragonal

Figure 2.1. The tetragonal bonding of a carbon atom with the four nearest silicon neighbors (111).

shape formed by four silicon atoms bonded to the carbon atom.

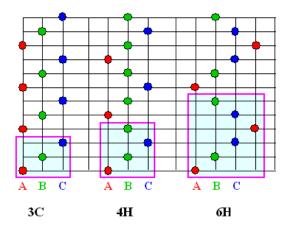

Polytypes are formed by stacking SiC molecules on top of each other in a certain order. The stacking order between succeeding double layers of carbon and silicon atoms determine the difference between different polytypes. The stacking sequence for the three most common polytypes, 3C, 4H, and 6H, is shown in (112). If the first double layer has an A position, the next layer that can be placed, according to a closed packed structure, will be placed on the B position or the C position. The different polytypes are created by permutations of these three positions. For instance, a stacking sequence, ABCABC ... or ACBACB..., represents a 3C-SiC polytype. The number in the formula of a polytype denotes the periodicity. The letter H, C, or R denotes the overall lattice type as being hexagonal, cubic, or rhombohedral, respectively.

During substrate manufacturing for semiconductor devices, it is important that the entire wafer is a single polytype. Growth conditions during substrate production should be stable, because any instability in the growing process will lead to spontaneous switching from one polytype to another. This will alter the electrical properties of the

Figure 2.2. Illustration of common SiC polytypes 3C, 4H, and 6H (112).

material and act as a nucleation site for micropipes (113).

Currently, two SiC polytypes are accepted in SiC research: 6H-SiC and 4H-SiC. Before the introduction of 4H-SiC wafers in 1994, 6H-SiC was the dominant polytype. Since then, both polytypes have been used in research; but recently, 4H-SiC has become the more dominant polytype. This is because the mobilities in 4H-SiC are identical along the two planes of the semiconductor, whereas the 6H-SiC polytype exhibits anisotropy, which means that the mobilities of the material in the two planes are not the same.

#### 2.3.1 Silicon Carbide Physical Properties

Silicon carbide displays a wide range of properties, such as high breakdown electric field strength, high thermal conductivity, high saturated drift velocity, and high thermal stability, which make it attractive for use as a material for semiconductor devices. Table 2.1 summarizes some of the physical properties for the most popular wide band gap semiconductors and Si. The most important properties that benefit 4H-SiC devices are explained in the following sections.

Table 2.1. Physical properties for various semiconductors.

| Material | $E_G$ , eV  | ℰ <sub>C</sub> , MV/cm | n <sub>i</sub> ,<br>cm <sup>-3</sup> | $\mu_r$ , cm <sup>2</sup> /Vs | $10^{7} \text{ cm/s}$ | σ <sub>T</sub> ,<br>W/m.K | CTE,<br>ppm/K |

|----------|-------------|------------------------|--------------------------------------|-------------------------------|-----------------------|---------------------------|---------------|

| Si       | 1.1 (114)   | 0.3 (114)              | 10 <sup>10 (114)</sup>               | 1400 (114)                    | 1.02 (114)            | 130 (114)                 | 2.6 (114)     |

| GaAs     | 1.424 (114) | 0.4 (114)              | $2.1x10^6$                           | 8500 (114)                    | 2.0 (115)             | 55 (114)                  | 5.73 (114)    |

| 3C-SiC   | 2.36 (116)  | 1 (116)                | 10 (118)                             | ≤ 800 <sup>(116)</sup>        | 2.0                   | 360 (116)                 | 3.8 (116)     |

| 4H-SiC   | 3.23 (116)  | 3-5 (116)              | 8.2x10 <sup>-9</sup>                 | ≤ 900 <sup>(116)</sup>        | 2.0                   | 370 (116)                 | 5.12 (116)    |

| 6H-SiC   | 3.0 (116)   | 3-5                    | 2.3x10 <sup>-6</sup>                 | ≤400 <sup>(116)</sup>         | 2.0                   | 490 (116)                 | 4.3-4.7 (116) |

| GaN      | 3.39 (116)  | 3-5 (116)              | 1.9x10 <sup>-10</sup>                | ≤1000 <sup>(116)</sup>        | 2.2                   | 130 (116)                 | 3.2-5.6 (116) |

| Diamond  | 5.45 (117)  | 5.6 (117)              | 1.6x10 <sup>-27 (117)</sup>          | 1900 (117)                    | 2.7 (117)             | 600-2,000 (117)           | 0.8 (117)     |

#### 2.3.2 Wide Band Gap

To understand the basic fundamental transport properties in a material, knowledge about electron band structure near the fundamental band gap is essential. In solid state physics, a band gap is an energy range where no electron states exist. It refers to the energy difference (in electron volts) between the top of the valence band and the bottom of the conduction band, which is found in insulators and semiconductors. Band gap is the amount of energy required to free a valence electron from its orbit around the nucleus so that it becomes a mobile charge carrier, capable of free movement in the solid.

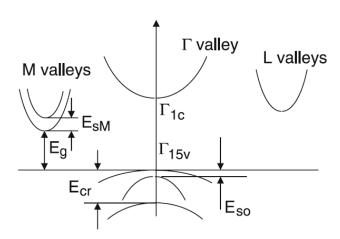

SiC is from the IV-IV group semiconductor family and has an indirect band gap. Every polytype has a different band gap. See the schematic energy band structures of 4H-SiC in Figure 2.3 (116), (120). The doping levels and the optically excited photocarriers are slightly low in the system. Therefore, the band edge transition, where the parabolic bands can be approximated, as characterized by carrier effective masses, should be considered (120).

The highest occupied state of the valence band is at the  $\Gamma$ -point, as the energy separation between  $\Gamma_{I5\nu}$ -valley and  $\Gamma_{Ic}$ -valley is  $E_{\Gamma} = 5$ -6 eV. The conduction band

Figure 2.3. Band structure of 4H-SiC (120)

minimum is at the M-point, and it determines the band gap of 4H-SiC  $E_g = 3.26$ . There is a second minimum of the conduction band at the M-point, which is approximately 0.1 eV above the lowest unoccupied state. The energy separation between  $\Gamma_{15\nu}$ -valley and L valley is approximately 4 eV. Other relevant physical parameters of the energy band structures are: energy of spin-orbital splitting  $E_{so} = 0.007$  eV and energy of critical-field splitting  $E_{cr} = 0.08$  eV.

Some of the electrical properties of the semiconductor materials, such as critical electrical field, intrinsic carrier concentration, mobility, and conductivity, are strongly dependent on the band gap. These dependencies of 4H-SiC will be discussed next.

#### 2.3.3 High Critical Electric Field

An expression for the critical electrical field in the band gap energy for the indirect band gap materials is (121):

$$\mathcal{E}_c = 2.38 \times 10^5 E_G^2 \tag{2.1}$$

There is no dependence on the background doping included in this expression, because the voltage blocking capability, during the off-state of power electronic devices, depends on the property of the lightly doped drift region.

The critical electric field of SiC is higher as compared to Si, because it has a wider band gap. A wider band gap of SiC indicates that energy required to break a bond is significantly higher compared to the energy required for Si. This allows a larger electrical field to be applied before the avalanche of a multitude of ionized carriers occurs in the semiconductor. The more than ten times higher critical electric field of SiC compared to

Si allows power devices to be designed with thinner, more highly doped drift regions for the same blocking voltage.

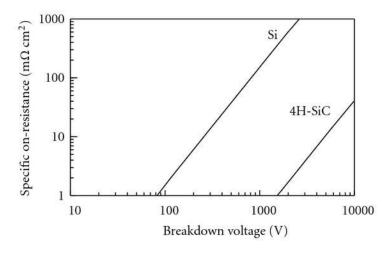

Figure 2.4 presents a theoretical, specific on-state resistance of blocking regions designed for certain breakdown voltages in Si and 4H-SiC, under optimum punch-through conditions (122). Also, the specific on-resistance can be related to the breakdown voltage, BV, electron mobility,  $\mu_n$ , dielectric constant,  $\varepsilon$ , and critical electric field strength,  $\mathcal{E}_C$ , by the following equation:

$$R_{SP-ON} = \frac{4BV^2}{\epsilon \mu_n \mathcal{E}_C^3} \tag{2.2}$$

Figure 2.4. Theoretical, specific on-state resistance of the blocking regions in function of the breakdown voltages for Si and 4H-SiC (122).

From Figure 2.4 and Equation (2.2), it can be deduced that, for the same blocking voltage, SiC devices offer specific on-resistance that is around 350 times lower than their Si counterparts. The doping concentration also affects the blocking voltage. For the same blocking voltage, the background doping in a SiC device is 10 to 100 times higher

than that of a Si device. An increase in doping concentration will also lead to a decrease in specific on-resistance. This is one of the most important advantages of high-voltage SiC; because for the same blocking voltage, the on-resistance is much lower. The fact that the devices can be made thinner and more highly doped means that SiC devices have the capability of operating at a higher frequency. Thinner devices are faster, because the carriers do not have to travel as far through the device.

#### 2.3.4 Low Intrinsic Carrier Concentration

The intrinsic carrier concentration of a semiconductor completely free of impurities and defects is the number of excited electrons from the valence band to the conduction band (and also the number of excited holes in the valence band) per unit volume. It is given by the equation:

$$n_i = N_S e^{-\frac{E_G}{2kT}} \tag{2.3}$$

where  $N_S$  is the number of effectively available states per unit volume;  $E_G$  is the energy band gap; k is Boltzmann's constant (1.381 $\mathbf{x}$ 10<sup>-23</sup> J/K); T is the absolute temperature in Kelvin, and it is assumed that  $kT \le E_G/5$ .

Due to the wide band gap of SiC, its intrinsic carrier concentration is approximately  $8.2 \times 10^{-9} \, \mathrm{cm}^{-3}$ , while the intrinsic carrier concentration of Si is  $10^{10} \, \mathrm{cm}^{-3}$ . Wide band gap semiconductors have the advantage of operating at high temperature and radiation. As the temperature increases, the electron's thermal energy in the valence band increases leading to an uncontrolled condition that should be avoided. The temperature at which this condition occurs for Si is about 150 °C, while SiC has a wide bandgap; and the

valence electrons require more thermal energy to move from valence to the conducting band. This intrinsic temperature for SiC is approximately 900 °C.

Radiation energy can also excite an electron and make it move to the conducting band. Similar to temperature, a wide band gap material will require more radiation energy to free an electron from the conducting band.

As a result of a wide band gap, devices built with SiC can endure more heat and radiation without losing their electrical properties. These devices can operate in extreme conditions where Si-based devices cannot operate.

#### 2.3.5 High Saturated Drift Velocity