Theses and Dissertations

Fall 2012

# Fault diagnosis of VLSI designs: cell internal faults and volume diagnosis throughput

Xiaoxin Fan University of Iowa

Copyright 2012 Xiaoxin Fan

This dissertation is available at Iowa Research Online: http://ir.uiowa.edu/etd/3450

#### **Recommended** Citation

Fan, Xiaoxin. "Fault diagnosis of VLSI designs: cell internal faults and volume diagnosis throughput." PhD (Doctor of Philosophy) thesis, University of Iowa, 2012. http://ir.uiowa.edu/etd/3450.

Follow this and additional works at: http://ir.uiowa.edu/etd

Part of the <u>Electrical and Computer Engineering Commons</u>

# FAULT DIAGNOSIS OF VLSI DESIGNS: CELL INTERNAL FAULTS AND VOLUME DIAGNOSIS THROUGHPUT

by Xiaoxin Fan

## An Abstract

Of a thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

December 2012

Thesis Supervisor: Professor Sudhakar M. Reddy

#### ABSTRACT

The modern VLSI circuit designs manufactured with advanced technology nodes of 65nm or below exhibit an increasing sensitivity to the variations of manufacturing process. New design-specific and feature-sensitive failure mechanisms are on the rise. Systematic yield issues can be severe due to the complex variability involved in process and layout features. Without improved yield analysis methods, time-to-market is delayed, mature yield is suboptimal, and product quality may suffer, thereby undermining the profitability of the semiconductor company. Diagnosis-driven yield improvement is a methodology that leverages production test results, diagnosis results, and statistical analysis to identify the root cause of yield loss and fix the yield limiters to improve the yield.

To fully leverage fault diagnosis, the diagnosis-driven yield analysis requires that the diagnosis tool should provide high-quality diagnosis results in terms of accuracy and resolution. In other words, the diagnosis tool should report the real defect location without too much ambiguity. The second requirement for fast diagnosis-driven yield improvement is that the diagnosis tool should have the capability of processing a volume of failing dies within a reasonable time so that the statistical analysis can have enough information to identify the systematic yield issues.

In this dissertation, we first propose a method to accurately diagnose the defects inside the library cells when multi-cycle test patterns are used. The methods to diagnose the interconnect defect have been well studied for many years and are successfully practiced in industry. However, for process technology at 90nm or 65nm or below, there is a significant number of manufacturing defects and systematic yield limiters lie inside library cells. The existing cell internal diagnosis methods work well when only combinational test patterns are used, while the accuracy drops dramatically with multicycle test patterns. A method to accurately identify the defective cell as well as the failing conditions is presented. The accuracy can be improved up to 94% compared with about 75% accuracy for previous proposed cell internal diagnosis methods.

The next part of this dissertation addresses the throughput problem for diagnosing a volume of failing chips with high transistor counts. We first propose a static design partitioning method to reduce the memory footprint of volume diagnosis. A design is statically partitioned into several smaller sub-circuits, and then the diagnosis is performed only on the smaller sub-circuits. By doing this, the memory usage for processing the smaller sub-circuit can be reduced and the throughput can be improved. We next present a dynamic design partitioning method to improve the throughput and minimize the impact on diagnosis accuracy and resolution. The proposed dynamic design partitioning method is failure dependent, in other words, each failure file has its own design partition. Extensive experiments have been designed to demonstrate the efficiency of the proposed dynamic partitioning method.

Abstract Approved:

Thesis Supervisor

Title and Department

Date

# FAULT DIAGNOSIS OF VLSI DESIGNS: CELL INTERNAL FAULTS AND VOLUME DIAGNOSIS THROUGHPUT

by Xiaoxin Fan

A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

December 2012

Thesis Supervisor: Professor Sudhakar M. Reddy

Copyright by

# XIAOXIN FAN

2012

All Rights Reserved

Graduate College The University of Iowa Iowa City, Iowa

## CERTIFICATE OF APPROVAL

## PH.D. THESIS

This is to certify that the Ph.D. thesis of

Xiaoxin Fan

has been approved by the Examining Committee for the thesis requirement for the Doctor of Philosophy degree in Electrical and Computer Engineering at the December 2012 graduation.

Thesis Committee:

Sudhakar M. Reddy, Thesis Supervisor

David R. Andersen

Wu-Tung Cheng

Jon G. Kuhl

Xiaodong Wu

Hantao Zhang

To My Family

#### ACKNOWLEDGMENTS

I would like to take this opportunity to express my sincere gratitude to all those who supported and encouraged me for completing this dissertation. First and foremost, words are not enough to express my appreciation to my PhD advisor, Professor Sudhakar M. Reddy. His knowledge, encouragement, patience, and guidance were invaluable in my graduate study and my life at University of Iowa. I learned a great deal from his problem solving skills and profound knowledge. I would also like to gratefully acknowledge Dr. Wu-Tung Cheng. He used his knowledgeable explanation and constructive suggestions to help and encourage me to overcome the difficulties in both research and life. I also want to thank my committee members Professor David R. Andersen, Professor Jon G. Kuhl, Professor Xiaodong Wu and Professor Hantao Zhang for their valuable feedbacks, and time and efforts spent in serving on my thesis committee. Many thanks to Huaxing Tang, Yu Huang, Brady Benware and Manish Sharma at Mentor Graphics who provided a great deal of helpful suggestions on my research projects .

I want to thank my colleagues at the Mentor Graphics - Ruifeng Guo, Liyang Lai, Xijiang Lin, Chen Wang, Shuo Sheng, Wei Zou, Wu Yang, Xiaogang Du and Hans Tsai, and friends at University of Iowa – Elham Khayat Moghaddam, Amit Kumar, Sharada Jha and other friends who always gave me support.

Words cannot express my feelings of gratitude to my parent and my brother for their love, continual encouragement and support throughout my life.

Finally, I would like to give my special thanks to my wife, Lei Bao, for her understanding, love and support that accompanied me in these years.

#### ABSTRACT

The modern VLSI circuit designs manufactured with advanced technology nodes of 65nm or below exhibit an increasing sensitivity to the variations of manufacturing process. New design-specific and feature-sensitive failure mechanisms are on the rise. Systematic yield issues can be severe due to the complex variability involved in process and layout features. Without improved yield analysis methods, time-to-market is delayed, mature yield is suboptimal, and product quality may suffer, thereby undermining the profitability of the semiconductor company. Diagnosis-driven yield improvement is a methodology that leverages production test results, diagnosis results, and statistical analysis to identify the root cause of yield loss and fix the yield limiters to improve the yield.

To fully leverage fault diagnosis, the diagnosis-driven yield analysis requires that the diagnosis tool should provide high-quality diagnosis results in terms of accuracy and resolution. In other words, the diagnosis tool should report the real defect location without too much ambiguity. The second requirement for fast diagnosis-driven yield improvement is that the diagnosis tool should have the capability of processing a volume of failing dies within a reasonable time so that the statistical analysis can have enough information to identify the systematic yield issues.

In this dissertation, we first propose a method to accurately diagnose the defects inside the library cells when multi-cycle test patterns are used. The methods to diagnose the interconnect defect have been well studied for many years and are successfully practiced in industry. However, for process technology at 90nm or 65nm or below, there is a significant number of manufacturing defects and systematic yield limiters lie inside library cells. The existing cell internal diagnosis methods work well when only combinational test patterns are used, while the accuracy drops dramatically with multicycle test patterns. A method to accurately identify the defective cell as well as the failing conditions is presented. The accuracy can be improved up to 94% compared with about 75% accuracy for previous proposed cell internal diagnosis methods.

The next part of this dissertation addresses the throughput problem for diagnosing a volume of failing chips with high transistor counts. We first propose a static design partitioning method to reduce the memory footprint of volume diagnosis. A design is statically partitioned into several smaller sub-circuits, and then the diagnosis is performed only on the smaller sub-circuits. By doing this, the memory usage for processing the smaller sub-circuit can be reduced and the throughput can be improved. We next present a dynamic design partitioning method to improve the throughput and minimize the impact on diagnosis accuracy and resolution. The proposed dynamic design partitioning method is failure dependent, in other words, each failure file has its own design partition. Extensive experiments have been designed to demonstrate the efficiency of the proposed dynamic partitioning method.

# TABLE OF CONTENTS

| LIST OF TABLES                                                | viii |

|---------------------------------------------------------------|------|

| LIST OF FIGURES                                               | ix   |

| CHAPTER 1. INTRODUCTION                                       | 1    |

| CHAPTER 2. REVIEW OF FAULT DIAGNOSIS                          | 4    |

| 2.1 Fault Models for Diagnosis                                |      |

| 2.2 Review of Logic Diagnosis Algorithms                      | 6    |

| 2.2.1 Cause-Effect Diagnosis                                  | 6    |

| 2.2.2 Effect-Cause Diagnosis                                  |      |

| 2.2.3 Multiple Faults Diagnosis                               |      |

| 2.3 Review of Cell Internal Diagnosis                         | 18   |

| 2.3.1 Logic Level Cell Internal Diagnosis                     | 19   |

| 2.3.2 Physical Level Cell Internal Diagnosis                  | 24   |

| 2.4 Logic Diagnosis Performance Improvement                   |      |

| 2. + Logie Diagnosis i enormanee improvement                  |      |

| CHAPTER 3. DIAGNOSIS OF CELL INTERNAL DEFECTS WITH MULTI-     |      |

| CYCLE TEST PATTERNS                                           | 33   |

| 3.1 Introduction                                              |      |

| 3.2 Terminology                                               |      |

| 3.3 Excitation Conditions Extraction                          |      |

| 3.4 Diagnosis Defective Cells for Multi-Cycle Patterns        |      |

| 3.4.1 Problems of Identifying Defective Cells for Multi-Cycle | 12   |

| Patterns                                                      | 42   |

| 3.4.2 Proposed Diagnosis Methodology                          | 12   |

| 3.5 Experimental Results                                      | 13   |

| 3.5.1 Experimental Results for Combinational Patterns         |      |

| 3.5.2 Experimental Results for Multi-Cycle Patterns           |      |

| 3.5.3 The Impact on Other Defect Types                        |      |

| 3.6 Conclusions                                               |      |

| <i>5.0</i> Conclusions                                        |      |

| CHAPTER 4. STATIC DESIGN PARTITIONING TO REDUCE MEMORY        |      |

| FOOTPRINT OF VOLUME DIAGNOSIS                                 | 55   |

| 4.1 Introduction                                              |      |

| 4.2 Problem Formulation for Static Design Partitioning        |      |

| 4.3 Static Design Portioning Algorithms for Logic Diagnosis   |      |

| 4.3.1 Overall Block Level Diagnosis Flow                      |      |

| 4.3.2 Partitioning Algorithm                                  | 63   |

| 4.3.3 Evaluating Design Partitions                            |      |

| 4.4 Experimental Results                                      | 67   |

| 4.4.1 Results for ISCAS'89 Circuits                           | 67   |

| 4.4.2 Block Level Diagnosis Results on Industrial Designs     |      |

| 4.4.3 Evaluation on Designs with Sequential Test Patterns     |      |

| 4.4.4 Evaluation on Designs with Test Compression             | 83   |

| 4.5 Conclusions                                               |      |

|                                                               |      |

| CHAPTER 5. IMPROVED VOLUME DIAGNOSIS THROUGHPUT USING         |      |

| DYNAMIC PARTITIONING                                          | 88   |

| 5.1 Introduction                                              |      |

| 5.1 muouucuon                                                 |      |

| 5.2 Preliminaries                                               | 91  |

|-----------------------------------------------------------------|-----|

| 5.3 Failure Dependent Design Partition Algorithm                |     |

| 5.3.1 Overview of the Proposed Methodology                      |     |

| 5.3.2 Extract Clock Information                                 |     |

| 5.3.3 Generation of the Initial Partition Based on Failing Bits |     |

| 5.3.4 Generation of the Final Partition Based on Passing Bits   |     |

| 5.3.5 Layout-aware Partition Generation                         |     |

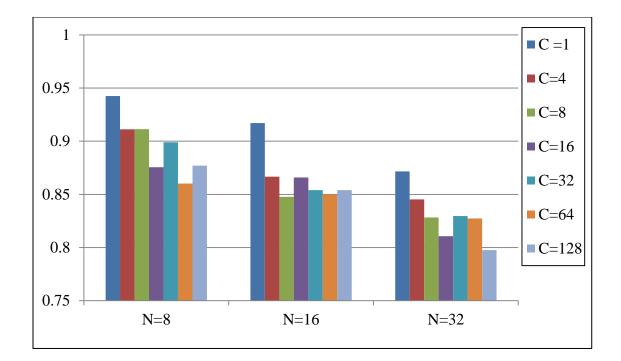

| 5.4 Experimental Results                                        |     |

| 5.4.1 Partitioning Results and Impact on Diagnosis Results      |     |

| 5.4.2 Comparison Experiments for Bridge Fault                   |     |

| 5.4.3 A Practical Example of Throughput Improvement             | 118 |

| 5.4.4 Layout-aware Design Partitioning Results                  |     |

| 5.5.5 Design Partitioning Results with Test Compression         | 122 |

| 5.5 Conclusions                                                 |     |

|                                                                 |     |

| CHAPTER 6. CONCLUSIONS AND FUTURE WORK                          | 125 |

| 6.1 Conclusions                                                 |     |

| 6.2 Future Work                                                 | 127 |

| REFERENCES                                                      | 129 |

# LIST OF TABLES

| Table 1. Truth Table for G1 With An Internal Defect                    | 43  |

|------------------------------------------------------------------------|-----|

| Table 2. Design Characteristic Information                             | 49  |

| Table 3. Diagnosis Results for Using Combinational Patterns            | 50  |

| Table 4. Diagnosis Results on Combination Cell Internal Defects        | 51  |

| Table 5. Diagnosis Results on Sequence-dependent Cell Internal Defects |     |

| Table 6. Impact on Diagnosing Stuck-at Faults                          | 53  |

| Table 7. Design Partition Results for ISCAS'89 Circuits                | 68  |

| Table 8. Prototype Diagnosis Results on ISCAS'89 Circuits              | 71  |

| Table 9. Simulation Score for Industry Designs                         | 73  |

| Table 10. Design Information                                           |     |

| Table 11. Diagnosis Impact and Performance for the Proposed Method     | 110 |

| Table 12. Impact on Physical Bridge Faults                             | 117 |

| Table 13. Partitioning Results for Layout-aware Design Partitioning    | 121 |

| Table 14. Throughput Improvement for Layout-aware Design Partitioning  | 122 |

| Table 15. Partitioning Results with Test Compression                   | 123 |

# LIST OF FIGURES

| Figure 1. Types of Failing Patterns                                       | 12 |

|---------------------------------------------------------------------------|----|

| Figure 2. Overall Flow of Error Propagation Analysis                      | 15 |

| Figure 3. Transistor Open and Bridge for 2-inputs NAND Cell               | 20 |

| Figure 4. Examples for Transformation of Single Transistor                | 21 |

| Figure 5. Examples for Transformation of Parallel Transistors             | 21 |

| Figure 6. Complete Diagnosis Flow [32]                                    | 22 |

| Figure 7. Test Patterns for Consistency Check                             | 23 |

| Figure 8. Effect-Cause Diagnosis Flow [9]                                 |    |

| Figure 9. Diagnosis Procedure Using Additional Dictionaries               | 30 |

| Figure 10. Example of Multiple Exercising Conditions                      |    |

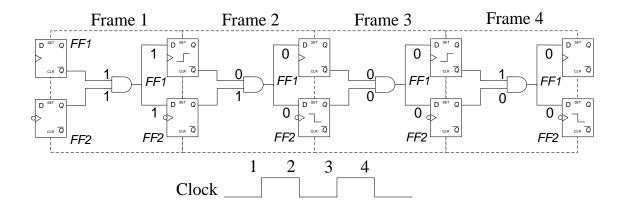

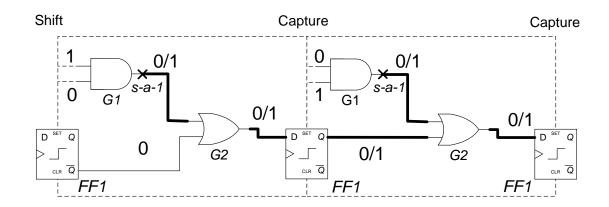

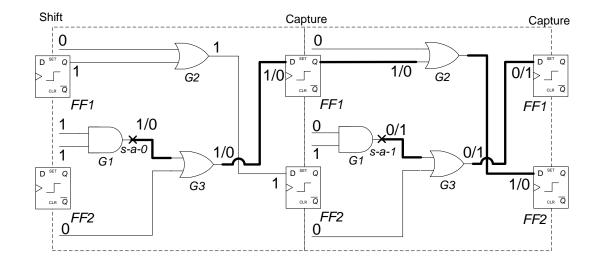

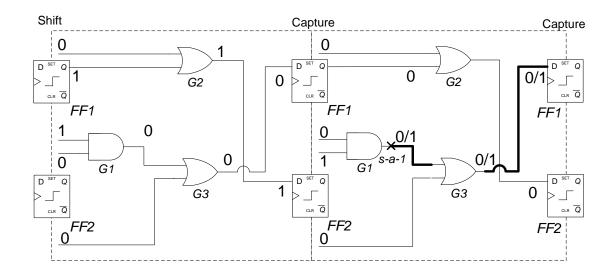

| Figure 11. Simulating with Two Capture Cycles                             |    |

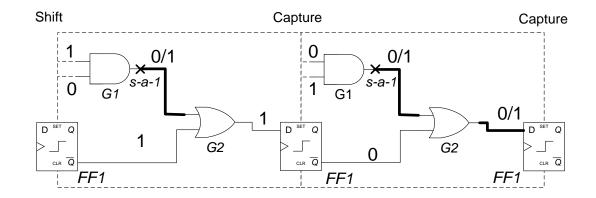

| Figure 12. Backtracing Procedure                                          | 40 |

| Figure 13. Inaccurate Excitation Conditions                               | 41 |

| Figure 14. Different Faulty Values In Two Capture Cycles                  | 43 |

| Figure 15. Partial Faulty Capture Cycle                                   | 44 |

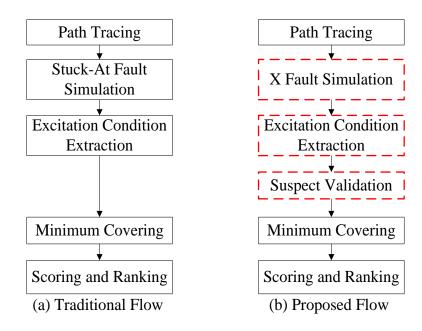

| Figure 16. Generic Traditional Diagnosis Flow vs. Proposed Diagnosis Flow | 45 |

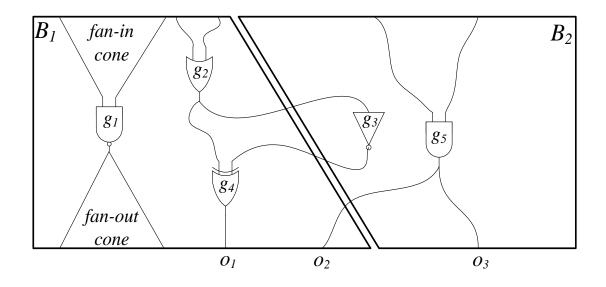

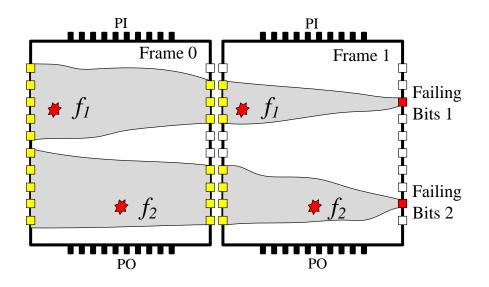

| Figure 17: Design Partitioning                                            | 60 |

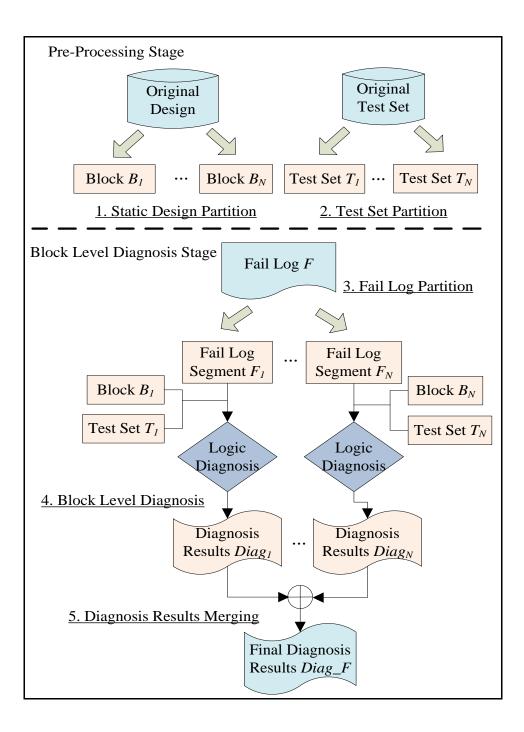

| Figure 18: Overall Flow of Block Level Diagnosis                          | 63 |

| Figure 19: Proposed Design Partitioning Algorithm                         | 65 |

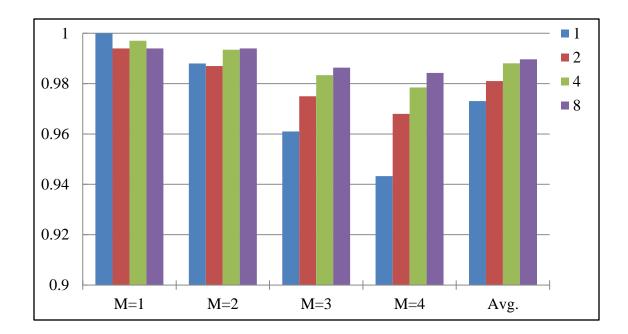

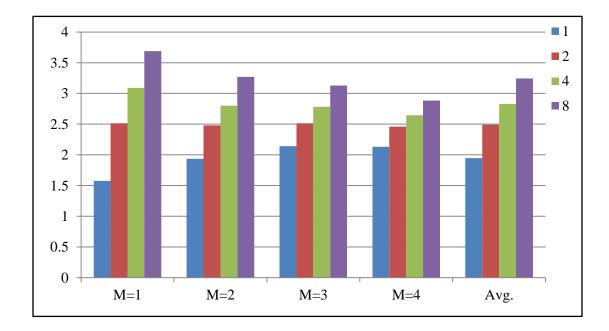

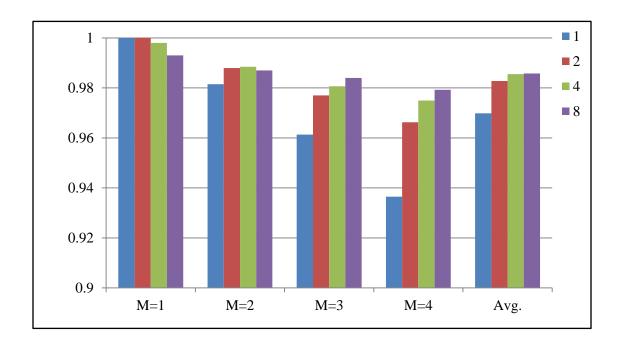

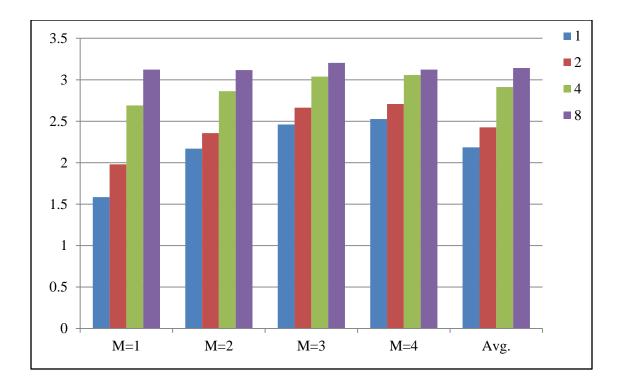

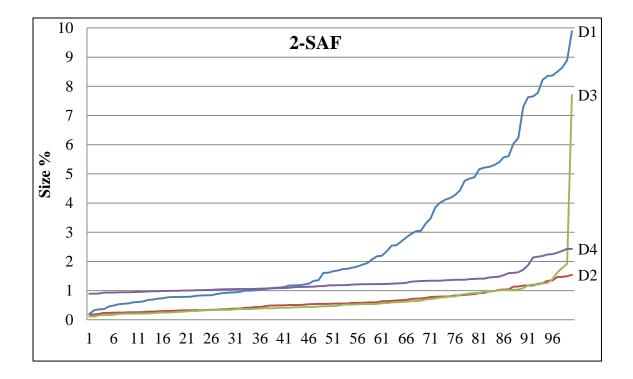

| Figure 20. Diagnosis Accuracy for D1                                      | 74 |

| Figure 21. Diagnosis Resolution for D1                                    | 75 |

| Figure 22. Diagnosis Accuracy for D2                                      | 75 |

| Figure 23. Diagnosis Resolution for D2                                    | 76 |

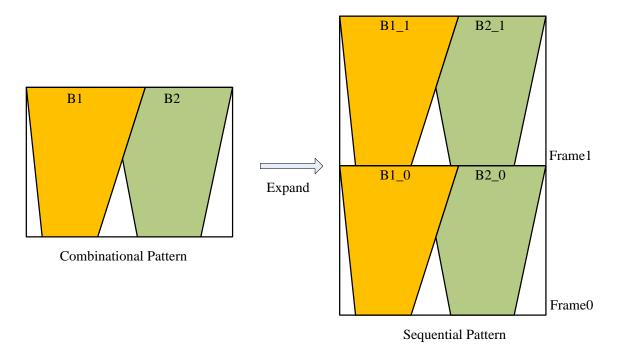

| Figure 24. Design Partitioning with Sequential Pattern                    | 78 |

| Figure 25. Extra Failing Bits for Sequential Pattern                      | 79 |

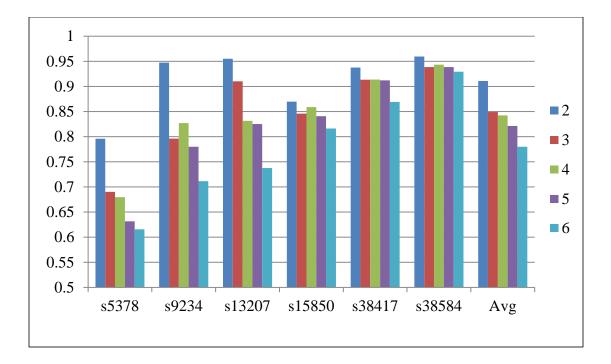

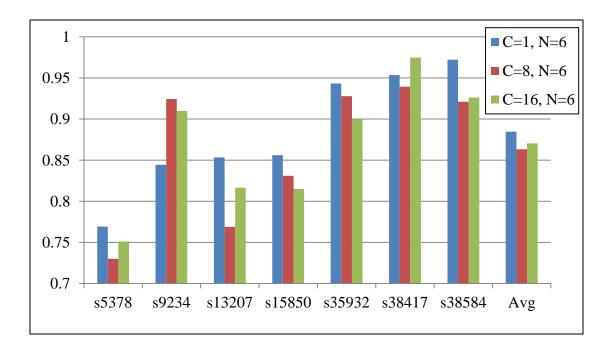

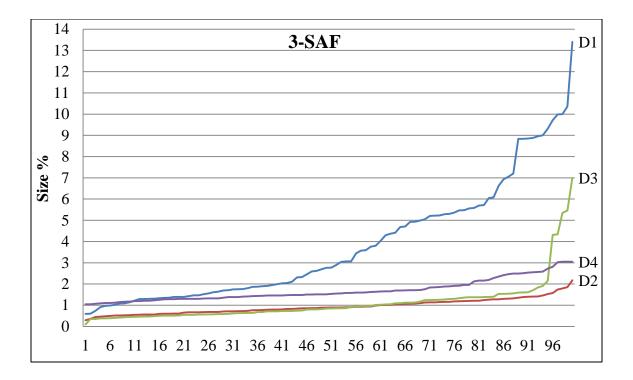

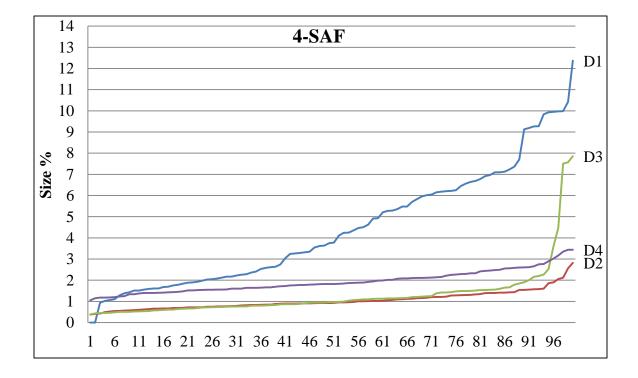

| Figure 26. Simulation Scores for ISCAS'89 Benchmarks with Sequential Patterns .                     | 81  |

|-----------------------------------------------------------------------------------------------------|-----|

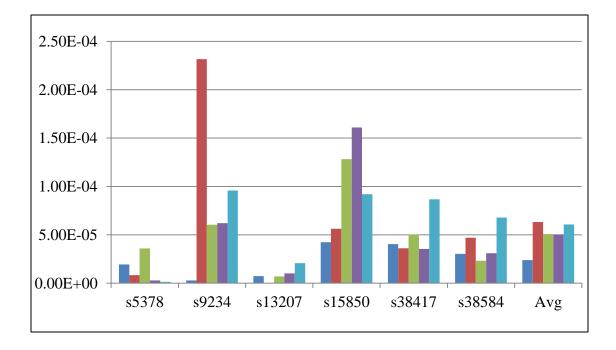

| Figure 27. Extra Failing Bits for ISCAS'89 Benchmarks                                               | 81  |

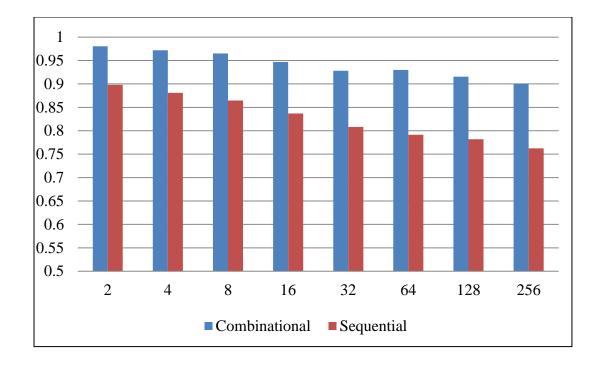

| Figure 28. Simulation Scores for Industrial Design D3 with Sequential Patterns                      | 82  |

| Figure 29. Simulation Scores for Industrial Design D4 with Sequential Patterns                      | 82  |

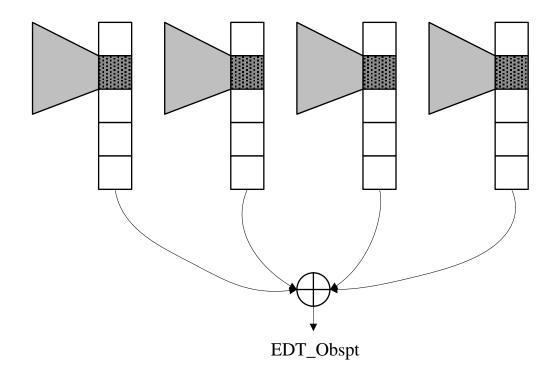

| Figure 30. Tracing Fan-in Cone for an External Observation Point with Test<br>Compression Structure | 84  |

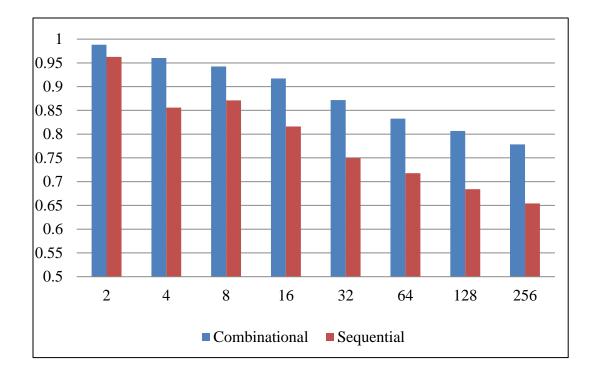

| Figure 31. Simulation Scores for ISCAS'89 Benchmarks with Test Compression<br>Structure             | 85  |

| Figure 32. Simulation Score for D5 with Test Compression Structure                                  | 86  |

| Figure 33. General Procedure of Effect-cause Diagnosis Algorithm                                    | 92  |

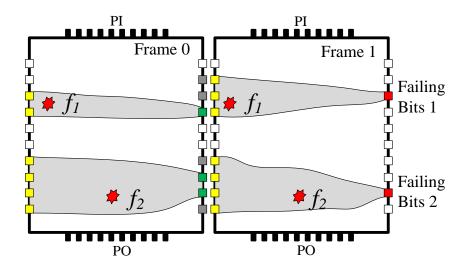

| Figure 34. Initial Partition Based on Failing Bits                                                  | 96  |

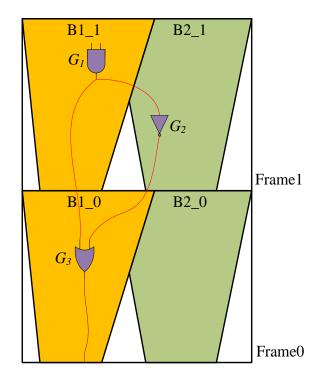

| Figure 35. Back Tracing for Sequential Pattern                                                      | 97  |

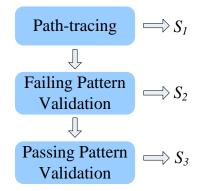

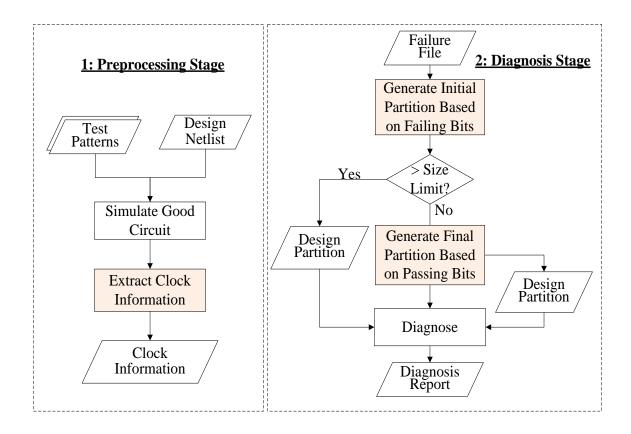

| Figure 36. Overall Flow of the Proposed Methodology                                                 | 99  |

| Figure 37. Back Tracing with Clock Information                                                      | 100 |

| Figure 38. Initial Partition Generation Procedure                                                   | 101 |

| Figure 39. Procedure of Final Partition Generation Based on Passing Bits                            | 102 |

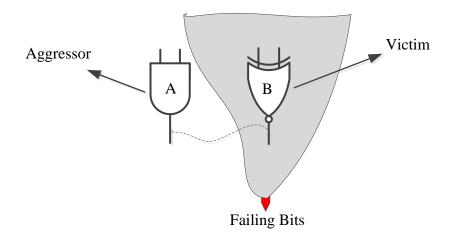

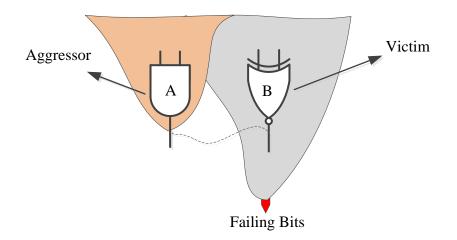

| Figure 40. Example of Misdiagnosed Physic Defect Based on Partition                                 | 106 |

| Figure 41. Example of Layout-Aware Partition                                                        | 106 |

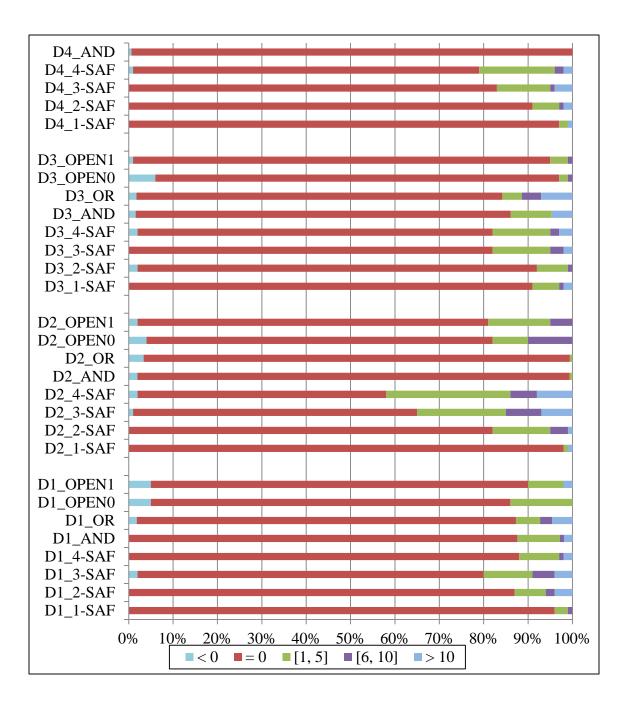

| Figure 42. Distribution of the Suspect Count Change                                                 | 113 |

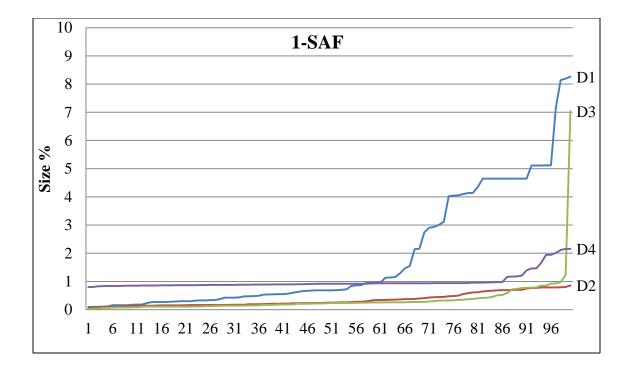

| Figure 43. Distribution of the Partition Size for Single Stuck-at Fault                             | 114 |

| Figure 44. Distribution of the Partition Size for Two Stuck-at Faults                               | 114 |

| Figure 45. Distribution of the Partition Size for Three Stuck-at Faults                             | 115 |

| Figure 46. Distribution of the Partition Size for Four Stuck-at Faults                              | 115 |

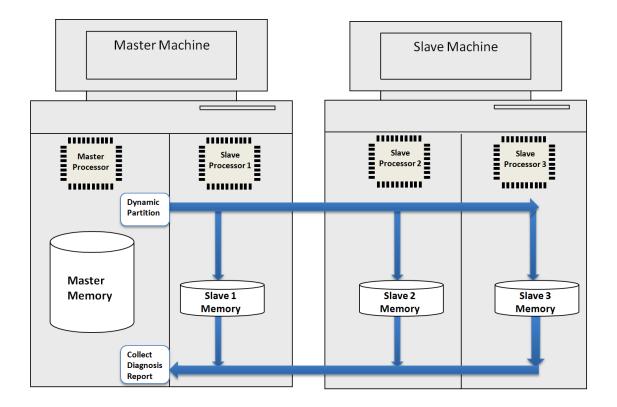

| Figure 47. Dynamic Partitioning Based Master-Slave Diagnosis Architecture                           | 118 |

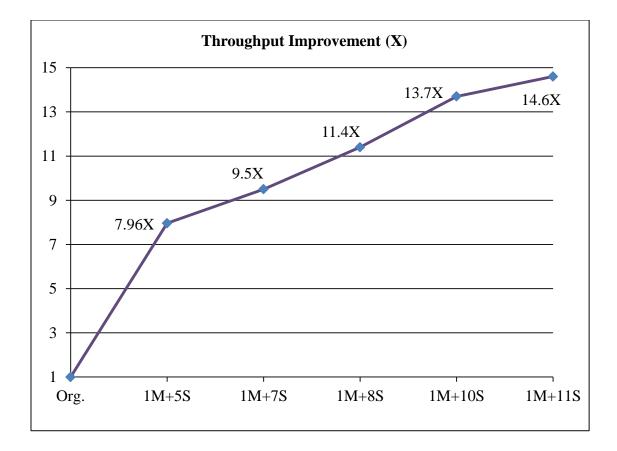

| Figure 48. Throughput Improvement Results                                                           | 120 |

#### **CHAPTER 1. INTRODUCTION**

The manufactured dies usually are tested by a set of test patterns such as structural test patterns to ensure the quality before being shipped out. Only those dies that pass all the tests will be delivered to the customers. The dies screened out by structural testing will not be thrown away. Instead logic diagnosis is typically performed on some or all failing dies to determine the cause of the failure inside the failing die. The diagnosis results generally can be leveraged by two applications. The first application is physical failure analysis (PFA) in which a small number of failing dies are investigated to reveal the physical evidences for the failures. The possible faulty locations and types identified by logic diagnosis can lead to a faster and cheaper PFA process. Another application is yield analysis over a large volume of diagnosis results to point out the systematic yield issues during fabrication process without explicit costly PFA. Through statistically analyzing the volume diagnosis information, the yield limiters can be learned, and then the yield can be quickly ramped up by tuning the fabrication process parameters or modifying the design rules and re-designing with new design rules.

Both the PFA and volume diagnosis based yield learning raises two essential requirements for diagnosis algorithms:

• High diagnosis quality: The diagnosis quality usually is measured by two metrics: accuracy and resolution. The accuracy describes the ability of the diagnosis algorithm in finding the real defects, while the resolution defines the capability of diagnosis algorithm in differentiating the ambiguity between the fake suspects and the real defects. With low accuracy and resolution, the time for PFA process for searching the defect locations becomes long and thus leads to expensive PFA. Also for yield learning, the accuracy of the systematic yield limiters heavily relies on the logic diagnosis accuracy and resolution on a volume of failing dies.

• **High diagnosis performance**: The performance for a diagnosis algorithm includes the runtime and memory consumed by the diagnosis algorithm. The long runtime of diagnosis can delay the PFA process. For volume diagnosis based yield learning, the long runtime and large memory consumption will reduce the number of failing dies processed within a given time and computational resources, thus will slow down the yield limiter identification.

Following the Moore's Law, the modern integrated circuit fabrication technology keeps shrinking and it has advanced from 90nm to 65 nm and beyond. The smaller feature size allows a single die to integrate thousands of millions of transistors. Both the shrinking feature size and increasing design scale pose challenges for the conventional logic diagnosis.

The first challenge is that for 65nm and beyond technology a large number of manufacturing defects and systematic yield issues lie inside library cells. Conventional logic diagnosis which only reports the faulty nets or cells may not be accurate enough for both PFA and yield learning. The defect inside the cell should be identified for fast and cheap PFA as well as successful and quick diagnosis-driven yield learning. Our first research objective is to enhance the quality of logic diagnosis by accurately and efficiently identifying the cell internal defects.

The second challenge is that the performance (runtime and memory consumption) of the logic diagnosis algorithm is degraded due to the extremely large design, as both the runtime and memory footprint of the conventional logic diagnosis algorithms are proportional to the scale of the design. The longer runtime and the large memory requirement can reduce the diagnosis throughput which is defined as the number of failing dies diagnosed within a time and a given computational resource. The low throughput can delay the PFA process and yield limiters identification, thus impact the time-to-market. In this dissertation, the second objective of our research is to improve the

performance of logic diagnosis, through reducing the runtime and memory consumption for logic diagnosis algorithms.

The rest of the dissertation is organized as following. In Chapter 2, we briefly review previous works including fault models used for fault diagnosis, fault diagnosis algorithms, cell-aware diagnosis and performance improvement for fault diagnosis. In Chapter 3, a method is presented to diagnose cell internal defects with multi-cycle test patterns. Chapter 4 proposes a static design partitioning approach to reduce the memory footprint of volume diagnosis. A failure-dependent dynamic design partitioning method is proposed in Chapter 5. Finally Chapter 6 draws the conclusion.

#### CHAPTER 2. REVIEW OF FAULT DIAGNOSIS

#### 2.1 Fault Models for Diagnosis

In logic diagnosis, fault models are used to model the failure behavior caused by a physical defect. Using logic level fault model can simplify simulating the fault effect caused by the real defect. Based on the fault models, defects can be identified by logic diagnosis. Fault models, such as stuck-at fault model, bridge fault mode, open fault mode, transition fault model, path delay fault model and cell internal fault mode, are widely used in current logic diagnosis procedures.

#### • Stuck-at fault model [1]

The stuck-at fault model has been used successfully for decades for describing the permanent faulty behavior on a line in the circuit caused by the defect. With a stuck-at fault on a line, the correct value on that line appears to be stuck at a constant logic value, either 0 or 1, referred as stuck-at-0 or stuck-at-1. The stuck-at-0 represents a short defect between the signal line and the ground line, while the stuck-at-1 could represent a short defect between the signal line and the power line.

#### • Bridge fault model [2][3]

The logic behavior of a short defect between signal lines is commonly represented by the bridge fault model. The bridge fault model that models the logic values of the shorted lines as logic AND or OR logic values of these two faulty nodes is referred to as wired-AND/wired-OR bridge fault model. The dominant bridge fault model was proposed to for the bridge defects in which one line is assumed to dominate the logic value on the other line. Usually the bridge fault mode captures the short defect between one signal line with another signal line instead of power or ground line.

#### • Open fault model

The open fault models the defect by assuming there is an interconnection on a signal line. Usually the open fault can model defect such as electrical open, break, and disconnected via in a circuit. Open fault can result in state-holding, intermittent, and pattern-dependent fault effects which are more complex. Stuck-at-0 open or stuck-at-1 open are often used in logic diagnosis.

#### • Transition fault model

The transition fault model [4] is used to model the delay fault that leads to the transition from the gate input to its output falling outside the specified timing limit. By the transition types there are two transition fault models: slow-to-rise fault model and slow-to-fail fault model. The slow-to-rise (slow-to-fail) fault assume that the transition from 0 to 1 (1 to 0) cannot reach the output within the specified time.

#### • Path delay fault model

The path delay fault model [5] describes the delay defect along a set of predefined structural paths. The path selected for path delay usually is a critical path identified by timing analysis tool, which consist of an ordered set of gates. The path delay fault can model the distributed small delay defects along the path by summing up the delays of the gates.

#### Cell internal fault model

Some fault models are proposed to describe the defects inside the cell. Usually those fault models are similar to the fault models used for describing the defects in inter-gates. Instead of modeling the defects between gates, the internal defect models, such as stuck-at fault, stuck-open fault, resistive-open fault and short/bridge, represent the internal defects existing between transistors.

The most widely used fault model for logic diagnosis is stuck-at fault model for its simplicity. Using the stuck-at fault model to run the simulation for logic diagnosis, we can first get a set of possible defective gates with stuck-at faults in its inputs or outputs. Based on the results, complex defects can be identified by applying more sophisticated fault models such as bridge fault model and net open fault model.

For the logic diagnosis using stuck-at fault model, the diagnosis algorithms can be classified into two categories. The first category is called cause-effect analysis in which a pre-simulated fault dictionary for all the faults with all the test patterns and then the fault dictionary is looked up to find a set of candidates that can best match the test fails by the failing device observed on the tester. The second category is effect-cause analysis which derives possible faulty locations by directly examining the failure syndrome of the failing chips.

#### 2.2 Review of Logic Diagnosis Algorithms

In this section, first we would like to review two basic logic diagnosis algorithms using stuck-at fault model: cause-effect diagnosis and effect-cause diagnosis. Previous works on diagnosing multiple defects will be further discussed in the rest of the subsection.

#### 2.2.1 Cause-Effect Diagnosis

The cause-effect diagnosis [6] algorithm first assumes if there is a fault in the circuit what the failure syndrome would be. Usually a specific fault type such as stuck-at fault is assumed to be the causes of the failure. A dictionary which records the responses of all the assumed faults for all the test patterns is generated ahead of diagnosis by intensively performing fault simulation. This dictionary also is referred as fault dictionary. After the fault dictionary is built, the failure syndrome of the failing device is examined using fault dictionary look-up. The fault whose test response best matches the observed failure will be considered as the most likely fault candidate.

The time for constructing the fault dictionary equals to the time for fault simulating all the test patterns for all the faults considered for the circuit, which is acceptable as it is one-time cost prior the diagnosis. During the diagnosis, it is fast for just looking up the table to derive the fault candidates. However, for practical application the cause-effect diagnosis algorithm could be limited by some problems. The first problem is the dictionary size problem: it requires a large amount of storage for recording all test response for all the faults with all the test patterns. Theoretically the size of the fault dictionary is  $O(F \cdot V \cdot O)$ , where is F is the number of faults in the circuit, V is the test patterns used for testing and O is the number of observation points in the circuit (usually this number is approximate to the number of scan cells). With the increasing size of the design, this method will require extremely large storage thus becomes inapplicable. This problem can be relived to some extent by using compaction and compression techniques.

Some works have been published to reduce the size of the fault dictionary. The pass-fail dictionary is the simple way to reduce the dictionary size by using a single pass-fail bit to replace the output response of the test vector [7]. Therefore the size of the fault dictionary can be reduced to  $O(F \cdot V)$ . However by doing this the resolution will become worse as some faults become undistinguishable by only using pass-fail bits. In [7] this is future improved by carefully selecting extra output responses for some test patterns such that the resolution will not be impacted. Another method was proposed [8] to build small fault dictionary by recording only the test responses of the failing patterns with the faults detected by failing patterns instead of recording the test responses of all the test patterns with all the faults. This can reduce the memory requirement without sacrificing resolution. The size can be further reduced by recording only k failing test patterns at the cost of slightly degrading the resolution. Researchers in [8], [9] proposed a technique to compress the fault dictionary by using a multiple input signature register (MISR) to generate a compressed fault signature. One problem for this method is two difference test responses may be compressed to the same failing signature.

Another issue using the cause-effect diagnosis algorithm is that it may miss the accuracy for some realistic defects which could not be modeled by stuck-at fault which is used to the build the fault dictionary. Sometimes some realistic defects, such as stuck-

open fault and bridge fault, may not behave as stuck-at fault. In [11], the realistic defects are used to build the fault dictionary such that some defects which could not be modeled by stuck-at fault will be considered. However since the number of realistic defects is much larger than the number of stuck-at faults, it will increase the size of the fault dictionary as well as the simulation time. Also the realistic defect should be carefully extracted otherwise it will lead to inaccurate diagnosis results. Bridge faults [12] has been targeted for building the fault dictionary, nevertheless, it still cannot cover all the realistic defects and suffers from inaccurate results.

These two problems limit the cause-effect diagnosis algorithm in practical application. Comparing with cause-effect analysis, the effect-cause is superior and widely used in nowadays digital circuit diagnosis.

#### 2.2.2 Effect-Cause Diagnosis

In contrast to cause-effect analysis paradigm, effect-cause diagnosis algorithms directly derive the fault candidates from the failing responses by using fault simulation technique without pre-simulating a table. Comparing with the cause-effect methodology, effect-cause has several advantages:

- It requires less memory storage. As most of the memory for effect-cause is consumed for simulating the circuit therefore it is applicable for practical use.

- No pre-assumed fault model. It does not pre-assume a fault model, thus it can be

used for diagnosis more realistic faults. Note that stuck-at fault model usually is

used for simulation and identifying the initial possible defective cells or locations.

Additional analysis using complex defect models such as bridge can be applied to

deduce the real physical defect types and locations.

One disadvantage for using effect-cause analysis is that it takes longer time to diagnose the defect as the fault simulation process requires more runtime than the fault

dictionary look-up. Before discussing the algorithms, we give some definitions of terms as following:

- Failing Observation Point: An observation point (scan-cell or primary output) is a failing observation point if there is a test pattern such that applying that pattern the value on the observation point captured by the tester is different with the value simulated using good circuit. It is also referred as failing bit.

- **Passing Observation Point:** An observation point (scan-cell or primary output) is a passing observation point if the values observed on the tester are identical with good circuit simulation when applying all the test patterns. It is also referred as passing bit.

- **Failing Pattern:** A test pattern is a failing pattern if one or more failing observation points are captured on the tester when applying the pattern.

- **Passing Pattern:** A test pattern is a passing pattern if no failing observation point is captured on the tester when applying the pattern.

The general procedure of effect-cause diagnosis algorithm if assuming single fault in the circuit can be summarized as following:

• Step 1: Initial faulty candidates identification. In [13], the critical path-tracing technique which was originally proposed for fast simulation [14] was applied to logic diagnosis. For each failing pattern, it first simulates the pattern on good circuit, and then it backtracks every failing bit to identify the faults in the fan-in cone of the failing bit that can account for the failure. A fault that is considered as an initial candidate if it is in the fan-in cone of the failing observation point, and it has a parity-consistent path to the failing observation point. If assuming single fault then the intersection of all the fault candidates for all the failing bits is considered as the final candidate set. Otherwise, the union will be the final candidate set.

- Step 2: Failing pattern validation. The initial candidates obtained at the Step 1 may contain too many suspects that need be pruned. In this step, all the initial candidates are fault simulated with all the failing test patterns. A candidate can explain a failing pattern if fault simulating the candidate with the failing pattern the test response matches the failure syndrome. If only part of the failing observation points matches the failure syndrome the candidate is considered as partially matching the failing pattern. The candidate can be weighted by the number of fully explained and partially explained failing patterns. A candidate that cannot explain any failing pattern will be discarded.

- Step 3: Passing pattern validation. The initial suspects can be further refined by simulating the passing test patterns. Intuitively a real defect should not produce any failing bits when simulating a passing pattern. Therefore, a candidate will be removed from the suspect set if it fails at a passing pattern.

With the increasing design complexity and shrinking feature size of transistors, it brings several issues for single fault assumption. First is that more and more realistic defects cannot be modeled by simple single fault model. For example, single defect can manifest its behavior as multiple faults. Also the defect density increases as the process technology advanced. Experiments in [15] show that if the diagnosis assuming single stuck-at fault in the circuit more than 41% defects cannot be correctly found. In order to have good diagnosis quality, it is necessary to develop some diagnosis algorithms to cope with multiple faults in the circuit. Next we would like to briefly review some previous works on multiple faults diagnosis.

#### 2.2.3 Multiple Faults Diagnosis

The challenge for directly address the multiple faults problem is the error space grows exponentially, as shown in [16]: error space =  $(\# \text{ of lines})^{(\# \text{ of faults})}$ , where "# of lines" is the number of signal lines in the circuit and "# of faults" is the number of faults

that we assumed in the circuit. In addition, multiple faults may be activated at the same time and the fault effect of one fault may be interfered or cancelled by other faults, which makes the multiple-fault diagnosis more difficult. Several works have been proposed to handle the multiple faults by using some heuristics or assumptions to reduce the complexity of above mentioned challenges.

#### 2.2.3.1 Xlists Based Multiple Fault Diagnosis

The ideal proposed in [17] using Xlist to refine a region with faults that can possible contribute the errors is based on the assumption that the faults are locally bounded and presents themselves in clusters. This method addresses the first problem by reducing the search space thus it has good runtime. However, when the faults are unrelated and scatter in the circuit this method may not effective to find the faulty locations.

#### 2.2.3.2 Single-Location-at-a-Time (SLAT)

In the previous work [15], [18], the authors assume that there are some patterns that cause only a single fault to produce fault effect at some observation points. Based on this assumption, it first finds out single-fault locations that could explain one or more failing test pattern. It shows that most of the failing patterns are indeed SLAT patterns, even though there possible are multiple faults in the circuit. The candidates found in the first phase have the property that it can explain at least one failing patterns. After find these candidates, the algorithm tries to find a minimum set of candidates that could explain all the failing patterns. The set of candidates that explain all the failing patterns is called multiplet. The results in [18] shows that it can handle complex defects like bridge faults. The algorithms however could not correctly identifying 7% of the cases in which either there is no SLAT pattern or the size of the multiplet is too large. In reality, this algorithm may lose accuracy if few SLAT patterns pattern exist or SLAT patterns are actually produced by multiple defects.

#### 2.2.3.3 Incremental Diagnosis and PO Partition

The work in [19], [20] handles multiple faults by an incremental simulation-based method and failing outputs partitioning without explicitly considering the behavior of multiple faults.

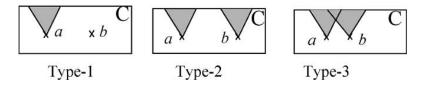

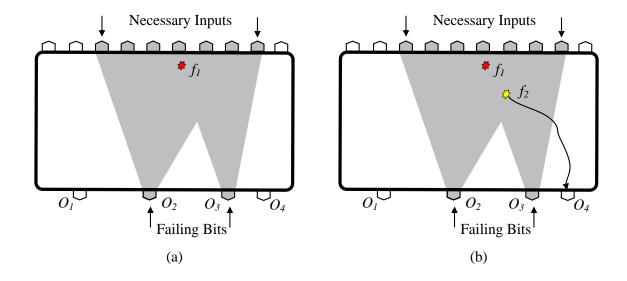

The failing patterns are firstly classified into three types, as shown in Figure 1:

- Type 1: SLAT pattern, i.e., only one fault can have its fault effects being observed.

- Type 2: A failing pattern activates multiple faults, but fault effects of them are not correlated.

- Type 3: A failing pattern activates multiple faults, and the fault effects may affect each other.

Figure 1. Types of Failing Patterns

Type 1 failing pattern can be handled by most of the SLAT based logic diagnosis algorithms. The method proposed in [19], [20] tries to address the Type 2 and 3 failing patterns which activate multiple faults. For Type 2 failing pattern, a failing PO partitioning method was proposed and in each partition is Type 1 case which can be easily diagnosed. The failing PO partitioning algorithm can be summarized as following:

- 1. Backward tracing for each failing PO to find reachable faults.

- 2. Construct a graph, in which the vertex is a failing PO and an edge exists between two vertices (failing POs) if they can reach some common faults in a failing

pattern. The weight of an edge is the number of failing patterns for which the two vertices (failing POs) have common reachable faults.

- 3. Partition the graph by greedily removing the lowest weight edges.

- 4. Diagnosis each groups of failing POs separately.

To handle the Type 3 failing pattern, based on the observation that Type 1 failing pattern always exists even if multiple-fault failure responses are also present, the proposed first use *Algsingle algorithm* [21] trying to find some candidates that perfectly some failing patterns, and then iteratively group candidates to explain the rest of the unexplained failing patterns by *n-perfect algorithm*. Next are the detail of some definitions and these two algorithms.

*n*-perfect candidate: *n*-perfect candidate is a group of *n* faults such that by injecting the group of faults into the circuit we can perfectly explain some failing patterns.

The *Algsingle algorithm* can be explained as following:

- 1. Initialize the fault candidate list using critical path-tracing.

- 2. Simulate each fault in initial candidate list to see if it can perfectly explain any of the failing patterns. If so assign it a weight equal to the number of patterns it explains on the current list. Store the candidate fault with the greatest weight, and removing the failing pattern explained by it.

- 3. Sort candidate faults using their weights obtained in Step 2. Report the possible candidates.

- For circuit with multiple defects, these 1-perfect candidates may not be able to explain all the failing patterns. Then n-perfect algorithm is used to incrementally find n-perfect candidates to explain the rest of the failing patterns.

*n-perfect algorithm:*[19], [20]

- 5. Find a 1-perfect fault candidate using *Algsingle algorithm*, remove the explained patterns.

- Inject each n-perfect candidate into the circuit and perform step 3 and 4 until all n-perfect candidates have been tried.

- 7. For each unexplained failing pattern, initialize the possible fault candidates.

- 8. Perform *Algsingle algorithm* on the modified circuit and construct (n+1)-perfect candidates based on the targeted fault model.

- Determine the (n+1)-perfect candidates that can further explain some failing patterns which are not explained before.

- 10. Rank and weight the (n+1)-perfect candidates based on failing and passing information. Eliminate those failing patterns that can be explained by (n+1)-perfect candidates from the failing pattern list. Increase n by 1.

- 11. Repeat steps 2-6 for the remaining unexplained failing patterns until no fault candidate can be found, or until all failing patterns have been explained.

- 12. Post process all possible k-perfect candidates (1≤k≤n) to remove the candidates cause many passing patterns to fail.

#### 2.2.3.4 Error Propagation Analysis

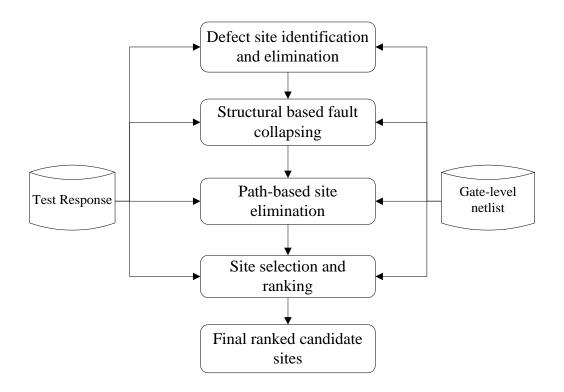

The authors in [22][23] developed a multiple defects diagnosis methodology including a defect site identification and elimination method, a path-based defect site elimination method and a defect site selection and ranking method. It has the capability to handle various defect behaviors and arbitrary failing pattern characteristics. The overall flow of the proposed method is given in Figure 2.

The initial candidates are obtained through path-tracing. Then a fault site will be eliminated from the candidate set if it will cause passing observation point to fail for some failing patterns. This is done by performing conservation implication analysis on passing observation points for all the failing patterns. Initial candidates are further collapsed by using structural equivalence information. Before analyzing the initial candidates, three definitions are given to describe the ability for some candidate to propagate the error to some observation points:

- For pattern t<sub>k</sub>, if site f<sub>i</sub> propagates to an observation point out<sub>j</sub> if all the side inputs of on-path gates have fault-free values, f<sub>i</sub> is said to "**output-explain**" out<sub>i</sub> for t<sub>k</sub>.

- For patter t<sub>k</sub>, if site f<sub>i</sub> propagates to an observation point out<sub>j</sub> if some side inputs of on-path gates have fault values, f<sub>i</sub> is said to "**partially output-explain**" out<sub>j</sub> for t<sub>k</sub>.

- Let f<sub>i</sub> -J<sub>i</sub> be the longest sub-path such that f<sub>i</sub> can propagate to J<sub>i</sub> when all the side inputs of on-path gates have fault-free values. The remaining sub-path J<sub>i</sub> out<sub>j</sub> is called the "under-explained" sub-path.

Figure 2. Overall Flow of Error Propagation Analysis

Based on the definitions, fault sites can be grouped:

- For each failing pattern and each defect site that explains any observed failing observation points, we find the "out-explained" *out<sub>j</sub>* and also the "under-explained" sub-path for each site.

- Group the sites that have the same "out-explained" observation points and the same "under-explained" sub-path together.

Then fault site set are selected if it out-explains the most observed failing points that have not been explained.

Finally the fault site sets are ranked according rules:

- Rule 1: A site that is an element of a smaller site set is ranked higher

- Rule 2: if rule 1 results in a tie, a site that output-explains more failing observation points is ranked higher.

- Rule 3: if rule 2 results in a tie, randomly choose one site.

One drawback of this method is the fault elimination step may not be able to eliminate many fault sites, which may increase the effort the following analysis steps.

#### 2.2.3.5 Diagnosis Multiple Faults using Fault-Tuple

#### Equivalence Trees (FTET)

A method [24] for diagnosing multiple arbitrary faults has been proposed recently without assuming fault models. In the given method, techniques for construction and scoring of fault-tuple equivalence trees are introduced to choose and rank the final candidates so as to handle multiple-fault mask and reinforcement effects. For each failing pattern, the method traces from all the failing observation points to the primary inputs to construct a FTET. For each failing test pattern, the initial fault-tuple is a set of all the failing observation points. Starting from the initial fault-tuple, the backward tracing tries to find more fault-tuple that could explain the failing pattern. After the FTET for a failing pattern is built, the faults in the FTET are given a score to estimate the capability for explaining the failing pattern. Then fault sites are selected based on the score to prune the FTET.

The experimental results show the method gives a good accuracy and resolution. However in the experiments randomly distributed multiple faults are injected which may not prove the capability of the proposed method in diagnosing multiple faults which are bounded in a local region which is common for a real single defect such as open or bridge defect.

#### 2.2.3.6 Diagnosis Multiple Physical Defects Using Logic

#### Fault Models

X. Tang and *et al.* [25] recently proposed a method to improve diagnosis results for multiple physical defects by analyzing the relations among the initial logical suspects and carefully choosing diagnostic metrics. Also a new set covering procedure and a ranking methodology for candidate sets were developed.

Diagnostic metrics are defined to measure how good a fault can explain the failures:

- SFTF: the number of failing bits that appear in both the test response of fault simulation and the failure that observed on the tester.

- SFTP: the number of observation points that fail in the fault simulation but pass on the tester.

- SPTF: the number of observation points that pass in the fault simulation but fail on the tester.

The method first identifies a set of initial stuck-at fault based on critical path tracing [14] and SLAT [18] patterns. SFTF, SFTP and SPTF are calculated for each suspect on the initial candidate list.

The next step is to derive physical defect from the obtained logic faults so as to explain the failing bits of the rest of unexplained patterns. Stuck-at faults that on the same interconnect net may be combined as a net-open fault, and faults that on the inputs and outputs of a gate may compose a cell internal fault. Bridge faults also can be derived from two or more logic locations that satisfy the excitation and propagation conditions. A metric, which is defined as  $\sigma'_T$  = sum of min(SFTF, SFTP) over all non-Type-3 failing patterns [19]. It is called a *seed* fault is  $\sigma'_T$  of the fault is 0. For a derived physical defect, only the failing patterns explained the component seed faults are counted. The final suspect selection is based on the Diagnosis Score = #EFP -  $\alpha \times$ #PMP, where #EFP is the number of explained failing patterns and #PMP is the number of passing mismatch patterns. Experimental results demonstrated the method can accurately identify the defect locations as well as the physical defect type.

#### 2.3 Review of Cell Internal Diagnosis

Conventional logic diagnosis can successfully determine the most likely locations and types of the defects by using effect-cause analysis. The location reported by the diagnosis tool usually is the net (nets for multiple faults) that connected to the input or output of gate. With the increasing complexity of the design along with the shrinking manufacturing size, a significantly number of manufacturing defects and systematic yield limiters reside in the internal of the gates. Therefore it is necessary for diagnosis tool to have the capability in finding the defects inside the cell. For physical failure analysis, the more detail results can accelerate the whole analysis process. Also finding out the cell internal detects can facilitate statistical yield learning to point out the systematic defects inside the library cells.

In this section, some previous works on cell internal diagnosis are briefly reviewed. The previous proposed cell internal diagnosis algorithms can be classified into two general categories [35]: logic level [26], [27], [28], [29], [30], [31], [32], [33] and physical level [34], [35].

#### 2.3.1 Logic Level Cell Internal Diagnosis

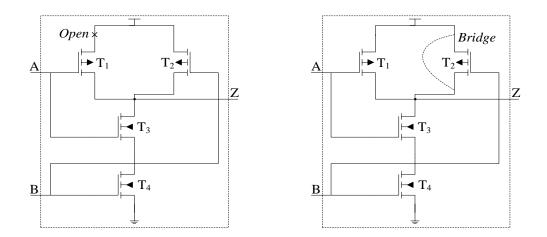

The defect models used for cell internal diagnosis usually are transistor stuckopen or transistor bridge defects extracted from the logical structure of the library cell without considering the real physical information of the cell. Below Figure 3 gives two examples for transistor stuck-open and bridge defects respectively for 2-inputs NAND library cell. The first example gives a stuck-open defect at the source of p-transistor T<sub>1</sub>. Because of this defect, the transistor T<sub>1</sub> cannot be charged properly when A = 0 and B = 1 and then the value on Z depends on the previous value on Z. This effect will not manifest itself as a stuck-at fault on input pin A or output Z thus using traditional stuck-at fault model based diagnosis may not find the internal defects. The second example presents a bridge fault between the source and drain of transistor T<sub>2</sub>. When A = 1 and B = 1, the value of the output Z is undetermined because of the short between source and drain of transistor T<sub>2</sub>. The traditional logic diagnosis which can only locate the possible locations of the defective library cells and cannot reach the internal defects will become inaccurate.

Li and et al. [26], [27], [28] first developed a methodology to diagnosis resistiveopen and stuck-open faults resides in internal transistors of the CMOS cell. Stuck-at fault mode first is used to find out the possible gates with stuck-at faults that could explain all the failing patterns. Then all the candidates obtained from logic diagnosis are fault simulated and for each candidate a fault signature (FS) table is generated. The FS table for a fault stores the failing pattern and failing bits when the fault is injected and simulated. Also logic simulation is performed and for each candidate the gat-input sequence (GIS) table is built in which all the input and output combinations of the applied test patterns are stored. For each library cell, a predefined excitation condition (EC) table is used to describe which input combination can excite which resistive open and stuck-open defects of the transistors inside the cell. Put these three tables together, we can know the possible stuck-open/resistive open detects (detected by the input combinations and sequences of the failing patterns) and also the failing bits caused by the present of each possible stuck-open/resistive open defect. Then final step is to greedily find a minimum set of stuck-open/resistive defects that can perfectly matching all the failing bits of the failing patterns.

Figure 3. Transistor Open and Bridge for 2-inputs NAND Cell

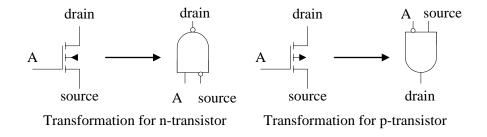

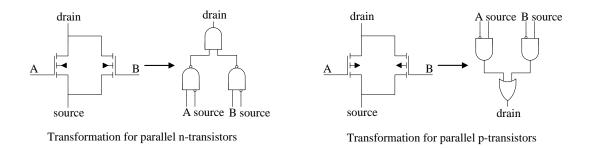

In order to avoid manually build up an excitation table for every type of library cells, researchers in [29], [30], [31] proposed a stuck-at fault model based method to diagnosis transistor stuck-open and transistor bridge defects. The first step of the proposed method is performing single stuck-at fault diagnosis. If the identified stuck-at faults can perfectly explain the failing patterns without passing mismatch, those faults are real stuck-at faults. Otherwise the gates with diagnosed stuck-at faults on the inputs or outputs are selected for future cell internal diagnosis. Instead of building an excitation table for each stuck-open/bridge fault for each library cell, the presented method transforms the gate from transistor level to gate level such that the stuck-open/transistor-

bridge defects can be converted into stuck-at/gate-bridge faults. After the gate transformation, new patterns are constructed from the previous and current input values of the transformed gates. For every pattern that detects that fault, the previous applied pattern is found. Then two consecutive patterns that present on the transformed gate are used to form a new pattern. Finally, the logic stuck-at/bridge diagnosis tool is applied on the transformed gates. And the stuck-at/bridge faults will be identified which can be mapped to stuck-open/bridge defects in the transistor level of the original gates. By doing so, the transistor stuck-open and bridge defects can be processed using any logic diagnosis tool. Below gives an example how a transistor can be converted to a gate.

Figure 4. Examples for Transformation of Single Transistor

Figure 5. Examples for Transformation of Parallel Transistors

Figure 4 gives the replacement of n/p-transistors. For the n-transistor, the replacement can guarantee that a zero voltage from the source will be transmitted to the drain when A = 1 and the values on the source and drain are equal. It is similar for the p-transistor. Following the same logic, the Figure 5 shows the replacement for two parallel connected n/p-transistors.

Figure 6. Complete Diagnosis Flow [32]

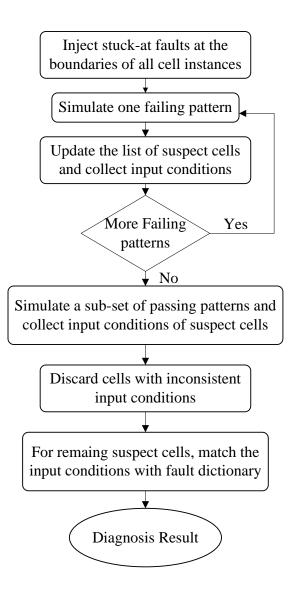

The work in [32] presents a mix-level diagnosis technique, which first performs diagnosis at logic level and then performs transistor-level analysis to locate defect at transistor level. The overall of the proposed mix-level diagnosis flow is given in Figure 6.

Figure 7. Test Patterns for Consistency Check

For each failing pattern, a number of suspect with stuck-at fault are identified which can explain that failing pattern. The suspect could potentially have cell internal defects and should be future checked. In order to find the possible internal defects in each suspect, the input conditions of the suspects are collected for that failing pattern. Those input conditions can determine a subset of internal defects that are detected by the input combinations. After diagnosing all the failing patterns, the suspects with stuck-at faults at the cell boundary can be obtained. A sub set of passing patterns are selected for further consistency check. Figure 7 shows the classification of all test patterns. If a stuck-at fault injected at the output of the suspect cell, then the internal defect was not excited on that test. Such passing pattern should be used for consistency check to remove some internal defects. The input combinations on the suspect cell are collected for all the selected passing patterns. With the failing input conditions and passing input conditions, the internal defect can be deduced. This is done by matching the pre-built switch level fault dictionary for the library cells.

The transistor level fault dictionary for each cell type stores the fault signatures for each internal defect for a giving input combination. The cell internal fault models involved include stuck-at fault mode, stuck-open fault model, and bridge fault model. All these fault models are based on the logic structure of the library cell. The inputs are exhaustively simulated for each internal defect, and its responses are recorded. Then together with the passing conditions and failing conditions, the most possible internal defects can be identified.

#### 2.3.2 Physical Level Cell Internal Diagnosis

The cell internal diagnosis results based on the defect models extracted from the logic level of the library cells may not accurately describe the real possible defects. Also some unknown defects may not be presented by the logic level defect models. All these can lead to inaccurate diagnosis results. In order to overcome this drawback, some previous works [34], [35] have been proposed in which physical information of the library cell is involved to more accurately capture the potential defects.

In [35], a fast cell internal diagnosis was proposed. The diagnosis method is based on the assumption that the excitation of a defect inside a cell is highly correlated to the logic values at the input pins of the cell. The excitation condition along with the SPICE or switch level simulation can determine the defect inside the cell. It pointed out that simply extracting the excitation condition from the failing patterns and passing patterns using the technique in [32] was able to correctly identify the defective cell in only 25% of the cases. This is mainly due to the multiple excitation conditions in the test pattern. With multiple excitation conditions, it is not easy to decide which excitation condition is the true excitation condition. Some excitation conditions may excite the defect but not propagate the fault effect. The multiple excitation conditions mainly come from three situations:

- Multiple cycles of the capture clock. Some faults many need multiple capture cycles to be active and detected. The multiple capture cycles in a test pattern can lead to multiple excitation conditions.

- Mixture of leading edge and failing edge in the design. When simulating test patterns for design with leading edge and trailing edge, a clock cycle is split into multiple simulation frames which can lead to multiple excitation conditions.

- Clock signal feeding into the system logic. The fault effect in the design can be captured by leading edge scan cells or observed at primary outputs when clocks are OFF. This is another set of exercising condition.

The works in [35] proposed an algorithm to heuristically the true failing and passing excitation conditions for each candidate cell when test patterns have multiple excitation conditions. Some terms are defined before giving the detail of the algorithm:

- **Observable Passing Pattern:** An observable passing pattern is defined with respect to a candidate defective library cell. If a passing pattern detects a stuck-at fault on the cell output pin then it is called an observable passing pattern for the cell.

- **Exercising Condition:** An input combination of a library cell in the design during the capture phase of a test pattern.

- Failing Exercising Condition: An exercising condition of a defective cell that actives the cell internal defect and propagates the faulty value to the cell output pins.

- **Passing Exercising Condition:** An exercising condition of a defective cell that does not excite the cell internal defect, or does not propagate the faulty value to the cell output pins.

The algorithm first extracts the Exercising Conditions Collection (ECC) for all the failing patterns and observable passing patterns. The ECCs are used to determine the actual failing and passing excitation conditions by using the following heuristic:

- All the excitation conditions are divided into three categories. Put excitation conditions that present only in failing pattern ECCs into failing excitation condition category. Excitation conditions that present only in observable passing patterns ECCs are passing excitation conditions. The rest of excitation conditions are undecided and will be processed in the following steps.

- For failing pattern ECCs, if it contains exactly one undecided exercising condition and no failing excitation condition, the undecided excitation condition will be labeled as failing excitation condition.

- For observable failing pattern ECCs, if it contains exactly one undecided exercising condition and no passing excitation condition, the undecided excitation condition will be labeled as passing excitation condition.

- If there are still some undecided exercising conditions, choose one which is associated with the largest number of observable passing patterns and put it into passing excitation condition category.

- If any undecided exercising condition was converted to a passing condition in Step 4, then go back to Step 2, otherwise terminate.

The results on controlled experiments show that the excitation condition extraction algorithm can correctly identify the passing and failing excitation conditions for 94% of the cases. For the remaining 6% of cases, a majority of failing and observable passing patterns have identical set of exercising conditions in which the method cannot handle.

#### 2.4 Logic Diagnosis Performance Improvement

A good logic diagnosis algorithm should not only accurately point out the location of the defects, but also produce the results within a reasonable short time with a reasonable amount of memory. This becomes more important when diagnosing a volume of failing devices. The throughput of volume diagnosis is defined as the number failing dies that could be processed within a time frame and with limited computational resource. Usually the time and space complexity of logic diagnosis (effect-cause) algorithm are linear to the number of gates in the circuit under diagnosis (CUD) as fault simulation and logic simulation is intensively used. With the increasing scale of the design the runtime and memory consumption keep growing which would lead to large impact on the throughput, thus the silicon debugging and yield learning will be slowed down.

In this section, several previous works on improving the performance of the logic diagnosis based on effect-cause paradigm will be briefly introduced [8], [9], [36], [37], [38].

#### 2.4.1 Circuit Partitioning [36]

The method presented in [36] reduced the number of simulation events required to diagnose a fault by logically partitioning the circuit into sub-circuits. The sub-circuits that include the potential defects are further partitioned into smaller sub-circuits until the desired resolution is met. The basic idea of the method is incrementally searching sub-circuits which could produce fault effects and the faults effects can be propagated to the failing primary outputs when the failing patterns are applied. Those sub-circuits could potentially contain the real defects that causing the failure.

The experiments were performed on single-stuck at fault and bridge fault. The results show the method has good diagnosis resolution and accuracy, and could reduce the number of faults that need to be simulated. However, this method may not be inapplicable for realistic defects which have multiple faulty locations. The reduction ratio

computed in the experiments assumed that all the faults should be simulated which might not be fair as the faults can be pruned by some techniques such as critical path tracing. And also the full circuit is simulated which may still have problem when the circuit becomes large.

# 2.4.2 Fault Dictionaries Based Methods to Accelerate

## Effect-Cause Diagnosis [8], [9], [37]

We know that cause-effect diagnosis paradigm is impractical for diagnosing large designs as the fault dictionary pre-built is too large to be accepted. However, one can build a fault dictionary of small size whose memory overhead is reasonable to speed-up the effect-cause diagnosis procedures [8], [9], [37].

Figure 8. Effect-Cause Diagnosis Flow [9]

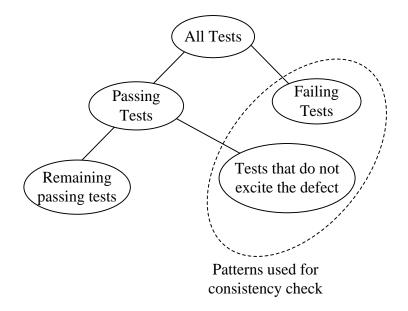

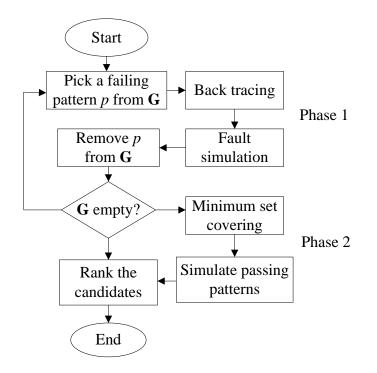

The effect-cause algorithm used in the previous works [8], [9], [37] has two phases as shown in Figure 8. In the first phase, critical-path tracing is employed to find the initial candidates and fault simulation is performed for the initial faults to further prune them. The second phase first using minimum set covering algorithm to find some sets of faults such that each set can perfectly explain all the failing patterns. These sets are simulated under the passing patterns and then ranked according the passing pattern mismatch results. Two runtime intensive works are involved for the described diagnosis procedure. The first one is the time for back tracing to find a set of initial candidates and fault simulating all the failing patterns with the obtained initial candidates. The second one is the runtime for the second phase for simulating all passing patterns.

In [9], a method was proposed to build a small dictionary used for determining the initial candidates that explain a failing pattern such that the CPU effort spend on back tracing can be avoided. Instead of recording the test response for each fault for each test pattern, a unique test response signature is stored by feeding the response into a 32-bit MSIR. Then the number of bits used to store the signatures for all the faults is  $32 \times U \times F$ , where U is average number of unique signatures for each fault and F is the number of faults. Besides this, for each fault the clocks which are used to capture the fault effects of that fault are stored. Then total fault dictionary size is  $32 \times U \times F + C \times F$  if there are C clocks. Then in the first phase, the initial candidates are obtained by looking up the fault dictionary instead of critical path tracing. It can reduce the runtime of the first phase in two aspects: 1) backward tracing is not used and dictionary look-up is fast; 2) during fault simulation the number of events triggered by the initial candidates obtained by fault dictionary is typically much smaller than that by the initial candidates found through critical path tracing. The second phase also can be improved by speed-up simulating the passing patterns. For simulating a fault, by the fault dictionary we can first find a subset of passing patterns that detect that fault. Therefore only a subset of passing patterns needs to be simulated instead of all the passing patterns. The clock information previously stored can be used to further reduce the number of passing patterns. Only the passing pattern which has at least one pulse clock for that fault is selected. The experimental results show that it can speed up effect-cause diagnosis by up to 156X without losing diagnosis accuracy.

Figure 9. Diagnosis Procedure Using Additional Dictionaries

While the method in [9] build the fault dictionary for all the faults may still require a large amount of memory for large design, the method in [8] future improve it by reducing the fault dictionary into a minimum size while still accelerating the effect-cause diagnosis without diagnosis accuracy loss. It is observed that for a design 98% of the failing patterns have 5 or less failing bits. Then a fault dictionary is used to store all unique response for each fault with  $N_{FB}$  failing bits or less. The dictionary is called  $N_{FB}$  *dictionary*. Since only the unique signatures for failing patterns with no more than  $N_{FB}$

failing bits are stored, the memory consumption is dramatically reduced. The fault dictionary can be further reduced by clustering faults in the fan-out free region (FFR) in a group and storing the unique signatures for that group. After the fault dictionary is built, to identify the initial candidates the fault dictionary is queried if the number of failing bits for a failing pattern is less  $N_{FB}$ , otherwise critical path tracing is invoked. The results show that the speed of effect-cause diagnosis can be improved to 3.5X and the memory reduction for storing the small fault dictionary is up to 27X comparing with [9].

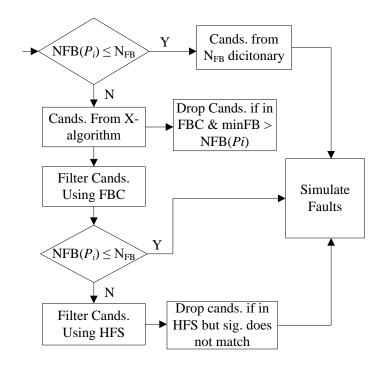

Based on the  $N_{FB}$  dictionary, the authors in [37] proposed two additional fault dictionaries: Failing Bit Count (FBC) Dictionary and Hyperactive Faults Signature (HFS) Dictionary. Two types of faults are defined: hypertrophic fault and hyperactive fault, where hypertrophic fault is a fault that causes many failing bits for a failing pattern and hyperactive fault is a fault with high number of simulation events. The FBC faults will not be found by N<sub>FB</sub> which require critical-path tracing, and HFS faults can cause lots of simulation events. Both FBC and HFS faults requires long simulation time. For FBC Dictionary, a pair ( $f_i$ , minFB( $f_i$ )) is entered for fault  $f_i$  that meet too conditions: 1) minFB( $f_i$ )  $\geq$  MINFB; and 2) Av\_Event( $f_i$ )  $\geq$  MINEVENT, where MINFB =  $N_{FB}$ +2, AV\_Event( $f_i$ ) is the average number of events caused by fault  $f_i$ , and MINEVENT is user specified minimum average event count. The entry in the HFS Dictionary is a 32-bit signature of a faulty test response and a set of associated faults.

Figure 9 gives the diagnosis flow based on the additional fault dictionaries. Basically it tries to identify some hyperactive and hypertrophic faults which could increase the simulation time by the FBC and HFS dictionaries. By doing this, the simulation events during critical path-tracing and fault simulation. Together with NFB dictionary, the proposed method can speed-up effect-cause diagnosis up to 13X by using additional small size FBC and HFS dictionaries.

#### 2.4.3 Machine Learning Based

The method proposed in [38] tries to diagnosis failing die with compression structures using machine learning techniques instead of conventional cause-effect and effect-cause analysis paradigms. It is based on the observation that defects in the same fault free region (FFR) have strong correlations in scan cells that capture the errors. Then each FFR can be considered as class, and the task for diagnosing the failing dies turns out to identify the FFR according the failing test response using classification methods. First training is performed with compressed output responses that are produced by different faulty circuits, where are done by injecting faults into each FFR (class) and simulating them with the given test patterns. A widely used machine learning method SVM [39] is employed to facilitate data training and classification. When diagnosing a failing flog, the SVM takes the failing response as an input and classifies into a FFR which may best fit for the test response. The experimental results show that the diagnosis success rate is more than 90% for circuit with 50x compression ratio. One potential problem with this method is that only single fault is considered and the present of multiple faults with fault effect masking may cause a problem. Also the training time for very large design may become extremely long.

# CHAPTER 3. DIAGNOSIS OF CELL INTERNAL DEFECTS WITH MULTI-CYCLE TEST PATTERNS

In this section, we present methodology to accurately diagnose cell internal defects when test patterns with multiple capture cycles are used [40].

#### 3.1 Introduction

When a chip fails test, fault diagnosis [1], [18], [21], [41] can determine the most likely faulty locations and fault types. Such information can be further utilized by yield learning [42], [43], [44] or physical failure analysis (PFA) procedures to find the root cause of the failure, and the yield can be improved by fixing the yield limiters. In order to speed-up PFA process or accurately learn the systematic yield issues, the faulty locations and fault types produced by fault diagnosis should be as close as possible to the real defect.

Traditionally fault diagnosis focuses on the defects that are present on the pins of a library cell or the interconnecting wires between library cells. We refer to these techniques as *gate-level diagnosis* techniques [1], [18], [21], [41]. With the integrated circuit manufacturing technology advancing to 65nm and smaller, there are a significant number of manufacturing defects and systematic yield limiters inside library cells [35] which are more complex than primitive gates. If a die fails due to cell internal defects, it is important to know the exact faulty locations inside the library cell. With such more accurate information, PFA process can be accelerated since fewer candidate locations are examined, and thus the overall cost of PFA is reduced. Furthermore, knowing the cell internal defect also greatly helps in collecting defect statistics that can point to systematic yield limiting issues in library cells. In contrast to gate-level diagnosis, the diagnosis technique used to determine the defects inside a cell is referred to as *cell internal diagnosis*. The existing works on cell internal diagnosis can be classified into two categories. The first category assumes some defect models in the transistor-level description of the cell, and then translates the transistor-level defects into gate-level defects [30], [31], [45]. By doing so, the conventional gate-level diagnosis tools can still work based on the converted gate-level net lists and the effort for developing new cell internal diagnosis techniques can be saved. One disadvantage of these techniques is that the success for identifying the real defects depends largely on the accuracy of the modified library cell model in representing all the realistic cell internal defects. In general, the model can cover switch-level logic defects but not sufficient for transistor-level physical defects.