Theses and Dissertations

Spring 2013

# Compaction mechanism to reduce test pattern counts and segmented delay fault testing for path delay faults

Sharada Jha University of Iowa

Copyright 2013 Sharada Jha

This dissertation is available at Iowa Research Online: http://ir.uiowa.edu/etd/2533

# Recommended Citation

Jha, Sharada. "Compaction mechanism to reduce test pattern counts and segmented delay fault testing for path delay faults." PhD (Doctor of Philosophy) thesis, University of Iowa, 2013. http://ir.uiowa.edu/etd/2533.

# COMPACTION MECHANISM TO REDUCE TEST PATTERN COUNTS AND SEGMENTED DELAY FAULT TESTING FOR PATH DELAY FAULTS

by

Sharada Jha

# An Abstract

Of a thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

May 2013

Thesis Supervisor: Professor Sudhakar M. Reddy

#### **ABSTRACT**

With rapid advancement in science and technology and decreasing feature size of transistors, the complexity of VLSI designs is constantly increasing. With increasing density and complexity of the designs, the probability of occurrence of defects also increases. Therefore testing of designs becomes essential in order to guarantee fault-free operation of devices.

Testing of VLSI designs involves generation of test patterns, test pattern application and identification of defects in design. In case of scan based designs, the test set size directly impacts the test application time which is determined by the number of memory elements in the design and the test storage requirements. There are various methods in literature which are used to address the issue of large test set size classified as static or dynamic compaction methods depending on whether the test compaction algorithm is performed as a post-processing step after test generation or is integrated within the test generation. In general, there is a trade-off between the test compaction achievable and the run-time. Methods which are computationally intensive might provide better compaction, however, might have longer run times owing to the complexity of the algorithm.

In the first part of the thesis we address the problem of large test set size in partially scanned designs by proposing an incremental dynamic compaction method. Typically, the fault coverage curve of designs ramp up very quickly in the beginning and later slows down and ultimately the curve flattens towards the tail of the curve. In the initial phase of test generation a greedy compaction method is used because initially there are easy-to-detect faults and the scope for compaction is better. However, in the later portion of the curve, there are hard-to-detect faults which affect compaction and we propose to use a dynamic compaction approach. We propose a novel mechanism to identify redundant faults during dynamic compaction to avoid targeting them later. The

effectiveness of method is demonstrated on industrial designs and test size reduction of 30% is achieved.

As the device complexity is increasing, delay defects are also increasing. Speed path debug is necessary in order to meet performance requirements. Speed paths are the frequency limiting paths in a design identified during debug. Speed paths can be tested using functional patterns, transition n-detect patterns or path delay patterns. However, usage of functional patterns for speed path debug is expensive because generation of functional patterns is expensive and the application cost is also high because the number of patterns is large and requires functional testers.

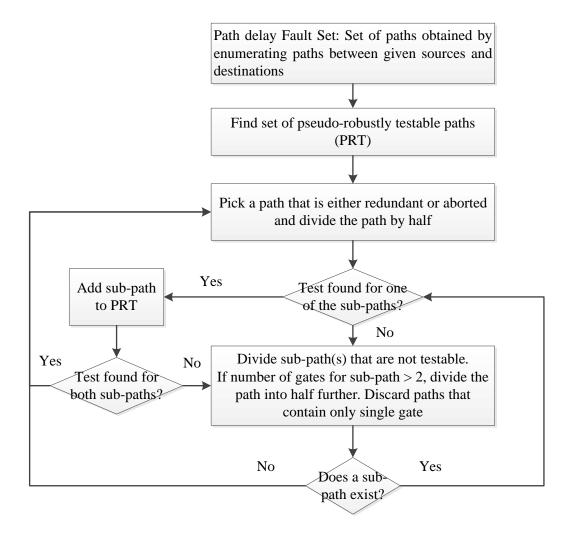

In the second part of the dissertation we propose a simple path sensitization approach that can be used to generate pseudo-robust tests, which are near robust tests and can be used for designs that have multiple clock domains. The fault coverage for path delay fault APTG can be further improved by dividing the paths that are not testable under pseudo robust conditions, into shorter sub-paths. The effectiveness of the method is demonstrated on industrial designs.

| Abstract Approved: |                      |  |

|--------------------|----------------------|--|

| 11                 | Thesis Supervisor    |  |

|                    | •                    |  |

|                    |                      |  |

|                    | Title and Department |  |

|                    | -                    |  |

|                    |                      |  |

|                    | Date                 |  |

# COMPACTION MECHANISM TO REDUCE TEST PATTERN COUNTS AND SEGMENTED DELAY FAULT TESTING FOR PATH DELAY FAULTS

by

Sharada Jha

A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

May 2013

Thesis Supervisor: Professor Sudhakar M. Reddy

Copyright by

SHARADA JHA

2013

All Rights Reserved

# Graduate College The University of Iowa Iowa City, Iowa

| CE                      | RTIFICATE OF APPROVAL                                                                                  |             |

|-------------------------|--------------------------------------------------------------------------------------------------------|-------------|

|                         | PH.D. THESIS                                                                                           |             |

| This is to certify that | t the Ph.D. thesis of                                                                                  |             |

|                         | Sharada Jha                                                                                            |             |

| for the thesis require  | by the Examining Committee ement for the Doctor of Philosophy and Computer Engineering at the May 2013 | graduation. |

| Thesis Committee:       | Sudhakar M. Reddy, Thesis Supervisor                                                                   |             |

|                         | David R. Andersen                                                                                      |             |

|                         | Mona K. Garvin                                                                                         |             |

|                         | Jon G. Kuhl                                                                                            |             |

|                         | Hantao Zhang                                                                                           |             |

To My Family

#### **ACKNOWLEDGMENTS**

I would like to extend my sincere gratitude and appreciation to all those who have challenged, supported and encouraged me in the entire course of PhD. First of all, I am deeply grateful to my thesis advisor, Professor Sudhakar Reddy and would like to extend my gratitude for all the expert guidance, valuable professional advice and help throughout my thesis. To work with him was a great opportunity for me and has been a great learning experience. He has been a constant support throughout the various phases of PhD. I would like to thank the dissertation committee members Professor David R. Andersen, Professor Mona K. Garvin, Professor Jon G. Kuhl and Professor Hantao Zhang for their time and effort for my dissertation. It is an honor for me to have them as my committee members.

I would like to express my sincere appreciation to Ramesh Sharma, Sanjay Sengupta, Yonsang Cho, Kameshwar Chandrasekar and Weixin Wu at Intel who guided and extended their valuable knowledge which helped me in my research work.

I would like to thank my colleagues Xiaoxin Fan, Amit Kumar, Joseph Howard and others at University of Iowa who made my stay at Iowa an enjoyable one. I would particularly like to thank my friends Swathi Kode, Hema Kumari Achanta and Pallavi Marrapu for all their help and support.

I would like to express my deepest and everlasting gratitude to my parents and my brothers for their love, support and encouragement throughout my life.

I would like to specially thank my husband, Saroj Kumar Jha, for his love, care and encouragement. His contribution towards my thesis is immeasurable.

#### **ABSTRACT**

With rapid advancement in science and technology and decreasing feature size of transistors, the complexity of VLSI designs is constantly increasing. With increasing density and complexity of the designs, the probability of occurrence of defects also increases. Therefore testing of designs becomes essential in order to guarantee fault-free operation of devices.

Testing of VLSI designs involves generation of test patterns, test pattern application and identification of defects in design. In case of scan based designs, the test set size directly impacts the test application time which is determined by the number of memory elements in the design and the test storage requirements. There are various methods in literature which are used to address the issue of large test set size classified as static or dynamic compaction methods depending on whether the test compaction algorithm is performed as a post-processing step after test generation or is integrated within the test generation. In general, there is a trade-off between the test compaction achievable and the run-time. Methods which are computationally intensive might provide better compaction, however, might have longer run times owing to the complexity of the algorithm.

In the first part of the thesis we address the problem of large test set size in partially scanned designs by proposing an incremental dynamic compaction method. Typically, the fault coverage curve of designs ramp up very quickly in the beginning and later slows down and ultimately the curve flattens towards the tail of the curve. In the initial phase of test generation a greedy compaction method is used because initially there are easy-to-detect faults and the scope for compaction is better. However, in the later portion of the curve, there are hard-to-detect faults which affect compaction and we propose to use a dynamic compaction approach. We propose a novel mechanism to identify redundant faults during dynamic compaction to avoid targeting them later. The

effectiveness of method is demonstrated on industrial designs and test size reduction of 30% is achieved.

As the device complexity is increasing, delay defects are also increasing. Speed path debug is necessary in order to meet performance requirements. Speed paths are the frequency limiting paths in a design identified during debug. Speed paths can be tested using functional patterns, transition n-detect patterns or path delay patterns. However, usage of functional patterns for speed path debug is expensive because generation of functional patterns is expensive and the application cost is also high because the number of patterns is large and requires functional testers.

In the second part of the dissertation we propose a simple path sensitization approach that can be used to generate pseudo-robust tests, which are near robust tests and can be used for designs that have multiple clock domains. The fault coverage for path delay fault APTG can be further improved by dividing the paths that are not testable under pseudo robust conditions, into shorter sub-paths. The effectiveness of the method is demonstrated on industrial designs.

# TABLE OF CONTENTS

| LIST OF | TABLES                                                        | viii |

|---------|---------------------------------------------------------------|------|

| LIST OF | FIGURES                                                       | ix   |

| СНАРТЕ  | R                                                             |      |

| 1.      | INTRODUCTION                                                  | 1    |

|         | 1.1 Motivation                                                | 1    |

|         | 1.2 Background                                                |      |

|         | 1.2.1 Fault Models                                            |      |

|         | 1.2.2 Test Generation.                                        |      |

|         | 1.2.3 Design for Testability                                  |      |

|         | 1.3 Organization of Thesis                                    |      |

| 2.      | INCREMENTAL DYNAMIC COMPACTION TECHNIQUE                      |      |

| ۷.      | INCREMENTAL DINAMIC COMPACTION TECHNIQUE                      | 9    |

|         | 2.1 Introduction                                              | 9    |

|         | 2.2 Review of Previous Work                                   | 11   |

|         | 2.2.1 Reverse Order Fault Simulation                          | 11   |

|         | 2.2.2 Forward-looking reverse order fault simulation          | 12   |

|         | 2.2.3 Reverse Order Test Compaction (ROTCO)                   | 12   |

|         | 2.2.4 COMPACTEST                                              |      |

|         | 2.2.5 Double Detection                                        | 19   |

|         | 2.2.6 Essential Fault Reduction Method                        | 21   |

|         | 2.2.7 Dynamic Test Vector Compaction                          | 25   |

|         | 2.3 The Proposed Method                                       |      |

|         | 2.3.1 Motivation                                              | 26   |

|         | 2.3.2 Preliminaries                                           |      |

|         | 2.3.3 Incremental Dynamic Compaction Approach                 |      |

|         | 2.3.4 Improving run time by Static Untestability Analysis     |      |

|         | 2.3.5 Reasoning Analysis to drop redundant faults             |      |

|         | 2.3.6 Automatic Identification of Parameters for Dynamic      |      |

|         | Compaction                                                    |      |

|         | 2.4 Experimental Results                                      | 42   |

|         | 2.4.1 Comparison of basic incremental dynamic compaction over |      |

|         | cube merging technique                                        | 42   |

|         | 2.4.2 Comparison of basic incremental dynamic compaction with |      |

|         | static untestability analysis over cube merging technique     | 45   |

|         | 2.4.3 Comparison of incremental dynamic compaction with       |      |

|         | automatic parameter identification method with cube           | 4 ~  |

|         | merging technique                                             |      |

|         | 2.5 Conclusion                                                | 50   |

|     | 3.   | PATH DELAY FAULT TESTING WITH SEGMENTED FAULT                    |    |

|-----|------|------------------------------------------------------------------|----|

|     |      | MODEL                                                            | 52 |

|     |      | 3.1 Introduction                                                 | 52 |

|     |      | 3.2 Preliminaries                                                |    |

|     |      | 3.3 Review of Previous Work                                      |    |

|     |      | 3.3.1 PODEM based Test generation for Path Delay Faults          |    |

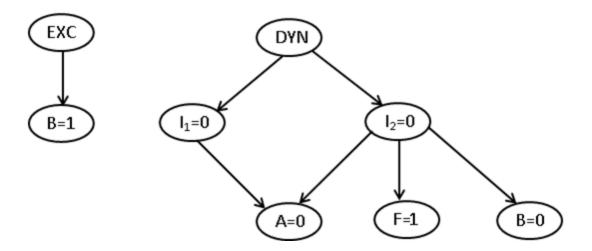

|     |      | 3.3.2 DYNAMITE                                                   |    |

|     |      | 3.3.3 Test Generation for Path Delay Faults in Non-scan Circuits | 61 |

|     |      | 3.3.4 NEST: A Non-enumerative Test Generation Method             | 64 |

|     |      | 3.3.5 Segment delay fault model                                  | 66 |

|     |      | 3.4 The Proposed Method                                          |    |

|     |      | 3.3.1 Motivation                                                 |    |

|     |      | 3.3.2 Test Generation Methodology                                | 70 |

|     |      | 3.3.3 Segment Delay Fault Testing to Improve Fault Coverage      | 78 |

|     |      | 3.5 Experimental Results                                         | 81 |

|     |      | 3.6 Conclusion                                                   |    |

|     | 4.   | CONCLUSIONS AND FUTURE RESEARCH                                  | 86 |

|     |      | 4.1 Conclusions                                                  | 86 |

|     |      | 4.2 Future Work                                                  |    |

| REF | EREI | NCES                                                             | 89 |

# LIST OF TABLES

| ٠. | l'able |                                                                                                                 |    |

|----|--------|-----------------------------------------------------------------------------------------------------------------|----|

|    | 2.1    | Before and after reverse order test compaction                                                                  | 13 |

|    | 2.2    | Example of double detection                                                                                     | 21 |

|    | 2.3    | Approximate size of designs                                                                                     | 43 |

|    | 2.4    | Results for incremental dynamic compaction vs. cube merging technique                                           | 43 |

|    | 2.5    | Maximum coverage achieved with cube merging and incremental dynamic compaction                                  | 44 |

|    | 2.6    | Comparison of BDR and BDR+SUA approach                                                                          | 44 |

|    | 2.7    | Comparison of results for API vs. cube merging technique for 32 bin size                                        | 47 |

|    | 2.8    | Maximum coverage achieved with API and cube merging for 32 bin size                                             | 47 |

|    | 2.9    | Parameter selection for API method for 32 bin size                                                              | 48 |

|    | 2.10   | Comparison of results for API(256 bin size) vs. cube merging technique (at 256 and 1000 bin size base coverage) | 49 |

|    | 2.11   | Test size reduction, run-time overhead and maximum coverage achieved with API and cube merging                  | 50 |

|    | 3.1    | Robust propagation requirements (output)                                                                        | 66 |

|    | 3.2    | Fault Statistics                                                                                                | 81 |

|    | 3.3    | Fault Statistics for path delay ATPG with segmented path delay faults                                           | 83 |

|    |        |                                                                                                                 |    |

# LIST OF FIGURES

| т. |     |     |

|----|-----|-----|

| Η1 | OII | ıre |

|    | 54  |     |

| 1.1  | Manufacturing test of a circuit                                   | 6  |

|------|-------------------------------------------------------------------|----|

| 1.2  | Scan based design                                                 | 7  |

| 2.1  | Example for maximal compaction                                    | 17 |

| 2.2  | EFR example                                                       | 24 |

| 2.3  | Test $T_i$ : X10 recording                                        | 25 |

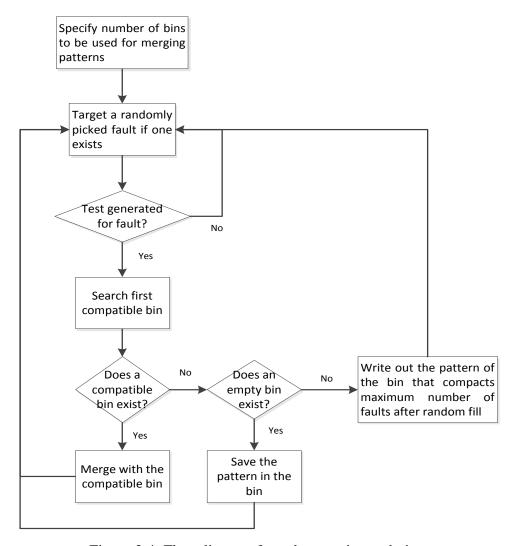

| 2.4  | Flow diagram for cube merging technique                           | 29 |

| 2.5  | Example for Cube Merging                                          | 30 |

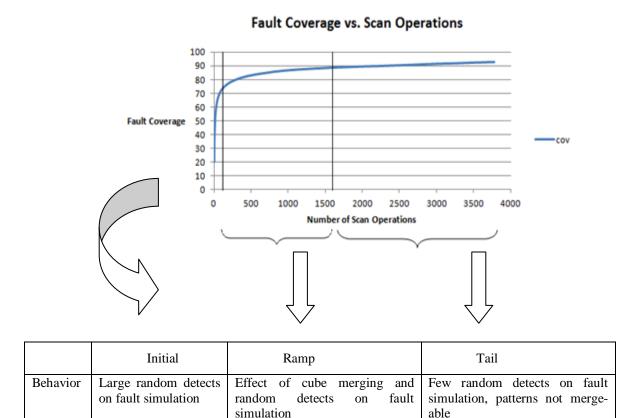

| 2.6  | An Example Fault Coverage Curve.                                  | 31 |

| 2.7  | An example circuit showing a redundant fault                      | 36 |

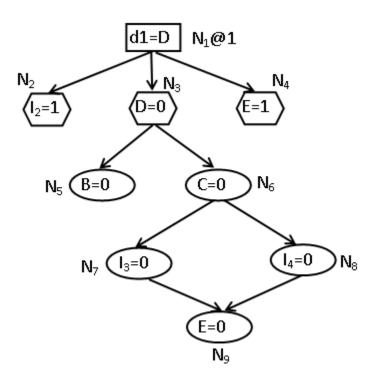

| 2.8  | Implication graph generated during ATPG for testing d1 s-a-1      | 37 |

| 2.9  | Implication graph generated during incremental dynamic compaction | 38 |

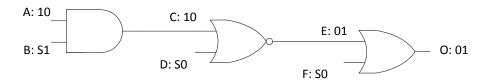

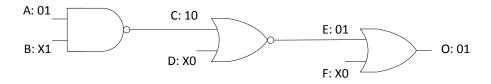

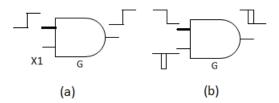

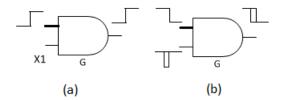

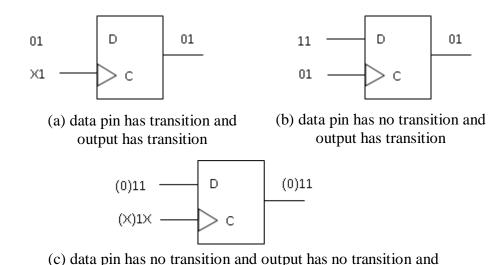

| 3.1  | Transition fault Model.                                           | 54 |

| 3.2  | Robust Sensitization                                              | 55 |

| 3.3  | Non-robust Sensitization                                          | 56 |

| 3.4  | Pseudo-robust sensitization of AND gate                           | 57 |

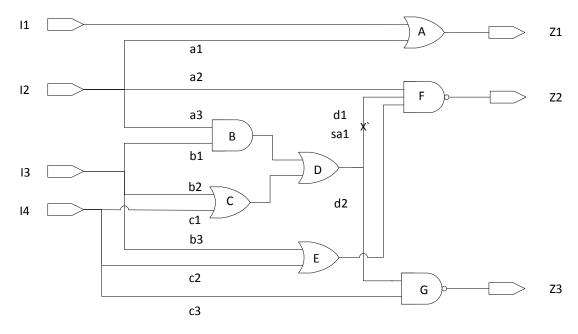

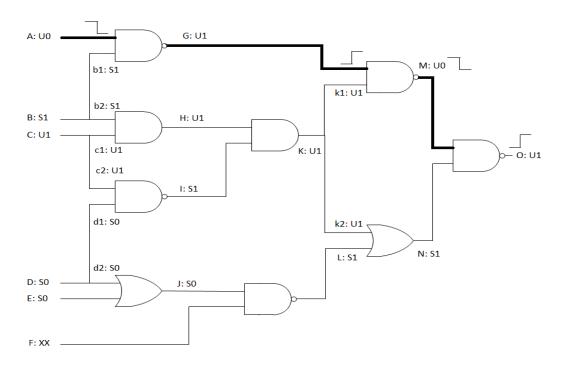

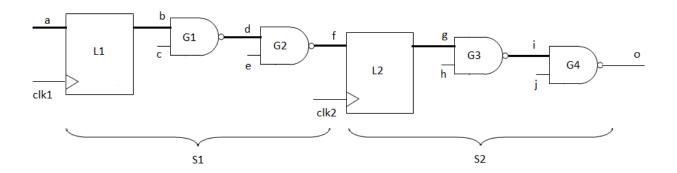

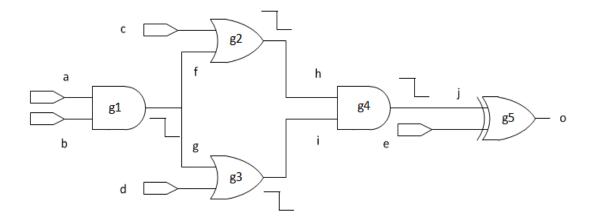

| 3.5  | An example circuit                                                | 58 |

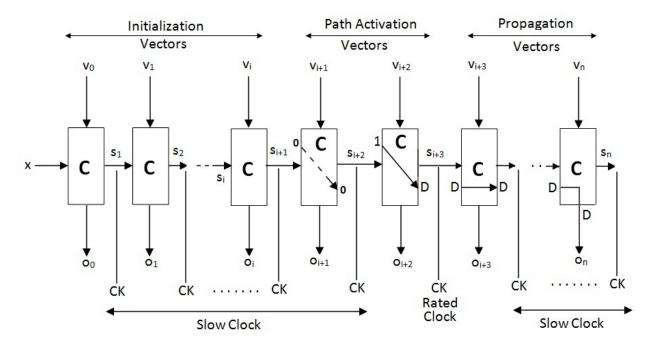

| 3.6  | Testing for path delay fault                                      | 62 |

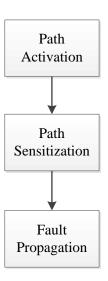

| 3.7  | Atpg Flow                                                         | 67 |

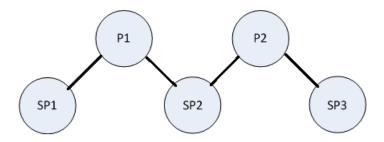

| 3.8  | Example path delay fault                                          | 71 |

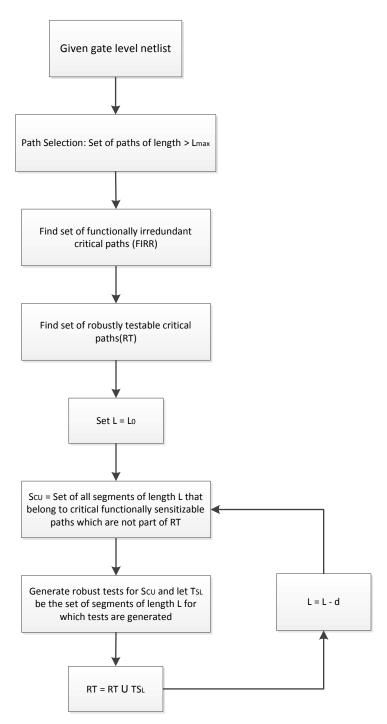

| 3.9  | Overall Test Generation Flow.                                     | 72 |

| 3.10 | Pseudo-robust conditions for AND gate                             | 73 |

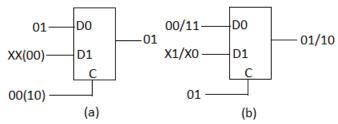

| 3.11 | Pseudo-robust conditions for MUX gate                             | 74 |

| 3.12 | Pseudo-robust sensitization of D-latch for rising transition at data pin | .76 |

|------|--------------------------------------------------------------------------|-----|

| 3.13 | Path sensitization with Sustaining.                                      | .78 |

| 3.14 | Overall flow for Segmented Delay Fault Testing.                          | .79 |

| 3.15 | An example circuit depicting paths that are robustly untestable          | .80 |

| 3.16 | Tree structure for path storage                                          | .80 |

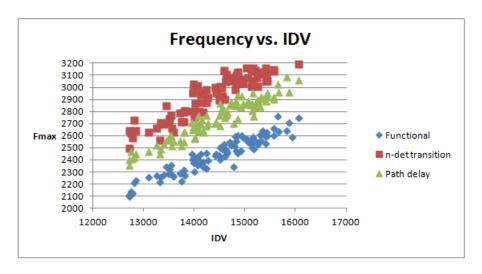

| 3.17 | Frequency versus IDV.                                                    | .83 |

#### CHAPTER 1 INTRODUCTION

With the advancement in science and technology, the VLSI designs today are becoming more complex day by day. Testing of manufactured chips is very essential as it directly impacts the cost. There are various types of errors – design errors, fabrication errors, fabrication defects and physical failures. Design errors could be because of incomplete or inconsistent specification, design rule violations. Fabrication errors can be caused by wrong components, improper wiring, and improper soldering that could lead to shorts of interconnects. Fabrication defects happen due to imperfections in manufacturing process. Physical failure can happen during the lifetime of a system attributed to wear-out or environmental factors or process variations. Apart from these types of errors coding bugs also can lead to incorrect design and can cause errors. Thus it becomes essential to test the devices for any defects after manufacturing.

#### 1.1 Motivation

In this work we address two issues related to testing devices for failures – (i) large test set size which impacts test application time and test storage requirements and (ii) usage of functional patterns for speed path debug which is very expensive.

With increasing device complexity, testing complexity increases which in turn increases cost of testing. Testing scan-based designs demands smaller test set sizes because the test application time for such circuits directly depends on the number of memory elements in the schips in a given amount of time and thus fewer testers would be needed. Test pattern compaction plays a very important role in reducing the cost of testing very large designs by reducing the test application time. This also impacts the storage requirements of the test patterns in the testing hardware. In order to address this issue, we propose a dynamic compaction technique which reduces the test pattern size.

The second issue that is addressed in this work is identifying speed path failures in design to meet high performance requirements. Generation of functional patterns for all the critical paths is difficult and expensive. Functional patterns when used for speed path debug have the disadvantage of long times for debug since functional patterns typically are long and may take several cycles to reach an observed point. Therefore test patterns for path delay faults can be used to address this issue. Typically the robust fault coverage is very low for designs and thus it is not possible to cover all critical paths with robust tests. To address this issue, a method of dividing a path into sub-paths and generating tests for the sub-paths is proposed.

Section 1.2 discusses various fault models and the test generation process.

#### 1.2 Background

#### 1.2.1 Fault Models

Physical defects occur in chips during the chip fabrication process. There can be various types of defects like signal line breaks, lines shorted to ground, delayed signal propagation, etc. As there is a huge number of types of defects it is very difficult to generate tests for all types of defects. Defects may or may not cause device failure. A fault is a representation of a defect at the abstracted function level [2]. A good fault model reflects the behavior of the defects closely and is easy to analyze. It also should be computationally effective in fault simulation and test generation process [3]. Fault models are technology independent and thus changes in technology do not change the test generation for the faults. The different types of fault models are stuck-at fault model, bridge fault model, transition fault model, path delay fault model, open and short fault model, some of which are described below:

#### Stuck-at fault model:

Stuck-at fault model is one of the earliest fault models and has been used for a very long time. A stuck-at fault is a fault that forces a constant logic value (1

or 0) on a signal line in the circuit, called stuck-at-1 or stuck-at-0 [5]. A short between the signal line and ground line is modeled by a stuck-at-0 fault and a short between a signal line and power line is modeled by a stuck-at-1 fault. The signal line can be a primary input, primary output, inputs and outputs of internal gates, fanout stems and fanout branches. A circuit that has n lines can have 2n single stuck-at faults and  $3^n - 1$  possible multiple stuck-at fault combinations [2, 4]. Stuck-at fault model is used in the current work for test pattern compaction. However, the technique is independent of the underlying fault model.

#### • Bridge fault model:

Bridge fault model is another important fault model. This is a commonly occurring type of fault. A bridge fault occurs when two signal lines are shorted unintentionally [6][7]. The shorts have a finite resistance. A bridge fault affects the voltage on both the signal lines involved in a bridge. Modeling and test generation of bridges is a challenging issue and thus there are several simplified models that have been developed for test generation. The wired AND/wired OR bridge fault model a short defect between two signal lines where the bridged nodes take a logic value which is the AND (OR) of the bridged signal lines. The four-way bridge fault model models various scenarios where the effect of the bridge fault depends on the relative strengths of the gates involved in the bridge [8].

#### • Transition fault model:

In the transition fault model, the time taken for a transition from input of gate to its output exceeds the specified limit [9]. The number of transition faults in a circuit is linear to the number of circuit lines. Just as the stuck-at fault model, there are two types of transition faults – slow-to-rise and slow-to-fall. A two pattern test is required to activate a transition fault, where the first

pattern sets the fault site to the initial value and the second pattern is required to launch the transition and once the fault is activated, it is propagated to an output.

# • Path delay fault model:

The path delay fault models the cumulative effect of the delays along a path in the circuit. If the cumulative delay exceeds the clock period for the path, then the test pattern that fails the chip is said to detect the path delay fault. A two pattern test is required to detect a path delay fault [1] which creates a transition at the input of the path. The transition at the input of the path is propagated along the path by satisfying necessary off-path conditions.

#### 1.2.2 Test Generation

Test generation is the process of generating an effective set of test patterns by which a high fault coverage can be achieved for a given fault model. The main objective of test generation is to generate patterns that will detect defects in a chip. Since the number of defects in a circuit is really large and generating test for all of them would be unrealistic, test pattern generators target the faults which are an abstract representation of defects. Test pattern generation consists of the following steps —

#### • Fault activation:

Fault activation sets the signal value on a line opposite to that produced by the fault at the faulty site in the faulty circuit. For example, in order to activate a stuck-at 1 fault on line l, 0 needs to be assigned to line l in order to excite the fault.

# • Fault propagation:

This is the second phase where the fault effect is propagated by sensitizing at least one path from the fault site to a primary output or a scan cell. In order to propagate the fault effect from the fault site, there could be one or more gates

through which the fault effect can be propagated. These choices are called as d-frontiers. D-frontiers are gates that have an output value of X and have a fault effect on at least one of the inputs. The fault effect is propagated by assigning non-controlling values to inputs other than the input that has the fault effect. In order to propagate the fault effect from a fault site to an output, there should be at least one x-path between the two nodes. An x-path is a path between two gates of a circuit where the output value of all the gates is X. If there exists no x-path between the fault site and any primary output or scan cell, then a test cannot be generated for the fault.

#### • Justification:

Justification is the process of specifying primary input values or scan cell values in order to produce the signal values required for fault activation and fault propagation. The justification process is carried out by assigning necessary values at the inputs of gates for which the output values are specified to be 1 or 0 during fault activation and propagation, but are not implied by the input values. The set of all such gates is called as j-frontier.

The effectiveness of the test set produced is measured in terms of fault coverage for the given fault model, the number of test patterns generated. The number of test vectors generated directly impacts the test application time.

### 1.2.3 Design for Testability

Test costs can be attributed to test pattern generation, fault simulation, generation of fault location information, test equipment cost, cost related to testing process which is the time required to detect and/or isolate a fault. The costs associated with testing could be high and can even exceed design costs. In order to limit the testing costs and to simplify testing a device, design for testability (DFT) techniques are used to ensure that a device is testable. Controllability and observability play an important role in generating a

test for a circuit. Controllability is the ability to obtain a required signal value at each gate in a circuit by setting certain values on the circuit's inputs. Observability is the ability to determine a signal value at on any gate of the circuit by controlling the inputs of the circuit and observing its outputs.

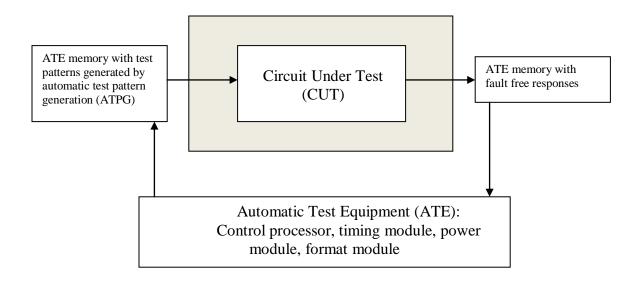

Basic testing infrastructure consists of three components: circuit under test, automatic test equipment (ATE) and ATE memory to store test patterns and expected test responses obtained by automatic test pattern generation (ATPG) tools as shown in Figure 1.1. In order to test a given circuit (CUT), test patterns are applied at the inputs of the circuit and the output values obtained are compared with the test responses stored in the ATE memory. A circuit is considered to be fault free if the output response of the circuit matches with the output response stored in the ATE.

Figure 1.1 Manufacturing test of a circuit [54]

Testing combinational circuit is easier than testing sequential circuits since the primary inputs can be set to required values and primary outputs can be observed. Testing

sequential designs is challenging because it takes several test cycles to get desired values on latches or flip-flops. This can also lead a large number of faults being untestable. In order to cope with low controllability and observability of sequential designs, design for testability (DFT) techniques is employed. The testability of a device improves with DFT methods since it enhances the controllability and observability of sequential elements. This is achieved by introducing scans in the design.

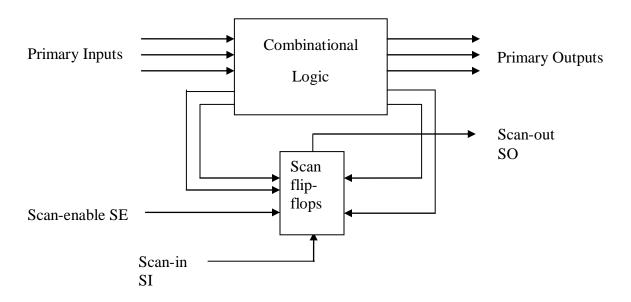

Scan design is the most widely used structured DFT method that is used to improve the controllability and observability of the storage elements in sequential design. This is achieved by converting the sequential design into a scan design and the design is operated in functional mode and test modes. In functional mode, the circuit operates in functional configuration by turning off all the test signals. During test mode, a test mode signal is applied which converts all the flip-flops in the design into one or more shift registers called scan chains. This improves the controllability of the flip-flops as they can now be set to desired state during the test mode by shifting in appropriate values.

Figure 1.2 Scan based design

The observability of the flip-flops is also enhanced since the states of the flip-flops can be observed by shifting out the content of the scan chains.

There are two types scan designs: full scan and partial scan designs. In full-scan design all the storage elements are converted into scan cells and combinational ATP can be used for test generation. In partial scan designs a portion of the storage elements is converted into scan cells and sequential ATPG is required for test generation since the design is still sequential since the complete design is not converted into scan design. The designs used in the current work are partially scan designs.

# 1.3 Organization of the Thesis

The thesis is organized as follows. Chapter 2 presents a dynamic compaction technique to address large test pattern size. Chapter 3 presents path delay fault test generation methodology in partially scanned designs and method to improve robust fault coverage. Chapter 4 draws the conclusions.

# CHAPTER 2 INCREMENTAL DYNAMIC COMPACTION TECHNIQUE

In this chapter we review various compaction techniques in the literature and present an incremental dynamic compaction approach to reduce test pattern size. In order to address the long run times of the approach we also present a static untestability and reasoning analysis method based on [15, 56]. Experimental results on industrial designs demonstrate the effectiveness of this technique.

### 2.1 Introduction

Earlier the major focus of research was to generate a complete test set efficiently for a given design. Several test generation algorithms have been proposed over the years [11-15]. Over the past two decades, the effort is directed towards minimizing the size of the test pattern set produced. The problem of finding the minimum test size for an irredundant combinational circuit by itself is proven to be NP-hard [17]. There are several compaction algorithms in the literature that are based on various heuristics, for example – test generation based on independent fault set and compatible fault sets[19-21], double detection[19, 22], reverse order fault simulation[23], rotating backtrace[20]. Every new methodology is targeted towards getting better test size reduction and thus closing the gap further to the lower bound.

The size of the test set directly impacts the test storage requirements and test application time, especially for circuits using scan design. The test application time is directly proportional to the product of the number of test patterns and the number of scan cells in the longest scan chain [19]. This necessitates generation of small test sets.

The complexity of the compaction process plays an important role in test compaction. There are computation-intensive procedures proposed in the literature that produce minimal size test sets close to the lower bound [21, 24, 25]. For instance, in [9] tests are generated repeatedly which can detect several faults at the same time so as to

replace previous tests found. Though these methods produce small test sets, they are not suitable to large designs. Methods based on simple and efficient heuristics can be found in [20, 23, 26].

Test pattern compaction is aimed at generating a pattern set in which a test detects as many faults as possible. There are two ways of compaction – static and dynamic and are described below.

# • Static Compaction

Static compaction is applied as a post processing step to already generated test sets, to reduce the test set size further and therefore is independent of the test generation process. Static compaction is performed after all the patterns are generated and this is independent of test generation.

# • Dynamic compaction

Dynamic compaction is incorporated within the test generation process where a test cube is generated for a fault and the generated test cube is added as constraints to the next targeted fault. The advantage of dynamic compaction over static compaction is that it reduces the time required for post-processing step for compacting patterns. The dynamic compaction begins with a fault which is on top of previously ordered fault list, called as primary fault. The primary fault is targeted for test generation and if a test is generated for the fault, another fault called secondary fault is picked and a test generation for the fault is attempted. The test generation tries to generate a test for the secondary fault with the primary input values and scan cell values specified by previously generated test vector. The test generation for the secondary fault specifies only the unspecified values remaining from the previous test vector. This process is repeated for all the remaining faults remaining in the fault list or all the inputs are specified [20]. The unspecified inputs of the resulting test vector at the end are then random filled with 1s and 0s. This process is repeated with a different primary fault and the

entire process of is repeated with remaining secondary faults and the process continues until all the faults in the fault list are tried as primary faults.

#### 2.2 Review of Previous Work

In this section below, some of the static and dynamic compaction methods are reviewed from literature.

#### 2.2.1 Reverse Order Fault Simulation

Reverse order fault simulation is a very simple and effective method of compacting test patterns. The test patterns are simulated in reverse order of test generation, wherein a test that was generated later is simulated earlier [5]. If a test does not detect any new faults when it is simulated, then the test is dropped from the test set. Reverse order fault simulation is a widely used static compaction technique [23, 28] suitable for combinational ATPG. But reverse order simulation is most beneficial when applied to effective tests. Effective tests are obtained by simulating a test set in the order in which it was generated with fault simulation used for fault dropping. A test generated by deterministic test generation method is fault simulated to drop the faults it detects and thus every new test detects faults not detected by previous tests. If the test set is generated by non-deterministic method like random test generation, fault simulation with fault dropping needs to be additionally done so as to get effective tests. Once the effective tests are obtained, these can be used for reverse order fault simulation. However, if the additional pass of fault simulation is not applied to non-deterministic patterns, the reverse order simulation would only identify effective tests of the test patterns in the reverse order which would not achieve as much test size reduction as obtained when applied to effective tests [29].

# 2.2.2 Forward-looking reverse order fault simulation

Forward-looking reverse order fault simulation [29] is an improvement over reverse order fault simulation. This method records the information about the first test in the test set that detects a fault for the first time. This is obtained by simulating the test set in the order in which it was generated combined with fault dropping. With this information, tests can be further dropped during reverse order fault simulation. This can be illustrated as follows. Consider a test set  $T=\{t_0,\,t_1,\ldots,\,t_{n\text{-}1}\}$  and let  $F=\{f_0,\,f_1,\ldots,\,f_{p\text{-}1}\}$ be the set of target faults. During forward looking reverse order fault simulation, every test in T is simulated in the reverse order with fault dropping similar to reverse order fault simulation. Before simulating a test t<sub>i</sub>, it is first determined whether it is necessary to simulate a pattern, and if it is not necessary then it is dropped without simulating the pattern. The decision to ascertain whether a test t<sub>i</sub> is necessary or not is based on the information of the first test that detects each test during the original order. Let the detection vector index of a test that detects a fault for the first time during forward order be denoted as detindex (f<sub>i</sub>). This can be obtained during fault simulation of F. During forward looking reverse order fault simulation, before simulating a test, the detection vector index of every fault  $fi \in F$ , is compared against the current test index. If the current test index i is greater than the detection vector index of all the faults in F, then the test is dropped without simulating it because the faults that will be detected by the test t<sub>i</sub> will be detected by later tests during reverse order fault simulation. If a fault  $fi \in F$  is such that the detection vector index of  $f_i$  is the same as current test index, then the pattern is simulated because there will be no further tests that would detect f<sub>i</sub>

# 2.2.3 Reverse Order Test Compaction (ROTCO)

Reverse Order Test Compaction[27] is a method similar to reverse order fault simulation in [23] but with the difference that the test vectors are allowed to be "modified" in the process, thereby increasing the possibility of detecting faults that were

detected by earlier test vector which could potentially result in a smaller test set. This is based on the following reason. During the process of test generation, after every test is generated, fault simulation is performed and all the faults detected by the test are dropped. The faults dropped include the target faults for which the test was found and the faults that were detected additionally due to random filling of unspecified bits in the test vector. Only small number of faults is typically detected by the specified bits of the last vectors in the test set which are detected for the first time by the test vectors. There are a large number of unspecified inputs which can be specified in such a way that the faults detected by test that are generated earlier during test generation would be detected by the later tests. Therefore, the tests generated earlier during test generally could be possibly dropped. The order in which the vectors are processed is in the reverse order of test generation.

Table 2.1 Before and after reverse order test compaction [27]

| Before reverse order test compaction |        | After reverse ord | der test compaction |

|--------------------------------------|--------|-------------------|---------------------|

| Test                                 | Fault  | Test              | Fault               |

| $t_1$                                | f1, f2 | $t_1$             | f1, f2              |

| $t_2$                                | f3     | $t_{21}$          | f2, f3              |

| $t_3$                                | f4     | t <sub>31</sub>   | f1, f4              |

The complexity of ROTCO is much less than the complexity of complete test generation because the specified values in a test vector are left unchanged.

The test compaction procedure can be explained with an example given in [27]. Consider an irredundant circuit with four faults  $\{f_1, f_2, f_3, f_4\}$ . Let the faults be detected by three test vectors as shown in the Table 2.1 above. The test  $t_3$  can be extended into a

test  $t_{31}$  which detects faults that are detected by earlier vectors by using the unspecified inputs of t3. Similarly if t2 can be extended to  $t_{21}$  such that it can detect f2 apart from f3, then t1 can be dropped from the test set. This is shown in Table 2.1. This would not be possible with reverse order fault simulation.

The following information is required for ROTCO-

- 1) The test set  $T = \{t_1, t_2, ..., t_k\}$ .

- 2) Fault detected by each test vector, which are not detected by earlier test vectors. This is obtained by fault simulation which drops faults that are detected by a test vector. Let  $F_i$  be the set of faults detected by a test  $t_i$

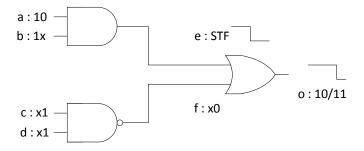

- 3) In order to distinguish the inputs specified by test generation from the inputs specified by random filling of unspecified bits, the unspecified bits filled by random filling should be given as  $x_0$  or  $x_1$  ( $x_0(x_1)$  stands for input randomly set to 0(1))

The tests are considered in reverse order. All the inputs with value  $x_0$  or  $x_1$  are changed to x. The fault lists  $F_1$ ,  $F_2$ ,....  $F_{i-1}$  are considered in increasing order of the size of the fault lists. The order within a fault set is not restricted. The test generation starts with specified inputs specified by test vector  $t_k$  until  $t_1$ . After attempting to generate a test  $t_{k1}$  which possibly detects other faults apart from  $F_k$ , the unspecified inputs that are still x are changed back to their original value ( $x_0$  or  $x_1$ ). Since some of the unspecified values might get specified in the test generation, some of the faults in  $F_i$  may no longer be detected. So, fault simulation is carried out for the modified  $t_i$  and if the faults in  $F_i$  are no longer detected by the test vector, the test vector is restored to its original values. This ensures that the fault coverage is maintained as before. If the modified  $t_i$  detects all the faults in  $F_i$ , it replaces the original test in the test set. All the faults in  $F_1$ ,  $F_2$ ,...,  $F_{i-1}$  are fault simulated and all the faults that get detected are removed from their respective fault lists and are added to fault list  $F_i$ . If a fault list becomes empty in this process, the

respective test is dropped from the test set. This process is repeated for all ti in test set T. The remaining vectors left after this procedure is the reduced test set for the circuit.

The test set size reduction when ROTCO is applied after test vectors generated using PODEM algorithm [13] is up to 56% on ISCAS 85 circuits and PLA benchmark circuits in [27]. Further when ROTCO was performed over COMPACTEST [20] with reverse order fault simulation, the test set size reduction was up to 20%. This is because the test sets produced by COMPACTEST is already compacted to a great extent and the number of faults detected by a test vector on an average is very large. This method is applicable for combinational patterns only.

#### 2.2.4 COMPACTEST

In COMPACTEST [20], the authors propose a test generation method which uses independent faults for fault ordering, a test compaction method and a dynamic line justification method to generate tests that detect large number of faults and hence reduce the test set size. The importance of independent fault sets in the reduction of test size has been established in [31, 32]. An independent fault set is defined as a set of faults for which there exists no test that detects any pair of faults in the set. Independent fault sets are very useful for test generation because the smallest test set size cannot be smaller than the size of the largest independent fault set. The problem of computing the set of independent faults of maximum cardinality in a circuit is np-hard [16]. Algorithms to compute the set of independent faults of maximum cardinality (MIFS) in a circuit is discussed in [20, 32].

During the pre-processing step of COMPACTEST, an ordered fault list is derived using MIFS for fanout free regions (FFRs) for collapsed fault set. The largest MIFS is placed at the top of the fault list, which is followed by the next largest MIFS and so on. The remaining collapsed faults which do not belong to any MIFS are added to the end of the fault list. During the computation of MIFS for the circuit, information regarding the

subsets of faults that can be potentially tested by the same vector is gathered. Basically, every fault f in an MIFS of an FFR is associated with other faults in the fanout-free region which can potentially be tested along with the fault f.

## 2.2.4.1 Maximal Compaction Procedure

The compaction procedure of COMPACTEST is described as follows. The fault at the top of the ordered fault list is selected to be targeted. This is called the primary fault. It is attempted to generate a test for the primary fault if possible. The information gathered during the pre-processing stage to find faults that can be targeted with the same fault in the FFR region to generate a test is utilized during the test generation process for the primary fault. As a result, a test vector is generated which detects a primary fault along with possibly additional faults in the FFR region. Once the test vector is generated, it is then maximally compacted to maximize the number of unspecified values in a test vector before targeting the next fault. The maximal compaction happens as follows. A primary input p is selected from the set of specified values in the test vector whose value is specified for the first time by the fault f targeted most recently. The value specified for the primary input is then complemented and implication is performed for the modified test vector. This is to ensure that the modified test vector still detects the fault f and if it still detects the fault f, the primary input p is marked, and otherwise it is left unmarked. The value of the primary input is restored to its original value as in the original test vector. This process is repeated for all the primary inputs specified for the first time during the test generation for f. Once all the primary inputs are tried, the primary inputs that were marked during the compaction procedure are then unspecified. This can be explained by an example from [20].

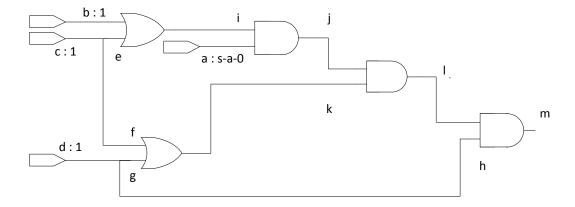

Consider a stuck at 0 fault on line a in the circuit shown in Figure 2.1. Let (1111) be the test vector generated for a stuck-at-0. The maximal compaction procedure starts by complementing the value of the primary input a, from 1 to 0. Implication is performed to

Figure 2.1 Example for maximal compaction [20]

check whether the fault a stuck-at 0 is still detected under the test (0111). Since a stuck-at 0 is not activated in this case, the input a is left unmarked and the value of input a is restored to 1. The next primary input b is considered and the value of 1 is flipped to 0 and implication is performed. Since the fault a stuck-at-0 still gets detected under the modified vector (1011), input b is marked. In a similar way, input is complemented and the same check is performed and since 1101 detects a stuck-at 0 it is also marked. Input 4 is left unmarked because 1110 does not detect a stuck-at 0. Thus the compacted vector is (1xx1), where inputs a and d are left unmarked and inputs b and c are marked.

The number of unspecified values obtained in the maximal compacted vector is independent of the order in which the inputs are processed since every input is processed beginning from the same initial state where all the other specified inputs in the original test vector remain the same except the current primary input on which the check is being performed. The resulting compacted vector contains the original vector, but not necessarily the fault for which the original test vector was generated will be detected by the specification of the unspecified values later.

After the primary fault f is targeted and the above compaction procedure is performed, the next fault in the ordered fault list picked for target for test generation. This fault is called secondary fault. The test generation process begins with the specified values in the test vector generated for the previous targeted fault and a test is generated for the secondary fault if possible by assigning values to only the unspecified inputs of the test vector. Once a test is generated for the secondary fault, additional faults present in the FFR region of the targeted secondary fault are tried for test generation to maximize the number of faults detected by the test vector. After this, the specified inputs of the test vector that were assigned during test generation of the secondary fault, are processed for maximal compaction. If the test generation for the targeted secondary fault was not possible, all the primary inputs specified during the process of test generation for the secondary fault are unspecified.

This process is repeated until either all the faults in the fault list have been tried as secondary faults or all the inputs are specified in the test vector. Once either of the conditions is met, if there are unspecified inputs left, then they are randomly specified and the test vector is fault simulated. All the faults detected by the test vector are dropped from the fault list. The process of test generation and maximal compaction is repeated with the next primary fault which is at the top of the fault list. This process continues until either all the faults have been tried or the fault list is empty.

### 2.2.4.2 Rotating backtrace

The backtrack process is modified in way such that different paths are sensitized each time a line needs to be justified on a line. In the process, different faults along the various paths are potentially detected by the test vector generation. Rotating backtrace works as follows. Every gate is associated with a counter which is initialized to 0. During backtrack, whenever the output of a gate needs to be justified to a value which can be obtained by setting any of the inputs to the controlling value, the backtrace procedure

selects an input which is given by the counter. The counter is then incremented modulo n, where n is the number of inputs to the gate. Thus, each time a value needs to be justified at the output of a gate; it is done by setting a different input line. If the input selected by the counter already is specified, another input is selected and the counter is not incremented. In addition to the rotating backtrace using a counter to select an input, controllability measures can also be used to bias the selection of inputs.

The experimental results with the heuristics of COMPACTEST applied on ISCAS-85 and ISCAS-89 benchmark circuits demonstrate a 50% reduction in the test set size on an average when compared to the test patterns generated on a test generator using PODEM and a deductive fault simulator, with reverse order fault simulation performed at the end of both the methods. There is a 2X increase in run-time with the COMPACTEST procedure of compaction. There is not much reduction in size of the test set when reverse order fault simulation is performed on the test set produced by COMPACTEST. This is illustrated the fact that COMPACTEST produces test patterns which are irredundant.

#### 2.2.5 Double Detection

In Double detection [22], a dynamic compaction method is proposed. Double detection is based on using the unspecified input values during test generation process to increase the possibility of obtaining and then later dropping redundant test vectors. In order to accomplish this, a fault is detected twice before it is dropped from the fault list. For every fault in the fault list the following information is recorded:

- 1) The fault index

- 2) The information about number of times a fault is detected is stored in a variable called *check* and is coded as follows-

check = 0 implies fault is not detected yet,

*check* = 1 implies the fault has been detected once,

*check* = 2 implies the fault has been detected at least twice

check = 3 is when a fault is aborted during test generation due to backtrack

3) The test vector that detects a fault for the first time is stored in a variable called *tvector*

limit

Deterministic test generation happens until there exists a fault with check is 0 exists. A fault  $f_I$  with check = 0 is chosen as a primary fault that is to be targeted. After a test is generated for the primary fault  $f_I$ , another fault  $f_2$  is selected.  $f_2$  is called secondary target fault. The test vector that was generated for  $f_I$  is attempted to be extended by specifying additional inputs and is possible a test is generated for fault  $f_2$ . This process is repeated until the test vector is fully specified or there are no more additional faults can be detected. Fault with check = 0 are selected first as secondary faults, followed by faults with check = 1. A fault is aborted when it is a primary fault there is no test that can be obtained within the given backtrack limit. The test generation procedure in [22] differs from [20] in which the faults with check = 1 are not selected as secondary faults and fault simulation is not performed on such faults.

After a test is generated, the test vector is simulated and the number of faults detected for the first time by the test are stored in a variable one\_check. When additional vectors are generated, if the variable *check* of a fault increases from 1 to 2, one\_check for the test vector is decreased by one. Therefore, one\_check represents the number of faults detected only by the test vector. If one\_check for a test vector is greater than 0, it means that the test vector is essential and cannot be dropped. If one\_check is 0, then the faults detected by the test vector are also detected by other vectors. This is shown in Table 2.2. Once test generation is completed, the redundant test vectors are reduced as follows. Vectors with one\_check is greater than 0 are simulated first since these vectors detect faults that cannot be detected by any other vector in the test set. Then the remaining vectors whose one\_check is 0 are simulated in reverse order compared to their original order in which they were generated. This way redundant test vectors are dropped and

Table 2.2 Example of double detection [22]

| Test vector    | Faults detected                 | one_check |

|----------------|---------------------------------|-----------|

| $\mathbf{t}_1$ | $f_1, f_3$                      | 1         |

| $t_2$          | $f_1, f_2$                      | 0         |

| t <sub>3</sub> | f <sub>2</sub> , f <sub>4</sub> | 0         |

| $t_4$          | $f_4, f_5$                      | 1         |

additional redundant vectors can be dropped by recalculating the variables *check* and *one\_check* and *tvector*. This process is repeated until one\_check for all test vectors becomes greater than 0. This method along with dynamic fault ordering and rotating backtrace [22] was compared against test patterns generated by the method used in [30] where redundant elements are removed from circuits using test pattern generation. The test pattern size is 50.7% smaller than [30] and the CPU time required is 3.6X times the time in [30].

#### 2.2.6 Essential Fault Reduction Method

Hamzaoglu and Patel in [47] propose an essential fault reduction (EFR) technique for generation of compact test sets in combinational circuits for single stuck-at faults and a heuristic for estimation of minimum stuck-at fault test set size. These algorithms together with dynamic compaction method of [22] are incorporated into the test generation system in [48]. This method found better lower bounds and generated smaller test sets than the methods of [49, 50]. EFR algorithm is an improvement over Two\_by\_One (TBO) [19, 51] and Essential Fault Pruning (EFP) algorithms [52].

Some of the definitions used in [47] are defined as follows. A test vector is called an *essential vector* if it detects at least one fault that is not detected by any other test vector in the test set. An *essential fault* of a test vector is a fault that is detected only by

the test vector in the test set. A test vector is considered *redundant* relative to a given test set, if it does not detect any essential faults. An essential fault f of a test vector  $t_i$  is said to be *pruned* if a test vector  $t_j \neq ti$  in the test set is replaced by a new test vector  $t_j'$  that detects the essential fault f, essential faults of  $t_i$  and faults detected only by  $t_i$  and  $t_i$ .

A pair of faults is *compatible* if they can be detected by the same test vector. If the two faults cannot be detected by the same vector, they are called as *incompatible*. An incompatibility graph for a given set of faults is defined as IG(FS) = (V, E) where  $V = \{v_i = f_i | 1 \le i \le n\}$  and  $E = \{e_j = (v_k, v_l) | v_k \text{ and } v_l \text{ are incompatible}, 1 \le k \le n \text{ and } 1 \le l \le n\}[18, 52, 19, 21].$

Once the initial test set is generated, EFR algorithm is used repetitively to prune essential faults of each test vector as much as possible. If all the essential faults of a test vector are pruned then a test is redundant and can be dropped from the test set. The TBO algorithm compacts tests by replacing two test vectors with a new one. This is accomplished by finding a test vector that detects the essential faults of both the vectors and the faults detected only by the two vectors. If this is not achievable by TBO, it may be achieved by three\_by\_two algorithm which replaces three test vectors with two new ones if possible. However, the  $N_by_M$  algorithm could be computationally expensive since in the worst case, it may involve  $O(T^N)$  checks where T is the number of initial test vectors generated.

EFP algorithm reduces the number of tests by pruning the essential faults of each test vector and if all the essential faults of a test vector are pruned, the vector can be dropped since it is redundant. EFP achieves better performance than TBO since it allows a test vector to prune its essential faults by replacing more than one vector in the test set. EFP tries to generate a test vector for O(FXT) fault sets, where F is the number of essential faults and T is the number of test vectors generated initially. Generally F is larger than T, therefore EFP is more expensive than TBO. For N>2, the N\_by\_M algorithm is however more expensive than EFP.

The limitation of TBO and EFP approaches is that they carry out a localized greedy search by focusing on removal of one test at a time by pruning its essential faults. If the algorithm fails to prune even one of the essential faults for a test  $t_i$ , the original test is recovered. This restriction may prevent elimination of another test vector  $t_j$  from the test set because the essential faults of  $t_j$  may be incompatible with essential faults of all other tests in the test set. However, the essential faults of  $t_j$  may be compatible with those of  $t_i$  except one of them. If  $t_i$  were allowed to prune the incompatible essential fault then the essential faults of  $t_i$  can be pruned and thus the test can be dropped from the test set.

EFR algorithm overcomes the limitation of TBO and EFP by reducing the number of essential faults for a test vector by pruning the essential faults as many as possible. The method does not stop when it fails to prune one of the essential faults and goes ahead pruning other essential faults of the test vector. This can be explained with an example in [47] shown in Figure 2.2. Let the test set  $T = \{t_1, t_2, t_3, t_4\}$  detect faults as given in the Figure 2.2. The incompatibility relation is also shown in Figure 2.2. TBO and EFP methods cannot reduce the test set size. EFR can reduce the size of the test set by replacing test vectors  $t_1$  with  $t_1'$  which detects  $t_2$  and  $t_3$ ,  $t_3$  with  $t_3'$  that detects  $t_4$  and  $t_5$ . It can be observed that  $t_2$  now is redundant and thus it can be dropped.

EFR can be used iteratively for further compaction. EFR has a worst case complexity as that of EFP and if used iteratively, the worst case complexity is O(FXTXI), where I is the number of iterations. The execution time is reduced based on a new incompatibility relation for stuck-at faults. This is based on the fact that even though a fault is pair-wise compatible with all the faults in a given fault set, it may be incompatible

if the faults are targeted together. The incompatibility relation is defined as follows. For a given set of faults  $FS = \{f_i | 1 \le i \le n\}$ , the new incompatibility graph is defined as IG(FS) = (V, E) where  $V = \{v_i \subset FS | 1 \le i \le n\}$  and  $E = \{e_j = (v_k, v_l) |$  the faults in  $v_k$  are incompatible with the faults in  $v_l$ ,  $1 \le k \le n$  and  $1 \le l \le n\}$ . This is used to speed up EFR algorithm. The iterations of the EFR algorithm are stopped as soon as the minimum test set size is reached instead of iterating a pre-determined number of times.

# Incompatibility Graph

| f1 | f3 f7       |

|----|-------------|

| f2 | f4 f5 f7    |

| f3 | f1 f5 f7    |

| f4 | f2 f5       |

| f5 | f2 f3 f4 f5 |

| f6 |             |

| f7 | f1 f2 f3 f5 |

|    |             |

# **Initial Test Set**

| Test<br>Vector | Faults<br>Detected |    |  |

|----------------|--------------------|----|--|

| t1             | f1                 | f2 |  |

| t2             | f3                 | f4 |  |

| t3             | f5                 | f6 |  |

| t4             | f7                 |    |  |

Step 1

| Test   | Faults   |         |  |

|--------|----------|---------|--|

| Vector | Detected |         |  |

| t1     | (f1)     | f2      |  |

| t2     | f3       | f4 🌙    |  |

| t3'    | f5       | f6 (f1) |  |

| t4     | f7       | $\sim$  |  |

Step 2

| Test   | Faults   |    |      |

|--------|----------|----|------|

| Vector | Detected |    |      |

| t1'    | X        | f2 | (f3) |

| t2     | (f3) f4  |    |      |

| t3'    | f5       | f6 | f1   |

| t4     | f7       |    |      |

Step 3

| Test   | Faults   |       |    |

|--------|----------|-------|----|

| Vector | Detected |       |    |

| t1'    |          | f2    | f3 |

| t2     | f3       | (f4)- |    |

| t3'    | f5       | f6    | f1 |

| t4'    | f7       | (f4)  |    |

= Detected

= Redundant

Figure 2.2 EFR example [47]

# 2.2.7 Dynamic Test Vector Compaction

The dynamic compaction approach in [53] differs from traditional dynamic compaction approach. Typically in dynamic compaction, once test is generated for a fault, the next fault is picked from the fault list and is targeted for test generation. In [53] however, after a test is generated for a fault, instead of selecting the next untested fault from the fault list and generating a test for the fault, a compaction procedure called COMPACT is used. In the compaction procedure, a test  $T_i$  is compared with other tests generated earlier and if  $T_i$  is compactable with any of the previous tests  $T_j$ , where j < i then  $T_j$  is replaced with  $T_i \cap T_j$ . If  $T_i$  is not compactable the test is added to the test vector set. This compaction is performed repetitively and test compaction is obtained.

T1: X10

The record of T<sub>1</sub>: cell T<sub>1</sub>

011 the depend field

010 the value field

Figure 2.3 Test  $T_i$ : X10 recording [53]

An efficient data structure is used for the comparison of test vectors. The data structure contains an N dimension table, where N is the expected number of tests. Each test vector is identified by index as  $T_i$  and belongs to a cell sequence of type *test-vector*. The *i*th test vector can be obtained from the table TEST as TEST[i]. Each  $T_i$  record is a cell which contains two fields called *depend* and *value* both being integer type. The first field *depend* specifies the "significance" of a PI, i.e., if the value is 0 or 1 then it is considered to be significant and *depend* is set to 1 and if value is X then *depend* is 0. The second field *value* contains the test vector values for the corresponding PIs and if *value* is

1, it is always significant and if it is 0, then *depend* field is looked-up. This is illustrated in Figure 2.3. An integer consisting of 32 bits can store upto 32 PI values. The values of PIs are stored with two integers as explained above.

In order to check for compactability between a test generated *test* and for a test generated previously TEST[i] from the table, the *depend* fields are compared first and then the *value* fields are compared. Once the comparisons are done and if the test generated *test* is compactable with the test TEST[i], the test is compacted with TEST[i]. In this way, the test generated *test* is compared with all the previously generated tests. If the test is not compactable with any of the tests, then the test is added to the table TEST. Before picking the next fault for targeting, the compacted result or the generated test *test* is fault simulated.

The advantage of this method is it is very simple and the memory requirements are minimal since the values of the inputs are stored in two integers. The compaction achieved by this method is 40% for smaller circuits and about 50% for larger circuits (over 1000 gates) when compared with tests generated using PODEM.

#### 2.3 The Proposed Method

In this section, we present an incremental dynamic compaction approach that uses a cube merging mechanism with dynamic compaction. We also propose a reasoning analysis approach to drop redundant secondary faults from being targeted again in order to improve the run-time.

#### 2.3.1 Motivation

The importance of minimum size test sets has been observed in the previous section and we have reviewed methods from literature to achieve this. Test set size impacts the test storage requirements and test application time. Test application time is directly proportional to the product of the number of tests and the number of scan cells in

the longest scan chain in the design. In this work, an incremental approach is proposed which addresses the issue of growing test pattern size.

The fault coverage curve for the designs typically ramps up vigorously in the beginning due to random fault detections and slows down ultimately becoming almost flat after certain fault coverage is reached. Therefore, towards the tail end of the fault coverage curve there are very few faults detected per pattern. The existing test generator uses cube merging initially which is a greedy way of compaction and we use focused dynamic compaction after a threshold fault coverage after which the ramp slows down so as to utilize the benefit of random detections in the initial portion of the fault coverage curve and get the benefit of dynamic compaction in the tail of the curve.

In this work we present an incremental dynamic compaction method and propose methods to reduce run-time. The contributions of the work are:

- Propose a test compaction approach that utilizes the benefit of both cube merging and dynamic compaction by initially performing cube merging/greedy compaction and later switching to dynamic compaction in the tail of the fault coverage curve.

- 2) Static untestability analysis to identify and skip targeting secondary faults that cannot be activated and/or propagated with a given testcube.

- Reasoning analysis to identify untestable faults during dynamic compaction which are untestable independent of constraints set by dynamic compaction

#### 2.3.2 Preliminaries

In this section the fault coverage curve is discussed and cube merging approach is described that is used during the initial ramp of the fault coverage curve. The basic incremental dynamic compaction with static untestability and reasoning analysis to reduce run time for dynamic compaction is presented later.

# 2.3.2.1 Cube merging Method

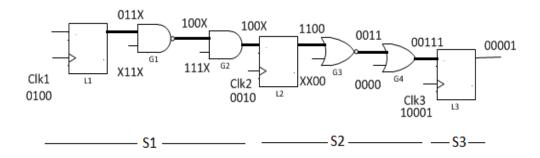

In this section we describe the cube merging technique existing in the test pattern generator similar to [53] which is used to compact patterns on the fly as they are generated. Once a test is generated for a fault, the raw pattern is stored in a bin. A bin is a data structure to hold a compacted pattern resulting by merging of raw patterns. The number of bins is programmable and can be specified at the beginning of ATPG. A test cube is a pattern generated by the ATPG and the unspecified values are not specified yet. A new pattern generated is merged with the first available bin with which the test cube is compatible. In order to find whether a pattern is compatible with the pattern in a bin, the scan cell values and the primary input values are compared. If there are no conflicting values then the pattern is merged with the pattern in the bin. If there is no such bin available with which the raw pattern can be merged, the pattern is stored in the next available empty bin. If there is no empty bin remaining, then a bin that has the most number of tests compacted is written out after filling the unspecified bits with 1s and 0s. The compacted pattern that is written out is simulated and all faults that are detected by the pattern are dropped and are not targeted later. The overall flow of cube merging is illustrated as a flowchart in Figure 2.4.

The process of cube merging can be explained with an example as shown in Figure 2.5. Consider a two bin datastructure for storing test cubes. The number of testcubes merged is initialized to 0 for every bin. When testcube  $t_1$  is generated, it is stored in the first bin, i.e. bin 0 as shown in Figure 2.5(b), since it is the first compatible bin available and the number of testcubes merged is updated to 1. When testcube  $t_2$  is generated, since it is compatible with the testcube in the first bin, it is merged with the testcube already existing in the bin and the merged pattern is stored in the bin. The number of testcubes merged is updated to 2 for bin 0. When testcube  $t_3$  is generated, since it is not compatible with the pattern in bin 0, it is stored in the next compatible bin, i.e. bin 1 as shown in Figure 2.5(b). The number of testcubes merged is changed from 0 to 1

Figure 2.4 Flow diagram for cube merging technique

for bin 1. When testcube  $t_4$  is generated, it is incompatible with both bin 0 and bin 1 and since there are only two bins available, testcube in bin 0 is picked to be fault simulated since it has the maximum number of testcubes merged. Once the testcube is selected for fault simulation, the unspecified bits are random filled and the pattern is then fault simulated and the detected faults are dropped from the fault list. The testcube  $t_4$  is now stored in bin 0 as shown in Figure 2.5(c).

| Test Index | Testcube |

|------------|----------|

| $t_1$      | 1X0X1X   |

| $t_2$      | 110X1X   |

| $t_3$      | 10X10X   |

| $t_4$      | 11010X   |

# (a) Test Cubes Generated

| Bin<br>Index | Merged testcube | Num cubes<br>merged |

|--------------|-----------------|---------------------|

| 0            | 110X1X          | 2                   |

| 1            | 10X10X          | 1                   |

<- Fault simulated after random fill

# (b) Bin data Structure - 1

| Bin<br>Index | Merged testcube | Num cubes<br>merged |

|--------------|-----------------|---------------------|

| 0            | 110X1X          | 2                   |

| 1            | 10X10X          | 1                   |

(c) Bin Data Structure - 2

Figure 2.5 Example for Cube Merging

The next section describes fault coverage curve when the cube merging technique is used and the motivation to use dynamic compaction so as to generate compatible test cubes and reduce the pattern count.

# 2.3.2.2 Fault Coverage Curve

A fault coverage curve plots the fault coverage with respect to the number of tests or equivalently scan operations. A fault coverage curve when the above cube merging

method/greedy method of compaction is used is shown in Figure 2.6. Initially there is huge number of detections during fault simulation. The random filling of unspecified values in the pattern causes a large number of faults to be detected during fault simulation. There is a rapid increase in the fault coverage within very small number of scan operations.

Figure 2.6 An Example Fault Coverage Curve

Cube merging not suitable and

friendly

compaction

needs

patterns

Cube merging performs well

Solution

No compaction

needed

Compaction does not really have an impact on the number of fault detections. This is shown as the initial region of the fault coverage curve in Figure 2.6. The coverage ramp slows down after a few scan operations and there is lesser number of detections during