Theses and Dissertations

Spring 2014

# Mesh-Bus, a double-layer coded, time-transparent digital distributed single-wire bus

Hamid Fahim Rezaei University of Iowa

#### Copyright 2014 Hamid Fahim Rezaei

This dissertation is available at Iowa Research Online: http://ir.uiowa.edu/etd/4626

#### Recommended Citation

Fahim Rezaei, Hamid. "Mesh-Bus, a double-layer coded, time-transparent digital distributed single-wire bus." PhD (Doctor of Philosophy) thesis, University of Iowa, 2014. http://ir.uiowa.edu/etd/4626.

# MESH-BUS, A DOUBLE-LAYER CODED TIME-TRANSPARENT DIGITAL DISTRIBUTED SINGLE-WIRE BUS

by

Hamid Fahim Rezaei

A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

May 2014

Thesis Supervisor: Professor Anton Kruger

Copyright by

HAMID FAHIM REZAEI

2014

All Rights Reserved

# Graduate College The University of Iowa Iowa City, Iowa

| CE<br>-                | RTIFICATE OF APPROVAL                                                                                  |             |

|------------------------|--------------------------------------------------------------------------------------------------------|-------------|

|                        | PH.D. THESIS                                                                                           |             |

| This is to certify tha | t the Ph.D. thesis of                                                                                  |             |

|                        | Hamid Fahim Rezaei                                                                                     |             |

| for the thesis require | by the Examining Committee ement for the Doctor of Philosophy and Computer Engineering at the May 2014 | graduation. |

| Thesis Committee:      | Anton Kruger, Thesis Supervisor                                                                        |             |

| -                      | David R. Andersen                                                                                      |             |

|                        | Weiyu Xu                                                                                               |             |

|                        | Mathews Jacob                                                                                          |             |

|                        | Craig Just                                                                                             |             |

#### **ACKNOWLEDGMENTS**

I would like to thank my committee members for accepting to serve on my committee. I would also like to thank Dr. James Niemeier for his helps and inputs during the whole period of my Ph.D. program. My deepest gratitude is for Professor Anton Kruger, not only for his brilliant ideas and extensive supports during the last for years as my Ph.D. advisor, but also for his kindness, understanding and insights as a life mentor. Finally I would like to thank my wife, Raheleh, and my family back in Iran, whose mental support helped me endure difficult times.

#### **ABSTRACT**

Medium access mechanisms are one of the most important aspects of buses, which are shared mediums. Almost all standard buses use Time Division Multiple Access (TDMA) as their medium access scheme. Such buses usually are multi-wire, very sensitive to time synchronization, and often managed by a master node.

In this thesis, we develop new non-TDMA schemes for bus communications which are based on Code Division Multiple Access (CDMA), or Frequency Division Multiple Access (FDMA) that do not have the intrinsic limitations of traditional buses. The proposed schemes are based on a single wire bus setting. Since, in theory, any node can have a dedicated communication link to any other node on the bus, the nodes virtually form a fully-connected mesh, hence the name *Mesh-Bus*.

In such schemes, no master node is required on the bus; therefore, we can have a distributed bus in which all the nodes have the same functionality. Also, no time synchronization is required. Every node, using its unique code/frequency, creates a virtual private link to the other nodes, and using such interference-resistant virtual private links, the nodes communicate data to each other.

This dissertation explores the underlying principles of such non-TDMA schemes and through extensive software simulations investigates various scenarios in for CDMA scheme, and studies the performance for the system. Finally, a hardware implementation of the CDMA scheme is presented, and some experimental results are provided to validate the simulation results.

# TABLE OF CONTENTS

| LIST OF TABLES                                             | VI  |

|------------------------------------------------------------|-----|

| LIST OF FIGURES                                            | VII |

| CHAPTER 1 INTRODUCTION                                     | 1   |

| CHAPTER 2 LITERATURE REVIEW                                | 6   |

| Network Topology and Embedded/Field Bus Protocols          | 6   |

| Bus Topology versus the Others                             | 6   |

| Bus Types                                                  |     |

| Current Serial Bus Standards                               | 12  |

| RS- XXX Family: RS-485, RS-232, RS-422, RS-423             | 12  |

| 1-Wire Bus                                                 | 15  |

| I <sup>2</sup> C Bus                                       |     |

| SPI Bus                                                    |     |

| Multiple Access Schemes                                    |     |

| TDMA                                                       |     |

| FDMA                                                       |     |

| CDMA                                                       |     |

| Z-Channel                                                  | 32  |

| Optical Orthogonal Codes (OOCs)                            | 34  |

| CHAPTER 3 THE MESH-BUS                                     | 37  |

| Introduction                                               | 37  |

| Mesh-Bus Setting, Bus-Modulator, and NOR Bus               |     |

| Operational Logic of Mesh-Bus                              | 43  |

| Detection process in a Mesh-Bus Setting                    |     |

| Coding: M-ary versus Unary                                 |     |

| Low Weight Atoms                                           | 52  |

| CHAPTER 4 THE WIRED-CDMA SCHEME                            | 55  |

| Introduction                                               | 55  |

| Traditional CDMA                                           |     |

| CDMA Codes                                                 | 58  |

| A. Walsh Codes                                             | 58  |

| B. <i>m</i> -sequences                                     |     |

| C. Gold Codes                                              |     |

| Near-Far Problem                                           |     |

| Wired-CDMA                                                 |     |

| Optical Orthogonal Codes                                   |     |

| Simulations                                                |     |

| Data Rate Evaluation                                       |     |

| Error Correcting through Time-Distanced Information Coding |     |

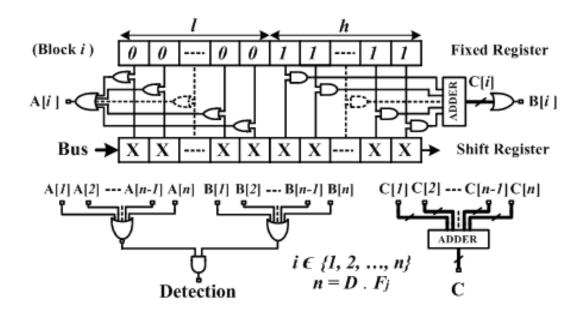

| CHAPTER 5 HARDWARE IMPLEMENTATION                          | 81  |

| Introduction                                      | 81  |

|---------------------------------------------------|-----|

| Hardware                                          |     |

| Firmware                                          |     |

| Transmission                                      |     |

| Detection                                         |     |

| CHAPTER 6 PERFORMANCE ANALYSIS OF WIRED-CDMA      | 105 |

| Predictable errors in the hardware implementation | 106 |

| Simulation of transmission/Detection              | 107 |

| Data Transmission                                 |     |

| CHAPTER 7 THE WIRED-FDMA SCHEME                   | 121 |

| Introduction                                      | 121 |

| Wired-FDMA Signaling                              |     |

| Transmission                                      |     |

| Detection                                         | 123 |

| Simulation and Analysis                           | 126 |

| CHAPTER 8 THE WIRELESS BUS                        | 129 |

| Introduction                                      | 129 |

| Wireless Bus, as a modified Mesh-Bus Scheme       |     |

| Hardware implementation                           |     |

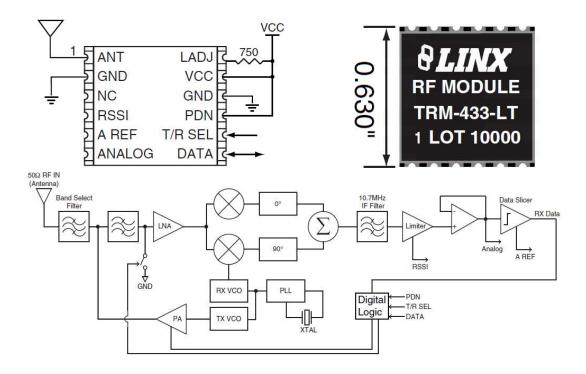

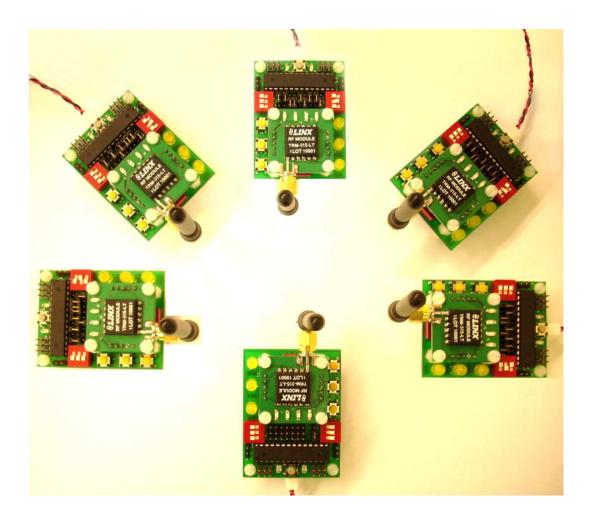

| Radio Transceiver Module                          | 134 |

| Microcontroller Board                             |     |

| Experiment Setting                                |     |

| REFERENCES                                        | 139 |

# LIST OF TABLES

| Table 1 Comparison between different interconnection topologies                        | 10  |

|----------------------------------------------------------------------------------------|-----|

| Table 2 The codewords of the Walsh codes of length 2, 4, 8, and 16.                    | 60  |

| Table 3 The auto and cross correlation of the codewords of (65, 3, 1)-OOC              | 74  |

| Table 4 Functionality and interconnection of the 10-pin connector of the Bus-Modulator | 87  |

| Table 5 Five codewords of the (256,3,1)-OOC.                                           | 137 |

# LIST OF FIGURES

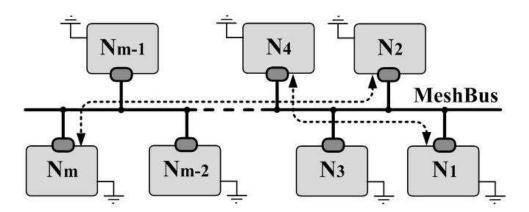

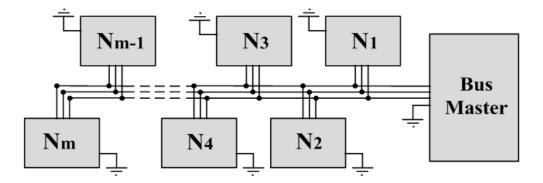

| Figure 1 The Mesh-Bus, through which <i>N</i> nodes communicate bidirectionally over a single wire. A common ground-connection is implied. Although it is a bus, but the nodes are able to form a virtual mesh configuration, because every node is capable of communicationg with any other node at any desired time. | 1  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

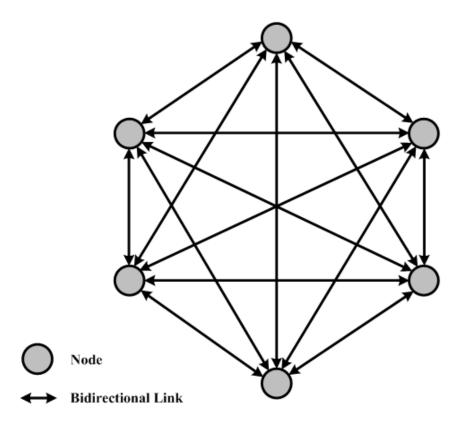

| Figure 2 A fully-connected mesh topology. In a fully-connected mesh with $n$ nodes, every node has a direct and dedicated connection to every $n-1$ other node of the network.                                                                                                                                         | 7  |

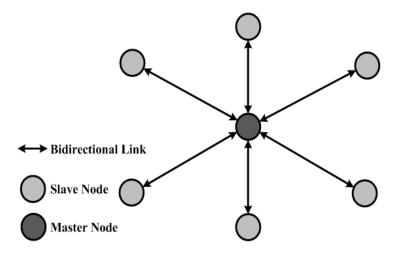

| Figure 3 A Star topology. The dark gray node is the hub or the master of the network. It manages all the communications of the network. Communication between every two nodes occurs through the master                                                                                                                | 8  |

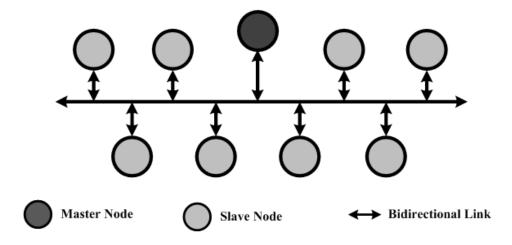

| Figure 4 A bus topology. Similar to the star topology, the dark gray node is the master node which orchestrates all the communications which occur through the bus.                                                                                                                                                    | 10 |

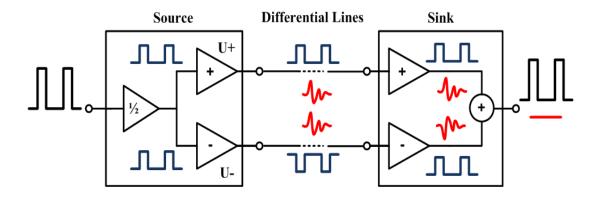

| Figure 5 Differential signaling scheme. Since the end signal is the difference of the signals on the lines, the effect of noise on the line gets canceled out                                                                                                                                                          | 13 |

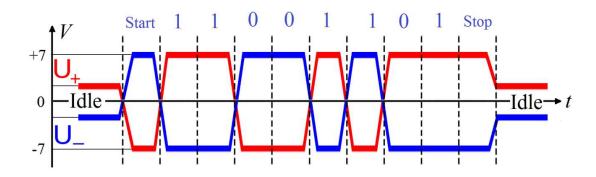

| Figure 6 Differential signaling and data encapsulation of the binary string: '11001011' in RS-485.                                                                                                                                                                                                                     | 13 |

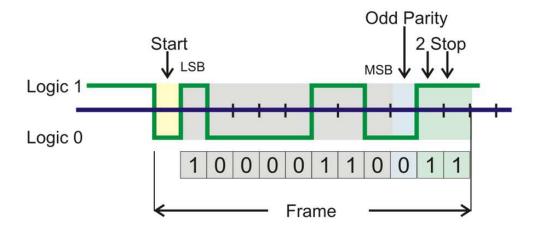

| Figure 7 Data encapsulation for USART. It begins with a start bit, the data, one odd parity check bit, and finally two stop bits                                                                                                                                                                                       |    |

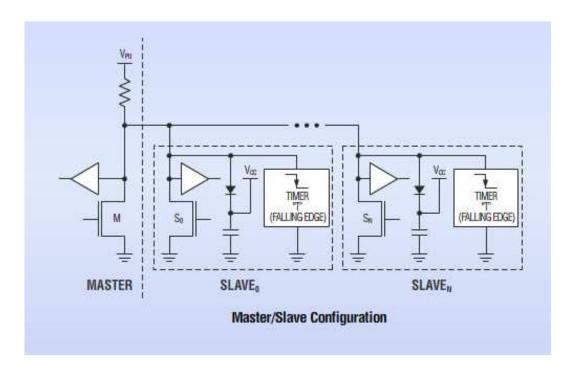

| Figure 8 The circuit diagrams of the master and slave nodes in a 1-Wire bus                                                                                                                                                                                                                                            | 15 |

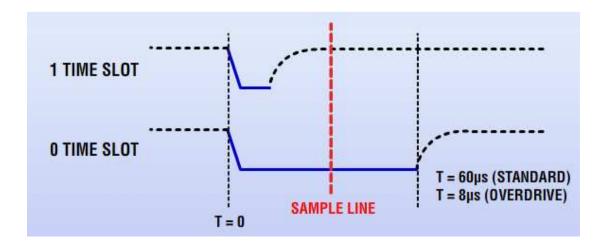

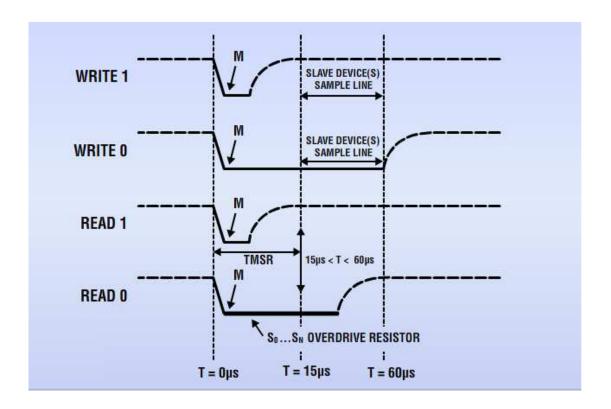

| Figure 9 The time slot in the standard mode of 1-Wire bus                                                                                                                                                                                                                                                              | 16 |

| Figure 10 The master's read/write request in standard mode 1-Wire bus.                                                                                                                                                                                                                                                 | 17 |

| Figure 11 The three phases of communication on a 1-Wire bus                                                                                                                                                                                                                                                            | 18 |

| Figure 12 The first phase of 1-Wire communication: device reset/synchronization                                                                                                                                                                                                                                        | 18 |

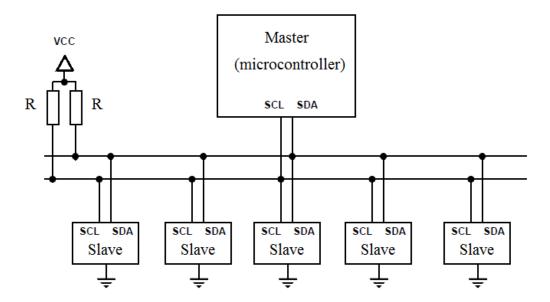

| Figure 13 The I2C bus. Both lines, the data and clock lines, are pulled up to <i>VCC</i> through resistors.                                                                                                                                                                                                            | 19 |

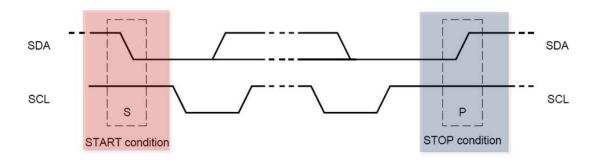

| Figure 14 The start (the shadowed area S) and stop (the shadowed area P) conditions of I2C bus protocol                                                                                                                                                                                                                | 20 |

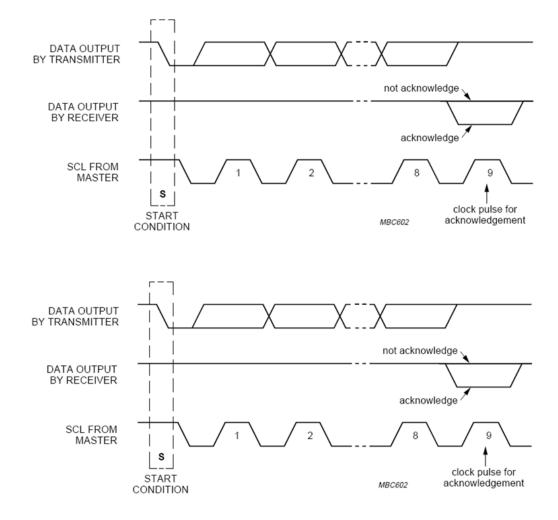

| Figure 15 Process of data acknowledgement between the master and slave in the I2C bus.                                                                                                                                                                                                                                 | 21 |

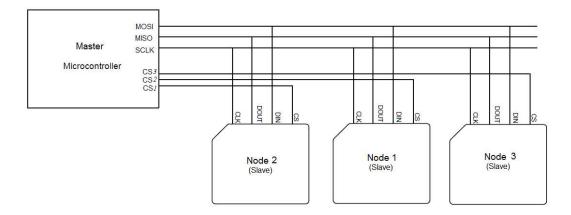

| Figure 16 The SPI bus, and the data and chip select lines.                                                                                                                                                                                                                                                             | 22 |

| Figure 17 Signaling of the SPI bus.                                                                                                                                                                                                                                                                                    | 23 |

| Figure 18 The multiple access schemes of FDMA. TDMA, and CDMA                                                                                                                                                                                                                                                          | 24 |

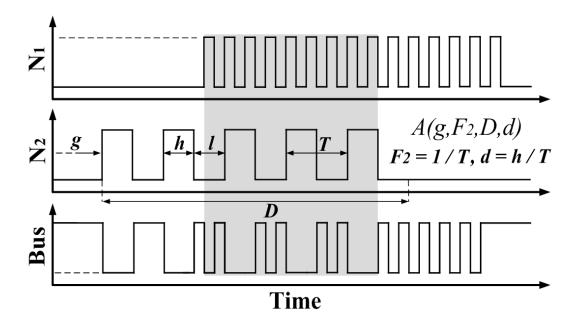

| Figure 19 | The frames of TDMA with N time slots. The time slots do not overlap with each other, and usually there are some guard time between every two time slots.                                                                            | 26  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 20 | The processes of FDMA. (a) The baseband signal (b) up-converted signal to frequency $f1$ (c) the occupation of frequency spectrum, (d) the filter at the receiver.                                                                  | 28  |

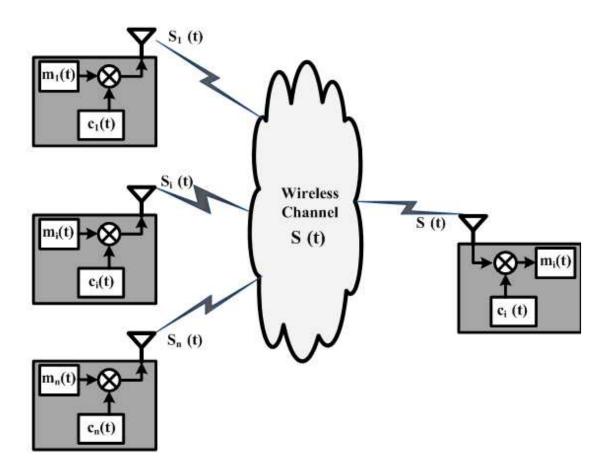

| Figure 21 | The processes of transmission and detection in CDMA scheme.                                                                                                                                                                         | 31  |

| Figure 22 | The Binary symmetric channel model. X is the input random variable, and Y is the output random variable.                                                                                                                            | 32  |

| Figure 23 | The Binary asymmetric channel model. X is the input random variable, and Y is the output random variable.                                                                                                                           | 33  |

| Figure 24 | The autocorrelation function (top,) and cross correlation function (bottom) of the $(n, w, \lambda a, \lambda c) - 00C$ .                                                                                                           | 35  |

| Figure 25 | Traditional TDMA-based buses use sets of wires that form the buss, and the nodes on the bus must be configured as one Master and some Slave nodes.                                                                                  | 38  |

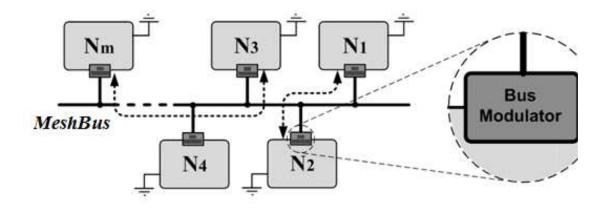

| Figure 26 | The Mesh-Bus setting. Every node has a intermediary device named the Bus-Modulator, through which connects to the bus                                                                                                               | 39  |

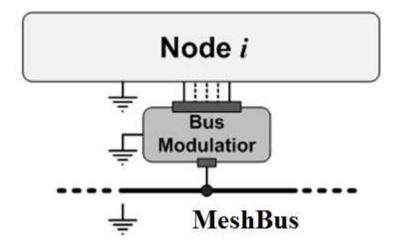

| Figure 27 | Bus-Modulators interfaces nodes to the Mesh-Bus. They provide high-level interfaces to sensors using the sensors' native interfaces and protocol. Bus-Modulators is a translator between the original data and the Mesh-Bus format. | 40  |

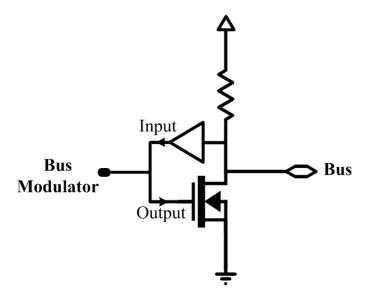

| Figure 28 | The open-drain interface of the Bus-Modulator. Such a configuration is very popular in microcontroller pins, so it is easily implementable using ordinary microcontrollers                                                          | 41  |

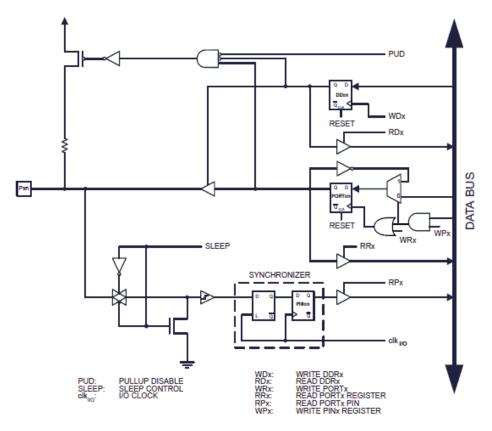

| Figure 29 | The diagram of general digital I/O of the ATMEL AVR microcontroller. The table shows the port pin configuration of such and I/O pin                                                                                                 | 42  |

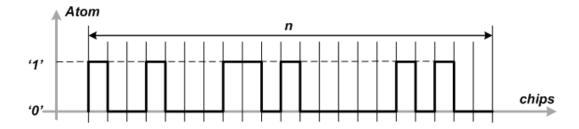

| Figure 30 | A sample Atom (21, 7). This Atom has length of 21 chips and the Hamming weight is 7.                                                                                                                                                | 43  |

| Figure 31 | The time-distanced unary coding scheme.                                                                                                                                                                                             | .48 |

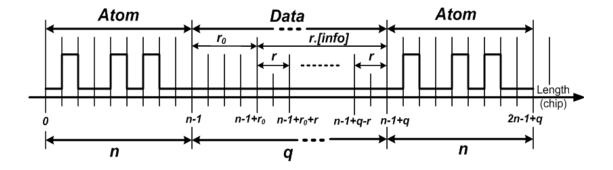

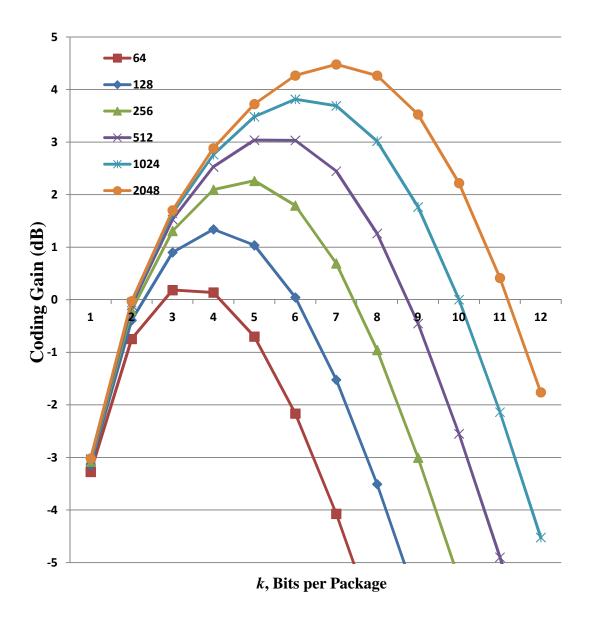

| Figure 32 | The message length of binary and unary coding, and the average coding gain.                                                                                                                                                         | 50  |

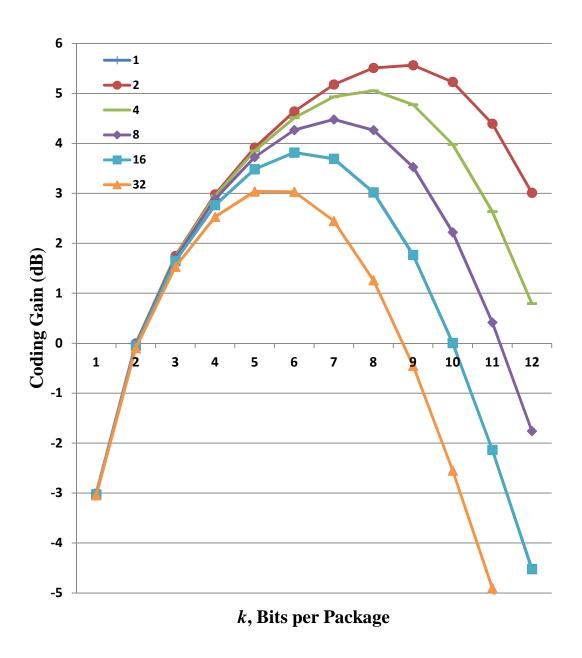

| Figure 33 | The coding gain of time-distanced unary coding versus $k$ , for different Atom length, where $r=16$                                                                                                                                 | 51  |

| Figure 34 | The average coding gain of unary scheme versus k for different values of $r$ , where $n=1024$ .                                                                                                                                     | 52  |

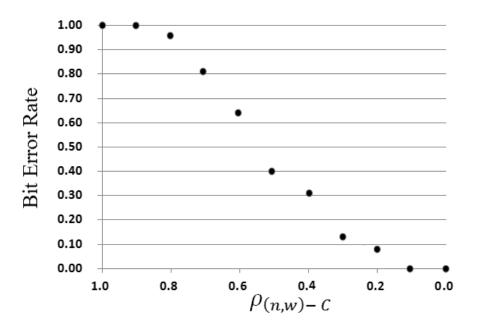

| Figure 35 | Code density versus error rate for 8 concurrent transmission on the bus                                                                                                                                                             | 53  |

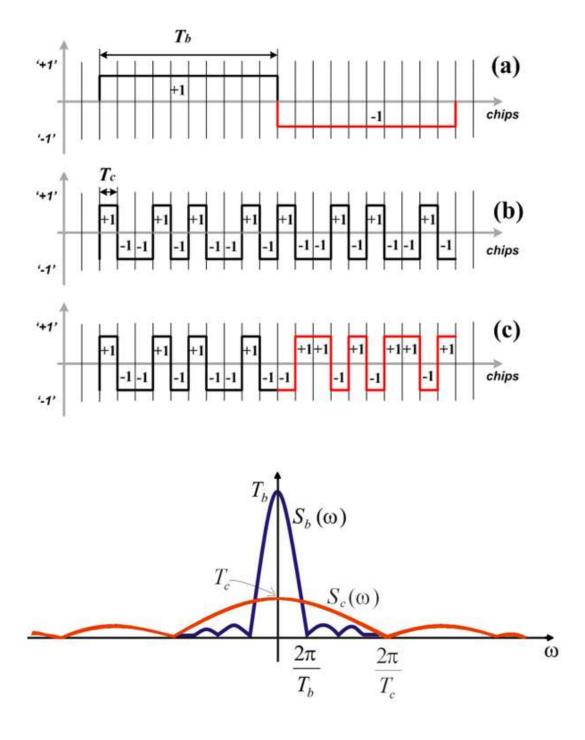

| Figure 36 | The process of spreading of information signal (a) by the spreading sequence (b). The signal (c) shows the spread data signal. At the bottom, the frequency spectrum of original information signal, $Sb(\omega)$ , and the spreading sequence, $Sc\omega$ are shown. | 56 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

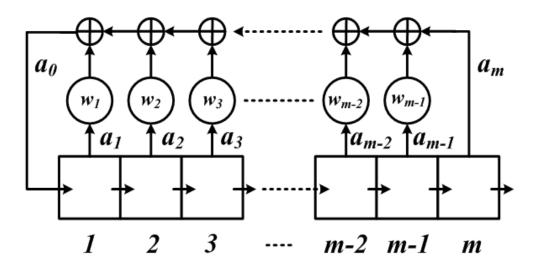

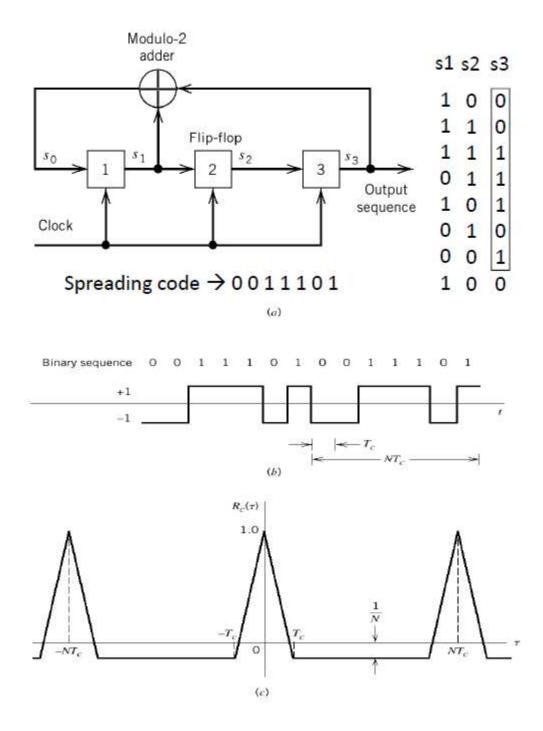

| Figure 37 | A Linear Feedback Shift Register.                                                                                                                                                                                                                                     | 61 |

| Figure 38 | m-Sequences and their properties: (b) The m-Sequence of '0011101, generated by (a) the LFSR of the primitive polynomial of $1 + X + X3$ . (c) The normalized autocorrelation of the m-sequence versus $\tau$                                                          | 63 |

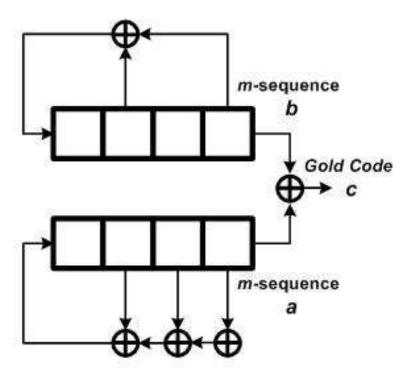

| Figure 39 | The sequence <i>cn</i> is a Gold code generated by the two m-sequences of <i>an</i> and <i>bn</i>                                                                                                                                                                     | 64 |

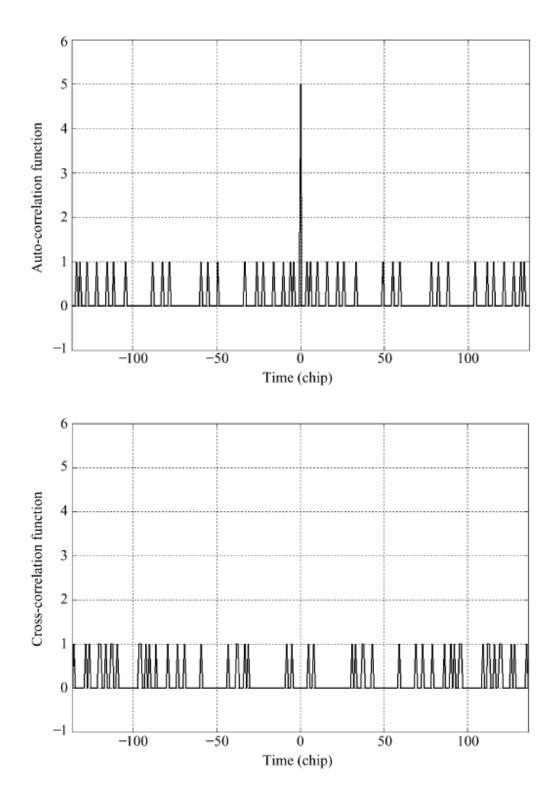

| Figure 40 | Correlation properties of (123, 5, 1, 1) – 00C: (Top) the autocorrelation of a codeword.(Bottom) The cross correlation functions between the codewords.                                                                                                               | 69 |

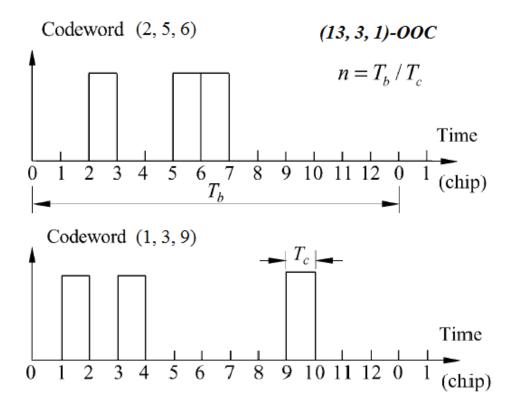

| Figure 41 | The two codewords of $(13, 3, 1) - 00C$ , $(2,5,6)$ and $(1, 3, 9)$                                                                                                                                                                                                   | 71 |

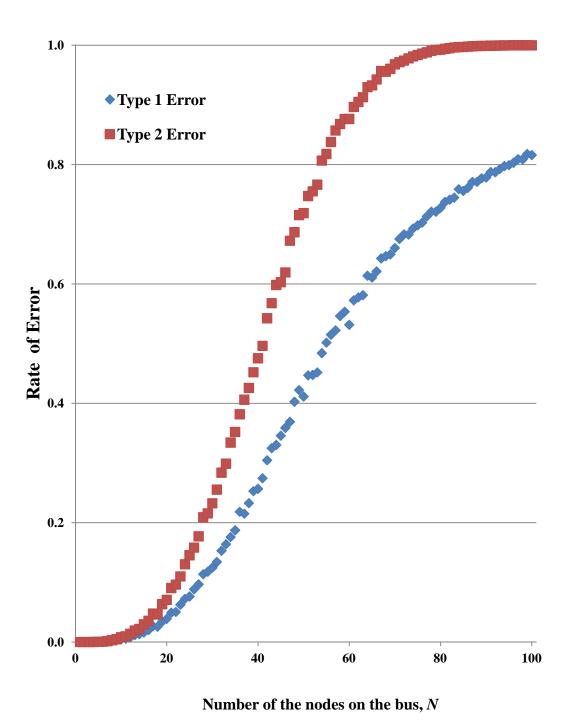

| Figure 42 | Simulation results for the error rate evaluation of the $(1000, 3, 1) - 00C$ . In the graph, the red curve shows the Type Two (the false positive detection), and the blue curve shows the Type One error rate                                                        | 77 |

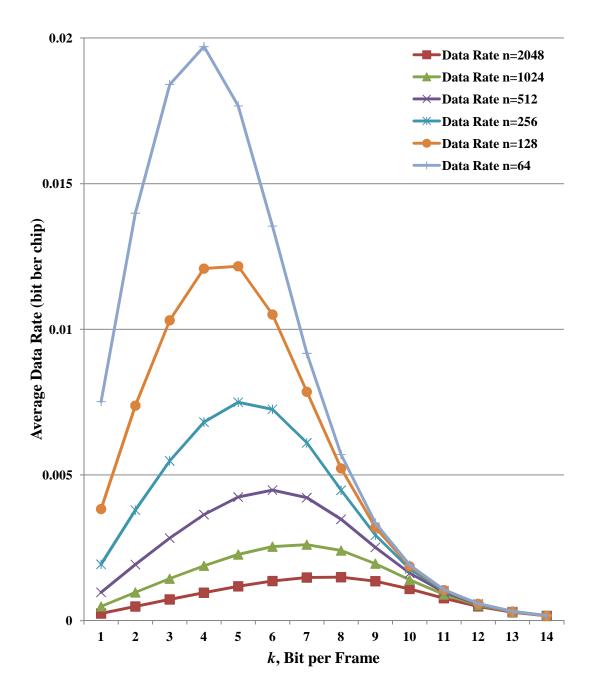

| Figure 43 | The data rate of the Wired-CDMA per chip, versus $k$ , for different length of Atoms. In this graph and $r = 10$ .                                                                                                                                                    | 78 |

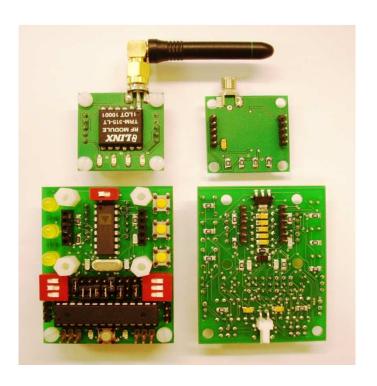

| Figure 44 | Top, bottom, and side view of the implemented Bus-Modulator. It has a 10-pin connector for high level interfacing and a 2-pin IDC connector for interfacing the bus.                                                                                                  | 82 |

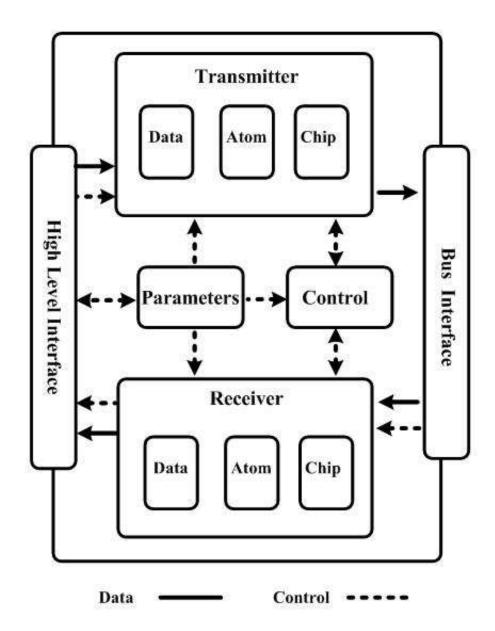

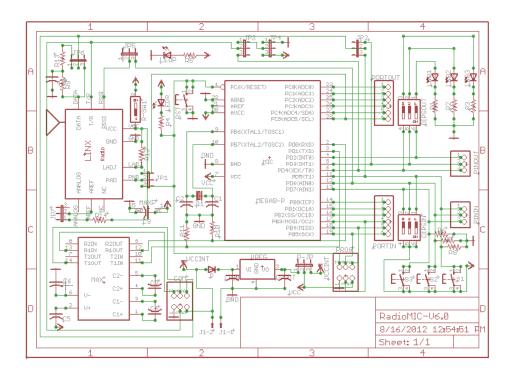

| Figure 45 | The schematic of the Bus-Modulator. It has two interfaces, namely, high and low level communications, and four functional block of parameters, control, transmitter and receiver.                                                                                     | 84 |

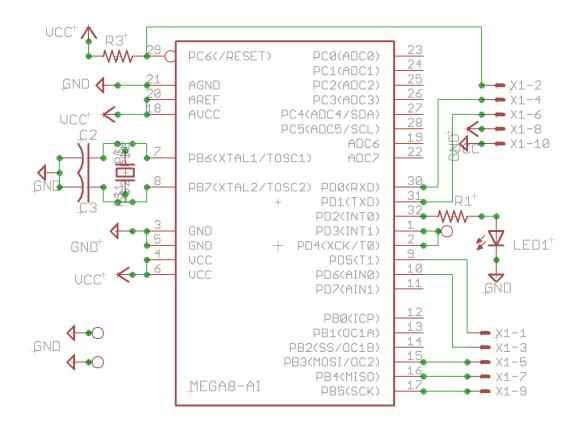

| Figure 46 | The schematic of the Bus-Modulator hardware, which is based on Atmel ATmega168PA                                                                                                                                                                                      | 86 |

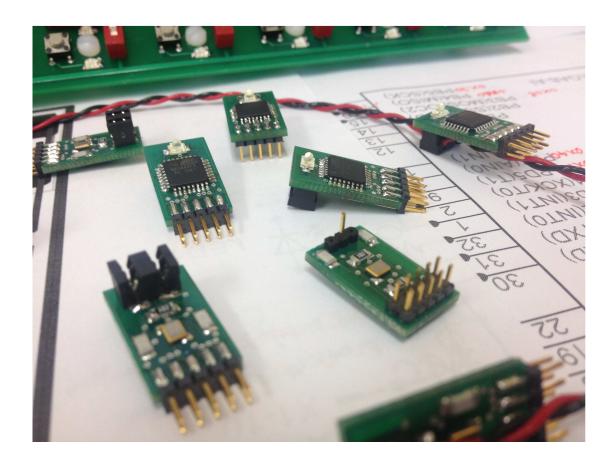

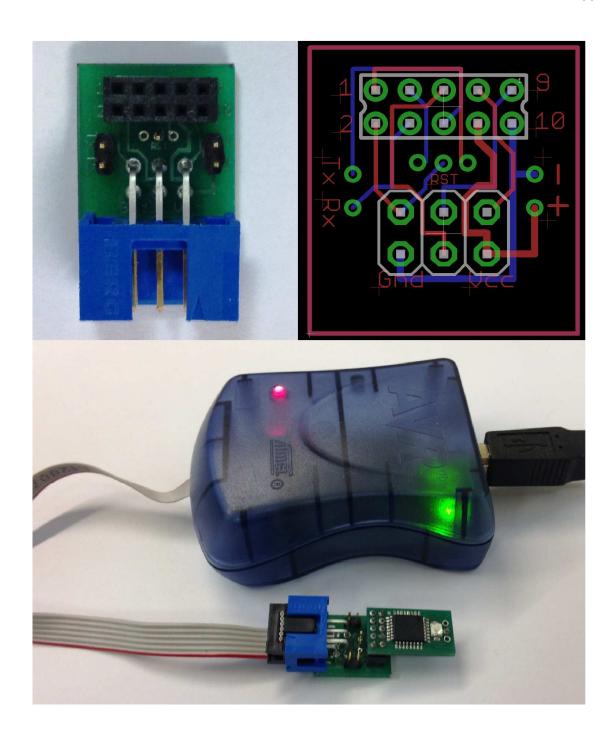

| Figure 47 | Printed circuit board for the external high level interfacing board (top right). The external high level interfacing board (top left). Interfacing of the Bus-Modulator V1.0 and The AVRISP programmer.                                                               | 88 |

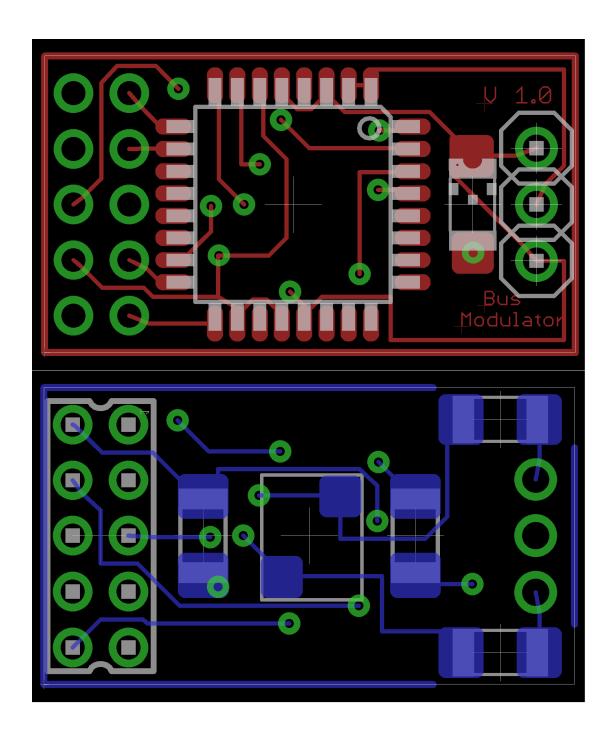

| Figure 48 | Top layer of the printed circuit board of the Bus-Modulator V1.0 (top). Bottom layer of the printed circuit board of the Bus-Modulator V1.0 (bottom).                                                                                                                 | 89 |

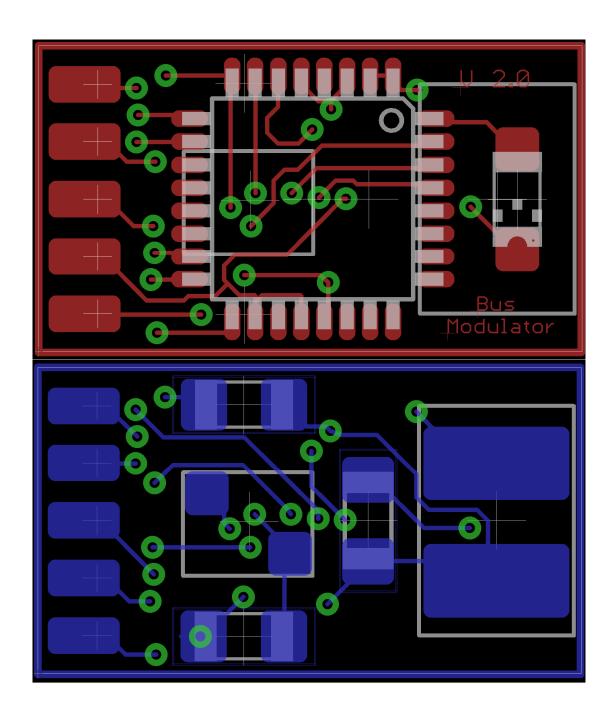

| Figure 49 | Top layer of the printed circuit board of the Bus-Modulator V2.0 (top). Bottom layer of the printed circuit board of the Bus-Modulator V2.0 (bottom)                                                                                                                  | 90 |

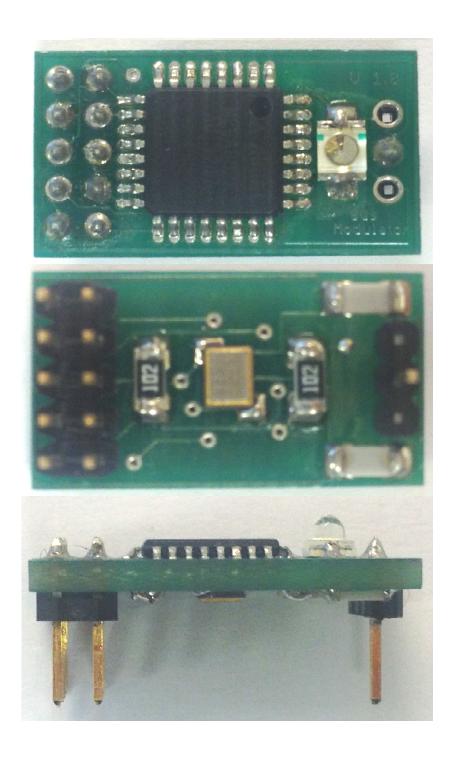

| Figure 50 | Top view, bottom view, and side view of the Bus-ModulatorV1.0                                                                                                                                                                                                         | 91 |

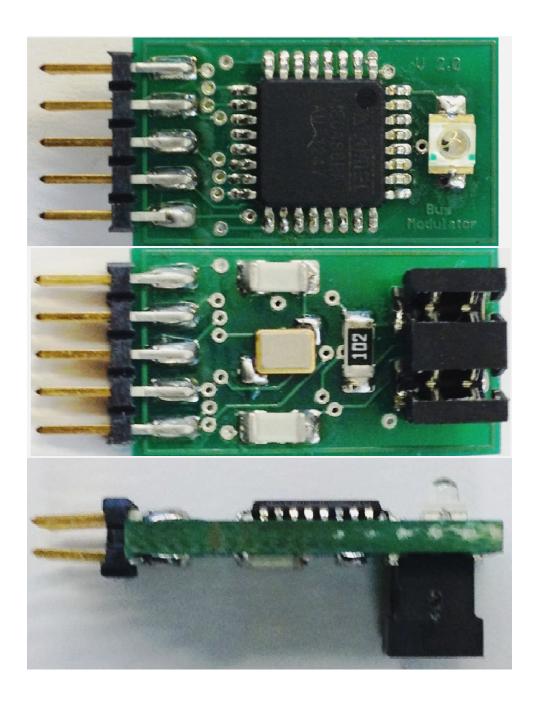

| Figure 51 | Top view, bottom view, and side view of the Bus-Modulator V2.0                                                                                                                                                                                                        | 92 |

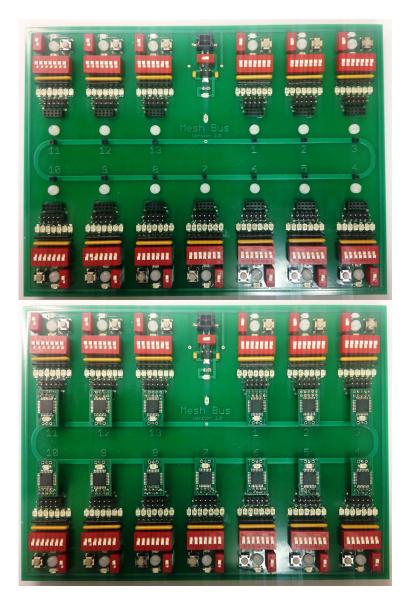

| Figure 52 | Top view of the Bus-Board (top). The Bus-Board with thirteen Bus-ModulatorV1.0 plugged in.                                                                                                                                                                                                                                              | 93  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

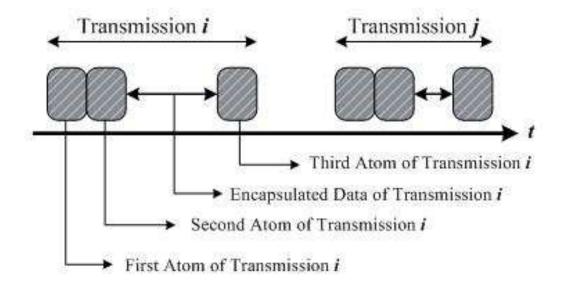

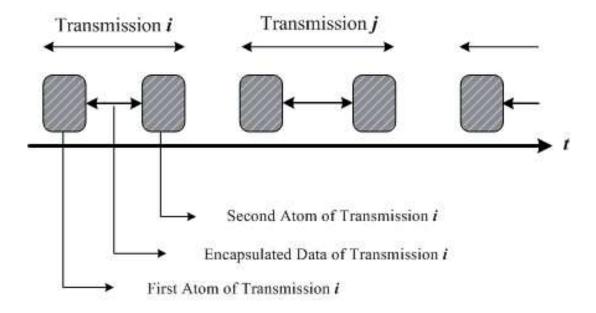

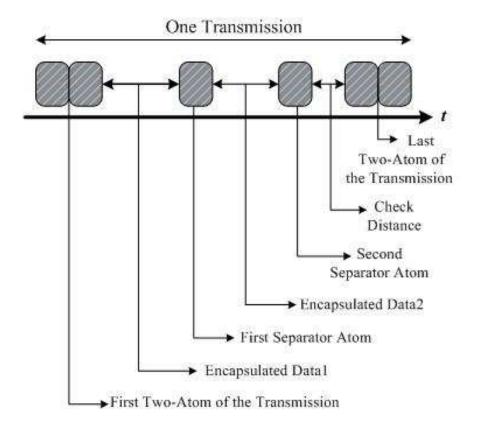

|           | Arrangement of Atoms for Complex Data 1. Every information packet starts with two zero-distanced Atoms which followed with an Atom timed distanced by the data.                                                                                                                                                                         | 97  |

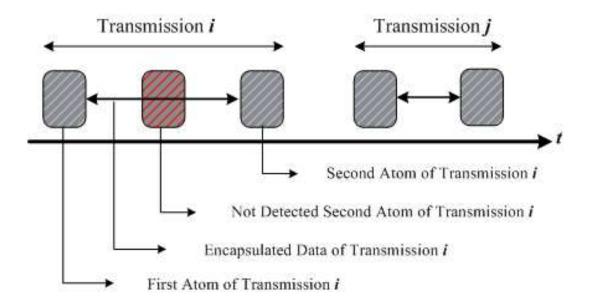

|           | Effect of the losing one Atom detection on miss interpreting the encapsulated data in a two-Atom arrangement system.                                                                                                                                                                                                                    | 98  |

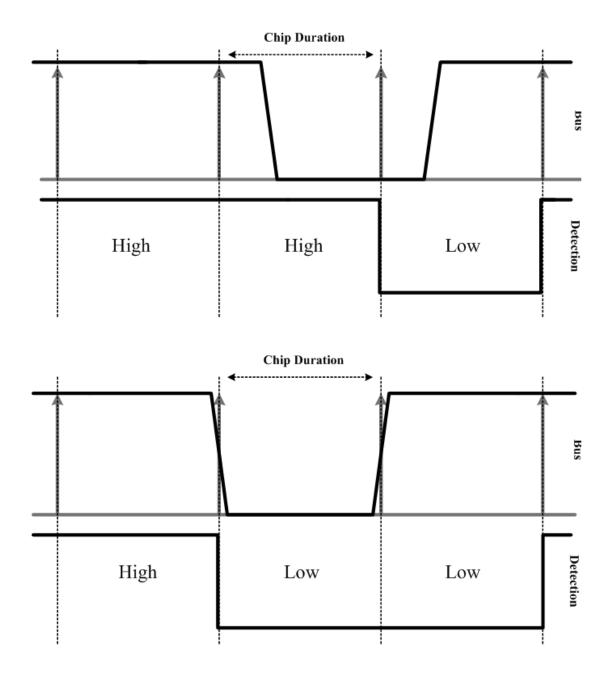

|           | Top diagram shows the situation where the sampling occurs in the middle of a chip, and detection of right. The bottom diagram shows the over detection, where the sampling occurs at the falling edge of a low chip, therefore the next sample coincides with the rising edge of the same chip and may be detected as another low chip. | 99  |

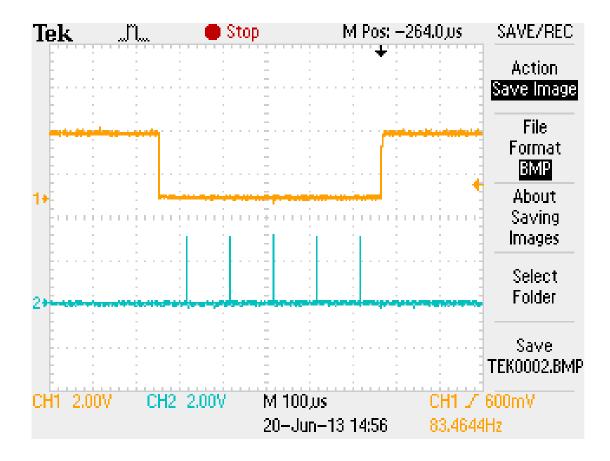

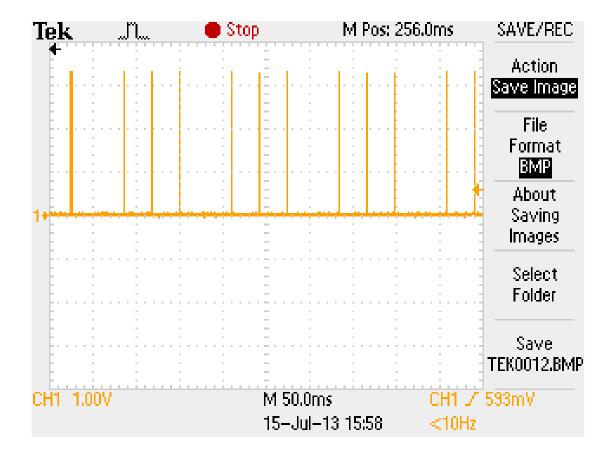

| Figure 56 | Five sub samples (green spikes) are accommodated in a single chip duration (yellow signal.)                                                                                                                                                                                                                                             | 101 |

|           | The chip (yellow signal) is wide enough to accommodate six sub samples.                                                                                                                                                                                                                                                                 | 102 |

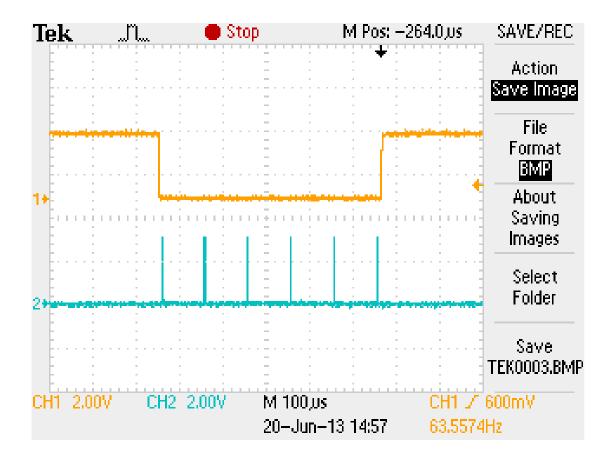

| Figure 58 | Detected Atoms. Every yellow spike shows a detected Atom whose detection time is recorded in the dtcArray.                                                                                                                                                                                                                              | 104 |

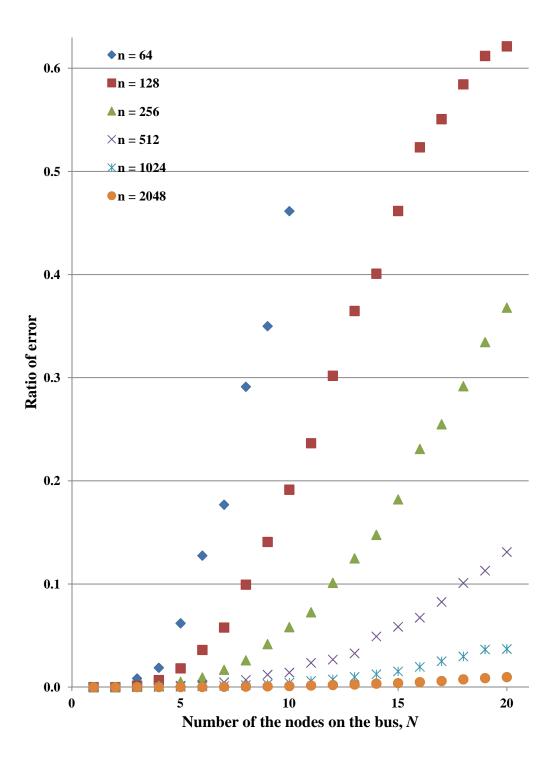

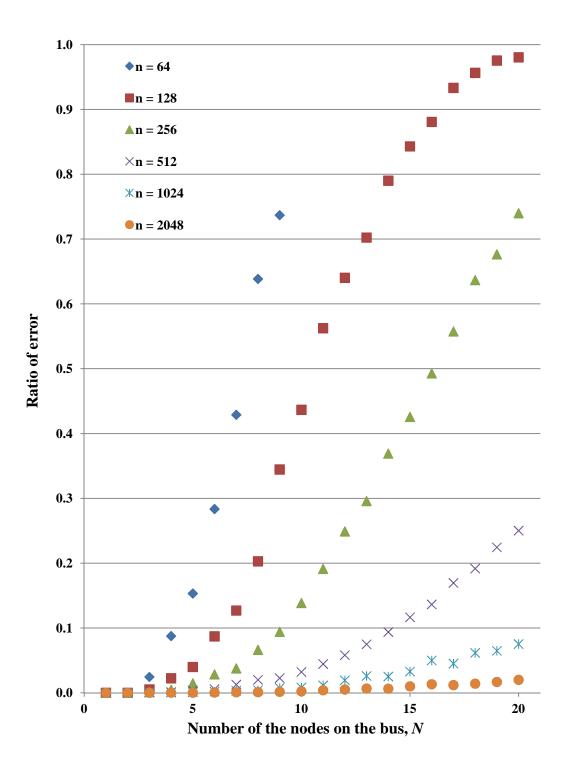

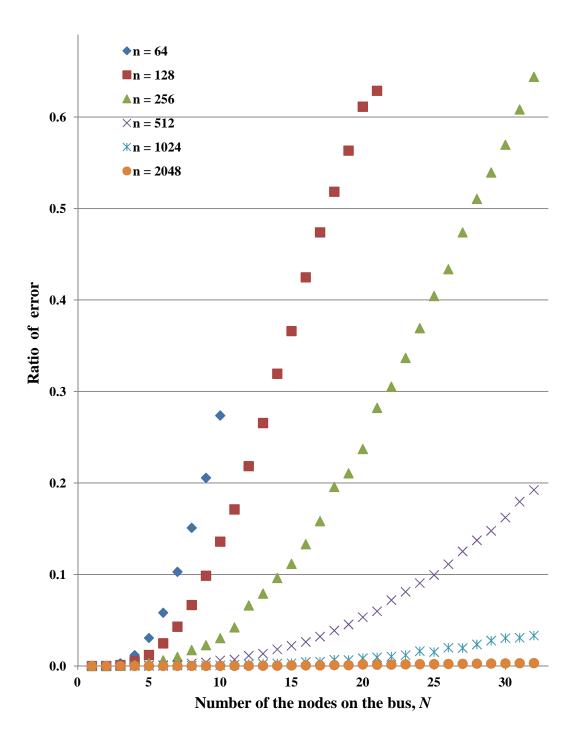

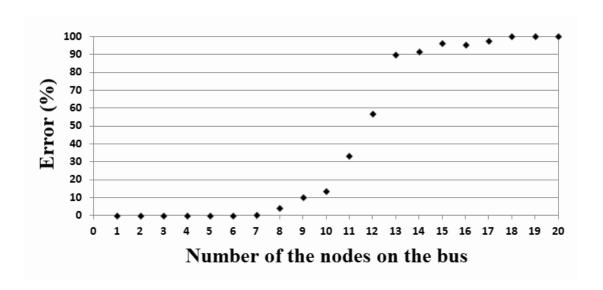

|           | Software simulation of the performance analysis of the detection of the transmitted Atoms versus the number of the nodes on the bus, for different length of the Atoms.                                                                                                                                                                 | 110 |

|           | Software simulation of the performance analysis of the detection of the not-transmitted Atoms versus the number of the nodes on the bus, for different length of the Atoms.                                                                                                                                                             | 111 |

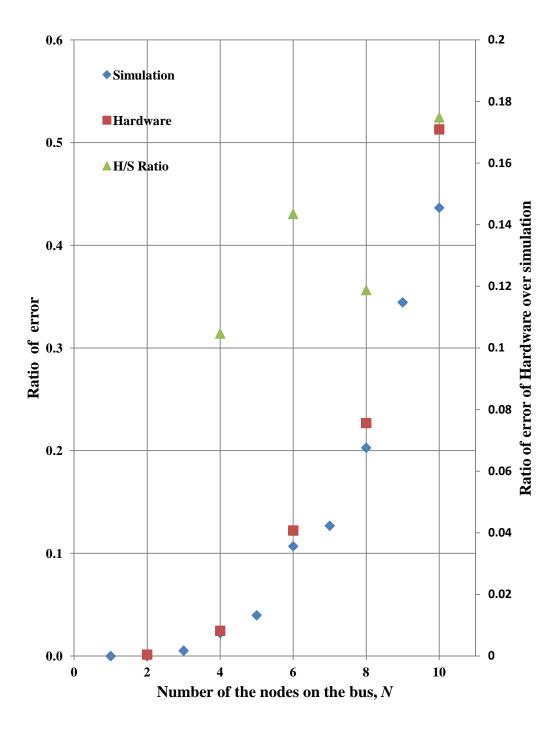

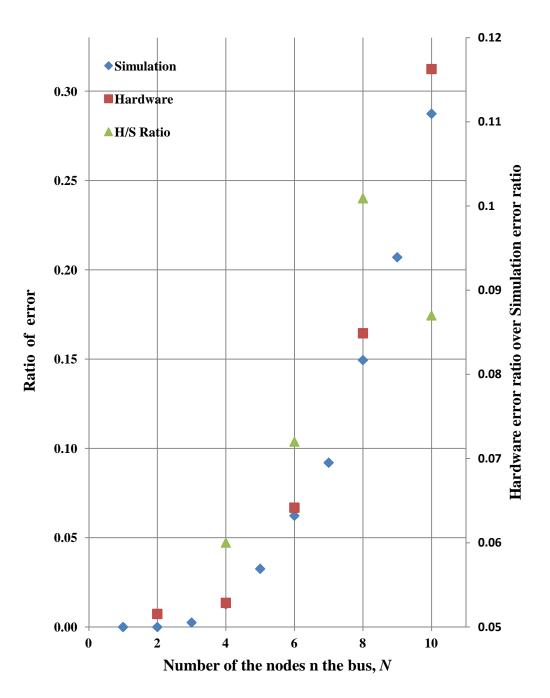

|           | Comparison between the software simulated performance analysis, and experimental result of the hardware, for detection of not-transmitted Atoms.                                                                                                                                                                                        | 112 |

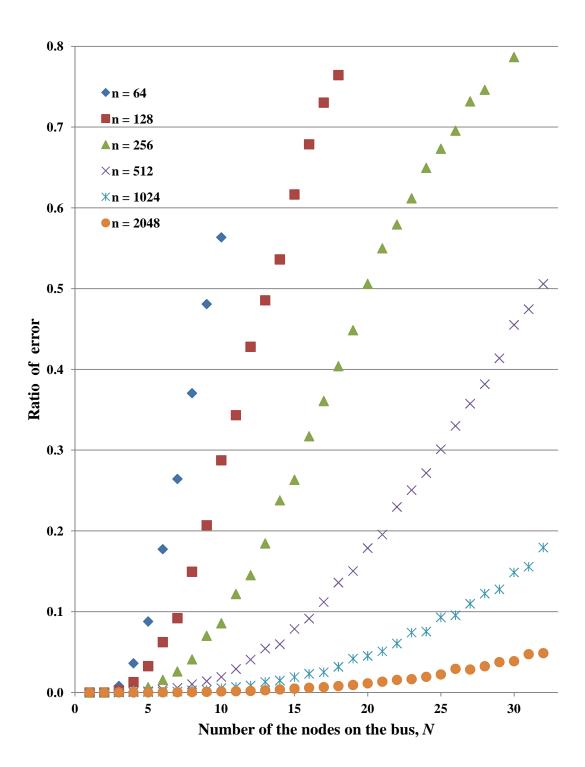

|           | Software simulated performance analysis of the complex data 1 Atom arrangement versus the number of the nodes on bus, for different length of Atoms.                                                                                                                                                                                    | 114 |

|           | Comparison between the software simulated performance analysis, and experimental result of the hardware, for complex data 1 arrangement                                                                                                                                                                                                 | 115 |

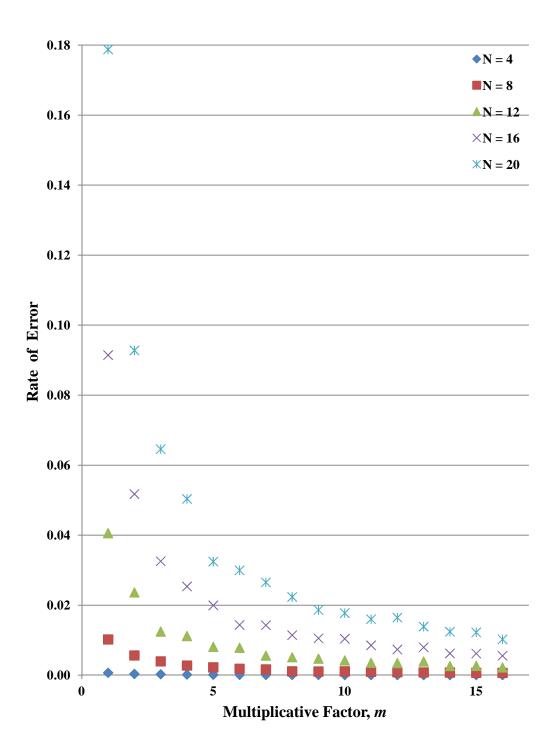

|           | Effect of the multiplicative factor on the rate of error for different length of Atoms with complex data 1 arrangement.                                                                                                                                                                                                                 | 117 |

|           | Arrangement of Atoms in complex data 2 format, in which every packet consisted of six Atoms and to $k$ bit data.                                                                                                                                                                                                                        | 118 |

|           | Software simulated performance analysis for complex data 2 arrangement versus the number of the nodes on the bus, for different length Atoms.                                                                                                                                                                                           | 120 |

|           |                                                                                                                                                                                                                                                                                                                                         |     |

| Figure 67 | The Wired-FDMA based Atoms, and their interaction with the NOR-bus                                                                                                                                                                                                                                                                                                                | .122 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

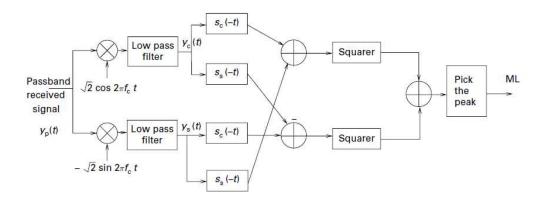

| Figure 68 | Detection process in the traditional DFMA schemes [44]                                                                                                                                                                                                                                                                                                                            | .123 |

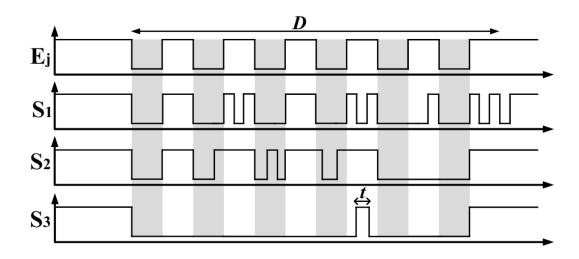

| _         | Detection phase of the Wired-FDMA. Nj is the expected Atom at the receiver side when there is no other transmission on the bus. S1, S2 and S3 are three sample signals which the S1 and S3 are candidates, but S2 is not, because in contrast with other two, it has high value in non-allowed (gray) areas.                                                                      | .124 |

| Figure 70 | A hardware scheme for the detection process of the Wired-FDMA                                                                                                                                                                                                                                                                                                                     | .126 |

| Figure 71 | The simulation result for Wired-FDMA                                                                                                                                                                                                                                                                                                                                              | .127 |

|           | The WirelessBus. This wireless communication is quite similar to the Mesh-Bus setting.                                                                                                                                                                                                                                                                                            | .130 |

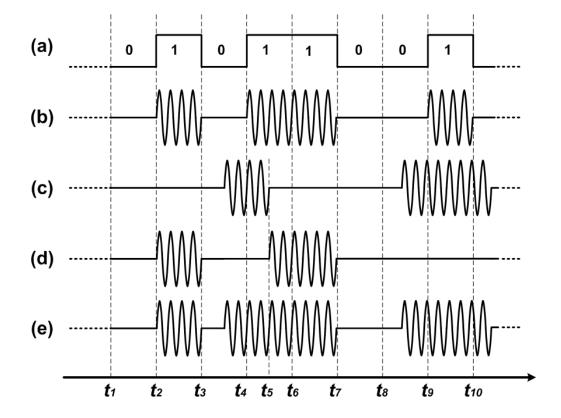

|           | The process of active listening/ virtual transmission. Signals (a) and (b) show the data which is required to be transmitted in two forms of analog waveform and digital string. (c) shows the pre existed signal on the medium, and (d) is what the node physically transmits, base on the condition of the medium. Finally, (e) shows the medium after the transmission of (b). | .132 |

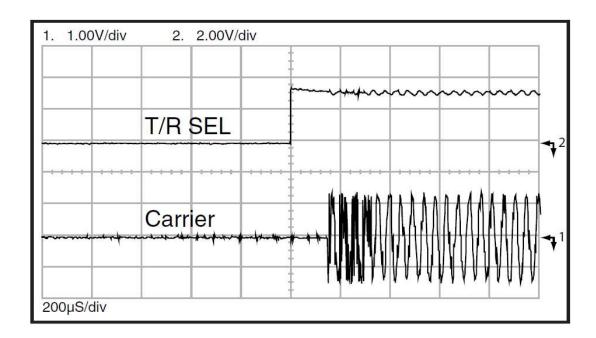

|           | Delay of switching from Rx mode to Tx mode. As the diagram shows, the delay for switching between TX and RX mode is about 150 µs                                                                                                                                                                                                                                                  | .133 |

| Figure 75 | LINX TRM-433-LT radio transceiver module                                                                                                                                                                                                                                                                                                                                          | .135 |

| Figure 76 | The schematic of the Radio-microcontroller board.                                                                                                                                                                                                                                                                                                                                 | .136 |

| Figure 77 | Radio breakout and the microcontroller boards.                                                                                                                                                                                                                                                                                                                                    | .136 |

| Figure 78 | A scenario for testng the WirelessBus scheme consisted of six radios, five transmitters and a receiver.                                                                                                                                                                                                                                                                           | .138 |

# CHAPTER 1 INTRODUCTION

The purpose of this study is to develop the underlying concepts for a new type of bus [2] for serial data communications. This type of bus is full-duplex, digital, binary, and shares just one wire among all the nodes on the bus for bidirectional data communications. We call this the *Mesh-Bus*, see Figure 1.

The goal of the Mesh-Bus is to provide a simple uncoordinated communications channel [3], similar to the concept of the 'ether', for low data rate communications to a group of low complexity sensors. In such a bus, new sensors are able to join the bus at any desired time. New nodes can join an existing communication channel, or form their own, independent channel(s) using the existing communications wire. As long as such new nodes follow a set of primitive rules of the host Mesh-Bus, their communications do not interfere with the existing communications, or will have a minimum and tolerable effect on the performance of the bus. Further, no node is responsible for managing the

Figure 1 The Mesh-Bus, through which *N* nodes communicate bidirectionally over a single wire. A common ground-connection is implied. Although it is a bus, but the nodes are able to form a virtual mesh configuration, because every node is capable of communicationg with any other node at any desired time.

bus, and in this sense, the Mesh-Bus is a distributed [4] bus, without the requirement of a master-slave configuration [5].

Current bus protocols are typically based on Time Division Multiple Access (TDMA) [6], i.e., the shared access to the bus occurs through time sharing. In such protocols, every node has a non-overlapping *timeslot*, during which that node is the sole owner of the bus. Accurate timing of the timeslots is the only mechanism of interference avoidance among the nodes. Thus, nodes need sophisticated hardware resources (such as good clocks) to facilitate accurate timing.

Additionally, the task of assigning and managing the timeslots is a major issue in TDMA-based buses. In the case of dynamic timeslot assignment, there must be a master node on the bus to do the job, and in the case of pre-determined static timeslot assignment, the bus is not able to serve in an uncoordinated way anymore.

Such limitations eliminate the choice of a TDMA-based medium-access for Mesh-Bus. Therefore, the medium access of the Mesh-Bus should be based on an non-TDMA scheme, e.g., Frequency Division Multiple Access (FDMA) [7] or Code Division Multiple Access (CDMA) [8].

The traditional multiple access schemes such as FDMA and CDMA were originally designed for analog, linear communication channels<sup>1</sup>. The communication channel of the Mesh-Bus is nonlinear and digital, and cannot use such schemes directly. Therefore, the main challenge of this study is to develop an appropriate CDMA-based, or FDMA-based, multiple-access scheme for the Mesh-Bus.

\_

<sup>&</sup>lt;sup>1</sup> The nonlinearity of the wireless channels as the result of nonlinear power amplification, analog-digital conversion, etc. [9],the frequency-selectiveness of the fading channels and so on., are addressed by various techniques such as the channel parameter estimation and so on a part of physical layer; therefore, the multiple access schemes, as of MAC layer protocols, function based on the assumption of linearity of the channels.

Chapter 2, the literature review, covers different topologies [10] of network interconnection, and explores the characteristics of buses, as one of such topologies. Then, different types of buses are explored briefly, and a few well-known serial buses, such as RS-485, RS-232, 1-Wire, I<sup>2</sup>C, and SPI are examined. The next section of the literature review explores the concepts of different multiple access schemes such as TDMA, FDMA, and CDMA. In the next section, digital binary channels [11], and their error models are introduced and examined. The chapter concludes with the introduction of Optical Orthogonal Codes [12]. These codes are the unipolar equivalents of the bipolar codes used in traditional CDMA, and were developed for Optical CDMA or OCDMA [13].

Chapter 3 starts with the characteristics and requirements of the Mesh-Bus, and introduces *Bus-Modulators*, which are hardware interfaces between the physical bus and the nodes, and act as bidirectional translators. Next, the concept of *NOR-bus*, as a Wired-OR [14] scheme with the Z-Channel [15] error model, is introduced, and a general detection rule for the NOR-bus is formulized. The concept of *Atoms*, as the specific unary massages with the property of being rather immune to the interference, is introduced and formalized. Atoms provide the required *channels-coding* [16] on a Mesh-Bus. Then, in order to transmit information over the Atom-based channels, an additional *information-coding* scheme is suggested. This information-coding scheme, which relies on the time-distancing of the transmissions of the Atoms, accompanied with the channel-coding scheme, form a double layer coded communication system called *double layered time-distanced unary coding scheme*. This coding scheme, as a general physical layer [17] scheme for the Mesh-Bus, could be employed for both the CDMA-based and the FDMA-based Mesh-Buses of the two following chapters, 4 and 5.

Chapter 4, Wired-CDMA, investigates CDMA-based Atoms, as the channel codes of the Mesh-Bus. It starts with exploring the traditional CDMA scheme and the properties of its codes. This section ends with introducing the near-far problem [18, 19], as the most

problematic issues of the wireless CDMA scheme. Next, OOCs as CDMA-based Atoms are presented in more depth, and their properties are examined. Then, a detection process with a linear computational complexity is suggested for such a scheme. Next, the derivation process of a specific group of OOCs is presented. Some error rate simulations are performed for these OOCs. This section concludes with studying the effects of the dime-distanced information coding scheme on the error rate, and the data rate of the Wired-CDMA.

Chapter 5 explores the hardware implementation of the Bus-Modulators. Such a hardware implementation deals with the electronic circuitry, which is a microcontroller based board, as well as the firmware of the microcontroller which is responsible for the operation of the Bus-Modulator. In this chapter the hardware and the firmware details are presented, and the difficulties and limitations of such an implementation are studied.

Chapter 6 presents the performance analysis for the Wired-CDMA, namely the rate of detection error versus the number of the nodes on the bus. In this chapter, the results of both software simulations and experimental data of the hardware implementation are used for these analyses.

Chapter 7 introduces Wired-FDMA as the FDMA equivalent of Wired-CDMA. For this new scheme, an Atom model and a detection process is suggested and examined. The chapter ends with the presentation of computer simulation results of the error rate in Wired-FDMA.

Chapter 8 introduces the *WirelessBus*, as the wireless equivalent of the Mesh-Bus scheme. The origin of the WirelessBus is the similarities between the NOR-bus and the OOK modulation scheme [20], as a special case of the analog ASK modulation scheme. Wireless communication systems use analog signals for data transmission, and assumes a linear (time-variant) channel models [21]. To address the problems which arise because of the differences between the wireless channel model and the channel model of the Mesh-Bus, a solution, namely *active listening/virtual transmission*, is suggested. This

chapter concludes with presenting the hardware test bed we developed for the WirelessBus, and will be used for experimental evaluation of this scheme in future work.

#### **CHAPTER 2**

#### LITERATURE REVIEW

#### Network Topology and Embedded/Field Bus Protocols

In this section we explore different internetworking topologies that most of the current communication networks are based on, and try to emphasize proper features of a specific one, the *bus* [10] topology. Next, we identify a set of important characteristics of the buses and categorize them. This sections ends with a brief exploration of some of the most popular buses.

#### Bus Topology versus the Others

When it comes to the interconnection of more than two devices in a way that they become able to communicate together, there is not much variety of topology choices. Such a topology should be chosen based on some requirements such as: either the communications are bidirectional or unidirectional, or whether the communications are needed to be possible for every pair of the devices or just among a specific subset of them. The devices are needed to get connected together either pair wise and form a fully-connected mesh, or all the communications no matter from which node toward which one, must pass through a single device which acts as a hub, which in this case they form a star topology. A bus is another popular interconnection topology. A bus is formed when the devices share a common communications medium, and are able to differentiate the communications and specify the ownership of the information content. There are other topologies such as a ring topology, which are outside the scope of our study.

The first and simplest topology is the *mesh* [4] topology. A mesh can be a fully-or partially-connected mesh. Figure 2 shows the case of a fully-connected mesh, where every single pair of devices or nodes has a direct and dedicated connection. In such a topology, there is no need for a management scheme for the interconnection of the nodes. If the pair-wise connection of the nodes supports full duplex communication, every single

node is capable of initiating a communication session with every other node in the network, at any desired time.

The problem with such topologies is the large amount of resources they consume in order to form. In a fully-connected graph of size of n nodes, number of the communication links has complexity of  $O(n^2)$  [10], which is a quite big growth rate. For example, connecting 10 nodes with an average distance of 1 m requires 45 m of wire and 90 connection interfaces. When number of nodes double to 20, the required quantities grow to 190 m of wire, and 380 connection interfaces, which is a quadratic growth rate.

Figure 2 A fully-connected mesh topology. In a fully-connected mesh with n nodes, every node has a direct and dedicated connection to every n-1 other node of the network.

In addition to complete connection between all nodes that the mesh topology provides, it has another very important feature. Namely, all the nodes in such a network could be identical. In other words, the full mesh topology allows that the functionality of all nodes of the network to be the same. There is no need for special node to manage the operation of the network.

Another popular interconnection topology is the *star* [2] or *hub* topology, which in fact is a special case of mesh topology. Here, there is at least one special node in the network, and this node has a direct and dedicated link to every other node in the network. This special node or *hub*, acts as a bridge between different nodes, and manages the connections of all the nodes in the network. Figure 3 shows a star topology interconnection.

Figure 3 A Star topology. The dark gray node is the hub or the master the network. It manages the communications the all network. Communication between nodes every two occurs through the master.

Clearly, since adding a new node to the network requires adding one direct link to the hub, therefore the resource growth is O(n). In this configuration, the hub node is a critical node, and must have enough processing power, bandwidth, and number of the hardware interfaces to service all the other nodes on the bus.

All the communication between the nodes must occur through the hub. Thus, on average, for n nodes, each node gets 1/n of the hub's time and other resources.

Another interconnection topology is the *bus* topology. In such a topology, every node in the network shares a common medium (e.g., set of wires.) Therefore, adding an extra node to the network does not cost any additional resource. However, since all the nodes use a shared resource. Thus, there must be rules to manage the access of the nodes to the shared communication medium. A popular medium access scheme uses the time sharing. In time sharing, every node has a time slot during which it is able to access the medium to read or write data to or from the bus. In order to avoid access interferences, the time slots must be mutually exclusive and non-overlapping. Figure 4 shows the bus topology.

Assigning the mutually exclusive time slots to the nodes of a bus is a highly important task which a special node on the bus decides about. The special node, namely the master node, is the orchestrator of the bus. Communication between the nodes is direct, and does not need to pass through the bus master. Still, the master has a crucial role in the operation of the network. Similar to the star topology resources are shared among the nodes. For n nodes on the bus, a node gets (on average) 1/n of the resources. Table 1 summarizes the features of each the three topologies.

Figure 4 A bus topology. Similar to the star topology, the dark gray node is the master node which orchestrates all the communications which occur through the bus.

Table 1 Comparison between different interconnection topologies.

| Topology | Resource | Distributed | Response Time |

|----------|----------|-------------|---------------|

| Mesh     | $O(n^2)$ | Yes         | Any time      |

| Star     | 0 (n)    | No          | 1/n of times  |

| Bus      | 0(C)     | No          | 1/n of times  |

#### **Bus Types**

The features of the bus topology makes it an attractive candidate for being used in embedded systems applications for interconnecting peripheral devices to the main microcontroller or to each other. Therefore, we will focus on the bus topology for the rest of the study.

The serial buses, based on the distance and data rate they can support, are divided in two groups. One group has some features that make the best option for interconnecting the microcontrollers to the peripheral devices, such as different types of sensors, external low volume memories and so on, which all are on the same board. We call them the embedded buses. The other groups of the buses, namely the field buses, usually are being used for longer distances, and off the board system-to-system communications.

Another important aspect of the serial buses is their dependence on a shared clock signal. Synchronous serial buses [22] are the buses that timing signal is provided to the nodes by the master of the bus. In contrast, there are another group of serial buses, the asynchronous [23] ones, which do not need for such a central timing signal. In the case of asynchronous buses, time synchronization between the nodes occurs through some special sequencing of data bits on the prior to every transmission.

In this study, our focus is on the serial buses. In addition to be a synchronous/ asynchronous or embedded/field bus, followings are some other important characteristics of the buses, which one should consider.

- Data rate

- Bus length

- Signaling type (differential, single ended)

- Number of the nodes on the bus

- Number of the data lines

- Voltage levels

Next, we will introduce some of the well-known buses, and the above mentioned parameters will be specified for them, to show their advantages and disadvantages.

#### Current Serial Bus Standards

There are many industrial standards for serial bus communication that today's devices use, some as very popular ones and some other as proprietary standards that only some licensed product are allowed to use.

One of the most popular and widely used standards for serial communications and bus bases interconnection is Telecommunications Industry Association/Electronic Industries Alliance (TIA/EIA) [24], [25], family of asynchronous serial interfaces. The best-known members of this family are RS-485 and RS-232 standards [26]. Also, RS-422 and RS-423 [27] are other two standards that being used to some extent.

The most-widely used bus protocol of this family, RS-485, is a very flexible protocol. It can be used in both full duplex and half duplex configurations, and it is capable of supporting baud rates as high as 35 *Mbit/s* over short distances. RS-485 uses differential signaling. That is, every bit is transmitted through an inverted signal on one wire, and non-inverted one on another wire. At the receiver, the difference between the two signals is calculated, and original signal is retrieved this way. In such a differential signaling scheme, the effect of interference on the wires signals are often nearly identical and get canceled at the receiver. Figure 5 shows the signal and noise in a differential signaling scheme.

The differential signaling scheme of the RS-485 protocol allows reliable communication up to  $1200 \, m$ . The signal voltage levels of the standard are -/+ 7 volts for such range of transmission.

The standard in full duplex mode has four signal lines and well as a reference pin. Similar to other members of its family, RS-485, encapsulates the ASCII values (7 bits of

Figure 5 Differential signaling scheme. Since the end signal is the difference of the signals on the lines, the effect of noise on the line gets canceled out.

data) between a start bit and some (one or two) stop bits. Figure 6 shows an example of data communication in RS-484, where the sequence of is encapsulated between a start and a stop bit. In this figure,  $U_+$  shows the non-inverted signal and  $U_-$  shows the inverted one.

As another widely-used member of TIA/EIA family, RS-232, is an asynchronous serial communication protocol, which is mainly used in point-to-point, short-distance

Figure 6 Differential signaling and data encapsulation of the binary string: in RS-485.

communications. Its signaling scheme, in contrast with RS-485, is not differential, and it does not support long distance communication. Its data rate is also much less that the RS-485. It supports the baud rate of for short distances, up to , and it is a full duplex protocol.

The two most common configurations of the RS-232 are 3-wires and 5-wires configurations. The 5-wire configuration provides the handshaking capabilities, which is a powerful flow control tool. In RS-232, as in RS-485, the data bits are packed in a data frame. For example, when transmitting ASCII characters, every character's bits are encapsulated between a *start* bit, one or two *stop* bits, and in some cases, as an error-detection mean, a *parity* bit. Figure 7 shows the data encapsulation and additional bits of data frame for RS-232.

The other two well-known members of this family, namely RS-422 and RS-423, are similar to RS-485 and RS-323 protocols. Both are high data rate protocols, where RS-422 uses differential signaling and supports distances up to , and RS-423 uses unbalanced (non-differential) signaling and supports distances up to .

Figure 7 Data encapsulation for USART. It begins with a start bit, the data, one odd parity check bit, and finally two stop bits.

#### 1-Wire Bus

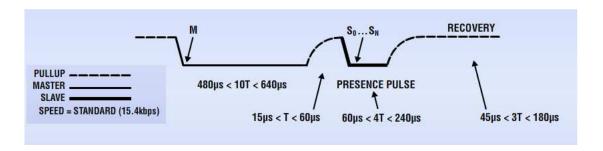

1-Wire [28] [29] is another asynchronous bus protocol which is developed by Dallas Semiconductor Corporation. It is a bidirectional, half duplex, single wire bus protocol that has data rate of 15.4 *kbps* in its standard mode. Every 1-Wire setting requires the presence of a master node on the bus. Communicate through 1-Wire bus, requires that every device has a factory-programmed, unalterable ID [1].

Figure 8 shows the internal circuit diagram of the nodes in a 1-Wire bus. As shown, in a 1-Wire communication setting, the bus itself is consisted of a resistively pulled up single strand of wire, as well as an implied ground wire, and all the nodes are connected to that wire through their open-drain interfaces.

Figure 8 The circuit diagrams of the master and slave nodes in a 1-Wire bus [1].

In such a setting, every communication is initialized by the master, and all the slave nodes synchronize themselves by the falling edge of the clock sequence of the master.

In every time slot, a single bit of data is transferred, where a long duration of low pulse is interpreted as zero, and a short duration low pulse is binary one. The duration of long pulses in standard mode is  $60 \,\mu s$ . Figure 9 shows the time slot in 1-Wire protocol, and Figure 10 shows the read/write request of the master node and the response of a slave.

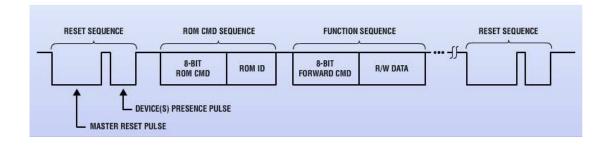

Every communication in a 1-Wire setting has the three following phases of transaction; (1) device reset/synchronization, (2) ROM command sequence, and (3) function sequence. Figure 2.11 shows these three sequences, which are explained below.

#### 1. Device Reset/Synchronization

In this phase, the master pulls the bus low for more than 480  $\mu$ s, and then releases it for the period of 15 to 60  $\mu$ s. Now all the slave nodes pull the line low for 60 to

Figure 9 The time slot in the standard mode of 1-Wire bus [1].

Figure 10 The master's read/write request in standard mode 1-Wire bus [1].

$240 \,\mu s$ . This is known as the presence pulse. By the end of the period of the presence pulse, the slaves release the line and let go back to high state or recovery. In such a state, all the nodes are in known synchronized state, and ready to communicate. Figure 12 shows the reset phase.

#### 2. ROM command sequence

In this phase, the master chooses a specific slave node based on its ID. In this way, all nodes one the bus one go to waiting mode and stay passive until the next reset phase. The ID which the master uses to identify and choose the target slave node is an unalterable, preprogrammed 64 bit string which all the 1-Wire capable devices must have.

Figure 11 The three phases of communication on a 1-Wire bus [1].

### 3. Function sequence

In the third phase, or the function sequence, the actual data transfer occurs through read and write requests initiated by the master, and responded by the selected slave node in phase two.

Figure 12 The first phase of 1-Wire communication: device reset/synchronization [1].

## I<sup>2</sup>C Bus

The Inter-Integrated Circuit, or I<sup>2</sup>C [30], protocol is a synchronous serial bus originally developed by Philips Semiconductors in the 1980's. It is a low-data rate bus protocol which is widely used in current days' embedded systems in order to provide the required interconnection between the microcontrollers and the peripheral devices.

The  $I^2C$  standard has two bidirectional open drain interfaces which both are resistively pulled up to  $\,$ , one signal line (SDA) for half-duplex data communication, and the other one (SCL) for the clock signal. A ground wire is also required. Figure 13 shows the  $I^2C$  bus configuration. The configuration of the bus is a master-slave, and more than one master is allowed on the bus.

Figure 13 The bus. Both lines, the data and clock lines, are pulled up to through resistors.

For every communication, the master node puts the address of the slave node it wants to communicate with on the bus. All slaves on the bus see the address, but only the node that matches the address responds and the master-slave communication channel is formed.

In the I<sup>2</sup>C protocol, the data is encapsulated between a start and a stop signal. As shown in Figure 14, both data and clock lines remain High when the bus is not busy. A High-to-Low transition of the data line, while the clock is High is defined as the start condition (see the shadowed area S). When a Low-to-High transition of the data line [30]occurs while the clock is High the stop condition take places (see the shadowed area P). The I<sup>2</sup>C protocol has a 7 bits (10 bit) address space, and supports the data rate of 10 kbps to 100 kbps. The mechanism of error detection of I<sup>2</sup>C bus is through ACK/NACK messages. Each byte of eight bits is followed by an acknowledgement bit (ACK). Upon transmission of the 8<sup>th</sup> bit, the master releases the SDA line, which goes HIGH, the master generates an ACK clock pulse, and the slave acknowledges by pulling the SDA line low. A master receiver must generate an acknowledgement after the reception of each byte that has been clocked out of the slave transmitter. Also, a master receiver must

Figure 14 The start (the shadowed area S) and stop (the shadowed area P) conditions of I2C bus protocol.

generate an acknowledgement after the reception of each byte that has been clocked out of the slave transmitter. Figure 15 shows this process.

A master receiver must signal an end of data to the transmitter by not generating an acknowledgement on the last byte that has been clocked out of the slave (NACK). In this event, the transmitter must leave the data line HIGH to enable the master to generate a stop condition.

Figure 15 Process of data acknowledgement between the master and slave in the I<sup>2</sup>C bus.

#### SPI Bus

The Serial Peripheral Interface, SPI [30], is a synchronous bus protocol. It is a full-duplex communication protocol, and the presence of a master node is necessary for every communication.

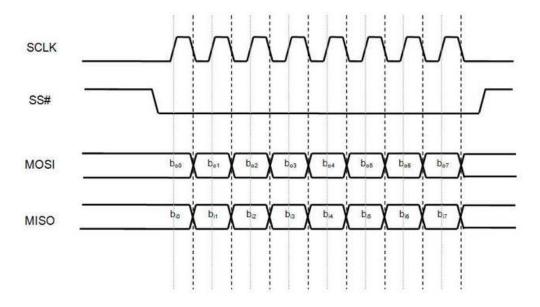

The main disadvantage of the SPI buses is that for every slave node on the bus, a chip select signal is required. Apart from the chip select signals, all the nodes on the bus share three signals of, serial clock (SCLK), master output, slave input (MOSI), and master input, slave output (MISO). Figure 16 and 17 show the SPI bus, as well as its signaling scheme.

Figure 16 The SPI bus, and the data and chip select lines.

Figure 17 Signaling of the SPI bus.

# Multiple Access Schemes

In situations where the communication medium as a resource (time, frequency spectrum, and physical links) is limited, the communicating devices must share the available resource. There are some well-known schemes that regulate this medium sharing process, which is called the multiple access schemes (MACs).

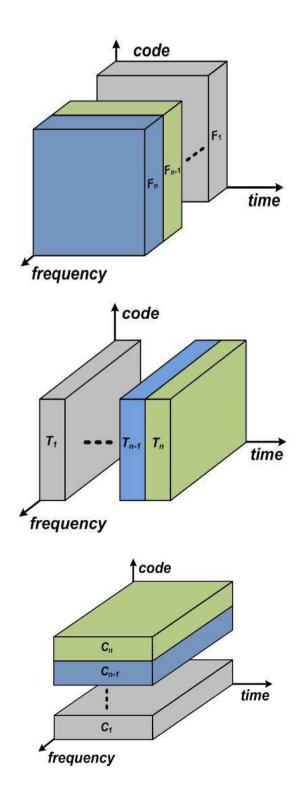

There are different multiple access schemes available such as TDMA, FDMA, CDMA, SDMA [31], OFDM [32] and so on. In the following sections, we briefly introduce the most important ones of them, and show some of their features. Also, Figure 18 conceptually summarizes some of these multiple access schemes.

Figure 18 The multiple access schemes of FDMA, TDMA, and CDMA.

#### **TDMA**

TDMA [6], which stands for time division multiple access, is a popular multiple access scheme. TDMA is based on the concept of time sharing, and requires a predetermined setting for every node that wants to use such a scheme. The total available time in which the communication media is accessible is divided to specific number of non-overlapping time intervals or time slots. Every node in the scheme is allowed to access the bus only during the time slot which is assigned to it.

The structure of such scheme mandates that at any given time instance, only one node access the medium i.e., just one node is allowed to put data on the bus. However, if the time slots are designed short enough that all the nodes be able to have adequate number of time slots frequently enough for their data communications, one can say that every node has access to the medium all the time, and in essence, the nodes share the medium.

In such scheme (in contrast with FDMA, see next section) the every node is allowed to occupy all the frequency spectrum that such a TDMA scheme allocates, and usually (in contrast with CDMA, see the following section) the transmitted data is not specifically coded for the communication channel.

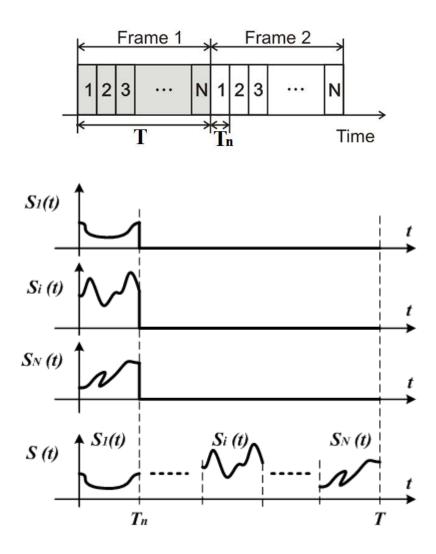

Consider a signal  $S_i(t)$ , where  $i \in \{1, 2, ..., N\}$  and assume its information content is confined to time duration of  $T_n$  defined as follows:

$$S_i(t) = \begin{cases} info & 0 \le t \le T_n \\ 0 & T_n < t < T \end{cases}$$

Where,

$$T_n \leq \left| \frac{T}{N} \right|$$

Then, is a timed-delayed non-overlapping summation of the signals arranged side by side in a time frame, as Figure 19 shows.

Figure 19 The frames of TDMA with *N* time slots. The time slots do not overlap with each other, and usually there are some guard time between every two time slots.

#### **FDMA**

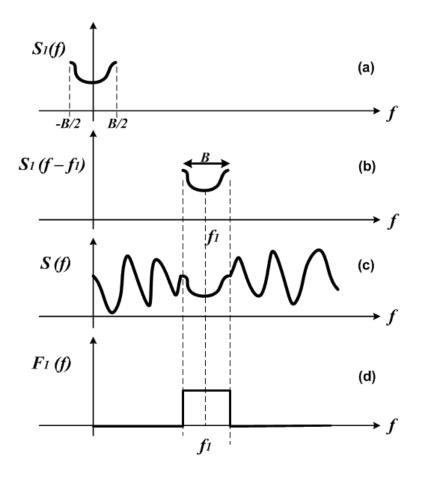

The next shared medium access scheme, frequency division medium access, FDMA [7], takes advantage of the available frequency spectrum by forming different communication channels in different frequency ranges. In this way, every pair of nodes can have an all-time accessible communication channel.

FDMA operates by modulating the different baseband signals to non-overlapping frequency bands, and transmits all of them together. Since the information transmissions are at different frequency bands, they do not interfere with each other. Of course, the frequency separation must be chosen in a way that the frequency bands have minimum possible overlapping when they get filtered out at the receivers.

Assuming that signal  $s_i(t)$  with the frequency spectrum of  $S_i(f)$  with bandwidth less that B/2 Hz ( $S_i(f) = 0$ ,  $|f| \ge B/2$ ), One can up-convert it to the frequency  $f_i$ , where:

$$\forall i, j \in \{1, 2, ..., N\}, |f_i - f_j| \ge B$$

Then, it is guaranteed that the superposition of all the signals, s(t), with frequency spectrum of S(f) as follows, can be transmitted without any interference by other signals.

$$S(f) = \sum_{i=1}^{N} S(f - f_i)$$

Figure 20 show the process of up-conversion, transmission, filtering, and down conversion of hypothetical signal  $s_1(t)$ . Part (a) shows the frequency spectrum of the band limited signal as  $S_1(f)$  which is a baseband signal with bandwidth of B Hz. Part (b)

Figure 20 The processes of FDMA. (a) The baseband signal (b) up-converted signal to frequency  $f_1$  (c) the occupation of frequency spectrum, (d) the filter at the receiver.

shows the very same signal translated to the center frequency of  $f_1$ . The next signal, S(t), shown in part (c), is the superposition of all the N translated (up converted) signals. Part (d) shows filter  $F_1(f)$ , a band pass filter with the bandwidth of B, which is the same bandwidth as  $S_{1(f)}$ . Such a filter is designed to filter out every frequency components of S(t) except for the ones for  $S_1(f - f_1)$ . The result of down-conversion of band pass  $S_1(f - f_1)$  to its baseband equivalent is the  $S_1(f)$ , the original signal.

Clearly, that as long as the information content of every channel is limited to the specified frequency limit, all the nodes are capable of transmitting and receiving their signals at any time instant they want to (in contrast with TDMA), without any channel coding (in contrast with CDMA.)

Examples of FDMA are very widespread: first generation of mobile telephone communication, ordinary commercial radio, TV all use FDMA as their multiple access schemes. Further, OFDM, as a variation of FDMA with overlapping frequency channels, is widely used in modern wired and wireless application, such as the various variants of DSL technologies (e.g., ADSL, HDSL, VDSL) as well as WLANs (e.g., IEEE 802.11a/n), WMAN (WiMAX or IEEE 802.16), LTE, DVB, DAB and so on.

#### **CDMA**

Code Division Multiple Access, CDMA [8], as another multiple access schemes, allows the simultaneous access of the medium through coding the information by some *spreading* sequences. In this scheme, every node has a unique code, or spreading sequence, and though this code, it is allowed to transmit its data at any time instant. Such codes usually have much higher bandwidth than the actual data; therefore, when the data is coded by them, the frequency spectrum of the data expands as well, here comes the name *Direct Sequence Spread Spectrum* [33] [34] technique. The advantage of Spread Spectrum Spread Spectrum (DSSS for short) is providing better signal to noise ratio[35], as well as multiple access communication channel through in case of CDMA i.e., it allows multiple accesses to medium if the codes of the spreading sequences are chosen properly.

In a DSSS scheme, if the codes are chosen as follows, they can be used as codes in a CDMA scheme to provide multiple accesses to a communication system.

- 1. Every pair of codewords in a code is orthogonal

- 2. The codewords of every code is normalized by its power

Such codes are called orthonormal [33] codes. The following formulas show the continuous and discrete forms of the orthonormality.

$$< C_i, C_j > = \int_{-\infty}^{+\infty} C_i(t) \cdot C_j^*(t) dt = \begin{cases} 1, & i = j \\ 0, & i \neq j \end{cases}$$

$$< C_i, C_j > = \sum_{k=-\infty}^{+\infty} C_i[k] \cdot C_j^*[k] = \begin{cases} 1, & i=j \\ 0, & i \neq j \end{cases}$$

Assuming that there are n pairs of transmitter and receivers in a CDMA scheme, and they want to transmit their messages. Transmitter i, multiplies its message  $m_1(t)$  by its unique code  $c_1(t)$  and transmits it. Therefore, the transmission of node i, is  $S_i(t) = m_i(t) \cdot c_i(t)$ . Assuming all the n nodes do the same thing, the total transmitted signal of all of the transmitters together is as follows:

$$S(t) = \sum_{i=0}^{n-1} S_i(t) = \sum_{i=0}^{n-1} m_i(t) \cdot c_i(t)$$

$$= m_1(t) \cdot c_1(t) + \dots + m_i(t) \cdot c_i(t) + \dots + m_n(t) \cdot c_n(t)$$

At the receiving end, if a receiver wants to receive the message of the transmitter i, it calculates the inner-product of the S(t), and the  $c_i(t)$  through its correlation-based detector, and the result is as follows:

$$< S, c_i > = < \sum_{i=0}^{n-1} m_i(t) \cdot c_i(t) , c_i > =$$

$$<\{m_1(t)\cdot c_1(t) + \dots + m_i(t)\cdot c_i(t) + \dots + m_n(t)\cdot c_n(t)\}, c_i> = \\ m_1(t)\cdot < c_1, c_i> + \dots + m_i(t)\cdot < c_i, c_i> + \dots + m_n(t)\cdot < c_n, c_i> \\ = m_i(t)$$

Figure 21 shows the CDMA process transmission and detection processes

Figure 21 The processes of transmission and detection in CDMA scheme.

There are groups of well-studied codes for CDMA scheme with very interesting properties such as Walsh codes, Maximal Length sequences, Gold Codes, and etc., which will be explored in chapter 4.

## **Z-Channel**

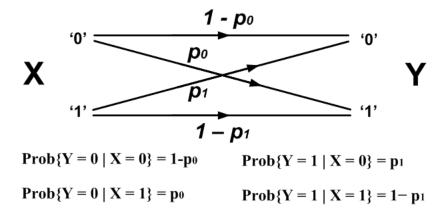

There several models for a digital communications channel. For example, binary symmetric channel (BSC), binary asymmetric channel (BAC), binary erasure channel (BEC), and so on [36]. The choice of the proper model depends on the characteristics of the application. Figure 22 shows the general model of a binary channel and associated error probability.

In our study, since we are going to use a NOR channel (NOR-bus will be introduced in next chapter). It is a nonlinear, asymmetric channel, which is best modeled with the binary asymmetric channel.

In a binary symmetric channel, where  $p_0 = p_1$ , the probability of a '0'  $\rightarrow$  '1' error is the same as the probability of a '0'  $\rightarrow$  '1' error. On the other hand, in a binary asymmetric channel, in contrast with binary symmetric channel the probability of error

Figure 22 The Binary symmetric channel model. X is the input random variable, and Y is the output random variable.

for '0'  $\rightarrow$  '1' is not the same as '1'  $\rightarrow$  '0', therefore it is a asymmetric channel.

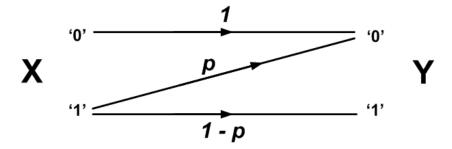

A special case of the binary asymmetric channels, where  $p_0 = 0$ , (the probability of '0'  $\rightarrow$  '1' error is zero,) the shape of the error model of the channel is in form of English letter 'Z'; therefore, it is named Z-Channel [15]. Figure 23 shows the Z-Channel model and the error probability model of it is as follows:

$$Prob\{Y = 0 \mid X = 0\} = 1$$

$Prob\{Y = 0 \mid X = 1\} = p$

$Prob\{Y = 1 \mid X = 0\} = 0$

$Prob\{Y = 1 \mid X = 1\} = 1 - p$

The Z-channel finds application in modeling the errors in storage media such as disk drives and RAM chips.

Figure 23 The Binary asymmetric channel model. X is the input random variable, and Y is the output random variable.

## Optical Orthogonal Codes (OOCs)

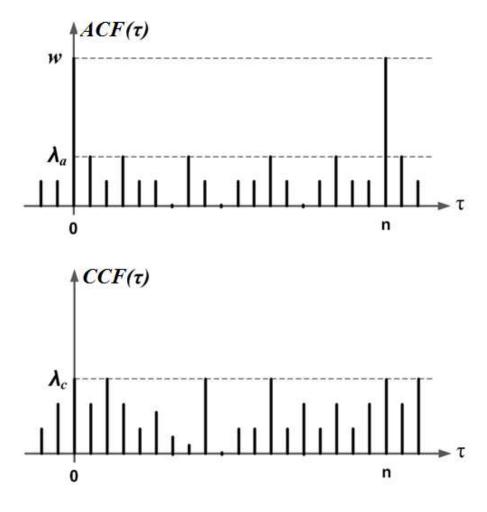

The unipolar optical orthogonal codes [12] [13], which will be used in this study, are a group of codes that are used in unipolar fiber optic communications. An OOC code is a group of binary ('0' and '1' bits) strings with general notation of:

$$(n, w, \lambda_a, \lambda_c) - 00C$$

Where n the length of the string is, w is the Hamming weight (number of the '1' bits in the string) of the strings, and  $\lambda_a$  and  $\lambda_c$  are circular autocorrelation and cross correlation functions of the codewords, respectively.  $\lambda_a$  and  $\lambda_c$  are defined as follows. Assuming  $c^i = (c^i_0, c^i_1, \dots c^i_{n-1})$  and  $c^j = (c^j_0, c^j_1, \dots c^j_{n-1})$ , (where  $c^k_l \in \{'0', '1'\}$ ,) are two distinct codewords of  $(n, w, \lambda_a, \lambda_c) - OOC$ . The circular autocorrelation function of a codeword defined as follows. For every codeword  $c^i \in (n, w, \lambda_a, \lambda_c) - OOC$

$$ACF(\tau) = \sum_{\substack{l=0 \\ \tau \neq 0}}^{n-1} c_l^i \cdot c_{l \oplus \tau}^i \le \lambda_a$$

Since this formula is a circular function,  $l \oplus \tau \triangleq (l + \tau) \mod n$  and for the special case of  $\tau = 0$ , we will have

$$ACF(0) = \sum_{l=0}^{n-1} c_l^i = w$$

For circular cross correlation, the definition is as follows:

$$CCF(\tau) = \sum_{\substack{l=0\\i\neq j}}^{n-1} c_l^i \cdot c_{l\oplus \tau}^j \le \lambda_c$$

The Figures 24 shows the autocorrelation function and cross correlation function a  $(n, w, \lambda_a, \lambda_c)$  – 00C respectively.

Figure 24 The autocorrelation function (top,) and cross correlation function (bottom) of the  $(n, w, \lambda_a, \lambda_c) - OOC$ .

The number of the codewords in a  $(n, w, \lambda_a, \lambda_c) - OOC$  is called the *cardinality* of the code, and is denoted by |C|. On the other hand, the maximum possible number of an OOC code  $(|C|_{max})$  is denoted by  $\Phi(n, w, \lambda_a, \lambda_c)$ . In general, there is no formula for calculating the maximum cardinality of an OOC, but as [12] shows, it is possible to derive the following upper bound (based on the Johnson upper bound for error correcting codes [37]) and lower bound (based on the greedy algorithm for construction of OOC's) for the cardinality of the  $(n, w, \lambda_a, \lambda_c) - OOC$ .

$$\phi(n, w, \lambda_a, \lambda_c) \leq \frac{(n-1).(n-2)...(n-\max\{\lambda_a, \lambda_c\})}{w.(w-1)...(w-\max\{\lambda_a, \lambda_c\})}$$

$$\phi(n, w, \lambda_a, \lambda_c) \ge \frac{\binom{n}{w} - \frac{n-1}{2} \binom{w}{\lambda_a + 1} \binom{n}{w - \lambda_a - 1}}{n \cdot \sum_{i=\lambda_c+1}^{\min \{n-w,w\}} \binom{n-w}{w-i} \binom{w}{i}}$$

When the number of discovered codewords for a  $(n, w, \lambda_a, \lambda_c) - OOC$  reaches the maximum possible (i.e.,  $|C| = |C|_{max} = \Phi(n, w, \lambda_a, \lambda_c)$ ), the code is considered an *optimal* [13, 38] code.

### CHAPTER 3

#### THE MESH-BUS

# Introduction

Experimental research in geosciences often involves deploying a number of sensors along with an attendant data logger. Deploying redundant sensors can enhance data reliability and quality. However, increasing the number of the sensors also increases the complexity and cost of connecting the sensors to the data-logging equipment.

By far the most common method of connecting sensors to a data logger is through a star configuration: the logger is at the canter and there is a terminal block with a set of connectors and wires dedicated to each sensor. This works well with a few sensors, but becomes problematic for a large number of sensors. For one, a user may not have enough ports on the data logger. Secondly, the number of wires one has to manage becomes unwieldy and expensive. The expense of high-quality cabling that will hold up to harsh weather conditions comes as a surprise to those that have not deployed and operated environmental field equipment.

An alternative to the star configuration is a bus where multiple sensors share a common set of wires that provide a shared communication channel, and may also supply power. Figure 25 depicts this arrangement. Since the bus is a shared resource, sensors on the bus need a compatible electrical or physical (PHY) interface. Sensors also need a scheme for medium access control (MAC) to the bus [17]. The payoff for this added complexity is lower cabling costs and simpler cable management.

Buses [10] are widely used in embedded systems. A non-exhaustive list of bus standards are I<sup>2</sup>C, SPI, CAN, Modbus. Some of these busses such as SPI are CPU/MCU busses, designed for interfacing peripherals located in close proximity (often on the same PCB) to a microcontroller. Other busses such as CAN are field busses designed for integrating heterogeneous sensors and actuators into a larger system. Field busses are

Figure 25 Traditional TDMA-based buses use sets of wires that form the buss, and the nodes on the bus must be configured as one Master and some Slave nodes.

widely used in industrial and automotive applications. *Field busses* are fully developed, providing definitions for the physical (PHY) layer, medium access control (MAC), data link layer, application layer, and so on. There are also bus standards that are not full field busses, but address the PHY and to some extent the MAC layers. An example is the RS-485 bus standard that is used in industry and also finds application in environmental sensing.

The aforementioned busses use Time Division Multiple Access as Medium Access Control (TDMA-MAC) to manage the access of the sensors to the common bus. Only a single sensor is allowed to transmit on the bus at any given time. Either sensors have pre-assigned time slots or, perhaps more commonly, there is a bus master that manages the other devices' (slaves) access to the bus.