Theses and Dissertations

Spring 2011

# On low power test and low power compression techniques

Elham Khayat Moghaddam University of Iowa

Copyright 2011 Elham khayat moghaddam

This dissertation is available at Iowa Research Online: http://ir.uiowa.edu/etd/997

#### Recommended Citation

Khayat Moghaddam, Elham. "On low power test and low power compression techniques." PhD (Doctor of Philosophy) thesis, University of Iowa, 2011. http://ir.uiowa.edu/etd/997.

Follow this and additional works at: http://ir.uiowa.edu/etd

# ON LOW POWER TEST AND LOW POWER COMPRESSION TECHNIQUES

## by

# Elham Khayat Moghaddam

## An Abstract

Of a thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

May 2011

Thesis Supervisor: Professor Sudhakar M. Reddy

#### **ABSTRACT**

With the ever increasing integration capability of semiconductor technology, today's large integrated circuits require an increasing amount of data to test them which increases test time and elevated requirements of tester memory.

At the same time, as VLSI design sizes and their operating frequencies continue to increase, timing-related defects are high proportion of the total chip defects and atspeed test is crucial. DFT techniques are widely used in order to improve the testability of a design. While DFT techniques facilitate generation and application of tests, they may cause the test vectors to contain non-functional states which result in higher switching activities compared to the functional mode of operation. Excessive switching activity causes higher power dissipation as well as higher peak supply currents. Excessive power dissipation may cause hot spots that could cause damage the circuit. Excessive peak supply currents may cause higher IR drops which increase signal propagation delays during test causing yield loss.

Several methods have been proposed to reduce the switching activity in the circuit under test during shift and capture cycles. While these methods reduce switching activity during test and eliminate the abnormal IR drop, circuits may now operate faster on the tester than they would in the actual system. For speed related and high resistance defect mechanisms, this type of undertesting means that the device could be rejected by the systems integrator or by the end consumer and thus increasing the DPPM of the devices. Therefore, it is critical to ensure that the peak switching activity generated during the two functional clock cycles of an at-speed test is as close as possible to the functional switching activity levels specified for the device.

The first part of this dissertation proposes a new method to generate test vectors that mimic functional operation from the switching activity point of view. It uses states obtained by applying a number of functional clock cycles starting from the scan-in state

of a test vector to fill unspecified scan cells in test cubes. Experimental results indicate that for industrial designs, the proposed techniques can reduce the peak capture switching on average by 49% while keeping the quality of test very close to conventional ATPG.

The second part of this dissertation addresses IR-drop and power minimization techniques in embedded deterministic test environment. The proposed technique employs a controller that allows a given scan chain to be driven by either the decompressor or pseudo functional background. Experimental results indicate an average of 36% reduction in peak switching activity during capture using the proposed technique.

In the last part of this dissertation, a new low power test data compression scheme using clock gater circuitry is proposed to simultaneously reduce test data volume and test power by enabling only a subset of the scan chains in each test phase. Since, most of the total power during test is typically in clock tree, by disabling significant portion of clock tree in each test phase, significant reduction in the test power in both combinational logic and clock distribution network are achieved. Using this technique, transitions in the scan chains during both loading of test stimuli and unloading of test responses decrease which will permit increased scan shift frequency and also increase in the number of cores that can be tested in parallel in multi-core designs. The proposed method has the ability of decreasing, in a power aware fashion, the test data volume. Experimental results presented for industrial designs demonstrate that on average reduction factors of 2 and 4 in test data volume and test power are achievable, respectively.

| Abstract Approved: |                      |   |

|--------------------|----------------------|---|

| 11                 | Thesis Supervisor    |   |

|                    |                      |   |

|                    |                      |   |

|                    | Title and Department | _ |

|                    | Title and Department |   |

|                    |                      |   |

|                    | <u></u>              | _ |

|                    | Date                 |   |

## ON LOW POWER TEST AND LOW POWER COMPRESSION TECHNIQUES

by

Elham Khayat Moghaddam

A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

May 2011

Thesis Supervisor: Professor Sudhakar M. Reddy

# Copyright by

# ELHAM KHAYAT MOGHADDAM

2011

All Rights Reserved

# Graduate College The University of Iowa Iowa City, Iowa

| CE                     | RTIFICATE OF APPROVAL                                                                              |             |

|------------------------|----------------------------------------------------------------------------------------------------|-------------|

|                        | PH.D. THESIS                                                                                       |             |

| This is to certify tha | t the Ph.D. thesis of                                                                              |             |

| ]                      | Elham Khayat Moghaddam                                                                             |             |

| for the thesis require | by the Examining Committee ement for Doctor of Philosophy and Computer Engineering at the May 2011 | graduation. |

| Thesis Committee:      | Sudhakar M. Reddy, Thesis Supervisor                                                               |             |

|                        | Janusz Rajski, Thesis Advisor                                                                      |             |

|                        | Jon G. Kuhl                                                                                        |             |

|                        | David R. Andersen                                                                                  |             |

| -                      | Xiaodong Wu                                                                                        |             |

|                        | Hantao Zhang                                                                                       |             |

To my parent

#### **ACKNOWLEDGMENTS**

I welcome this opportunity to express my heartfelt gratitude to my advisor, Professor Sudhakar M. Reddy for the guidance, candor, encouragement, patience and support which he has provided me throughout the years needed to complete this work. I would also like to express my appreciation and sincere thanks to my supervisor, Dr. Janusz Rajski, who guided and encouraged me throughout my studies. His advice and research attitude have provided me with a model for my entire future career.

My sincere thanks are given to my advisory committee members, Professor Jon Kuhl, Professor David Andersen, Professor Xiaodong Wu and Professor Hantao Zhang for their comments and advices on this work.

I want to thank my friends at the Mentor Graphics Corp. and University of Iowa especially Xijiang Lin, Chen Wang, Santiago Remersaro, Mark Kassab and Nilanjan Mukherjee for their sharing and help.

Word cannot express my feelings of gratitude to my parent and my husband for their love, continual encouragement and support throughout this work.

Finally, I would like to dedicate this dissertation to the memory of my father. I am deeply indebted to him for his love, continued support and unwavering faith in me. He will be with me forever, in my heart and memories.

#### **ABSTRACT**

With the ever increasing integration capability of semiconductor technology, today's large integrated circuits require an increasing amount of data to test them which increases test time and elevated requirements of tester memory.

At the same time, as VLSI design sizes and their operating frequencies continue to increase, timing-related defects are high proportion of the total chip defects and atspeed test is crucial. DFT techniques are widely used in order to improve the testability of a design. While DFT techniques facilitate generation and application of tests, they may cause the test vectors to contain non-functional states which result in higher switching activities compared to the functional mode of operation. Excessive switching activity causes higher power dissipation as well as higher peak supply currents. Excessive power dissipation may cause hot spots that could cause damage the circuit. Excessive peak supply currents may cause higher IR drops which increase signal propagation delays during test causing yield loss.

Several methods have been proposed to reduce the switching activity in the circuit under test during shift and capture cycles. While these methods reduce switching activity during test and eliminate the abnormal IR drop, circuits may now operate faster on the tester than they would in the actual system. For speed related and high resistance defect mechanisms, this type of undertesting means that the device could be rejected by the systems integrator or by the end consumer and thus increasing the DPPM of the devices. Therefore, it is critical to ensure that the peak switching activity generated during the two functional clock cycles of an at-speed test is as close as possible to the functional switching activity levels specified for the device.

The first part of this dissertation proposes a new method to generate test vectors that mimic functional operation from the switching activity point of view. It uses states obtained by applying a number of functional clock cycles starting from the scan-in state

of a test vector to fill unspecified scan cells in test cubes. Experimental results indicate that for industrial designs, the proposed techniques can reduce the peak capture switching on average by 49% while keeping the quality of test very close to conventional ATPG.

The second part of this dissertation addresses IR-drop and power minimization techniques in embedded deterministic test environment. The proposed technique employs a controller that allows a given scan chain to be driven by either the decompressor or pseudo functional background. Experimental results indicate an average of 36% reduction in peak switching activity during capture using the proposed technique.

In the last part of this dissertation, a new low power test data compression scheme using clock gater circuitry is proposed to simultaneously reduce test data volume and test power by enabling only a subset of the scan chains in each test phase. Since, most of the total power during test is typically in clock tree, by disabling significant portion of clock tree in each test phase, significant reduction in the test power in both combinational logic and clock distribution network are achieved. Using this technique, transitions in the scan chains during both loading of test stimuli and unloading of test responses decrease which will permit increased scan shift frequency and also increase in the number of cores that can be tested in parallel in multi-core designs. The proposed method has the ability of decreasing, in a power aware fashion, the test data volume. Experimental results presented for industrial designs demonstrate that on average reduction factors of 2 and 4 in test data volume and test power are achievable, respectively.

# TABLE OF CONTENTS

| LIST OF | TABLES                                                                                                                                                                                                                                                                                                      | viii           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| LIST OF | FIGURES                                                                                                                                                                                                                                                                                                     | ix             |

| СНАРТЕ  | R                                                                                                                                                                                                                                                                                                           |                |

| 1       | INTRODUCTION                                                                                                                                                                                                                                                                                                | 1              |

|         | 1.1 DFT Methods  1.1.1 Scan Design  1.1.2 Built-In Self-Test  1.1.3 Test Compression  1.2 Fault Models  1.2.1 Stuck-at Fault Model  1.2.2 Transition Fault Model  1.2.2.1 Launch Off Shift Method (LOS)  1.2.2.2 Launch Off Capture Method (LOC)  1.2.2.3 Enhanced Scan Method  1.2.3 Path Delay Faut Model |                |

|         | 1.3 Test Power Issues                                                                                                                                                                                                                                                                                       | 12             |

|         | 1.4 Organization and Contributions of This Work                                                                                                                                                                                                                                                             |                |

| 2       | MOTIVATIONS AND PREVIOUS WORKS                                                                                                                                                                                                                                                                              | 16             |

|         | 2.1 Motivation for Low Power Testing                                                                                                                                                                                                                                                                        | 18<br>18<br>24 |

| 3       | LOW CAPTURE POWER AT-SPEED TEST IN SCAN DESIGN                                                                                                                                                                                                                                                              | 39             |

|         | 3.1 Motivation 3.2 WTM and WSA Modeling 3.3 Switching Activity Caused By LOC tests 3.4 Low Power Test Vectors with Functional Profile 3.5 Experimental Results 3.6 Conclusion                                                                                                                               | 40<br>41<br>44 |

| 4       | LOW CAPTURE POWER AT-SPEED TEST IN EMBEDED DETERMINISTIC TEST ENVIRONMENT                                                                                                                                                                                                                                   | 57             |

|         | 4.1 Motivation                                                                                                                                                                                                                                                                                              | 60<br>68<br>72 |

|         | 4.5 Conclusion                                                                                                                                                                                                                                                                                              | / /            |

| 5.1 Basic Concepts and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                    | 5   | LOW POWER COMPRESSION UTILIZING CLOCK-GATING                  | 78  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------|-----|

| 5.2 Cube Merging and Compression for stuck-at faults 82 5.3 Low Power Test Architecture 87 5.4 Experimental Results for Stuck-at Faults 88 5.5 Motivation for Low Power Compression of Transition Faults 94 5.6 Proposed Launch-off-Capture Test Cube Generation 96 5.7 Cube Merging for Proposed LOC Test Cubes 104 5.8 Experimental Results for Transition Faults 106 5.9 Conclusion 113 6.1 Summary of work presented 115 6.2 Future research 117 |     | 5.1 Basic Concepts and Motivation                             | 79  |

| 5.3 Low Power Test Architecture 87 5.4 Experimental Results for Stuck-at Faults 88 5.5 Motivation for Low Power Compression of Transition Faults 94 5.6 Proposed Launch-off-Capture Test Cube Generation 96 5.7 Cube Merging for Proposed LOC Test Cubes 104 5.8 Experimental Results for Transition Faults 106 5.9 Conclusion 113 6.1 Summary of work presented 115 6.2 Future research 117                                                         |     | 5.2 Cube Merging and Compression for stuck-at faults          | 82  |

| 5.4 Experimental Results for Stuck-at Faults 88 5.5 Motivation for Low Power Compression of Transition Faults 94 5.6 Proposed Launch-off-Capture Test Cube Generation 96 5.7 Cube Merging for Proposed LOC Test Cubes 104 5.8 Experimental Results for Transition Faults 106 5.9 Conclusion 113 6 CONCLUSIONS 115 6.1 Summary of work presented 115 6.2 Future research 117                                                                          |     | 5.3 Low Power Test Architecture                               | 87  |

| 5.5 Motivation for Low Power Compression of Transition Faults                                                                                                                                                                                                                                                                                                                                                                                        |     | 5.4 Experimental Results for Stuck-at Faults                  | 88  |

| 5.6 Proposed Launch-off-Capture Test Cube Generation                                                                                                                                                                                                                                                                                                                                                                                                 |     | 5.5 Motivation for Low Power Compression of Transition Faults | 94  |

| 5.7 Cube Merging for Proposed LOC Test Cubes. 104 5.8 Experimental Results for Transition Faults 106 5.9 Conclusion 113 6 CONCLUSIONS 115 6.1 Summary of work presented 115 6.2 Future research 117                                                                                                                                                                                                                                                  |     |                                                               |     |

| 5.8 Experimental Results for Transition Faults 106 5.9 Conclusion 113 6 CONCLUSIONS 115 6.1 Summary of work presented 115 6.2 Future research 117                                                                                                                                                                                                                                                                                                    |     | 5.7 Cube Merging for Proposed LOC Test Cubes                  | 104 |

| 5.9 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |                                                               |     |

| 6.1 Summary of work presented                                                                                                                                                                                                                                                                                                                                                                                                                        |     |                                                               |     |

| 6.2 Future research                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6   | CONCLUSIONS                                                   | 115 |

| 6.2 Future research                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | 6.1 Summary of work presented                                 | 115 |

| REFERENCES                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 6.2 Future research.                                          | 117 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                      | REI | FERENCES                                                      | 119 |

# LIST OF TABLES

| 3.1 Reduction in peak WSA after different numbers of cycles of simulation                      | 45  |

|------------------------------------------------------------------------------------------------|-----|

| 3.2 Circuit characteristics                                                                    | 50  |

| 3.3 Percentage reduction in Peak WSA during 1 <sup>st</sup> and 2 <sup>nd</sup> capture cycles | 52  |

| 3.4 Percentage reduction in Peak SET during 1 <sup>st</sup> and 2 <sup>nd</sup> capture cycles | 53  |

| 3.5 Comparing Reduction in average power during shift                                          | 54  |

| 3.6 Comparing pattern counts and bridging coverage estimate                                    | 55  |

| 4.1 Circuit characteristics                                                                    | 73  |

| 4.2 Comparing capture power reduction in first and second capture cycles                       | 74  |

| 4.3 Comparing shift power reduction                                                            | 75  |

| 4.4 Comparing pattern counts and bridging coverage estimate                                    | 76  |

| 5.1 Circuit characteristics                                                                    | 89  |

| 5.2 Result for test data volume reduction and pattern count                                    | 91  |

| 5.3 Result for test power reduction                                                            | 92  |

| 5.4 Result for multiple-detection ATPG                                                         | 94  |

| 5.5 Circuit characteristics                                                                    | 107 |

| 5.6 Result for peak and average power reduction during shift                                   | 108 |

| 5.7 Result for peak and average power reduction during capture                                 | 109 |

| 5.8 Result for test data volume, pattern count and BCE                                         | 111 |

| 5.9 Result for test data volume, pattern count and BCE                                         | 113 |

# LIST OF FIGURES

| т. |      |   |

|----|------|---|

| H1 | gure | - |

|    | 5000 | _ |

| 1.1 Manufacturing test of a circuit [1]               | 2  |

|-------------------------------------------------------|----|

| 1.2 Scan based circuit                                | 3  |

| 1.3 Multiplexer based scan cell                       | 4  |

| 1.4 High level view of the BIST scheme                | 5  |

| 1.5 Architecture for test compression [4]             | 6  |

| 1.6 On-chip decompressor [4]                          | 7  |

| 1.7 Example of four-output 8-bit decompressor [4]     | 7  |

| 1.8 Waveform for Launch-off-Shift delay test          | 10 |

| 1.9 Waveform for Launch-off-Capture delay test        | 11 |

| 1.10 Power dissipation in CMOS circuits [12]          | 12 |

| 2.1 Flow of Progressive Match Filling [31]            | 21 |

| 2.2 Signal probability calculations [28]              | 23 |

| 2.3 A JP-filling example                              | 24 |

| 2.4 Mux as a blocking logic                           | 25 |

| 2.5 Clock gate cell operation during test             | 26 |

| 2.6 Scan chain reordering                             | 27 |

| 2.7 A circuit with segmented scan chains [38]         | 28 |

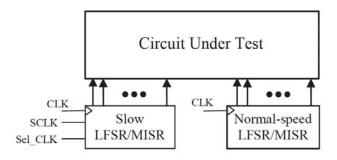

| 2.8 Low-power BIST with DS-LFSRs [48]                 | 31 |

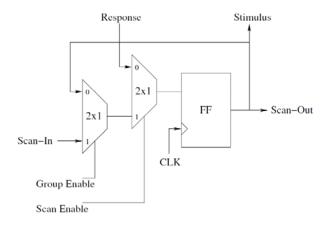

| 2.9 Modified scan cell [50]                           | 32 |

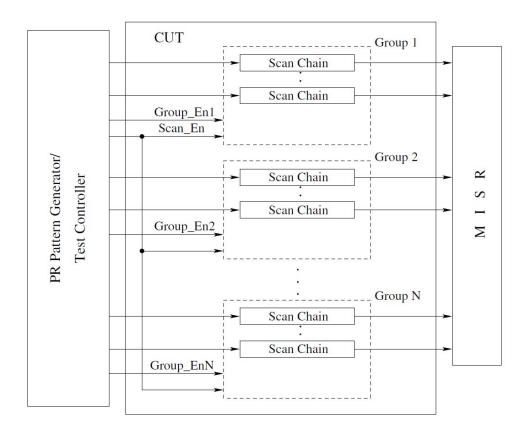

| 2.10 BIST scheme proposed in [50]                     | 33 |

| 2.11 LFSR with one input [56]                         | 34 |

| 2.12 Low power decompressor proposed in [57]          | 36 |

| 2.13 Low power scheme proposed in [58]                | 37 |

| 2.14 Shadow register in decompressor proposed in [58] | 38 |

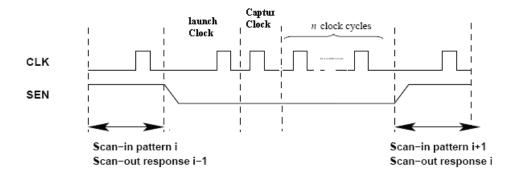

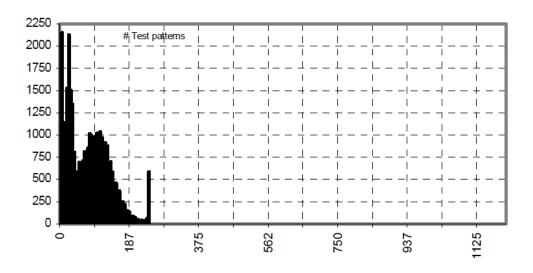

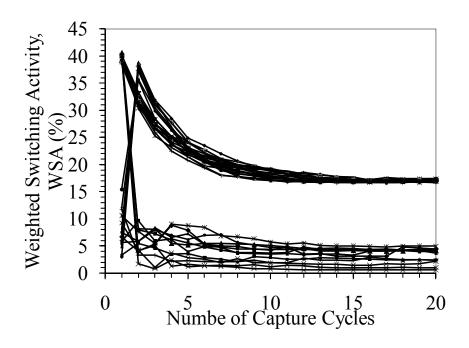

| 3.1 | The timing diagram for generating functional background in LOC test                                                                                                     | 42 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

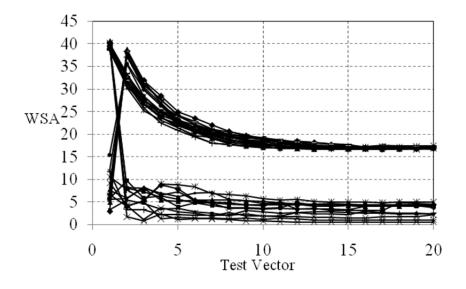

| 3.2 | Applying 20 clock cycles to the test vectors generated for LOC test using random fill                                                                                   | 42 |

| 3.3 | Applying 20 clock cycles to the test vectors generated for LOC test using zero                                                                                          | 43 |

| 3.4 | Applying 20 clock cycles to the test vectors generated for LOC test using preferred fill                                                                                | 44 |

| 3.5 | The proposed low-power test generation procedure                                                                                                                        | 46 |

| 3.6 | Percentage difference in WSA in the first capture cycle of the proposed tests relative to the WSA when the test cubes were simulated for five cycles after random fill. | 47 |

| 3.7 | Percentage difference in WSA in the second capture cycle of the proposed tests relative to the WSA when the test cubes were simulated for 5 cycles after random fill.   | 47 |

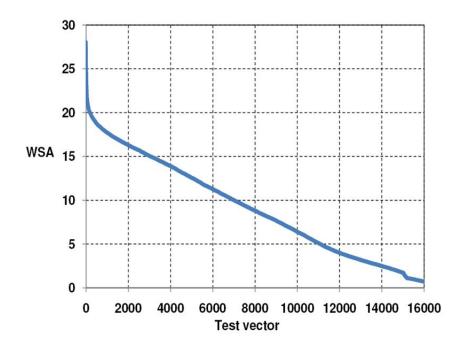

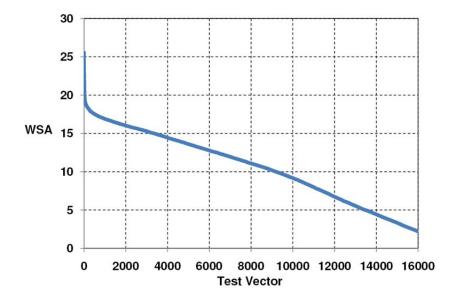

| 3.8 | WSA of 1 <sup>st</sup> and 2 <sup>nd</sup> capture using random fill for Circuit C2225                                                                                  | 49 |

| 3.9 | WSA of 1 <sup>st</sup> and 2 <sup>nd</sup> capture using proposed method for Circuit C2225                                                                              | 49 |

| 4.1 | Scan chains with specified bits [58]                                                                                                                                    | 58 |

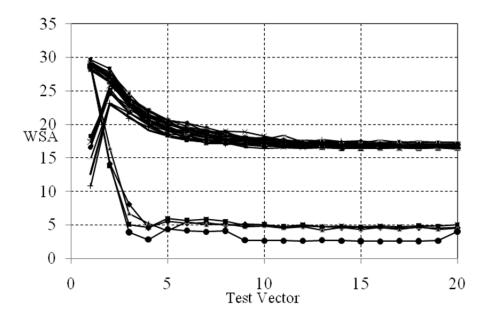

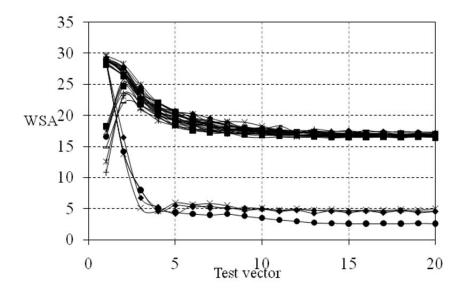

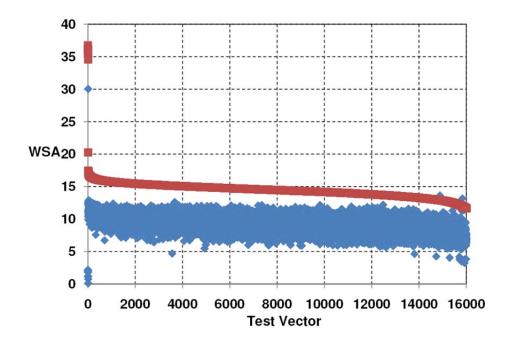

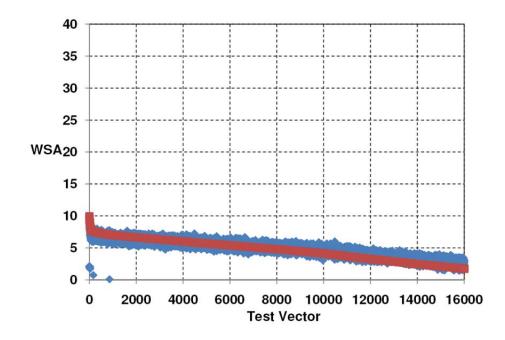

| 4.2 | Applying 20 capture cycles to LOC test vectors generated using random fill                                                                                              | 59 |

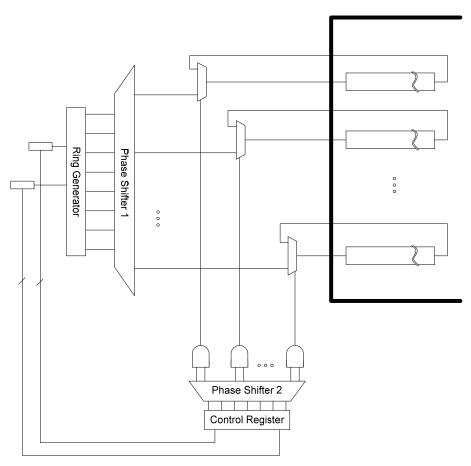

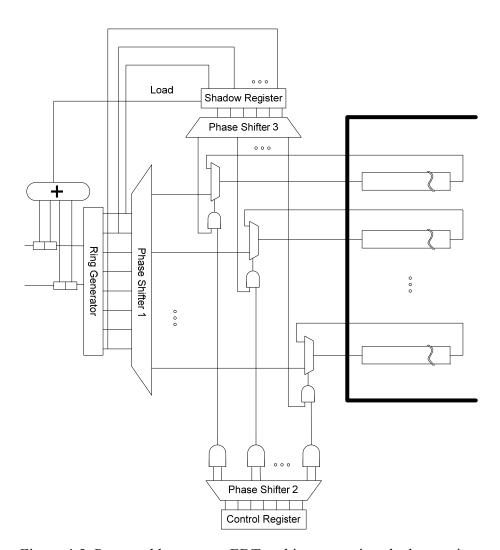

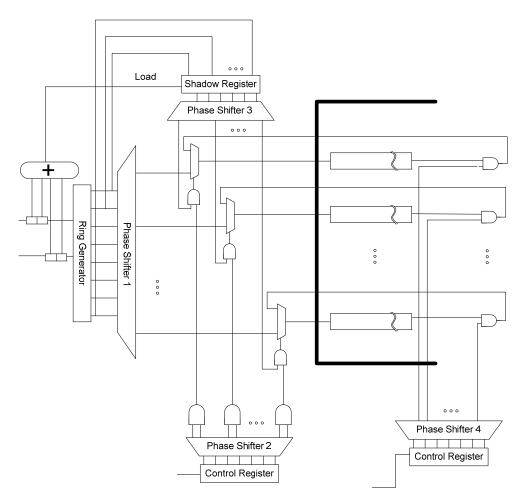

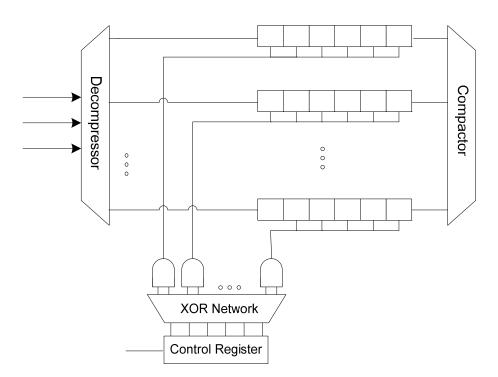

| 4.3 | Proposed low power EDT architecture                                                                                                                                     | 61 |

| 4.4 | Clock gating for unbalanced scan chains                                                                                                                                 | 63 |

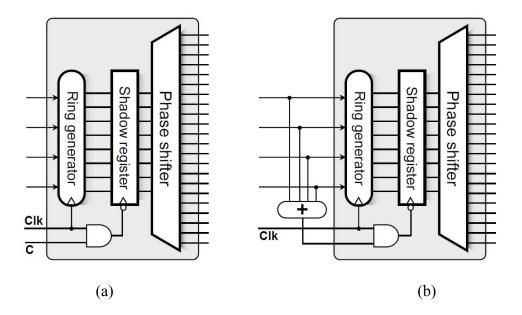

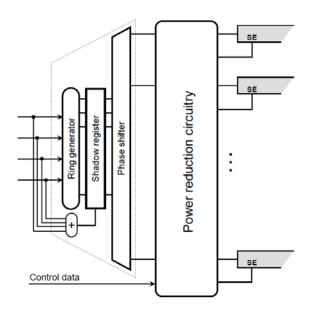

| 4.5 | Proposed low power EDT architecture using shadow register                                                                                                               | 64 |

| 4.6 | An example of test cube                                                                                                                                                 | 65 |

| 4.7 | Corresponding Control pattern of test cube of Figure 4.6                                                                                                                | 65 |

| 4.8 | Low power EDT Architecture with separate X-masking scheme                                                                                                               | 67 |

| 4.9 | The proposed low-power test generation procedure                                                                                                                        | 69 |

| 4.1 | 0 Compression of control pattern                                                                                                                                        | 72 |

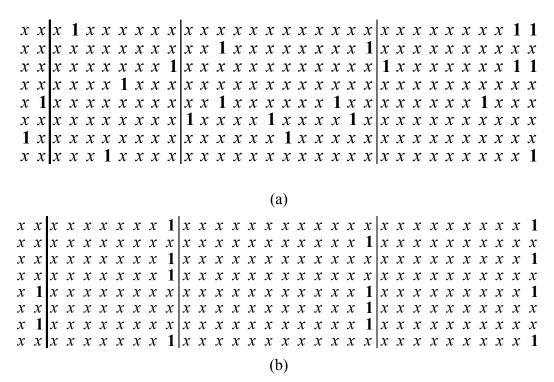

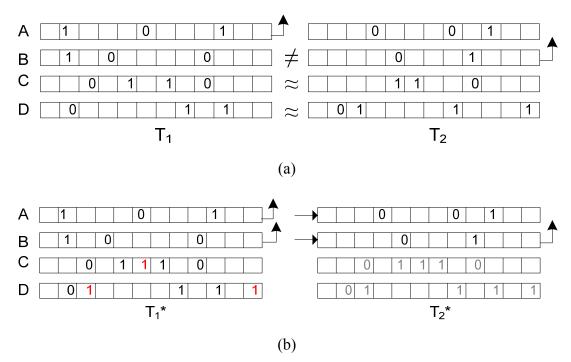

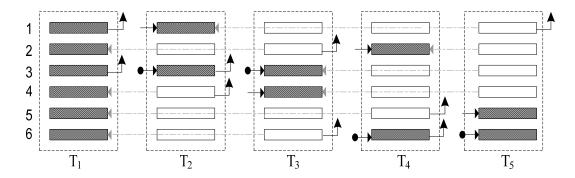

| 5.1 | Two consecutive test vector                                                                                                                                             | 81 |

| 5.2 | Generating of low power compressed pattern                                                                                                                              | 84 |

| 5.3 | An example of merging and generating test cubes                                                                                                                         | 85 |

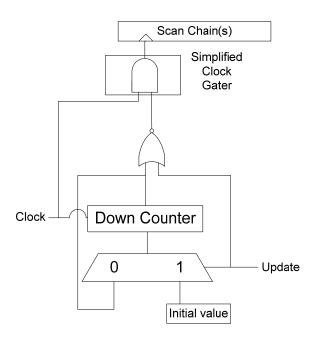

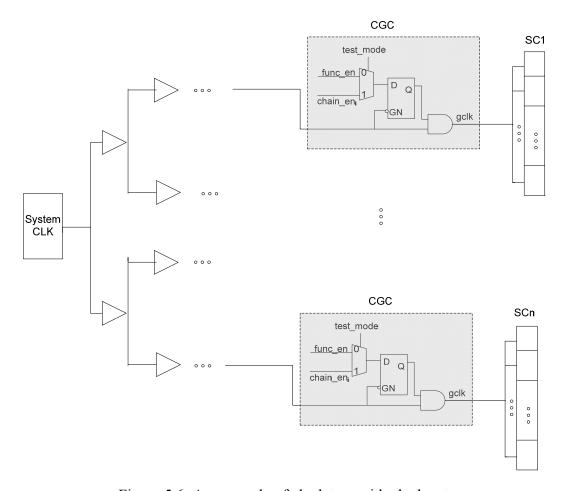

| 5.4 | Low power test architecture                                                                                                                                             | 87 |

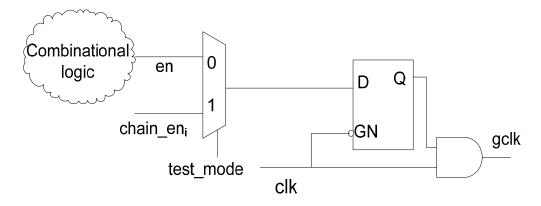

| 5.5 | An example of Clock gater structure                                                                                                                                     | 97 |

| 5.6 An example of clock tree with clock gaters                                  | 97  |

|---------------------------------------------------------------------------------|-----|

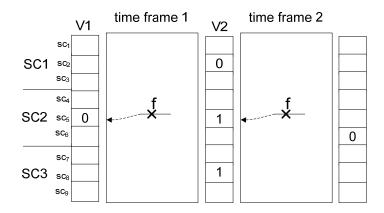

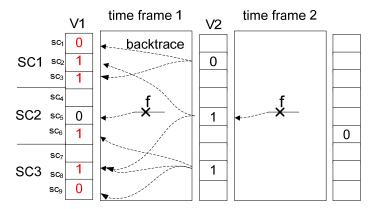

| 5.7 Two-timeframe Circuit for detecting slow-to-rise transition fault at line f | 99  |

| 5.8 Example of backtrace operation in LOC test method                           | 99  |

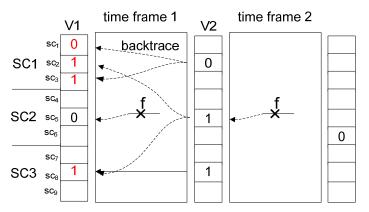

| 5.9 Proposed LOC using clock gater circuitry                                    | 101 |

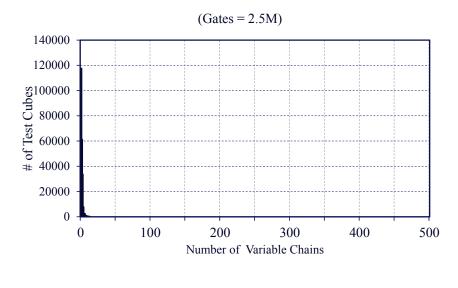

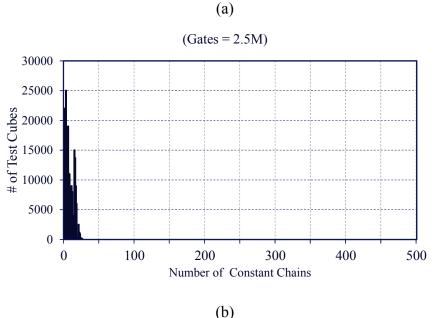

| 5.10 Distribution of variable chains and constant chains                        | 104 |

#### CHAPTER 1

#### **INTRODUCTION**

According to Moore's law, the number of transistors integrated per square inch on a die has doubled every year and half since the integrated circuit was invented. Also, every few years the size of the transistors employed is shrunken and the frequency of circuits increases. As these trends continue, several new challenges become relevant in the testing of very-large-scale-integrated (VLSI) circuits. With the advance of semiconductor manufacturing technology, the requirements of digital VLSI circuits have led to many challenges during manufacturing test. This is because of the large and complex chips which require a huge amount of test data and dissipate a substantial amount of power during test, resulting in considerable increases in the test cost.

This study addresses the problem of reducing power consumption during test and the problem of keeping the test data volume and test application time moderate. The main objective of this study is to introduce novel techniques that improve the power consumption and test data volume during at-speed test in scan designs and test data compression environments.

This chapter introduces some important concepts in testing of digital VLSI circuits and the importance of minimizing power consumption during test.

#### 1.1 DFT Methods

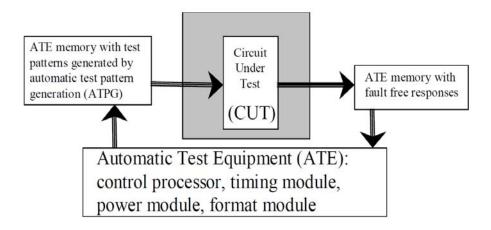

Deploying reliable integrated circuits depends strongly on testing to eliminate defective circuits caused by the manufacturing process. Manufacturing test is performed after a circuit comes out of the manufacturing line to screen defective parts. Figure 1.1 shows the basic principle of manufacturing testing with its three basic components: circuit under test (CUT), automatic test equipment (ATE), and ATE memory to store test patterns or test vectors and expected responses obtained by automatic test pattern generation (ATPG) tools. As shown Figure 1.1, to test a digital circuit several test

vectors are applied to its inputs. Then, CUT response is analyzed. If the CUT responses match the fault-free responses, then the circuit is considered to be functioning properly. The input test vectors and their responses are stored in an Automatic Test Equipment (ATE) which applies the tests to the CUT and analyze its responses.

Figure 1.1 Manufacturing test of a circuit [1]

The manufacturing test of a circuit composed of only combinational logic is a relatively easy task. The primary inputs can be set to the desired values and the primary outputs can be observed. However, the test of circuits containing sequential elements such as flip-flops or latches is a more complicated task. Sequential elements in the circuit need to be set to the desired values. In this case, the ATPG needs to create test sequences over many clock cycles to justify desired assignments to circuit inputs that increases run times and complexity of the test generation. This method has been found to be impractical for large circuits.

Design for testability (DFT) refers to design techniques that make products easier to test. DFT techniques improve testability, in increasing controllability and observability of sequential elements by adding test hardware to the CUT. The most popular DFT

techniques for testing VLSI circuits include scan design, Built-In Self-Test (BIST) and test data compression. In this sub-section, we briefly describe each of these techniques.

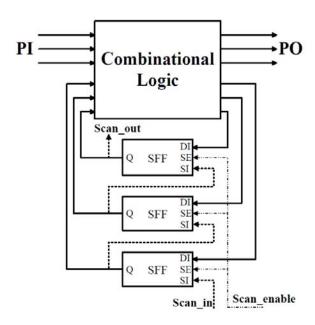

## 1.1.1 Scan Design

The most common DFT methodology is scan design [2] where sequential elements are modified to scan cells to obtain controllability and observability for flip-flops. This is performed by adding a test mode to the circuit such that when the circuit is in this mode, all flip-flops functionally form one or more shift registers which is called scan chains. The inputs and outputs of these shift registers are made into primary inputs and primary outputs respectively. Thus using the test mode, all flip-flops can be set to any desired states by shifting appropriate logic values into the shift register. Similarly, the states of flip-flops are observed by shifting out the contents of the scan chains. All flip-flops can be set or observed in a time (in terms of clock periods) that equals the number of flip-flops in the longest scan chain.

Figure 1.2: Scan based circuit

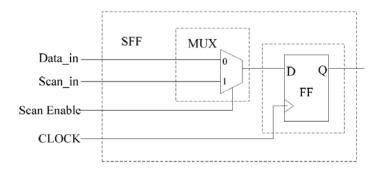

Figure 1.3: Multiplexer based scan cell

Scan design can be further divided into full scan and partial scan designs. The main advantage of full scan (Figure 1.2) is that by modifying all the sequential elements to scan cells it reduces the sequential TPG to combinational TPG. On the other hand, partial scan modifies only a small subset of sequential elements leading to lower test area overhead at the expense of more complex TPG.

There are more than one possible implementations of a scan cell; the most common is shown in Figure 1.3. This scan cell is composed of a D flip-flop and a multiplexer. The multiplexer uses a Scan\_enable input to select between the Data\_in and the Scan\_in. In scan based test, the circuit sequential elements can be set to arbitrary combinations of values by shifting through Scan\_in the desired combinations. Also the state of the circuit sequential elements can be observed by shifting out the values stored in scan cells through Scan\_out. This enables the test of previously un-testable faults but it may set the circuit into non-functional states.

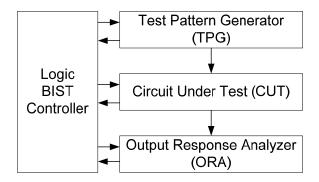

## 1.1.2 Built-In Self-Test (BIST)

Built-In Self-Test (BIST) [3, 68] is a technique of designing additional hardware and software features into integrated circuits to allow performing self-testing. BIST is a DFT technique which employs on chip test pattern generator (TPG) and signature analyzer (SA). Figure 1.4 shows a CUT with BIST. When the circuit is in test mode, a test pattern generator (TPG) generates patterns that are loaded into the CUT and a

signature analyzer (SA) examines the CUT response to the test patterns. The signature analyzer has an output to indicate if the circuit has passed or failed the test. In most BIST architectures, linear feedback shift registers (LFSRs) is usually used as a TPG because LFSR can generate sequence of good random property with little area overhead [3]. The typical components of an LFSR are memory elements (latches or flip flops) and exclusive OR (XOR) gates. The signature analyzers (SAs) are commonly constructed from multiple-input signature registers (MISRs). The MISR is basically an LFSR that uses and extra XOR gate at the input of each LFSR stage for compacting the output responses of the CUT into the LFSR during each shift operation.

Figure 1.4: High level view of the BIST scheme

BIST is a good solution for testing of critical circuits that have no direct connections to external pins, such as embedded memories used internally by the devices. In BIST, typically up to 95% coverage of stuck-at faults can be achieved provided that test points are employed to address random pattern resistance. Other types of fault models, such as transition or path-delay faults, are not handled efficiently by pseudorandom patterns. In BIST, all test responses have to be known. Unknown values corrupt the signature and, therefore, have to be bounded by additional test logic. Also, deterministic tests are almost always needed to target the remaining random pattern resistance faults.

## 1.1.3 Test Compression

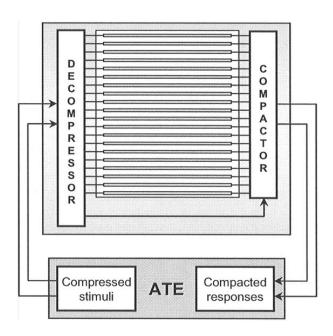

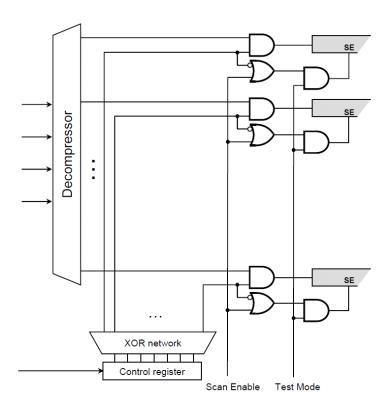

As devices grew in gate count, scan test data volume and application time grew as well. Test compression techniques have been developed to reduce test data volume and test application time. Test compression techniques are easy to adopt in industry because they are based on scan. Test compression is achieved by adding some additional on-chip hardware before the scan chains to decompress the test stimuli coming from the tester and after the scan chains to compact the response going to the tester (Figure 1.5).

Figure 1.5: Architecture for test compression [4]

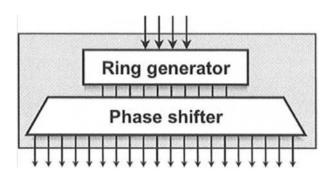

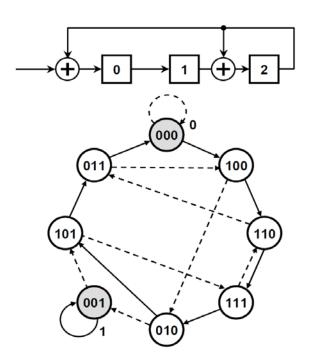

Here a technique called Embedded Deterministic Test (EDT) [4] is described. EDT is based on adding a data decompressor at the inputs and response compactor at the outputs of the circuit. The data decompressor is implemented by a ring generator (optimized LFSR) and a phase shifter (Figure 1.6). The phase shifter is necessary to drive a large number of scan chains and to reduce linear dependencies between sequences

entering the scan chains. In addition, the phase shifter's design guarantees balanced use of all memory elements in the ring generator.

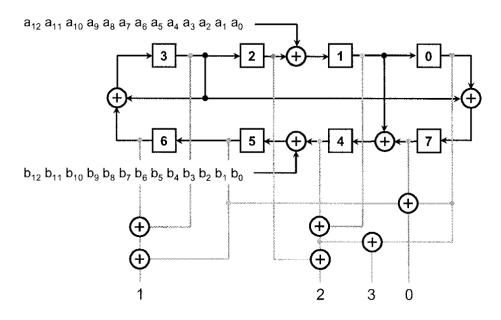

The circuits scan chains are divided evenly, if possible, into several shorter chains. For the purpose of producing the desired output, the ring generator is continuously seeded with data. The ratio between the inputs of the ring generator and the outputs of the phase shifter determines the maximal compression possible. Figure 1.6 shows the internal schematic of an on-chip decompressor and Figure 1.7 shows an implementation of a four-output 8-bit decompressor.

Figure 1.6: On-chip decompressor [4]

Figure 1.7: Example of four-output 8-bit decompressor [4]

In EDT the compactor consists of an XOR tree and masking logic. Since XORs always propagate fault effects (when no unknown values exist), every scan chain can be observed at the same time using a reduced number of outputs which effectively reduce the response data. Since unknown values can be present in the CUT response to a test, AND-gates are placed at the outputs of every scan chain to selectively block these unknown values.

### 1.2 Fault Models

In this sub-section some most popular fault models, the stuck-at fault model, the transition fault model and the path delay fault model, will be reviewed.

#### 1.2.1 Stuck-at Fault Model

The stuck-at fault model is the earliest fault model, and still the most common. A stuck-at fault [5] happens when a line in the circuit is stuck at a fixed logic value. To test for stuck-at faults, two steps are involved: one to generate a test vector that excites the fault and the other to propagate the faulty effect to a primary output or a scan flip-flop. Research has shown that stuck-at fault model covers a large percentage of physical defects. However, with the continuously shrinking sizes of the transistors employed in modern designs, increasing clock speed and decreasing power supply voltage, other types of defects not covered by the tests for stuck-at faults are beginning to appear in the CUTs. For this reason, tests for other types of faults are being applied, such as the transition fault model, which is presented next.

#### 1.2.2 Transition Fault Model

Certain types of defects in the manufacturing of the transistors that comprise the circuit gates may cause the gate to have a higher than normal delay. This abnormal delay causes the gate to switch at a lower than normal speed when its inputs change. When this delay is large enough the defect is modeled as a transition delay fault [6].

The transitional delay fault model is the first delay fault model to be developed and is also the simplest. A transition delay fault [6] occurs when the time required for switching outputs from 0 (1) to 1 (0) in the gate, due to a change in the gate's inputs, takes longer than its normal time. If the delay introduced is large enough so that its effects can be seen at least at one of the circuit primary outputs (POs) or captured in a scan cell, the circuit cannot operate at its intended clock speed without having a faulty behavior.

According to the transition-fault model, there are two types of faults possible: a slow-to-rise fault and a slow-to-fall fault. A slow-to-rise fault at any node means that the effect of any transition from 0 to 1 (or 1 to 0 for slow-to-fall) will not reach a primary output or scan flip-flop within the stipulated time. To perform a transition fault test, two test vectors (V<sub>1</sub>, V<sub>2</sub>) are required. Firs vector initialize the fault and second vector launch a transition and propagate and capture the fault effect in an observation point. Depending on how the transition is launched and captured, there are three transition fault pattern generation methods: launch-off-shift or skewed load test method [7], launch-off-capture or broadside test method [8] and enhanced scan [9] which are briefly explained below.

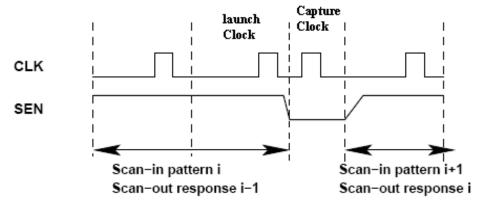

# 1.2.2.1 Launch-off-Shift Method (LOS)

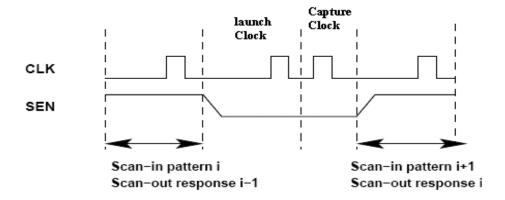

In launch-off-shift (LOS) approach [7], the transition at the gate output is launched in the last shift cycle during the shift operation. Figure 1.8 shows the launch-off-shift method waveform. The launch clock is a part of the shift operation and is immediately followed by a fast capture pulse. The scan enable (SEN) is high during the last shift and must go low to enable response capture at the capture clock edge. Since the capture clock is applied at the full system clock speed after the launch clock, the scan enable signal, which typically drives all scan flip-flops in the CUT, should also switch in the full system clock cycle. This requires the scan enable signal to be driven by a

sophisticated buffer tree or strong clock buffer. Such a design requirement is often too costly to meet.

Figure 1.8: Waveform for Launch-off-Shift delay test

# 1.2.2.2 Launch-off-Capture Method (LOC)

In the launch-off-capture approach [8], the launch cycle is separated from the shift operation. Figure 1.9 shows the waveforms of the launch-off-capture (LOC) method. At the end of scan-in (shift mode), pattern  $V_1$  is applied and CUT is set to an initialized state. A pair of at-speed clock pulses is applied to launch and capture the transition at the target gate terminal. This relaxes the at-speed constraint on the scan enable (SEN) signal and dead cycles are added after the last shift to provide enough time for the SEN signal to settle low. The launch-off-shift method is more preferable based on the ATPG complexity and pattern count compared to LOC method. The LOC technique is based on a sequential ATPG algorithm, while the LOS method uses a combinational ATPG algorithm. This will increase the test pattern generation time in case of LOC, and also, a high fault coverage cannot be guaranteed due to the correlation between the two patterns,  $V_1$  and  $V_2$ ; note that  $V_2$  is the functional response of pattern  $V_1$ . The main concern about the LOS is its requirement to at-speed SEN signal.

Figure 1.9: Waveform for Launch-off-Capture delay test

#### 1.2.2.3 Enhanced Scan Method

In the enhanced scan approach [9], two vectors  $V_1$  and  $V_2$  are shifted into the scan flip-flops simultaneously in order to initialize and propagate the fault. The drawback on enhanced scan is that it needs hold-scan flip-flops which make it unattractive for application specific integrated circuit (ASIC) designs.

#### 1.2.3 Path Delay Fault Model

The path delay fault model [10] focuses on the testing of a set of predefined structural paths in order to detect the accumulated delays along these paths. A path is defined as an ordered set of gates  $\{g_0, g_1, \dots g_n\}$ , where  $g_0$  and  $g_n$  are primary input and primary output, respectively and gate  $g_i$  is an input to gate  $g_{i+1}$  (0 < i < n-1)). A delay defect on a path can be observed by propagating a transition through the path. The path delay fault model takes the sum of all delays along a path into accounts, while the transition fault model accounts for localized faults (delays) at the inputs and outputs of each gate. Test for path delay fault model can detect small distributed delay defects caused by statistical process variations. A major limitation of this fault model is that the number of paths in the circuit can be very large. Therefore testing all path delay fault in the circuit is not practical.

## 1.3 Test Power Issues

With the development of portable devices and wireless communication systems, design for low power VLSI circuits has become an important issue. Minimizing power dissipation in VLSI circuits increases battery lifetime and the reliability of the circuit [11-12]. The power dissipation of complementary metal oxide semiconductors (CMOS) circuits can be generally divided into two main categories: static power and dynamic power [11].

- The static power dissipation: the power is dissipated by a gate when it is inactive. A significant fraction of static power is caused by the reduced threshold voltage used in modern the CMOS technology that prevents the gate from completely turning off, but causing sources to drain leakage. All components of static power dissipation have a minor contribution to the total power dissipation.

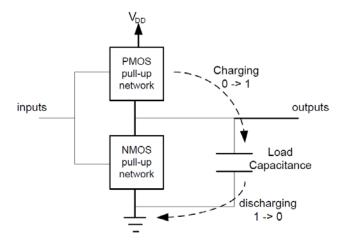

- The dynamic power dissipation: the power dissipation is predominantly caused by the current required for charging/discharging the load capacitance through the pull-up/ pull-down networks (Figure 1.10).

Figure 1.10: Power dissipation in CMOS circuits [12]

Dynamic power dissipation is the dominant source of power dissipation in CMOS circuits. The energy consumed from the source for changing the output from 0 to 1 during the time interval [0, T] is

$$E_{0\to 1} = V_{DD} \int_0^T i(t)dt = V_{DD} \int_0^{V_{DD}} C_L dV = C_L V_{DD}^2$$

where  $C_L$  is the load capacitance. Only half of this energy is stored in the capacitor, while the other half is converted into heat [12]. In the same manner, when the output switches from 1 to 0 the capacitor discharges through the pull down network and the same amount of energy is dissipated as a heat. Therefore, the rate at which the outputs change their value determines the average dynamic power dissipation.

Previous studies also confirm considerably higher switching activity during testing compared to that during functional operation which may result in higher dynamic power dissipation during the test. This can decrease the reliability of the circuit under test due to excessive temperature and current density which cannot be tolerated by circuits designed using power minimization techniques. On the other hand, high switching activity during test application causes a high rate of current flowing in power and ground lines leading to excessive peak supply current. Excessive peak supply currents may cause higher IR drops, which tend to increase signal propagation delays of affected gates. Increased gate delays during test can erroneously change the logic state of circuit lines leading to incorrect operation of circuit gates which may cause some good dies to fail the test and consequently yield loss [13]. Therefore, addressing the problems associated with testing low power VLSI circuits has become an important issue.

In the meantime, as feature size shrinks into the deep-submicron (DSM) scale and circuit speed increases, due to the timing-related defects a higher number of chips failure may be observed in the circuit. As a result, at-speed scan testing, which captures the test response of the scan design at the rated clock-speed, is becoming mandatory to ensure high product quality [14, 15]. Despite the importance of at-speed scan testing, it is being

severely challenged by excessive power supply current during test and test-induced yield loss. It has been reported that a 10% drop in power supply voltage may increase path delay by 30% [16]. Consequently, increased gate delays during test may cause good chips to fail at-speed tests resulting in test-induced yield loss [17-19]. Therefore, it is important to reduce IR-drop during at-speed scan testing, in order to avoid IR-drop-induced yield loss.

#### 1.4 Organization and Contributions of This Work

This research presents new techniques for reducing power supply noise and IR-drop during at-speed delay test in VLSI circuits. Also it presents a new low power compression technique using clock gating circuitry to achieve better test data volume and test power. The rest of the dissertation is organized as follows. Motivation for low power testing and a review of previously reported approaches for minimizing power dissipation and overtesting during test application is provided in Chapter 2.

Chapter 3 introduces a new technique [20] for IR-drop and overtesting during test application in scan sequential circuits with no penalty in area overhead, test efficiency, performance, or volume of test data when compared to standard scan method described in Section 1.2. It uses states obtained by applying a number of functional clock cycles starting from the scan-in state of a test vector to fill unspecified scan cells in test cubes. Since the number of specified values in test cubes is small, switching activity caused by using functional backgrounds is very close to the switching activity caused by functional operation.

Chapter 4 introduces a new low power techniques [23] in embedded deterministic test environment [4] and shows how with low overhead in test area and volume of test data, and no penalty in test efficiency, significant reduction in power dissipation and ovetesting during test application in large sequential circuits is achieved.

Chapter 5 introduces a new low power test data compression technique [47] using systematically clock gater circuitry to simultaneously reduce test data volume and test power. Using this technique, transitions in the scan chains during both loading test stimuli and unloading test responses decrease which results in the acceleration of the speed of shifting and an increase in the number of cores that can be tested in parallel.

Chapter 6 outlines a summary of the methods proposed in this study.

Recommendations for future research into this subject are also provided.

#### CHAPTER 2

## MOTIVATION AND PREVIOUS WORKS

With the development of wireless communication technology and high-performance portable computing devices, design for low power has become a major objective in system design. Power dissipation is not only a critical parameter in the design procedure, but also during manufacturing test as the system may consume much more power during test than during normal operation [14-19]. Thus, low power test of digital VLSI systems has become a major issue of research in recent years. On the other hand, as was discussed in the previous chapter, at-speed tests are more important in order to maintain sufficient level of outgoing quality [14, 73-74]. However, generating at-speed test patterns using functional patterns is very complex and time consuming. DFT techniques are widely used in order to improve the testability of a design. While DFT techniques increase the number of testable faults, they may cause the test vectors contain non-functional states which result in higher switching activities compared to the normal mode of operation.

In this chapter, the need for low power testing to preserve high circuit yield and reliability will be discussed and justified in Section 2.1. In Section 2.2 and Section 2.3, an overview of the solutions proposed in the literature to reduce power dissipations and IR-drop during test application in scan design and test data compression techniques is provided, respectively.

#### 2.1 Motivation for Low Power Testing

Considerable research on low power design and testability of VLSI circuits have been shown that the power consumed in test mode of operation is often much higher than the power consumed in normal mode of operation due to the high switching activity in the nodes of the circuit under test [16-19, 21 and 22]. The main reasons for high switching activity in test mode [17, 19] are as follows:

- Scan based tests eliminate various functional constrain imposed on the sequential circuits by changing sequential circuits to combinational circuits. Given a circuit with k scan cells, there are 2<sup>k</sup> possible states that some of which are not functional or legal states. For example in a BCD counter with 4 scan cells, only ten (0-9) of sixteen states are legal states. Non-functional characteristics of test stimuli and test responses in scan based test causes higher switching activity at circuit nodes during test. (We use the words legal states, reachable states, and functional states interchangeably to mean the states of the sequential circuit under test that can be reached during normal/functional operation of the circuit. By unreachable or illegal or non-functional states, we mean the states that cannot occur during normal functional operation.)

- Modern ATPG tools tend to generate test patterns with a high toggle rate in order to reduce pattern count which may lead to a shorter test application time. Thus, the node switching activity in the CUT in the test mode is much higher than that in normal mode.

- In the test mode, parallel testing is often used to reduce the test application time.

This parallelism inevitably increases switching activity during the test.

- The design for testability circuitry inserted in the circuit will probably be idle

during normal mode but may be used intensively during test mode which may

result in a considerable increase in switching activity during the test.

- The correlation between the successive functional input vectors applied to a given circuit during normal operation is generally very high. For instance, in a speech signal processing circuit, the input vectors behave in a predictable manner, with the least significant bits more likely to change than the most significant bits. In contrast, there is no definite correlation between successive test patterns generated

by an ATPG tool during scan testing. This will increase the switching activity in the circuit during test.

The excessive switching activity causes many problems in circuit-under-test. Higher switching activity causes higher power dissipation as well as higher peak supply currents. Excessive power dissipation may cause hot spot that could cause a device malfunction, shorter product lifetime, or even permanent damage of the circuit. Excessive peak supply currents may cause higher IR drops, which tend to increase signal propagation delays of affected gates. Increased gate delays during test may cause good chips to fail tests causing yield loss [13, 19]. Therefore, in order to avoid IR-drop-induced yield loss, it is important to reduce IR-drop during test.

Several methods have been proposed to reduce the peak switching activity during shift and capture cycles in scan design, logic BIST and test data compression techniques. Following, earlier methods to reduce switching activity during shift and capture cycles will be discussed.

### 2.2 Low Power Testing in ATPGs

Several methods have been proposed to reduce the switching activity in the circuit on the test (CUT) during shift and capture cycle. These techniques can be classified into three main categories: ATPG techniques, DFT modification techniques and functional/pseudo functional techniques. Following, a brief review of some of these techniques are presented.

#### 2.2.1 ATPG Techniques

In conventional ATPG, each don't care bit (X) in a test cube is filled with 0 or 1 randomly; the resulting fully specified test cube (called test pattern) is then fault simulated to confirm the detection of all targeted faults and additional faults. While the state-of-the-art dynamic and static test pattern compaction techniques have been

extensively used to reduce pattern count, the number of unspecified bits in a generated test cube in ATPG remains high. This provides a great opportunity that can be exploited for power minimization during scan testing.

In [24], a low-power ATPG method was proposed to minimize difference between before-capture and after-capture output values of scan cells. This is achieved by introducing a capture conflict (C-conflict) in addition to the conventional detection conflict (D-conflict). In conventional PODEM-based ATPG, backtrack of decisions occurs when a detection conflict occurs, i.e. when there are no paths containing unspecified values between the gates on the D-frontier and any PO (primary output) or PPO (pseudo-primary output). Here a new backtrack condition is introduced; PODEM will also backtrack when the PPO and its correspondent scan cell input, PPI (pseudoprimary input), have different values, which is called a C-conflict. However, backtracking for C-conflict may make fault detection impossible. In this case, the backtracking for C-conflict is preserved, and the transition at the scan cell is tolerated because the primary goal is fault detection. This technique has the advantage that no modifications to the CUT are necessary (as the following software techniques) and that the pattern count is only slightly increased, while it has the disadvantages that it is necessary to modify the existing ATPG and relatively high run times, which makes it non-scalable to industrial circuits.

Another technique to reduce test power is the use of power-aware X-filling heuristics. These heuristics do not modify the overall ATPG process but assign appropriate values to don't care bits of deterministic test cube generated by ATPG algorithm to minimize the number of transitions in the scan cells. By reducing the number of transitions in the scan cells during scan shifting, the overall switching activity in the CUT is reduced, thus the power consumption during test is minimized.

The adjacent fill (AF) [25] method is one of technique developed based on X-filling solution in which a set of unspecified bits in each test is identified by the AF and

then, filled in the following way: whenever there is an unspecified bit, AF fills it with the previous specified logic value, and if there are unspecified bits at the beginning of the test cube, the AF will fill them with the first specified value. For example, if XX1XX100 is a test cube for a given set of faults, adjacent fill will create the test vector 11111100 which has only one transition in it. This method has the advantage that no modification on ATPG algorithms is needed. Results on benchmark circuits have shown that both average and peak power consumption during test can be efficiently minimized with the adjacent fill technique [26].

Another X-filling technique that is widely used to reduce the switching activity is zero-fill [13]. Zero-fill increases 0's in a test vector, which helps reduce switching activity especially during scan shift, but tends to increase pattern counts significantly.

In the context of at-speed scan testing, some X-filling solutions have also been described to reduce power during the test cycle and thus avoid IR-drop-induced yield loss [27, 28 and 33].

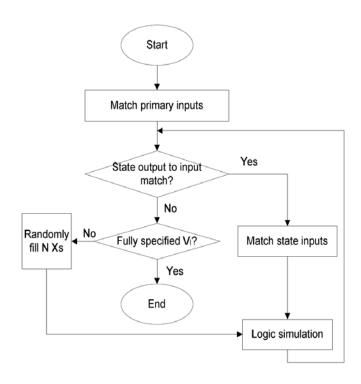

In [31], a Progressive Match Filling (PMF) technique was proposed to reduce the peak current and power dissipation during the fast capture cycle in broadside delay fault testing. Figure 2.1 gives the flow of the progressive match filling procedure [31]. In this method, the unspecified values in the generated initialization vector are filled such that the resulting launch vector  $(V_2)$  will be in its minimal Hamming distance from the initialization vector  $(V_1)$ . If a primary input is assigned a specified value a in  $V_1$   $(V_2)$  and there is an X value in the corresponding position in  $V_2$   $(V_1)$ , then, it assigns the value a to this primary input in  $V_2$   $(V_1)$ . If a primary input is unspecified in both  $V_1$  and  $V_2$ , then, it assigns the same randomly chosen binary value to this primary input in both  $V_1$  and  $V_2$ . Then, it searches for corresponding state inputs which have unspecified values in pseudo primary input (PPI) of  $V_1$  and specified values in PPI of  $V_2$ . If PPI of  $V_2$  has a specified value and the corresponding PPI in the  $V_1$  has an unspecified value X, then it fills the X in  $V_1$  with the specified value in  $V_2$ . Then, it performs logic simulation using the updated

initialization vector  $V_1$  to find more newly specified values in the next state outputs which can be used to fill the unspecified values in  $V_1$ .

Figure 2.1: Flow of Progressive Match Filling [31]

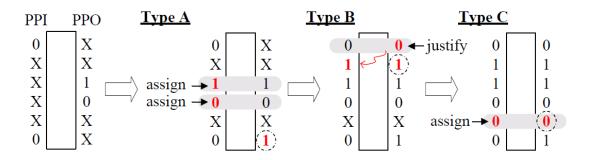

Another technique for reducing capture power in transition faults is presented in [27]. This technique, called low-capture-power (LCP), attempts to reduce the hamming distance between the shifted in test vector and the CUT response to it by assigning 0s and 1s to unspecified bits in a test cube. LCP fill divides filling each scan cell into four cases depending on if the pseudo primary input and/or pseudo primary output is specified or not. If in a scan cell PPI and the PPO bits are both specified nothing can be done. If in a scan cell PPI bit is unspecified and the corresponding PPO bit is specified it assigns the PPO value to the PPI bit. This can be done because the PPI values are shifted into the CUT. If the PPI bit is specified and the PPO bit is unspecified it tries to justify in the PPO the value of PPI value. If both are unspecified, LCP tries to assign a value to the PPI that

will produce the same value in the PPO. When the filling is done, i.e. no more unspecified bits remain in the test cube, the resulting test pattern is fault simulated for newly detected faults. Then a new set of faults is targeted for detection and so on. The LCP technique leads to considerable reduction in peak and average WSA of LOC tests compared to random fill of the unspecified values in the test cubes. This method has the advantage of not requiring any modifications to the CUT and existing ATPGs. However the run time of this procedure could be potentially high. The reasons for this are the repeated simulations of incrementally updated test cubes and use of implications and line justification steps as part of the procedure so it is non-scalable to industrial designs. LCP fill increases pattern count considerably because the filling procedure detects fewer faults than the normal random fill method.

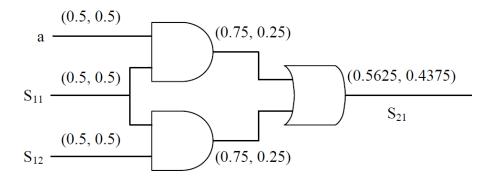

The preferred fill (PF) technique proposed in [28], attempts to reduce the Hamming distance between the initialized and captured patterns by using a procedure based on signal probabilities. PF fills all unspecified bits in the cube at once with predetermined values (called preferred values) that will produce less WSA than random fill. To determine these values, PF calculates the signal probabilities of each circuit PPO. Figure 2.2 shows an example of signal probability calculation for a simple circuit.

It uses simple procedures to compute signal probabilities that ignore correlation between gate inputs together. So it assigns the probability of 0.5 to logic value 0 and 1 for each PI and PPI, and calculates every signal probability until the PPOs are reached. If the PPO has larger signal probability of being at 1 the preferred value for the correspondent PPI is 1. The same happens at 0, and if they have equal probabilities the preferred value is unspecified and the position is filled at random. The method can be applied to both stuck-at and transition faults. This method increases pattern counts significantly because a constant pre-determined value is used to fill unspecified bits in test cubes and so fortuitous detection reduces.

Figure 2.2: Signal probability calculations [28]

In order not to increase test pattern counts, a given set of specified test patterns are relaxed to obtain tests with unspecified values and then the unspecified values are filled using preferred fill [27] or LCP [28] values. In this method [29], after generating a test set in the conventional way the post processing applies a procedure called relaxation. Relaxation consists of identifying don't care positions on each test pattern and unspecifying them. After relaxing every pattern the filling method in [27] or [28] or combination of both methods is used to obtain a low capture power test set. The advantage over the previous methods is that the pattern count remains the same (or lower) when compared to the original test set, at the cost of increased run times, because relaxation is a time consuming procedure.

In [30], authors proposed a hybrid technique employing two methods; justification based method proposed in [27] and probability based method proposed in [28]. This technique, called JP-filling, is both effective and scalable in minimizing launch cycle power supply noise. JP-filling tries to reduce the Hamming distance between the pattern itself and its output response. The result is reduced flip-flop switching activity in the launch cycle, which indirectly brings down the switching activity during launch cycle. The first operation is conducted for PPI-PPO bit-pairs of the form <logic value, X>, but not for any PPI-PPO bit-pair of the form <X, X> for which time-consuming, multiple passes of justification are needed. This is to achieve higher scalability. The second

operation is conducted for PPI-PPO bit-pairs of the form <X, X>, but in multiple passes. That is, the logic value for a PPI X-bit is determined only if its corresponding PPO X-bit has significantly different 0 and 1 probabilities; otherwise, signal probabilities are recalculated in the next pass. This is to achieve higher effectiveness through improved accuracy in logic value determination. Figure 2.3 gives a JP-filling example. The circled PPO's are the ones that become specified after event-driven simulation.

Figure 2.3: A JP-filling example

## 2.2.2 DFT Modification Techniques

In [32], the authors keep the peak power below a specified limit by inserting a few test points at selected scan cell outputs. Given a set of test patterns, logic simulation is carried out to identify the cycles in which peak power violations occur. Those cycles are called violating cycles. By using integer linear programming (ILP) techniques, the optimization problem is solved to select as few test points as possible such that all violating cycles can be eliminated. The disadvantages of this method are inserting test points that are test set dependent. Therefore, violating cycles may not be eliminated when the test set is changed. In addition, solving an ILP problem with a constraint matrix in the size of  $vc \times 2sc$  is not applicable to large industrial circuits, where vc is the total number of violating cycles, and sc is the total number of scan cells.

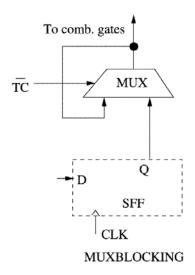

In [33] authors used multiplexer at the output of the scan cells which hold the previous states of the scan register during shifting and, thus, prevent activity in combinational logic. As shown in Figure 2.4 the output of the scan cell is connected to one of the data inputs of the MUX, while the output of the MUX has a feedback connection to the other data input and also feeds the combinational gates that the scan cell will usually feed. In this way when SE is at 1 the MUX holds its previous value and when SE is at 0 the circuit assumes normal functioning. Another method for reduction in combinational power using blocking is to use a scan-hold circuit as a sequential element.

Figure 2.4: Mux as a blocking logic

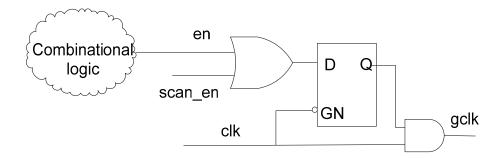

In [35], authors proposed to use the existing clock gating logic in the design to hold the clock controlling the flops that are not required to switch within a given test pattern (Figure 2.5). During scan shift the scan enable signal overrides the clock gate and allows all flops to clock concurrently. During the capture cycle the scan enable is inactive and the clock gate is controlled from its functional enable. If the functional enable can be selectively disabled in conjunction with the ATPG algorithm then capture power can be reduced without impacting the ability to capture fault effects.

Figure 2.5: Clock gate cell operation during test

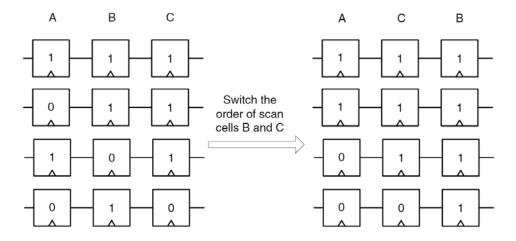

A scan cells reordering technique is proposed in [36] to reduce switching activity, and hence power dissipation in scan design by changing the order of scan cells in each scan chains. In deterministic test patterns, the best order of cells is the one that gives the best compromise between reducing the transitions in the scan cells during both scanning in test patterns and scanning out captured responses. As a simple example to demonstrate how cell ordering algorithms reduce the number of transitions in the scan-chain, assume a scan chain with 3 flip-flops A, B, and C with initial values of 111 as shown in Figure 2.6. Assume that the test vector 010 is to be scanned into the scan chain. The total number of transition generated in the scan chains by the loading of vector 010 will be equal to 6. However, by changing the order of scan cells B and C, the number of transitions is reduced from 6 to 2. The modified scan cell order may conflict with other objectives during scan chain optimization, such as wire length minimization and timing closure. To address this problem, the approach from [37] shows that, by clustering scan cells from the same physical region of the chip and chaining them in a power-aware fashion, it is possible to efficiently trade off test power reduction and wire length minimization. Although these algorithms reduce average and peak power consumption during the scanning cycles, but they have no effect on capture power reduction.

Figure 2.6: Scan chain reordering

A scan chain architecture using scan chain partitioning and disabling is proposed in [38] to reduce both the average and peak power consumption. The scan chain is split into several length-balanced segments and only one segment is enabled in each test clock during both shift and capture cycles. In this method, only a subset of scan cells is loaded with test stimulus and captured with test responses by freezing the remaining scan cells according to the spectrum of unspecified bits in the test cubes. Figure 2.7 shows a circuit whose scan chains have been segmented. Although this method reduces peak and average capture power during test, they increase test time and test pattern counts, in addition to consume additional chip area to enable independently clocking scan segments.

In [39] authors utilized a segmented scan chain environment to see the effect of partial clocking on transition faults and power reduction when segmented scan chains are clocked selectively in the capture mode. The benefit of partial clocking increases as the resolution of a gated clock (the number of registers with a gated clock) increases. By dividing a circuit into multiple scan segments, authors also improved transition fault coverage using launch-off-capture test method.

Staggering the clock [40] during shift or capture achieves power savings, without significantly affecting test application time. Staggering can be achieved by ensuring that

the clocks to different scan flip flops (or chains) have different duty cycles or different phases, thereby, reducing the number of simultaneous transitions. The biggest challenge to this technique is its implications on the clock generation, which is a sensitive aspect of chip design.

Figure 2.7: A circuit with segmented scan chains [38]

# 2.2.3 Functional / Pseudo Functional Scan Test Techniques

As we discussed in Chapter 1, design-for-testability (DFT) for synchronous sequential circuits allows the generation and application of tests that rely on non-functional operation of the circuit. This can result in unnecessary yield loss due to the detection of faults that do not affect normal circuit operation.

The test generation methods proposed in [41, 42] restrict the scanned in states to the set of reachable states to insure that the (CUT) operates only in the functional mode during capture cycles. Thus, such tests not only avoid abnormal switching activity during capture cycles but also avoid detection of certain faults that do not affect normal functional operation. Identifying reachable states has high complexity for large designs. This is addressed in [41, 42] by simulation based procedures that enumerate reachable states only as necessary for detecting targeted faults. No modifications are required to the test generation procedure and no sequential test generation is needed in these techniques. However for large designs determining that the state of the initialization pattern is a reachable state may be difficult.

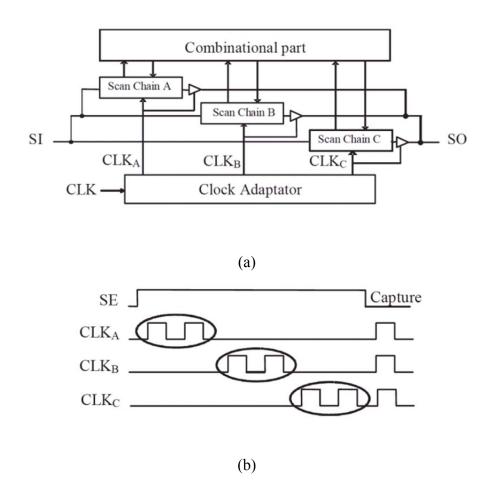

In [43], authors used a sequential boolean satisfiability (SAT) solver to extract the functional constraints in the system. While theoretically SAT solver is able to find almost all the unreachable states in a circuit, its computational complexity is extremely high and hence cannot be applied to a large circuit.