Theses and Dissertations

2008

# VLSI circuit defect diagnosis: open defects and run-time speed

Chen Liu University of Iowa

# Copyright 2008 Chen Liu

This dissertation is available at Iowa Research Online: http://ir.uiowa.edu/etd/8

# Recommended Citation

Liu, Chen. "VLSI circuit defect diagnosis: open defects and run-time speed." PhD (Doctor of Philosophy) thesis, University of Iowa,

http://ir.uiowa.edu/etd/8.

# VLSI CIRCUIT DEFECT DIAGNOSIS: OPEN DEFECTS AND RUN-TIME SPEED

by

Chen Liu

# An Abstract

Of a thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

August 2008

Thesis Supervisor: Professor Sudhakar M. Reddy

#### **ABSTRACT**

To shorten time-to-market of VLSI circuit chips, the yield must be ramped up by quickly discovering and rectifying the causes for systematic defects. Due to the shrinking feature size of devices 90nm and below, yield ramp up is becoming more and more difficult. Volume diagnosis with statistical learning is needed to cost effectively discover systematic defects. An accurate and high throughput diagnosis tool is required to diagnose large numbers of failing devices to aid statistical yield learning. In this work, we propose techniques to improve diagnosis accuracy and resolution, techniques to improve run-time performance.

We consider the problem of determining the location of open defects in interconnects of deep submicron designs. We investigate a procedure that uses minimal information beyond the circuit net lists and give experimental results to demonstrate the defect resolution obtained using the method. The additional information used by the proposed method is a list of nodes in the neighborhoods of circuit nodes and the circuit layout. Specifically, difficult to determine circuit parameters of manufactured instances of a design such as coupling capacitances between circuit nodes and threshold voltages of gates in the circuit are not needed to use the proposed diagnosis procedure.

A dictionary called  $N_{FB}$  dictionary of small size and does not grow linearly with pattern count is proposed. It further reduced dictionary size over previous dictionary while still achieve higher failing pattern diagnosis performance than industry standard Effect-Cause diagnosis procedures.

In this work we also propose a method to achieve higher speedup with a marginally larger dictionary than the  $N_{FB}$  dictionary. We achieve this by identifying a set of faults called hyperactive faults for which we create a novel dictionary. Hyperactive faults tend to propagate fault effects to many observation points and cost a large amount of time to simulate.

In addition to speed-up of failing pattern diagnosis, we propose a method to improve passing pattern performance. A pass-fail dictionary with high compression ratio is proposed. The dictionary is stored in a database on disk with a small cache memory and high diagnosis performance is demonstrated.

| Abstract Approved: |                      |

|--------------------|----------------------|

| 11                 | Thesis Supervisor    |

|                    | 1                    |

|                    |                      |

|                    | Title and Department |

|                    |                      |

|                    |                      |

|                    | Date                 |

# VLSI CIRCUIT DEFECT DIAGNOSIS: OPEN DEFECTS AND RUN-TIME SPEED

by

Chen Liu

A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

August 2008

Thesis Supervisor: Professor Sudhakar M. Reddy

# Graduate College The University of Iowa Iowa City, Iowa

| CE                      | RTIFICATE OF APPROVAL                                                                                   |                 |

|-------------------------|---------------------------------------------------------------------------------------------------------|-----------------|

| -                       | PH.D. THESIS                                                                                            |                 |

| This is to certify that | at the Ph.D. thesis of                                                                                  |                 |

|                         | Chen Liu                                                                                                |                 |

| for the thesis require  | by the Examining Committee ement for the Doctor of Philosophy and Computer Engineering at the August 20 | 008 graduation. |

| Thesis Committee:       | Sudhakar M. Reddy, Thesis Supervisor                                                                    | -               |

|                         | Wu-Tung Cheng                                                                                           | -               |

|                         | Jon G. Kuhl                                                                                             | -               |

|                         | Sukumar Ghosh                                                                                           | -               |

|                         | John P. Robinson                                                                                        | -               |

|                         | Karl Lonngren                                                                                           | -               |

To my family

#### **ACKNOWLEDGMENTS**

First and foremost, I would like to express my sincere gratitude to my academic advisor, Professor Sudhakar M. Reddy, for his excellent guidance and solid management throughout this research. Without his guidance, this work would not be even possible. Equal amount of thanks are given to Dr. Wu-Tung Cheng for his constructive advices and knowledgeable explanations. I also want to thank my committee members Prof. Kuhl, Prof. Zhang, Prof. Robinson, and Prof. Lonngren for serving on my committee and giving valuable suggestions.

Mentor Graphics Corporation, Semiconductor Research Corporation (2007-TJ-1642) provided a resourceful research environment and financial support. I hereby express my sincere appreciation.

Many thanks to my friends and co-workers in my research: Huaxing Tang, Wei Zou, Manish Sharma, Chen Wang.

I would like to thank my family for their understanding and encouragement.

#### **ABSTRACT**

To shorten time-to-market of VLSI circuit chips, the yield must be ramped up by quickly discovering and rectifying the causes for systematic defects. Due to the shrinking feature size of devices 90nm and below, yield ramp up is becoming more and more difficult. Volume diagnosis with statistical learning is needed to cost effectively discover systematic defects. An accurate and high throughput diagnosis tool is required to diagnose large numbers of failing devices to aid statistical yield learning. In this work, we propose techniques to improve diagnosis accuracy and resolution, techniques to improve run-time performance.

We consider the problem of determining the location of open defects in interconnects of deep submicron designs. We investigate a procedure that uses minimal information beyond the circuit net lists and give experimental results to demonstrate the defect resolution obtained using the method. The additional information used by the proposed method is a list of nodes in the neighborhoods of circuit nodes and the circuit layout. Specifically, difficult to determine circuit parameters of manufactured instances of a design such as coupling capacitances between circuit nodes and threshold voltages of gates in the circuit are not needed to use the proposed diagnosis procedure.

A dictionary called N<sub>FB</sub> dictionary of small size and does not grow linearly with pattern count is proposed. It further reduced dictionary size over previous dictionary while still achieve higher failing pattern diagnosis performance than industry standard Effect-Cause diagnosis procedures.

In this work we also propose a method to achieve higher speedup with a marginally larger dictionary than the  $N_{FB}$  dictionary. We achieve this by identifying a set of faults called hyperactive faults for which we create a novel dictionary. Hyperactive faults tend to propagate fault effects to many observation points and cost a large amount of time to simulate.

In addition to speed-up of failing pattern diagnosis, we propose a method to improve passing pattern performance. A pass-fail dictionary with high compression ratio is proposed. The dictionary is stored in a database on disk with a small cache memory and high diagnosis performance is demonstrated.

# TABLE OF CONTENTS

| LIST OF TABLES   |                                                           | . viii |

|------------------|-----------------------------------------------------------|--------|

| LIST OF FIGURES  | S                                                         | ix     |

| CHAPTER          |                                                           |        |

| 1. INTRODUCT     | ΓΙΟΝ                                                      | 1      |

| 2. REVIEW OF     | DEFECT DIAGNOSIS ALGORITHMS                               | 3      |

| 2.1              | Fault Models                                              | 3      |

| 2.2              | Cause-Effect Diagnosis                                    |        |

| 2.3              | Effect-Cause Diagnosis                                    |        |

| 2.3.1            | Single Location at a Time (SLAT)                          |        |

| 2.3.1            | Multiple Fault Diagnosis                                  | /<br>Q |

| 2.4              | Defect Diagnosis Using Open Fault Model                   | 16     |

| 2.4.1            | Super Fault or Composite Stuck-at Open Fault Diagnosis    | 17     |

| 2.4.1            | Super Fault of Composite Stuck-at Open Fault Diagnosis    | l/     |

|                  | Symbolic Simulation to Identify Open Defects              | 10     |

| 2.4.3            | Interconnect Open Diagnosis with Physical Information     | 19     |

|                  | FECT DIAGNOSIS WITH MINIMAL PHYSICAL ON                   | 23     |

| 11 (1 0111/11111 | <u> </u>                                                  | 0      |

| 3.1              | Introduction                                              | 23     |

| 3.2              | Preliminaries                                             |        |

| 3.2.1            | Review of Previous Works                                  | 26     |

| 3.2.2            |                                                           |        |

| 3.3              | Identifying Open Defects with Only Neighborhood Node List | 50     |

| 5.5              | Information                                               | 31     |

| 3.3.1            | Identifying the Open Nets Using Logic Diagnosis           | 21     |

| 3.3.2            | Identifying the Open Segments Using Segment Fault         | 31     |

| 3.3.2            |                                                           | 22     |

| 2 2 2            |                                                           | 3∠     |

| 3.3.3            | Identifying Open Vias by Solving Inequalities             | 32     |

| 3.3.4            | Open Via Driving Multiple Gates                           | 3/     |

| 3.4              | Experimental Results                                      |        |

| 3.5              | Discussion                                                |        |

| 3.6              | Conclusions                                               | 4 /    |

| 4 IMPROMINIC     | DIA CNIQUIG DEDECODA ANICE WITH MINIMAL MEMODY            |        |

|                  | DIAGNOSIS PERFORMANCE WITH MINIMAL MEMORY                 | 40     |

| OVERHEAD         |                                                           | 48     |

| <i>l</i> . 1     | Intro disation                                            | 40     |

| 4.1              | Introduction                                              |        |

| 4.2              | Motivations                                               |        |

| 4.2.1            | Terminology                                               | 49     |

| 4.2.2            | Review of Effect-Cause Diagnosis                          | 50     |

| 4.2.3            | Review of Cause-Effect Diagnosis                          | 52     |

| 4.2.4            | Signature-Based Small Dictionary                          | 54     |

| 4.3              | Proposed Techniques and Diagnosis Procedure               | 55     |

| 4.3.1            | N <sub>FB</sub> Dictionary                                |        |

| 4.3.2            | FFR Grouping                                              | 57     |

| 4.3.3                   |                                                                         | 59  |

|-------------------------|-------------------------------------------------------------------------|-----|

| 4.4                     | Experimental Results                                                    | 60  |

| 4.4.                    | - J - · · · · · · · · · · · · · · · · ·                                 |     |

| 4.4.2                   |                                                                         |     |

| 4.4.3                   |                                                                         | 67  |

| 4.5                     | Conclusion                                                              | 68  |

| 5. INCREASE<br>DICTIONA | D FAULT DIAGNOSIS THROUGHPUT USING<br>RY FOR HYPERACTIVE FAULTS         | 70  |

| 5.1                     | Introduction                                                            | 70  |

| 5.2                     | Review of Previous Works                                                |     |

| 5.2.                    |                                                                         |     |

| 5.2.2                   | Review of Cause-Effect Diagnosis                                        | 73  |

| 5.2.3                   | Review of Effect-Cause Diagnosis                                        | 73  |

| 5.2.4                   | 4 Signature-based Small Dictionary                                      | 75  |

| 5.2.5                   |                                                                         | 77  |

| 5.3                     | Dictionaries for Hyperactive Faults                                     | 81  |

| 5.3.                    | 1 Failing Bit Count Dictionary                                          | 82  |

| 5.3.2                   | Failing Bit Count Dictionary  Hyperactive Faults Signature Dictionary   | 83  |

| 5.3.3                   | 3 Dictionary Sizes                                                      | 84  |

| 5.3.4                   |                                                                         | 86  |

| 5.3.:                   | 5 Example of a Diagnosis Flow                                           | 88  |

| 5.4                     | Experimental Results                                                    | 89  |

| 5.5                     | Conclusions                                                             | 93  |

| 6. PASSING P            | PATTERN PERFORMANCE IMPROVEMENT                                         | 94  |

| 6.1                     | Introduction                                                            | 94  |

| 6.1.                    | I Ideas on Passing Pattern Processing Speed Up                          | 96  |

| 6.1.2                   | Database for Pass-Fail Dictionary Pass-Fail Information Characteristics | 97  |

| 6.1                     | Pass-Fail Information Characteristics                                   | 99  |

| 6.2                     | Review of Previous Works                                                | 103 |

| 6.2.                    | Frequency Directed Run-Length Codes (FDR)                               | 103 |

| 6.2.2                   | 2 Golomb Codes                                                          | 106 |

| 6.2                     |                                                                         |     |

| 6.2.4                   | 4 Burrows-Wheeler Transformation                                        | 110 |

| 6.3                     | Proposed Methods                                                        | 110 |

| 6.4                     | Experimental Results                                                    | 112 |

| 7. CONCLUSI             | IONS                                                                    | 116 |

| REFERENCES              |                                                                         | 118 |

# LIST OF TABLES

| Table 1:  | Open Diagnosis Experiment Results                               | 44  |

|-----------|-----------------------------------------------------------------|-----|

| Table 2:  | Inaccurate Neighbor Capacitances                                | 46  |

| Table 3:  | Design Information and Dictionary Size                          | 53  |

| Table 4:  | FFR Grouping Faults                                             | 58  |

| Table 5:  | Memory Overhead VS. Small Dictionary                            | 64  |

| Table 6:  | Information on Some Industrial Circuits Used in the Study       | 78  |

| Table 7:  | Failing Bit Count (FBC) Dictionary                              | 83  |

| Table 8:  | Hyperactive Faults Signature (HFS) Dictionary                   | 85  |

| Table 9:  | Sizes (in MB) of Small Dictionary [37], NFB and HF Dictionaries | 86  |

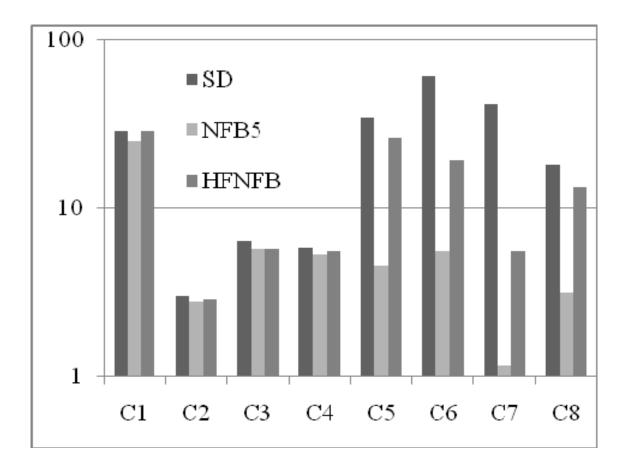

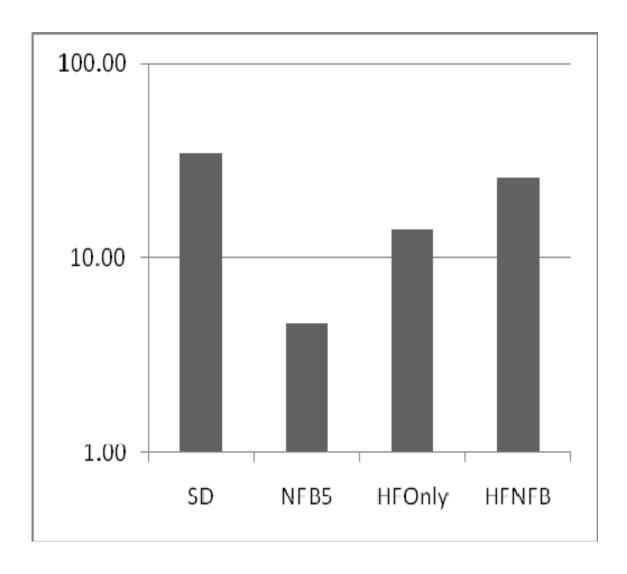

| Table 10: | Average Failing Pattern Process Time for Each Case in Seconds   | 92  |

| Table 11: | Information on Some Industrial Circuits Used in the Work        | 94  |

| Table 12: | Circuit Data for Pass Fail Information Characteristics          | 100 |

| Table 13: | FDR Uni-Phase Coding Example                                    | 105 |

| Table 14: | FDR Alternating Coding Example                                  | 106 |

| Table 15: | Golomb Uni-Phase Coding Example                                 | 107 |

| Table 16: | Burrows-Wheeler Transformation                                  | 111 |

| Table 17: | Pass-Fail Dictionary Circuit Info                               | 112 |

| Table 18: | Pass-Fail Dictionary Experiment Data                            | 114 |

# LIST OF FIGURES

| Figure 1: Flow of Diagnosis Procedure Using Effect-Cause Diagnosis        | 6  |

|---------------------------------------------------------------------------|----|

| Figure 2: Byzantine Effect                                                | 17 |

| Figure 3: Interconnect Open Model                                         | 20 |

| Figure 4: A Net's Routing in the Layout                                   | 27 |

| Figure 5: Interconnect Open Model                                         | 28 |

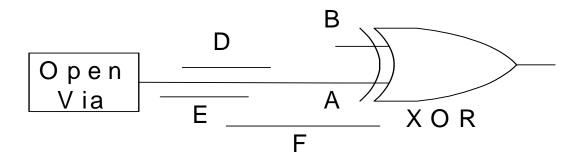

| Figure 6: Circuit for Example 1                                           | 36 |

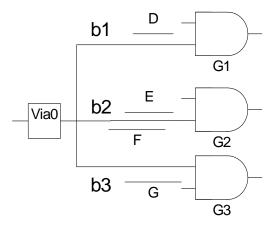

| Figure 7: Example of Via Driving Multiple Gates                           | 38 |

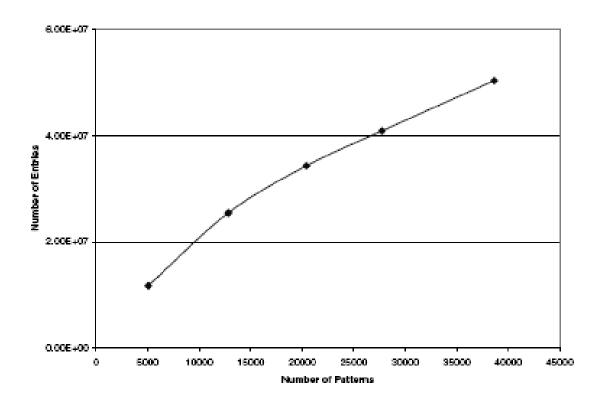

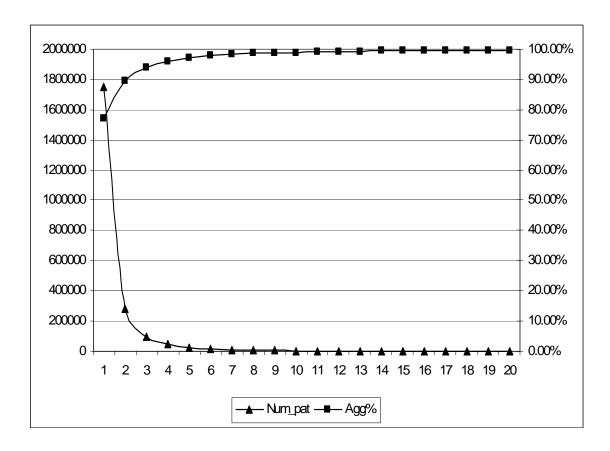

| Figure 8: Size of Small Dictionary for D1                                 | 54 |

| Figure 9: Number of Failing Bit per Failing Pattern Distribution          | 56 |

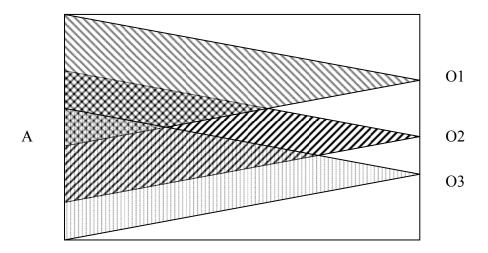

| Figure 10: Intersection of Critical Path Tracing                          | 57 |

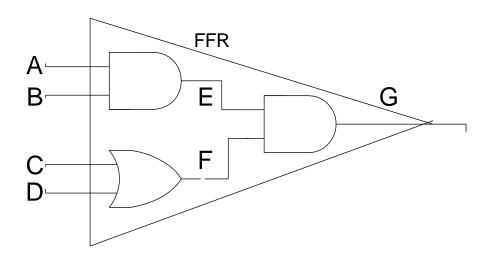

| Figure 11: Fault Grouping Using FFR.                                      | 58 |

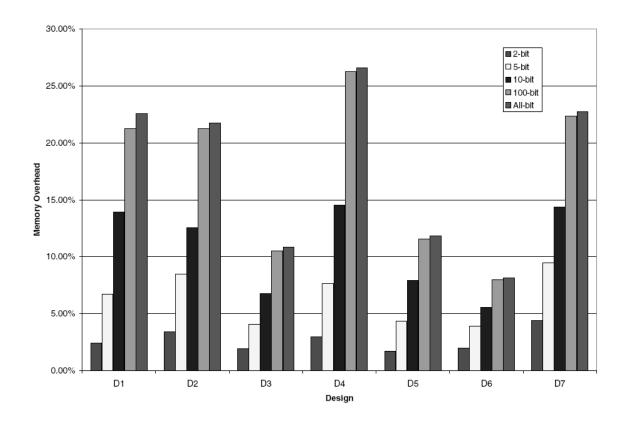

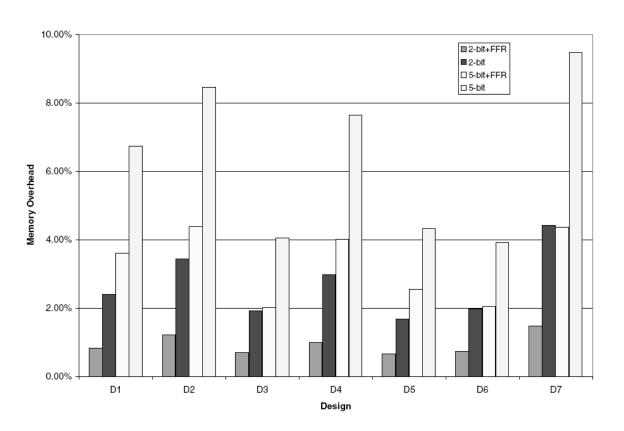

| Figure 12: Memory Overhead Without Fault Grouping                         | 61 |

| Figure 13: Memory Overhead With Fault Grouping                            | 63 |

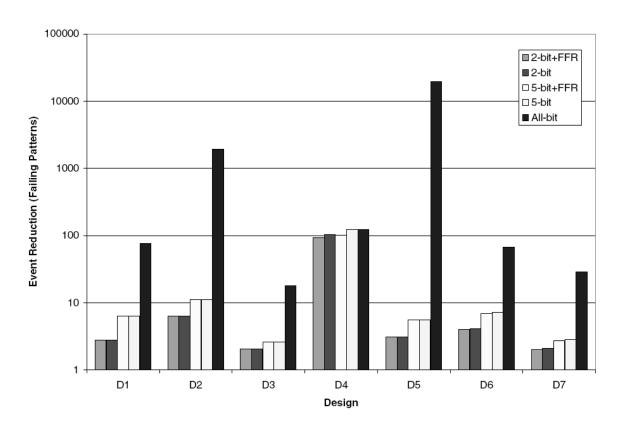

| Figure 14: Reduction of the Number of Events                              | 66 |

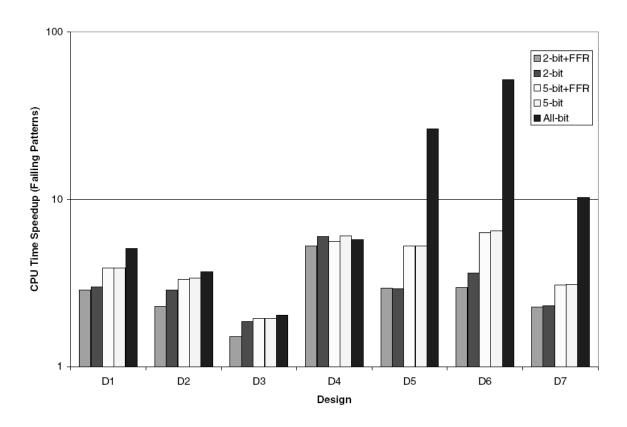

| Figure 15: CPU Time Speedup (Failing Patterns)                            | 67 |

| Figure 16: Flow of Diagnosis Procedure Using Effect-Cause Diagnosis       | 74 |

| Figure 17: Flow of Diagnosis Procedure Using Small Dictionary             | 76 |

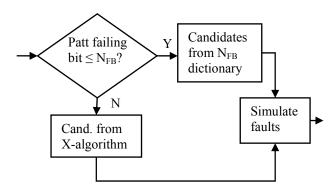

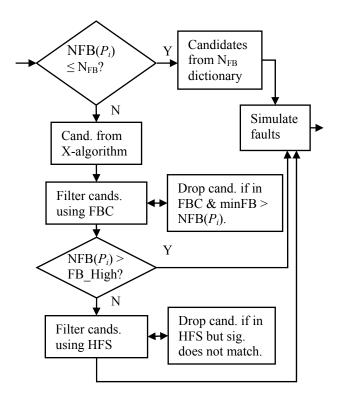

| Figure 18: Flow of Diagnosis Procedure Using N <sub>FB</sub> Dictionary   | 77 |

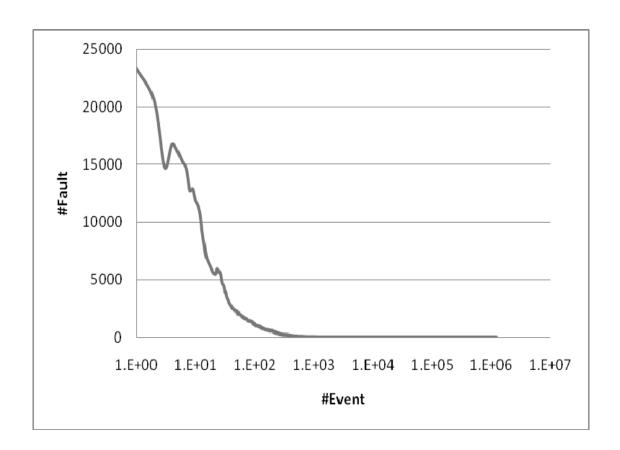

| Figure 19: Distribution of the Number of Events                           | 79 |

| Figure 20: Hyperactive Fault Characteristics                              | 80 |

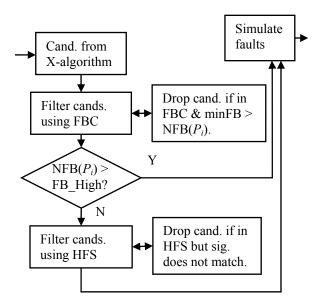

| Figure 21: Flow of Diagnosis Procedure Using $N_{FB}$ and HF Dictionaries | 87 |

| Figure 22: Diagnosis Time SpeedUp                                         | 90 |

| Figure 23: Flow of Diagnosis Procedure Using Only HF Dictionary           | 91 |

| Figure 24: Hyperactive Fault Dictionary Only Approach Speed Up            | 92 |

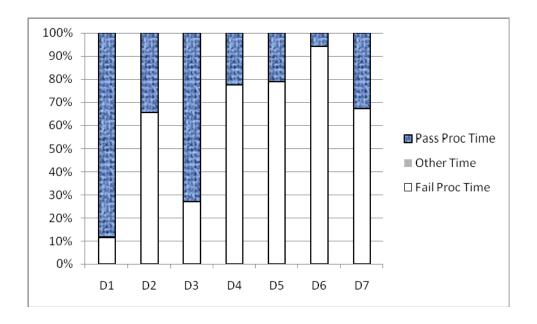

| Figure 25: Diagnosis Time in Each Major Step                              | 95 |

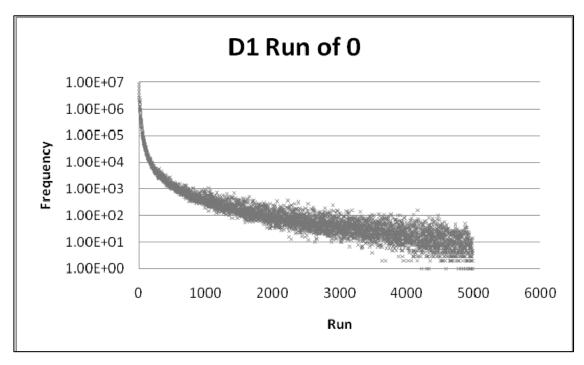

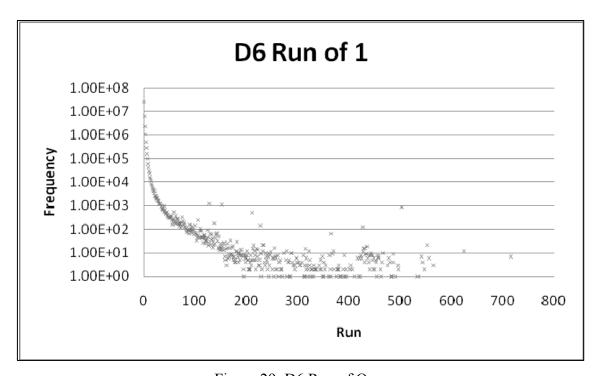

| Figure 26: D1 Run of Zero            | 101 |

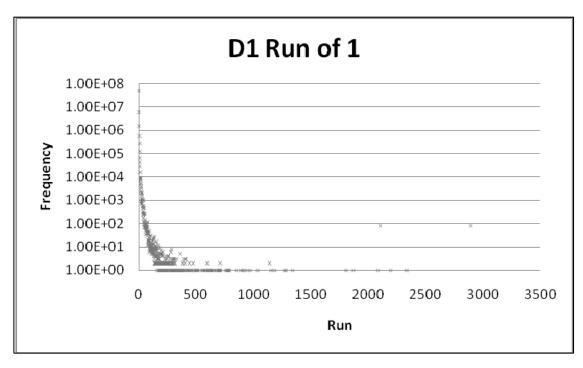

|--------------------------------------|-----|

| Figure 27: D1 Run of One             | 101 |

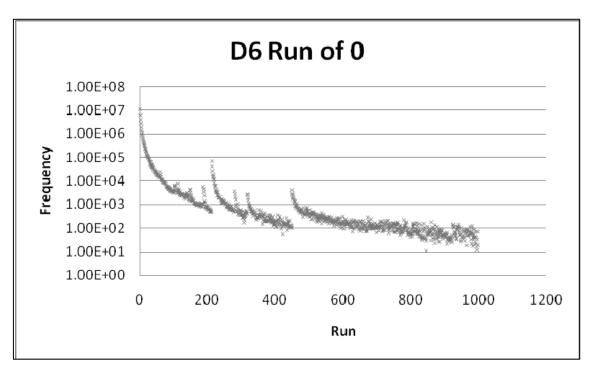

| Figure 28: D6 Run of Zero            | 102 |

| Figure 29: D6 Run of One             | 102 |

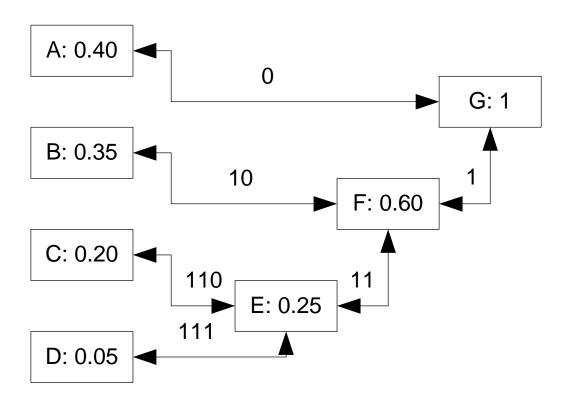

| Figure 30: Example of a Huffman Tree | 109 |

#### CHAPTER 1. INTRODUCTION

The purpose of fault diagnosis is to determine the cause of failure in a manufactured chip. To assist a designer or failure analysis engineer, the diagnosis tool tries to locate the possible positions of the failure effectively and quickly. The quality of a diagnosis impacts directly the time-to-market and the total product cost. Yield analysis can use diagnosis results of multiple failed devices to collect statistical data to identify yield limiting manufacture process issues or design errors. Due to the increasing difficulty of physical inspection for today's multi-layer deep sub-micron designs and the increasing cost of inspection equipments, logic diagnosis becomes a very important step in the process of silicon debug, yield ramp-up and field return analysis. We will briefly review the field of defect diagnosis.

A state-of-the-art diagnosis tool should have the following properties:

High diagnosis resolution: The number of candidate locations reported should be as small as possible. If the reported candidate set size is too large, the real defect will be hidden in vast number of false candidates and makes physical failure analysis extremely difficult. Cost of time and human power would be huge.

High diagnosis accuracy: The set of candidate locations reported should be close to the set of real defects validated by physical analysis. Low accuracy wastes time and resources in physical failure analysis because the reported candidate set has low correlation with the real defects.

High runtime efficiency: The speed of performing quality diagnosis should be high to facilitate volume diagnosis. With deep-submicron processes, especially 65nm design and below, systematic defects have become dominant. In order to catch systematic defects, a large volume of failed chips need to be diagnosed and the diagnosis results used for the statistical analysis. To diagnose a large number of failed chips in a reasonable time, the run time of diagnosis must be short.

The objective of diagnosis research is to improve diagnosis resolution and accuracy as well as improve diagnosis runtime performance. To make the research practical, the techniques developed were built on a commercial diagnosis tool and tested with real industrial designs. More realistic problems would be discovered by industrial circuits than small academic benchmarks.

Following the introduction, we will briefly review previous works on the defect diagnosis in Chapter 2 and propose an open defect diagnosis technique in Chapter 3. In Chapter 4 we will propose a method of using dictionary to improve failing pattern diagnosis. In Chapter 5 we propose an additional dictionary to address the issue of hyperactive faults. In Chapter 6, a compressed database dictionary method to improve passing pattern diagnosis performance is proposed. Chapter 7 concludes the thesis.

#### CHAPTER 2. REVIEW OF DEFECT DIAGNOSIS ALGORITHMS

In this chapter, we review current fault model based diagnosis techniques, including stuck fault model and open model. Also single fault diagnosis and multiple fault diagnosis are reviewed.

#### 2.1 Fault Models

We use fault models to model the effect of a defect for diagnosis. Currently logical fault models are widely used due to speed of simulation and simplicity. A logic fault model describes faulty behavior of a defect at the logic level. Model based defect diagnosis is a procedure to identity defects by using fault model simulations. Popular models are: stuck-at fault model, bridge fault model, open fault model, gate delay fault model and path delay fault model.

Stuck-at fault model: Stuck-at is the simplest and most widely used model. Yet it effectively describes the behavior of a large portion of defects. In the stuck-at fault model, a node in the circuit always takes a fixed logic value, either 0 (stuck-at 0) or 1 (stuck-at 1). Stuck-at 0 could be the result of a short to the ground line. Stuck-at 1 could be the result of a short to the power supply line.

Bridge fault model: The bridge fault model is used to describe logic behavior of two nodes that are shorted in the circuit. Common bridge fault models are: wired-AND/OR fault model, dominate fault model, 4-way bridge fault model. The wired-AND/OR bridge model assumes that the faulty node of the bridge always has the logic value 0(1). The dominate bridge model assumes that one node of the bridge always dominates the other node by imposing its logic value. Bridge model is a important model since bridging is a common defect in circuits.

Open fault model: Open fault model attempts to model the open defects, such as electrical open, break, and disconnected via in a circuit. Opens can result in state-holding, intermittent, and pattern-dependent fault effects, thus open models are more complex.

Delay fault model: To represent timing related defects, gate delay model and path delay model are used. The gate delay model assumes the defect-induced delay is only between a single gate input and output. The path delay model spreads the total delay along a circuit path from a circuit input to a circuit output.

Most diagnosis is based on stuck-at fault model. When we don't know what the defect category is, we first run stuck-at diagnosis. Base on the stuck-at diagnosis result, we can apply bridge and open model to determine whether the suspect is more like a bridge or open.

There are two ways to use stuck-at fault model. One is the Effect-cause diagnosis that assumes there is a stuck-at fault and back trace from erroneous circuit outputs to find candidates, and then simulate the candidates to find the ones that best match the failure responses observed from the tester. The other is the Cause-effect diagnosis which uses a pre-simulated fault dictionary to lookup the failure response.

## 2.2 Cause-Effect Diagnosis

A fault dictionary is a record of the errors that the modeled faults in the circuit are expected to cause [1]. It stores a mapping from the modeled fault to simulated response. The procedure of fault dictionary diagnosis is to look up the mapping table to find the suspect that is simulated to cause the faulty behavior. The fault candidate whose expected faulty signature matches best with the observed faulty signature will be chosen as the final fault candidate. If we assume a single stuck-at defect, there should be an exact match between the expected signature of the fault candidate and the observed faulty signature.

There are several ways to store the signature information: a pass-fail dictionary, complete dictionary and compressed signature dictionary. The pass-fail dictionary only stores a single bit (pass or fail) of failure information for each fault per test pattern. Since it omits useful information of where the failing bits are, it renders distinguishing some

faults impossible. A complete dictionary is a full-response dictionary, which stores all circuit outputs in the presence of each fault for each test pattern. The number of bits required to store a complete dictionary equals F\*V\*O, where F is the number of faults, V is the number of test patterns, and O is the number of primary outputs. The downside of a complete dictionary is that the storage it requires is huge for designs with multi-million gates. The compressed signature dictionary is obtained by feeding the output information through a 32 or a 64 bit multiple input signature register (MISR) to get a compressed signature. There is the problem of aliasing, that two different output responses may be compressed to the same failure signature. But by choosing a MISR with more bits, the chance of aliasing is slim. The compressed signature dictionary saves storage space and provides about the same diagnosis resolution as the complete dictionary.

In order to reduce the memory requirement for a complete dictionary, a number of procedures are proposed. In [2], dynamic creation, test set partitioning, and reduced fault lists are used to achieve a reduced fault dictionary. Pomeranz and Reddy [3] proposed a space compaction method that augments a pass-fail dictionary using a greedy algorithm to choose the primary outputs of some test patterns from a full response dictionary, which can distinguish the largest number of undistinguished fault pairs.

Two diagnostic tree structures: vector-based diagnostic experiment tree and output-based diagnostic experiment tree are proposed in [4] to encode the full response dictionary. Vector-based diagnostic experiment tree in which each level represents the application of a test vector, and each edge e is associated with a list of outputs O(e) that is the set of all the primary outputs of the circuit. Output-based diagnostic experiment tree in which each level represents a (test vector, output) pair rather than a test vector, and each edge is associated with a single primary output of the circuit.

Chess and Larrabee introduced an error set data structure in [5] to construct the dictionary. An error set is a set of primary outputs that carry errors. A fault often has the

same error set for many test patterns. To reduce the redundancy, only one copy of each error set is saved. It's similar to signature based dictionary.

W. Zou et al. [6] proposed a technique that combines the benefits of effect-cause and cause-effect diagnosis. For each fault and a test pattern that detects this fault, a 32-bit MISR compressor is used to generate a signature for this fault. Only unique signatures are stored for each fault. If for the same fault there are two patterns generating the same signature, only one copy is stored. This lowers the size of the dictionary to 32\*F\*U, where F is the number of faults and U is the average number of unique signatures for each fault. When performing diagnosis, the dictionary of the signatures (called small dictionary) are looked up to find the initial suspect lists and followed by fault simulation and matching.

# 2.3 Effect-Cause Diagnosis

Effect-cause diagnosis procedures typically use Single Location at a Time (SLAT) patterns [8]. SLAT patterns are those for which the observed failing response is matched by the simulated response (to this pattern) of a single fault at a location.

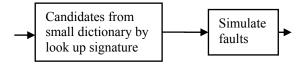

Figure 1: Flow of Diagnosis Procedure Using Effect-Cause Diagnosis

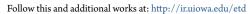

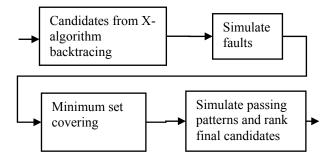

An effect-cause diagnosis procedure uses the following steps (cf. Figure 1):

- For each failing pattern, using X-algorithm [9] backtrace from the failing observation points for each pattern to obtain the initial set of fault candidates.

Use fault simulation to remove or filter out the candidates which do not match the observed failing bits of the pattern.

- 2) Perform minimum set covering on the candidates obtained in Step 1 above to find a minimal set of candidates to explain a maximum number of failing patterns. The selected candidates are referred to as suspects.

- 3) Simulate the suspects using all the passing patterns and compute a score based on the passing/failing pattern match/mismatch.

The advantage of effect-cause diagnosis is the small memory requirement. No dictionary is used and memory is available for holding larger designs and test patterns. The disadvantage is also obvious for volume diagnosis. Fault simulation may waste time repeatedly on some time consuming candidate faults that are filtered out. Using dictionary could effectively alleviate this situation by filtering out such faults without simulation. The other time consuming step in the standard effect-cause procedures is the time for backtracing to find the initial set of candidates. Using a dictionary backtracing can be completely avoided. Also, since the number of passing patterns is often very high, passing pattern processing in Step 3 above is time consuming also.

# 2.3.1 Single Location at a Time (SLAT)

Waicukauski and Lindbloom [8] proposed a diagnosis procedure based on effectcause diagnosis. The steps can be stated as below.

1) Initialize the fault-candidate list using a path-tracing technique. Initial fault candidates satisfy the following requirements to reduce the search space and improve diagnosis efficiency:

- The fault must reside in the input cone of a failing primary output (PO) of the given pattern

- There must exist a parity-consistent path from the faulty site to the failing PO

- If a failing pattern affects more than one PO, that candidate fault

must reside in the intersection of all the input cones of those failing

POs. This is based on a single defect assumption that for a failing

pattern, only one defect is activated and propagated.

- 2) Simulate each fault on the initial candidate list to see if it explains perfectly any of the failing patterns. If it does, assign to it a weight equal to the number of patterns it explains in the current list. Store the candidate fault with the greatest weight, and remove the failing pattern explained by it.

- 3) After explaining the entire failing-pattern list, or when the candidate list has all been examined, terminate the algorithm, and report the possible candidate sites. Sort candidate faults by their weights, reporting first the fault with the greatest weight.

#### 2.3.2 Multiple Fault Diagnosis

Several papers on multiple fault diagnosis have been published. Multiple-fault diagnosis mainly has the following difficulties:

If the multiple-fault problem is addressed directly, the error space grows exponentially. Error space = (# of lines)<sup>(# of defects(errors))</sup>[10], where # of lines is the number of signal lines in the circuit. This would be expensive to explore exhaustively. Assumptions and heuristics are proposed to address this problem.

Multiple-faults may interact with each other and create fault masking that is hard to diagnose.

# 2.3.2.1 Multiple Error Diagnosis Based on Xlists

In [43], the authors assumed that the logical errors are locally bounded. They use Xlist to mark a region with X (don't care) and perform 3-value simulation (0,1,X) to see if X is propagated to the output. If there is no X at the output, this region cannot contain fault. This method has good computation speed and generally good resolution when the faults are in clusters. However, in real designs faults may scatter and are not related. Using this method will not be effective to localize the fault locations.

Definition 1: (Xlist) A set of nodes whose actual values would be replaced during simulation by the value X, and the X-values propagated to subsequent logic levels by 3-valued logic simulation is called an Xlist.

Two forms of Xlists-Error models are defined. They are topologically bounded errors and region based error. Let the circuit have n nodes. Let T = (1,2,...,n) be a topological order on the nodes of the circuit.

Topologically bounded error: If the logic functions at the nodes in set  $E = \{e_1, e_2, ..., e_k\}$  are erroneous and satisfy the following: Exist i, j,  $(1 \le i \le j \le n)$  such that  $\{I \le e_q \le j, for any \ l \mid 1 \le q \le k\}$ . The integers i, j are the lower and upper bounds within which the error lies.

Region based error: If the logic functions at the nodes in set  $E = \{e_1, e_2, ..., e_k\}$  are erroneous and satisfy the following: For any l,  $1 \le q \le k$ , Structual\_Distance $(e_q, p) \le r$ .

When diagnosing topologically bounded errors, if the error is assumed to be bounded by k topologically, then by choosing overlapping Xlists will guarantee that there exists an Xlist containing all the error nodes: (1,2,...,2k), (k+1,k+2,...,3k), (2k+1,...,4k), ... ((roof(n/k)-2)k+1,...,n). The problem is again if the faults are scattered (k=n) then no diagnosis is possible.

When diagnosing region-based errors, the errors are assumed to be bounded by a radius r. By choosing a region-based Xlist at each node in the circuit that includes every node within a radius of r from that node will be guaranteed to contain the fault region.

The Xlists are simulated and compared to the primary output. If an Xlist produces a mismatch  $\{(0,1) \text{ or } (1,0)\}$  (match  $\{(0,0) \text{ or } (1,1)\}$ , partial match  $\{(X,0) \text{ or } (0,X)\}$ , the potential of that Xlist to contain the error nodes is reduced (increased, increased slightly), the Xlist is scored accordingly. Xlists are ranked according to the scores.

Symbolic variables can also be used to improve the accuracy of the diagnosis procedure. BDD representation of the symbolic function simulated removes the losses in 3-valued simulation. However there are circuits for which efficient BDD representation is hard to obtain. For large circuits, BDD could be too large to be practical.

# 2.3.2.2 Curable Vectors and Curable Outputs

In [44] the author proposed a diagnosing procedure with measures of two matching mechanisms: curable vectors (vector match) and curable outputs (failing PO match). Each possible candidate error is ranked according to these two matches. When single defect diagnosis does not explain the behavior, double defect diagnosis is considered and a heuristic for multiple (more than two) defect diagnosis is proposed.

Curable output: Assume that the response of a primary output Zi is failing with respect to an input vector v. It is called a curable output of a signal f with respect to test vector v if v is able to sensitize a discrepancy path from f to Zi. By notation, Zi belongs to curable output(f,v).

This essentially implies that a fault injected at f matched the failing output Zi for vector v. A curable output based heuristic is outlined as follows: First, the curable outputs of each signal with respect to each failing input vector is calculated, either by fault simulation, back propagation, or observability measure [45]. The signals are sorted based on their total curable outputs for all the failing vectors. The signal with a large number of curable outputs is regarded to be a more likely defect candidate.

Curable vector: An input vector v is curable by a signal f if the output response can be fixed by replacing f with a new Boolean function (re-synthesize). Partially curable

vector: An input vector is partially curable by a signal f if the response of every failing output reachable by f can be fixed by re-synthesizing f.

The diagnosis procedure will first assume only single defect existed and if there exists signals that pass the curable output and curable vector filtering then the process stops. Otherwise, double faults are assumed and every signal pair is enumerated to check against the curable vector based criterion. The detail procedure of double-defect diagnosis is referred to [46]. If any valid candidate is found, then the process stops. Otherwise, it moves on to the next stage to apply a heuristic to generate a signal list sorted by their defect possibilities. The heuristic algorithm records 2 ranks, rank1 records the total number of partially curable vectors while the rank2 records curable outputs. The signals are sorted according to rank1, if rank1 is the same, sort according to rank2.

# 2.3.2.3 Design Error Diagnosis and Correction via Test

# **Vector Simulation**

In [10] the authors proposed "Design Error Diagnosis and Correction via Test Vector Simulation" technique.

The algorithm guesses N or is given N, where N is the number of errors. First this method performs an implicit enumeration of suspicious lines in an effort to avoid the exponential explosion of the error space. Use path-trace [11] to collect candidate error lines to form a graph. Then the graph is reduced to prune the error space. Next error simulation is performed to output a set of candidate error lines Cerror. If Cerror is empty, then diagnosis is repeated for higher N and other parameter. Otherwise, it proceeds to correction and a logic verifier is used to output valid corrections.

Intersection Graph G = (V, E) is an undirected graph where each vertex contains a set of lines from the circuit. Edge (Vi, Vj) belongs to E if and only if intersection of Vi and Vj is not empty.

Each run of the path-trace will give a set of lines that will be added to one vertice. For example, line a, b and e would be the result of one run of path trace. The reduction of two adjacent vertices is actually taking the intersection of different fan-in cones from different back-tracing. Actually in the reduction, the real defect might be removed if it is not in the intersection of the merged vertices.

Implicit enumeration: all the N-error line tuples from G are enumerated. A tuple is a set of lines from different vertices.

Error Simulation: Simulates all the excitation combination of the N-error line tuple L. If for vector v that no error excitation scenario for L yields correct PO response, L is removed from the error list. This could be time consuming if N is large.

In the Correction phase, the list of corrections is exhaustively compiled.

# 2.3.2.4 Incremental Diagnosis and Correction of Multiple

#### Faults and Errors

Veneris et al proposed an incremental diagnosis method in [47]. It is outlined below. First, path-trace is used to mark suspect lines in the circuit. Then for each line a fault is injected and propagated. Heuristic 1: Sort lines according to the number of failing PO that are corrected by the fault on this line.

Second, some heuristics are used to guide the correction phase. Let  $V_{err}^{l}$  be the logic value bit list of line l for the subset of vectors that activate the errors. The i-th bit of  $V_{err}^{l}$  is the value on line l of simulating i-th input vector. Let  $l_1, l_2, ..., l_N$  be the set of lines where a set of valid corrections can be applied and rectify a design. Heuristic 2: Any qualifying correction must complement at least  $|V_{err}^{l}|/N$  bits in  $V_{err}^{l}$ . N is set initially at 70% of the total lines and reduced progressively when the algorithm returns no corrections. Heuristic 3: Any qualifying correction may sensitize only a small number of new paths to previously correct primary outputs. This is for fault masking that when adding some valid corrections that some correct PO maybe wrong but finally adding

other faults will mask these PO and match the faulty behavior. So we cannot drop a correction just because it creates some passing mismatches. The limit on the new mismatch is around 3-8%.

When searching the error space and adding corrections, the algorithm searches in a Breadth First Search/Depth First Search (BFS/DFS) trade-off way. This method requires exhaustive searching, which may be impractical for modern large industrial designs.

#### 2.3.2.5 <u>Incremental diagnosis and PO partition</u>

In [30], Wang et.al proposed a version of incremental diagnosis and primary output partition method.

A fault is defined as a hard fault when only one pattern detects it. The only pattern that detects a hard fault is called the essential pattern of this fault. Suppose n faults can perfectly explain some failing patterns. These n faults as a group are called the n-perfect candidate for those explained patterns.

Failing pattern types: Type-1: SLAT pattern. Type-2: Different fault effect that are not correlated. Type-3: Dependency on the faults. Type-2 can be dealt with PO partition. Type-3 is hard to diagnose.

$$FC(g) = \frac{\sum_{i=1}^{M} \left(\sum_{j=1}^{N} Ob_{ij}\right)}{M}.$$

Functional congestion FC of a gate g. M is the number of faults in g's fanin cone, N is the total number of patterns in test T. If the fault i under pattern j can be observed by g,  $Ob_{ij}$  is 1; otherwise 0. Gates with high functional congestion are often the cause of incomplete or wrong candidate fault sites, since multiple faults are more likely to interact

at functional congestion locations. N-detection test sets will increase the diagnosis results since more patterns will be Type-1 or Type-2 than in the single detection test set.

The A single Algorithm [26] is used as the base algorithm:

- Initialize the fault-candidate list using a path-tracing technique. Initial fault candidates satisfy the following requirements to reduce the search space and improve diagnosis efficiency:

- a. The fault must reside in the input cone of a failing PO of the given pattern

- There must exist a parity-consistent path from the faulty site to the failing

PO

- c. If a failing pattern affects more than one PO, that candidate fault must reside in the intersection of all the input cones of those failing POs (SLAT assumption)

- 2) Simulate each fault on the initial candidate list to see if it explains perfectly any of the failing patterns. If it does, assign to it a weight equal to the number of patterns it explains in the current list. Store the candidate fault with the greatest weight, and remove the failing pattern explained by it.

- 3) After explaining the entire failing-pattern list, or when the candidate lists have all been examined, terminate the algorithm, and report the possible candidate sites. Sort candidate faults by their weights, reporting first the fault with the greatest weight.

The n-perfect Algorithm:

1) Find a 1-perfect fault candidate: n=1. Apply A\_single. Eliminate the explained patterns.

- 2) Inject each n-perect candidate into the circuit and perform steps 3 and 4 until all n-perfect candidates have been tried.

- 3) For each unexplained failing pattern, initialize the possible fault candidates.

- 4) Perform A\_single on the modified circuit and construct (n+1)-perfect candidates based on the targeted fault model.

- 5) Determine the (n+1)-perfect candidates that can further explain some failing patterns no yet explained by those (1 through n)-perfect candidates.

- 6) Rank and weight the (n+1)-perfect candidates based on failing and passing information. Eliminate those failing patterns that can be explained by (n+1)-perfect candidates from the failing pattern list. Increase n by 1.

- 7) Perform steps 2-6 for the remaining unexplained failing patterns until no fault candidate can be found, or until all failing patterns have been explained.

- 8) Post process all possible k-perfect candidates  $(1 \le k \le n)$  to eliminate the candidates that cause many passing patterns to fail when multiple-fault candidate are injected into the circuit. This is to eliminate wrong candidates assumed in the very beginning, which may imply other wrong candidates.

Not all n-perfect candidates that explain all failing patterns will be found. In the final step, the algorithm will find the minimum cardinality group of faults as the fault candidates that can explain the most failure responses.

Failing PO partition algorithm:

1) Back trace from each failing PO. If back tracing from POi finds a possible fault candidate, we mark it as reachable from POi.

- 2) For each failing pattern Pi, create failing PO connectivity graph, gPi. Each PO corresponds to a vertex in gPi. If two failing POs can reach the same fault there is an edge between them.

- 3) Collect gPi to form Gp. Gp has vertices corresponding to POs. There is an edge in Gp if there is an edge between these vertices in any of the gPi. Assign a weight to an edge in Gp equal to the number of corresponding gPi's that contain that contain that edge. If Gp is a disjoint graph, the heuristic stops. Perform the diagnosis separately on each sub graph without losing any failing-pattern information.

- 4) Partition Gp by removing low-weight edges.

- 5) Use each group of failing POs induced by the partition to filter out the original failure responses, and generate the new failure responses.

- 6) Diagnose each group of POs separately and obtain the fault candidates.

In worst case, this method has exponential time complexity.

### 2.4 <u>Defect Diagnosis Using Open Fault Model</u>

Circuit open is a common defect type occurring in manufacturing. When the interconnect is open, the driven node is floating. When a via is open, the driven poly or metal is floating too. If the interconnect drives multiple gate, since the downstream gates' input thresholds are different, the floating voltage will be interpreted as different logic values. This phenomenon is called Byzantine effect.

For example, in Figure 2, gate G1 drives three gates. If there exists an open fault on the stem interconnect to the three gates, the logic input value will be determined by the corresponding gate's input threshold. If the floating voltage is bigger than the threshold, will be interpreted as logic 1, otherwise logic 0.

Figure 2: Byzantine Effect

# 2.4.1 Super Fault or Composite Stuck-at OpenFault Diagnosis

Venkatarman and Drummonds [12] proposed a method to locate the interconnect open using composite stuck-at signature. The composite signature is the union of all the stuck-at faults at the stem and branch of the open net. One limitation is that multiple errors on branches are not simultaneously simulated. Some errors which cause propagation through multiple reconvergent paths may not be captured.

When matching the observed response, the super fault (composite) signature is compare with the observed failing response. If the suspect's composite signature is a super set of the observed failing response, this fault is kept. The limitation is, not many fault will be dropped which results in large candidate set size.

The matching algorithm looks for containment and weights intersection and non-prediction high, weights mis-prediction low.

Liu et al. [13] proposed an incremental multiple open-fault diagnosis based on X simulation. The first phase is to use critical path tracing to find a set of signal lines tuples that could explain the pattern using X simulation. Logic unknown 'X' is placed at the candidate sites and then logic simulated, the failed outputs should be covered by X for

each failing pattern. The critical path tracing is 3-valued, that can handle X in the path. A line already is X will not be marked as a candidate. The second phase is to simulate all the logic combinations of the signal lines in the tuple. If for a candidate tuple, any failing pattern has an explanation by some combination, the fault is kept in the candidate list. Otherwise, if there exist a failing pattern cannot be explained by all the logic combinations, the fault is dropped from the candidate list. Since there are 2^n-1 faulty combinations for a size n tuple, the simulation time could be impractical. The authors propose to place the unknown value X on a subset of the signal line in the tuple and perform the enumeration on other lines. But this does not solve the long simulation time problem.

# 2.4.2 Symbolic Simulation to Identify Open

#### **Defects**

Huang [14] proposed a procedure using symbolic simulation to identify interconnect open defects. The procedure first, for each failing pattern, injects a symbol at each branch on the suspect open net. Then perform the symbolic fault simulation and the symbols are propagated to outputs. Try to resolve the symbolic output expression to match the failing output. If no assignment could be found, the candidate is dropped. Ordered binary decision diagram (BDD) is used in storing symbolic simulations and symbolic expressions are also resolved by BDD.

Also a segment fault model is proposed. The interconnect routing can be represented as a binary tree. The edges of the segment-tree are the connections in the layout. The leaves on the tree are driven gates. For a binary tree with K leaves, there are 2k-1 edges. So for an open interconnection driving K gates, there are 2k-1 open suspects we need to target. For each open suspect, if the number of the gates it is driving is small, all the combinations of the logic values of inputs of the driven gates are simulated to see whether the open suspect can explain the failing pattern. If the number of the gates the

open suspect is driving is large, symbolic simulation is used to see whether the open suspect is real defect or not.

The limitation is some circuit does not have an efficient BDD representation that takes too much memory requirement to store them.

Wen et al, [15] uses a form of X simulation to identify the interconnect opens. Different X's (X1, X2, ...) are placed at the open branches and simulated. Instead of using symbolic simulation, they use a new X to represent the output of a gate if it is an expression of different Xs. When the X are all propagated to the outputs, the method tries to resolve the output by simulating all combinations of the logic values of the symbols injected at the branches to see whether there exists a combination which can explain the pattern.

Per-test in the title of [15] means that failing vectors are processed one at a time. The basic idea is that only one of the multiple defects in a circuit may be activated by on failing vector in some cases. Same as a SLAT vector. The authors use relaxed matching criterion, comparison is only conducted at primary outputs that are structurally reachable from a fault.

The shortcoming of symbolic simulation is to encode the different Xs, if we assume a net may have 10-32 branches, the simulation is not easily simulated in parallel. The long simulation time is a hinder to practical use.

# 2.4.3 Interconnect Open Diagnosis with Physical

#### Information

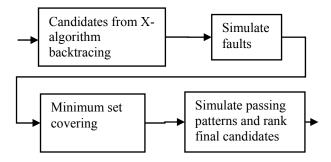

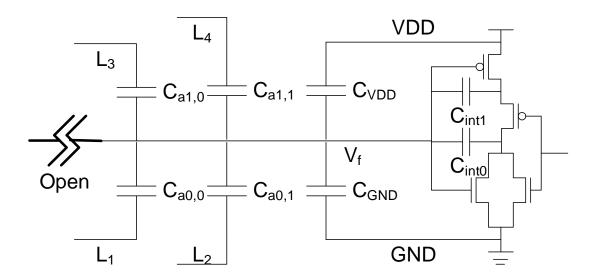

The model used in [16] [17] to determine the voltage on a floating node is illustrated in Figure 3, which shows an input node of a 2-input NOR gate completely open. Floating node voltage  $V_f$  satisfies the following equations:

$$V_f = \frac{C_1}{C_0 + C_1} V_{dd} + \frac{Q_{trap}}{C_{gnd}}$$

(1)

Figure 3: Interconnect Open Model

$$C_0 = C_{gnd} + C_{a0} + C_{\text{int 0}} \tag{2}$$

$$C_1 = C_{vdd} + C_{a1} + C_{int1} (3)$$

Where  $C_{a0}\left(C_{al}\right)$  is the sum of the capacitances between the floating node and its neighboring nodes which have low (high) voltage values.  $Q_{trap}$  is the initial trapped charge of the floating node.  $C_{vdd}$  and  $C_{gnd}$  are the capacitances between the floating node and power supply and ground rail. Because the voltages on the adjacent nodes depend on the test pattern P applied, we have  $C_{a0} = C_{a0}(P)$  and  $C_{a1} = C_{a1}(P)$ . That is these capacitances are pattern dependent.  $C_{int0}$  and  $C_{int1}$  are the internal capacitances inside the driven gate and these depend on voltage  $V_f$ .

To avoid calculating  $V_f$  explicitly, [16] defines a variable E and assumes that  $C_{a\theta}$  and  $C_{al}$  are dominant.

$$E = E(P) = \frac{C_1}{C_0 + C_1} = \frac{C_{a1}(P)}{C_{a0}(P) + C_{a1}(P)}$$

(4)

Since  $Q_{trap}$  /  $C_{gnd}$  is constant, variable E is sufficient to capture the change in  $V_f$  with varying patterns. Furthermore the test patterns that imply logic value 0 and 1 at the floating node of the circuit are divided into sets  $\Omega 0$  and  $\Omega 1$ , respectively.  $\Omega 0$  ( $\Omega 1$ ) is the set of test patterns under which the floating node voltage is less than (larger than) the threshold voltage of the driven gate. In [16] the threshold voltages of all driven gates are assumed to be identical. Next two ranges of values,  $E(\Omega 0)$  and  $E(\Omega 1)$ , defined below are introduced.

$$E(\Omega 0) = [\min E(P), \max E(P)] \quad \forall P \in \Omega 0$$

$$E(\Omega 1) = [\min E(P), \max E(P)] \quad \forall P \in \Omega 1$$

For a floating node due to an open defect the following should be true:

$$E(\Omega 0) < E(\Omega 1) \tag{5}$$

Equation (5) implies that the range of values in  $E(\Omega 0)$  must be below the range in  $E(\Omega 1)$ .

The method in [16] was enhanced in [17] by computing the threshold voltages of all library cells and using them in the diagnosis procedure. Each input of every gate type has a threshold. Additionally, the capacitances internal to the driven gates are considered in the form of trapped charge:

$$Q_{trap} = Q_{wire} (P, V_f) + Q_{gate} (V_f)$$

(6)

$$Q_{wire}(P, V_f) = V_f \bullet C_{a0}(P) + (V_f - V_{dd}) \bullet C_{a1}(P)$$

(7)

Where  $Q_{wire}(P, V_f)$  is the sum of the charge stored in the capacitors between the floating node and its neighboring nodes.  $Q_{gate}$  is the charge stored in the capacitors inside the gate driven by the suspect via. The remaining symbols are as defined earlier. The test patterns are also divided into two sets  $\Omega 0$  and  $\Omega 1$  as defined earlier. Let

$$Q(P,V) = Q_{wire}(P,V) + Q_{gate}(V)$$

For patterns in  $\Omega$ 0, let  $V_i$  be the smallest threshold voltage of the driven gates that has fault effect, then  $V_f < V_i$  and we have  $Q_{trap} < Q(P_i, V_i)$ . For patterns in  $\Omega$ 1, let  $V_j$  be the largest threshold voltage of the driven gates that has fault effect, then  $V_j < V_f$  and we have  $Q(P_j, V_j) < Q_{trap}$ . Then for a candidate open via, the following should be true:

$$\operatorname{Max}\left\{Q(P_{i}, V_{i})\right\} \quad < \quad \operatorname{Min}\left\{Q(P_{i}, V_{i})\right\}, \quad \forall P_{i} \in \Omega 0, \forall P_{j} \in \Omega 1$$

(8)

The method in [17] achieves better resolution than the method of [16] since it includes different threshold voltages for different library cells and also implicitly includes capacitances internal to driven gates. However as noted earlier, both methods require values of inter node coupling capacitances and use threshold voltage information, both of which may not be accurately known in the nanometer designs.

# CHAPTER 3. OPEN DEFECT DIAGNOSIS WITH MINIMAL PHYSICAL INFORMATION

We consider the problem of determining the location of open defects in interconnects of deep submicron (DSM) designs. The target defect sites for this work are the vias in interconnects which are known to be defect prone. It is known that in DSM designs below 90 nm technology the circuit parameters may vary widely from nominal or design values and process variations make them less predictable. Thus it becomes necessary to develop methods for locating defect sites without accurate knowledge of circuit parameters. Logic diagnosis which is based on gate level net lists is one such method but the resolution of defect sites obtained by logic diagnosis is considered to be unacceptably low for locating open vias. We investigate a procedure that uses minimal information beyond the net lists and give experimental results to demonstrate the defect resolution obtained using the method. The additional information used by the proposed method is a list of nodes in the neighborhoods of circuit nodes and the circuit layout. Specifically, difficult to determine circuit parameters of manufactured instances of a design such as coupling capacitances between circuit nodes and threshold voltages of gates in the circuit are not needed to use the proposed diagnosis procedure.

#### 3.1 Introduction

In deep sub-micron (DSM) designs open is a common defect type. Opens most frequently occur in contacts and vias. Open can be of finite resistance or infinite resistance (complete opens). In this work we consider complete opens in vias in circuit interconnects.

When a complete open occurs some circuit node is disconnected from the gate driving it and the disconnected node is said to be floating. The open node is part of a circuit net which typically contains many sections of interconnect and vias. Given a circuit net with an open, the location of the open can be determined from attenuation and

phase shift measurements during physical failure analysis [18]. Fault diagnosis procedures are first used to determine a list of candidate sites for physical failure analysis. Depending on the fault diagnosis procedure used, the candidate sites could be circuit nets or segments or vias. Methods that determine open segments narrow the sites for failure analysis more than the methods that locate the opens to within circuit nets. Similarly methods that resolve the opens to vias in circuit nets provide much shorter interconnect sections for investigation during failure analysis. The work reported in this paper considers locating interconnect opens to locations of vias in circuit nets.

The voltage on a floating node depends on several things including the state of the neighboring nodes and coupling capacitances between the floating node and its neighbors, the capacitances to power supply lines and substrate, initial trapped charge, leakage currents and the internal capacitances of the gates driven by the floating node [19] - 21]. Additionally, depending on their threshold voltages, the voltage on the floating node may be interpreted differently by different gates driven by the open node. This is referred to as Byzantine effect [22]. Several methods have been proposed to diagnose interconnect open defects [8], [12], [15], [16], [17], [23 – 28]. The methods in [8], [12], [15], [23 – 26], [28] use gate level net lists only and do not use layout or cell library information. Such diagnosis procedures are referred to as logic diagnosis procedures in this work. The logic diagnosis methods include diagnosis based on the net fault model [12, 23], symbolic simulations [15, 24], incremental heuristic using X simulations [25, 28] and location based diagnosis [8, 26, 29]. These logic diagnosis methods typically report a candidate list that contains suspect circuit nets. Circuit nets may have many sections of interconnects that span multiple metal layers and have many vias. Tracing a suspect net during physical failure analysis to find the defect site could be a long and expensive task.

To reduce the time and cost of physical failure analysis, Huang [27] proposed segment fault model. A segment is a unique subset of gates driven by a gate through an

interconnect net. Segment fault model requires the layout of the circuit in addition to the gate level net list to determine the gates in a segment. Symbolic simulation is proposed to locate suspect segments of nets that are likely to contain the open via [27]. Thus the method of [27] reports suspect segments instead of suspect nets as done by logic diagnosis procedures. Hence diagnosis based on segments identifies smaller sections of interconnects in circuit nets for physical failure analysis. Sato et al. [16] proposed to identify open vias instead of open segments by using a physical interconnect open model. This method uses the values of capacitances between the floating node and its neighboring nodes and also considers the initial trapped charge on the floating node. However the capacitances between internal nodes of the driven gates are not included in the model. Additionally the threshold voltages of all gates driven by the floating node are considered to be identical. In [17], Zou et al. investigated a procedure which takes into account the capacitances between the floating node and its neighboring nodes, the initial trapped charge, the internal capacitances of the driven gates and differing gate input threshold voltages of the driven gates. The threshold voltages of library cells were determined in a preprocessing step. This method is more accurate since essentially all the circuit parameters that determine the behavior of the floating node are included. Since the methods of [16] and [17] determine open vias the diagnosis resolution provided by them is finer than that provided by [27] using segment fault model. However the methods of [16] and [17] need accurate extraction of capacitances between circuit nodes which may not be feasible in nanometer designs. Also the threshold voltages of different instantiations of the same library cell in a design may vary considerably and hence threshold voltages that are determined a priori may not accurately reflect the actual values in a manufactured design. For nanometer devices which may have large process variations and whose circuit parameters may deviate considerably from nominal values, diagnosis procedures that do not use extracted capacitance values and parameters of library cells may be needed.

In this work, we investigate a diagnosis method with the goal to determine open vias. It uses knowledge of neighbors of a circuit node and the circuit layout only. The information regarding the neighboring nodes can be obtained through proximity analysis and hence can be regarded as a minimal requirement. Layout information is needed for any method whose goal is determination of the location of open vias. Specifically, in the proposed method the coupling capacitances between circuit nodes and parameters of library cells, such as threshold voltages and internal capacitances are regarded as unknowns. Hence, the method does not require extraction of coupling capacitances and knowledge of inter node capacitances and threshold voltages of library cells in the devices which failed manufacturing test.

The rest of the section is organized as follows. In Section 3.2 we briefly review the previous related work and give an overview of the proposed procedure. In Section 3.3 we describe the proposed procedure. In Section 3.4 we present experimental results. In Section 3.5 we have some discussions. Section 3.6 concludes the work.

## 3.2 Preliminaries

In this section we first give a brief review of previous works related to the proposed method followed by an overview of the proposed diagnosis procedure to identify open vias in interconnects.

#### 3.2.1 Review of Previous Works

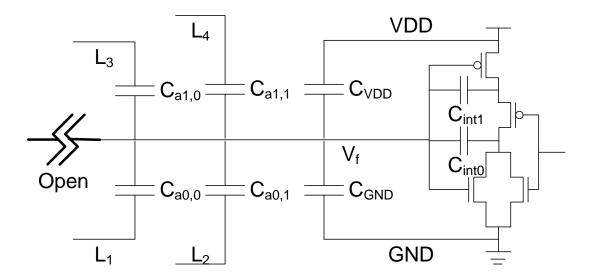

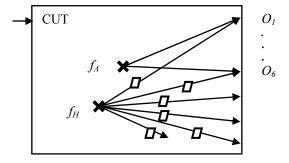

If a net in the gate level netlist drives multiple gates, the routing of the net in the layout can be divided into several segments that drive different subsets of gates [27].

In Figure 4(a) we show a net driven by gate G1 driving gates G2, G3 and G4. The net can be considered to contain five segments [27] as shown in Figure 4(b). Each segment contains a part of the net that drives different subsets of gates. The five segments S1, S2, S3, S4 and S5 in Figure 4(b) drive subsets of gates {G2, G3, G4}, {G3}, G4}, {G3} and {G4}, respectively.

Figure 4: A Net's Routing in the Layout

In Figure 4(b) the smaller squares represent vias. From the layout we can determine that segments S1, S2, S3, S4 and S5 contain subsets of vias {1}, {2}, {3, 4}, {5} and {6, 7}, respectively. The method by Huang [27] locates open vias up to segments. For example if segment S3 is identified as containing the open via then the actual open via could be via 3 or via 4. The methods of [16] and [17] attempt to obtain better resolution using extracted capacitances coupled to the open net. For example in the previous case these methods may determine which of the vias 3 or 4 is open. This is possible because the capacitances coupled to the open node and the neighbors may be different when via 3 is open compared to when via 4 is open. The neighbors are the nodes that are in the neighborhood of the sections of interconnect downstream of the open. Because of the distance between vias 3 and 4, their neighbors are quite likely to be different. Similarly, in segment S5 it may be possible to locate the open via to 6 or 7. The goal of our work is also to locate the open vias in segments similar to that of [16] and [17] but without requiring the knowledge of circuit parameters whose values may not be determinable precisely.

Figure 5: Interconnect Open Model

The model used in [16, 17] to determine the voltage on a floating node is illustrated in Figure 5, which shows an input node of a 2-input NOR gate open. The voltage  $V_f$  on the floating node satisfies the following equations:

$$V_{f} = \frac{C_{1}}{C_{0} + C_{1}} V_{dd} + \frac{Q_{trap}}{C_{gnd}}$$

$$C_{0} = C_{gnd} + C_{a0} + C_{int 0}$$

$$C_{1} = C_{vdd} + C_{a1} + C_{int 1}$$

In the equations above,  $C_{a0}$  and  $C_{a1}$  are the sums of the capacitances between the floating node and its neighboring nodes which have logic 0 and logic 1 values, respectively.  $Q_{trap}$  is the initial trapped charge of the floating node.  $C_{vdd}$  and  $C_{gnd}$  are the capacitances between the floating node and power supply and ground rail. Because the voltages on the adjacent nodes depend on the test pattern P applied, we have  $C_{a0} = C_{a0}(P)$

and  $C_{al}=C_{al}(P)$ . That is, these capacitances are pattern dependent.  $C_{int0}$  and  $C_{int1}$  are the capacitances internal to the driven gate whose actual values depend on voltage  $V_f[9]$ .

To avoid calculating  $V_f$  explicitly, [16] defines a variable E and also assumes that  $C_{a0}$  and  $C_{a1}$  are dominant.

$$E = E(P) = \frac{C_1}{C_0 + C_1} = \frac{C_{a1}(P)}{C_{a0}(P) + C_{a1}(P)}$$

Since  $Q_{trap}$  /  $C_{gnd}$  is constant, variable E is sufficient to capture the change in  $V_f$  with varying patterns. Furthermore the test patterns that imply logic value 0 and 1 at the floating node of the circuit are divided into sets  $\Omega 0$  and  $\Omega 1$ , respectively.  $\Omega 0$  ( $\Omega 1$ ) is the set of test patterns under which the floating node voltage is less than (larger than) the threshold voltage of the driven gate. In [16] the threshold voltages of all driven gates are assumed to be identical. Next two ranges of values,  $E(\Omega 0)$  and  $E(\Omega 1)$ , defined below are introduced.

$$E(\Omega 0) = [\min E(P), \max E(P)] \forall P \in \Omega 0$$

$$E(\Omega 1) = [\min E(P), \max E(P)] \forall P \in \Omega 1$$

For a floating node due to an open defect the following must be true:

$$E(\Omega 0) < E(\Omega 1) \tag{9}$$

The meaning of equation (9) is that the range of values in  $E(\Omega 0)$  must be below the range of values in  $E(\Omega 1)$ .

The method in [16] was enhanced in [17] by computing the threshold voltages of all library cells and using them in the diagnosis procedure. Each input of every gate type has a threshold. Additionally, the capacitances internal to the driven gates are considered in the form of trapped charge:

$$Q_{trap} = Q_{wire}(P, V_f) + Q_{gate}(V_f)$$

(10)

$$Q_{wire}(P, V_f) = V_f \bullet C_{a0}(P) + (V_f - V_{dd}) \bullet C_{a1}(P)$$

(11)

In equations (10) and (11),  $Q_{wire}(P, V_f)$  is the sum of the charge stored in the capacitors between the floating node and its neighboring nodes.  $Q_{gate}$  is the charge stored in the capacitors inside the gate driven by the suspect via. The remaining variables are as defined earlier. The test patterns are also divided into two sets  $\Omega 0$  and  $\Omega 1$  as defined earlier. Let

$$Q(P, V_f) = Q_{wire}(P, V) + Q_{gate}(V)$$

For patterns in  $\Omega$ 0, let  $V_i$  be the smallest threshold voltage of the driven gates that has fault effect, then  $V_f < V_i$  and we have  $Q_{trap} < Q(P_i, V_i)$ . For patterns in  $\Omega$ 1, let  $V_j$  be the largest threshold voltage of the driven gates that has fault effect, then  $V_j < V_f$  and we have  $Q(P_j, V_j) < Q_{trap}$ . Then for a candidate open via, the following should be true:

$$\operatorname{Max}\left\{Q(P_{j}, V_{j})\right\} \leq \operatorname{Min}\left\{Q(P_{i}, V_{i})\right\}, \ \forall P_{i} \in \Omega 0, \forall P_{i} \in \Omega 1$$

$$\tag{12}$$

The method in [17] can achieve better resolution since it includes different threshold voltages for different library cells and also implicitly includes capacitances internal to driven gates. However as noted earlier, both methods require values of internode coupling capacitances and use threshold voltage information, both of which may not be accurately known for nanometer designs.

### 3.2.2 Overview of the Proposed Diagnosis Procedure

The proposed diagnosis procedure first identifies a set of candidate segments that are open using segment fault model [27] and determines the vias in the suspect segments. Next, the vias in the suspect segments are analyzed to determine the suspect vias. Interconnect open model discussed in the section above is used during this step. However, the actual values of various capacitances and gate threshold voltages are assumed to be unknown. Using variables to represent these unknown quantities, for each via in a suspect segment certain sets of inequalities are set up. The inequalities which have solution identify the vias which are suspected to be open by the proposed method.

As in earlier works [16] and [17] we assume that the defect in chip being diagnosed has a single open via.

# 3.3 <u>Identifying Open Defects with Only Neighborhood Node List</u> Information

In this section we describe the proposed diagnosis procedure. The procedure uses three steps. In the first step candidate open nets are identified using logic diagnosis. In the second step, the candidate open segments are identified using segment fault model. In the third step suspect open vias are determined. These steps are described next.

# 3.3.1 Identifying the Open Nets Using Logic Diagnosis

In the first step the logic diagnosis procedure of [29] is used to derive a list of candidate nets. We use only SLAT [8] (single location at a time) failing patterns in this step. SLAT patterns are those patterns that can be explained by a single fault site [8]. That is, the circuit outputs produced by the failing chip when the pattern is applied are matched by a single fault injected at a fault site. When all the single fault sites that can explain some failing SLAT pattern(s) are determined a set of candidate circuit nodes are obtained. At this point, typical logic diagnosis procedures [8, 26, 30, 31] determine minimal sized subsets of the set of candidate sites that can explain all the failing SLAT patterns. Each such subset corresponds to potential candidate sites for defects. Each candidate subset is then analyzed based on fault models used. Since all the branches of a fanout stem are the same net in the layout, in [29], if one or more branches of a fanout stem are included in the set of candidate fault sites, all branches are replaced by their parent fanout stem followed by determining a minimum set cover to find the subsets of candidates with minimal size which can explain all the failing patterns. Thus, at the end of logic diagnosis suspect nets are determined.

# 3.3.2 Identifying the Open Segments Using Segment Fault Model

Next a segment fault model described in [27] is used to find the open segments and only the vias on the open segment will be analyzed by the physical open model in the next step described in Section 3.3.3. If a segment drives multiple gates, it may cause failures on one or more driven gates. We simulate all the possible combinations for the faults. Each driven input can have faulty or not faulty values. So for a segment including N gates, (2^N - 1) multiple faults are simulated. A segment is added to the list of suspect segments if any one of these faults explains the failing pattern. Otherwise the segment is dropped from the candidate list. Since some gates are included in several segments we simulate faults of increasing multiplicity (i.e. faults with multiple fault sites) as well as use the results of fault simulation used in logic diagnosis of Step 1 discussed in the last section. We also take advantage of the earlier proposed methods to fault simulate multiple faults associated with stems of large fan outs described in [32]. These steps aid in improving the efficiency of the procedure to simulate multiple faults at gates in a segment.

# 3.3.3 Identifying Open Vias by Solving Inequalities

Diagnosis procedures for interconnect opens use the information regarding a fault at a gate input explaining or not explaining the observed response from a tested device. In determining the expected behavior of the device under test, when a candidate open defect is considered, one needs to know the threshold voltage of the gate inputs driven by the floating node. For primitive gates such as NAND, NOR etc. for each gate input only one threshold voltage is needed, since inputs to such gates can be sensitized only if all other inputs to these gates are at non-controlling value. In non-primitive gates a gate input may be fanned out to more than one pair of NFET and PFET. For such gates one will have to use more than one threshold voltage for a gate input. In general if a non-primitive gate

has n inputs then for each gate input one may have to use 2^(n-1) threshold voltage values. Multiple threshold voltages at a non-primitive gate input are also needed for the procedure in [17].