## Washington University in St. Louis Washington University Open Scholarship

All Theses and Dissertations (ETDs)

1-1-2011

# Low-Impact Profiling of Streaming, Heterogeneous Applications

Joseph Lancaster

Washington University in St. Louis

Follow this and additional works at: http://openscholarship.wustl.edu/etd

#### Recommended Citation

Lancaster, Joseph, "Low-Impact Profiling of Streaming, Heterogeneous Applications" (2011). *All Theses and Dissertations* (ETDs). 603. http://openscholarship.wustl.edu/etd/603

This Dissertation is brought to you for free and open access by Washington University Open Scholarship. It has been accepted for inclusion in All Theses and Dissertations (ETDs) by an authorized administrator of Washington University Open Scholarship. For more information, please contact digital@wumail.wustl.edu.

#### WASHINGTON UNIVERSITY IN ST. LOUIS

School of Engineering and Applied Science

Department of Computer Science and Engineering

Dissertation Examination Committee:

Roger Chamberlain, chair

Jeremy Buhler

Patrick Crowley

Ron Cytron

Chris Gill

Ron Indeck

Henric Krawczynski

## $\label{low-impact} \mbox{LOW-IMPACT PROFILING OF STREAMING}, \\ \mbox{HETEROGENEOUS APPLICATIONS}$

by

Joseph Marion Lancaster

A dissertation presented to the Graduate School of Arts and Sciences of Washington University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> August 2011 Saint Louis, Missouri

copyright by  $\label{eq:copyright} \mbox{Joseph Marion Lancaster}$  2011

#### ABSTRACT OF THE THESIS

Low-Impact Profiling of Streaming, Heterogeneous Applications

by

Joseph Marion Lancaster

Doctor of Philosophy in Computer Engineering

Washington University in St. Louis, 2011

Research Advisor: Roger D. Chamberlain

Computer engineers are continually faced with the task of translating improvements in fabrication process technology (i.e., Moore's Law) into architectures that allow computer scientists to accelerate application performance. As feature-size continues to shrink, architects of commodity processors are designing increasingly more cores on a chip. While additional cores can operate independently with some tasks (e.g. the OS and user tasks), many applications see little to no improvement from adding more processor cores alone.

For many applications, heterogeneous systems offer a path toward higher performance. Significant performance and power gains have been realized by combining specialized processors (e.g., Field-Programmable Gate Arrays, Graphics Processing Units) with general purpose multi-core processors. Heterogeneous applications need to be programmed differently than traditional software. One approach, stream processing, fits these systems particularly well because of the segmented memories and explicit expression of parallelism. Unfortunately, debugging and performance tools that support streaming, heterogeneous applications do not exist.

ii

This dissertation presents *TimeTrial*, a performance measurement system that enables performance optimization of streaming applications by profiling the application deployed on a heterogeneous system. TimeTrial performs low-impact measurements by dedicating computing resources to monitoring and by aggressively compressing performance traces into statistical summaries guided by user specification of the performance queries of interest.

## Acknowledgments

I would like to extend my deep appreciation to my adviser, Dr. Roger Chamblerlain for his guidance throughout my graduate career. Without his encouragement I doubt I would have pursued a doctoral degree. The many hours of discussions regarding research directions, feedback on manuscripts, and career advice truly helped contribute to my successfully completing this doctoral degree.

I would like to thank Dr. Jeremy Buhler for acting as a secondary adviser, always keeping the engineer in me in check with a healthy dose of theoretical approaches. Dr. Buhler helped me to expand my research skills and dive into problems that I might have been reluctant to otherwise explore. His patience and support throughout my graduate career will always be appreciated.

I am extremely grateful for financial support provided by NIH award R42 HG003225 and NSF award CNS-0931693. This support allowed me to concentrate exclusively on my research.

I would like to thank the members of my dissertation committee for their insightful questions that helped improve and focus my research.

I would like to thank all of my graduate colleagues, especially the members of the High Performance Computational Biology group. It has been a pleasure to learn and grow with all of you. I want to mention one colleague in particular, Arpith Jacob, with whom I worked closely with for my entire graduate career. It has been quite the journey.

Finally, I want to thank the eternal patience of my wife, Sarah Katherine Lancaster, who supported me through the most challenging times as a graduate student.

Joseph Marion Lancaster

Washington University in Saint Louis August 2011

To my lovely wife, Sarah Katherine Lancaster.

## Contents

| $\mathbf{A}$  | bstra                  | nct                                                  | ii   |

|---------------|------------------------|------------------------------------------------------|------|

| A             | ckno                   | wledgments                                           | iv   |

| $\mathbf{Li}$ | st of                  | Tables                                               | viii |

| Li            | $\operatorname{st}$ of | Figures                                              | ix   |

| 1             | Intr                   | ${f roduction}$                                      | 1    |

|               | 1.1                    | Utility of Heterogeneous Computing Systems           | 2    |

|               | 1.2                    | Programming Heterogeneous Computing Systems          | 3    |

|               | 1.3                    | Difficulties in Profiling Heterogeneous Applications | 6    |

|               | 1.4                    | Research Questions                                   | 7    |

|               | 1.5                    | Summary of our Approach                              | 8    |

|               | 1.6                    | Contributions                                        | 9    |

|               | 1.7                    | Outline                                              | 10   |

| 2             | Bac                    | kground and Related Work                             | 12   |

|               | 2.1                    | Profiling Application Performance                    | 12   |

|               | 2.2                    | Stream Processing                                    | 14   |

|               | 2.3                    | The X Coordination Language                          | 15   |

|               | 2.4                    | Heterogeneous Computing Systems                      | 19   |

|               |                        | 2.4.1 Traditional Architectures                      | 20   |

|               |                        | 2.4.2 Specialized Computing Architectures            | 22   |

|               |                        | 2.4.3 The Viability of Heterogeneous Systems         | 23   |

|               | 2.5                    | Related Work                                         | 24   |

|               |                        | 2.5.1 Performance Profiling and Monitoring           | 24   |

|               |                        | 2.5.2 Trace Compression                              | 29   |

|               |                        | 2.5.3 Performance Debugging Languages                | 29   |

| 3             | Pro                    | filing the Performance of Streaming Applications     | 31   |

|               | 3.1                    | Profiling a Streaming Application                    | 31   |

|               | 3.2                    | Online Aggregation of Performance Events             | 32   |

|               | 3.3                    | Framing: Measuring Performance Through Time          | 33   |

|               | 3.4                    | The TimeTrial Performance Query Language             | 35   |

|               |                        | 3.4.1 Formal Language Definition                     | 40   |

|               |                        | 3.4.2 Examples of Use                                | 42   |

|               | 2.5                    | Chapter Summery                                      | 42   |

| 4 | $\mathbf{Arc}$ | hitecture and Implementation of TimeTrial         | 44  |

|---|----------------|---------------------------------------------------|-----|

|   | 4.1            | Overview                                          | 44  |

|   | 4.2            | TimeTrial Compiler                                | 47  |

|   | 4.3            | Architecture of the FPGA Agent                    | 48  |

|   | 4.4            | Architecture of the Software Agent                | 50  |

|   | 4.5            | Implementing the TimeTrial Language               | 52  |

|   | 4.6            | Cross-platform issues: Timezones and Virtual Time | 54  |

|   | 4.7            | TimeTrial Performance: Overhead and Impact        | 56  |

|   |                | 4.7.1 Performance of the FPGA Agent               | 57  |

|   |                | 4.7.2 Performance of the Software Agent           | 58  |

|   | 4.8            | Chapter Summary                                   | 59  |

| 5 | Moi            | nitoring Virtual Queues                           | 61  |

| • | 5.1            | Approach to Virtual Queue Occupancy               | 62  |

|   | 5.2            | Assessment of Modeling Technique                  | 65  |

|   | 5.3            | Modeling Virtual Queue Occupancy                  | 69  |

|   | 5.4            | Chapter Summary                                   | 74  |

| 6 | Mea            | asuring Performance with TimeTrial                | 75  |

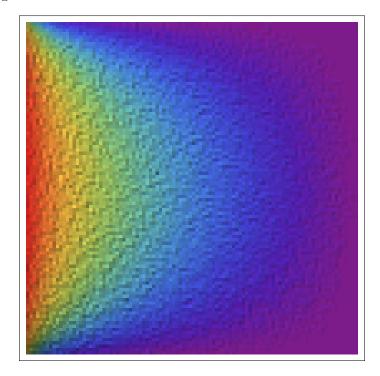

| Ū | 6.1            | Monte Carlo Solution to Laplace's Equation        | 75  |

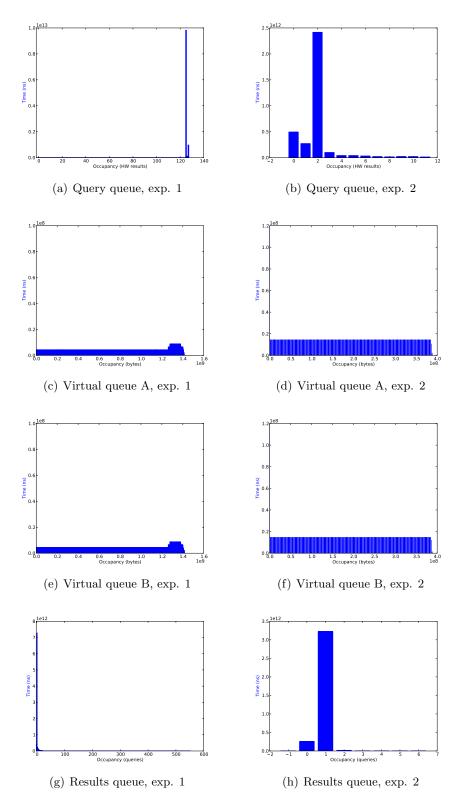

|   | 0.1            | 6.1.1 Virtual Queues                              | 84  |

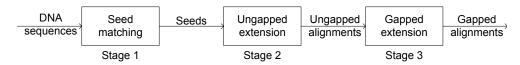

|   | 6.2            | Biosequence Search using BLASTN                   | 86  |

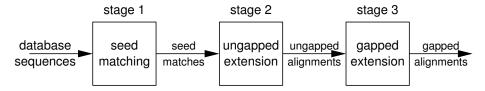

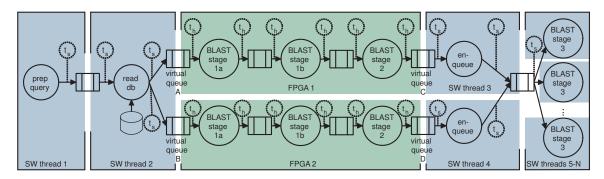

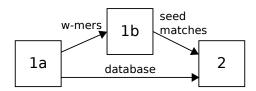

|   |                | 6.2.1 The BLASTN Application                      | 87  |

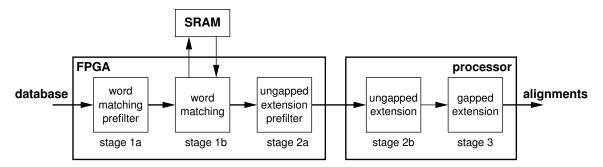

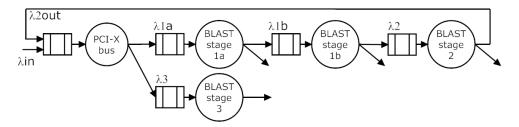

|   |                | 6.2.2 Mercury BLASTN                              | 88  |

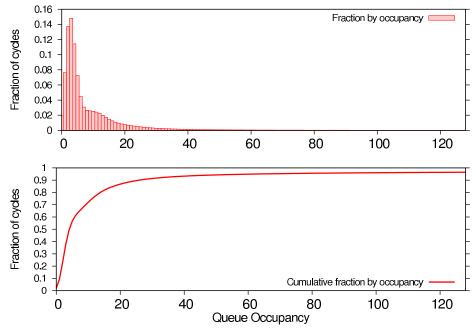

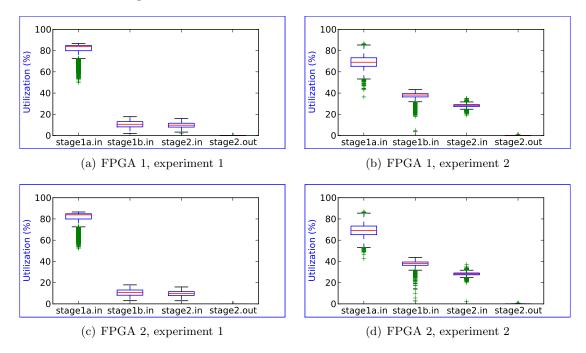

|   |                | 6.2.3 Provisioning FPGA Queue Sizes               | 89  |

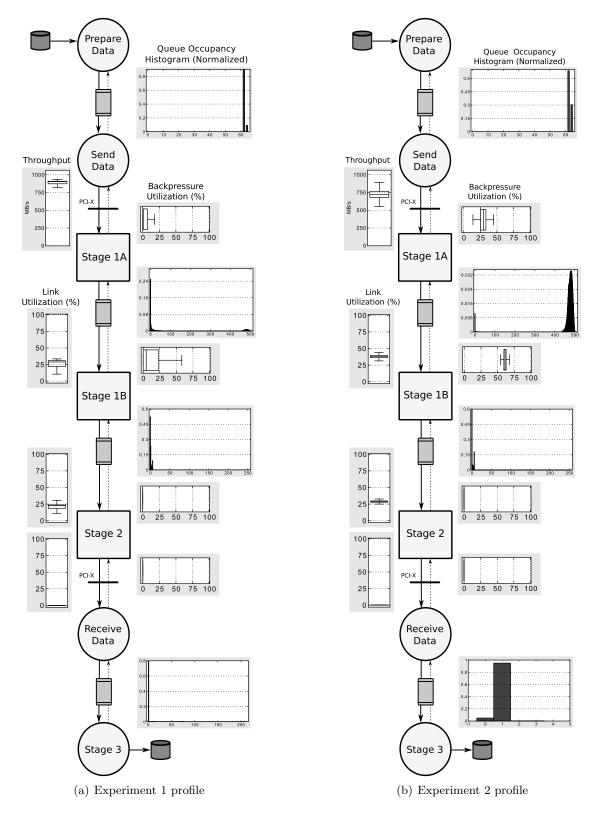

|   |                | 6.2.4 Profiling Mercury BLASTN                    | 91  |

|   |                |                                                   | 102 |

|   |                |                                                   | 104 |

|   | 6.3            | · · · · · · · · · · · · · · · · · · ·             | 105 |

| 7 | Cali           | ibrating and Validating Performance Models        | 107 |

|   | 7.1            |                                                   | 107 |

|   | 7.2            | G 11                                              | 109 |

|   | 7.3            |                                                   | 110 |

|   | 7.4            | ·                                                 | 111 |

|   | 7.5            |                                                   | 113 |

| 8 | Con            | aclusions and Future Research                     | 115 |

|   | 8.1            |                                                   | 117 |

| ъ | c              |                                                   |     |

## List of Tables

| 4.1 | Compatibility between statistic types and measurement types in a TimeTrial |     |

|-----|----------------------------------------------------------------------------|-----|

|     | language statement                                                         | 54  |

| 4.2 | Maximum achievable clock frequencies (rounded to the nearest integer) for  |     |

|     | three configurations of the performance monitor. The results are shown for |     |

|     | a Xilinx Virtex 4 LX100 speed grade 12 FPGA                                | 57  |

| 4.3 | Performance monitor resource overhead for the same three configurations in |     |

|     | Table 4.2. Numbers in parenthesis below the resource type show the total   |     |

|     | number of each resource available on the LX100 FPGA                        | 58  |

| 6.1 | Performance impact of instrumenting Mercury BLASTN with TimeTrial          | 101 |

| 6.2 | FPGA agent resource utilization                                            | 101 |

| 6.3 | Measured dummy message counts from stage 1a for Mercury BLASTN. $$         | 104 |

| 7.1 | Input parameters to queuing model                                          | 112 |

| 7.2 | Model predictions vs. empirical measurements.                              |     |

## List of Figures

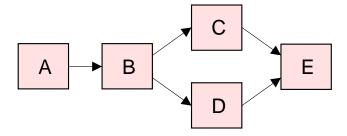

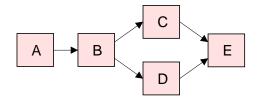

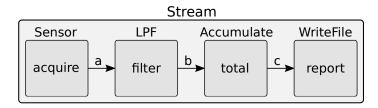

| 1.1<br>1.2 | Example of a heterogeneous computing system                                                                                                                                                                                                                                                                                              |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

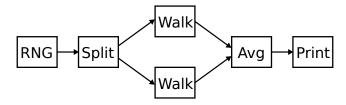

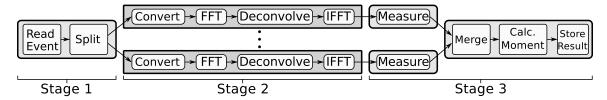

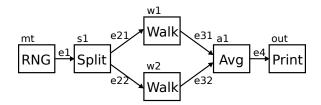

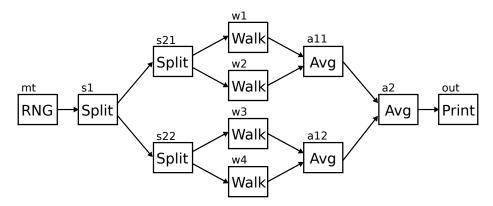

| 1.3        | An example streaming implementation of a Monte Carlo solution to Laplace's equation. Computation is performed within each block, communication is one-way along edges                                                                                                                                                                    |

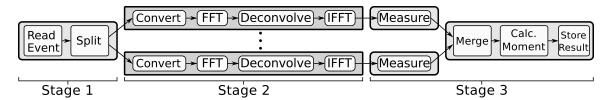

| 1.4        | An example streaming application from computational astrophysics [110]. Computation is performed within each kernel, communication is one-way along edges                                                                                                                                                                                |

| 2.1        | Sample application dataflow graph                                                                                                                                                                                                                                                                                                        |

| 2.2<br>2.3 | Example DSP streaming application                                                                                                                                                                                                                                                                                                        |

| 2.4        | Data traces collected with X-Sim[42]                                                                                                                                                                                                                                                                                                     |

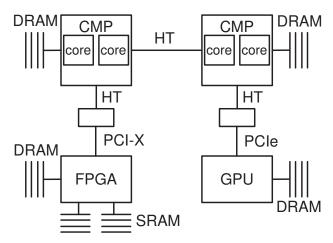

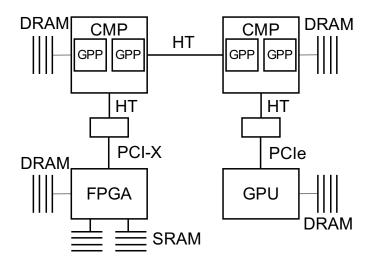

| 2.5        | Example heterogeneous system that reflects the type we utilize in this dissertation. Two chip multiprocessors (CMP) are interconnected with a Hyper-Transport (HT) link. Additional HT links are used to connect to an FPGA                                                                                                              |

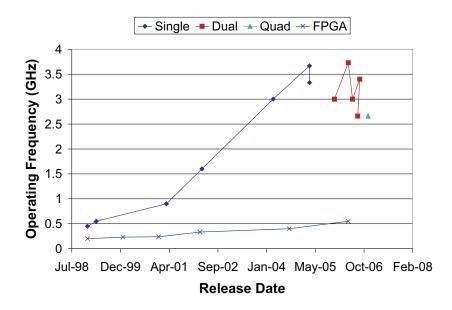

| 2.6        | through a PCI-X bus and a graphics processing unit (GPU) via a PCIe bus. Operating frequencies of Intel Xeon processors and Xilinx Virtex series FP-GAs over time. FPGA performance is for a 16-bit addition on the Virtex through Virtex-5                                                                                              |

| 3.1        | An example streaming application from computational astrophysics [110]. Computation is performed within each kernel, communication is one-way                                                                                                                                                                                            |

| 3.2        | along edges                                                                                                                                                                                                                                                                                                                              |

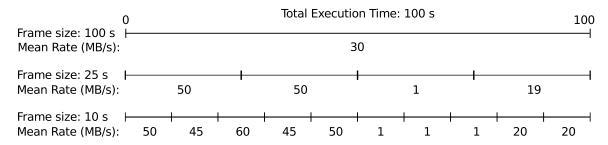

| 0.2        | one aggregated metric                                                                                                                                                                                                                                                                                                                    |

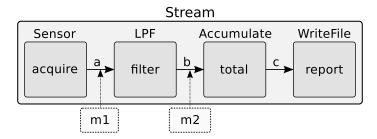

| 3.3        | Stream application instrumented with measurements m1 and m2. Dotted lines                                                                                                                                                                                                                                                                |

| 3.4        | and blocks represent the performance monitoring instrumentation                                                                                                                                                                                                                                                                          |

|            | grammar either come from the target streaming language (e.g., <b>PortLabel</b> and <b>EdgeLabel</b> are identifiers of ports and edges, respectively) or follow common usage (e.g., <b>Number</b> , <b>Identifier</b> and <b>ParamList</b> ). While not explicitly included above, parentheses are also supported in Boolean expressions |

|            | for the purpose of describing operator precedence                                                                                                                                                                                                                                                                                        |

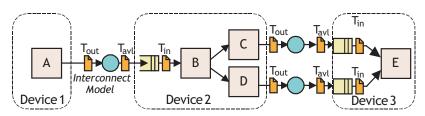

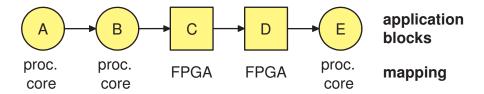

| 4.1        | Example application topology ( $A \rightarrow B \rightarrow C \rightarrow D \rightarrow E$ ) and its mapping to processor cores and FPGA                                                                                                                                                                                                 |

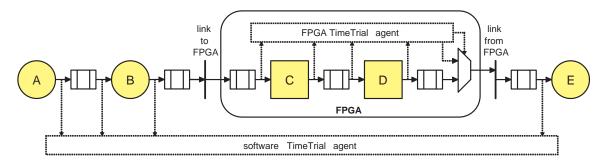

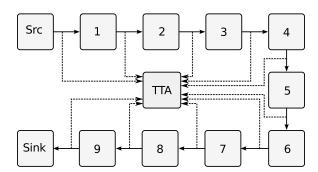

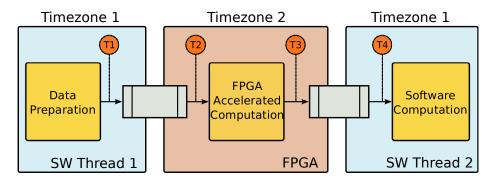

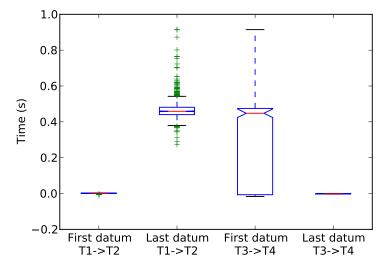

| 4.2  | Example application from Figure 4.1 deployed on an heterogeneous platform comprised of processor cores and an FPGA. The dotted lines and boxes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | illustrate the runtime instrumentation of the application via Time<br>Trial. $$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47  |

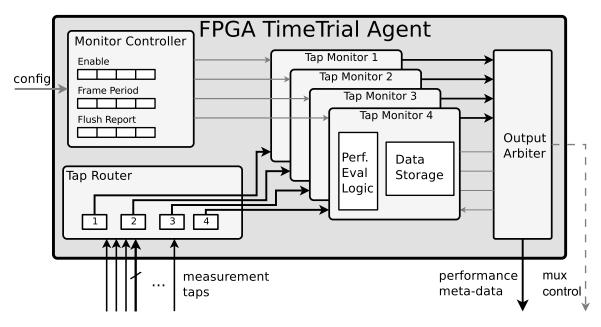

| 4.3  | Detailed view of the TimeTrial agent for the FPGA shown with for tap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|      | monitors. The FPGA agent is a high-speed, parametrized circuit designed to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|      | aggregate measurements on the FPGA. Data paths are shown as dark lines,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|      | control paths are grey lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 49  |

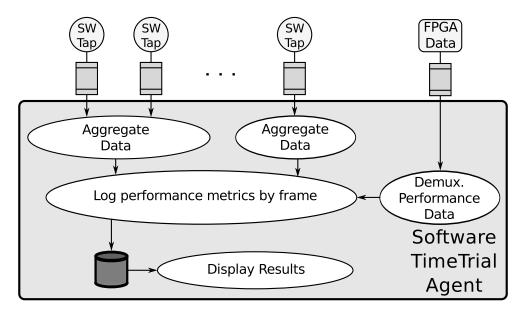

| 4.4  | Overview of the software TimeTrial agent. In addition to aggregating event                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|      | streams online, the software agent is responsible for logging results from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

|      | FPGA agents to disk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51  |

| 4.5  | Software agent micro-benchmark application. The source generates data and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|      | each block consumes and forwards the data as fast as it is able. Each block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | has its affinity set to a unique processor core                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 58  |

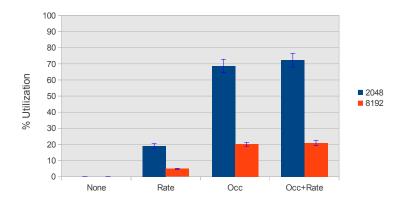

| 4.6  | Overhead of the measurements for the software agent measured by utiliza-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|      | tion of one processor core for two array transfer sizes. Error bars show one                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _,  |

| 4 7  | standard deviation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59  |

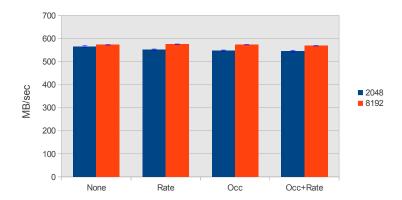

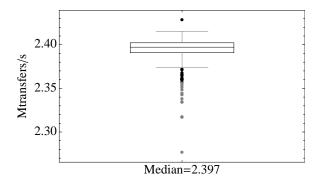

| 4.7  | Impact on the throughput of the micro-benchmark by the software agent.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.0 |

|      | Error bars show one standard deviation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60  |

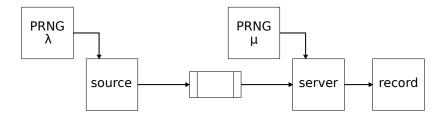

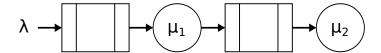

| 5.1  | Single-stage queueing station                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65  |

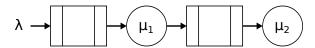

| 5.2  | Micro-benchmark application that mimics queue activity of the single-stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| ·    | queueing station                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66  |

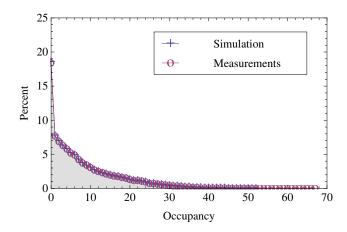

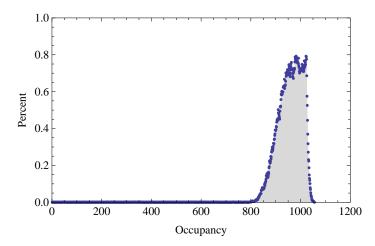

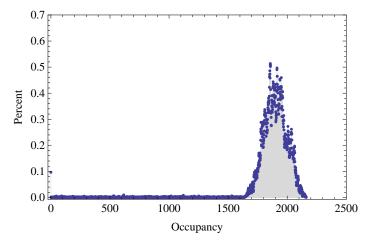

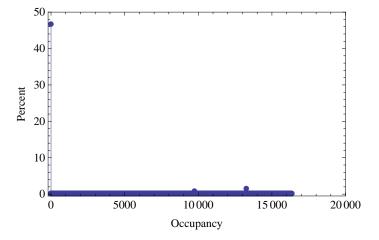

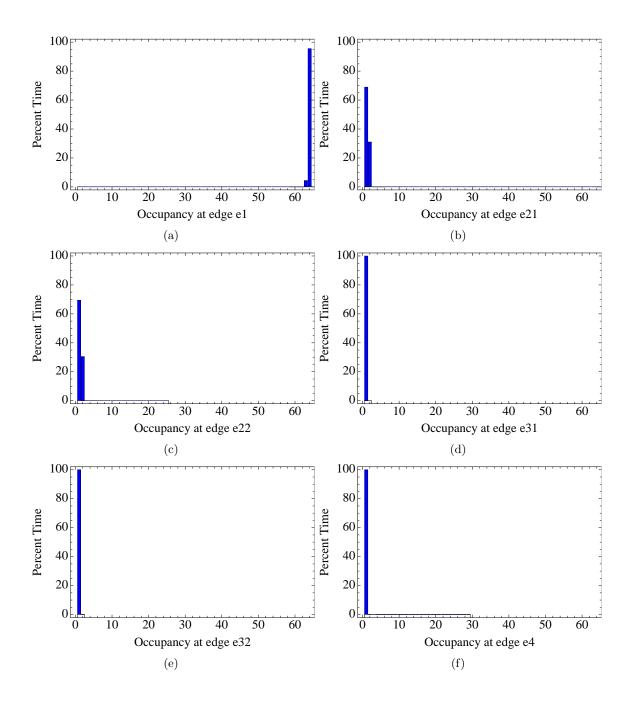

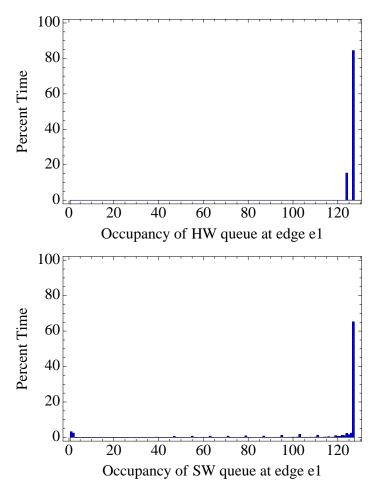

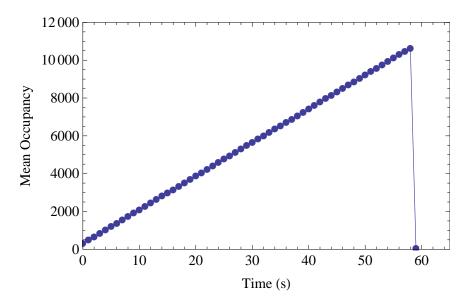

| 5.3  | Queue occupancy in $M/M/1$ micro-benchmark deployed in software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67  |

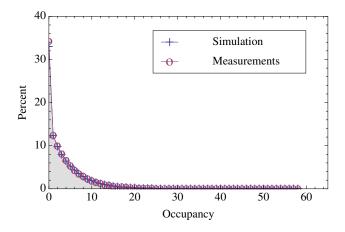

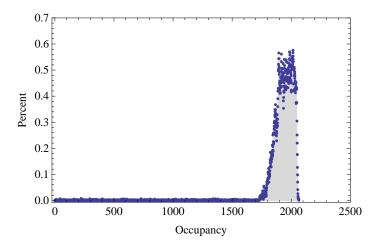

| 5.4  | Queue occupancy in $M/M/1$ micro-benchmark deployed in hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67  |

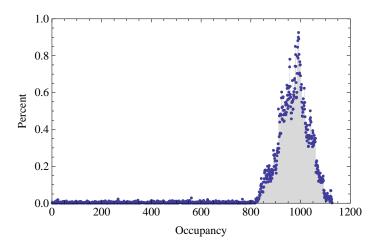

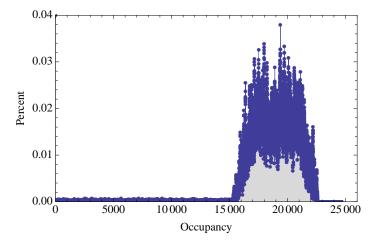

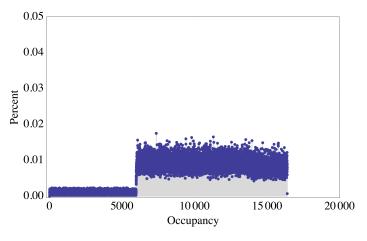

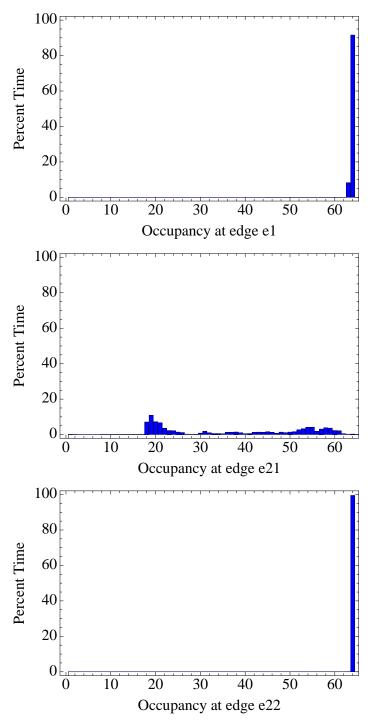

| 5.5  | True queue occupancy in $M/M/1$ micro-benchmark with software-to-hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|      | virtual queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 68  |

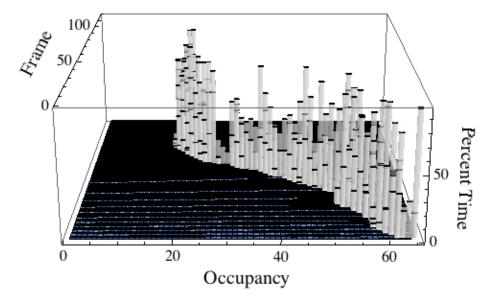

| 5.6  | Modeled queue occupancy in $M/M/1$ micro-benchmark with software-to-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|      | hardware virtual queue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68  |

| 5.7  | Two-stage tandem queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 69  |

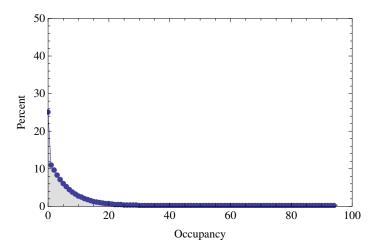

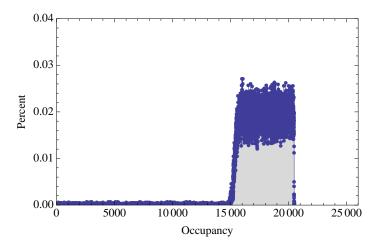

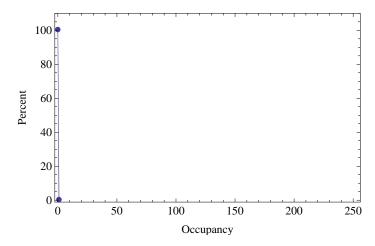

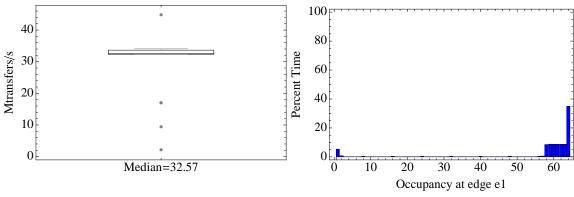

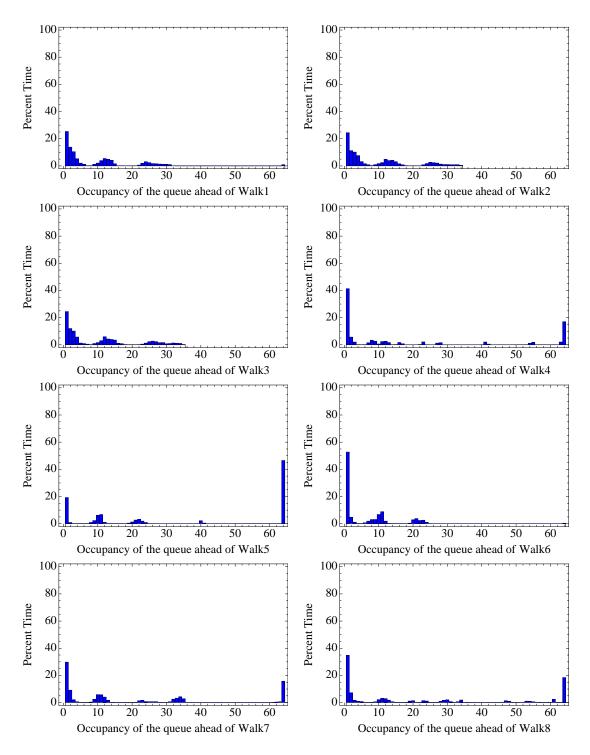

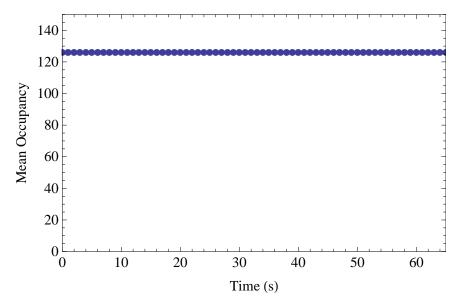

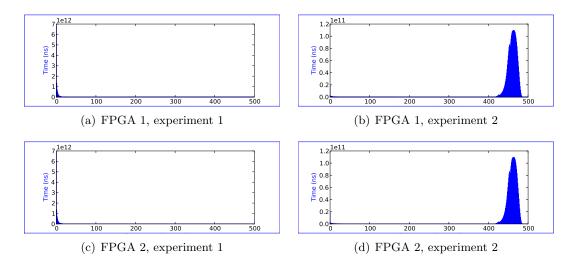

| 5.8  | Modeled queue occupancy in $M/M/1$ micro-benchmark with software-to-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |