### Washington University in St. Louis Washington University Open Scholarship

Engineering and Applied Science Theses & Dissertations

Engineering and Applied Science

Winter 12-15-2014

# Modeling Algorithm Performance on Highlythreaded Many-core Architectures

Lin Ma Washington University in St. Louis

Follow this and additional works at: http://openscholarship.wustl.edu/eng\_etds Part of the <u>Engineering Commons</u>

**Recommended** Citation

Ma, Lin, "Modeling Algorithm Performance on Highly-threaded Many-core Architectures" (2014). *Engineering and Applied Science Theses & Dissertations*. 63. http://openscholarship.wustl.edu/eng\_etds/63

This Dissertation is brought to you for free and open access by the Engineering and Applied Science at Washington University Open Scholarship. It has been accepted for inclusion in Engineering and Applied Science Theses & Dissertations by an authorized administrator of Washington University Open Scholarship. For more information, please contact digital@wumail.wustl.edu.

#### WASHINGTON UNIVERSITY IN ST. LOUIS

School of Engineering and Applied Science Department of Computer Science and Engineering

> Dissertation Examination Committee: Kunal Agrawal, Chair Roger Chamberlain, Co-Chair James Buckley Jeremy Buhler Tao Ju

Modeling Algorithm Performance on Highly-threaded Many-core Architectures by Lin Ma

> A dissertation presented to the Graduate School of Arts and Sciences of Washington University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> > December 2014 Saint Louis, Missouri

$\bigodot$  2014, Lin Ma

# **Table of Contents**

| List of | $\operatorname{Figures}$                            | v  |

|---------|-----------------------------------------------------|----|

| List of | Tables                                              | x  |

| Acknow  | pledgments                                          | xi |

| Abstra  | et                                                  | ii |

| Chapte  | r 1: Introduction                                   | 1  |

| 1.1     | Examples of Highly-threaded Many-core Architectures | 4  |

| 1.2     | Research Questions                                  | 6  |

| 1.3     | Methodology for Performance Modeling                | 9  |

|         | 1.3.1 Find Key Factors of Performance               | 10 |

|         | 1.3.2 Correlate 3 Spaces of Parameters              | 13 |

|         | 1.3.3 Define Performance Metric                     | 14 |

| 1.4     | Contribution and Dissertation Structure             | 14 |

| Chapte  | r 2: Background and Related Work                    | 17 |

| 2.1     | GPU Architectures and Programming Model             | 17 |

| 2.2     | Abstract Machine Models                             | 20 |

|         | 2.2.1 Sequential Machine Models                     | 20 |

|         | 2.2.2 Parallel Machine Models                       | 21 |

|         | 2.2.3 GPU Machine Models                            | 23 |

| 2.3     | Calibrated Performance Models                       | 24 |

| 2.4     | Algorithms for Memory Constrained Applications      | 25 |

| Chapte  | r 3: Threaded Many-core Memory (TMM) Model          | 27 |

| 3.1     | Abstraction of Highly-threaded Many-core Machines   | 27 |

|        | 3.1.1   | Architectures                                            | 28  |

|--------|---------|----------------------------------------------------------|-----|

|        | 3.1.2   | Parameters                                               | 29  |

|        | 3.1.3   | Applicability                                            | 32  |

| 3.2    | TMM     | Analysis Structure                                       | 33  |

| Chapte | er 4: A | Application of the TMM Model                             | 36  |

| 4.1    |         | irs Shortest Path (APSP)                                 | 36  |

|        | 4.1.1   | Dynamic Programming via Matrix Multiplication            | 37  |

|        | 4.1.2   | Johnson's Algorithm: Dijkstra's Algorithm (Binary Heaps) | 40  |

|        | 4.1.3   | Johnson's Algorithm: Dijkstra's Algorithm (Arrays)       | 42  |

|        | 4.1.4   | <i>n</i> Iterations of Bellman-Ford Algorithm            | 45  |

|        | 4.1.5   | Comparison of Various Algorithms                         | 47  |

|        | 4.1.6   | Effect of Problem Size                                   | 51  |

|        | 4.1.7   | Empirical Validation                                     | 53  |

| 4.2    | String  | Matching                                                 | 64  |

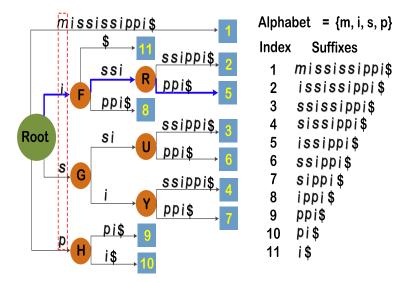

|        | 4.2.1   | Suffix Tree                                              | 64  |

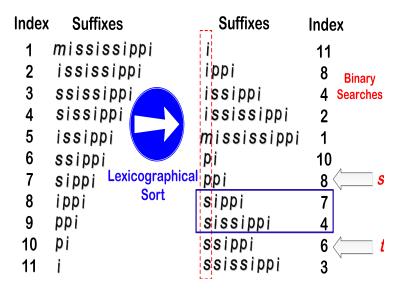

|        | 4.2.2   | Suffix Array                                             | 68  |

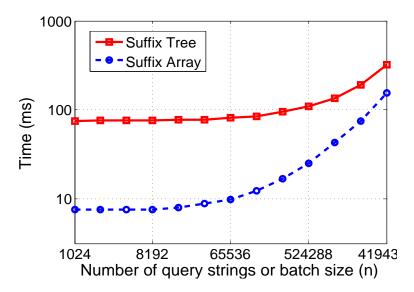

|        | 4.2.3   | Comparison and Empirical Validation                      | 70  |

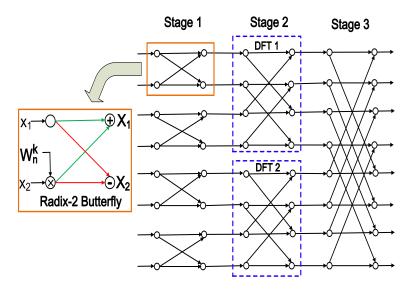

| 4.3    | Fast F  | ourier Transform (FFT)                                   | 74  |

| 4.4    | Merge   | Sort                                                     | 77  |

|        | 4.4.1   | Blocked Merge                                            | 77  |

|        | 4.4.2   | Merge Sort                                               | 78  |

| 4.5    | List R  | anking                                                   | 80  |

| 4.6    | Analys  | sis of Additional Algorithms                             | 82  |

| Chapte | er 5: C | Calibrated Performance Model                             | 83  |

| 5.1    |         | mance Modeling                                           | 84  |

|        | 5.1.1   | Base Model                                               | 85  |

|        | 5.1.2   | Model Extension                                          | 88  |

| 5.2    | Model   | Application                                              | 92  |

|        | 5.2.1   | Synthetic Micro-benchmark for Hashing                    | 92  |

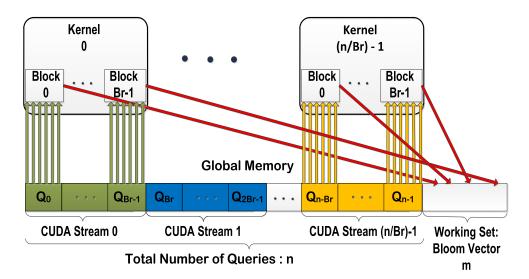

|        | 5.2.2   | Parallel Bloom Filters Algorithm Design and Implement    | 97  |

|        | 5.2.3   | Bloom Filters in BLAST                                   | 103 |

|        | 5.2.4   |                                                          | 113 |

|        | 5.2.5   | DNA Classification                                                                                                                    |

|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------|

| Chapte | er 6: I | ntegrated Analytical Framework                                                                                                        |

| 6.1    | Bridge  | the Asymptotic Model and the Calibrated Model 118                                                                                     |

|        | 6.1.1   | Combining the Two Models                                                                                                              |

| 6.2    | Applic  | ation of the Integrated Analytical Framework                                                                                          |

| 6.3    | Empir   | ical Validation $\ldots \ldots 126$ |

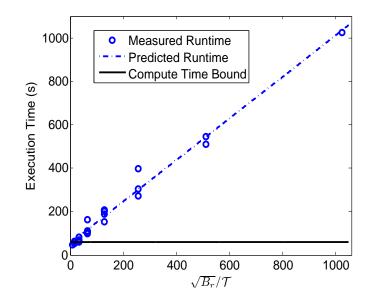

|        | 6.3.1   | Effect of $\sqrt{B_r}/\mathcal{T}$                                                                                                    |

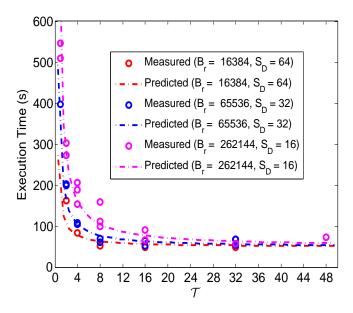

|        | 6.3.2   | Effect of $\mathcal{T}$                                                                                                               |

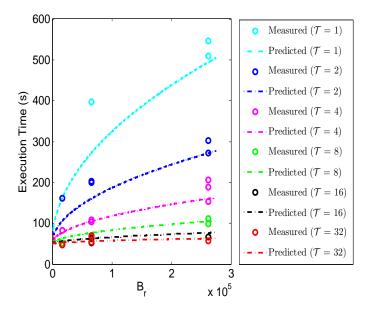

|        | 6.3.3   | Effect of $B_r$                                                                                                                       |

| 6.4    | Discov  | ering Unexpected Behavior                                                                                                             |

| Chapte | er 7: C | Conclusion and Future Work                                                                                                            |

| Refere | nces .  |                                                                                                                                       |

| Vita . |         |                                                                                                                                       |

# List of Figures

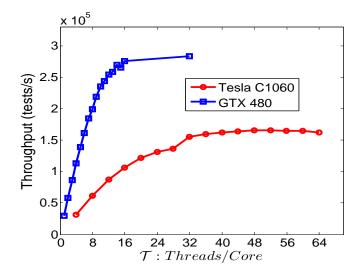

| Figure 1.1 | Throughput of Bloom filter algorithm for set membership testing on<br>biosequence data. Performance (in membership tests per second) is<br>plotted vs. number of threads per processor both for a Tesla C1060<br>and a GTX 480 GPU | 8  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

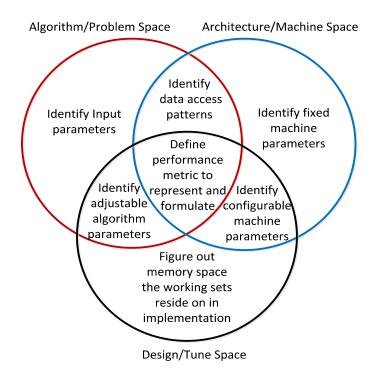

| Figure 1.2 | Approach to bridge the problem space, architecture space, and design space.                                                                                                                                                        | 13 |

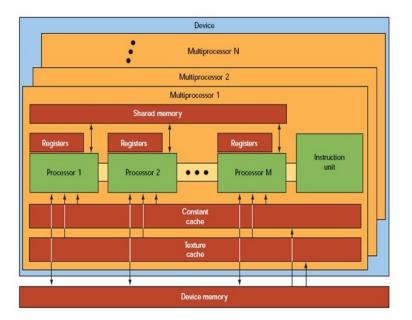

| Figure 2.1 | NVIDIA GPU Architecture [118]                                                                                                                                                                                                      | 18 |

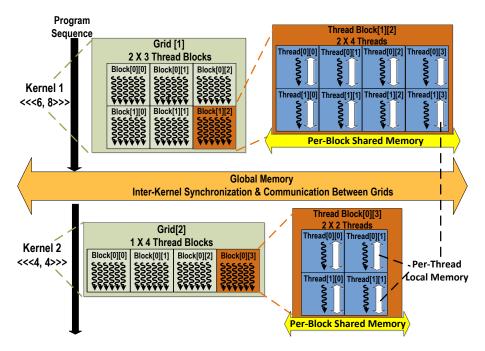

| Figure 2.2 | NVIDIA GPU thread hierarchy and programming model $\ . \ . \ .$ .                                                                                                                                                                  | 19 |

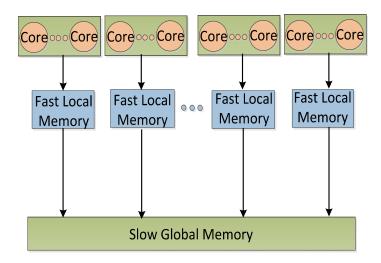

| Figure 3.1 | Abstracted highly-threaded, many-core architecture. The short arrows<br>from the cores to the local memory symbolize low latency, while the<br>long arrows to the global memory symbolize high latency                             | 29 |

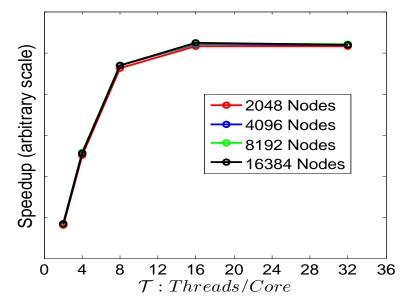

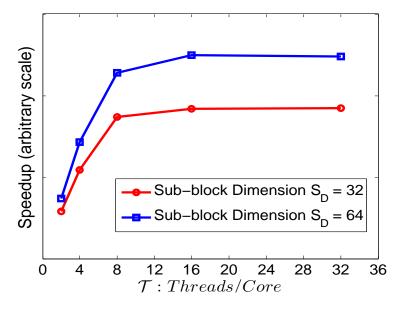

| Figure 4.1 | Speedup (theoretical $T_1$ via PRAM model over empirically measured $T_P$ ) of the dynamic programming algorithm, varying the number of threads per core from 2 to 32 (sub-block dimension $S_D = 64$ )                            | 56 |

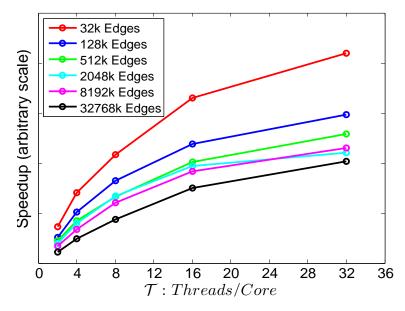

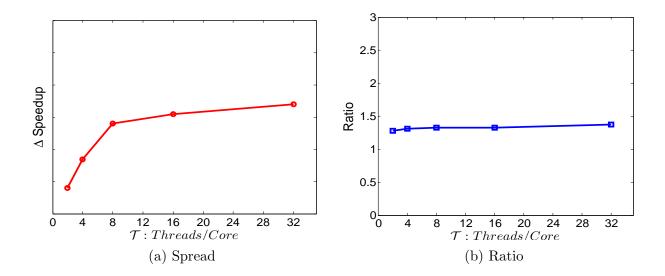

| Figure 4.2 | Speedup of Johnson's algorithm using arrays vs. threads/core for dif-<br>ferent graph densities. All curves are with 8K nodes. Again, speedup<br>is theoretical $T_1$ divided by empirically measured $T_P$                        | 57 |

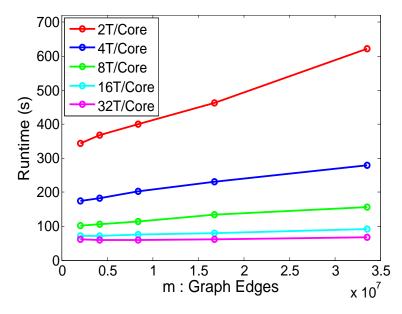

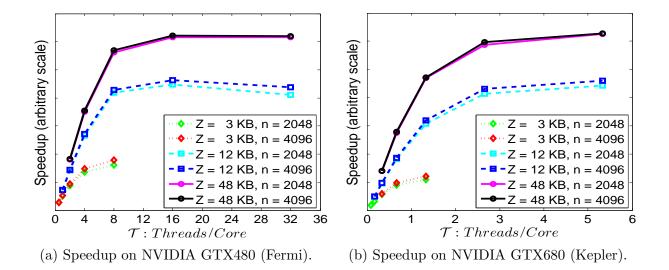

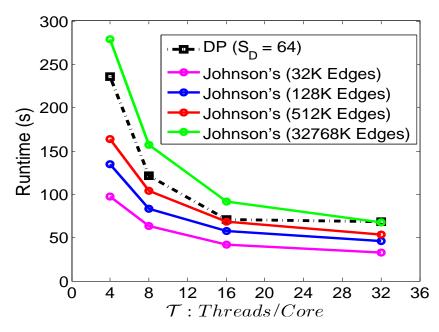

| Figure 4.3 | Runtime of Johnson's algorithm on graphs with constant 8K nodes<br>and varying density by increasing edges. Threads/core varies from 2<br>to 32                                                                                    | 58 |

| Figure 4.4  | Speedup of the dynamic programming algorithm for different sub-block dimensions $(S_D)$ , varying the threads/core on graphs with 16K nodes.                                                                                                                                                                                                                                                     | 59 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.5  | Different format of data from the two curves in Fig. 4.4 with the same speedup scale in order to isolate the effect of sub-block size from the effects of other parameters. (a) Spread of performance between sub-block dimension 64 and sub-block dimension 32. (b) Ratio of performance between sub-block dimension 64 and sub-block dimension 32.                                             | 60 |

| Figure 4.6  | Speedup of dynamic programming using adjacency matrix for all-pairs short-<br>est paths problem on two generations of NVIDIA GPUs. On GTX480,<br>with memory size 12 KB and 48 KB, using more than 16 threads hides the<br>memory latency completely; on GTX680, due to the hardware limit on $\mathcal{T}$ ,<br>latencies are not fully hidden, and the speedup curve is still climbing slowly. | 62 |

| Figure 4.7  | Runtime of the dynamic programming (DP) algorithm relative to Johnson's algorithm on a graph with 8K nodes, varying threads/core from 4 to 32 and edges from 32K to 32M.                                                                                                                                                                                                                         | 63 |

| Figure 4.8  | Suffix tree for string ' <i>mississippi</i> '. Each suffix is terminated by the special character \$. Leaves appear immediately after \$, represented by squares and labeled with suffix indices. Circles represent the internal nodes                                                                                                                                                           | 65 |

| Figure 4.9  | Suffix array for string 'mississippi'. Suffixes are sorted in lexicograph-<br>ical order. $s$ and $t$ are the suffixes immediately ordered before and<br>after the query string 'si', and located by binary searches. 'sippi' and<br>'sissippi' are the suffixes between $s$ and $t$ , representing all occurrences<br>of the query string                                                       | 68 |

| Figure 4.10 | Performance of suffix trees and suffix arrays on GPU. Empirical data are from Encarnaijao et al. [48].                                                                                                                                                                                                                                                                                           | 73 |

| Figure 4.11 | Data path and computation pattern of FFT. Radix-2 butterfly is the basic computation unit of FFT                                                                                                                                                                                                                                                                                                 | 75 |

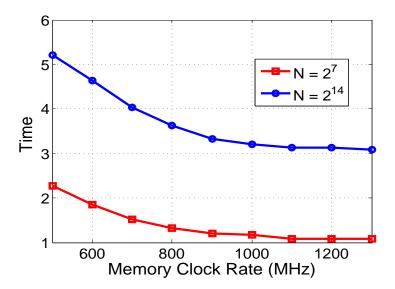

| Figure 4.12 | Runtime of FFT algorithm with various memory frequencies on an NVIDIA GTX280. The FFTs are performed for two problem sizes $N = 2^7$ and $N = 2^{14}$ . The <i>y</i> -axis is the runtime plotted on an arbitrary scale, as the runtime data are converted from GFLOPs from Govindaraju et al. [60]. The <i>x</i> -axis shows increasing memory clock rate, denoting decreasing memory latency <i>L</i> . | 76  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

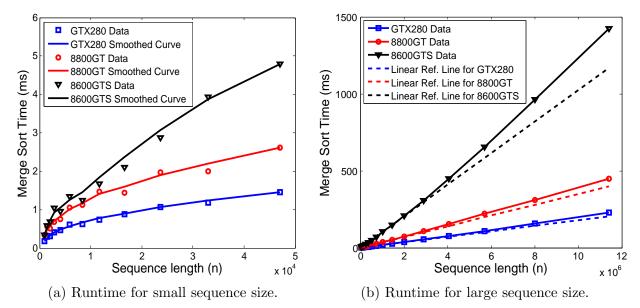

| Figure 4.13 | Merge sort on multiple GPUs (data from [134]); Solid lines are smoothed curves from data and dotted lines are linear references. (a) For small $n$ , the runtime increases slower than linearly with $n$ . (b) For large $n$ , the runtime increases faster than linearly with $n$                                                                                                                        | 80  |

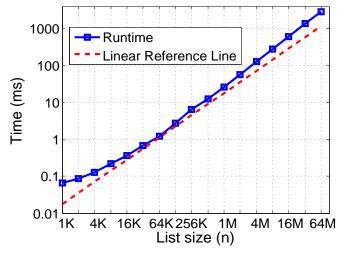

| Figure 4.14 | Runtime of Wyllie's algorithm on NVIDIA GTX 280 (data from [131]). The runtime grows slowly for small $n$ and faster for larger $n$ (dotted line is a linear reference). Note that the graph is a log-log plot in order to expose the trends over a wide range of $n$ .                                                                                                                                   | 81  |

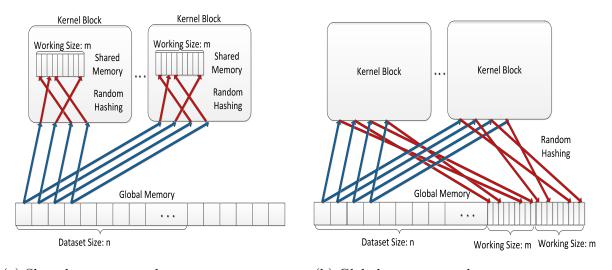

| Figure 5.1  | Micro-benchmark for random hashing on GPU architectures. (a) Hash table on shared memory. (b) Hash table on global memory                                                                                                                                                                                                                                                                                 | 93  |

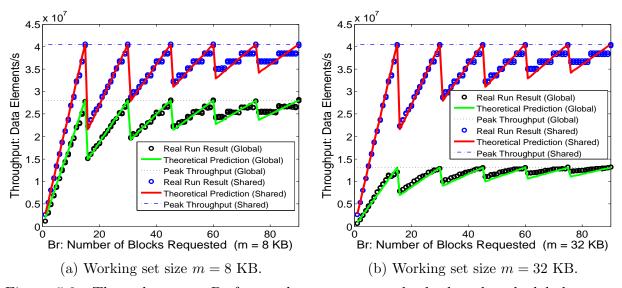

| Figure 5.2  | Throughput vs. $B_r$ for random accesses to both shared and global<br>memory subsystems with same problem size $(n = 2^{25})$ but distinct<br>working set sizes. (a) $m = 8$ KB. (b) $m = 32$ KB                                                                                                                                                                                                          | 95  |

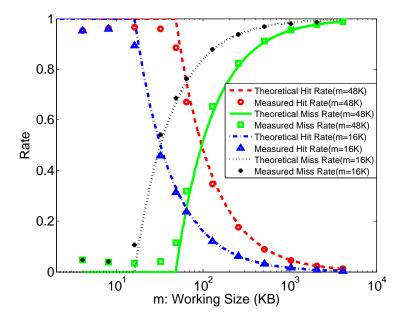

| Figure 5.3  | Cache hit and miss rates                                                                                                                                                                                                                                                                                                                                                                                  | 97  |

| Figure 5.4  | Impact of cache on execution time                                                                                                                                                                                                                                                                                                                                                                         | 98  |

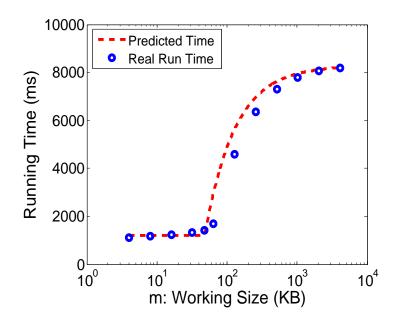

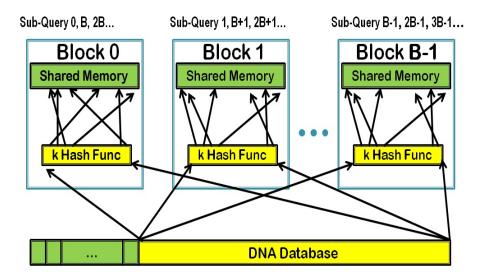

| Figure 5.5  | Parallel Bloom filters for detecting string matches of fixed length $w$ between a query and a database.                                                                                                                                                                                                                                                                                                   | 99  |

| Figure 5.6  | Implementation of parallel Bloom filter algorithm on GPU                                                                                                                                                                                                                                                                                                                                                  | 102 |

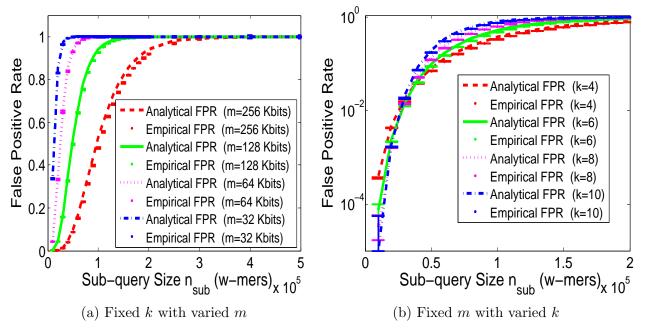

| Figure 5.7  | Theoretical and empirical results of FPR with varied sub-query size $n_{sub}$ . (a) shows FPR for several values of $m$ with a fixed $k = 6$ .<br>(b) shows FPR for several values of $k$ with a fixed $m = 256$ Kbits                                                                                                                                                                                    | 106 |

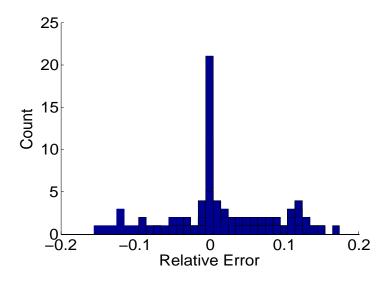

| Figure 5.8  | Histogram of relative error between theoretical predictions and empir-<br>ical measurements for FPR                                                                                                                                                                                                                                                                     | 107  |

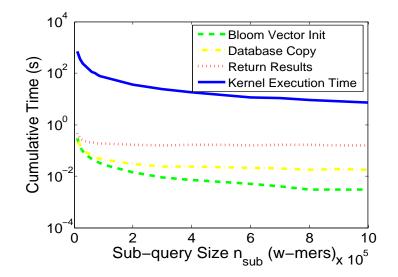

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 5.9  | Cumulative execution time for data movement and kernel. $\ . \ . \ .$                                                                                                                                                                                                                                                                                                   | 108  |

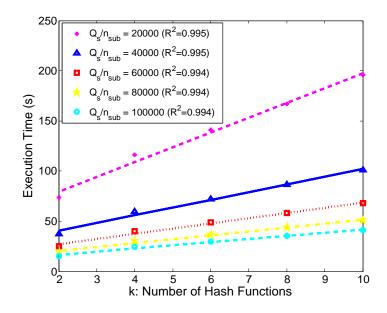

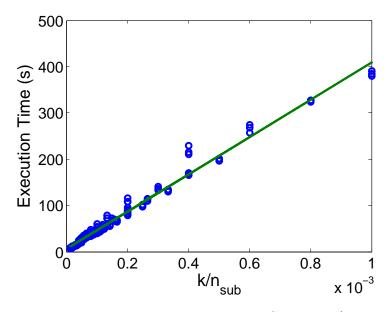

| Figure 5.10 | Execution time for different number of hash functions                                                                                                                                                                                                                                                                                                                   | 109  |

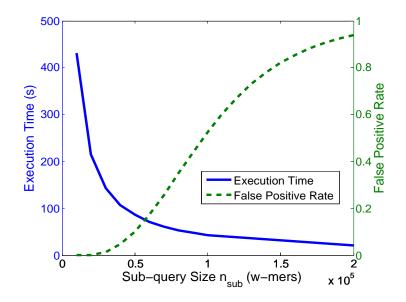

| Figure 5.11 | Execution time for different sub-query sizes                                                                                                                                                                                                                                                                                                                            | 110  |

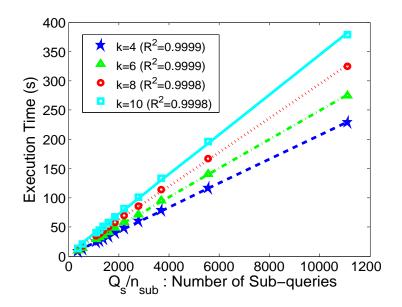

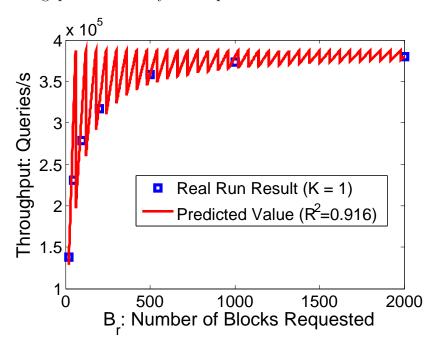

| Figure 5.12 | Throughput vs. $B_r$ on two GPU machines for Bloom filter of BLASTN.<br>(a) is for prediction and empirical measurements on GTX 480. Peak<br>performance is hit every 15 blocks as GTX 480 has 15 multiprocessors.<br>(b) is for prediction and empirical measurements on Tesla C1060. Peak<br>performance is hit every 30 blocks as Tesla C1060 has 30 multiprocessors | .111 |

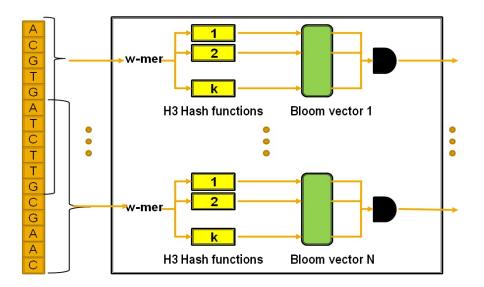

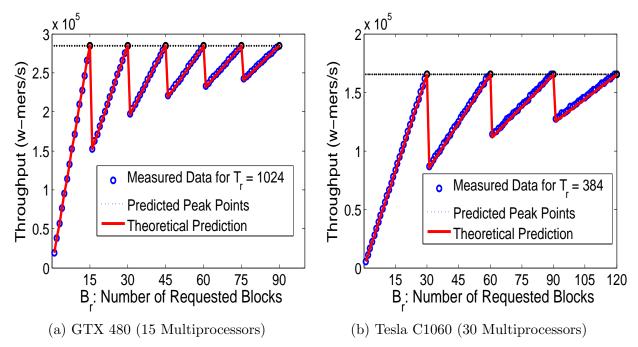

| Figure 5.13 | Modeled vs. measured execution time on GTX 480 $(a_1 = 4.01 \times 10^5, a_0 = 10, R^2 = 0.9909)$ .                                                                                                                                                                                                                                                                     | 113  |

| Figure 5.14 | Tradeoff between false positive rate and execution time                                                                                                                                                                                                                                                                                                                 | 114  |

| Figure 5.15 | Implementation of FACS DNA classification application                                                                                                                                                                                                                                                                                                                   | 115  |

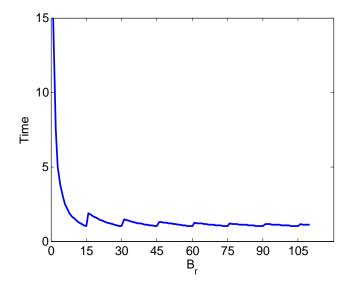

| Figure 5.16 | FACS throughput for different numbers of requested blocks                                                                                                                                                                                                                                                                                                               | 117  |

| Figure 6.1  | Execution time variation with requested number of blocks, $B_r$ . For<br>this example, $B_a = 1$ , $P/Q = 15$ (e.g., as in an NVIDIA GTX480),<br>and the max term in (6.3) is artificially set to 1                                                                                                                                                                     | 127  |

| Figure 6.2  | Runtime and model prediction in terms of $\sqrt{B_r}/\mathcal{T}$ for all-pairs shortest<br>paths problem with 8192 vertices. Measurements are from various runtime<br>configurations of $(B_r, \mathcal{T}, S_D)$ , therefore with different $B_a$ . Specifically, $B_r = (n/S_D)^2$ , $B_a$ is determined by Eq. (5.2)                                                | 129  |

| Figure 6.3  | Empirically measured and model predicted runtimes in terms of $\mathcal{T}$ for all-<br>pairs shortest paths problem with 8192 vertices. Measurements are from<br>various runtime configurations of $(B_r, \mathcal{T}, S_D)$ , therefore with different $B_a$ .<br>Specifically, $B_r = (n/S_D)^2$ , $B_a$ is determined by Eq. (5.2).                                 | 130  |

- Figure 6.4 Empirically measured and model predicted runtimes in terms of  $B_r$  for allpairs shortest paths problem with n = 8192 vertices. Measurements are from various runtime configurations of  $(B_r, \mathcal{T}, S_D)$ , therefore with different  $B_a$ . Specifically,  $B_r = (n/S_D)^2$ ,  $B_a$  is determined by Eq. (5.2). . . . . . 131

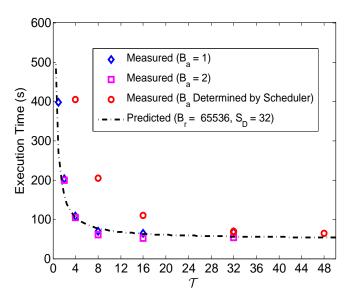

- Figure 6.5 Empirical measures of all-pairs shortest paths runtime for scenarios when  $B_a = 1, B_a = 2$  and  $B_a$  is determined automatically by the scheduler. The APSP problem with 8192 vertices is divided into sub-blocks of dimension 32. 132

# List of Tables

| Table 3.1 | Architecture parameters                                                                                   | 30 |

|-----------|-----------------------------------------------------------------------------------------------------------|----|

| Table 3.2 | Program parameters                                                                                        | 31 |

| Table 4.1 | Algorithm running times and constraints for linear speedup. $\ldots$ .                                    | 48 |

| Table 4.2 | Batch size $n$ at which suffix tree and suffix array runtime starts depending on $n$ .                    | 71 |

| Table 4.3 | Bounds for suffix tree and suffix array after the transition point when runtime starts depending on $n$ . | 72 |

| Table 4.4 | Analysis for some more classic algorithms.                                                                | 82 |

| Table 5.1 | Application Parameters                                                                                    | 86 |

| Table 5.2 | Architecture Parameters                                                                                   | 86 |

| Table 5.3 | Model Variables                                                                                           | 89 |

| Table 5.4 | NVIDIA GTX 480 Architecture Specification                                                                 | 94 |

## Acknowledgments

The fact that I survived the past 6 years, defended this dissertation and finally graduated as a computer science Ph.D. would not be true without the many people for whom I am grateful.

First of all, I would like to express my sincere gratitude to the two great advisors: Dr. Roger Chamberlain and Dr. Kunal Agrawal. Roger is the most patient and friendly person I have ever met. Since picked up into his research group, I was greatly impacted by his research advice, systematic insight, and optimistic attitude towards both work and life. Thank him for giving me so much freedom and flexibility so that I can manage my time with a good balance, and finish a successful internship in NVIDIA Research. I was kept being moved by his trust and kindness on me, as well as his warm smiles. Every tiny little piece of my achievement would not have been achieved without his strong support and encouragement. I would also thank Kunal to lead me and shape my thinking in theoretical parallel computing. She impressed and influenced me by her critical thinking, straightforward writing, and hardworking. I'm a firm believer that these influences, as life-long treasure, would significantly benefit and train me as a capable researcher. It's my great honor to be her first graduated Ph.D. in her academic life.

I would like to thank my committee James Buckley, Jeremy Buhler, and Tao Ju for their incisive comments and suggestions, and my colleagues Peng Li, Chengjie Wu, Jonathan Beard, Michael Hall, Shobana Padmanabhan, Joseph M. Lancaster, Joseph G. Wingbermuehle, and Arpith C. Jacob for their kind help and insightful discussion. I truly appreciate the patience and help from all the staff members in the Department of Computer Science and Engineering over these years. Myrna Harbison, Lauren Huffman, Kelli Eckman, Jayme Moehle, Madeline Hawkins, Andrea Levy, and Sharon Matlock make my Ph.D. study and life here really easier and more colorful than it is supposed to be. Special thanks also go out to Dr. Ken Wong and Dr. Jonathan Turner for their kind encouragement and strong endorsement.

I would also like to acknowledge the NSF Grant CNS-0905368, CNS-0931693, the NIH Award R42 HG003225, and Exegy, Inc. for financially funding my research.

Finally on a personal note, I take this opportunity to express my deepest gratitude to my parents for their unconditional love and consistent support. It is their thoughtful care and encouragement that helped me going through those hard times over all these years. Part of my life goal is to make their lives happier and happier than ever before. It is to them that I dedicate this work and degree.

Lin Ma

Washington University in Saint Louis December 2014

#### ABSTRACT OF THE DISSERTATION

Modeling Algorithm Performance on Highly-threaded Many-core Architectures by Lin Ma Doctor of Philosophy in Computer Science Washington University in St. Louis, 2014 Professor Kunal Agrawal, Chair Professor Roger Chamberlain, Co-Chair

The rapid growth of data processing required in various arenas of computation over the past decades necessitates extensive use of parallel computing engines. Among those, highlythreaded many-core machines, such as GPUs have become increasingly popular for accelerating a diverse range of data-intensive applications. They feature a large number of hardware threads with low-overhead context switches to hide the memory access latencies and therefore provide high computational throughput. However, understanding and harnessing such machines places great challenges on algorithm designers and performance tuners due to the complex interaction of threads and hierarchical memory subsystems of these machines. The achieved performance jointly depends on the parallelism exploited by the algorithm, the effectiveness of latency hiding, and the utilization of multiprocessors (occupancy). Contemporary work tries to model the performance of GPUs from various aspects with different emphasis and granularity. However, no model considers all of these factors together at the same time.

This dissertation presents an analytical framework that jointly addresses parallelism, latencyhiding, and occupancy for both theoretical and empirical performance analysis of algorithms on highly-threaded many-core machines so that it can guide both algorithm design and performance tuning. In particular, this framework not only helps to explore and reduce the configuration space for tuning kernel execution on GPUs, but also reflects performance bottlenecks and predicts how the runtime will trend as the problem and other parameters scale. The main contribution of the dissertation is a pair of analytical models with one focusing on higher-level asymptotic algorithm performance on GPUs and the other one emphasizing lower-level details about scheduling and runtime configuration. Based on the two models, we have conducted extensive analysis of a large set of algorithms. Two analysis provides interesting results and explains previously unexplained data. In addition, the two models are further bridged and combined as a consistent framework. The framework is able to provide an end-to-end methodology for algorithm design, evaluation, comparison, implementation, and prediction of real runtime on GPUs fairly accurately.

To demonstrate the viability of our methods, the models are validated through data from implementations of a variety of classic algorithms, including hashing, Bloom filters, all-pairs shortest path, matrix multiplication, FFT, merge sort, list ranking, string matching via suffix tree/array, etc. We evaluate the models' performance across a wide spectrum of parameters, data values, and machines. The results indicate that the models can be effectively used for algorithm performance analysis and runtime prediction on highly-threaded many-core machines.

# Chapter 1

## Introduction

General-purpose computation has irreversibly stepped into the parallel era, along with radically increased volumes of data, new algorithms, and emerging powerful parallel hardware platforms. Thanks to the development of new algorithms and computer systems, parallel processing not only can solve problems faster, it can also handle larger problems than is possible for sequential machines. However, as is commonly accepted, not every algorithm runs well on every parallel machine. We attribute the performance to the joint effect of algorithms and underlying architectures.

Abreast with traditional parallel architectures, such as shared memory machines and multicores, highly-threaded, many-core devices such as GPUs have gained popularity in the last decade; both NVIDIA and AMD manufacture general purpose GPUs that fall in this category. The important distinction between these machines and traditional multi-core machines is that these devices provide a large number of cores that support a massive numbers of hardware threads with low-overhead context switching between them; this fast context-switch mechanism is used to hide the memory access latency of transferring data from slow large (and often global) memory to fast, small (and typically local) memory. Over the years, various models have been designed to capture the most important aspects of architectures and algorithms that dominate the effect on performance for a diverse range of sequential and parallel machines. The most fundamental model that is used to analyze sequential algorithms is the Random Access Machine (RAM) model [4], which we teach undergraduates in their first algorithms class. This model assumes that all operations, including memory accesses, take unit time. While this model is a good predictor of performance on computationally intensive programs, it does not properly capture the important characteristics of the memory hierarchy of modern machines and the nonuniform costs of accessing memory. There are a number of other models that consider the memory access costs of sequential algorithms in different ways [1, 2, 7, 8, 52, 126, 153]. For parallel computing, the analogue for the RAM model is the Parallel Random Access Machine (PRAM) model [51], and there is a large body of work describing and analyzing algorithms in the PRAM model [79, 152]. In the PRAM model, the algorithm's complexity is analyzed in terms of its work — the time taken by the algorithm on 1 processor, and span (also called depth and critical-path length) — the time taken by the algorithm on an infinite number of processors. Given a machine with P processors, a PRAM algorithm with work W and span S completes in  $\max(W/P, S)$  time. The PRAM model also ignores the vagaries of the memory hierarchy and assumes that each memory access takes unit time. For modern machines, however, this assumption seldom holds. All these models fail to capture the nature of highly-threaded many-core machines.

There is no generally accepted theoretical model suitable for all architectures. Algorithm design and analysis tends to be agnostic to architectures and neutral to the number of processors so as to be general and universal. Unfortunately, this approach is insufficient for complex parallel machines, because while these machines provide substantial parallelism and efficiency, they impose important constraints on programs running on them. Failure to respect those constraints will likely result in downgraded performance. Attempts to understand algorithms' performance on modern machines have been extensively made during the past decades. Researchers have designed various models that capture memory hierarchies for various types of modern machines such as distributed memory machines [44, 147, 155], shared memory machines and multi-cores [11, 19, 20, 36, 41], or the combination of the two [38, 39]. However, there is limited literature unveiling this relation on highly-threaded many-core machines such as GPUs [64, 84, 116]. This becomes our motivation of successfully bridging algorithms and highly-threaded many-core machines, so that people can be enabled to predict and control the tradeoffs towards overall optimal performance.

We consider the general problem of how to understand, analyze, and ultimately optimize algorithm performance on highly-threaded many-core machines and hopefully guide designers or programmers to develop solutions with limited pitfalls and high performance. This is a broad problem, in part because not every type of application manifests similar performance patterns on many-core machines. Performance of some applications heavily relies on the behavior of the memory subsystem. While other applications require fewer memory transactions but more computation, in which case the performance is mostly subject to the capability of the computing engine. In this dissertation, distinct from existing approaches, we formalize a set of analytical models to reflect the performance of arbitrary algorithms. A performance analysis framework is designed to bridge the gap of understanding between algorithms and performance on such machines, consisting of a theoretical asymptotic model — *Threaded Many-core Memory (TMM)* model and an empirical prediction model — *Calibrated Performance Model*. Based on the insight gained from the performance analysis framework, we also explore an end-to-end methodology for algorithm design, evaluation, comparison, implementation, and prediction of real runtime on many-core GPUs accurately.

# 1.1 Examples of Highly-threaded Many-core Architectures

The most common instantiation of highly-threaded many-core architectures include NVIDIA GPUs, AMD/ATI GPUs, and YarcData uRiKA system. Although each of these machines has its own distinctive features, there are some common properties that categorize them as highly-threaded many-core machines. Those architectures typically consist of a number of core groups, each containing a number of processors (or cores) <sup>1</sup>, a fixed number of registers, and a fixed quantity of fast local on-chip memory shared within a core group. A large slow global memory is shared by all the core groups. Registers and local on-chip memory are the fastest to access, while accessing the global memory many potentially take 100s of cycles. Data is transferred from slow to fast memory in *chunks* in order to reduce long-latency memory transfers and achieve high bandwidth; instead of just transferring one word at a time, the hardware tries to transfer a large number of words during a memory transfer. The chunk can either be a cache line from hardware managed caches, or an explicitly-managed combined read from multiple threads.

On NVIDIA GPUs, a number of streaming multiprocessors (core groups in our terminology) share the same global memory residing on the device. On each of these streaming multiprocessors, there are a number of CUDA cores<sup>2</sup> that share a fixed number of registers and on-chip (fast) memory shared among the cores of the streaming multiprocessor. Accessing the off-chip global memory usually takes 20 to 40 times more clock cycles than accessing the on-chip shared memory/L1 cache [118]. The streaming multiprocessor creates, manages,

<sup>&</sup>lt;sup>1</sup>A core group can also have a single core.

<sup>&</sup>lt;sup>2</sup>CUDA (aka Compute Unified Device Architecture) is a parallel computing platform and programming model created by NVIDIA.

schedules, and executes threads in groups of 32 parallel threads called *warps*. When a warp executes an instruction that accesses global memory, it *coalesces* the memory accesses of the threads within the warp into one or more of these memory transactions depending on the size of the word accessed by each thread and the distribution of the memory addresses across the threads. Accesses are fully coalesced as long as all threads in a warp are organized such that consecutive 32-bit words are accessed by consecutive thread IDs. A fast hardware-supported context-switching mechanism enables a large number of threads simultaneously in flight. The threads can be manually organized and managed in thread blocks. Each thread block consists of a number of warps. One or more thread blocks will be scheduled on a streaming multiprocessor, depending on the usage of on-chip resources per block.

AMD/ATI GPUs consist of multiple Single-Instruction-Multiple-Data (SIMD) computation engines as core groups. Each of these compute engines accommodates a number of Thread Processors (TP) and Local Data Store (LDS) shared by all the thread processors associated with the SIMD engine. Each thread processor possesses ALUs called Stream Cores (SC), and is arranged as a five-way or four-way Very Long Instruction Word (VLIW) processor depending on different device families. Each of these thread processors executes a single instruction across each lane for each of a block of 16 work-items. The instruction is repeated over four cycles to make the 64-element vector called a *wavefront*. Taking Cypress, the codename of Radeon HD5800 series GPUs, as an example, the architecture is composed of 20 SIMD computation engines. In each SIMD engine, there are 16 thread processors and a 32 KB local data store. Low context-switch threading is well supported, and every 64 threads are grouped into a wavefront executing the same instruction in lockstep.

The uRiKA system from YarcData is also a good example of such machines. Based on fundamental assumption from Smith et al. [10] about the nature of the computations this processor was going to run, it is a purpose-built appliance for real-time graph analytics featuring graph-optimized hardware that provides up to 512 terabytes of global shared memory, massively-multithreaded graph processors (named Threadstorm) supporting 128 threads/processor, and highly scalable I/O. There can be up to 65,000 threads in a 512 processor system and over 1 million threads at the maximum system size of 8192 processors, so that the latencies are hidden by accommodating so many remote memory references in flight. The processor's instruction execution hardware essentially does a context switch every instruction cycle, finding the next thread that is ready to issue an instruction into the execution pipeline. This suggests that the memory access width is 1 on these machines. Threads do not share anything, as the Threadstorm processor has 128 hardware copies of the register set, program counter, stack pointer, etc., necessary to hold the current state of one software thread that is executing on the processor. But different than the two GPU architectures above, it has only one core on-chip.

## **1.2** Research Questions

While superficially, highly-threaded many-core machines are shared memory machines, their characteristics are very different from traditional multicore or multiprocessor shared memory machines. The most important distinction between multi-cores and highly-threaded many-core machines is the number of threads per core. On multi-core machines, context switch cost is high, and most models nominally assume that only one (or a small constant number of) thread(s) are running on each machine and this thread blocks when there is a memory access. Therefore, many existing models consider the number of memory transfers from slow memory to fast memory as a performance measure, and algorithms are designed to minimize

these, since memory transfers take a significant amount of time. In contrast, highly-threaded many-core machines are explicitly designed to have a large number of threads per core and a fast context switching mechanism. They are explicitly designed to hide memory latency; if a thread stalls on a memory operation, some other thread can be scheduled in its place. In principle, the number of memory transfers does not matter as long as there are enough threads to hide their latency. Therefore, if there are enough threads, we should, in principle, be able to use PRAM algorithms on GPUs, since we can ignore the effect of memory transfers which is exactly what the PRAM model does. However, the number of threads required to reach the point where one gets PRAM performance depends on both the algorithm and the hardware.

To motivate this enterprise and to understand the importance of high thread counts on many-core machines, let us consider a simple application that performs Bloom filter set membership tests on an input stream of biosequence data [105] on GPUs. The problem is embarrassingly parallel, each set membership test is independent of every other membership test. Fig. 1.1 shows the performance of this application, varying the number of threads per processor core, for two distinct GPUs. For both GPUs, the pattern is quite similar, at low thread counts, the performance increases (roughly linearly) with the number of threads, up until a transition region, after which the performance no longer increases with increasing thread count. While the location of the transition region is different for distinct GPU models, this general pattern is found in many applications. Once sufficient threads are present, the PRAM model adequately describes the performance of the application and increasing the number of threads no longer helps.

Figure 1.1: Throughput of Bloom filter algorithm for set membership testing on biosequence data. Performance (in membership tests per second) is plotted vs. number of threads per processor both for a Tesla C1060 and a GTX 480 GPU.

Since no highly-threaded many-core machine allows an infinite number of threads, and different thread/block counts may result in a huge search space of diversified performance, it is important to understand:

- 1. How many threads does a particular algorithm need to achieve PRAM performance asymptotically?

- 2. How does an algorithm perform and compare when it has fewer threads than required to get PRAM performance?

- 3. How does the variation of thread counts and thread block counts influence the scheduling, and therefore the real performance?

- 4. How can the real performance be predicted or calibrated for arbitrary runtime configurations?

For the first two problems, we design a high-level theoretical model (TMM model), which should abstract away the details of particular implementations so as to be applicable to many instantiations of these machines, while still being particular enough to model the performance of algorithms on these machines with reasonable accuracy. Basically it will characterize properties of algorithms and machines, capture how well the latencies are hidden by a given number of threads for a particular algorithm, and reveal how the performance of algorithms compares with asymptotically changing problem size and hardware parameters. For the last two problems, we develop a calibrated performance model, which, quite differently, plays with real throughput rather than asymptotic performance by incorporating the impact of hardware resources, real scheduling, and execution configuration. It will not tell you which algorithm is more efficient among candidates, but it will reflect the calibrated performance curve or pattern however you twist the execution configuration for the selected algorithm (or application) and machine being used.

## **1.3** Methodology for Performance Modeling

Performance analysis relies upon models that represent underlying assumptions; if a model does not capture the important aspects of target machines and programs, then the analysis is not predictive of real performance. Therefore, failure to capture unique features of highlythreaded many-core machines, especially the interaction between memory and the number of threads, will lead to misleading model. Given the heterogeneity and complexity of emerging many-core architectures relative to previous architectures, most well-known models for parallel architectures typically do not fit highly-threaded many-core machines. Researchers and developers need a way to bridge between algorithms and their possible performance on such machines so as to find key factors, understand their correlation, define a unified metric to represent, measure, and predict the performance accurately and make decisions wisely. Conceptually, our modeling process consists of 3 steps as followed.

#### **1.3.1** Find Key Factors of Performance

It's not too hard to implement an algorithm on a highly-threaded many-core machine, like a GPU, but it is much more difficult to get it to run efficiently. The crux of the problem is that few models or tools can precisely pinpoint the weakness of an algorithm in terms of latency hiding and the efficiency of the program execution in terms of processor scheduling, figure out the cause of the under-valued performance, and meticulously track the cause back to various key factors as a systematic methodology. Our performance analysis framework is designed to achieve this goal in a bottom-up approach. Basically, one needs to encompass the following aspects that are pertinent to overall algorithm performance:

#### 1. Architecture Parameters

Each highly-threaded many-core machine being used has its own hardware parameter settings among machines from different manufacturers and of different generations along the production road-map. Those parameters may include the number of cores, core groups, registers, the maximal number of threads and thread blocks supported, the memory access width, the size of local memory, and the latency between fast local memory and global memory, etc. Some of these parameters are even configurable.

#### 2. Algorithm Efficiency

For previous parallel machines, algorithm efficiency is mainly weighted by work and parallelism, in terms of the number of computational instructions. For highly-threaded many-core machines, this still holds, but is insufficient, due to unique memory subsystem. Some algorithms that are efficient for previous machines, may exhibit irregular memory accesses, and incur too much remote memory traffic on many-core machines. Memory locality and cost plays a more critical role on such machines than other machines, and should not be ignored.

#### 3. Design/Tune Settings

In the process of design or performance tuning, there are a number of aspects that can be controlled and varied: runtime configuration for scheduling, choice of access pattern, choice of memory spaces, and choice of data structures. The *frequency*, *pattern*, *usage*, and *cost* of memory interactions are largely the determinant factors to be considered.

#### (a) Thread Access Patterns

In highly-threaded many-core machines, threads are typically organized and scheduled in batches, each executing the same instruction for all the inclusive threads in lock-step. If a batch of threads access a contiguous block of memory, those accesses will be *coalesced* into just one memory transaction. This is an important pattern for reducing memory delays. The access pattern most of the time is determined by the algorithm itself, but sometimes also affected by the data structures. For example, Structure of Arrays (SoA) and Array of Structures (AoS) refer to two different ways of laying out data in memory, and they can significantly impact the data access patterns and therefore perform distinctively.

#### (b) Choice of Data Structures

Various algorithms have preferred data structures on different machines in terms of performance, depending on computation patterns. For example, if we look at two example algorithms for all-pairs shortest path problem, the Floyd Warshall algorithm uses an adjacency matrix for the vector-wise computation; while Johnson's algorithm would prefer an adjacency list to save space. On the other hand, due to coalescing and divergence, not all data structures are friendly to many-core machines. Poor choice of data structures results in more long-latency memory accesses and downgrades performance dramatically.

#### (c) Choice of Memory Space

Which memory space to use can make significant difference in performance even for cases with the same work or access pattern. We cannot avoid global memory transactions in general, but some important classes of computation can be designed to have the working sets almost entirely fit on fast local memory and hence benefit from that memory's advantages. For example, if an algorithm unavoidably requires data accesses in a purely random way, designers may wish to partition the random access range and deposit it on to fast local memory to radically reduce the long-latency memory transactions.

#### (d) Efficiency of Scheduling

Scheduling has great impact on performance. On many-core machines, peak performance only comes when all the cores are fully scheduled in use (i.e. full *occupancy*). The same algorithm may behave distinctively given different scheduling by altering the runtime configuration (i.e. threads per block, number of thread blocks). Finally, the occupancy is determined by hardware resource requested and real usage including registers, local memory, etc.

### 1.3.2 Correlate 3 Spaces of Parameters

Cognizant of the impact of various factors described above, we attempt to build performance models by folding them into 3 spaces and correlating them as illustrated in Fig. 1.2 below.

Figure 1.2: Approach to bridge the problem space, architecture space, and design space.

For the problem space, we need to identify both input parameters and adjustable parameters in the algorithm; for the architecture space, we need to identify both fixed (e.g. memory sizes and cores) and configurable parameters (e.g. threads and thread blocks) for the machine. Data access patterns stipulated by the algorithms should also be recognized considering the memory spaces the machine can provide. If the pattern is somehow random or heavily revisited, in design space, the fast local memory would be preferred for working sets to reside on in order to reduce latency in the real implementation, as accessing fast local memory would be 100s times faster than accessing the global memory for strided accesses. If the fast local memory size is not big enough to accommodate the whole working set, designers might either want to decompose the problem into smaller but more working sets, or just use the slow global memory with sufficient amount of threads to hide latency. The strategy of choice in the design space depends on all these parameters and factors, which are actually intertwined and affected by some of the others. They jointly determine the overall performance of the algorithm running on the underlying machines.

#### **1.3.3** Define Performance Metric

To count in the effect of individual parameters, a performance metric needs to be defined to encode, correlate, and formulate the information obtained above. Then the relationships between input parameters and predicted performance can be explored both theoretically and empirically. We will expose runtime as a unified metric for performance across all 3 spaces/domains presented in Fig. 1.2 above, with expression of parameters from individual spaces positively contributing to it. From the theoretical side, we can effectively use the number of instructions to measure runtime, assuming instructions take constant time. This holds for both computation and memory instructions, although they differ from each other by a factor. From the empirical side, we will measure real runtime with varied parameter settings.

## **1.4** Contribution and Dissertation Structure

This dissertation makes contributions in the following aspects:

- 1. We design a high-level theoretical performance model named the Threaded Many-core Memory (TMM) model to capture the performance characteristics of highly-threaded many-core systems, and analyze algorithm performance using it. This is the first formalized asymptotic model for algorithm design, analysis, and comparison in any system which has fast context switching and large number of threads to hide memory latency. It provides a more fine-grained and accurate performance prediction than the PRAM analysis. This model is designed in [99, 101] and will be introduced in Chapter 3.

- 2. A wide range of classic algorithms are analyzed through the TMM model with sufficient details and empirical results to examine and highlight the power of the TMM model. The algorithms involved include 4 all-pair shortest path algorithms (dynamic programming via a adjacency matrix, Johnson's algorithm via array/heap, Bellman-Ford), FFT, merge sort, string matching via suffix array/string, list ranking, etc. These analyses provide the detailed TMM results and extensively compare with PRAM results in [100, 102] and will be described in Chapter 4.

- 3. A low-level calibrated performance model is designed to quantitatively predict runtime for all possible runs with various configurations by only one real run. This is achieved by explicit inclusion of performance-impacting factors that are only important over some range of the model's input domain (especially, for example, for smaller input sizes) in addition to the scale factors that enable the calibrated model to make specific quantitative performance predictions throughout the entire configuration space. Those critical factors include application algorithmic complexity, caching factor, and scheduling factor. This model is designed in [104, 105] and will be expatiated in Chapter 5.

- 4. A number of empirical validations towards the calibrated performance model have been done to demonstrate the effectiveness of this model. A parallel Bloom filter algorithm is designed and implemented on GPUs with 35-fold speedup in [105]. A synthetic microbenchmark for hashing is presented [104], allowing us to quantitatively explore impact of various access patterns and memory spaces of GPUs on application throughput. Bloom filters in BLAST (the most widely used tool for biosequence similarity search) and another application that exploits hashing in DNA classification are implemented. Empirical results from all applications above line up closely with the model prediction and are presented in Chapter 5.

- 5. An analytical performance framework is defined in [103] by exploring the coordinated use of the TMM model and the calibrated model and confirming their consistency of prediction for algorithm performance analysis. The framework is able to address parallelism exploited by the algorithm, effectiveness of latency-hiding, and utilization of multiprocessors (occupancy) all together. In particular, it not only helps to explore and reduce the configuration space for tuning kernel execution on highly-threaded many-core machines, but also reflects performance bottlenecks and predicts how the runtime will trend as the problem and other parameters scale. The framework is mainly described in Chapter 6.

In addition to those chapters mentioned above, Chapter 1 briefly introduces the architectures, research questions and methodologies, and highlights the contributions of this dissertation. Chapter 2 describes background information, lists and compares related works for machine models, calibrated models, and GPU algorithms from the literature. At the end, the conclusion and future work are discussed in Chapter 7.

# Chapter 2

## **Background and Related Work**

In this chapter, we briefly describe GPU architectures and programming models. Then, we review the abstract machine models for sequential machines, parallel machines, and particular GPU machines as related work. After that, we also review recent work on algorithms and performance analysis of GPUs which are the most common current instantiations of highly-threaded, many-core machines.

## 2.1 GPU Architectures and Programming Model

Generally, GPUs consist of a number of *core groups*, each of which can be a *streaming multiprocessor* in NVIDIA GPUs or an *SIMD compute engine* in AMD/ATI GPUs. Those core groups share the same global device memory for inter-core-group communications. On each of the core groups, there are a certain number of processors, named *CUDA cores* in NVIDIA GPUs, and *Thread Processors* in AMD/ATI GPUs. Those processors have their own local storage for individual thread such as registers, but they do share the same on-chip shared memory and caches of different features for inter-core and inter-thread communications.

Figure 2.1: NVIDIA GPU Architecture [118]

While AMD GPUs are similar, we will focus the discussion on NVIDIA GPUs since the empirical results we present are all on various NVIDIA platforms. Fig. 2.1 illustrates the general architecture of NVIDIA GPUs. On GPU device, there are a number of multiprocessors sharing the same device (global) memory. On each of the multiprocessors, there are a number of processors (cores) sharing the same shared memory and other specialized memory space such as constant memory and texture memory. For each of the processors, there is also local memory such as registers associated with it.

To harness such architecture, the *Compute Unified Device Architecture (CUDA)*, a parallel computing platform and programming model, is designed by NVIDIA to efficiently solve many complex computational problems and transparently scale their GPU parallelism to the ever-increasing number of processor cores and threads, while maintaining a stable structure for programs and low learning curve for programmers familiar with the C programming language [118]. As shown in Fig. 2.2, it mainly has 3 key components exposed to

the programmer – a hierarchy of thread groups, a hierarchy of shared memories, and barrier synchronizations. Utilizing these components, people can easily manipulate fine-grained data parallelism and thread parallelism, nested with coarse-grained data parallelism and task parallelism. A CUDA program invokes parallel functions called *kernels* that, when called,

Figure 2.2: NVIDIA GPU thread hierarchy and programming model

are executed N times in parallel by N different CUDA threads. A **thread block** is a set of concurrently executing threads that can cooperate among themselves through barrier synchronization and shared memory. A **grid** is an array of thread blocks that execute the same kernel, read inputs from global memory, write results to global memory, and synchronize between dependent kernel calls.

Each thread has a per-thread *local memory* space used for register spills, function calls, and C automatic array variables. Each thread block has a per-block *shared memory*

space used for inter-thread communication, data sharing, and result sharing in parallel algorithms. Grids of thread blocks share results in *global memory* space after kernel-wide global synchronization.

## 2.2 Abstract Machine Models

Theoretical analysis relies upon models that represent underlying assumptions; if a model does not capture the important aspects of target machines and programs, then the analysis is not predictive of real performance. Over the years, computer scientists have designed various models to capture important aspects of the machines that we use. Many machine and memory models have been designed for various types of sequential and parallel machines.

#### 2.2.1 Sequential Machine Models

The most fundamental model that is used to analyze sequential algorithms is the Random Access Machine (RAM) model [4], which we teach undergraduates in their first algorithms class. This model assumes that all operations, including memory accesses, take unit time. While this model is a good predictor of performance on computationally intensive programs, it does not properly capture the important characteristics of the memory hierarchy of modern machines. Aggarwal and Vitter proposed the Disk Access Machine (DAM) model [3] which counts the number of memory transfers from slow to fast memory instead of simply counting the number of memory accesses by the program. Therefore, it better captures the fact that modern machines have memory hierarchies and exploiting spatial and temporal locality on these machines can lead to better performance. Aggarwal et al. [1] present the Hierarchical Memory Model (HMM) and use it for a theoretical investigation of the inherent complexity of solving problems in RAM with a memory hierarchy of multiple levels. It differs from the RAM model by defining that access to location x takes log x time, but it does not consider the concept of block transfers, which collects data into blocks to utilize spatial locality of reference in algorithms. The Block Transfer model (BT) [2] addresses this deficiency by defining that a block of consecutive locations can be copied from memory to memory, taking one unit of time per element after the initial access time. Alpern et al. propose the Memory Hierarchy (MH) Framework [8] that reflects important practical considerations that are hidden by the RAM and HMM models: data are moved in fixed size blocks simultaneously at different levels in the hierarchy, and the memory capacity as well as bus bandwidth are limited at each level. But there are too many parameters in this model that can obscure algorithm analysis. Thus, they simplified and reduced the MH parameters by putting forward a new Uniform Memory Hierarchy (UMH) model [7, 153]. Later, an 'ideal-cache' model was introduced in [52, 126] allowing analysis of cache-oblivious algorithms that use asymptotically optimal amounts of work and move data asymptotically optimally among multiple levels of cache without the necessity of tuning program variables according to hardware configuration parameters.

#### 2.2.2 Parallel Machine Models

For parallel computing, the analogue for the RAM model is the Parallel Random Access Machine (PRAM) model [51], and there is a large body of work describing and analyzing algorithms in the PRAM model [79, 152]. In the PRAM model, the algorithm's complexity is analyzed in terms of its *work* — the time taken by the algorithm on 1 processor, and *span* (also called *depth* and *critical-path length*) — the time taken by the algorithm on an infinite

number of processors. Given a machine with P processors, a PRAM algorithm with work W and span S completes in  $\max(W/P, S)$  time.

The PRAM model, although widely used, also unrealistically ignores the vagaries of the memory hierarchy and assumes that all processors work synchronously with uniform cost per memory access, and that interprocessor communication is free. For modern machines, however, this assumption seldom holds. Quite different to PRAM, the Bulk-Synchronous Parallel (BSP) model [147] attempts to bridge theory and practice by allowing processors to work asynchronously, and it models latency and limited bandwidth for distributed memory machines without shared memory. Culler et al. [44] offer a new parallel machine model called LogP based on BSP, characterizing a parallel machine by four parameters: number of processors, communication bandwidth, delay, and overhead. It reflects the convergence towards systems formed by a collection of computers connected by a communication network via message passing. Vitter et al. [155] present a two-level memory model and give a realistic treatment of parallel block transfers in parallel machines. But this model assumes processors are interconnected via sharing of internal memory.

More recently, several models have been proposed emphasizing the use of private-cache chip multiprocessors (CMPs). Arge et al. [11] present the Parallel External Memory (PEM) model with P processors and a two-level memory hierarchy, consisting of the main memory as external memory shared by all processors and caches as internal memory exclusive to each of the P processors. Blelloch et al. [19] present a multicore-cache model capturing the fact that multi-core machines have both per-processor private caches and a large shared cache on-chip. Bender et al. [17] present a concurrent cache-oblivious model. Blelloch et al. [20] also propose a parallel cache-oblivious (PCO) model to account for costs of a wide range of cache hierarchies. Chowdhury et al. [36] present a hierarchical multi-level caching model (HM), consisting of a collection of cores sharing an arbitrarily large main memory through a hierarchy of caches of finite but increasing sizes that are successively shared by larger groups of cores. They in [39] consider three types of caching systems for CMPs: D-CMP with a private cache for each core, S-CMP with a single cache shared by all cores, and multi-core with private  $L_1$  caches and a shared  $L_2$  cache. All the models above do not accurately describe highly-threaded, many-core systems, due to their distinctive architectures, i.e. the explicit use of many threads for the purpose of hiding memory latency.

#### 2.2.3 GPU Machine Models

More recently, there are a number of machine models proposed particularly for GPUs. Kirtzic et al. [84] proposed the Parallel GPU Model (PGM), which is essentially an adaption of the Bulk-Synchronous Parallel (BSP) model [147], and equates a super-step in BSP with a function unit of a GPU program. This model does not explicitly model the memory subsystem and assumes uniform cost access to all levels of memory. Nakano [116] proposed the Hierarchical Memory Machine (HMM) model, which consists of multiple Discrete Memory Machines (DMMs) representing shared memory and a single Unified Memory Machine (UMM) representing global memory. The HMM model does consider both shared memory accesses and the grouping of global memory accesses. Haque et al. [64] proposed a Many-core Machine Model (MMM) based on the Graham-Brent theorem, which is quite similar to the TMM model, but does not model the impact of threading for hiding memory latency.

# 2.3 Calibrated Performance Models

While there hasn't been much work on abstract machine models for highly-threaded, manycore machines, there has been a lot of recent work on designing calibrated performance models for particular instantiations of these machines such as NVIDIA GPUs. We review some of that work here.

He et al. [67] focus on the access patterns of gather and scatter operations, which can suffer from low memory bandwidth utilization, and design a probabilistic cache model to predict cache misses. Govindaraju et al. [59] propose a cache model for efficiently implementing three memory intensive scientific applications with nested loops. It is helpful for applications with 2D-block representations while choosing an appropriate block size by estimating cache misses, but is not completely general. Liu et al. [92] describe a general performance model that predicts the performance of a biosequence database scanning application fairly precisely. Their model incorporates the relationship between problem size and performance, but only targets their biosequence application. Ryoo et al. [133] summarize five categories of optimization mechanisms, and use two metrics to prune the GPU performance optimization space by 98%via computing the utilization and efficiency of GPU applications. They do not, however, consider memory latency and multiple conflicting performance indicators. Kothapalli et al. are the first to define a general GPU analytical performance model in [85]. They propose a simple yet efficient solution combining several well-known parallel computation models: PRAM, BSP, QRQW, but they do not model global memory coalescing. Using a different approach, Hong et al. [73] propose another analytical model to capture an estimate of the cost of memory operations by counting the number of parallel memory requests in terms of memory-warp parallelism (MWP) and computation-warp parallelism (CWP). However, their assumption of no cache misses is not always realistic. Sim et al. [138] extend this MWP-CWP model and present the GPUPerf framework. This framework quantitatively estimates performance along four dimensions: inter-thread instruction-level parallelism, memory-level parallelism, computing efficiency, and serialization effects. These four metrics help to identify performance bottlenecks and suggest what types of optimizations should be done. Baghsorkhi et al. [13] measure performance factors in isolation and later combine them to model the overall performance via workflow graphs so that the interactive effects between different performance factors are modeled correctly. The model can determine data access patterns, branch divergence, and control flow patterns only for a restricted class of kernels on traditional GPU architectures. Zhang and Owens [170] present a quantitative performance model that characterizes an application's performance as being primarily bounded by one of three potential limits: instruction pipeline, shared memory accesses, and global memory accesses. More recently, Kim et al. [82] also design a tool to estimate GPU memory performance by collecting performance-critical parameters. Parakh et al. [120] present a model to estimate both computation time by precisely counting instructions and memory access time by a method to generate address traces.

# 2.4 Algorithms for Memory Constrained Applications

There has been a rich body of work on the design of parallel algorithms to solve various memory constrained problems on many-core machines, primarily GPUs. Graph exploration is one of the important classes of such problems due to the irregularity of the underlying graph and random nature of memory access patterns. Attempts at accelerating graph processing on GPUs have been extensively made in the past several years for many algorithms, such as breadth-first search (BFS) [65, 71, 72, 97, 111], shortest paths [28, 65, 81, 107, 108, 112], maximum flow/min cut [66, 69, 74, 98, 140, 149], minimum spanning trees [117, 132, 150, 159], inclusion-based points-to analysis [110], list ranking [46, 130], and connected components [14, 46, 142]. In addition to graph algorithms, a wide range of other memory constrained algorithms have also been attempted on GPUs, including hashing [5, 43, 94], sorting [29, 58, 61, 83, 88, 134, 139, 167], matrix multiplication [34, 55, 61, 63, 76, 88], FFT [61, 88, 113], and dynamic programming [91, 93, 95].

Other than those classic algorithms above, there are also a large set of complicated algorithms for real-world memory constrained problems that can potentially be accelerated on GPUs, such as reducing prediction and test time in machine learning [32, 54, 164, 165, 166], reducing search time in artificial intelligence [33], boosting the efficiency in real-time systems [161] and streaming systems [27, 75, 90], parallelly solving game theory algorithms for optimization [162] and 3D modeling algorithms for imaging [171, 172].

# Chapter 3

# Threaded Many-core Memory (TMM) Model

The *Threaded Many-core Memory (TMM)* model is meant to model the asymptotic performance of algorithms on highly-threaded, many-core machines. The model abstracts away the details of particular implementations so as to be applicable to many instantiations of these machines, while being particular enough to model the performance of algorithms on these machines with reasonable accuracy. In this chapter, we will describe the important characteristics of these highly-threaded, many-core architectures and our model for analyzing algorithms for these architectures.

# 3.1 Abstraction of Highly-threaded Many-core Machines

This model is a high-level model meant to be generally applicable to a number of machines which allow a large number of threads with fast context switching. Therefore, it abstracts away many implementation details of both the machine and the algorithm. We also assume that the hardware provides 0-cost, perfect scheduling between threads. In addition, it also models the machine as having only 2 levels of memory. In particular, we model a slow global memory shared by all processors and fast local memory shared by one *core group*. In practice, these machines may have many levels of memory. However, we are interested in the interplay between the farthest level, since the latencies are the largest at that level, and therefore have the biggest impact on the performance. We expect that the model can be extended to also model other levels of the memory hierarchy.

#### 3.1.1 Architectures

The most important high-level characteristic of highly-threaded, many-core architectures is that they provide a large number of hardware threads and use fast and low-overhead context-switching in order to hide the memory access latency from slow global memory.

Highly-threaded, many-core architectures typically consist of a number of *core groups*, each containing a number of processors (or cores), a fixed number of registers, and a fixed quantity of fast local on-chip memory shared within a core group. A large slow global memory is shared by all the core groups. Registers and local on-chip memory are the fastest to access, while accessing the global memory may potentially take 100s of cycles. The TMM model models these machines as having a memory hierarchy with two levels of memory: slow global memory and fast local memory. In addition, on most highly-threaded, many-core machines, data is transferred from slow to fast memory in *chunks*; instead of just transferring one word at a time, the hardware tries to transfer a large number of words during a memory transfer. The chunk can either be a cache line from hardware managed caches, or an explicitly-managed combined read from multiple threads. Since this characteristic of using high-bandwidth

transfers in order to counter high latencies is common to most many-core machines (and most multi-core machines), the TMM model captures the chunk size as one of its parameters.

Figure 3.1: Abstracted highly-threaded, many-core architecture. The short arrows from the cores to the local memory symbolize low latency, while the long arrows to the global memory symbolize high latency.

These architectures support a large number of hardware threads, much larger than the number of cores. Cores on a single core group execute in synchronous style where groups of threads execute in lock-step. When a thread group executing on a core group stalls on a slow memory access, in theory, a context switch occurs and another thread group is scheduled on that core group. The abstract architecture is shown in Fig. 3.1. Note that this architecture abstraction ignores a number of details about the physical machine, including thread grouping, scheduling, etc.

#### 3.1.2 Parameters

The TMM model captures the important characteristics of a highly-threaded, many-core architecture by using six parameters shown in Table 3.1. L is the latency for accessing the