### University of South Carolina Scholar Commons

Theses and Dissertations

2015

# Defect Characterization of 4H-SIC by Deep Level Transient Spectroscopy (DLTS) and Influence of Defects on Device Performance

Mohammad Abdul Mannan University of South Carolina - Columbia

Follow this and additional works at: http://scholarcommons.sc.edu/etd

#### **Recommended** Citation

Mannan, M. A.(2015). Defect Characterization of 4H-SIC by Deep Level Transient Spectroscopy (DLTS) and Influence of Defects on Device Performance. (Doctoral dissertation). Retrieved from http://scholarcommons.sc.edu/etd/3083

This Open Access Dissertation is brought to you for free and open access by Scholar Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact SCHOLARC@mailbox.sc.edu.

### DEFECT CHARACTERIZATION OF 4H-SIC BY DEEP LEVEL TRANSIENT SPECTROSCOPY (DLTS) AND INFLUENCE OF DEFECTS ON DEVICE PERFORMANCE

by

Mohammad Abdul Mannan

Bachelor of Science Bangladesh University of Engineering and Technology, 1998

> Master of Science Concordia University, 2011

Submitted in Partial Fulfillment of the Requirements

For the Degree of Doctor of Philosophy in

**Electrical Engineering**

College of Engineering and Computing

University of South Carolina

2015

Accepted by:

Krishna C. Mandal, Major Professor

Yinchao Chen, Committee Member

Guoan Wang, Committee Member

Fanglin Chen, Committee Member

Lacy Ford, Vice Provost and Dean of Graduate Studies

© Copyright by Mohammad Abdul Mannan, 2015 All Rights Reserved.

### DEDICATION

This dissertation is dedicated to my wife Farhana Anjum, my daughter Fabliha Maliyat and my son Fawaz Mustaneer, whose relentless encouragement and support during this extraordinary odyssey has helped me to put my best efforts toward this research work.

#### ACKNOWLEDGEMENTS

Firstly, I would like to thank my advisor, Dr. Krishna C. Mandal, for his continued support and guidance on this research. My development within his group has allowed me to undertake this work with the proper knowledge and skillset. I would also like to thank my committee members, Dr. Yinchao Chen, Dr. Guoan Wang, and Dr. Fanglin Chen, for taking the time to oversee my research and their support of my work.

I would also like to thank the following people for their contributions to the research performed in this work:

- Khai Nguyen, who assisted heavily to set up take Alpha Spectrometer and taking Spectroscopy measurement.

- Dr. Sandeep K. Chaudhuri (Electrical Engineering, University of South Carolina) for his assistance during the set-up of the DLTS equipment.

- The staff of Electron Microscopy Center (EMC) at the University of South Carolina for their assistance with Scanning Electron Microscopy (SEM) and Energy Dispersive X-ray Spectroscopy (EDX) studies.

- Dr. Shuguo Ma (College of Engineering and Computing, University of South Carolina) for performing the XPS characterization.

I would also like to thank my fellow lab members, Ramesh Krishna, Sandip Das, Kelvin Zavalla, Rahmi Pak, and Cihan Oner for their support and friendship throughout this process. Finally, I would like to thank all those faculty members and staff in the Electrical Engineering department at the University of South Carolina whose cumulative efforts have contributed to the successful completion of my doctoral research. Without their contributions, this work would have been impossible to perform.

#### ABSTRACT

Silicon carbide (SiC) is one of the key materials for high power opto-electronic devices due to its superior material properties over conventional semiconductors (e.g., Si, Ge, GaAs, etc). SiC is also very stable and a highly suitable material for radiation detection at room temperature and above. The availability of detector grade single crystalline bulk SiC is limited by the existing crystal growth techniques which introduce extended and microscopic crystallographic defects during the growth process. Recently, SiC based high-resolution semiconductor detectors for ionizing radiation have attracted world-wide attention due to the availability of high resistive, highly crystalline epitaxial layers with very low micropipe defect content ( $< 1 \text{ cm}^{-2}$ ). SiC Schottky barrier radiation detectors on epitaxial layers can be operated with a high signal-to-noise ratio even above room temperature due to its wide band-gap. However, significant amount of intrinsic defects and impurities still exist in the grown SiC epilayer which may act as traps or recombination/generation centers and can lead to increased leakage current, poor carrier lifetime, and reduced carrier mobility. Unfortunately, the nature of these electrically active deep levels and their behavior are not well understood. Therefore, it is extremely important to identify these electrically active defects present in the grown epitaxial layers and to understand how they affect the detector performance in terms of leakage current and energy resolution.

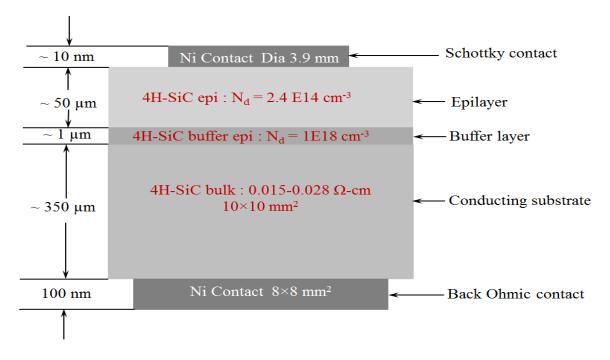

In this work, Schottky barrier radiation detectors were fabricated on high quality n-type 4H-SiC epitaxial layers. The epitaxial layers were grown on nitrogen doped n-type 4H-SiC (0001) substrates by a hot wall chemical vapor deposition (CVD) process. The epitaxial growth was carried out with 8° off-cut towards the [ $11\overline{2}0$ ] direction. The Schottky barriers were formed on the epitaxial layers (Si-face) by depositing thin (~10 nm) circular Ni contact (area ~10 mm<sup>2</sup>) which acts as the detector window. The thickness of the detector window was decided such that there was minimal alpha energy attenuation while maintaining a reliable electrical contact. For the back contact, ~100 nm thick square (~40 mm<sup>2</sup>) Ni contact was deposited on the C-face of the 4H-SiC substrate.

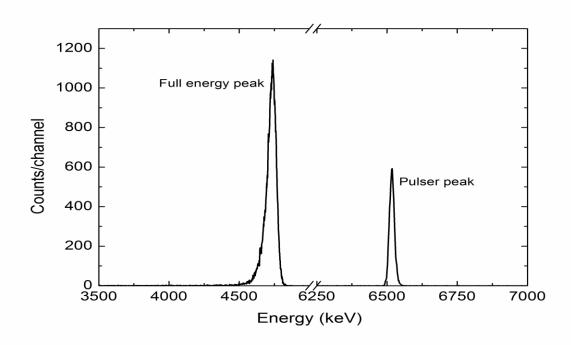

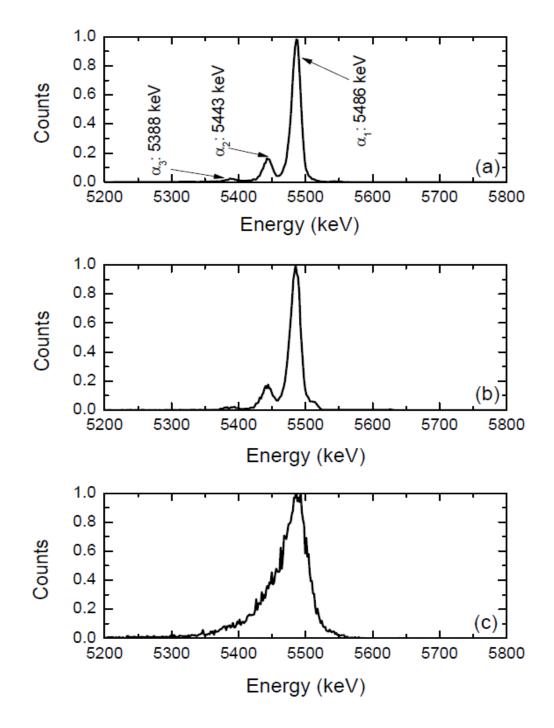

The junction properties of the fabricated Schottky barrier radiation detectors were characterized through current-voltage (I-V) and capacitance-voltage (C-V) measurements. From the fabricated devices, those with high barrier height (~ 1.6 eV) and extremely low leakage current (few pA at a reverse bias of ~ -100 V) were selected for alpha spectroscopic measurements. Alpha pulse-height spectra was obtained from the charge pulses produced by the detector irradiated with a standard 0.1  $\mu$ Ci <sup>241</sup>Am source. The charge transport and collection efficiency results, obtained from the alpha particle pulse-height spectroscopy, were interpreted using a drift-diffusion charge transport model. The detector performances were evaluated in terms of the energy resolution. From alpha spectroscopy measurements the FWHM (full width at half maxima) of the fabricated Schottky barrier detectors were in the range of 0.29% - 1.8% for the main alpha peak of  $^{241}$ Am (5.486 MeV).

Deep level transient spectroscopy (DLTS) studies were conducted in the temperature range of 80 K - 800 K to identify and characterize the electrically active defects present in the epitaxial layers. Deep level defect parameters (i.e. activation energy, capture cross-section, and density) were calculated from the Arrhenius plots which were obtained from the DLTS spectra at different rate windows. The observed defects in various epitaxial layers were identified and compared with the literature. In the 50  $\mu$ m epitaxial layer, a new defect level located at E<sub>c</sub> - 2.4 eV was observed for the first time. The differences in the performance of different detectors were correlated on the basis of the barrier properties and the deep level defect types, concentrations, and capture cross-sections. It was found that detectors, fabricated on similar wafers, can perform in a substantially different manner depending on the defect types. For 20 µm epitaxial layer Schottky barrier radiation detectors, deep levels  $Z_{1/2}$  (located at ~ E<sub>c</sub> - 0.6 eV) and EH<sub>6/7</sub> (located at ~  $E_c$  - 1.6 eV) are related to carbon vacancies and their complexes which mostly affect the detector resolution. For 50 µm epitaxial layer Schottky barrier radiation detectors, Z<sub>1/2</sub>, EH<sub>5</sub>, and the newly identified defect located at E<sub>c</sub> - 2.4 eV mostly affect the detector resolution.

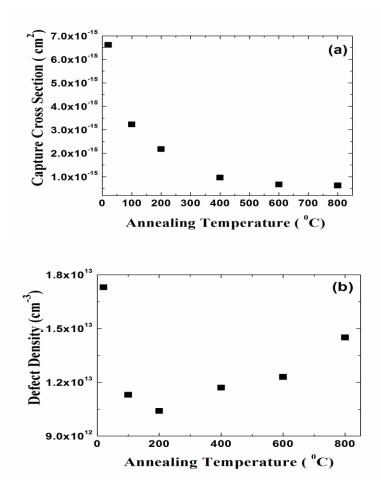

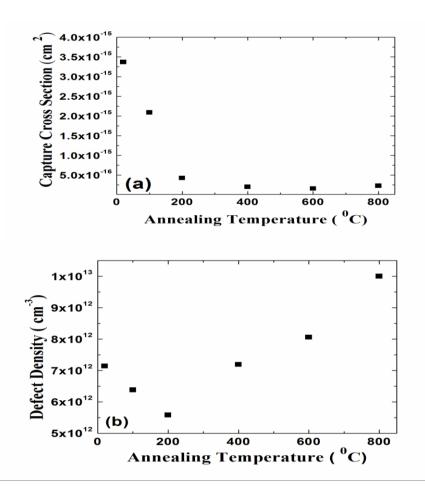

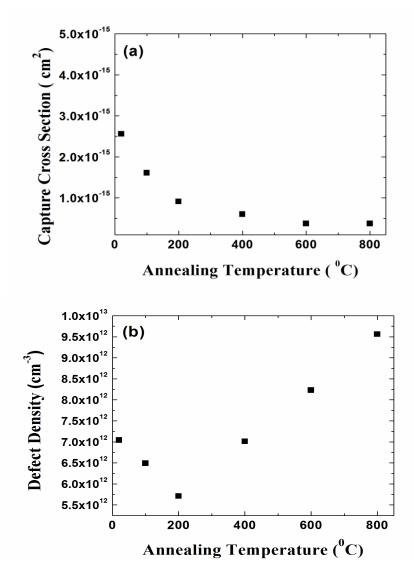

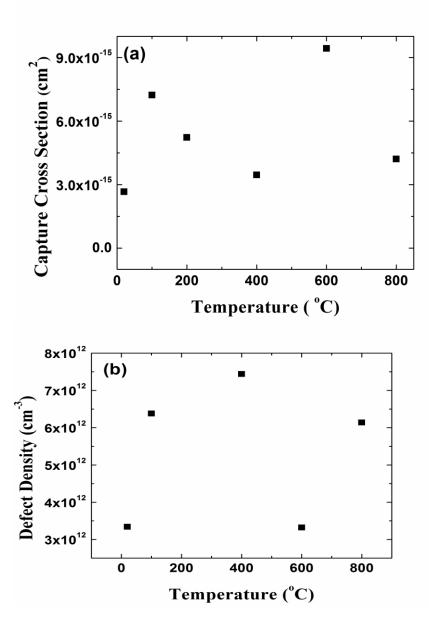

The annealing behavior of deep level defects was thoroughly investigated by systematic C-DLTS measurements before and after isochronal annealing in the temperature range of 100 °C - 800 °C. Defect parameters were calculated after each isochronal annealing. Capture cross-sections and densities for all the defects were investigated to analyze the impact of annealing. The capture cross-sections of the defects Ti (c) (located at  $E_c - 0.17$  eV) and EH<sub>5</sub> (located at  $E_c - 1.03$  eV) were observed to

decrease with annealing temperature while the densities did not change significantly. Deep level defects  $Z_{1/2}$  and  $EH_{6/7}$  were found to be stable up to the annealing temperature of 800 °C.

•

## TABLE OF CONTENTS

| DEDI | CATIONiii                                             |

|------|-------------------------------------------------------|

| ACKN | IOWLEDGEMENTS iv                                      |

| ABST | RACTvi                                                |

| LIST | OF TABLES xii                                         |

| LIST | OF FIGURES xiii                                       |

| LIST | OF ABBREVIATIONS xviii                                |

| СНАР | TER 1: GENERAL INTRODUCTION1                          |

| 1.1  | DISSERTATION INTRODUCTION                             |

| 1.2  | DISSERTATION OVERVIEW                                 |

| СНАР | TER 2: SIC: PROPERTIES AND ELECTRONIC DEVICES         |

| 2.1  | SIC MATERIAL PROPERTIES                               |

| 2.2  | SIC CRYSTAL GROWTH                                    |

| 2.3  | THEORETICAL BACKGROUND METAL-SEMICONDUCTOR CONTACT 12 |

| 2.4  | CONCLUSION                                            |

| СНАР | TER 3: DEFECTS IN SIC                                 |

| 3.1  | OVERVIEW                                              |

| 3.2  | POINT DEFECTS                                         |

| 3.3  | MORPHOLOGICAL DEFECTS                                 |

| 3.4  | MORPHOLOGICAL DEFECTS DELINEATION BY ETCHING          |

| 3.5  | Conclusions                                           |

| CHAP | TER 4: DETECTOR FABRICATION AND CHARACTERIZATION 37   |

| 4.1  | 4H-SIC DETECTOR FABRICATION                           |

| 4.2  | ELECTRICAL CHARACTERISTICS OF FABRICATED DETECTOR       | 39  |

|------|---------------------------------------------------------|-----|

| 4.3  | RADIATION INTERACTION WITH SEMICONDUCTOR MATERIALS      | 47  |

| 4.4  | DRIFT-DIFFUSION MODEL                                   | 48  |

| 4.5  | RADIATION DETECTION                                     | 49  |

| 4.6  | ALPHA SPECTROSCOPY MEASUREMENT RESULTS                  | 58  |

| 4.7  | CONCLUSION                                              | 64  |

| CHAP | TER 5: DEFECT CHARACTERIZATION BY DLTS STUDIES          | 65  |

| 5.1  | INTRODUCTION                                            | 65  |

| 5.2  | Defect Parameters                                       | 67  |

| 5.3  | DEFECT CHARACTERIZATION BY THERMALLY STIMULATED CURRENT | 68  |

| 5.4  | THEORETICAL BACKGROUND OF DLTS MEASUREMENT              | 75  |

| 5.5  | DLTS EXPERIMENTAL SETUP                                 | 83  |

| 5.6  | DEFECTS' ROLE ON DETECTOR PERFORMANCE                   | 97  |

| 5.7  | CONCLUSION                                              | 101 |

| CHAP | TER 6: ANNEALING BEHAVIOR OF CRYSTALLINE DEFECTS        | 102 |

| 6.1  | INTRODUCTION                                            | 102 |

| 6.2  | DEEP LEVEL TRANSIENT SPECTRA BEFORE ANNEALING           | 102 |

| 6.3  | EXPERIMENT FOR ISOCHRONAL ANNEALING STUDIES             | 105 |

| 6.4  | ANNEALING STUDIES RESULTS                               | 107 |

| 6.5  | CONCLUSION                                              | 125 |

| CHAP | TER 7: CONCLUSION AND SUGGESTIONS FOR FUTURE WORK.      | 127 |

| 7.1  | CONCLUSION                                              | 127 |

| 7.2  | FUTURE WORK                                             | 129 |

| REFE | RENCES                                                  | 132 |

# LIST OF TABLES

| Table 2.1. Comparisons of properties of selected important materials at 300 K [35]9    |

|----------------------------------------------------------------------------------------|

| Table 4.1. I-V characteristics parameters of the Schottky detector                     |

| Table 5.1. Trap parameters deduced from TSC measurements [86]    72                    |

| Table 5.2. Trap parameters by TSC measurements for the 4H-SiC n-type epilayer [92]. 74 |

| Table 5.3. Defect parameters of the deep levels for the detector AD06                  |

| Table 5.4. Defect parameters of the detector AS1 obtained from the DLTS scans          |

| Table 5.5. Defect parameters of the detector AS2 obtained from the DLTS scans          |

| Table 5.6. Defect parameters of the detector AS3 obtained from the DLTS scans          |

| Table 5.7. Detector properties and defect parameters for the detector AS1       99     |

| Table 5.8. Detector properties and defect parameters for the detector AS2              |

| Table 5.9. Detector properties and defect parameters for the detector AS3              |

| Table 5.10. Detector properties and defect parameters for the detector AD06 100        |

| Table 6.1. Defect Parameters Obtained from the DLTS Measurements.    104               |

| Table 6.2. Defect parameters obtained after annealing at 100 °C 115                    |

| Table 6.3. Defect parameters after annealing at 200 °C    116                          |

| Table 6.4. Defect parameters after annealing at 400 °C 117                             |

| Table 6.5. Defect parameters after annealing at 600 °C 118                             |

| Table 6.6. Defect parameters after obtained annealing 800 °C 119                       |

# LIST OF FIGURES

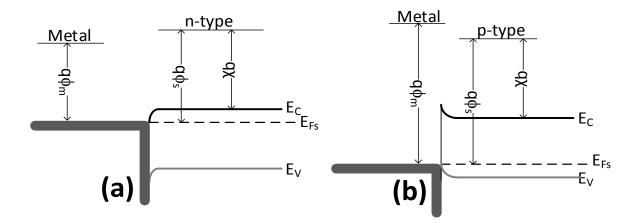

| Figure 2.1. Energy band diagram of metal-semiconductor Ohmic contact: (a) Metal and n-type semiconductor; (b) Metal and p-type semiconductor                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2. Energy band diagram of metal-semiconductor Schottky contact; (a) Metal and n-type semiconductor; (b) Metal and p-type semiconductor                                                                                  |

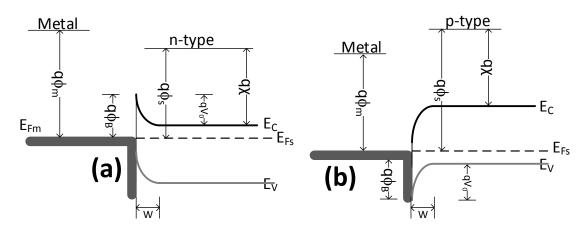

| Figure 2.3. Transport process in a forward biased Schottky barrier                                                                                                                                                               |

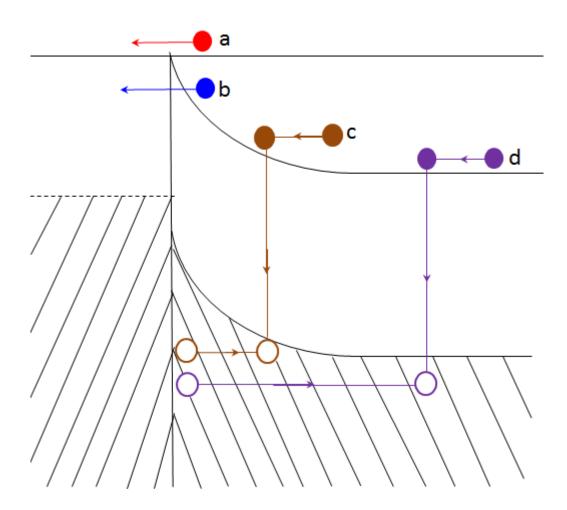

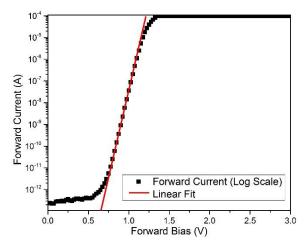

| Figure 2.4. Linear fit of current-voltage (I-V) acquired data plotted in logarithmic scale22                                                                                                                                     |

| Figure 2.5. Capacitance-voltage data acquired using a Schottky diode                                                                                                                                                             |

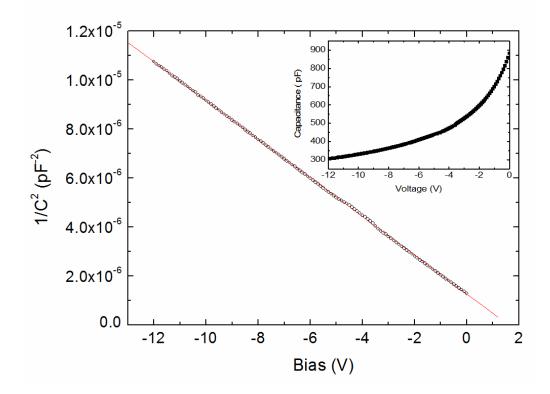

| Figure 2.6. $1/C^2$ vs. reverse bias plot with linear fitting. Variation of $1/C^2$ as a function of reverse bias corresponding to the C-V plot shown in above . The straight line shows the linear fit of the experimental data |

| Figure 3.1. SEM image of the molten KOH etched bulk SiC: (a) Region with TSDs and TEDs; (b) Regions with BPDs and TEDs                                                                                                           |

| Figure 3.2. SEM images of the molten KOH etched bulk SiC: (a) Region with TSDs and TEDs; (b) Enlarge images of micropipes; (C) ) Enlarge images of closed core and threading edge dislocations                                   |

| Figure 3.3. (a) SEM images of the molten KOH etched SiC epitaxial layers; (b) Enlarged images of closed core and threading edge dislocations                                                                                     |

| Figure 4.1. Photograph of an n-type 4H-SiC epitaxial layer wafer                                                                                                                                                                 |

| Figure 4.2. Schematic diagram of the cross-sectional view of 50µm thick n-type 4H-SiC<br>Schottky barrier device                                                                                                                 |

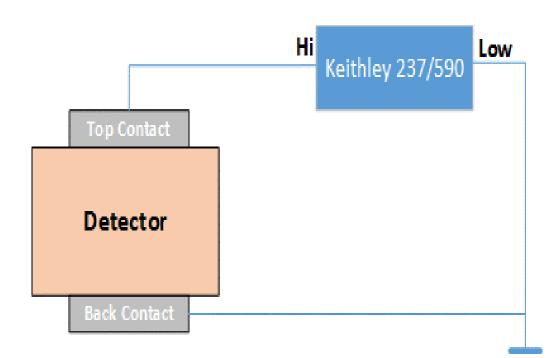

| Figure 4.3. Schematic of the I-V and C-V experimental setup                                                                                                                                                                      |

| Figure 4.4. Photograph of the experimental setup for the I-V and C-V measurements. The detector is mounted inside the aluminum box                                                                                               |

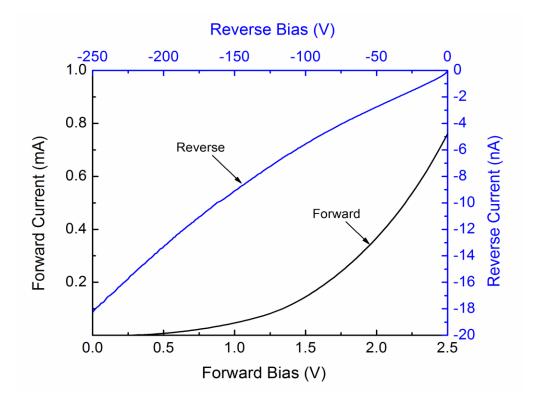

| Figure 4.5. Variation of junction current as a function of applied bias for a 50 µm n-type Ni/4H-SiC epitaxial Schottky barrier radiation detector                                                                               |

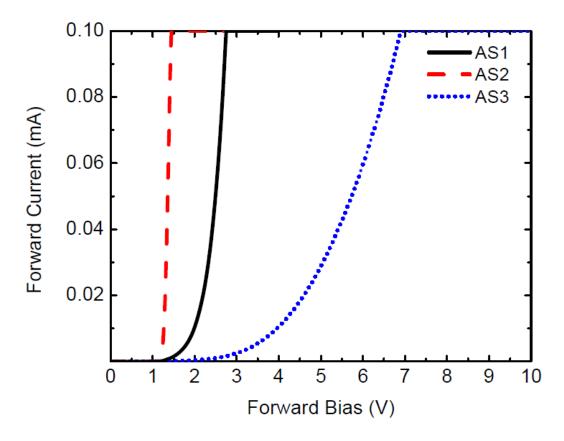

| Figure 4.6. Forward I-V characteristics on 4H-SiC epitaxial Schottky barrier detectors AS1, AS2, and AS3                                                                                                                         |

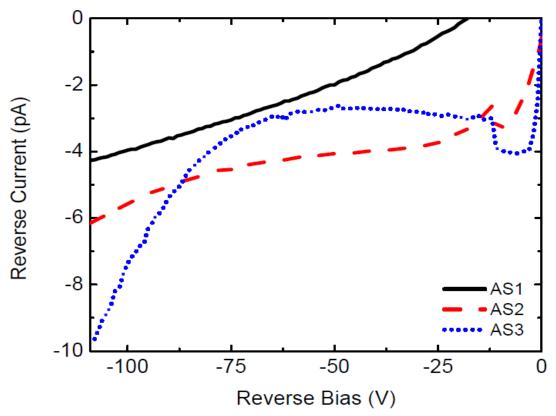

| Figure | 4.7. Reverse I-V characteristics obtained for 4H-SiC epitaxial Schottky barrier detectors AS1, AS2, and AS3                                                                                                                                              |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 4.8. $1/C^2$ vs V plot for a 50 $\mu$ m n-type Ni/4H-SiC epitaxial Schottky barrier detector. The open circles are the experimental data points and the solid line is a straight line fit to the experimental data. Inset shows the original C-V plot 45 |

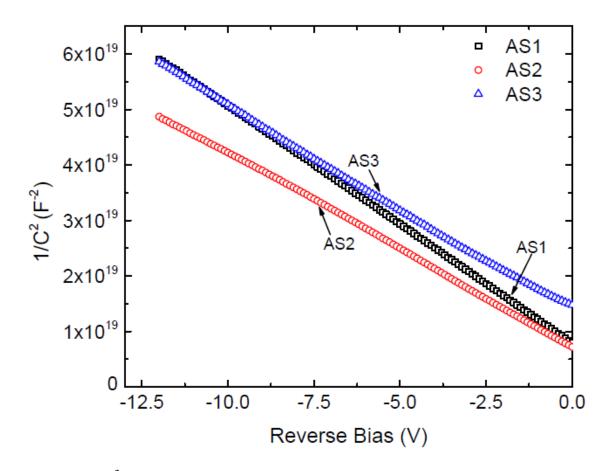

| Figure | 4.9. 1/C <sup>2</sup> vs V plots for 4H-SiC epitaxial Schottky barrier radiation detectors AS1, AS2, and AS3                                                                                                                                             |

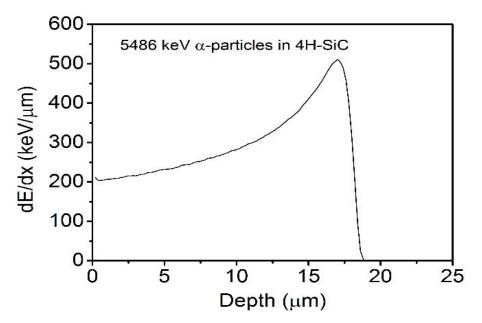

| Figure | 4.10. Energy loss of 5.48 MeV alpha particle as a function of penetration depth. 48                                                                                                                                                                      |

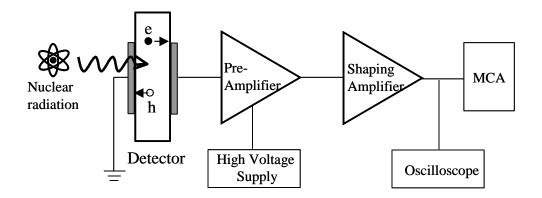

| Figure | 4.11. Schematic diagram of an analog radiation detection measurement system. 50                                                                                                                                                                          |

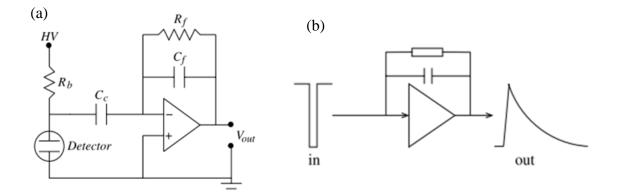

| Figure | 4.12. (a) Simplified circuit diagram for a charge sensitive preamplifier used in a detection system. (b) Input and output pulse shapes seen by a preamplifier [7] 51                                                                                     |

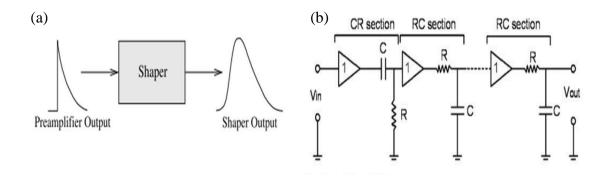

| Figure | 4.13. (a) Typical input and output pulse shapes seen by a shaping amplifier. (b) Simplified circuit diagram for the various stages of differentiation (CR) and integration (RC) used by an analog shaping amplifier [81]                                 |

| Figure | 4.14. Photograph of the 4H-SiC epitaxial Schottky barrier radiation detector inside RFI/EMI shielded test box                                                                                                                                            |

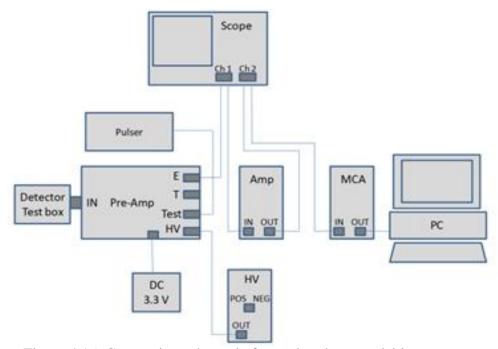

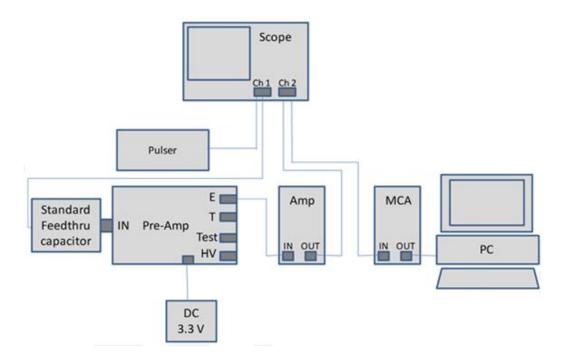

| Figure | 4.15. Connection schematic for analog data acquisition set-up                                                                                                                                                                                            |

| Figure | 4.16. Schematic of the electrical connections for energy calibration                                                                                                                                                                                     |

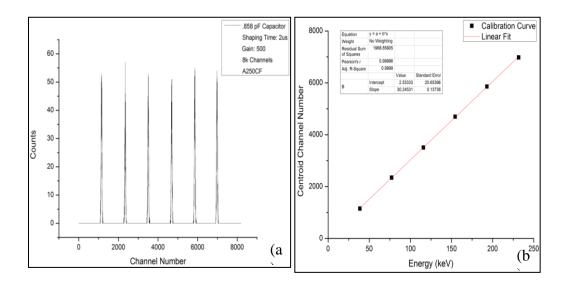

| Figure | 4.17. (a) Pulse-height spectrum obtained for six different pulse sizes, and (b)<br>Corresponding calibration curve                                                                                                                                       |

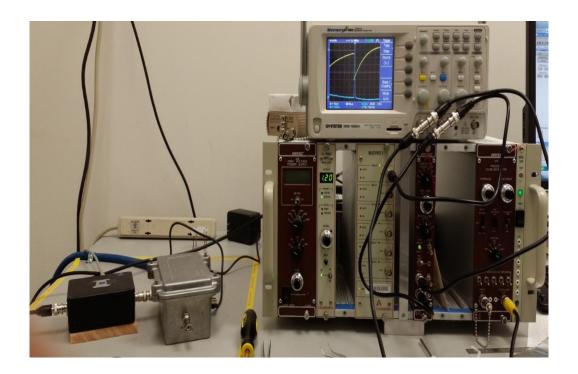

| Figure | 4.18. Picture of the radiation detection system at USC                                                                                                                                                                                                   |

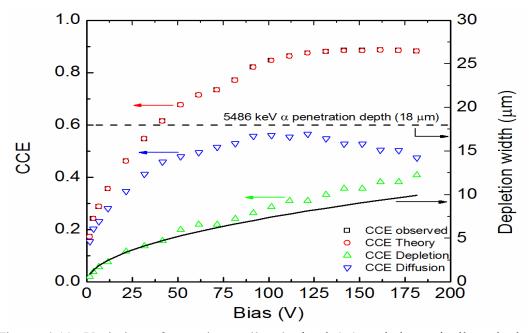

| Figure | 4.19. Variation of experimentally obtained $(\Box)$ and theoretically calculated $(\circ)$ CCE. CCE from drifts ( $\Delta$ ) and diffusion ( $\nabla$ ) are also shown. The solid line shows the variation in depletion width                            |

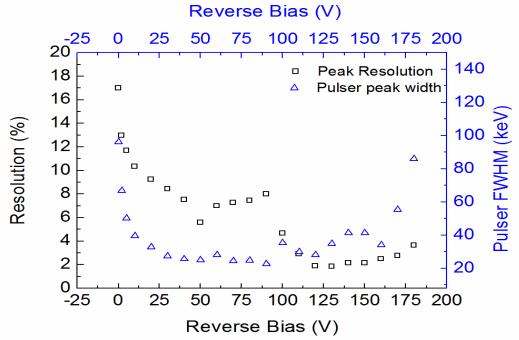

| Figure | 4.20. Variation of detector energy resolution as a function of reverse bias voltage.<br>The variation of the peak width (FWHM) of the pulser recorded simultaneously<br>has also been plotted                                                            |

| Figure | 4.21. An <sup>241</sup> Am pulse-height spectrum obtained using the 50 $\mu$ m n-type Ni/4H-SiC epitaxial Schottky barrier detector reverse biased at 130 V                                                                                              |

| Figure | 4.22. Alpha pulse-height spectra obtained for detectors (a) AS1, (b) AS2,and (c) AS3 using an <sup>241</sup> Am source                                                                                                                                   |

| Figure | 5.1. Illustration of electron and hole trapping and de-trapping phenomena in a semiconductor material                                                                                                                                                    |

| Figure 5.2. TSC spectrum showing trap centers at temperatures $Tm_1$ and $Tm_2$ . [85] 6                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.3. Schematic of the TSC experimental setup7                                                                                                                                                                                                      |

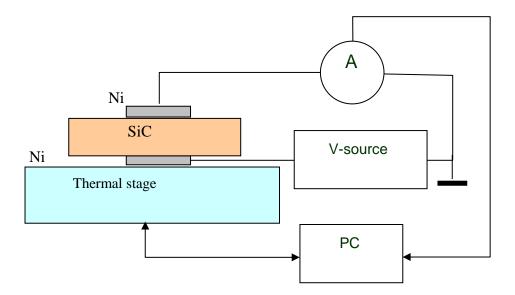

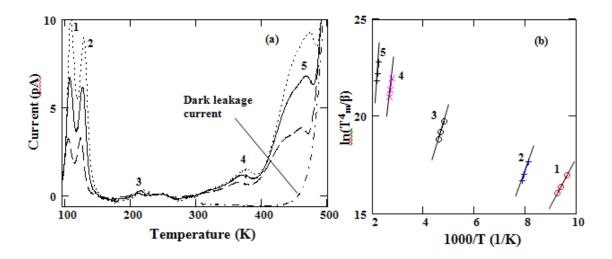

| Figure 5.4. TSC spectra for the heat rates of 5 K/min (), 10 K/min (), and 15 K/min () at 10 V bias voltage. (b): Arrhenius plot of ln $(T_m^4/\beta)$ versus 1000/T for five traps corresponding to peak numbers $1 - 5$ in Figure (a)                   |

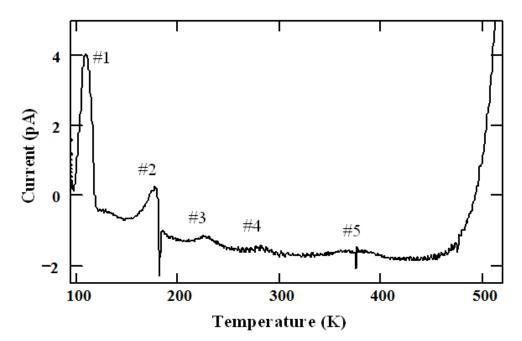

| Figure 5.5. TSC spectrum of n-type 4H-SiC epitaxial layer obtained at 10 V reverse bias<br>and 15 K/min heat rate [92]7                                                                                                                                   |

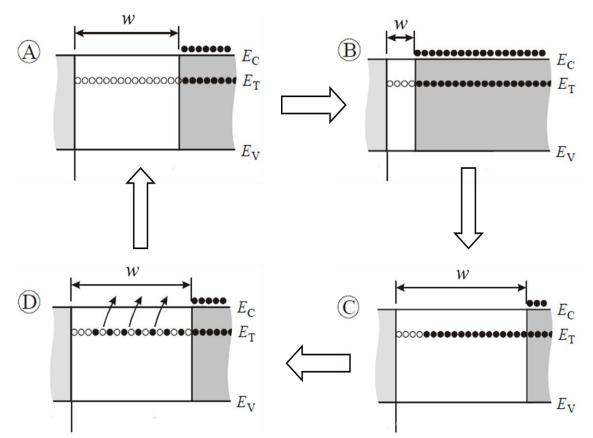

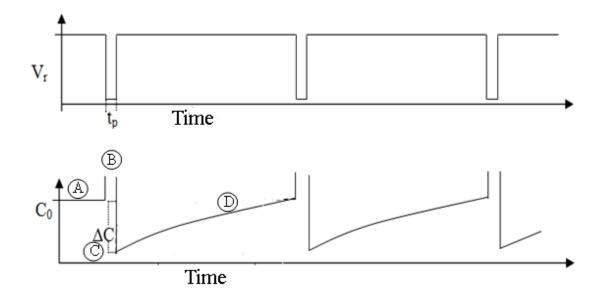

| Figure 5.6. A schematic of the DLTS transient signal generation. (A): Steady state<br>reverse bias, (B): Applying pulse; (C) Just after removing pulse; (D) Capacitance<br>transient due to thermal emission of carriers                                  |

| Figure 5.7. The applied bias and the capacitance change of the Schottky device as a function of time                                                                                                                                                      |

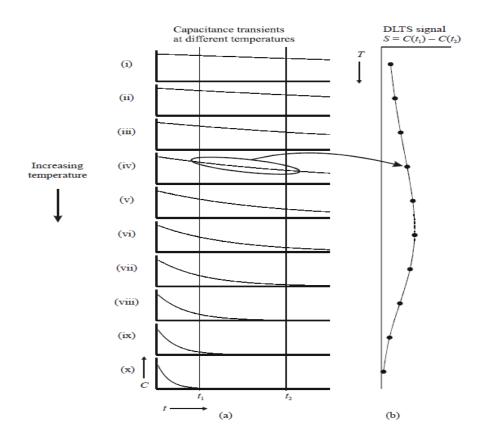

| Figure 5.8. (a) Capacitance transient at various temperature (b) DLTS signal obtained by using double boxcar is plotted as a function of sample temperature [14]                                                                                          |

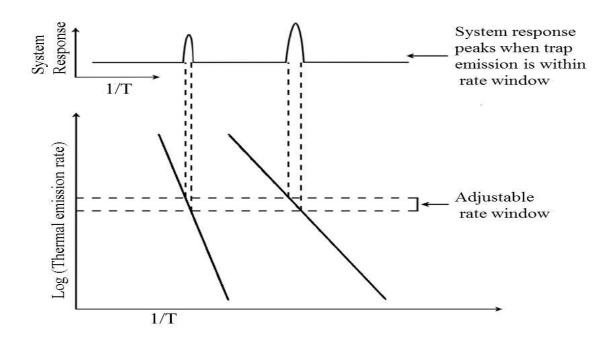

| Figure 5.9. An illustration of how a rate window produces a peak in its response when th emission rate of the input signal matches the rate selected by the window [14]8                                                                                  |

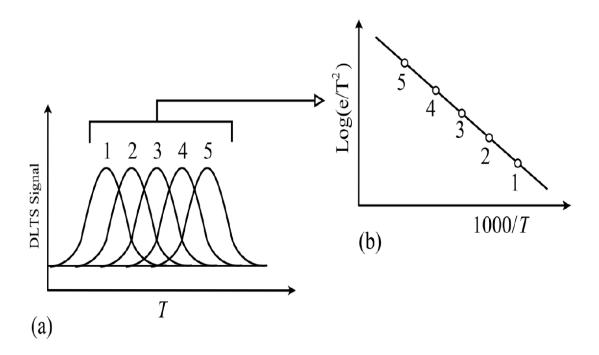

| Figure 5.10. (a) The DLTS spectra corresponding to a trap center at various rate window and (b) the Arrhenius plots obtained from the spectra                                                                                                             |

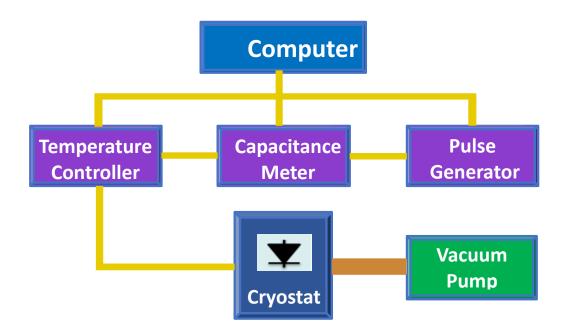

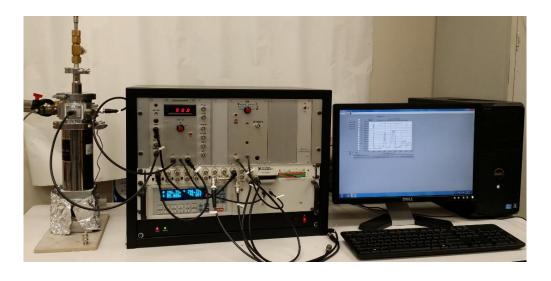

| Figure 5.11. Block-Diagram of the SULA DDS-12 DLTS setup                                                                                                                                                                                                  |

| Figure 5.12. Photograph of the SULA DDS-12 DLTS measurement system                                                                                                                                                                                        |

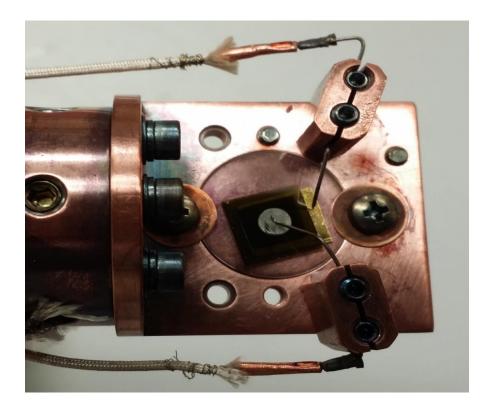

| Figure 5.13. Photograph of the sample holder used in DLTS measurements                                                                                                                                                                                    |

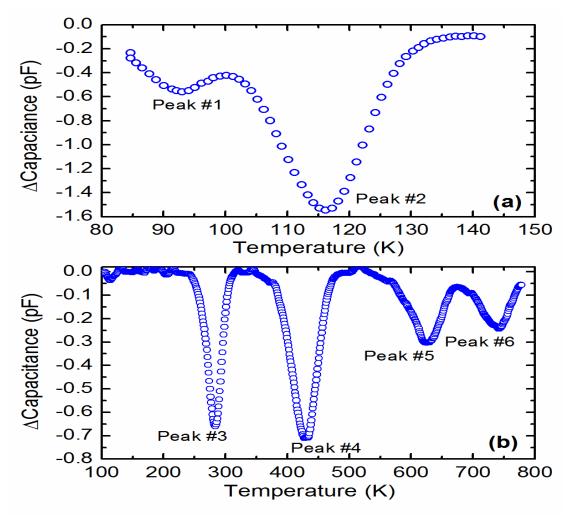

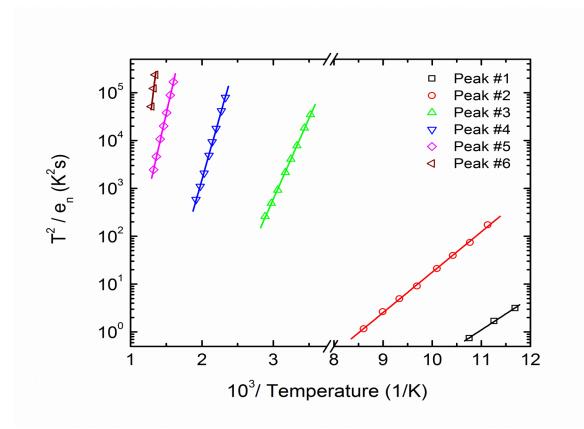

| Figure 5.14. DLTS spectra obtained using the 50 μm n-type Ni/4H-SiC epitaxial<br>Schottky barrier radiation detector (AD06) in a temperature range (a) 80 K - 140<br>K with the smallest initial delay (b) 80 K - 800 K with the largest initial delay. 8 |

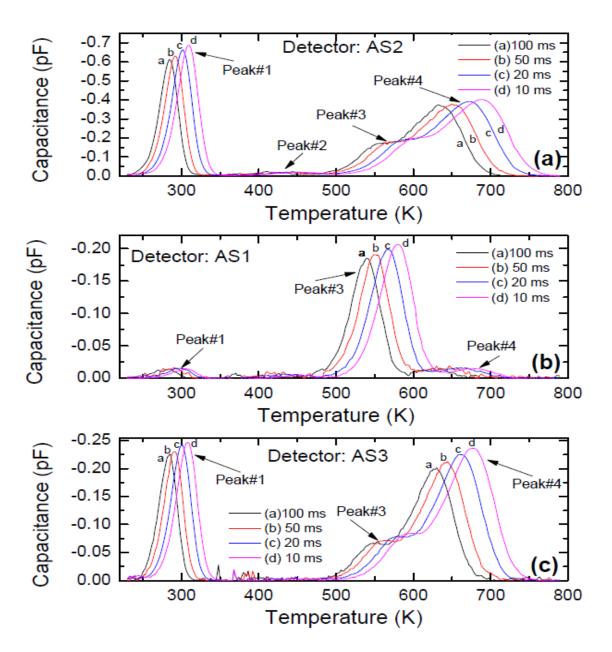

| Figure 5.15. DLTS scan for detectors AS2, AS1, and AS3 showing negative peaks relate<br>to electron traps present in the 4H-SiC epilayer detectors                                                                                                        |

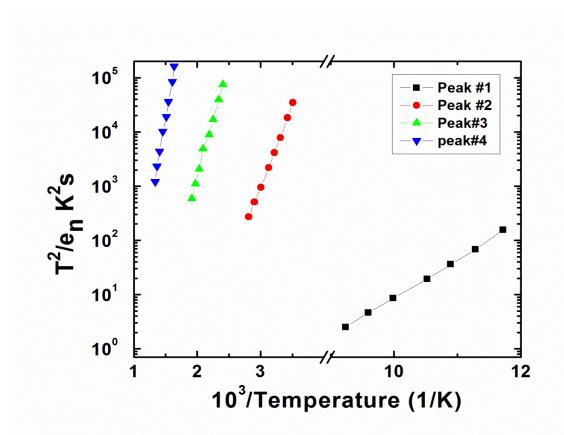

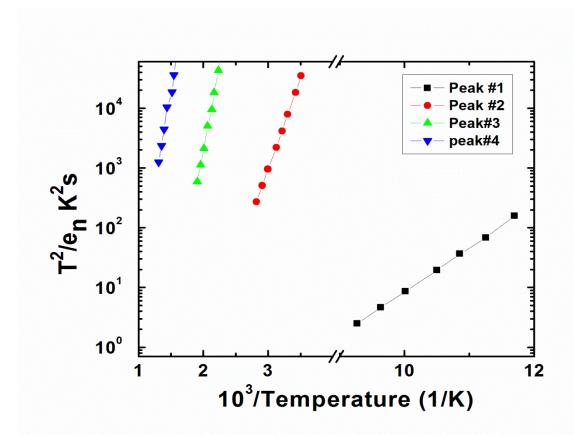

| Figure 5.16. Arrhenius plots obtained for the Peaks #1 - #6 corresponding to the DLTS spectra shown inFigure 5.14                                                                                                                                         |

| Figure 5.17. Arrhenius plots for determining the activation energy obtained from the DLTS scans shown in Figure 5.15 for detectors (a) AS2, (b) AS1, and (c) AS3.The solid lines show the linear fits                                                     |

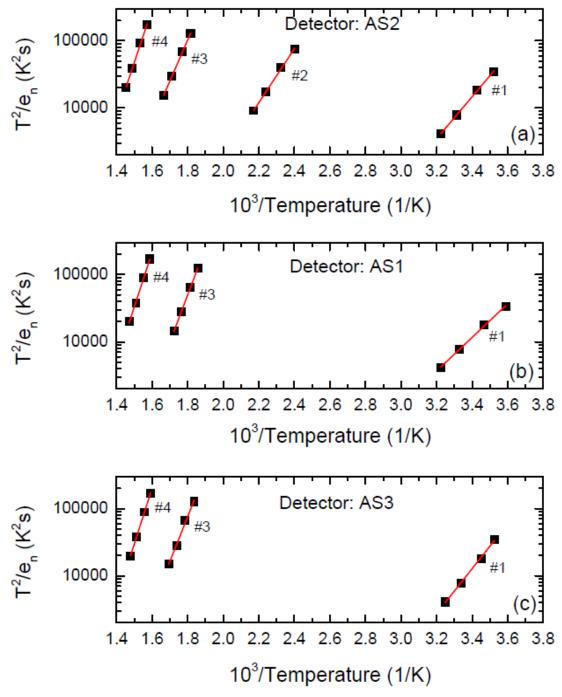

| Figure 6.1. DLTS spectra obtained using the 50 μm thick n-type Ni/4H-SiC unannealed epitaxial Schottky barrier in the temperature range: (a) 85 K - 130 K with a                                                                                          |

|        | smaller set of initial delays, and (b) 200 K - 800 K with a larger set of initial delays                                                                                                                                                        |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

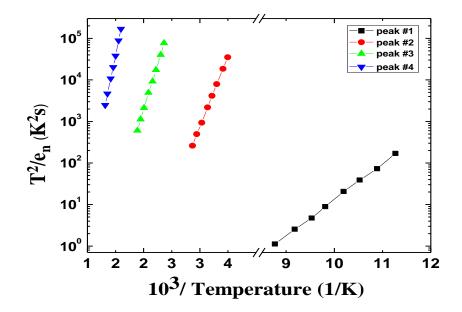

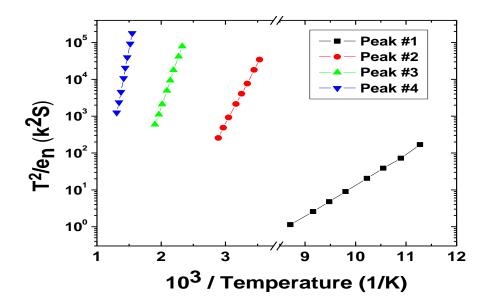

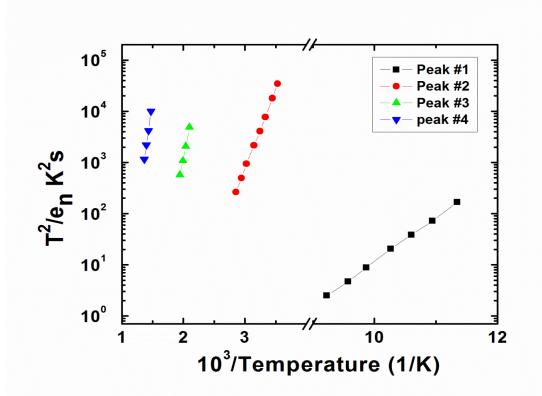

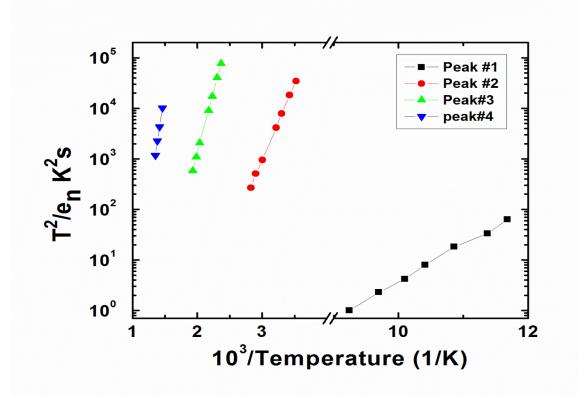

| Figure | 6.2. Arrhenius plots obtained for the peaks #1 - #4 corresponding to the DLTS spectra shown                                                                                                                                                     |

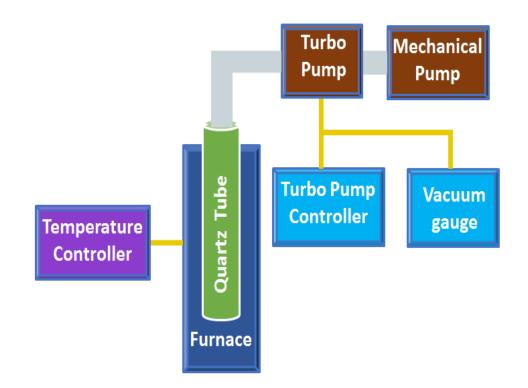

| Figure | 6.3. Block diagram of annealing set up at USC 105                                                                                                                                                                                               |

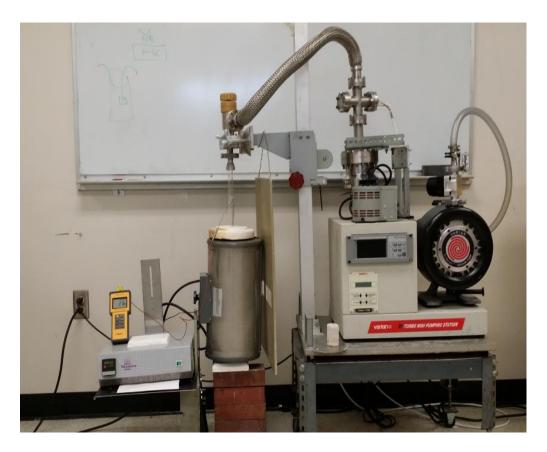

| Figure | 6.4. Picture of the annealing set up at USC 106                                                                                                                                                                                                 |

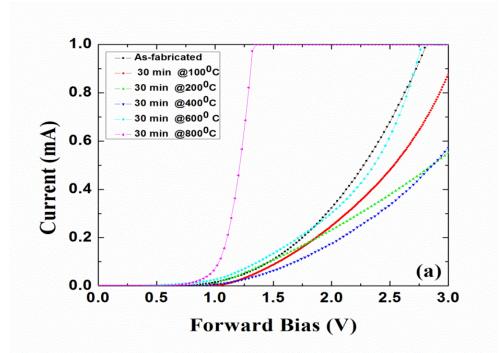

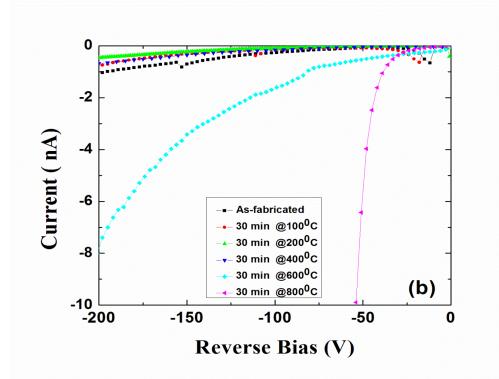

| Figure | 6.5. Forward current voltage (I-V) characteristics of the as-fabricated 50 μm thick<br>n-type 4H-SiC Schottky barrier and after isochronal annealing at different<br>temperatures:                                                              |

| Figure | 6.6. Reverse current voltage (I-V) characteristics of the as-fabricated 50 μm thick<br>n-type 4H-SiC Schottky barrier and after isochronal annealing at different<br>temperatures:                                                              |

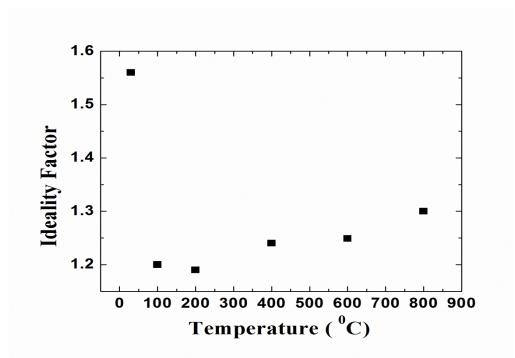

| Figure | <ul><li>6.7. Variation of ideality factors with isochronal annealing of 50 μm thick n-type</li><li>4H-SiC Schottky barrier device.</li></ul>                                                                                                    |

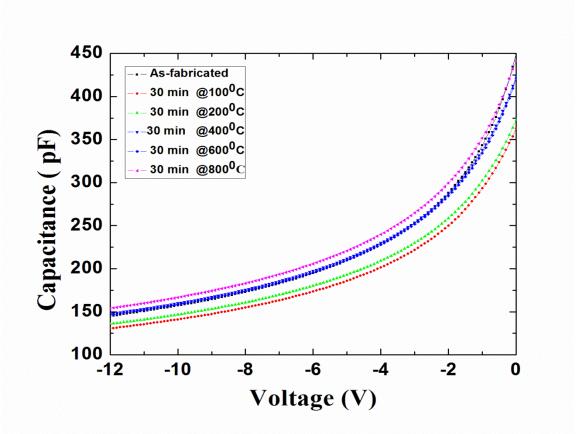

| Figure | 6.8. Capacitance vs voltage of the as-fabricated 50 μm thick n-type 4H-SiC Schottky barrier and after isochronal annealing at different temperatures 111                                                                                        |

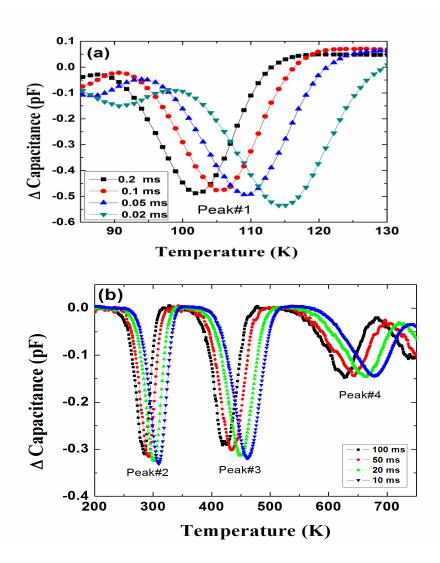

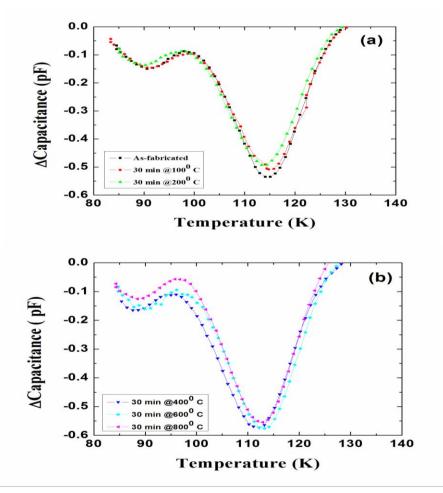

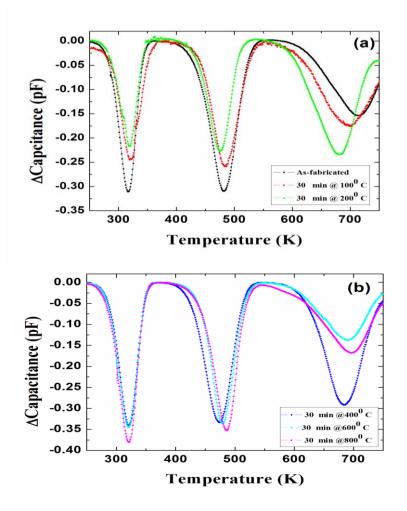

| Figure | 6.9. DLTS spectra obtained using the 50 μm thick n-type Ni/4H-SiC epitaxial Schottky barrier in a temperature range 80 K - 140 K: (a) as-fabricated, annealed at 100 °C and 200 °C; and (b) annealed at 400 °C, 600 °C, and 800 °C respectively |

| Figure | 6.10. DLTS spectra obtained in a temperature range 250 K - 750 K: (a) as-<br>fabricated and annealed at 100 °C and 200 °C; and (b) annealed at 400 °C, 600 °C,<br>and 800 °C                                                                    |

| Figure | 6.11. Arrhenius plot corresponding to the DLTS spectra obtained after annealing at 100 °C                                                                                                                                                       |

| Figure | 6.12. Arrhenius plots corresponding to the DLTS spectra obtained after annealing at 200 °C                                                                                                                                                      |

| Figure | 6.13. Arrhenius plots corresponding to the DLTS spectra obtained after annealing at 400 °C                                                                                                                                                      |

| Figure | 6.14. Arrhenius plots corresponding to the DLTS spectra obtained after annealing at 600 °C                                                                                                                                                      |

| Figure | 6.15. Arrhenius plot corresponding to the DLTS spectra obtained after annealing at 800 °C                                                                                                                                                       |

- Figure 6.17. Defect  $Z_{1/2}$  (corresponding to peak #2,  $E_c 0.67 \text{ eV}$ ) parameters variation with annealing temperature: (a) capture cross-section, and (b) defect density... 122

- Figure 6.18. Defect EH<sub>5</sub> (corresponding to peak #3, E<sub>c</sub> 1.03 eV) parameters variation with annealing temperature: (a) capture cross-section, and (b) defect density... 124

- Figure 6.19. Defect EH<sub>6/7</sub> (corresponding to peak #4, E<sub>c</sub> 1.6 eV) parameters variation with annealing temperature: (a) capture cross-section, and (b) defect density... 125

# LIST OF ABBREVIATIONS

| BPDs  | Basal Plane Dislocations                     |

|-------|----------------------------------------------|

| CVD   | Chemical Vapor Deposition                    |

| DLTS  | Deep Level Transient Spectroscopy            |

| EBIC  | Electron Beam Induced Current                |

| FWHM  | Full Width at Half Maxima                    |

| HEMT  | High Electron MobilityTtransistor            |

| keV   | Kilo Electron Volt                           |

| LPE   | Liquid Phase Epitaxy                         |

| MeV   | Mega Electron Volt                           |

| MCA   |                                              |

| MBE   | Molecular Beam Epitaxy                       |

| PICTS | Photo Induced Current Transient Spectroscopy |

| SEM   | Scanning Electron Microscopy                 |

| TSC   | Thermally Stimulated Current                 |

| TED   |                                              |

#### **CHAPTER 1: GENERAL INTRODUCTION**

#### 1.1 DISSERTATION INTRODUCTION

The perfect crystal, described in any introductory solid state book, is rare to find in nature. Many things, such as impurities, vacancies, broken bonds, lattice strain and stress, are responsible for imperfections in the crystal. Imperfect crystals are due to the introduction of impurities which are desirable in a vast area of solid state application. Hence, adding impurities in a controlled way (doping) is very important for successful device fabrication. However, in many cases the presence of impurities and other imperfections affect the semiconductor properties in an undesired way which is detrimental for the device performance. Therefore, the nature of the defects and their impact on carrier transport are crucial for device fabrication.

Imperfection in crystal structure arises mainly due to the structural defects, impurities, and vacancies. Structural defects are created due to lattice strain during material growth and processing which gives rise to stacking faults and dislocations. Impurities, either intentionally or inadvertently introduced, disturb the lattice periodicity by substituting native crystal atoms or forming complexes [1]. Vacancies, i.e. missing atoms from their regular atomic site, are formed during solidification of the crystal which disturbs the periodic structure of the crystal. The impurity and vacancy induced defects are known as point defects which create localized energy levels in the energy band-gap. Semiconductor electrical and optical properties strongly depend upon these defects' energy levels, their concentration, and nature.

On the basis of energy level location in the band-gap, the defects are classified as shallow and deep levels. Shallow levels are located near the band edges of the conduction band or valence band of the semiconductor. Substitutional impurities mainly introduce shallow levels and are used for doping to control the electrical conductivity, mobility, and resistivity of the semiconductor. Deep levels located further away from the band edges may originate from impurities, vacancies or structural defects. Their contribution to conduction is negligibly small compared to shallow levels. However deep levels may act as generation or recombination centers and can control the lifetime of the charge carriers. Consequently, optical and electrical characteristics of semiconductor devices are greatly influenced by electrically active deep level defects. It is proven that deep level defects affect the detector performance [2], degrade solar cell performance and reduce hetero-junction laser efficiency [3].

Both theoretical and experimental attempts have been made to characterize the deep level defects of semiconductors. Many techniques have been employed to develop a suitable theory for deep levels. In perturbative method the Hamiltonian and corresponding Eigen value problem is solved by assuming a perturbative potential introduced by the defect. By using this method, Jaros *et al.* calculated substitutional oxygen impurity in GaP [4], and Baraff *et al.* depicted vacancy related defects in Si [5,

6]. This approach suffers from convergence problems. In non-perturbative method, the eigenvalue problem is solved by assigning a single potential function to a cluster of atoms. Sulfur related defects in Si are calculated by this method which is in good agreement with experimental results [7]. Calculation based on this method is flawed by surface states and impurities in the crystal. Density Functional Theory (DFT) based *ab* initio calculations are used in several approaches to calculate vacancies and antisite related defects for wide band-gap materials [8]. Each theoretical method for deep level defect calculation is based on its own specific assumption which usually makes the method only suitable for a particular type of impurity and semiconductor.

Experimental characterization of deep level defects, such as temperature dependence of Hall effect, photoconductivity, electroluminescence etc, involve thermal or optical excitation to fill the defect center and subsequent de-excitation. In 1966 Williams first conducted a junction based experiment to investigate the deep level impurities located in the space charge region [9]. In junction based method, the experimental measurement is done either by static or dynamic technique. In static measurement, the current or capacitance is recorded as a function temperature such as thermally stimulated current [10] and thermally stimulated capacitance [11]. On the other hand, in dynamic technique, the capacitance or current transient is measured at different temperatures during the defect relaxation to equilibrium after a perturbation. In Deep Level Transient Spectroscopy (DLTS) [12, 13, 14] the excitation is done by electrical pulse, and in Photo Induced Current Transient Spectroscopy (PICTS) [15, 16], the excitation is done by optical signal.

DLTS is considered one of the most powerful equipment used for semiconductor defect characterization. DLTS is widely used to investigate deep level defects of different material such as Si [17], GaAs [18], GaN [19, 20], NiSi<sub>2</sub> precipitates in silicon [21], CZTS [22] etc. Besides Schottky diodes DLTS measurements also have been done on solar cells [23], high electron mobility transistors (HEMTs) [24], quantum wells [25, 26] etc. Presently, DLTS equipment is considered an essential tool in semiconductor fabrication and processing technology due to its wide application, sensitivity to lower defect concentration, and capability of determining most defect parameters.

#### 1.2 DISSERTATION OVERVIEW

This work focuses on DLTS investigation of deep levels in the epitaxial layers of 4H-SiC wide band-gap materials and the correlation of defects with detectors fabricated on 4H-SiC epitaxial layers.

Chapter 1 is an introductory chapter to describe the background, importance, and organization of this work. The whole study related to this work is described in seven chapters.

Chapter 2 is an introduction to SiC material properties, growth, and a brief description of SiC based devices. Junction theory of metal-semiconductor Schottky contact and Ohmic contact is also explained in this chapter.

Chapter 3 is a description of SiC extended and point defects. This chapter also discusses the etching studies to delineate different extended defects.

Chapter 4 is dedicated to detector fabrication based on the epitaxial layer of 4H-SiC and in detailed characterization of the fabricated detectors. Current-Voltage (I-V) and Capacitance-Voltage (C-V) measurement technique, Alpha spectroscopy measurement technique, and the results obtained are discussed here.

Chapter 5 is an introduction to defect characterization by different techniques. Basic principles of thermally stimulated current (TSC) and results obtained by TSC measurements are described. The detailed background description of DLTS technique, the experimental setup and results obtained in this work are explained in this chapter. The experimental results are analyzed by comparing with previously reported data. The correlation between deep level defects and detector performance are discussed in this chapter.

Chapter 6 is dedicated to describing the annealing behavior of the deep levels in 4H-SiC epitaxial layers. Isochronal annealing impact on the defect parameters of each individual defect is described in this chapter.

Finally, Chapter 7 concludes the research presented in this dissertation and provides suggestions for future work.

#### CHAPTER 2: SIC: PROPERTIES AND ELECTRONIC DEVICES

#### 2.1 SIC MATERIAL PROPERTIES

Silicon carbide is an indirect wide band-gap semiconductor. SiC is thermally stable up to about 2000 °C, even in oxidizing and aggressive environments. SiC is one of the most intensively studied materials among all the other wide band-gap semiconductors. The Swedish scientist Jons Jakob Berzelius first discovered silicon carbide in 1824 [27]. Since then silicon carbide has been commercialized as an abrasive due its extreme hardness (~ 9.5 in Mohs scale). Silicon carbide is also used for fireproofing, high-temperature ceramics, and resistive heating elements. After discover of its rectifying properties, silicon carbide crystal detectors were used in the early days of radio communications. Around the 1940s, silicon carbide was abandoned as a semiconductor material with the emergence of silicon based semiconductor technology. In the late 1970s, silicon carbide was in focus as a suitable semiconductor material for blue light emitting diode, but soon it was replaced by group III-nitride wide band-gap direct semiconductor. The main bottle neck of spreading silicon carbide technology is difficulty in producing good quality crystals. However, the availability of high quality silicon carbide crystal with the advanced semiconductor technology and the necessity of suitable high power electronic device materials prompted the commercialization of silicon carbide devices in the beginning of the 21<sup>st</sup> century.

Silicon carbide crystal lattice is structured from closely packed silicon-carbon bilayers (also called Si-C double layers). Si-C bilayer can be viewed as a planar sheet of silicon atoms coupled with a planar sheet of carbon atoms. Due to the sequential variation of these stacked bilayers silicon carbide has many crystal structures. This property is known as polytypism. Polytypes represent different staking sequences of atomic planes in one certain direction. The staking sequence causes hexagonal and cubic lattice sites in the crystal structure. The different layers are usually designated by the letter A, B, and C. To specify the cubic, hexagonal and rhombohedral symmetry of the crystal lattice the letters C, H and R are used, respectively [28]. The repetition number of bilayers in the stacking sequence is expressed by an integer number. From the side view, the staking sequence of SiC crystal shows a zig-zag pattern which terminates with a silicon face on a surface and with carbon atoms on the opposing surface.

Different polytypes vary from each other only in the stacking sequence of double layers of Si and C atoms. However, due to this difference in staking sequence, the optical and electrical properties such as band-gap, saturated drift velocity, breakdown electric field strength, and the impurity ionization energies vary significantly from polytype to polytype [29, 30, 31]. Even for a given polytype, some electrical properties are shown non-isotropic behavior and have strong dependency on the crystallographic direction. Among all of the existing polytypes, the following are the most common:

- 2H This is a wurtzite structure with the stacking sequence AB and has hexagonal symmetry. Growth of this polytype is difficult and did not receive any attention.

- 3C Here the stacking repeats itself every three bilayers. This polytype is cubic zinc blende structure with the stacking sequence ABC.

- 4H This polytype has wurtzite structure with the stacking sequence ABAC and has hexagonal symmetry. It has 50% cubic and 50% hexagonal lattice sites and most intensively studied poly-type for power electronic devices.

- 6H It has the stacking sequence ABCACB and contains 2/3 cubic and 1/3 hexagonal lattice sites. 6H polytype has more pronounced anisotropy compared to 4H silicon carbide.

Among different polytypes, 4H-SiC is usually preferred for electronic devices due to its better charge transport properties [32, 33, 34]. However, any promising semiconductor properties are usually evaluated against silicon due to its wide market share in the solid state technology. The comparison of the properties of 4H-SiC with other commonly used semiconductor is shown in Table 2.1 [35]. From the table, it is apparent that 4H-SiC is superior to silicon for the device material where wide bandgap energy, high breakdown electric field, high carrier saturation drift velocity, and high atom displacement energy are expected.

#### 2.2 SIC CRYSTAL GROWTH

The SiC based electronic and optoelectronic device performances highly depend upon the improvement of bulk crystal and epitaxial growth technology. SiC does not show a liquid

phase and the only way to grow, synthesize, and purify silicon carbide is by means of gaseous phases. For the growth of electronic-grade silicon carbide the most common techniques are:

| -                                                                              |       |       | -     |       |       |        |

|--------------------------------------------------------------------------------|-------|-------|-------|-------|-------|--------|

| Properties/Material                                                            | $D^*$ | Si    | Ge    | GaAs  | CdTe  | 4H-SiC |

| Bandgap (eV)                                                                   | 5.5   | 1.12  | 0.67  | 1.42  | 1.49  | 3.27   |

| Relative dielectric constant                                                   | 5.7   | 11.9  | 16    | 13.1  | 10    | 9.7    |

| Breakdown field<br>(MV cm <sup>-1</sup> )                                      | 10    | 0.3   | 0.1   | 0.4   | 0.5   | 3.0    |

| Density ( g cm <sup>-3</sup> )                                                 | 3.5   | 2.3   | 5.33  | 5.3   | 5.9   | 3.2    |

| Atomic number Z                                                                | 6     | 14    | 32    | 31-33 | 48-52 | 14-6   |

| e-h creation energy (eV)                                                       | 13    | 3.6   | 2.95  | 4.3   | 4.42  | 7.78   |

| Saturation electron velocity ( $\times 10^7$ cm <sup>2</sup> s <sup>-1</sup> ) | 2.2   | 1.0   | 0.6   | 1.2   | 1.0   | 2      |

| Electron mobility $(cm^2 V^{-1} S^{-1})$                                       | 1800  | 1300  | 3900  | 8500  | 1100  | 800    |

| Hole mobility<br>( $cm^2 V^{-1} S^{-1}$ )                                      | 1200  | 460   | 1900  | 400   | 100   | 115    |

| Threshold displacement<br>energy (eV)                                          | 40-50 | 13-20 | 16-20 | 8-20  | 6-8   | 22-35  |

| Minimum ionizing<br>energy loss (MeV cm <sup>-1</sup> )                        | 4.7   | 2.7   | 6     | 5.6   |       | 4.4    |

Table 2.1. Comparisons of properties of selected important materials at 300 K [35]

#### D<sup>\*</sup>-Diamond

Physical Vapor Transport (PVT): A solid source of silicon carbide is evaporated at high temperatures and the vapors crystallize at a colder part of the reactor.

Chemical Vapor Deposition (CVD): Gas-phase silicon and carbon containing precursors react in a reactor and silicon carbide is solidified on target.

#### 2.2.1 Bulk Growth

Bulk growth of SiC is the first step for any SiC application. During bulk growth the target is to grow large single crystals in high quantities, and the emphasis placed on achieving a high growth rate. Silicon carbide cannot be grown by seeded solidification from melts because SiC sublimes before it melts. Therefore, the bulk growth is usually done by a method based on physical vapor transport which is known as modified-Lely method [36]. In the modified Lely method, either powder or polycrystalline source materials are sublimed at ~ 2300 °C - 2500 °C in a closed crucible under low-pressure inert gas ambient. The vapor from the sublimation mainly consists of Si, Si<sub>2</sub>C, and SiC<sub>2</sub> from sublimation which migrates and deposits on a monocrystalline SiC seed kept at a lower temperature. The crystal growth parameters such as growth rate uniformity, grown stress in the material, crystalline quality, are dependent on the reactor design. Different approaches have been offered to optimize the reactor design in order to have better control of thermal gradients inside the growth chamber [37]. In every approach, the main focus is always on increasing the diameter of the wafers while at the same time reducing the density of extended material defects such as micropipes and dislocations. At present, 3-inchdiameter substrates are commercially available from multiple vendors [38]. Recently CREE Inc. has presented zero micropipe wafers [39]. In this method of crystal growth, precise doping and uniformity cannot be controlled easily because the evaporation and growth takes place in a closed environment. This fact discourages device fabrication directly on the sublimation grown SiC wafers.

#### 2.2.2 Epitaxial Growth

SiC devices are hardly fabricated directly in sublimation-grown bulk wafers because of low crystal quality. Higher crystalline quality SiC epitaxial layers are needed for SiC electronic applications. The epilayers are more controllable and reproducible than bulk SiC wafer. There are several growth techniques for SiC epitaxial layers including liquid phase epitaxy (LPE), sublimation epitaxy, molecular beam epitaxy (MBE), and chemical vapor deposition (CVD).

Liquid phase epitaxy (LPE) is a technique where the growth of SiC takes place from a supersaturated solution of Si and C at slightly above 1415° C which is the melting temperature of silicon. In LPE, it is difficult to control the surface morphology, doping level, and conductivity type. This method suffers from low carbon solubility in a silicon melt and is used for the healing of micropipe defects and to grow a buffer layer on substrates [35, 40].

Sublimation epitaxy growth mechanism is similar to those for bulk sublimation growth. However compared to bulk, the sublimation epitaxy is grown at lower temperature (1800 °C – 2200 °C) with higher growth pressure (~ 1 atm) [41]. This technique is suitable for thick epitaxial layers with high growth rate.

In molecular beam epitaxy (MBE), the growth rate is very low (order of nanometers per hour) and the growth temperature is also quite low. This technique is usually applied to grow a very thin epitaxial layer for surface science studies [35].

Chemical Vapor Deposition (CVD) is the most promising technique for growing thick epitaxial layers of low and uniform doping concentration with good morphology. In this process, silicon and carbon containing gases are transported to a chamber where chemical reaction occurs and material is deposited on the SiC substrate surface. In a typical SiC-CVD epitaxial process, growth rates up to 50  $\mu$ m h<sup>-1</sup> can be achieved at substrate temperatures of around ~1500 °C. In SiC-CVD process, horizontal hot-wall reactor is used to reach higher growth temperature (up to 2000 °C) with more efficient heating of the substrate [42]. In this technique, the precursor gases are utilize more efficiently, and consequently, a growth rate up to 100  $\mu$ m h<sup>-1</sup> can be achieved.

#### 2.3 THEORETICAL BACKGROUND METAL-SEMICONDUCTOR CONTACT

#### 2.3.1 Overview

Semiconductor junctions are the most important device in solid state technology. Due to the interesting electrical or opto-electrical properties of the junction, numerous opto-electronic devices can be made based on the semiconductor junction. The semiconductor junction can be formed in the following ways:

- a. Junction formed from the joining of p-type and n-type of the same semiconductor called as p-n homojunction.

- b. Junctions made of two different semiconductors with different band-gap, such as GaAs and AlGaAs. These can be p-n junctions or isotype heterojunctions (n-n or p-p).

- c. Junctions created between metals of suitable work function and semiconductors of suitable electron affinity are known as Schottky barriers.

- d. Junctions made of metals and semiconductors that form Ohmic contacts.

All *p-n* junction and Schottky barriers have rectifying characteristics. P-n junctions are widely used in power electronic devices. Schottky diode is preferable for fast response diode and photodetectors. For the defect characterization by DLTS technique, both p-n junction and Schottky diode are suitable. In this study, Schottky diode is used to investigate the defects in 4H-SiC epitaxial layer. The Schottky diodes are fabricated on 4H-SiC epitaxial layer, and Ohmic contact is formed on the bulk side of 4H-SiC. Therefore, it is very important to understand the theoretical concepts behind the formation of Schottky and Ohmic contact. For Schottky contacts, the thermionic emission model was used in order to study the contact properties in SiC diodes in terms of the barrier height and the ideality factor using current-voltage (I-V) measurements. For further characterization of the Schottky contact, the calculation procedure of doping concentration and built-in voltage using capacitance-voltage (C-V) measurements are described.

#### 2.3.2 Ohmic Contact

A metal-semiconductor junction is formed Ohmic contact when it does not show any rectifying characteristics during I-V measurements. The contact simply behaves as a resistor and the current-voltage across the resistance follow a linear relationship. A good Ohmic contact would have negligible contact resistance, small voltage drop even at a large current, and same voltage drop for both forward and reverse current.

Figure 2.1. Energy band diagram of metal-semiconductor Ohmic contact: (a) Metal and n-type semiconductor; (b) Metal and p-type semiconductor.

The metal is characterized by the work function of the metal  $\Phi_m$  (energy required to remove an electron from the Fermi level to the vacuum level), and the semiconductor is characterized by the work function of the semiconductor  $\Phi_s$  (energy required to remove an electron from the Fermi level to the vacuum level). The work function of metal and semiconductor are measured with respect to the vacuum level (the energy of an electron at rest outside the material). Figure 2.1 shows the thermal equilibrium energy band diagram of a metal-semiconductor Ohmic contact for n-type and p-type semiconductor. For Ohmic contact formation the metal work function should be less than the n-type semiconductor work function and greater than the p-type semiconductor work function. In both cases the Fermi levels are aligned between the metal and the semiconductor. The difference between metal Fermi levels and semiconductor Fermi level diminishes at the moment of forming the junction by exchanging charges at the edges of the bands. The energy band diagrams shows that there is no barrier blocks to halt the flow of electrons in the case of metal n-type contact and holes in the case of metal p-type contact. Hence the current can flow through the junction regardless of the polarity of the applied voltage.

The 4H-SiC material used for Schottky diode fabrication can be considered as intrinsic with the energy band-gap of ~3.26 eV at 300K [43] and the work function was calculated to be 4.73 eV using Equation 2.1

$$\phi_s = \chi + \frac{E_g}{2} \tag{2.1}$$

where  $\chi$  is the electron affinity (energy required to remove an electron from the conduction band to the vacuum level), and  $E_g$  is the band-gap. In order to form Ohmic contact, deposited metal work function should be less than 4.73 eV.

#### 2.3.3 Schottky Contact Formation and Energy Band Diagram

A metal-semiconductor contact is called Schottky contact when it has a rectifying effect providing current conduction at forward bias (metal to semiconductor) and presenting a low saturation current at reverse bias (semiconductor to metal). Figure 2.2 shows the Schottky metal-semiconductor contact after thermal equilibrium. In the Schottky model, the vacuum level is assumed to be continuous across the interface and the metal work function and semiconductor electron affinity are assumed to be constant throughout the material right to the interface. In both cases it can be observed that the Fermi levels are aligned between the metal and the semiconductor.

Figure 2.2. Energy band diagram of metal-semiconductor Schottky contact; (a) Metal and n-type semiconductor; (b) Metal and p-type semiconductor.

At the interface itself the vacuum level is same for the two sides such that there is a barrier due to the difference between  $\phi_m$  and  $\chi$ . This difference, the ideal barrier of the junction,  $\phi_B$ , is given by the following equation 2.2

$$q\phi_B = q(\phi_m - \chi) \tag{2.2}$$

The rectifying effect of the Schottky contact is due to the formation of this barrier height ( $q\phi_B$ ) at the junction. So it is important to note that the condition to form a Schottky barrier for a *n*-type semiconductor is is  $\phi_m > \phi_s$  and for p-type semiconductor is  $\phi_m < \phi_s$ . For n-type semiconductor as the distance from the interface increases, the conduction band bends to match with the bulk region value. This band bending builds an electric field which sweeps free electrons from the vicinity of the contact interface and creates fixed positive charge distribution due to ionized donors and thus forms a depletion region (also known as space charge region). The bands become flat at the edge of depletion region and the electric field falls to zero at the edge which persists throughout the semiconductor. In the metal side a neutralizing negative charge is accumulated at the contact. A Schottky junction is consists of a space charge region (entirely depleted of mobile charge) and an electrically neutral bulk region where they are separated by a sharp interface [44].

Electrons coming from the n-type semiconductor into the metal face a barrier known as built-in voltage (V<sub>bi</sub>) are obtained from  $\phi_m$ - $\phi_s$ . The barrier faced by holes moving from p-type semiconductor to metal is  $\phi_s$ - $\phi_m$ . The depletion width for a Schottky barrier on an *n*-type semiconductor can be obtained following expression [45],

$$W = \sqrt{\frac{2 \times V_{bi} \times \varepsilon \times \varepsilon_0}{q \times N_D}}$$

2.3

where  $\varepsilon$  is the dielectric constant of the semiconductor material,  $\varepsilon_0$  is the permittivity of vacuum, q is the electronic charge (1.6 × 10<sup>-19</sup> C) and  $N_D$  is the effective doping concentration and V<sub>bi</sub> is the built-in potential. For n-type semiconductor the built-in voltage V<sub>bi</sub> is given by

$$V_{bi} = \Phi_B - \frac{kT}{q} \ln\left(\frac{N_C}{N_D}\right)$$

2.4

A forward bias opposes the built-in voltage and reduces the overall band bending while a reverse bias does the opposite.

# 2.3.4 Carrier Transport Mechanism

The current transport in metal-semiconductor contacts is mainly due to majority carriers. The various electrons transport mechanisms across a metal – semiconductor junction under a forward bias are as follows [46]:

- a. Electron thermionic emission over the top of the barrier (holes for *p*-type material) in which electrons with energies greater than the barrier height can pass across the junction

- b. Quantum mechanical tunneling which is important for heavily doped semiconductors where the depletion width is small.

- c. Depletion width is small. Recombination in the space charge region

d. Recombination in the neutral region.

Figure 2.3. Transport process in a forward biased Schottky barrier

The four different electron transport mechanisms are shown in Figure 2.3. Besides this, edge leakage current may flow at the contact periphery due to high electric field. There may also be current flow due to traps at the metal-semiconductor interface. The inverse process happens under the reverse bias. In ideal cases, the current flows mainly by the process (a). The other processes (b), (c), and (d) are responsible for the departures from ideality. The electron emission over the barrier from semiconductor to metal is governed by two basic processes: (i) electrons transport from the bulk semiconductor and across the depletion region by diffusion and drift in the barrier electric field and (ii) the electron emission at metal-semiconductor interface which is determined by the rate of transfer of electrons across the boundary. According to the diffusion theory of Schottky [47], the first process is dominant one. According to Bethe thermionic–emission theory [48], the second process, the actual transfer of electrons across the metal-semiconductor interface, is a current limiting factor.

## 2.3.5 Current-Voltage (I-V) Analysis

Many semiconductor devices; such as p-n and Schottky junctions, solar cells, photodiodes, MOSFET etc., electrical performances are evaluated through current-voltage (I-V) characteristics. The performance level and degradation are highly dependent upon the material, the operating current flowing through the device and series resistances. The voltage dependent junction current in a Schottky contact can be expressed as [46]:

$$I = I_s \left( e^{\frac{\beta V}{n}} - 1 \right) \tag{2.5}$$

where  $I_S$  is the saturation current, V is the applied voltage, *n* is the diode ideality factor,  $\beta = q/k_BT$ , *q* being the electronic charge (1.6 × 10<sup>-19</sup> C),  $k_B$  the Boltzmann constant (8.62 × 10<sup>-5</sup> eV/K), and *T* is the absolute temperature (°K). The saturation current is given by Equation 2.6

$$I_S = A^* A T^2 \left( e^{-\beta \varphi_B} \right)$$

2.6

where *A* is the area of the diode,  $\varphi_B$  is the Schottky barrier height, and *A*<sup>\*</sup> is the effective Richardson constant which can be expressed as [49]

$$A^* = 4\pi^2 \ m^*/h^3 = 120 \ (m^*/m) \ Acm^{-2} \ K^{-2}$$

2.7

where h is Planck constant, and  $m^*$  is the electron effective mass .

Plot of log (I) vs. V will be a straight line if  $I_0$  and n are constant. The voltage across the diode becomes  $V_d = V - IR_s$ , where  $R_s$  is the series resistance of the diode and V is the measured voltage across the entire diode including contact resistance as well as other resistance components.

$$I = I_{s}(e^{\frac{\beta(V - IR_{s})}{n}} - 1)$$

2.8

By taking the logarithm the equation 2.6 can be written as

$$\log(I) = \frac{\beta V}{n} + \log(I_S)$$

2.9

which is an equation of straight line where  $\frac{\beta}{n}$  is the slope and log( $I_S$ ) is the intercept as shown in Figure 2.4. The plot gives a straight line over the range where the condition IR<sub>s</sub><<V and k<sub>B</sub>T/q<<1 are satisfied. The plot deviates from straight line for lower current due to the term -1 in the parenthesis of the equation and deviates from

straight line for higher current due to series resistance. The slope and the intercept can be easily calculated using a linear regression of log (I) vs V plot obtained from I-V measurements. As the sample temperature is known, the ideality factor is obtained from the measured slope according to the equation 2.10.

$$n = \frac{1}{slope \times 1/\beta}$$

2.10

Figure 2.4. Linear fit of current-voltage (I-V) acquired data plotted in logarithmic scale

The reverse saturation current  $I_s$  is obtained by extrapolation of the straight line portion of the curve, and surface barrier height is calculated from the equation. The diode ideality factor gives the uniformity of surface barrier height across the detector surface [50]. An ideality factor greater than unity, indicates the presence of patches (i.e. presence of generation-recombination centers) on the detector surface where the surface barrier height is considerably lower than the rest of the surface [51].

## 2.3.6 Capacitance-Voltage (C-V) Analysis

The voltage dependence of the capacitance (C-V) measurement relies on the fact that the depletion region width of a semiconductor junction depends upon the applied voltage. The effective doping concentration ( $N_D$ ) in the active region of a Schottky diode or p-n junction can be obtained from the C-V measurement. The knowledge of effective doping concentration allows the calculation of the depletion width under certain applied bias (According to Equation 2.11) and also the determination of full depletion bias. In order to calculate the doping concentration and the built-in voltage, analysis of the data acquired from capacitance-voltage (C-V) measurements is needed.

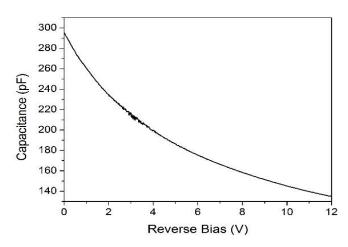

Figure 2.5. Capacitance-voltage data acquired using a Schottky diode.

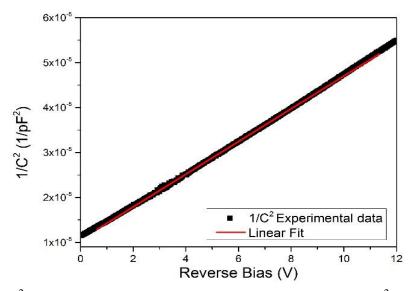

Figure 2.5 shows a C-V measurement conducted on a Schottky device. The capacitance can be seen decreasing with the increase in reverse bias because the capacitance is inversely proportional to the depletion width as is shown in Equation 2.11 and the depletion width in a p-n junction or Schottky diode increases as reverse bias increases. Mathematically, the capacitance of a Schottky diode can be expressed as [52],

$$C = \frac{\varepsilon \times \varepsilon_0 \times A}{W} = A \left[ \frac{\varepsilon \varepsilon_0 N_D}{2(V_{bi} + V)} \right]^{1/2}$$

2.11

where the symbols have their usual meaning.

The variation in capacitance as a function of reverse bias is given by

$$\frac{1}{C^2} = \frac{2V_{bi}}{A^2 q \varepsilon \varepsilon_0 N_D} + \frac{2V}{A^2 q \varepsilon \varepsilon_0 N_D}$$

2.12

which is a straight line equation in a  $1/C^2$  vs. V plot. The doping concentration  $N_D$  is calculated by the following equation:

$$N_D = \frac{2}{A^2 q \varepsilon \varepsilon_0 \times slope}$$

2.13

The first term of Equation 2.12 allows calculation of the built-in voltage  $(V_{bi})$  using the intercept obtained from the linear fit. Figure 2.6 shows one such linear  $1/C^2$  vs. V plot obtained for a Schottky diode.

Figure 2.6.  $1/C^2$  vs. reverse bias plot with linear fitting. Variation of  $1/C^2$  as a function of reverse bias corresponding to the C-V plot shown in above . The straight line shows the linear fit of the experimental data.

## 2.4 CONCLUSION

In this chapter material properties and the crystal structure of SiC are discussed. The crystal growth process for both bulk and epitaxial layer are also described briefly. The theoretical concepts of the device's structure used in the experiments of this thesis are explained here. For the detector fabrication, it is important to understand how to obtain the desired type of metal-semiconductor contact, e.g. Ohmic or Schottky. For Schottky contacts, the thermionic emission model is described in order to study the contacts' properties in SiC diodes in terms of the barrier height and the ideality factor using current-voltage (I-V) measurements. For further characterization of the Schottky contact, the calculation procedures for doping concentration and built-in voltage using capacitance-voltage (C-V) measurements are described.

# **CHAPTER 3: DEFECTS IN SIC**

# 3.1 OVERVIEW

Defects in semiconductors can be classified as: point defects and extended defects. Point defects are localized in a lattice site, involving only a few nearest neighbors and not extended to any spatial dimensions. Extended defects, such as, grain boundaries, dislocations and/or stacking faults, are extended in all dimensions and will be discussed in the next section. This chapter will discuss on the defects and their detrimental properties.

## 3.2 POINT DEFECTS

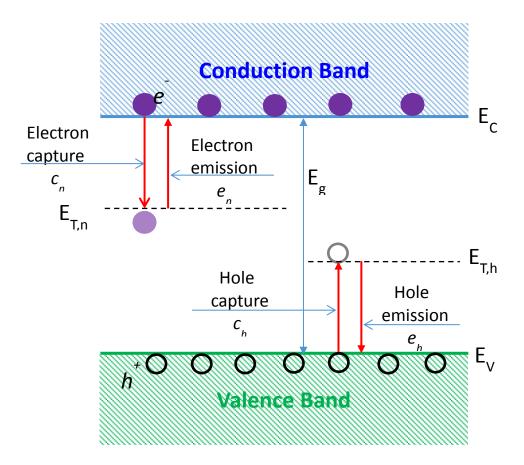

Point defects exist in small concentrations in all semiconductor materials and formed mainly due to vacancies, interstitials, and substitutions. Aggregation of few point defects which generate a perturbation in a lattice site and its immediate vicinity, such as, divacancies, vacancy–donor complexes, are also considered as point defects. Point defects introduce electronic energy states within the semiconductor band-gap which can act as, 'traps', 'recombination centers', or 'generation centers' and may modify the semiconductor properties and device performances significantly. The point defects are desirable for some devices and introduced intentionally. As for example, in switching devices, energy levels introduced by point defects can be used as recombination centers which help to remove minority carriers quickly during turning off and enhance the device's switching speed thereby increasing efficiency [53, 54]. However for many cases point defects are detrimental to the device performances. Energy states created by point defects may act as a recombination centers for the generated electron-hole pairs and degrade the performance of radiation detectors and photovoltaic solar cells. Point defects and their characterization will be discussed in detail in chapter five of this dissertation.

## 3.3 MORPHOLOGICAL DEFECTS

Most SiC devices are fabricated is such a way that their electrically active regions resides entirely within the epilayer grown on bulk crystal substrate. The electrical characteristics of these devices critically depend on the quality and smoothness of the semiconductor surface. So the defects contained in the epilayer are of great interest to any opto-electrical devices. The defects in SiC epilayer that impact electrical device performances are threading screw dislocation (TSD), threading edge dislocation (TED), basal plane dislocation (BPD), small growth pits, triangular inclusions, carrots, and comet tail defects [55, 56, 57]. Lot of defects originated in bulk cannot propagate to the epilayer, so the epitaxial layer contains significantly fewer defects than bulk wafers.

## 3.3.1 Threading Screw Dislocation (TSD) and Micropipes

Threading screw dislocation (TSD) can penetrate along the crystallographic c-axis through the entire length of the crystal. Screw dislocations terminate only in the crystal surface and are present in all wafers cut from the grown crystal. This screw dislocation can propagate throughout the whole thickness of epitaxial layer grown by CVD technique. Additional screw dislocation may also form during the epitaxial growth [58, 59]. Extended screw dislocation is usually measured by the length of the Burgers vector (b). For pure screw dislocation the Burgers vector is parallel to the crystallographic *c*-axis and the Burger vector length is related to the step height of the screw dislocation.

Screw dislocation with large Burger vector forms hollow cores and is widely known as micropipes. Micropipes are hollow tubular defects penetrating the SiC single crystals and their radius ranges from a few tens of nanometers to several tens of micrometers. The performance of SiC based power devices and radiation detectors is severely degraded by these micropipes [56, 60, 61]. Substrate micropipe defects with an area of 1 mm<sup>2</sup> or larger may cause pre-avalanche reverse-bias point failure in epitaxially grown *p*-*n* junction devices. With the steady development of the material growth process, the micorpipe densities have been reduced drastically (from  $10^4$  cm<sup>-2</sup> to less than 1 cm<sup>-2</sup>) and recently vendors have grown micropipe-free epitaxial layers [57].

The SiC screw dislocation with small Burgers vector forms close core and sometimes termed as elementary screw dislocations which exist at densities on the order of thousands per cm<sup>2</sup> in 4H- and 6H-SiC wafers and epilayers [62]. Close core dislocation is not as detrimental as micropipes, however, experimentally it is proven that theses defects have negative impact on device performances [63]. It is found that soft breakdown (at voltage <250 V) in 4H-SiC *p-n* junction diodes may happen due to these close core dislocation [64]. Wahab *et al.* showed that increasing density of close core dislocations in the active region can cause the degradation of the breakdown voltages [65].

## 3.3.2 Basal Plane Dislocation (BPD)

Basal plane dislocations (BPDs) probably have the highest density of all the dislocations. BPDs form to relaxation of the thermal stress which mainly occurred during cooling down from high growth temperature to room temperature. BPDs in *p-n* diodes may dissociate into two Shockley partials and cause an increase of forward voltage drop [66]. Basal plane tilt low angle grain boundaries due to the pile-up of BPDs [67].

# 3.3.3 Threading Edge Dislocation (TED)

Threading edge dislocation (TED) is an edge type dislocation which has Burgers vectors perpendicular to along the c-axis of the crystal. TEDs are mostly inherited from the substrate. Basal plane dislocations (BPDs) propagate from the off-axis 4H-SiC substrate into the homoepitaxial layer and convert into threading edge dislocations in the epitaxial layer. The conversion from BPDs to TEDs happens due to the image force in the

epilayers. The converted dislocations are inclined from the c-axis toward the down-step direction by about 15° [68]. Ha *et al.* [69] suggest that TEDs may also form due to prismatic plane slip.

#### 3.3.4 Staking Faults

Staking faults (SFs) are kind of planar defects and exist mostly in the primary slip plane  $\{0001\}$  of SiC. SFs occur due to the deviation of Si–C bilayers from the perfect stacking sequence along the c-axis of the crystal. SFs reduce the barrier height and the breakdown voltage of a Schottky diode. An electrostatic potential may appear in SiC *p-i*-*n* diodes due to the charge accumulation in the stacking faults and can increase the forward voltage drop in the diode [68].

# 3.4 MORPHOLOGICAL DEFECTS DELINEATION BY ETCHING

Chemical etching of silicon carbide is the most versatile way to characterize silicon carbide crystals and has been used effectively to evaluate the crystal qualities. Most of the chemicals used in chemical etching process are used in molten state. Since the sublimation temperature of SiC is 2830 °C, it is possible to etch SiC at temperature as high as 1200 °C. Due to high amount of hazards involved in etching SiC at such high temperature, a new method of etching SiC at low temperature is absolutely necessary. Molten KOH etching is the widely used method of etching to investigate the growth defects in SiC wafers. SiC etching by molten KOH is an isotropic etching which is a non-

directional etching with uniform etch rate in all directions of the wafers. So molten KOH remove the SiC surface layers at the same etch rate in all directions irrespective of the crystal orientation.

## 3.4.1 Experimental Procedure for SiC Etching

In our studies, etching studies have been conducted for bulk 4H-SiC crystals and 4H-SiC epitaxial layers. The epilayers were grown by chemical vapor deposition on ~ 350 µm 4H-SiC thick substrate. Both the bulk and the epitaxial layers were diced into 10×10 mm<sup>2</sup> size. Before etching, the samples have been cleaned thoroughly by an established procedure. This involved cleaning tri-chloro-ethylene (TCE) for 5 minutes and cleaning in HF and acetone for 5 min successively. A nickel crucible, inert to molten KOH, was used for holding the dry KOH pellets. A hot plate was used for heating the nickel crucible containing the KOH pellets. The temperature of the crucible is monitored by a thermocouple and the temperature was controlled with the help of a knob of the hot plate. The temperature is gradually increased to 500 °C to melt the KOH pellets. The SiC samples were immersed into the molten KOH with the help of a specially designed sample holder. The sample holder is also made from a thick nickel sheet. Throughout the etching period, KOH solution temperature is kept constant (~ 500 °C) by adjusting the power knob of the hot plate. After 20 minutes of etching, the samples were taken out from the solution and quickly washed by acidified water to neutralize the KOH. After repeated cleaning by DI water, the samples were finally cleaned with acetone. The whole etching experiment was carried out inside the chemical hood in the advanced microelectronic materials laboratory at USC. A very thin layer (~ 5 nm) of gold was deposited on the etched surface of SiC samples for SEM studies.

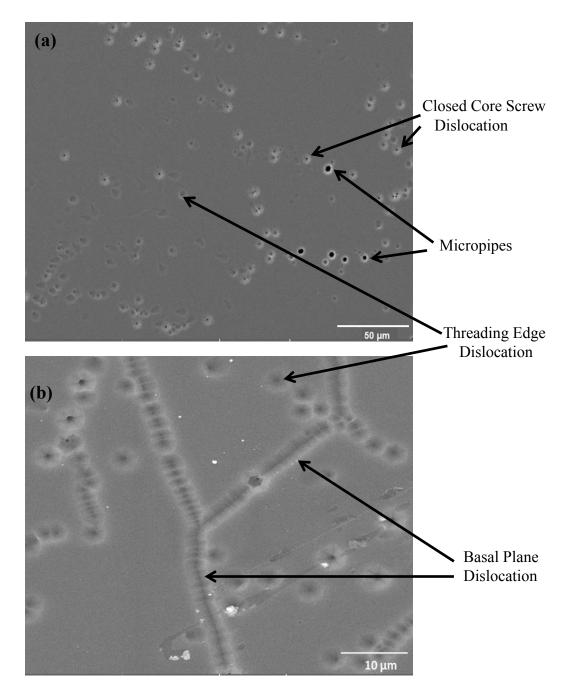

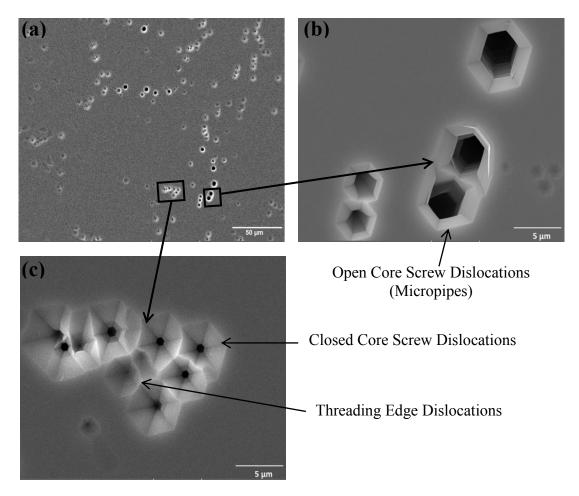

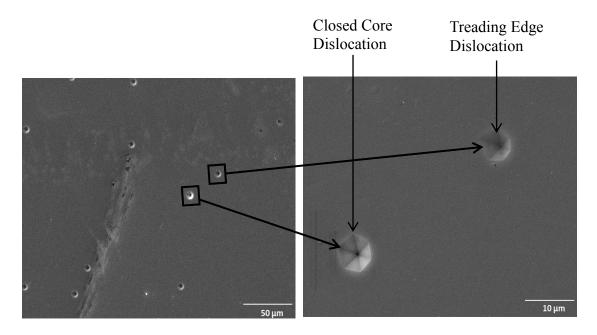

#### 3.4.2 Result of SEM Studies

Figure 3.1 shows the SEM image of a Si-face etched bulk SiC crystal. In the SEM images observed pits with hexagonal shapes are correlated to three types of dislocations. Hexagonal pits with a small black spot in the center are the closed-core screw dislocations [70, 71, 72]. The larger hexagonal pits with a hollow core in the center are considered as the open-core screw dislocations (micropipes) [73, 74]. Hexagonal pits without any center spot are the treading edge dislocations [72, 73]. The hexagonal pits images corresponding to the treading edge dislocations are less bright than those of open core or close core dislocations. In the SEM image shown in Figure 3.1 (b), the basal plane dislocations are appeared as sharp elongated lines which are formed by the interconnection of a series of asymmetrical pits. Figure 3.2 shows the magnified images of the following observed dislocations.

Figure 3.3 (a) shows the SEM images of etched SiC epitaxial layers. The experimental set up and etching process was kept exactly the same for both bulk and epitaxial layers. Figure 3.3 (b) shows the enlarged SEM images of closed core dislocations and threading edge dislocations of the epitaxial layers. The densities of the identified dislocations are much lower in the epitaxial layer compared to the bulk

crystals. Micropipes and BPDs are not observed in the SEM images of the etched epitaxial layers.

Figure 3.1. SEM image of the molten KOH etched bulk SiC: (a) Region with TSDs and TEDs; (b) Regions with BPDs and TEDs.

Figure 3.2. SEM images of the molten KOH etched bulk SiC: (a) Region with TSDs and TEDs; (b) Enlarge images of micropipes; (C) ) Enlarge images of closed core and threading edge dislocations.

Figure 3.3. (a) SEM images of the molten KOH etched SiC epitaxial layers; (b) Enlarged images of closed core and threading edge dislocations.

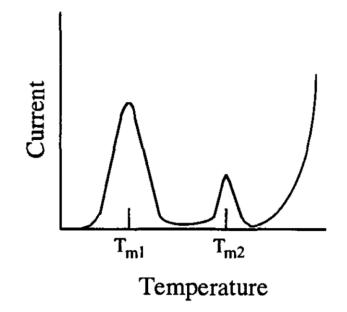

## 3.5 CONCLUSIONS