## Washington University in St. Louis Washington University Open Scholarship

Engineering and Applied Science Theses & Dissertations

Engineering and Applied Science

Winter 12-15-2014

# The Synchronized Filtering Dataflow

Peng Li Washington University in St. Louis

Follow this and additional works at: http://openscholarship.wustl.edu/eng\_etds Part of the <u>Engineering Commons</u>

#### **Recommended** Citation

Li, Peng, "The Synchronized Filtering Dataflow" (2014). *Engineering and Applied Science Theses & Dissertations*. 61. http://openscholarship.wustl.edu/eng\_etds/61

This Dissertation is brought to you for free and open access by the Engineering and Applied Science at Washington University Open Scholarship. It has been accepted for inclusion in Engineering and Applied Science Theses & Dissertations by an authorized administrator of Washington University Open Scholarship. For more information, please contact digital@wumail.wustl.edu.

#### WASHINGTON UNIVERSITY IN ST. LOUIS

School of Engineering and Applied Science Department of Computer Science and Engineering

> Dissertation Examination Committee: Jeremy Buhler, Chair Kunal Agrawal Roger D. Chamberlain Christopher D. Gill Joseph A. O'Sullivan

The Synchronized Filtering Dataflow by Peng Li

A dissertation presented to the Graduate School of Arts and Sciences of Washington University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

> December 2014 Saint Louis, Missouri

© 2014, Peng Li

# **Table of Contents**

| List of l | igures                                                        | V   |

|-----------|---------------------------------------------------------------|-----|

| List of [ | ables                                                         | vii |

| Acknow    | ledgments                                                     | iii |

| Abstrac   | t                                                             | xi  |

| Chapte    | 1: Introduction                                               | 1   |

| 1.1       | New Trends in Computing                                       | 1   |

|           | 1.1.1 Parallel Computing                                      | 1   |

|           | 1.1.2 Streaming Processing                                    | 5   |

| 1.2       | The Streaming Computing Paradigm                              | 8   |

|           | 1.2.1 Integrating Parallel Computing and Streaming Processing | 8   |

|           | 1.2.2 Design Concerns in Streaming Computing                  | 10  |

| 1.3       | Problem Statement                                             | 10  |

|           | 1.3.1 Filtering in Streaming Computing                        | 11  |

|           | 1.3.2 Synchronization for Determinism                         | 11  |

|           | 1.3.3 Synchronization Is a Natural Application Behavior       | 13  |

|           | 1.3.4 The Deadlock Issue                                      | 15  |

| 1.4       | Summary of Our Approach                                       | 15  |

| 1.5       | Contributions                                                 | 16  |

| Chapte    | 2: Background and Related Work                                | 18  |

| 2.1       | A Brief History of Streaming Computing                        | 18  |

| 2.2       | Models of Streaming Computing                                 | 19  |

| 2.3       | Deadlock Avoidance Approaches                                 | 23  |

| Chapte    | 3: The Synchronized Filtering Dataflow                        | 25  |

| 3.1       | General Description                                           | 25  |

|           | 3.1.1 Notations                                               | 26  |

| 3.2     | Synchronizing and Filtering Behaviors                                           |    |

|---------|---------------------------------------------------------------------------------|----|

| 3.3     | Deadlock Concerns                                                               |    |

|         | 3.3.1 Deadlock Example                                                          | 28 |

|         | 3.3.2 Conditions for Deadlock                                                   | 29 |

| 3.4     | Summary                                                                         | 34 |

| Chapter | r 4: Bounded-memory Execution of SFDF Applications                              | 35 |

| 4.1     | Dummy Messages for Deadlock Avoidance                                           | 35 |

| 4.2     | Limiting the Frequency of Dummy Messages                                        |    |

| 4.3     | Eliminating Propagation of Dummy Message                                        | 40 |

| 4.4     | Comparison of Algorithms                                                        | 43 |

|         | 4.4.1 A Paper-and-pencil Comparison                                             | 43 |

|         | 4.4.2 Experimental Evaluation                                                   | 44 |

| 4.5     | Summary                                                                         | 49 |

| Chapter | r 5: Efficient Deadlock Avoidance for Applications with Structured Topologies . | 50 |

| 5.1     | Destination-Tagged Propagation Algorithm                                        | 51 |

| 5.2     | Efficient Deadlock Avoidance for SP-DAGs                                        | 52 |

|         | 5.2.1 SP-DAG Preliminaries                                                      | 53 |

|         | 5.2.2 The Destination-Tagged Propagation Algorithm for SP-DAGs                  | 56 |

|         | 5.2.3 The Non-Propagation Algorithm for SP-DAGs                                 | 62 |

| 5.3     | CS4 DAGs: a Larger Set of Simple Streaming Topologies                           | 64 |

| 5.4     | Efficient Deadlock Avoidance for CS4 DAGs                                       | 72 |

|         | 5.4.1 Destination-Tagged Propagation Algorithm for SP-ladders                   | 74 |

|         | 5.4.2 Non-Propagation Algorithm                                                 | 80 |

| 5.5     | Summary                                                                         | 81 |

| Chapter | r 6: Polyhedral Constraints for Dummy Message Scheduling                        | 83 |

| 6.1     | Polyhedral Characterization of Safe Dummy Intervals                             | 83 |

| 6.2     | Constraints for Series-parallel DAGs                                            | 90 |

| 6.3     | Selection of Dummy Intervals for Performance                                    |    |

| 6.4     | Summary                                                                         |    |

| Chapter | r 7: Support for General Control Messages in SFDF Applications                  | 98 |

| 7.1     | Control Messages and Their Uses                                                 | 98 |

|         | 7.1.1 An Application Example                                                    | 99 |

|         | 7.1.2 Other Potential Uses of Control Message                                   | 00 |

| 7.2     | Precise Control-Data Ordering for SFDF                                          | 01 |

|         | 7.2.1   | Delivery of Control Messages                   |

|---------|---------|------------------------------------------------|

|         | 7.2.2   | A Credit-based Protocol                        |

|         | 7.2.3   | Correctness and Safety                         |

| 7.3     | Extend  | ing SFDF with Precise Control                  |

|         | 7.3.1   | Deadlocks Due to Full Data Channels            |

|         | 7.3.2   | Avoiding Deadlocks for the Extended SFDF Model |

|         | 7.3.3   | Verifying Safety of Heartbeat Intervals        |

|         | 7.3.4   | Finding Extrema of Heartbeat Interval          |

|         | 7.3.5   | Deadlocks Due to Full Control Channels         |

| 7.4     | Experie | mental Evaluation                              |

| 7.5     | Summa   | ary                                            |

|         |         |                                                |

| Chapter | :8: Co  | nclusion and Future Work 121                   |

| 8.1     | Conclu  | sion                                           |

| 8.2     | Future  | Work                                           |

| Referen | ces     |                                                |

# **List of Figures**

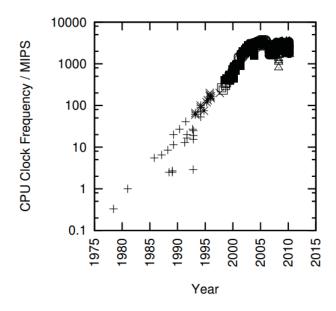

| Figure 1.1 | Clock-frequency trend for Intel CPUs, adopted from [75]                                                                                                        | 2  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

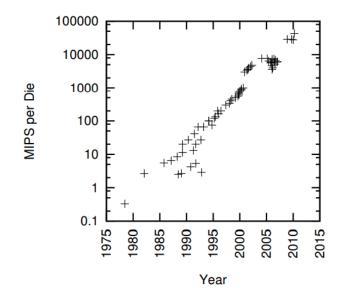

| Figure 1.2 | MIPS per die trend for Intel CPUs, adopted from [75]                                                                                                           | 3  |

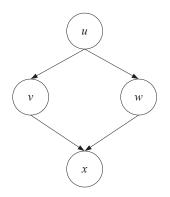

| Figure 1.3 | An example of the dataflow graph of an application. The circles represent tasks, while the arrows represent unidirectional data transmission                   | 4  |

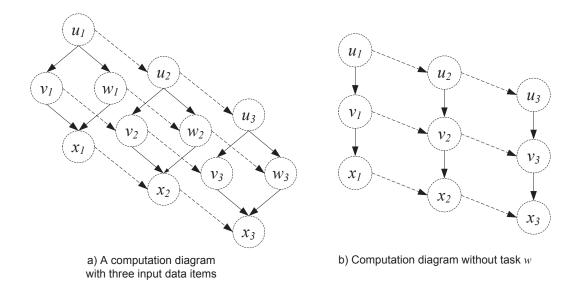

| Figure 1.4 | Computation diagram for three input data items. Solid lines represent data transmission, while dashed lines represent other dependencies between computations. | 4  |

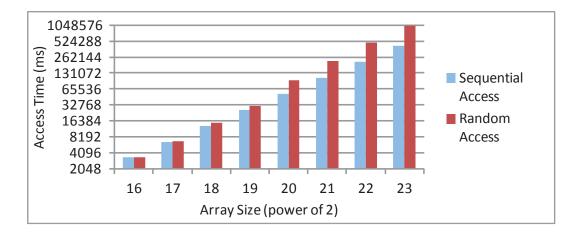

| Figure 1.5 | Comparison of data access times.                                                                                                                               | 7  |

| Figure 1.6 | Dataflow graph of a streaming computing system                                                                                                                 | 9  |

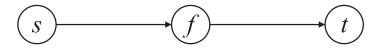

| Figure 1.7 | A streaming pipeline with a filtering node                                                                                                                     | 11 |

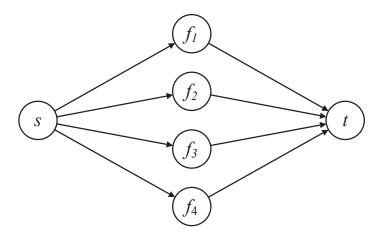

| Figure 1.8 | A streaming application with multiple filtering nodes                                                                                                          | 12 |

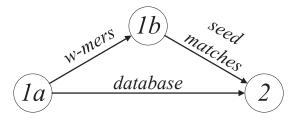

| Figure 1.9 | The first two stages of Mercury BLAST                                                                                                                          | 14 |

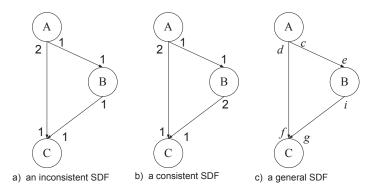

| Figure 2.1 | Examples of SDFs [66]                                                                                                                                          | 21 |

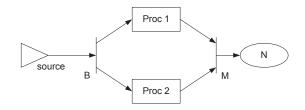

| Figure 2.2 | A parallel discrete-event simulation system from [77]                                                                                                          | 24 |

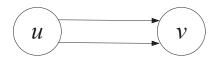

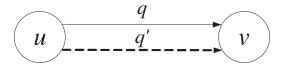

| Figure 3.1 | A pair of nodes connected by two channels                                                                                                                      | 25 |

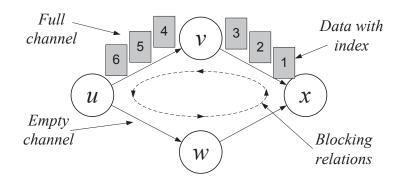

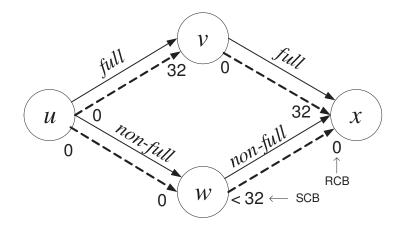

| Figure 3.2 | A deadlock example in SFDF. Both $uv$ and $vx$ are assumed to have a buffer size of 3                                                                          | 29 |

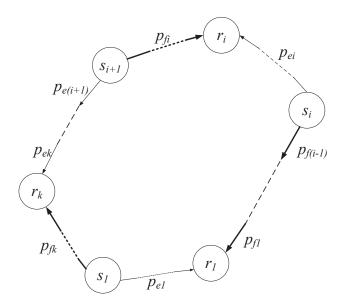

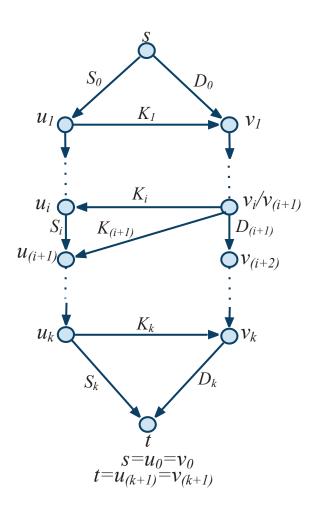

| Figure 4.1 | The division of a blocking cycle for Theorem 4.1                                                                                                               | 38 |

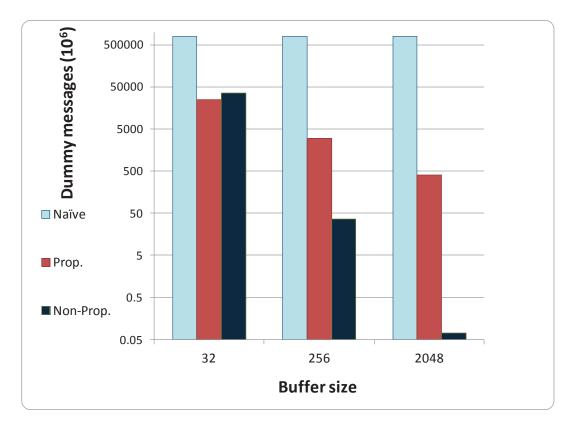

| Figure 4.2 | Dummy message counts for Mercury BLASTN                                                                                                                        | 46 |

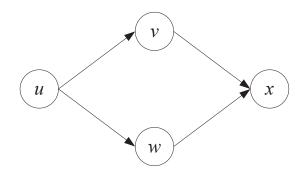

| Figure 5.1 | A simple split/join streaming topology.                                                                                                                                                                                                                                     | 52  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

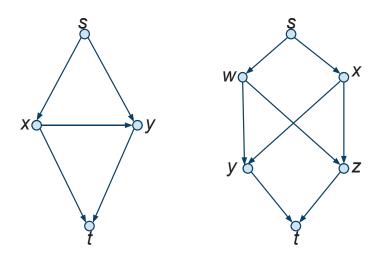

| Figure 5.2 | Two simple non-SP-DAGs                                                                                                                                                                                                                                                      | 65  |

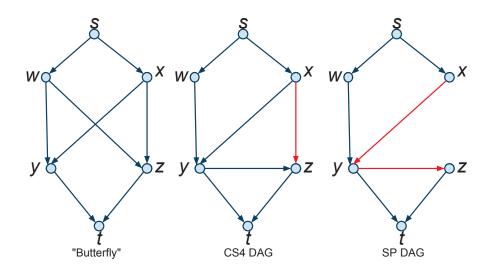

| Figure 5.3 | transforming butterfly to CS4 DAG and SP-DAG                                                                                                                                                                                                                                | 66  |

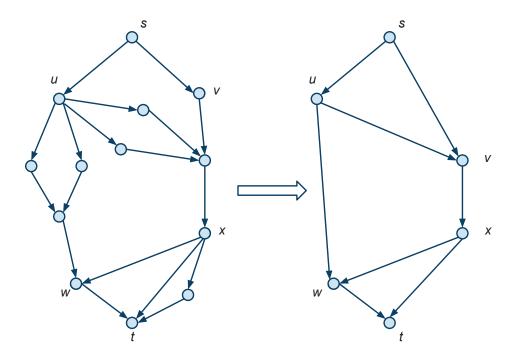

| Figure 5.4 | Decomposition of an SP-ladder graph                                                                                                                                                                                                                                         | 68  |

| Figure 5.5 | General structure of a decomposed SP-ladder graph, including an example of cross-links sharing an endpoint.                                                                                                                                                                 | 69  |

| Figure 6.1 | The division of a blocking cycle, previously used as Figure 4.1. Node and channel labels are used in the proofs of Theorem 6.1 and Theorem 6.2                                                                                                                              | 84  |

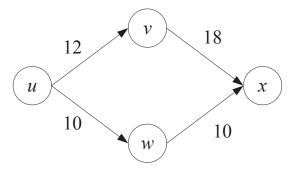

| Figure 6.2 | A simple streaming topology with buffer sizes labeled                                                                                                                                                                                                                       | 85  |

| Figure 6.3 | Visualization of safe dummy intervals for the topology shown in Figure 6.2.                                                                                                                                                                                                 | 86  |

| Figure 6.4 | Dataflow graph of a synthetic application.                                                                                                                                                                                                                                  | 94  |

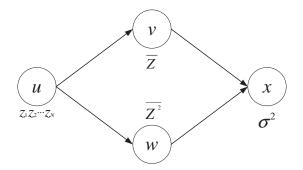

| Figure 7.1 | A streaming computation for variance. It occurs as part of large streaming computing systems, including the next generation of VERITAS [111], a ground-based gamma-ray observatory system.                                                                                  | 99  |

| Figure 7.2 | An edge with paired data and control channels $q$ and $q'$                                                                                                                                                                                                                  | 101 |

| Figure 7.3 | A deadlock example. $w$ filters 46 of 64 consumed data tokens, and no other<br>node filters data. Now data channels $uv$ and $vx$ are full, blocking $u$ and $v$ ;<br>SCB values for $uw$ and $wx$ are not big enough to prompt credit messages,<br>blocking $w$ and $x$    | 107 |

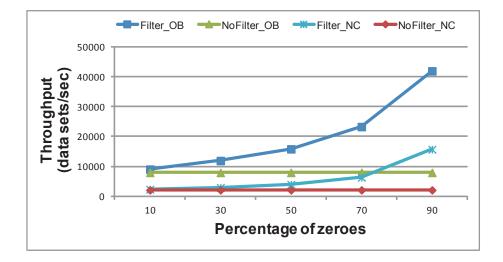

| Figure 7.4 | Throughput of variance application vs. rate of filtering (heartbeat interval = 16). Filter_OB, NoFilter_OB, Filter_NB, NoFilter_NB represent: filtering w/ output buffer, non-filtering w/ output buffer, filtering w/o output buffer, and non-filtering w/o output buffer. | 119 |

# **List of Tables**

| Table 1.1 | Summary of different task-level parallelisms                                     | 6  |

|-----------|----------------------------------------------------------------------------------|----|

| Table 4.1 | Measured dummy message counts from module 1a for Mercury BLASTN .                | 45 |

| Table 4.2 | Simulation results for Marsaglia polar algorithm (filtering ratio = $21.46\%$ ). | 48 |

| Table 4.3 | Simulation results for 4 replicated filters and filtering ratio = $95\%$         | 48 |

| Table 4.4 | Simulation results for 4 replicated filters and filtering ratio = $5\%$          | 49 |

| Table 6.1 | Measured dummy message counts for correlated filtering                           | 95 |

| Table 6.2 | Measured dummy message counts for uncorrelated filtering                         | 96 |

## Acknowledgments

I lived through the most challenging part of my life so far, thanks to many people.

First, I would like to sincerely thank my advisor, Dr. Jeremy Buhler, for his guidance through the journey. Dr. Buhler has been supportive and encouraging throughout my PhD study. He pointed the research direction to me, fixed my broken proofs, and left mark on me with his affluent knowledge and serious attitude. I could not have finished the dissertation without his advice. I also thank Dr. Roger Chamberlain for being my co-advisor. As a veteran researcher, he knows almost every aspect of computer science and engineering – from hardware to software, and from theory to applications. Thanks to his broad knowledge, I enjoyed incredible research freedom. Whatever ideas I proposed, he was always there to give me insightful advice. Very few students have the luxury of being supervised by three professors – I was lucky being one of them. Dr. Kunal Agrawal, also my co-advisor, guided me through complex parallel computing theories. Without her help, I couldn't have formalized my ideas and published them in peer-reviewed papers. In addition, I would like to thank Dr. Chris Gill and Dr. Joseph O'Sullivan for being on my dissertation and research. Dr. Gill also ardently tried to help me find a job.

I am grateful for financial support provided by NIH award R42 HG003225, NSF award CNS-0751212, and NSF award CNS-0905368. This support allowed me to focus on my research without worrying financial situation.

I would like to thank the department staff members Kelli Eckman, Sharon Matlock, Jayme Moehle, Lauren Huffman, and Myrna Harbison, who make WUCSE like a big family. I would like to thank my collegues and friends Lin Ma, Hongtao Sun, Steve Cole, Arpith Jacob, Joe Lancaster,

Michael Hall, Jonathan Beard, and Joe Wingbermuehle – this list could go very long. Conversations with them have helped shape my research.

Finally, I want to thank my family in China, especially my parents. They have been a source of consistent encouragement and support. I am really proud of them.

Peng Li

Washington University in Saint Louis December 2014 Dedicated to the memory of my grandfather, who passed away on November 17th, 2014.

#### ABSTRACT OF THE DISSERTATION

The Synchronized Filtering Dataflow by Peng Li Doctor of Philosophy in Computer Science Washington University in St. Louis, 2014 Professor Jeremy Buhler, Chair

In the past decade, the world has seen the rise of big data, which calls for a paradigm shift in data processing. Streaming processing, where data are processed in their spatial or temporal order, is increasingly common. Meanwhile, parallel computing has become a household term in the computing world. The combination of streaming processing and parallel computing, *streaming computing*, has been playing an important role in data processing.

A streaming computing system is a network of *nodes* connected by unidirectional first-in firstout (FIFO) data *channels*. When a node has multiple input channels, to ensure the deterministic behavior of the whole system, *synchronization* is required on those channels when the node consumes data. After a streaming computing node finishes a computation, it may choose not to produce output on some of its output channels. This behavior, known as *filtering*, is data-dependent and unpredictable. When filtered data streams are synchronized, applications can *deadlock* due to empty and full channel buffers.

To avoid deadlocks and ensure bounded-memory execution, we turn to model-based approaches. In this dissertation, we propose the synchronized filtering dataflow (SFDF) to model synchronization and filtering behaviors. We avoid deadlocks in SFDF applications by augmenting data streams with *dummy messages*. We design *decentralized* algorithms that compute a *dummy interval* for each channel during compilation time and schedule dummy messages according to the dummy intervals during runtime.

The runtime parts of our algorithms are very efficient, adding little overhead to computing nodes, but computing dummy intervals could be very time-consuming on general dataflow graphs.

We design efficient algorithms to compute dummy intervals for streaming applications with special topologies. In particular, we focus on series-parallel directed acyclic graphs (SP-DAGs) and CS4 DAGs, where each *undirected* cycle is single-source and single-sink.

We further extend our work to describe a set of polyhedral constraints that define all sets of safe dummy intervals for any dataflow graphs, which gives us more flexibility to choose dummy intervals. We also provide a polynomial-time algorithm to verify the safety of given dummy intervals for SP-DAGs.

Dummy messages are only one type of *control message* used by streaming applications. We extend our SFDF model to support more types of control message, which are precisely synchronized with data streams. We use two types of control messages, dummy message and *credit message*, to guarantee bounded-memory execution. We demonstrate that the extended model can help improve performance of some applications by adding filtering behavior to non-filtering applications.

## **Chapter 1**

## Introduction

For decades, sequential computer programs with random access to input data have prevailed. However, in recent years, the world has increasingly seen hardware built for parallel computing. Even in embedded systems, such as mobile phones, multi-core processors are common. Meanwhile, in data-processing applications, large data sizes push people to use streaming processing. The two trends converge into a new computing paradigm: streaming computing.

## 1.1 New Trends in Computing

## 1.1.1 Parallel Computing

In the 1960s, Gordon Moore predicted that the number of transistors that could be placed on a chip would double every two years; the prediction is known as "Moore's Law" [79]. Thanks to the evolution of semiconductor technology, Moore's Law has been continuing for more than four decades, far beyond Moore's expectation. As a result, the computing power of a single chip has been doubling every two years. Before the early 2000s, increases in processor computing power resulted mainly from increases of clock speed, which, however, has plateaued in recent years (see Figure 1.1). In the meantime, more processor cores were integrated into a single chip. Nowadays it is common to see workstations, personal computers, and even mobile phones equipped with multicore processors [12]. Graphics processing units (GPUs) can have hundreds of cores [84]. While

as a whole chip, processors are more powerful today (see Figure 1.2), single-core performance has not seen a corresponding growth and has even slowed down. But computing demand keeps growing. To meet the requirement for computing power, we need parallel computing<sup>1</sup>.

A parallel computing system, or a parallel program, is a collection of sequential modules cooperating with each other, some of which can be executed concurrently. *Parallelism* characterizes the availability of computations that can take place concurrently. Understanding different forms of parallelism is key to understanding parallel computing.

Figure 1.1: Clock-frequency trend for Intel CPUs, adopted from [75].

#### **Understanding Parallelisms**

Parallel computing can be boiled down to extracting and implementing parallelism in applications. Depending on the granularity of executing entities, there are bit-level parallelism [19], where a bit is the finest processing granularity, instruction-level parallelism [115], where multiple instructions

<sup>&</sup>lt;sup>1</sup>Some people might make a distinction between *parallel computing* and *distributed computing*, arguing that processing units are more tightly coupled in parallel computing (e.g. hardware cores in a processor) than in distributed computing (e.g. different computers in a cluster). In this dissertation, we do *not* make such a distinction. We simply use the term *parallel computing* to refer to computations that involve multiple computer programs or modules.

Figure 1.2: MIPS per die trend for Intel CPUs, adopted from [75].

of one program are executed concurrently on different functional units of a processor, and *task-level parallelism* [26, 101], where multiple tasks run in parallel. *Task* here refers to a *sequential* computation module of an application. We discuss task-level parallelism in this dissertation. We define a *computation* as the process of a task computing on an input data item and use  $X_i$  to represent the computation of task X on the *i*th data item. We use Figure 1.3, which shows the dataflow graph of an application with four tasks u, v, w, and x, to help explain different forms of parallelism. Figure 1.4 is a *computation diagram*<sup>2</sup> of Figure 1.3 with three input data items. To differentiate computations from tasks, we use dashed circles to represent computations. We remove task w from the graph in Figure 1.4b to simplify the diagram.

Given two *computations* a and b, if b cannot start before a finishes, we say that b is dependent on a. For example, in Figure 1.4b, both  $v_1$  and  $u_2$  are dependent on  $u_1$ . Dependencies are transitive. Note that data transmission implies a dependency (*data dependency*). We use solid lines to represent data dependency and dashed lines to represent other possible dependencies. Even if two *tasks* have data transmission between them, their computations are not necessarily dependent.

$<sup>^{2}</sup>$ We do not use the term *computation graph* because historically it was used to refer to some special systems [58].

Figure 1.3: An example of the dataflow graph of an application. The circles represent tasks, while the arrows represent unidirectional data transmission.

Figure 1.4: Computation diagram for three input data items. Solid lines represent data transmission, while dashed lines represent other dependencies between computations.

For example, tasks v and u are connected by a data transmission channel, but  $v_1$  and  $u_2$  have no dependency between them, so tasks u and v can actually run in parallel on different data items.

**Pipeline Parallelism.** Computations  $v_1$  and  $u_2$  can be executed in parallel, as can  $x_1$ ,  $v_2$ , and  $u_3$ . We can generalize this pattern as follows:  $x_i$ ,  $v_j$ , and  $u_k$ , i < j < k, have no dependency between them and so can run concurrently. In practice, the tasks u, v, and x can be mapped onto separate executable resources. After the initial setup, u, v, and x can work on different data items concurrently like a workflow pipeline, so this form of parallelism is named *pipeline parallelism*.

**Data Parallelism.** Whether dependencies exist between  $v_1$ ,  $v_2$ , and  $v_3$  depends on the task v's program. If task v is *stateless*, which means previous input data have no effect on the processing of the current data (v always produces the same output for a given input regardless of input history; otherwise, v is *stateful*), then there is no dependency between input data and  $v_1$ ,  $v_2$ , and  $v_3$  can run in parallel. This form of parallelism is called *data parallelism*.

If v is stateless and processing one data item by v takes much more time than by u and by x, we can improve application throughput by running multiple instances of v in parallel. In contrast, if node v is stateful, it is not easy to extract data parallelism from v. Thies [110] demonstrated a method combining data duplication and batching to extract data parallelism from stateful nodes when node state is based on a sliding window of data history.

**Task Parallelism.** Regardless of the values of i and j,  $v_i$  and  $w_j$  have no dependency between them and can always run in parallel. This is because there is no data exchange between v and w in the application's dataflow graph. We name this form of parallelism *task parallelism* if v and w are not replications of the same program, which is just one type of *task-level* parallelism.

To summarize, parallelisms might be available if there are multiple tasks or multiple input data items. Pipeline parallelism is exposed by *different* and *dependent* tasks processing *different* input data; data parallelism is exposed by the *same* task processing *different* input data; task parallelism is exposed by *different* and *independent* tasks processing *any* input data, same or not. Note that the availability of multiple data items is a necessary but not sufficient condition for the availability of data parallelism. Stateful computing could still eliminate data parallelism. Table 1.1 is a summary of the classification.

## 1.1.2 Streaming Processing

Besides the trend of parallel computing, we are also seeing a change in data processing patterns. Because computer memory is randomly accessible, and many data structures and algorithms require random access (e.g. trees and binary search), random data access has been a commonly used

|                      | Same Task        | Different Tasks                   |

|----------------------|------------------|-----------------------------------|

| Same Input Data      | No Parallelism   | Task Parallelism                  |

| Different Input Data | Data Parallelism | Pipeline Parallelism <sup>a</sup> |

|                      |                  | Task Parallelism <sup>b</sup>     |

Table 1.1: Summary of different task-level parallelisms

<sup>a</sup> when tasks are dependent

<sup>b</sup> when tasks are independent

pattern. However, random data access exposes no spatial locality and fails to utilize caching and prefetching [27].

We use a microbenchmark to show the time difference between the random access and sequential access. In each test run, we accessed all n elements in an array of size n in sequential order and in random order, respectively. For each element, we performed a sequence of reading, modifying, and writing operations. All test runs started with cold cache on a machine with an Intel Core i5 processor (3MB cache) and 4 GB memory. From Figure 1.5 we can see that as data size grows, sequential access shows more advantage over random access. When the array size is  $2^{23}$ , sequential access took less than half of the time taken by random access.

Random data access requires randomly accessible memory. In the big data era, however, this can be challenging for some applications. For example, graphs for social networks and biological networks, such as protein interaction networks, can have billions of edges [105]. Such data are too big to be entirely loaded into today's computer memory. If we store the data in disks, we should not use random data access because disks are too slow<sup>3</sup>.

*Streaming processing* is a better choice for processing big data. On the one hand, it requires memory constant to the size of a data item; on the other hand, streaming can hide disk latency [38, 39, 121]. Note that not all applications are suitable for streaming processing. Historically, the terms "stream," "stream processing," and "streaming processing" have been used to describe different models and systems. "Stream" in computer science refers to a sequence of data, which can

<sup>&</sup>lt;sup>3</sup>For a disk with a rotational speed of 7, 200 RPM (revolutions per minute), it can be calculated that the average seek time is 4.2 milliseconds, which is substantial considering clock speeds of today's computers.

Figure 1.5: Comparison of data access times.

be finite or infinite, such as I/O streams [2]. "Stream" is also a data type in some dataflow languages (e.g. Lucid [7] and Lustre [97, 46]) and functional programming languages (e.g. Scala [86] and Haskell [51]). In data processing, the term "streaming processing" has been used to describe pipelined SIMD (single instruction, multiple data) systems, where a "data stream" is a finite set of data with known length [88]. Each pipeline module computes on an entire stream in one computation. Example languages and systems include Brook [13] and Merrimac [28].

In this dissertation, "streaming processing" is a data access pattern where data are processed sequentially according to their stored locations or arrival times, as opposed to randomly. Here, a "data stream" is an *unbounded* sequence of data [106]. Note that streaming processing is not necessarily parallel computing. A sequential program can also do streaming processing. Some streaming processing systems involve no parallel processing, such as Aurora, a data stream management system [4].

## **1.2 The Streaming Computing Paradigm**

Parallel computing has become an important solution for computation-heavy applications, and streaming processing can handle big data. When we combine the two together, we have a new computing paradigm: *streaming computing*<sup>4</sup>.

### **1.2.1 Integrating Parallel Computing and Streaming Processing**

A streaming computing system is a parallel computing system with computing *nodes* connected by *first-in first-out (FIFO)* data channels. Each node runs a *streaming processing* module (i.e. a task); each channel is *unidirectional* and delivers data in order. There are three types of nodes in the system: source nodes, sink nodes, and intermediate nodes. Source nodes read data from external data sources (e.g. sensors, network requests, and database queries) and emit data to their receivers; intermediate nodes receive data, process them, and send intermediate output data to their downstream receivers; sink nodes are responsible for writing final output. Figure 1.6 shows the dataflow graph of a streaming computing system with five nodes and channels between the nodes. u and y the are the source node and the sink node, respectively. Other nodes are intermediate nodes.

Streaming computing is suitable for applications that can be decomposed into multiple tasks and process multiple data, which together expose various forms of parallelism for streaming computing to exploit. For example, in Figure 1.6, nodes u, v, x, and y (or u, w, w, and y) represent pipeline parallelism, as they can process different data concurrently like a workflow pipeline. If v and w are duplicated tasks, they represent data parallelism; otherwise, if v and w are different tasks, they represent task parallelism.

Streaming computing systems can be decentralized, which means they do not need a central authority to manage nodes and channels, such as streaming applications deployed by frameworks

<sup>&</sup>lt;sup>4</sup>The term *distributed streaming processing* also refers to this paradigm [25, 52].

Figure 1.6: Dataflow graph of a streaming computing system.

such as Auto-Pipe [20] and StreamIt [109]. These systems can also be centralized with a master node to provide management over the system, such as applications deployed by frameworks Storm [1] and MillWheel [5]. In this dissertation, we focus on decentralized models for streaming computing.

As it takes advantage of streaming processing, parallel computing, and FIFO communication, streaming computing has the following attractive features:

- **Exploiting parallelisms**. Streaming computing can exploit all three common parallelisms in applications (data parallelism, pipeline parallelism, and task parallelism), as illustrated by Figure 1.6.

- **Exploiting data locality**. Since each node processes data in streaming fashion, the spatial locality of input data is utilized. The FIFO communication also exposes producer-consumer locality [27].

- Analyzable Properties Because of FIFO communication and streaming processing, data movement and computations are well-organized. Analytical tools can be used to analyze system properties. For example, queueing theory [45] can be used to predict application performance [82, 90, 92], and linear algebra can be used to analyze memory requirement of some streaming applications [64, 66].

We will review the history of streaming computing and its formal models further in Chapter 2.

## 1.2.2 Design Concerns in Streaming Computing

Like all computing paradigms, streaming computing is concerned with two fundamental issues: performance and correctness.

Performance is important because it is the reason we turn to parallel computing. Two important metrics for performance are throughput and latency. Throughput is the amount of data processed per unit time, while latency is the time spent in processing one data item. For a single sequential program, reducing latency is equivalent to improving throughput. But when multiple tasks need to coordinate with each other, due to communication overhead, throughput and latency can sometimes go against each other [90]. For example, pipelining improves throughput by exploiting pipeline parallelism, but it also increases latency for each data item. There are numerous performance optimization problems considering different constraints and optimization goals, such as optimizing throughput [68], optimizing latency [114], balancing throughput and latency [107, 92], and minimizing power usage [9]. Hirzel et al. provide a comprehensive summary of performance optimization techniques for streaming computing [48].

While performance is important, *correctness*, which is prerequisite to performance, should be guaranteed first. Correctness of a streaming application means that the application can finish and yield correct results. Even assuming each task of an application executes correctly, there are still factors at network level that can affect correctness, such as deadlocks [67, 94, 102] and failure of hardware or software [52, 8, 120]. In this dissertation, we focus on the correctness of streaming applications, in particular, deadlock avoidance.

## **1.3 Problem Statement**

In streaming computing, some nodes *synchronize* input data and/or *filter* output data in a datadependent and unpredictable fashion. When a streaming application has both filtering and synchronization, it might require unbounded memory to process unbounded streams, which means *deadlock* given bounded memory<sup>5</sup>. Our goal is to execute such applications with bounded memory while avoiding deadlocks.

### **1.3.1** Filtering in Streaming Computing

According to how output streams are produced from input streams, the *producing behaviors* of streaming computing nodes with input data items  $x_i$  can be roughly classified as mapping (e.g.  $x_i \rightarrow x_i+1$ ), reduction or aggregation (e.g.  $x_1, x_2, \ldots, x_N \rightarrow \sum_{i=1}^N x_i$ ), and filtering (e.g.  $x_i \rightarrow x_i$  if  $x_i$  is even *else* nothing). In this dissertation, we focus on the *filtering* behavior. Filtering here means that a node consumes input but does not produce output. It is different from the filtering in signal processing [56, 72], which is actually selective mapping by the definitions above.

Many applications expose filtering behaviors: in computer networking, a packet filter drops packets that fail to meet firewall rules [31]; in machine learning, a classifier filters datasets that do not have the required feature [113]; in a gamma-ray observation system, a data processing module discards images that do not indicate any gamma-ray events [111]. Figure 1.7 shows a filtering module f that receives data from s and sends data that pass its filtering rule to t for further processing.

Figure 1.7: A streaming pipeline with a filtering node.

## 1.3.2 Synchronization for Determinism

According to how input streams are consumed, the *consuming behavior* of a streaming computing node can be synchronized or unsynchronized. Synchronized consumption at a node means that if the node has multiple input channels, it decides the number of data items consumed from each

<sup>&</sup>lt;sup>5</sup>Some people call it "artificial deadlock" to distinguish from deadlocks caused by all empty channels [49, 43].

channel during a computation based on the available data at all input channels. Synchronized consumption or *synchronization* is usually adopted because of its importance to determinism.

To understand synchronization, consider the scenario that f in Figure 1.7 takes a lot of time to process a data item and hence is a performance bottleneck. To speed up data processing, we can add data parallelism to the application by replicating f in multiple copies to process data concurrently, as Figure 1.8 shows. Now t faces a question: when there are data at its input channels, from which channel it should choose to consume data? It can randomly choose a channel, which, however, leads to nondeterminism as the same sequence of input data may result in different output sequence in different runs. Another option is assigning priorities to input channels. For example, if both  $f_1t$  and  $f_2t$  have input data, t chooses to consume data from  $f_1t$ . But this still does not guarantee determinism in the presence of unpredictable delays in data transmission on these channels. Filtering makes the problem more complicated as an anticipated data item may never arrive.

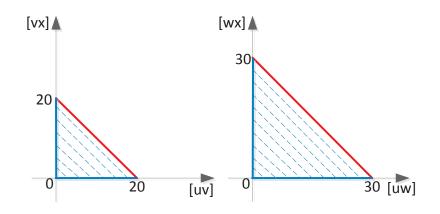

Figure 1.8: A streaming application with multiple filtering nodes.

To counter transmission delay and filtering, we can add a data index to each data item. The data indices at each channel should be strictly increasing so that t can synchronize input data accordingly. If an input channel has no data available, t might have to wait, not consuming data from other channels, because a data item with a lower index might eventually arrive at the empty input channel. However, waiting can cause problems. Imagine that, in a rare situation,  $f_1$  filters all incoming data, but t does not know this and waits for data from  $f_1$ ; in the meantime, both channel

$sf_2$  and channel  $f_2t$  fill up, causing backpressure to s. Now s and  $f_2$  are blocked by full output channels while  $f_1$  and t are waiting on empty input channels, which means a *deadlock*.

If t can poll  $f_1$ , asking whether  $f_1$  has filtered data with indices up to some i, such deadlocks might be avoided. However, we avoid this approach for two reasons. First, it requires a communication channel going the opposite direction from the data channel, which adds listening overhead to the sender and makes it harder to analyze application properties. Second and more importantly, it is difficult for t to decide when it should poll upstream senders; t could end up sending many unnecessary polling requests, only to hurt performance. As a result, instead of letting receivers poll senders, we try to let senders notify receivers about filtering when it is necessary.

### **1.3.3** Synchronization Is a Natural Application Behavior

In the previous example, synchronization is added for determinism when data parallelism is exploited. We may avoid synchronization in Figure 1.8 by not replicating f if we are satisfied with the performance. However, in some applications, synchronization is a natural behavior that cannot be eliminated. Below, we describe an example of such a system, Mercury BLAST [17].

Mercury BLAST is an FPGA-accelerated implementation of the Basic Local Alignment Search Tool (BLAST), a bioinformatics tool for comparing DNA or protein sequences, which is one of the most widely used computational tools in molecular biology. It compares a short query sequence to a large sequence database to discover regions of biologically meaningful similarity between them.

Detailed comparison of a query to any region of a sequence database requires an expensive edit distance computation. To avoid this expensive computation whenever possible, BLAST uses filtering heuristics to quickly discard large portions of the database that are unlikely to match the query sequence. The principal heuristic, *seed matching*, divides the database into overlapping sequences of some short, fixed length w, then tests whether each such "*w-mer*" appears in the query. If a *w*-mer is present at position x in the database and position y in the query, this test generates a *seed match* (x, y). The portions of the database and query near these coordinates are then subjected to further testing to confirm or reject the presence of biologically meaningful similarity. In BLASTN, the variant of BLAST used for DNA sequences, w is on the order of 10 characters, and only about one in 100 database positions generates a seed match even for a query tens of thousands of characters in length.

Mercury BLASTN implements BLASTN's filters as a streaming computation network, with a split-join topology as shown in Figure 1.9. The query is preprocessed into a lookup table stored in seed matching module 1b. The database is then streamed into module 1a, which both divides it into w-mers that are sent to 1b for matching and forwards it unmodified to later stages of the application (represented in the diagram by module 2). Seed matches discovered by 1b are forwarded to module 2 for further testing.

Figure 1.9: The first two stages of Mercury BLAST

Testing a seed (x, y) requires module 2 to inspect a window of the database centered at position x; hence, module 2 cannot discard a given chunk of database sequence until it is sure that no seed match has been found in it. Module 2 must therefore *synchronize* its two input streams to ensure correctness. Moreover, the rate at which module 1b generates seed matches is highly data-dependent: some database regions may generate many matches, while others may generate none over thousands of positions. Because the database input channel to module 2 has a finite buffer (on the order of 64 Kchars), there is a risk of deadlock if 1b happens not to find any seed matches in a long enough piece of the database. The filtering ratio at module 1b is usually higher than 98%, making the application very vulnerable to deadlocks.

In Figure 1.8, all filters  $f_i$  use the same filtering rule. In contrast, in Figure 1.9, multiple data streams from the same node (1a) are processed with different filtering rules (think of an imaginary

node between module 1a and module 2 that simply forwards database locations), which inherently requires synchronization.

### **1.3.4** The Deadlock Issue

As demonstrated by the two example applications above, when filtering and synchronization are both featured in an application, they pose deadlock risk. Bounded memory is part of the reason for deadlocks. If channels have unbounded memory, such deadlocks cannot happen because no node is ever blocked by a full channel. Unfortunately, in real systems, memory is limited, so deadlock is a real threat to streaming applications. For example, Mercury BLAST runs with limited memory resources and does not resize channel buffers during runtime, as is typical in embedded systems. In the rest of the dissertation, the terms *bounded-memory execution* and *deadlock avoidance* are used interchangeably.

Because streaming applications have strong performance requirements, potential deadlock solutions should be lightweight, not causing significant overhead. Considering some applications' inability to resize channel buffers during runtime, potential solutions should not require dynamic buffer resizing.

## **1.4 Summary of Our Approach**

For a specific application, *ad hoc* solutions may be used to avoid deadlocks, but we prefer generic solutions that can be applied to a broad range of applications. To find generic solutions, we turn to designing *dataflow models*. If we can model the range of possible filtering and synchronization behaviors, we can then work on bounded-memory scheduling in such models to provide model-based solutions.

We propose a new model named *synchronized filtering dataflow* (SFDF) featuring both data filtering and synchronization. To prevent deadlocks in SFDF, we augment data streams with special

messages called *dummy messages*. The augmentation is based on both the application's dataflow graph and nodes' runtime behavior. We try to add as few dummy messages as possible to reduce computation and communication overhead. For applications with special dataflow graphs, we can can improve the efficiency of our generic solutions without sacrificing correctness.

Our work involves algorithm design and extensive theorem proving because correctness of execution is our top priority. We also provide experimental evaluation when necessary.

## **1.5** Contributions

In this dissertation, we make the following contributions:

- In Chapter 3, we propose the deterministic *synchronized filtering dataflow* (SFDF) model, which features both filtering and synchronization behaviors. We characterize under what circumstances an SFDF application can deadlock with bounded memory.

- In Chapter 4, we design decentralized algorithms to guarantee bounded-memory execution of SFDF applications. Our algorithms augment data streams with dummy messages. Each algorithm has two parts, a compile-time part and a runtime part. The compile-time part computes a *dummy interval* for each channel; the runtime part schedules dummy messages according dummy intervals. The runtime algorithm adds negligible overhead to applications, but the compile-time algorithm could have high asymptotic complexity.

- In Chapter 5, for applications with special dataflow topologies, we provide efficient compiletime algorithms to compute dummy intervals. In particular, we focus on topologies that are series-parallel DAGs or CS4 DAGs, which are a new category of DAGs defined by us. In a CS4 DAG, each *undirected cycle* has only one source node and one sink node.

- In Chapter 6, we use polyhedral theory to develop safe dummy interval polyhedra to provide multiple sets of safe dummy intervals for application developers. We provide a polynomial-time algorithm to verify the safeness of dummy intervals for SP-DAGs.

• In Chapter 7, we extend our SFDF model to support precise synchronization of data streams and *control messages*. Dummy messages are only one type of control messages that are used by streaming applications. There is also other control information, such as data boundaries and node configurations, that needs to be passed from upstream nodes to downstream nodes. Control messages including dummy message are integrated into the model and precisely synchronized with data streams. Bounded-memory execution of application is still guaranteed. The extended model can help improve performance of some applications by facilitating the conversion of a non-filtering application to a filtering application.

## Chapter 2

## **Background and Related Work**

## 2.1 A Brief History of Streaming Computing

Streaming computing can date back to the 1960s, when the computation graph [58, 76] was proposed as a model for parallel computing. In the early 1970s, another model, Kahn's process network (KPN) [55], was also proposed. Both models feature computing nodes connected by FIFO data channels, which are conceptually similar to today's streaming computing systems. In the 1980s, an influential dataflow model, synchronous dataflow (SDF) [64, 66], was invented by Lee et al. In an SDF application, computing behaviors are static and defined before computations start, which makes static schedules possible. SDF has found success in many areas, especially signal-processing applications [63, 29, 93]. Following SDF, dataflow models such as boolean dataflow and dynamic dataflow were proposed to allow data-dependent node behaviors [14, 15, 65]. Based on those dataflow models, dataflow programming languages, which describe a program as a dataflow system, were designed to explore non-von Neumann programming, such as KPN-based Lucid [7] in the 1970s and SDF-based Lustre [46, 97] in the 1980s. Those models and languages can handle unbounded streams.

Pipelined SIMD processing, which is also a form of streaming computing, began to draw attention in 1990s, when Streaming SIMD Extensions (SSE) were added to x86 architectures for streaming processing [108, 98]. In the 2000s, specialized stream processors were used as coprocessors to take advantage of the power of streaming computing [57, 60, 28, 119]. Meanwhile, the use of GPU for streaming computing was also studied [13, 47, 103]. The use of GPU for pipelined SIMD processing has taken off since then [85]. In recent years, embedded systems such as the field-programmable gate array (FPGA) [44, 80, 54, 100] and multiprocessor System-on-Chip (MPSoC) [50, 99, 116, 122, 81] have also been popular platforms for streaming computing.

Numerous languages and frameworks for processing unbounded streams have also been designed since the early 2000s. StreamIt [109] is a language and a compiler for developing SDFbased applications. Auto-Pipe [20] is a framework for developing streaming applications on architecturally diverse systems. Database management systems (DBMS) are another area in which streaming computing has thrived. Compared with traditional DBMSes, which manage stored finite data, a stream-based DBMS is designed for continuous queries on real-time data streams. Aurora [4] and Borealis [3] are examples of such systems. As big data prevail, streaming computing has become an important choice for data processing in many companies. In recent years, many frameworks have been implemented and used in processing real-time data, such as Storm [1], S4 [83], Kafka [61], and MillWheel [5].

As to applications, streaming computing has found success in many application areas, such as digital signal processing [30, 64, 111, 29], computational biology [37, 53, 71], multimedia [34, 59, 89], database management systems [6, 3, 22], and web data analysis [83, 5].

## 2.2 Models of Streaming Computing

Though streaming computing is a relatively new trend, many formal models of this paradigm have historically been proposed. As this dissertation foci on model-based solutions, we now review some influential models and discuss their ability to model the filtering and synchronization behaviors described in Chapter 1.

### Kahn Process Networks

In the early 1970s, Gilles Kahn introduced a computation model where sequential processes communicate through first-in first-out channels [55], which was later referred to as the Kahn Process Network (KPN). In KPNs, processes are determinate, and channels have unlimited buffering capacity. Each process can be associated with multiple input and output channels, and the data consumption is synchronized for determinism. Filtering is not prohibited in KPNs; however, since channels are assumed to be unbounded, deadlocks due to full data channels do not exist in the model, though they can be a problem in real-world systems.

## **Computation Graphs**

To represent task and pipeline parallelisms in program loops, Karp and Miller formulated *computation graphs* [58], which are structurally similar to KPNs. A computation graph is also a network of processes connected by FIFO queues (or channels). Different from a KPN, each queue is parameterized by a tuple (A, U, W, T), where A is the initial number of data items in the queue, U is the number of data items produced on the queue each time the producing process is fired, and T is number of data items removed from the queue each time the consuming process is fired, and T is the least number of data items required for the consuming process to fire. In [58], the authors provided necessary and sufficient conditions to decide the termination and memory boundedness of computation graph networks. Since data consuming and producing rates are fixed, the model prohibits data-dependent filtering computations.

#### **Synchronous Dataflow**

Synchronous dataflow is a restricted version of KPN or computation graph. Like these models, an SDF network is also a network of computing nodes connected by FIFO channels. Each channel has known and static data consuming and producing rates, which are called *sample rates* [64,

66]. Homogeneous dataflow (HDF) [64] is a special case of SDF where all sample rates are 1. While KPNs and computation graphs are focused on computability issues such as determinacy and termination, the inventors of SDF provided scheduling strategies for bounded-memory execution (if possible), which makes SDF more attractive than the other two models.

A periodic schedule of an SDF application clears all channels and return to its initial status after each node repeats execution a specified finite number of times. With a periodic schedule, the application can process unbounded data with bounded memory. However, not all SDF applications permit a periodic schedule. The sample rates of an SDF application are *consistent* if a periodic schedule exists; otherwise, they are inconsistent. For example, given SDF graphs with indicated sample rates in Figure 2.1, graph 2.1a is inconsistent, and no periodic schedule can be found; graph 2.1b is consistent as node A, B, and C can be executed for 1, 1, and 2 times in a periodic schedule.

Figure 2.1: Examples of SDFs [66]

To compute a periodic schedule, a *topology matrix* is defined in [66], where each row represents an arc and each column represents a node. The (i, j)th element in the matrix is the number of data items placed on i after each invocation of j. If i is an input channel for j, element (i, j) is negative. The topology matrix for Figure 2.1c is as follows:

$$\left(\begin{array}{ccc} c & -e & 0 \\ d & 0 & -f \\ 0 & i & -g \end{array}\right) \cdot$$

Lee et al. proved that given a connected SDF graph, a necessary condition for the existence of a periodic schedule is that the rank of the topology matrix is s - 1, where s is the number of nodes. This condition is sufficient if the SDF topology is a directed acyclic graph. A vector q with positive integers in the nullspace of the topology matrix is a valid repetition vector for the SDF, which can be used to construct a periodic schedule.

Since its invention, SDF has been popular for many applications, especially digital signal processing [64, 10]. The static schedule property is very helpful for orchestrating deadlock-free execution, and it has become a widely used dataflow model. A number of frameworks have been implemented based on it, such as Ptolemy [16] from Berkeley and StreamIt [109] from MIT. However, SDF prohibits data-dependent filtering.

### **Cyclo-Static Dataflow**

Cyclo-Static Dataflow (CSDF) is a variant of SDF [36, 11]. The difference is that instead of static sample rates for each channel, the sample rates change cyclically according to *statically* defined cyclic values. Parks et al. pointed out that CSDF has advantages over SDF in eliminating dead code and exposing additional parallelism [96]. They also provided a method to transform a CSDF graph into an SDF graph using higher-order functions. Like SDF, CSDF also prohibits data-dependent filtering computations.

#### **Boolean Dataflow and Dynamic Dataflow**

SDF and CSDF cannot handle dynamic node behaviors, e.g. conditional execution. Boolean dataflow (BDF) and dynamic dataflow (DDF) were proposed to support dynamic behaviors [14, 15, 65]. Compared to SDF, BDF adds two kinds of *switch nodes*, which are like multiplexers or demultiplexers. A control token tells the switch from which channel a data item should be consumed (for input cases) or to which channel a data item should be produced (for output cases). DDF extends BDF to support control switches to consume multiple control tokens and allow computing nodes

execute conditionally based on input data. BDF and DDF are Turing-complete; however, whether an arbitrary BDF or DDF application can be scheduled with bounded memory is undecidable [14].

#### **Summary of Related Models**

KPNs allow filtering and synchronization, but they are assumed to have unbounded channel buffers, so they have no deadlock associated with full channels. Computation graph, SDF, and variants like CSDF all prohibit filtering, so they cannot model streaming applications with filtering computations. BDF and DDF can model applications with dynamic data rates, but we cannot check whether an arbitrary BDF/DDF application can execute with bounded memory or not. Moreover, although BDFs and DDFs are Turing-complete, implementing filtering behavior on them is not straightforward. In short, none of these existing models can guarantee bounded-memory execution while allowing data-dependent filtering computations.

## 2.3 Deadlock Avoidance Approaches

Deadlocks in computer systems can be divided into two categories: resource deadlocks and communication deadlocks [23]. Resource deadlocks are caused by multiple processes trying to access a resource that must be accessed exclusively, such as the Dining Philosophers' Problem [32, 33]. Communication deadlocks, which usually happen in distributed systems, are caused by multiple processes waiting for communication activity from each other, such as the deadlocks described in Chapter 1.3.4.

Communication deadlocks have been well studied. Chandy et al. developed algorithms to detect distributed deadlocks based on probes [23, 24]. Mitchell and Merritt designed a deadlock detection algorithm using public and private labels [78], which are similar to the notion of Chandy's probes. After raising the issue of artificial deadlock in bounded KPNs, Parks tried to avoid such deadlocks by dynamically increasing channel capacity [95]. Geilen and Basten improved Parks' idea and

proposed a new scheduling algorithm which guarantees fairness and behaves correctly for bounded and effective KPNs [43]. Here "effective" means all tokens produced are ultimately consumed. This algorithm also requires dynamic changes to channel capacity. Olson and Evans improved Mitchell's algorithm to detect local deadlocks in bounded KPNs [87]. All these deadlock avoidance and resolution algorithms require runtime change to channel capacities, while we seek algorithms that do not.

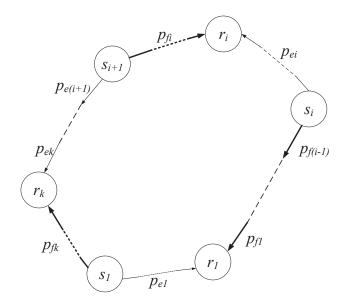

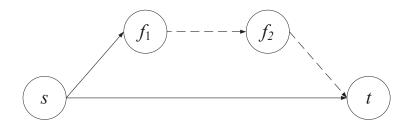

We avoid deadlocks by augmenting data streams with special dummy messages, which are inspired by the null messages [42, 77] in parallel discrete-event simulation (PDES). In a discrete-event simulation, a system operates on a ordered sequence of events with time stamps. PDES utilizes parallel systems and runs multiple processes concurrently during simulation. Figure 2.2 shows a PDES system with multiple processes. At merge point M, events from Proc 1 and Proc 2 need to be synchronized according to their time stamps. After finite time, a deadlock can occur if Proc 1 routes every message to M while Proc 2 does not route any message, which is very similar to the deadlocks we described in streaming computing applications.

Figure 2.2: A parallel discrete-event simulation system from [77].

Chandy and Misra proposed null message-based methods to resolve deadlocks in PDES [23, 77]. A null message (t, null) received by a process p means that no message will show up until time t. Null messages mean the absence of messages and allow receivers to advance their clocks safely to avoid deadlocks. While we use a similar idea in dummy messages, we make contributions in providing provably correct schedules for sending dummy messages.

# Chapter 3

# **The Synchronized Filtering Dataflow**

In streaming computing, filtering and synchronization can cause deadlocks, as we explained in Chapter 1. To prevent such deadlocks and ensure bounded-memory execution, we prefer model-based solutions. In this chapter, we introduce our *synchronized filtering dataflow* (SFDF) model and explain the conditions for deadlocks.

## **3.1** General Description

Besides the basic features of streaming computing described in Chapter 1.2, the SFDF model assumes that dataflow graphs are directed acyclic multigraphs (DAMGs), which are most common in streaming applications. A *multigraph* differs from an ordinary graph in that there can be multiple edges between two vertices. The dataflow graph of a streaming application can be a multigraph when some senders send multiple data streams to their receivers, each of those data streams with its dedicated channel. Figure 3.1 illustrates the notion of multigraph by connecting the sender and the receiver with two channels, which may deliver streams of the same data type (e.g. two streams of integers) or streams of different data types (e.g. a stream of integers and a stream of floats).

Figure 3.1: A pair of nodes connected by two channels.

Each node computes *sequentially* and spends a finite but *unpredictable* amount of time to process an input item, which we call a *token*. There are two types of tokens: tokens that are from the original input data and tokens that are generated by nodes during the computing process to carry control information. When we need to distinguish the two types, we use *data token* to refer to the first type and *control message* or simply *message* (e.g. dummy message) to refer to the second type.

Each channel in the model has a finite buffer capacity, which is known at compile time and does not change during runtime. In practice, it might be possible to shrink or expand the channel buffers of software applications, but for hardware modules (e.g. FPGA applications), it is very hard to change buffer size at runtime, so as a general rule, we assume channel buffers cannot be resized during runtime. We denote the buffer size of channel q as |q|, which means q can hold up to |q| tokens. Channels in our model are reliable and guarantee ordered transmission, so tokens on a channel are received in the same order as they are emitted. However, a system provides no timing guarantee. There may be an arbitrary finite delay before a token emitted into a channel is received. Streams can be bounded or unbounded. If a stream is bounded, there should be an *End-of-Stream* message with index  $\infty$  at the end of the stream.

Each token is associated with an integer, which we call its *data index*. A token emitted into a channel should have a strictly larger index than the ones emitted earlier. Note that those indices might be implicit. For example, in Mercury BLAST, the database stream consists of strictly increasing database locations, which are also indices. Note that indices are not necessarily consecutive; for example, filtering can cause index gaps.

#### 3.1.1 Notations

In this dissertation, we will be consistent with notations for SFDF. Given a dataflow graph, we use letters from  $\{s, t, u, v, w, x, y, z\}$  to represent nodes, and s and t are usually used to represent the sole source node and the sole sink node, respectively. To refer to an *edge* in a graph, we use

*e* or the connected vertices (e.g. uv), while to refer to a *channel* in an application, we use *q*. In most chapters, *e* and *q* can be used interchangeably with the exception of Chapter 7, where an graph edge is associated with two application channels, so we have to distinguish graph edges from application channels. We use *p* to denote a path in a dataflow graph. |a| denotes the length or the buffer size of *a*, which could be an edge, a path, or an application channel. We use *C* to refer to an *undirected cycle* in dataflow graphs. For other notations that are not used frequently, we will explain them when first using them.

# 3.2 Synchronizing and Filtering Behaviors

When a node has multiple input channels, it needs to decide how many tokens to consume from each channel during a computation. In SFDF, a computation at a node *consumes only input tokens with the same index*, which is called the *computation index*. At any time, a node's current computation index is the index of the last set of inputs that it consumed. Computation on data with index i does not require that all input channels contain tokens with that index; it is well-defined even if only a subset of input channels ever receive tokens with index i. However, a node may not proceed to compute for index i unless it knows that no further tokens with this index will ever arrive at its inputs. In other words, input tokens are synchronized by data indices, and all input tokens with the same index must be consumed in one computation. Since no two tokens in a channel have the same index, at most one token can be consumed from a channel during one computation.

A computation may output tokens with the same index as its inputs on any subset of a node's outputs, including the empty set. We say that a computation *filters* a data token on a channel q if it does not result in an output token on q. Filtering is a data-dependent behavior, performed independently by each node, that cannot be predicted at the time that a system is constructed. For example, a filtering node may decide whether to pass a data token depending on the result of a predicate.

Detailed behavior of a single *intermediate* node is described in Algorithm 3.1. For conciseness, we do not explicitly describe single-node behaviors of source node and sink node, which are similar to the behavior of intermediate node except source nodes do not consume tokens and sink nodes do not send tokens. Note that, in this and all following protocols, all **emit** operations block until the output channel is not full.

Algorithm 3.1: Behavior of a single intermediate node in SFDF.

- 1 ComputeIndex  $\leftarrow 0$

- **2 while** *ComputeIndex*  $\neq$  *Index of EOS* **do**

- 3 wait until every input channel has a pending token

- 4 let *i* be minimum index of any pending token

- s consume pending tokens with index i from input channels ComputeIndex  $\leftarrow i$

- 6 **compute** on data tokens with index *i*

- 7 **emit** output tokens with index i

# 3.3 Deadlock Concerns

#### **3.3.1 Deadlock Example**

Due to the filtering and synchronizing behaviors, even if each node runs on an independent computing resource, deadlocks are still a potential threat to the execution of SFDF applications. Figure 3.2 illustrates a deadlock in an SFDF application with four nodes. u and v are blocked due to full channels, while w and x are blocked due to empty channels. If there is unbounded memory, deadlocks like this would not have happened, because there would not be any full channels and the cycle of blocking relations is hence broken. For real-world applications, however, memory and channel buffers are bounded. For applications deployed on embedded platforms such as FPGAs, memory resources can be scarce, and resizing channel buffers during application runtime can be difficult. Even if runtime memory resizing is possible, there is no guarantee that memory would be sufficient to prevent deadlock.

Figure 3.2: A deadlock example in SFDF. Both uv and vx are assumed to have a buffer size of 3.

#### **3.3.2** Conditions for Deadlock

During a computing process, one node may be temporarily blocked by another due to an empty input or full output channel. However, not every blocking situation is a deadlock. In this section, we derive the conditions under which blocking can lead to deadlock in SFDF.

**Definition 3.1** (*Blocking Relation*) If a node v is waiting for input from an upstream neighbor u, or if v is waiting to send output to a downstream neighbor u because the channel buffer between them is full, we say that u blocks v, denoted  $u \dashv v$ . If there exists a sequence of nodes  $v_1 \dots v_n$ such that  $v_i \dashv v_{i+1}$  for  $1 \le i < n$ , we write  $v_1 \dashv^+ v_n$ .

**Definition 3.2** (*Liveness*) *If a node can increase its compute index in finite time, we say the node is live, or equivalently that it* makes progress.

**Definition 3.3** (*Deadlock*) A system is said to deadlock if no node in the system is live, but some channel in the system still retains unprocessed tokens (so that the computation is incomplete).

We now prove that a cycle of blocking relations is a sufficient and necessary condition of deadlock.

**Theorem 3.1 (Deadlock Theorem)** A system eventually deadlocks if and only if, at some point in the computation, there exists a node u s.t.  $u \dashv^+ u$ .

*Proof.* ( $\leftarrow$ ) Suppose that at some point in the computation, there is a node u such that  $u \dashv^+ u$ . Because a blocked node cannot make progress, no node on the cycle involving u can make progress. Hence, once the blocking cycle occurs, it will remain indefinitely. Moreover, not every pair of successive nodes in the cycle can be linked by an empty channel; otherwise, we would have that u is waiting for input from u, which is impossible because the graph of computing nodes is a DAMG. Hence, the blocking cycle contains at least one full channel, which means there are unprocessed tokens, and so the system is deadlocked.

$(\rightarrow)$  Suppose that  $u \dashv^+ u$  does not hold for any node u at any point in the computation. We show that, as long as there is any data in the system, *some* node is able to make progress; hence, the computation will never halt with unprocessed data on a channel.

At any point in the computation, either every node with input data can make progress, or some such node u is blocked. Let H be the directed graph obtained by tracing all blocking relationships outward from u, such that there is an edge from v to w iff  $v \dashv w$ . (H is also called a "waiting-for graph" [23, 78].) By assumption, H has no cycles and is therefore a DAG. Let  $v_0$  be a topologically minimal node in H, which is not blocked by any node. If  $v_0$  has tokens on its input channels, it is able to consume them and so make progress. Otherwise,  $v_0$ 's input channels are all empty, so that it cannot block any upstream neighbors. Moreover, since  $v_0$  itself is not blocked, either it is a source node that can advance its computation index by spontaneously producing tokens, or it must have received the EOS message and so cannot block any downstream neighbors (which contradicts  $v_0$ 's presence in H). Conclude that  $v_0$  is able to make progress, as desired.

**Definition 3.4** (*Blockwise* (not *clockwise*) and *Counterblockwise*) Let C be a cycle of blocked nodes  $v_1 \dots v_n$ , such that  $v_1 \dashv^+ v_n$  and  $v_n \dashv v_1$ . The direction of increasing index on C is called blockwise, while the opposite direction is counterblockwise.

A channel on C between  $v_i$  and  $v_{i+1}$  may be oriented either blockwise from  $v_i$  to  $v_{i+1}$  or counterblockwise from  $v_{i+1}$  to  $v_i$ . Because  $v_i \dashv v_{i+1}$ , a blockwise channel on a blocking cycle is always

*empty, while a counterblockwise channel is always full.* For example, in Figure 3.2, uw and wx are blockwise channels, while uv and vx are counterblockwise channels.

We note that not all systems have deadlocks. For example, a system with just two nodes connected by one channel will never deadlock, even with filtering; the sender can block the receiver because the channel is empty, or the receiver can block the sender because the channel is full, but they cannot block each other at the same time. However, even quite simple systems, such as one with just two nodes connected by two parallel data channels, can deadlock.

We claim that filtering and synchronizing behaviors are two necessary (but not sufficient) conditions for deadlocks in this model.

**Theorem 3.2** (*Filtering Theorem*) If no node ever filters any input, then the system cannot deadlock.

#### Proof.

The proof is by contradiction. Suppose there is a deadlock; then by the Deadlock Theorem, the computation reaches a state in which some node  $y \dashv^+ y$ . Let C be the cycle of blocked nodes that includes y. Each node z on cycle C may be labeled with one of four types, depending on the directions of the channels that link z to its two neighbors in C:

- 1. Both channels are oriented blockwise, as for node w in Figure 3.2;

- 2. Both channels are oriented counterblockwise, as for node v in Figure 3.2;

- 3. The channel located to blockwise of z is oriented blockwise, while that to counterblockwise of z is oriented counterblockwise, as for node u in Figure 3.2;

- 4. The channel located to blockwise of z is oriented counterblockwise, while that to counterblockwise of z is oriented blockwise, as for node x in Figure 3.2.

We now argue that, in the absence of filtering, the minval of a channel on C is always  $\geq$  that of its counterblockwise neighbor. Let z be a node between two channels on the cycle.

- If z has type 1, both channels are empty, with one pointing into z and one pointing out. Because z does not filter, every token input to z causes a token to be emitted; hence, the two channels have the same minval.

- If z has type 2, both channels are full, with the blockwise channel pointing into z and other pointing out. Any value output by z has a strictly smaller index than a value waiting to be input to it, so the blockwise channel has the larger minval.

- If z has type 3, then both channels are outputs from z, and the blockwise channel is empty while the other is full. Because z does not filter, it always emits tokens with a given index on both channels at once. Hence, the minval of the blockwise channel is at least the index of the most recently emitted value on the other channel, which is ≥ the latter's minval.

- If z has type 4, then both channels are inputs to z, and the blockwise channel is full while the other is empty. The minval of the full channel must be strictly greater than that of the empty channel; otherwise, z could consume a value from the full channel.

Hence, the minvals of the channels in C increase monotonically to blockwise. Moreover, because there are no directed cycles in the original network, there is always a node of type 4 in C, and so the minvals of all channels in C cannot be identical. But this is impossible, because traversing the entire cycle implies that the minval of some channel is strictly greater than itself. Conclude that no blocking cycle can exist in the absence of filtering.