#### Electronic Thesis and Dissertation Repository

December 2016

# Towards Comprehensive Parametric Code Generation Targeting Graphics Processing Units in Support of Scientific Computation

Ning Xie

The University of Western Ontario

Supervisor Marc Moreno Maza The University of Western Ontario

Graduate Program in Computer Science

A thesis submitted in partial fulfillment of the requirements for the degree in Doctor of Philosophy

© Ning Xie 2016

Follow this and additional works at: https://ir.lib.uwo.ca/etd

Part of the <u>Numerical Analysis and Scientific Computing Commons</u>, and the <u>Programming Languages and Compilers Commons</u>

#### Recommended Citation

Xie, Ning, "Towards Comprehensive Parametric Code Generation Targeting Graphics Processing Units in Support of Scientific Computation" (2016). *Electronic Thesis and Dissertation Repository*. 4257. https://ir.lib.uwo.ca/etd/4257

This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact tadam@uwo.ca.

### **Abstract**

The most popular multithreaded languages based on the fork-join concurrency model (Cilk-Plus, OpenMP) are currently being extended to support other forms of parallelism (vectorization, pipelining and single-instruction-multiple-data (SIMD)). In the SIMD case, the objective is to execute the corresponding code on a many-core device, like a GPGPU, for which the CUDA language is a natural choice. Since the programming concepts of CilkPlus and OpenMP are very different from those of CUDA, it is desirable to automatically generate optimized CUDA-like code from CilkPlus or OpenMP.

In this thesis, we propose an accelerator model for annotated C/C++ code together with an implementation that allows the automatic generation of CUDA code. One of the key features of this CUDA code generator is that it supports the generation of CUDA kernel code where program parameters (like number of threads per block) and machine parameters (like shared memory size) are treated as unknown symbols. Hence, these parameters need not to be known at codegeneration-time: machine parameters and program parameters can be respectively determined when the generated code is installed on the target machine.

In addition, we show how these parametric CUDA programs can be optimized at compiletime in the form of a case discussion, where cases depend on the values of machine parameters (e.g. hardware resource limits) and program parameters (e.g. dimension sizes of threadblocks).

This generation of parametric CUDA kernels requires to deal with non-linear polynomial expressions during the dependence analysis and tiling phase of the input code. To achieve these algebraic calculations, we take advantage of techniques from computer algebra, in particular in the RegularChains library of Maple. Various illustrative examples are provided together with performance evaluation. Our preliminary implementation uses LLVM, Maple and PPCG; moreover, it successfully processes a variety of standard test-examples.

**Keywords:** Many-core machine model; Parametric CUDA code generation; Polynomial arithmetic; Compiler optimization

### Acknowledgements

With your greatest help, I become who I am today. With your enlightenment, I achieve what I have today.

Special thanks sincerely for the insightful guidance from Prof. Marc Moreno Maza and the great collaboration with Prof. Robert M. Corless, Dr. Changbo Chen, Dr. Yuzhen Xie, Dr. Sardar A. Haque, Svyatoslav Covanov, Farnam Mansouri, Robert H.C. Moir and Xiaohui Chen. Many thanks to industry partners: Dr. Jürgen Gerhard from Maplesoft R&D department, and Wang Chen, Abdoul-Kader Keita and Jeeva Paudel from IBM compiler group for making this research work have practical uses.

Big thanks to the supervisory committees: Prof. Mark Daley and Prof. Yuri Boykov for advices and comments. It is my honor to have Dr. Matteo Frigo, Prof. Robert M. Corless, Prof. Michael Bauer and Prof. Roberto Solis-Oba as the examiners. I would like to express my gratitude for their comments and questions. With all my heart, I appreciate the continued support of my parents, colleagues, friends, the ORCCA laboratory and the Computer Science Department of The University of Western Ontario.

The work was supported by NSERC of Canada, MITACS, Maplesoft Inc. and IBM Corp..

# **Contents**

| Al | bstrac     | et            |                                                       | İ   |  |

|----|------------|---------------|-------------------------------------------------------|-----|--|

| A  | cknov      | vledgen       | nents                                                 | ii  |  |

| Li | st of l    | Figures       |                                                       | V   |  |

| Li | st of      | <b>Fables</b> |                                                       | X   |  |

| Li | st of      | Algoritl      | hms                                                   | xi  |  |

| Li | st of A    | Append        | lices                                                 | xii |  |

| 1  | Intr       | oductio       |                                                       | 1   |  |

|    | 1.1<br>1.2 |               | ibutions of this thesis                               |     |  |

| 2  |            | kgroun        |                                                       | 10  |  |

| 4  | 2.1        | _             | u<br>ls of computation                                |     |  |

|    | 2.1        | 2.1.1         | Fork-join model                                       |     |  |

|    |            | 2.1.1         | PRAM model                                            |     |  |

|    | 2.2        |               | al-purpose GPU computing                              |     |  |

|    | 2.2        | 2.2.1         | The Compute Unified Device Architecture (CUDA)        |     |  |

|    |            | 2.2.2         | Modern GPU architectures                              |     |  |

|    | 2.3        |               | arithmetic over finite fields with the CUMODP library |     |  |

|    | 2.4        |               | etaFork language                                      |     |  |

|    | 2.5        |               | natic parallelization in the polyhedral model         |     |  |

|    |            | 2.5.1         | $\mathbb{Z}$ -polyhedron                              |     |  |

|    |            | 2.5.2         | Polyhedral iteration domain                           |     |  |

|    |            | 2.5.3         | Data dependence graph                                 |     |  |

|    |            | 2.5.4         | Dependence polyhedron                                 |     |  |

|    |            | 2.5.5         | Affine transformation                                 |     |  |

|    |            | 2.5.6         | Farkas multipliers                                    | 24  |  |

|    |            | 2.5.7         | Feautrier's algorithm                                 |     |  |

|    |            | 2.5.8         | PLUTO's algorithm                                     | 25  |  |

|    | 2.6        | Solvin        | ng systems of polynomial equations and inequalities   | 26  |  |

| 3  | The        | Basic I       | Polynomial Algebra Subprograms                        | 30  |  |

|   | 3.1            | Design and specification                                  | 30       |

|---|----------------|-----------------------------------------------------------|----------|

|   | 3.2            | User interface                                            | 31       |

|   | 3.3            | Implementation techniques                                 | 34       |

|   | 3.4            | Experimental evaluation                                   | 35       |

|   | 3.5            | Application                                               | 37       |

| 4 | A M            | any-Core Machine Model                                    | 41       |

|   | 4.1            | Introduction                                              | 41       |

|   | 4.2            | A many-core machine model                                 | 43       |

|   |                | 4.2.1 Characteristics of the abstract many-core machines  | 43       |

|   |                | 4.2.2 Many-core machine programs                          |          |

|   |                | 4.2.3 Complexity measures for the many-core machine model |          |

|   |                | 4.2.4 A Graham-Brent theorem with parallelism overhead    |          |

|   | 4.3            | The Euclidean algorithm                                   |          |

|   | 4.4            | Fast Fourier Transform                                    | 52       |

|   |                | 4.4.1 Cooley & Tukey algorithm                            |          |

|   |                | 4.4.2 Stockham algorithm                                  |          |

|   |                | 4.4.3 Comparison of running time estimates                |          |

|   | 4.5            | Polynomial multiplication                                 |          |

|   |                | 4.5.1 Plain multiplication                                |          |

|   |                | 4.5.2 FFT-based multiplication                            |          |

|   |                | 4.5.3 Comparison of running time estimates                |          |

|   | 4.6            | Radix sort                                                |          |

|   | 4.7            | Conclusion                                                |          |

| 5 | Meta           | aFork-to-CUDA: Generation of Parametric CUDA Kernels      | 63       |

|   | 5.1            | Optimizing CUDA kernels depending on program parameters   |          |

|   | 5.2            | Automatic parametric CUDA kernel generation               |          |

|   | 5.3            | The MetaFork-to-CUDA code generator                       |          |

|   | 5.4            | Experimentation                                           |          |

|   | 5.5            | Conclusion                                                |          |

| 6 | Con            | aration of Ontimized CUDA Kornel Code                     | 84       |

| U | 6.1            |                                                           | 84       |

|   | 6.2            | •                                                         | 90       |

|   | 6.3            | <del>-</del>                                              | 90<br>94 |

| _ | -              |                                                           | ۰.       |

| 7 | <b>Tow</b> 7.1 | r                                                         | 96<br>99 |

|   | 7.1            | 7.1.1 Hypotheses on the input code fragment               |          |

|   |                | 7.1.1 Hypotheses on the input code fragment               |          |

|   |                | 7.1.2 Hardware resource mints and performance measures    |          |

|   |                | 7.1.3 Evaluation of resource and performance counters     |          |

|   |                | 7.1.4 Optimization strategies                             |          |

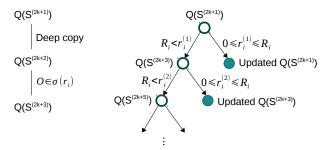

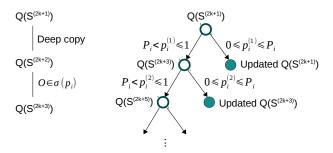

|   |                | 7.1.6 Data-structures                                     |          |

|   |                | 1.1.V 12010-0010V011V0                                    |          |

|    | 7.1.7 The algorithm                                                       | 104 |

|----|---------------------------------------------------------------------------|-----|

|    | 7.2 Comprehensive translation of an annotated C program into CUDA kernels | 109 |

|    | 7.2.1 Input MetaFork code fragment                                        | 110 |

|    | 7.2.2 Comprehensive translation into parametric CUDA kernels              |     |

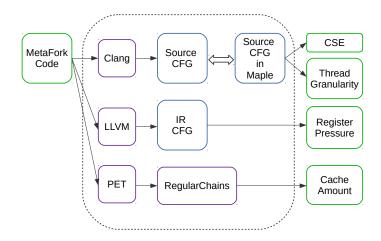

|    | 7.3 Implementation details                                                | 111 |

|    | 7.4 Experimentation                                                       |     |

|    | 7.5 Conclusion                                                            | 121 |

| 8  | Conclusion and Future Work                                                | 123 |

| Bi | oliography                                                                | 125 |

| A  | Sample Code in the BPAS Library                                           | 135 |

|    | A.1 Adaptive algorithms                                                   | 135 |

|    | A.2 User interfaces                                                       |     |

| В  | Theoretical Analysis of Fundamental Algorithms Using the MCM Model        | 139 |

| C  | Documentation for MetaFork-to-CUDA Code Generator                         | 181 |

|    | C.1 Assumptions on the sytax of MetaFork statements                       | 181 |

|    | C.2 Schedule tree for MetaFork and parametric CUDA code                   | 183 |

| D  | <b>Examples Generated by PPCG</b>                                         | 188 |

| E  | The Implementation for Generating Comprehensive MetaFork Programs         | 193 |

| Cı | rriculum Vitae                                                            | 196 |

# **List of Figures**

| 1.1  | A C program for reversing a one-dimensional array                                                                                                                                                                                                                                                     | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | The CUDA program for reversing a one-dimensional array                                                                                                                                                                                                                                                | 3  |

| 1.3  | Parametric CUDA kernel for reversing a one-dimensional array                                                                                                                                                                                                                                          | 4  |

| 1.4  | Two CUDA kernels based on possible values of machine and program parameters for reversing a one-dimensional array, where $Z$ is the maximum number of shared memory words per processor supported by the hardware architecture and $R$ is the maximum number of registers per thread supported by the |    |

|      | hardware architecture                                                                                                                                                                                                                                                                                 | 6  |

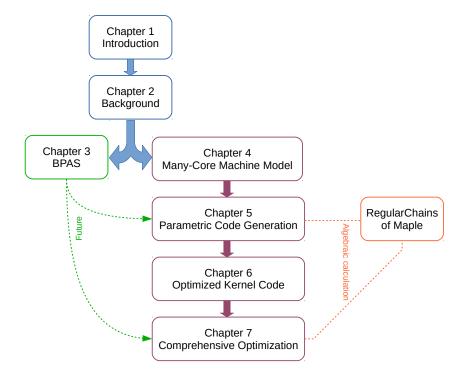

| 1.5  | Overview of the thesis                                                                                                                                                                                                                                                                                | 8  |

| 2.1  | An example of computation DAG: Fourth Fibonacci                                                                                                                                                                                                                                                       | 11 |

| 2.2  | Matrix multiplication written in CilkPlus                                                                                                                                                                                                                                                             | 12 |

| 2.3  | Overview of a hybrid CPU-GPU system                                                                                                                                                                                                                                                                   | 13 |

| 2.4  | Execution of a CUDA program                                                                                                                                                                                                                                                                           | 14 |

| 2.5  | Using MetaFork to translate a given CilkPlus program into a OpenMP program                                                                                                                                                                                                                            | 18 |

| 2.6  | Using MetaFork to translate a given OpenMP program into a CilkPlus program                                                                                                                                                                                                                            | 18 |

| 2.7  | Using MetaFork to translate a given OpenMP program into a CilkPlus program                                                                                                                                                                                                                            | 19 |

| 2.8  | For-loop nest in the polyhedral model                                                                                                                                                                                                                                                                 | 20 |

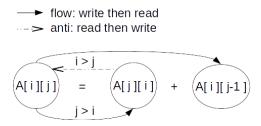

| 2.9  | An example of the data dependence graph of the source program                                                                                                                                                                                                                                         | 22 |

|      | The transformed code based on time and processor coordinates                                                                                                                                                                                                                                          | 24 |

| 2.11 | A triangular decomposition into semi-algebraic systems computed with the                                                                                                                                                                                                                              |    |

|      | RealTriangularize command                                                                                                                                                                                                                                                                             | 28 |

| 2.12 | Output of the RealTriangularize command for the EVE surface                                                                                                                                                                                                                                           | 28 |

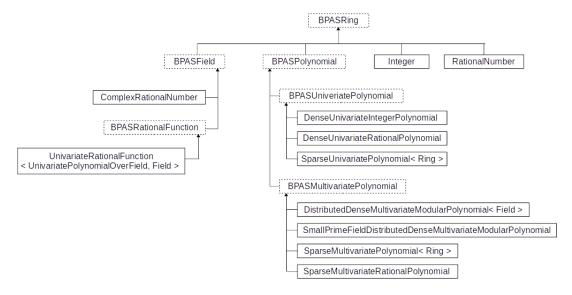

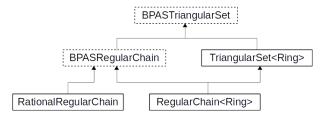

| 3.1  | A subset of BPAS algebraic data structures                                                                                                                                                                                                                                                            | 32 |

| 3.2  | Another subset of BPAS algebraic data structures                                                                                                                                                                                                                                                      | 33 |

| 3.3  | A snapshot of BPAS code                                                                                                                                                                                                                                                                               | 33 |

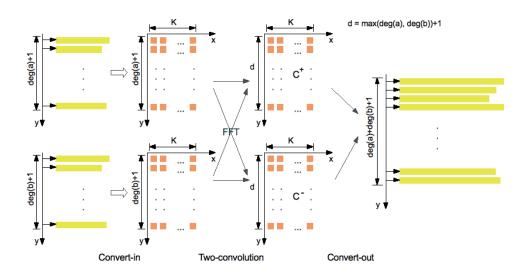

| 3.4  | Multiplication scheme for dense univariate integer polynomials                                                                                                                                                                                                                                        | 35 |

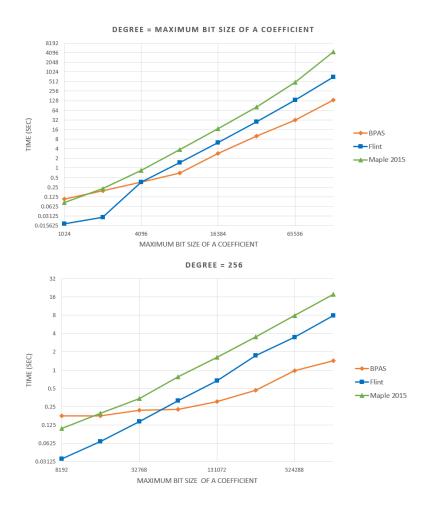

| 3.5  | Dense integer polynomial multiplication: BPAS vs FLINT vs Maple                                                                                                                                                                                                                                       | 36 |

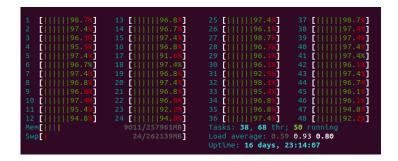

| 3.6  | The htop screenshot of multiplying two large integer polynomials in BPAS                                                                                                                                                                                                                              | 37 |

| 3.7  | An example of matchable interval lists                                                                                                                                                                                                                                                                | 39 |

| 3.8  | A sample output of realSymbolicNumericIntegrate                                                                                                                                                                                                                                                       | 40 |

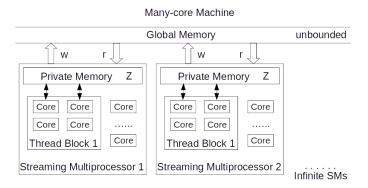

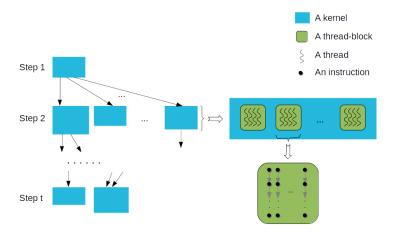

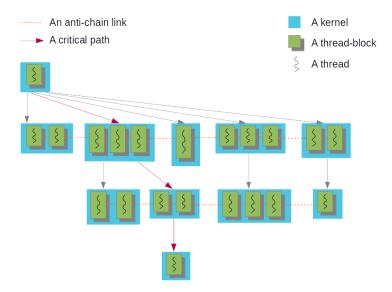

| 4.1  | Overview of an abstract many-core machine                                                                                                                                                                                                                                                             |    |

| 4.2  | Overview of a many-core machine program                                                                                                                                                                                                                                                               |    |

| 4.3  | An example of a thread-block DAG                                                                                                                                                                                                                                                                      | 48 |

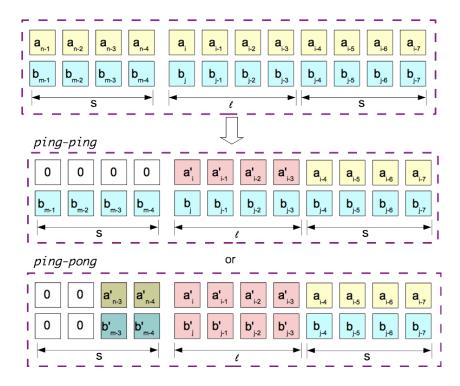

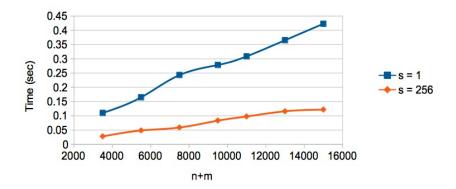

| 4.4  | Illustration of reads and writes by a thread-block in either ping-ping or ping-pong phase of the Euclidean algorithm                                                           |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.5  | Running time on GeForce GTX 670 of our multithreaded Euclidean algorithm for univariate polynomials of sizes $n$ and $m$ over $\mathbb{Z}/p\mathbb{Z}$ , where $p$ is a 30-bit |

|      | prime, whereas the program parameter takes values $s = 1$ and $s = 256$ 5                                                                                                      |

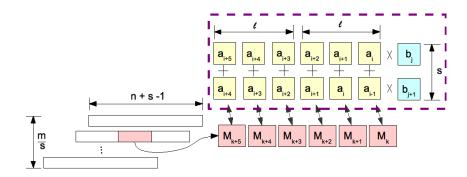

| 4.6  | Multiplication phase: illustration of a thread-block reading coefficients from a,                                                                                              |

|      | b and writing to the auxiliary array $M$                                                                                                                                       |

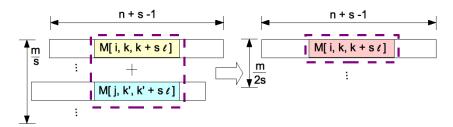

| 4.7  | Addition phase: illustration of a thread-block reading and writing to the auxil-                                                                                               |

|      | iary array $M$                                                                                                                                                                 |

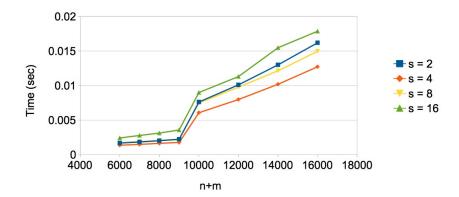

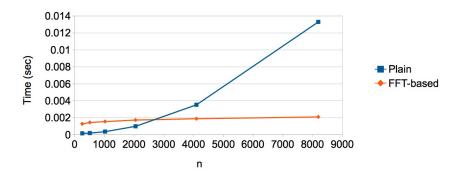

| 4.8  | Running time of the plain polynomial multiplication algorithm with polynomials $a$ (deg( $a$ ) = $n$ – 1) and $b$ (deg( $b$ ) = $m$ – 1) and the parameter $s$ on GeForce      |

|      | GTX 670                                                                                                                                                                        |

| 4.9  | Running time of the plain and FFT-based multiplication algorithms with the input size <i>n</i> on GeForce GTX 670                                                              |

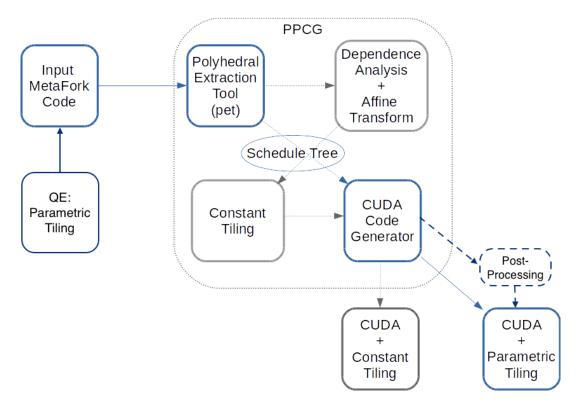

| 5.1  | Overview of the implementation of the MetaFork-to-CUDA code generator 6                                                                                                        |

| 5.2  | One-dimensional stencil computation, namely Jacobi, written in C                                                                                                               |

| 5.3  | 1D Jacobi written in MetaFork                                                                                                                                                  |

| 5.4  | Generated parametric CUDA kernel for 1D Jacobi                                                                                                                                 |

| 5.5  | Generated host code for 1D Jacobi                                                                                                                                              |

| 5.6  | Serial code, MetaFork code and generated parametric CUDA kernel for array reversal                                                                                             |

| 5.7  | Serial code, MetaFork code and generated parametric CUDA kernel for 2D Jacobi 7                                                                                                |

| 5.8  | Serial code, MetaFork code and generated parametric CUDA kernel for LU decomposition                                                                                           |

| 5.9  | Serial code, MetaFork code and generated parametric CUDA kernel for matrix transpose                                                                                           |

| 5.10 | Serial code, MetaFork code and generated parametric CUDA kernel for matrix addition                                                                                            |

| 5.11 | Serial code, MetaFork code and generated parametric CUDA kernel for matrix vector multiplication                                                                               |

| 5.12 | Post-processing CUDA kernel with coalesced accesses for matrix vector multiplication                                                                                           |

| 5.13 | Serial code, MetaFork code and generated parametric CUDA kernel for matrix                                                                                                     |

|      | matrix multiplication                                                                                                                                                          |

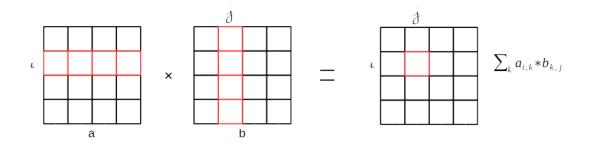

| 6.1  | Multiplication of two matrices                                                                                                                                                 |

| 6.2  | The MetaFork code with the granularity loop and good data alignment for                                                                                                        |

|      | matrix multiplication                                                                                                                                                          |

| 6.3  | Post-processing the generated CUDA kernel code for matrix multiplication with                                                                                                  |

|      | the granularity loop                                                                                                                                                           |

| 6.4  | CUDA kernel with unrolling the granularity loop for matrix multiplication 8                                                                                                    |

| 6.5  | The serial C code with good data locality for matrix multiplication 9                                                                                                          |

| 6.6  | The MetaFork code and its kernel code with the granularity loop for reversing                                                                                                  |

|      | a one-dimensional array                                                                                                                                                        |

| 6.7<br>6.8 | The MetaFork code and its kernel code with the granularity loop for 1D Jacobi The MetaFork code and its kernel code with the granularity loop for matrix | 93 |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 0.0        | • • •                                                                                                                                                    | 93 |

| 6.9        | The MetaFork code and its kernel code with the granularity loop for matrix transpose                                                                     | 94 |

| 6.10       | The MetaFork code and its kernel code with the granularity loop for matrix vector multiplication                                                         | 95 |

| 7.1        | Matrix addition written in C (the left-hand portion) and in MetaFork (the right-                                                                         |    |

|            | hand portion) with a meta_for loop nest, respectively                                                                                                    | 97 |

| 7.2        | Comprehensive translation of MetaFork code to two kernels for matrix addition                                                                            | 98 |

| 7.3        | 1 1                                                                                                                                                      | 99 |

| 7.4        | Matrix vector multiplication written in C (the left-hand portion) and in Meta-<br>Fork (the right-hand portion), respectively                            | 02 |

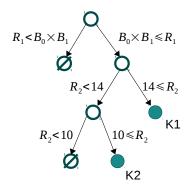

| 7.5        | The decision subtree for resource or performance counters                                                                                                |    |

| 7.6        | The serial elision of the MetaFork program for matrix vector multiplication 1                                                                            |    |

| 7.7        | The software tools involved for the implementation                                                                                                       |    |

| 7.8        | Computing the amount of words required per thread-block for reversing a 1D                                                                               |    |

|            | array                                                                                                                                                    | 13 |

| 7.9        | The first case of the optimized MetaFork code for array reversal                                                                                         | 14 |

| 7.10       | The second case of the optimized MetaFork code for array reversal 1                                                                                      | 15 |

| 7.11       | The third case of the optimized MetaFork code for array reversal                                                                                         | 15 |

| 7.12       | The first case of the optimized MetaFork code for matrix vector multiplication 1                                                                         | 15 |

| 7.13       | The second case of the optimized MetaFork code for matrix vector multiplication 1                                                                        | 16 |

| 7.14       | The third case of the optimized MetaFork code for matrix vector multiplication 1                                                                         | 16 |

| 7.15       | The MetaFork source code for 1D Jacobi                                                                                                                   | 17 |

|            | The first case of the optimized MetaFork code for 1D Jacobi                                                                                              |    |

| 7.17       | The second case of the optimized MetaFork code for 1D Jacobi                                                                                             | 18 |

| 7.18       | The third case of the optimized MetaFork code for 1D Jacobi                                                                                              | 18 |

| 7.19       | The first case of the optimized MetaFork code for matrix addition                                                                                        | 19 |

| 7.20       | The second case of the optimized MetaFork code for matrix addition 1                                                                                     | 19 |

| 7.21       | The third case of the optimized MetaFork code for matrix addition                                                                                        | 19 |

| 7.22       | The first case of the optimized MetaFork code for matrix transpose 12                                                                                    | 20 |

| 7.23       | The second case of the optimized MetaFork code for matrix transpose 12                                                                                   | 20 |

| 7.24       | The third case of the optimized MetaFork code for matrix transpose 12                                                                                    | 20 |

| 7.25       | The first case of the optimized MetaFork code for matrix multiplication 12                                                                               | 21 |

| 7.26       | The second case of the optimized MetaFork code for matrix multiplication 12                                                                              | 21 |

| 7.27       | The third case of the optimized MetaFork code for matrix multiplication 12                                                                               | 22 |

| C.1        | An example of the meta_schedule statement                                                                                                                | 82 |

| D.1        | PPCG code and generated CUDA kernel for array reversal                                                                                                   |    |

| D.2        | PPCG code and generated CUDA kernel for matrix addition                                                                                                  |    |

| D.3        | PPCG code and generated CUDA kernel for 1D Jacobi                                                                                                        | 89 |

| D.4        | PPCG code and generated CUDA kernel for 2D Jacobi                                                                                                        | 89 |

| D.5 | PPCG code and generated CUDA kernel for LU decomposition             | 190 |

|-----|----------------------------------------------------------------------|-----|

| D.6 | PPCG code and generated CUDA kernel for matrix vector multiplication | 191 |

| D.7 | PPCG code and generated CUDA kernel for matrix transpose             | 191 |

| D.8 | PPCG code and generated CUDA kernel for matrix multiplication        | 192 |

# **List of Tables**

| 3.1<br>3.2 | One-dimensional modular FFTs: Modpn vs BPAS                                                                                                      | 34<br>37   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.3        | Univariate real root isolation running times (in secs.) for four examples                                                                        | 38         |

| 3.4        | Running times (in secs.) of multivariate real root isolation: BPAS vs Maple 17                                                                   | 30         |

|            | RealRootIsolate vs C (with Maple 17 interface) Isolate                                                                                           | 40         |

| 4.1        | Running time (in secs) of the Cooley & Tukey and Stockham FFT algorithms with the input size <i>n</i> on GeForce GTX 670                         | 55         |

| 5.1        | Speedup comparison of reversing a one-dimensional array between PPCG and MetaFork kernel code                                                    | <b>7</b> 4 |

| 5.2        | Speedup comparison of 1D Jacobi between PPCG and MetaFork kernel code                                                                            | 75         |

| 5.3        | Speedup comparison of 2D Jacobi between PPCG and MetaFork kernel code                                                                            | 75         |

| 5.4        | Speedup comparison of LU decomposition between PPCG and MetaFork kernel code                                                                     | 77         |

| 5.5        | Speedup comparison of matrix transpose between PPCG and MetaFork kernel                                                                          | , ,        |

| 0.0        | code                                                                                                                                             | 77         |

| 5.6        | Speedup comparison of matrix addition between PPCG and MetaFork kernel                                                                           |            |

|            | code                                                                                                                                             | 79         |

| 5.7        | Speedup comparison of matrix vector multiplication among PPCG kernel code,<br>MetaFork kernel code and MetaFork kernel code with post-processing | 80         |

| 5.8        | Speedup comparison of matrix multiplication between PPCG and MetaFork                                                                            | 00         |

| 2.0        | kernel code                                                                                                                                      | 81         |

| 5.9        | Timings (in sec.) of quantifier elimination for eight examples                                                                                   | 82         |

| 6.1        | Experimental results of matrix multiplication for the CUDA kernel with the                                                                       |            |

|            | shared memory for the output matrix and the granularity of threads                                                                               | 86         |

| 6.2        | Experimental results of matrix multiplication for the CUDA kernel with the local                                                                 |            |

|            | memory for the output matrix and the granularity of threads                                                                                      | 88         |

| 6.3        | For input matrices of order $2^{10}$ , speedup factors of the matrix multiplication                                                              |            |

|            | kernel unrolling the computation                                                                                                                 | 88         |

| 6.4        | For input matrices of order $2^{10}$ , speedup factors of the matrix multiplication                                                              |            |

|            | kernel unrolling the copy-in, computation and copy-out phases with a compilation float manufacture 40                                            | 00         |

| 6.5        | lation flagmaxrregcount=40                                                                                                                       | 90         |

| 0.5        | post-processing, respectively, w.r.t. the serial C code with good data locality                                                                  |            |

|            | for matrix multiplicationm                                                                                                                       | 91         |

|            | 1                                                                                                                                                |            |

| 6.6  | Speedup factors of reversing a one-dimensional array for input vector of length                 |     |

|------|-------------------------------------------------------------------------------------------------|-----|

|      | $2^{25}$                                                                                        | 91  |

| 6.7  | Speedup factors of 1D Jacobi for time iteration 4 and input vector of length 2 <sup>15</sup> +2 | 92  |

| 6.8  | Speedup factors of matrix addition for input matrix of order $2^{12}$                           | 92  |

| 6.9  | Speedup factors of matrix transpose for input matrix of order $2^{14}$                          | 94  |

| 6.10 | Speedup factors of matrix vector multiplication for input matrix of order 2 <sup>13</sup>       |     |

|      | and input vector of length $2^{13}$ (An error indicates that the total amount of re-            |     |

|      | quired shared memory exceeds the hardware limit.)                                               | 94  |

| 7.1  | Optimization strategies with their codes                                                        | 114 |

# **List of Algorithms**

| 1 | OptGcdKer(a,b,s,da,db)                                                                 |

|---|----------------------------------------------------------------------------------------|

| 2 | PlainMultiplicationGPU $(a, b, s)$                                                     |

| 3 | MulKer $(a, b, M, n, m, s)$                                                            |

| 4 | $AddKer(M,f,y,s,x,i)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |

| 5 | ComprehensiveOptimization $(Q(S))$                                                     |

| 6 | Optimize                                                                               |

| 7 | MultiParametricCodeOptimizer(fileName)                                                 |

| 8 | Optimize( <i>plan</i> , <i>task</i> )                                                  |

| 9 | Optimize( <i>plan</i> , <i>task</i> )                                                  |

# **List of Appendices**

| Appendix A Sample Code in the BPAS Library                                    | 135 |

|-------------------------------------------------------------------------------|-----|

| Appendix B Theoretical Analysis of Fundamental Algorithms Using the MCM Model | 139 |

| Appendix C Documentation for MetaFork-to-CUDA Code Generator                  | 181 |

| Appendix D Examples Generated by PPCG                                         | 188 |

| Appendix E The Implementation for Generating Comprehensive MetaFork Programs  | 193 |

# Chapter 1

## Introduction

It is well known that the impact of the high-performance software for both numerical and exact linear algebra on engineering and scientific computing is tremendous, worthy of the great efforts that have been put for more than thirty years. The most significant results are software projects like BLAS [76], LAPACK [3], ATLAS [121] and LinBox [43]. The same remark should be extended to the processing of linear transforms, in particular, Fast Fourier Transforms, where notable works are the SPIRAL [98] and FFTW [48] projects, as well as to computer algebra, see the recent proceedings of the international workshop on parallel symbolic computation (PASCO) [44, 88, 89].

The successful techniques employed in those software projects include implementation of highly efficient algorithms for basic routines, block-based algorithms for better exploiting the memory hierarchies, parallel and distributed processing, as well as automatically optimizing and tuning code on different platforms. This trend has been stimulated by the advent of hardware acceleration technologies (multicore processors, cell processors, general-purpose graphics processing units (GPGPUs), field programmable gate arrays (FPGAs)) provide vast opportunities for innovation in computing. In particular, GPGPUs combined with *low-level heterogeneous programming models*, such as CUDA (the *Compute Unified Device Architecture*, see [95, 73]), brought super-computing to the level of the desktop computer.

However, these low-level programming models carry notable challenges, even to expert programmers. Indeed, fully exploiting the power of hardware accelerators by writing CUDA code often requires significant code optimization efforts. While such efforts can yield high performance, it is desirable for many programmers to avoid the explicit management of the hardware accelerator, e.g. data transfer between the host (or CPU) and the device (or GPGPU) or between memory levels of the device. For this reason, the most popular multithreaded languages, in particular CilkPlus [10, 79] and OpenMP [41, 13, 9], are based on the fork-join concurrency model targeting multi-core architectures rather than GPGPUs. Currently, these multithreaded languages are being extended to support other forms of parallelism, such as vectorization, pipe-lining and single-instruction-multiple-data (SIMD). In the SIMD case, the case we are interested in this thesis, the objective is to execute the corresponding code on a many-core GPGPU, for which the CUDA language is a natural choice.

To overcome the challenge of developing software targeting many-core GPGPUs, *high-level* models for accelerator programming, notably OpenMP and OpenACC [113, 56], have become an important research direction. With these models, programmers only need to annotate

their C/C++ (or FORTRAN) code to indicate which portion of code is to be executed on the device, and how data is mapped between the host and the device.

In OpenMP and OpenACC, the work distributed among the processors of the device can be expressed in a loose manner or even ignored. This implies that code optimization techniques must be applied in order to derive efficient CUDA code. Moreover, existing software packages (e.g. PPCG [115], C-to-CUDA [6], hiCUDA [57], CUDA-CHiLL [101]) for generating CUDA code from annotated C/C++ programs, either let the user choose, or make assumptions on the characteristics of the targeted hardware and on how the work is divided among the processors of that device. These choices and assumptions limit *code portability* as well as opportunities for *code optimization*. This latter fact will be illustrated with the following example for reversing a one-dimensional array.

**Example 1** Consider the C program on Figure 1.1 for reversing a one-dimensional array, where each element of the input vector In is moved to the appropriate position of the output vector Out. Figure 1.2 gives a corresponding CUDA program, where the host code, shown on Figure 1.2(a), launches a kernel on the device, shown on Figure 1.2(b). Note that the kernel code makes a few assumptions:

- (1) The array length N is less than the maximum number of threads that the hardware architecture supports.

- (2) 32 divides N.

2

In order to launch a kernel function, one must specify the grid and thread-block formats (introduced in Section 2.2). In our example of Figure 1.2 32 threads per thread-block and N/32 thread-blocks per grid are specified for kernel0. Observe also that the program explicitly handles the data placement on the device, for instance, on Figure 1.2, allocating shared memory for array In and using the global memory for array Out.

```

int N, In[N], Out[N];

// Initializing

for (int i = 0; i < N; i++)

In[i] = i+1;

// Reversing the array In

for(int i = 0; i < N; i++)

Out[N-1-i] = In[i];</pre>

```

Figure 1.1: A C program for reversing a one-dimensional array

The C-to-CUDA code generation introduced in [6] is known to be the first source-to-source polyhedral framework (see Section 2.5 for the term *polyhedral*) that translates serial C programs into CUDA programs. However, manual post-processing, such as placing synchronization statements in the kernel code, is required for generating a compilable CUDA kernel.

PPCG [115] automatically generates CUDA code from a given serial C program. In particular, Feautrier's and PLUTO's algorithms, respectively presented in [46] and [15], are adopted by the PPCG designers for exploring parallelization opportunities in serial programs.

```

int N, In[N], Out[N];

// Initializing

for (int i = 0; i < N; i++)

In[i] = i+1;

int *dev_In, *dev_Out;

// Allocating memory spaces on the device

cudaMalloc((void **) &dev_In, (N)*sizeof(int));

cudaMalloc((void **) &dev_Out, (N)*sizeof(int));

// Copying the data from host to device

cudaMemcpy(dev_In, In, (N)*sizeof(int), cudaMemcpyHostToDevice);

cudaMemcpy(dev_Out, Out, (N)*sizeof(int), cudaMemcpyHostToDevice);

// Launching the kernel

dim3 dimBlock(32);

dim3 dimGrid(N/32);

kernel0 <<<dimGrid, dimBlock>>> (dev_In, dev_Out, N);

// Copying the data from device to host

cudaMemcpy(Out, dev_Out, (N)*sizeof(int), cudaMemcpyDeviceToHost);

// Freeing the memory spaces on the device

cudaFree(dev_In);

cudaFree(dev_Out);

(a) The host code

__global__ void kernel0(int *In, int *Out, int N) {

int idx = blockIdx.x * 32 + threadIdx.x;

__shared__ int shared_In[32];

if (idx < N) {

shared_In[threadIdx.x] = In[idx];

__syncthreads();

Out[N-1-idx] = shared_In[threadIdx.x];

}

}

(b) The device code

```

Figure 1.2: The CUDA program for reversing a one-dimensional array

However, by default, PPCG uses 32 (resp.  $16 \times 32$ ) as the thread-block format in the generated one-dimensional (resp. two-dimensional) kernels; meanwhile, PPCG also allows the user to pass a numerical value as the thread-block format.

hiCUDA (acronym for high-level CUDA) [57] is defined as a directive-based language for generating CUDA programs from C programs. To be precise, hiCUDA relies on the pragma mechanism provided by the C/C++ standards to indicate how the work is distributed among

threads and how the data is mapped on the device. However, the grid and thread-block formats of a kernel must be specified as integer expressions.

CUDA-CHill [101] presents a script-based compiler framework for transforming annotated C programs to CUDA programs. Moreover, in [72], a transformation strategy generator is introduced with CUDA-CHill, such that several candidate CUDA kernels are generated, by varying data placement (shared memory or register) and numerical values of parameters (like thread-block sizes). Then, empirical evaluation of those candidate CUDA kernels is performed so as to select the CUDA kernel with the best performance by the end.

In summary, for those CUDA kernels generated by PPCG, C-to-CUDA, hiCUDA and CUDA-CHiLL, the program parameters (e.g. the number of threads per thread-block) and the machine parameters (e.g. the shared memory size) are numerical values instead of unknown symbols.

In this thesis, we propose an accelerator model for annotated C/C++ code, together with an implementation, that allows the automatic generation of CUDA code. One of the key features of this CUDA code generator is that it supports the generation of CUDA kernel code where program parameters (like number of threads per block) and machine parameters (like shared memory size) are treated as unknown symbols. Thus, machine parameters can be specialized to actual values when the generated CUDA code is compiled on the targeted hardware. The program parameters can be either optimized by techniques developed in this thesis or automatically tuned at run-time. As an illustration, following up on Example 1, a CUDA kernel code depending on one program parameter, along with a kernel function call from the host, is shown in Figure 1.3 where the variable B specifies the thread-block format. Observe that kernel1 takes the program parameter B as an argument, whereas the kernel0 in Figure 1.2 takes data parameters In, Out and N only.

```

__global__ void kernel1(int *In, int *Out, int N, int B) {

int idx = blockIdx.x * B + threadIdx.x;

// BLOCK_0 should be pre-defined as a constant

// and be equal to B

__shared__ int shared_In[BLOCK_0];

if (idx < N) {

shared_In[threadIdx.x] = In[idx];

__syncthreads();

Out[N-1-idx] = shared_In[threadIdx.x];

}

}

// The kernel function call from the host

dim3 dimBlock(B);

dim3 dimGrid(N/B);

kernel1 <<<dimGrid, dimBlock>>> (dev_In, dev_Out, N, B);

```

Figure 1.3: Parametric CUDA kernel for reversing a one-dimensional array

Furthermore, given machine parameters represented as unknown symbols as well, we aim at optimizing CUDA kernels, such that for each possible value of the machine and program parameters, we provide a correspondingly optimal CUDA kernel. Of course, the meaning of *optimal* has to be clearly defined, which will be done in Chapter 7.

To continue with our example, consider two machine parameters for the targeted GPGPU device:

- Z: the maximum number of shared memory words per processor supported by the hardware architecture.

- *R*: the maximum number of registers per thread supported by the hardware architecture. For the C program in Example 1, we generate two CUDA kernels based on the possible values of the machine and program parameters, see Figure 1.4.

Observe that each thread in kernel2 moves two elements of array In to the corresponding positions of array Out, whereas kernel1 is identical to the kernel in Figure 1.3. By doing so, kernel2 increases arithmetic intensity so as to hide the data transfer time between the global and shared memories for array In; however, this increases both register usage (from 6 to 8) and shared memory usage (from B to 2\*B) machine words. Therefore, kernel2 works correctly and is optimal under the system of the constraints  $C_2$  but not under the system of the constraints  $C_1$ .

#### 1.1 Contributions of this thesis

One of main objectives of this thesis is to generate CUDA kernels with program and machine parameters represented by unknown symbols. We call such kernels *parametric*. These parameters need not be known at code-generation time. Machine parameters (e.g. shared memory size) and program parameters (e.g. number of threads per thread-block) can be, respectively, determined when the generated CUDA code is installed on the targeted hardware. The challenge here is that any manipulation of non-linear expressions to be generated in the CUDA kernel requires specific code generation techniques relying on algebraic computation.

A second objective is to optimize parametric CUDA programs at compile-time, in the form of a case discussion, where cases depend on the possible values of machine parameters and program parameters. This leads us to the concept of *comprehensive parametric* CUDA *kernels*. To be more precise, given an input annotated C code., this is a decision tree, where each edge holds a Boolean expression (given by polynomial constraints) and each leaf is either a CUDA program such that for each leaf *K* we have:

- 1. *K* works correctly under the conjunction of the Boolean expressions located between the root node and the leaf, and

- 2. *K* is semantically equivalent to *C*.

In each Boolean expression, the unknown variables represent machine parameters and program parameters. This case discussion can be handled by techniques from symbolic computation. Automatic parametric kernel code generation can, then, be achieved by means of combining an optimizing compiler and a computer algebra system.

A third objective of this thesis is to measure the performance of *parametric* algorithms or programs targeting many-core devices like GPGPUs. To this end, a model of multithreaded computation targeting many-core architectures is introduced, such that one can either tune a program parameter to determine a value range minimizing parallelism overheads, or compare different multi-threaded algorithms solving the same problem.

```

__global__ void kernel1(int *In, int *Out, int N, int B)

int idx = blockIdx.x * B + threadIdx.x;

// BLOCK_0 should be pre-defined as a constant

// and be equal to B

__shared__ int shared_In[BLOCK_0];

if (idx < N) {

C_1: \left\{ B \leq Z < 2B \right.

shared_In[threadIdx.x] = In[idx];

\cup \left\{ \begin{array}{c} 6 \leq R < 8 \end{array} \right.

__syncthreads();

Out[N-1-idx] = shared_In[threadIdx.x];

}

dim3 dimBlock(B);

dim3 dimGrid(N/B);

kernel1 <<<dimGrid, dimBlock>>> (dev_In, dev_Out, N, B);

__global__ void kernel2(int *In, int *Out, int N, int B)

int even_idx = blockIdx.x * 2 * B + 2 * threadIdx.x;

int odd_idx = blockIdx.x * 2 * B + 2 * threadIdx.x + 1;

// BLOCK_0 should be pre-defined as a constant

// and be equal to B

__shared__ int shared_In[2*BLOCK_0];

if (even_idx < N && odd_idx < N) {</pre>

C_2: \left\{ \begin{array}{l} 2B \le Z \\ 8 \le R \end{array} \right.

shared_In[2*threadIdx.x] = In[even_idx];

shared_In[2*threadIdx.x+1] = In[odd_idx];

__syncthreads();

Out[N-1-even_idx] = shared_In[2*threadIdx.x];

Out[N-1-odd_idx] = shared_In[2*threadIdx.x+1];

}

}

dim3 dimBlock(B);

dim3 dimGrid(N/(2*B));

kernel2 <<<dimGrid, dimBlock>>> (dev_In, dev_Out, N, B);

```

Figure 1.4: Two CUDA kernels based on possible values of machine and program parameters for reversing a one-dimensional array, where Z is the maximum number of shared memory words per processor supported by the hardware architecture and R is the maximum number of registers per thread supported by the hardware architecture

We observe that classical models of parallel computation, namely the fork-join concurrency model [11] and the parallel random access machine (PRAM) model [110, 51], do not distinguish between the task-based and data-based parallelism. Thus, those models are too simplistic for analyzing algorithms targeting GPGPUs.

### 1.2 Outline of this thesis

In Chapter 2, various topics related to our work are reviewed. We first discuss briefly classical models of computation for concurrency platforms. In particular, we review the CUDA programming model and some important features of modern GPU architectures [36, 37]. We also

review the MetaFork language [29], which is a linguistic extension of C/C++ with high-level parallel programming constructs. Similarly to OpenMP and OpenACC, the MetaFork language offers a *high-level* model for accelerator programming. We stress the fact that this thesis does not deal with dependence analysis and the computation of schedules in automatic parallelization; this can be done via the polyhedral model [46, 15] that we briefly review in Chapter 2. Finally, in that same chapter, we give an overview of the algorithmic tools [4, 25, 23, 24, 112, 22] for dealing with systems of non-linear polynomial equations and inequalities.

In Chapter 3, we present the *Basic Polynomial Algebra Subprograms* (BPAS) library for arithmetic operations with univariate and multivariate polynomials, dense or sparse. The BPAS library is written in CilkPlus targeting multi-core architectures. The original goal of this thesis was to investigate how to integrate code targeting GPGPUs (for instance, from the CUMODP library) within the BPAS library. These two libraries, BPAS and CUMODP, are developed in our research group; moreover, this leads us to the idea of developing frameworks, such as Meta-Fork, for translating programs between different concurrency platforms. We also note that, the BPAS library, as a computer algebra library targeting high-performance, could also be used, in the future, for improving the efficiency of our algebraic tools for generating parametric CUDA kernels. The work reported in Chapter 3 is an extended version of [20] as well as a joint project with Changbo Chen, Svyatoslav Covanov, Farnam Mansouri, Robert Moir, Marc Moreno Maza and Yuzhen Xie. Appendix A lists sample codes from the BPAS library.

Chapter 4 presents a model of multithreaded computation with an emphasis on estimating the parallelism overheads of programs targeting many-core machines. To evaluate the performance of a given CUDA-like program, we consider three complexity measures, namely *work*, *span* and *parallelism overhead*. We also extend the Graham-Brent theorem so as to estimate the running time of a CUDA-like program on a given number of streaming multiprocessors. We evaluate the benefits of our model on six fundamental algorithms, including the Euclidean algorithm for univariate polynomial GCDs, two fast Fourier transform algorithms, the plain and FFT-based univariate polynomial multiplication algorithms, and radix sort [103]. Each studied algorithm is either implemented in the CUMODP library or reported in [103]. We observe that experimentation is coherent with the theoretical analysis based on our model. The work in Chapter 4 is an extended version of [61] as well as a joint project with Sardar Anisul Haque and Marc Moreno Maza.

Chapter 5 reports on a preliminary implementation of the C-to-CUDA code generator discussed above. Generating parametric CUDA kernels implies dealing with non-linear polynomial expressions, particularly during the tiling phase. To achieve these algebraic calculations, we take advantage of quantifier elimination (QE) and its implementation of the RegularChains library of Maple [27]. In order to illustrate the merits of parametric CUDA kernels, we use our code generator on eight test cases: array reversal, 1D Jacobi, 2D Jacobi, LU decomposition, matrix transposition, matrix addition, matrix vector multiplication and matrix matrix multiplication. The performance evaluation of the generated CUDA programs of each test case is provided as well. Chapter 5 is related to [19] and is joint work with Changbo Chen, Xiaohui Chen and Marc Moreno Maza. Appendix C provides documentation of our MetaFork-to-CUDA code generator, while Appendix D collects the generated CUDA programs by PPCG for those same eight test cases.

In Chapter 6, based on the experimental results conducted in Chapter 5, we study advanced optimization techniques, such as the controlling granularity of threads and loop unrolling, We

8

use six test cases so as to verify whether these techniques can, in general, further improve the performance of parametric CUDA kernels. For each test case, since we use the MetaFork language as the high-level accelerator programming model, the portion of the code that should be translated into CUDA kernels is annotated manually. Along with the previous chapter, experimentation shows that the generation of parametric CUDA kernels can lead to significant performance improvement w.r.t. approaches based on the generation of CUDA kernels that are not parametric. Moreover, for certain test cases, our experimental results show that the optimal choices for program parameters may depend on the problem size.

In Chapter 7, we propose an algorithm for *comprehensive optimization* of an annotated C program, depending on parameters treated as symbols at compile-time. We use this algorithm to generate *optimized parametric* CUDA *kernels* in the form of a case discussion based on the possible values of the machine and program parameters. In our preliminary implementation of the *comprehensive optimization* algorithm, we consider two machine parameters: register usage per thread and required shared memory per thread-block; meanwhile, we apply four code optimization strategies: caching data in local or shared memory, reducing register usage per thread, controlling thread granularity and eliminating common sub-expressions. This is *a proof-of-concept* implementation written in Maple and dedicated to the comprehensive generation of optimized MetaFork programs from an input MetaFork program. For each of the six test cases: array reversal, matrix vector multiplication, 1D Jacobi, matrix addition, matrix transpose and matrix matrix multiplication, three optimized MetaFork programs are generated with systems of constraints. Chapter 7 is joint work with Xiaohui Chen and Marc Moreno Maza. Appendix E provides the pseudo-codes of the implemented algorithms.

Figure 1.5: Overview of the thesis

To summarize, Figure 1.5 gives an overview of this thesis. The BPAS library is freely

available in source at http://www.bpaslib.org, and the MetaFork-to-CUDA code generator is freely available in source at http://www.metafork.org.

In the future, we plan to apply our MetaFork-to-CUDA code generator to efficiency-critical routines of the BPAS library code. Meanwhile, we plan to improve the run-time performance of our MetaFork-to-CUDA code generator by using BPAS instead of Maple for dealing with the non-linear expressions arising in the generation of parametric CUDA code.

# Chapter 2

# **Background**

In this chapter, we review background materials related to our work. Section 2.1 is dedicated to classical models of parallel computation. Section 2.2 discusses briefly the features of modern GPU architectures and the programming model CUDA. Section 2.3 gives an overview of the CUMODP library, which is used in the experimentation reported in Chapter 4. In Section 2.4, we present the MetaFork language, which serves as a high-level parallel programming model for automatic CUDA code generation in Chapters 5, 6 and 7. In Section 2.5, we study Feautrier's and PLUTO's algorithms in the so-called *polyhedral model*. Finally, Section 2.6 is an overview of the algorithmic tools used for dealing with systems of polynomial equations and inequalities.

## 2.1 Models of computation

Based on Flynn's taxonomy [47], *single instruction multiple data* (SIMD) is defined as one of the categories of parallel computers, where multiple processing units execute the same instructions on multiple data sets. In this scheme, data is distributed across different processing units so as to achieve *data parallelism*. In contrast, *task parallelism* distributes tasks (or functions) to different processing units.

As mentioned before, with the pervasive ubiquity of many-core processors, in particular GPUs, models of computation must take into account both task-based and data-based parallelism. In fact, popular concurrency platforms (such as CilkPlus [10, 79], CUDA [95, 73] and OpenCL [111]) offer both forms of parallelism, with parallel constructs specific to each case.

Hereafter, we review two classical models of parallel computation, the fork-join model in Section 2.1.1 and the parallel RAM (PRAM) model in Section 2.1.2. Those models do not distinguish between task-based parallelism and data-based parallelism; thus, those models are too simplistic for analyzing algorithms targeting many-cores.

### 2.1.1 Fork-join model

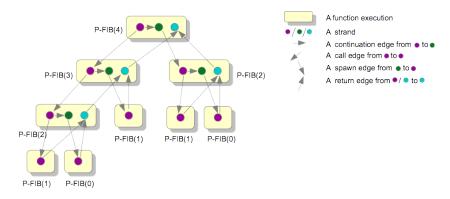

In the fork-join model [11], one can consider a multithreaded program (see Chapter 27 in [34]) as a directed acyclic graph G = (V, E), called *computation DAG*. Figure 2.1 shows the computation DAG for calculating the 5-th Fibonacci number, namely  $F_4$ , where  $F_n = F_{n-1} + F_{n-2}$  if

$n \ge 2$  and  $F_0 = F_1 = 1$  otherwise. In a multithreaded program, we call a *strand* a sequence of consecutive instructions without parallel constructs.

Figure 2.1: An example of computation DAG: Fourth Fibonacci

This model defines two complexity measures:

- 1. the work  $T_1$  of a multithreaded computation is the total time to execute the entire computation on one processor, and

- 2. the span  $T_{\infty}$  is the longest time to execute the strands along any path in the DAG. Assuming that each strand executes in unit time, the work is the number of vertices, and the span equals the number of vertices on a longest path or *critical path* in the computation DAG.

Those two measures, work and span, and one machine parameter, the number P of processors, can be combined in results like the Graham-Brent theorem ([11, 53]) or the Blumofe-Leiserson theorem (Theorems 13 & 14 in [12]) in order to give running time estimates. We recall that the Graham-Brent theorem states that the running time  $T_P$  on P processors satisfies  $T_P \leq T_1/P + T_\infty$ . A refinement of this latter theorem actually supports the implementation (on multi-core architectures) of the parallel performance analyzer, called Cilkview [63]. In this context, the running time  $T_P$  is bounded in expectation by  $T_1/P + 2\delta T_\infty$ , where  $\delta$  is a constant (called the *span coefficient*) and  $\widehat{T_\infty}$  is the so-called *burdened span*.

The fork-join model has become popular with the development of the concurrency platform CilkPlus [10, 79] targeting multi-core architectures. An example of code written in CilkPlus is given in Figure 2.2 for computing matrix multiplication. This CilkPlus code is implemented with a divide & conquer method and the blocking strategy reported in [49] by Frigo, Leiserson, Prokop and Ramachandran.

#### 2.1.2 PRAM model

The PRAM model [110, 51] is defined as a synchronous model of parallel computation. The PRAM machine consists of a number of processors, each of which is a RAM with a private local memory, and a shared memory that processors communicate with. Since the amount of shared memory is limited, it restricts the amount of data that can be communicated between processors in one step.

Moreover, the PRAM model defines four types of accesses to the same shared memory cell with respect to read and write operations. These four types are *exclusive read exclusive write*

```

/**

* Square matrices A, B, C of order N

* The base case size is set to X

* Call to parallel_dandc(0, N, 0, N, 0, N, A, B, C, N, X);

void parallel_dandc(int i0, int i1, int j0, int j1, int k0, int k1, int* A,

int* B, int* C, int N, int X) {

int di = i1 - i0;

int dj = j1 - j0;

int dk = k1 - k0;

if (di >= dj \&\& di >= dk \&\& di >= X) {

int mi = i0 + di / 2;

cilk_spawn parallel_dandc(i0, mi, j0, j1, k0, k1, A, B, C, N, X);

parallel_dandc(mi, i1, j0, j1, k0, k1, A, B, C, N, X);

cilk_sync;

}

else if (dj >= dk \&\& dj >= X) {

int mj = j0 + dj / 2;

cilk_spawn parallel_dandc(i0, i1, j0, mj, k0, k1, A, B, C, N, X);

parallel_dandc(i0, i1, mj, j1, k0, k1, A, B, C, N, X);

cilk_sync;

}

else if (dk >= X) {

int mk = k0 + dk / 2;

parallel_dandc(i0, i1, j0, j1, k0, mk, A, B, C, N, X);

parallel_dandc(i0, i1, j0, j1, mk, k1, A, B, C, N, X);

}

// The base case using the serial, naive matrix multiplication

for (int i = i0; i < i1; ++i)

for (int j = j0; j < j1; ++j)

for (int k = k0; k < k1; ++k)

C[i * N + j] += A[i * N + k] * B[k * N + j];

}

}

```

Figure 2.2: Matrix multiplication written in CilkPlus

(EREW), concurrent read exclusive write (CREW), exclusive read concurrent write (ERCW) and concurrent read concurrent write (CRCW). At one step, "exclusive" indicates that at most one processor can read from or write to the same memory cell, while "concurrent" indicates that processors can simultaneously read from or write to the same memory cell. The advantage of the PRAM model is that it focuses on designing efficient parallel algorithms in terms of arithmetic operations while ignoring communication issues. In addition, all memory accesses are assumed to take place in constant time. Unfortunately, concrete machines cannot currently scale to large numbers of processors while preserving uniformly fast access time to the shared memory.

An attempt to integrate memory contention into the PRAM model has been made with the *queue read queue write* (QRQW) PRAM, defined in [52]. This model enhances the Graham-Brent theorem with memory access time. However, both time spent in arithmetic operations

and time spent in read/write accesses are conflated in a single quantity. We believe that this unification is not appropriate for recent many-core processors, such as NVIDIA GPUs, for which the ratio between one global memory read/write access and one floating point operation can be in the 100's.

A more practical PRAM model is proposed in [51] called *asynchronous PRAM*. Unlike the PRAM model, the processors of an asynchronous PRAM run asynchronously, that is, each processor executing its instructions independently without interrupting others. It considers subset independent synchronization and fixed communication delays for global reads/writes. However, this family of PRAM is not suitable to modern GPUs, since it is trivial to consider a machine parameter for synchronization, which is not an issue for modern GPUs.

## 2.2 General-purpose GPU computing

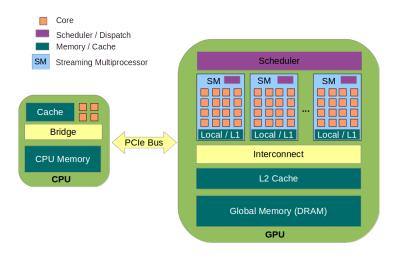

Figure 2.3: Overview of a hybrid CPU-GPU system

General-purpose GPU computing has evolved from graphics processors to massively parallel many-core multiprocessors with the adoption of co-processing between the CPU and the GPU. In such a hybrid CPU-GPU system, GPUs can be used to accelerate a portion of sequential code by employing task-parallelism and data-parallelism. Figure 2.3 shows an overview of a typical CPU-GPU system architecture. One of the main differences between the CPU and the GPU is the number of cores that are designed for different types of execution. Indeed, a GPU device consists of several *streaming multiprocessors* (SMs); meanwhile, each SM consists of a large number of processing cores. For this reason, these cores are particularly designed to take advantage of parallel execution in the SIMD (*single instruction multiple data*) manner. While memory coherence is maintained by the CPU, the programmer needs to explicitly deal with data management on the GPU. Section 2.2.1 introduces the programming model, the *Compute Unified Device Architecture* (CUDA). In Section 2.2.2, we summarize the characteristics of modern GPU architectures.

14 Chapter 2. Background

### **2.2.1** The Compute Unified Device Architecture (CUDA)

CUDA is the programming model introduced to implement parallel algorithms on NVIDIA GPU devices [95, 73]. A CUDA program consists of one or more blocks of code that are executed on either the host (CPU) or the device (GPU). On the host, the code is implemented with little or no parallelism, while on the device, the code is designed to exhibit a rich amount of task or data parallelism, in particular, in a SIMD fashion.

Figure 2.4: Execution of a CUDA program

The execution of a typical CUDA program is shown in Figure 2.4. It starts with the serial C/C++ code and then launches a kernel on the device to execute the parallel code. Upon the completion of the kernel, the process resumes to the execution of serial code on the host. When a kernel function is invoked, the number of thread-blocks and the number of threads per thread-block are specified, according to the problem size, by the programmer. The syntax for launching a kernel from the host code extends that of a C function call with kernel execution configuration parameters surrounded by <<< and >>>, where the execution configuration parameters define the dimensions of the grid and the dimensions of each thread-block. All the threads comprising a kernel during an invocation are collectively called a *grid*.

In addition, the programmer needs to allocate the problem size on the device memory using the keyword cudaMalloc and free the device memory after computation using the keyword cudaFree. To transfer pertinent data between the host and allocated device memories, one can use the keyword cudaMemcpy, with cudaMemcpyHostToDevice and cudaMemcpyDeviceTo-Host specifying where the data is copied from and to. The function type qualifier \_\_global\_\_¹, written prior to a function declaration, indicates that the function is a kernel; meanwhile, on the host, this kernel is called to generate a grid of threads on the device. Moreover, threadIdx,

<sup>&</sup>lt;sup>1</sup>See http://docs.nvidia.com/cuda/cuda-c-programming-guide/index.html for CUDA C programming guide.