## LEARNING IN SILICON: A FLOATING-GATE BASED, BIOPHYSICALLY INSPIRED, NEUROMORPHIC HARDWARE SYSTEM WITH SYNAPTIC PLASTICITY

A Thesis Presented to The Academic Faculty

by

Stephen Brink

In Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the School of Biomedical Engineering

Georgia Institute of Technology December 2012

## LEARNING IN SILICON: A FLOATING-GATE BASED, BIOPHYSICALLY INSPIRED, NEUROMORPHIC HARDWARE SYSTEM WITH SYNAPTIC PLASTICITY

#### Approved by:

Professor Jennifer Hasler, Advisor School of Electrical and Computer Engineering Georgia Institute of Technology

Professor David Anderson School of Electrical and Computer Engineering Georgia Institute of Technology

Asst. Professor Pamela Bhatti School of Electrical and Computer Engineering Georgia Institute of Technology Assoc. Professor Robert Liu Department of Biology Emory University

Professor Steve DeWeerth School of Biomedical Engineering Georgia Institute of Technology

Date Approved: 23 August 2012

To my amazing family and friends.

Your love, support, and companionship

mean the world to me.

### ACKNOWLEDGEMENTS

One of the most gratifying moments of a major accomplishment is giving credit to all of the people who have helped along the way, and I certainly have a lot of people to thank, so here goes. To my parents, thank you for inspiring my love of learning, and for guiding and supporting my 24-year-long education every step of the way. More importantly, thank you for teaching me to value honesty, to not fear hard work, and to treat others with respect and love. You are the most important good influence in my life.

To Lauren, thank you for brightening my life for the past 5 years. You have helped me keep things in perspective through the ups and downs of graduate school. I am thrilled and excited for us to enter the next stage of our lives together.

To David and Jared, Earl and Cindy, Dylan, Christian and Sarah, Nick and Amber, Ryan and Laveeta, Aubrey, Travis, Andrew, Wes, Ali, and Quill, thank you for the countless hours that we have spent together. You have enriched my life in so many ways. I have learned so much from you all, and you have challenged and inspired me to be the best that I can be. I cherish the happy memories of times we have had, and look forward to many more to come.

To Mark van Schilfgaarde, thank you for giving me my first opportunity to participate in a scientific research effort. Thank you for introducing me to the extremely rewarding study of modern physics. You were my first role model of a scientist who expects and demands that the theory agrees with experiment, and your example remains influential to me to this day.

I have had the privilege of learning from some excellent educators throughout my life, but Denis Kirkley, Dan Ayub, Ian Gould, and Jerry Coursen have been especially influential to me. Thank you all for your dedication to maintaining the highest standard of education, and thank you for the incredibly positive impact you have had on my life.

Arindam Basu, thank you for being a fantastic mentor to me. I have learned so much from you about IC design, mathematics, and dynamics. Working closely with you was one of the highlights of graduate school for me. I can't enumerate the contributions you made to my work because you influenced all of it.

Richie Wunderlich, thank you for the many enlightening discussions of quantum physics and semiconductor devices. Thank you for teaching me most of what I know about digital design, for your instruction and technical support regarding CAD tools and IC layout, and for your significant contributions to the adaptive FPAA, the tunneling studies, and the neuron IC. Thank you so much for providing moral support at the moments when I needed it most. Also thanks for including me in memorable events such as the hot tub camping.

Steve Nease, thank you for your huge contributions to the neuron IC, including the mismatch characterization, STDP measurements, help with layout, and countless coding and debugging details. A significant portion of the credit for the successes of this effort belongs to you, and I'm excited to see what you do with this research effort in the future. Thank you also for the many discussions about philosophy of science and life in general, and for your incredibly positive and cooperative attitude. Collaborating with you has been a delight.

Scott Koziol, thank you for your early work on the PCB designs, for teaching me about the PCB CAD tools, and for the rewarding collaboration on the path planning project. Thanks for the countless administrative tasks you have performed through the years to support the lab. Thanks for lending a sympathetic ear in times of frustration, and for your bright personality that has always made our lab a more enjoyable place to work.

Shubha Ramakrishnan, thank you for your help with the design of the neuron IC and your significant contributions to the STDP implementation and measurements. Farhan Adil, thank you for your help with the neuron IC design, and for providing me with your insights about RF design and IC design in general. Brian "Degs" Degnan, thanks for your help with the neuron IC layout, the USB coding for the microcontroller, for helping out with creating artwork at various times, and for the test chip that you made that proved so valuable for my research. Thanks also for making the lab a more interesting place by always saying things that nobody else would dream of saying, regaling us with your (tall?) tales, sharing your amazingly unique life experiences, and keeping me fixed up with new music. Jordan Gray, thanks for so many interesting technical discussions about circuits and systems and computing, and thanks for willingly helping me get set up with useful software and hardware tools. Bo Marr, thanks for including me in some of your interesting research early in my graduate career, and for being such a fun companion at the Telluride Neuromorphic Workshop. Hakan Toreyin and Jon Bergdoll, thank you for your willing help with the neuron IC layout. Craig Schlottmann, thanks for your early work on the PCB design. Sam Shapero, thanks for engaging me in some very interesting discussions about neural computing, neural modeling, and circuit design. You continue to impress me with your work, and a few of your ideas have been very influential to me. Gokce Gurun and Jaime Zahorian, thank you for providing me with die photos of my ICs. Csaba Petre, thanks for sharing my enthusiasm for neural computation, and for the interesting discussions that resulted.

To the "older generation"— Chris Twigg, Ryan Robucci, Dave Abramson, Kofi Odame, Thomas Peng, and Christal Gordon— thank you for the legacy of hardware, software, and general know-how that you passed down, and for your belief in me, for the inspiration to accomplish great things, and for the many nuggets of sage advice.

To Suma George, presently the lone representative of the "younger generation",

thanks for the fun discussions that we've had. I look forward to seeing some exciting results of your research. Thank you to my many colleagues in BME and ECE for providing companionship, camaraderie, and inspiration. In particular, thank you to Jon Newman, Keith Van Antwerp, and Prashanth Challa for some engaging and influential scientific discussions.

Thanks to my committee for thoughtful critiques of my research, and for your positive influence on my graduate career through the various roles that you have played.

To Jennifer Hasler, my advisor, thank you for facilitating my involvement in neuro-morphic engineering research. You have helped me to realize goals and ambitions that I have had for many years prior to coming to Georgia Tech. I have learned a tremendous amount about semiconductor devices and circuit design from you. You introduced me to fascinating field of IC design and insisted that I become an expert in it. This has created many exciting possibilities for a rewarding career for me in the future. Thank you for always pushing me to excel and for helping me out at crucial times when I was struggling.

Thanks to the wonderful faculty and staff of the BME and ECE schools and the bioengineering program.

Thanks to the NSF for providing the majority of my funding by way of the IGERT program and the graduate research fellowship. Special thanks to Steve DeWeerth and Rob Butera for doing such a great job with the IGERT program. Thanks to DARPA for providing some funding for my work, through the CT2WS, SyNAPSE, and IRIS programs.

## Contents

| DE            | EDIC          | ATIO   | N                                                         | iii  |

|---------------|---------------|--------|-----------------------------------------------------------|------|

| AC            | CKN           | OWLE   | DGEMENTS                                                  | iv   |

| LIS           | вт о          | F TAE  | BLES                                                      | xi   |

| LIS           | вт о          | F FIG  | URES                                                      | xii  |

| $\mathbf{SU}$ | MM            | ARY .  |                                                           | viii |

| Ι             | $\mathbf{TH}$ | E BIG  | PICTURE                                                   | 1    |

|               | 1.1           | Goals: | neural and analog computing                               | 1    |

|               |               | 1.1.1  | Why study neural computing?                               | 1    |

|               |               | 1.1.2  | The importance of computational modeling                  | 3    |

|               |               | 1.1.3  | Computational modeling by numerical integration           | 5    |

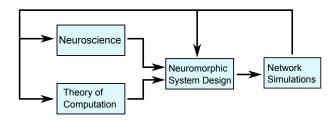

|               |               | 1.1.4  | The neuromorphic approach                                 | 7    |

|               |               | 1.1.5  | Analog computing                                          | 9    |

|               | 1.2           | Metho  | ods: VLSI and floating-gate transistor technology         | 10   |

|               | 1.3           | Achiev | vements: from devices to systems                          | 12   |

| II            | $\mathbf{BU}$ | ILDIN  | G BLOCKS FOR FLOATING-GATE SYSTEMS                        | 14   |

|               | 2.1           | Hardw  | vare platform                                             | 14   |

|               | 2.2           | Fast a | and flexible software interface                           | 17   |

|               |               | 2.2.1  | Communication speed and floating gate programming times . | 17   |

|               |               | 2.2.2  | Flexible framework to support multiple hardware systems   | 17   |

|               |               | 2.2.3  | Specialized functions for data acquisition                | 18   |

|               | 2.3           | Appro  | each for floating-gate transistor programming             | 18   |

|               |               | 2.3.1  | Modeling hot electron injection                           | 19   |

|               |               | 2.3.2  | Reasoning for injection algorithm                         | 22   |

|               | 2.4           | FPAA   | circuits measured in this framework                       | 25   |

| III          |     | W DEVICE CHARACTERISTICS: BI-DIRECTIONAL TUN-LING           | 36  |

|--------------|-----|-------------------------------------------------------------|-----|

|              | 3.1 | Floating-gate array programming and bidirectional tunneling | 36  |

|              | 3.2 | Modeling floating-gate voltage and electron tunneling       | 39  |

|              | 3.3 | Measured tunneling characteristics                          | 45  |

|              | 3.4 | Choosing bidirectional tunneling parameters                 | 50  |

|              | 3.5 | Characterization method                                     | 56  |

|              | 3.6 | Process variation of tunneling properties                   | 59  |

| IV           |     | ALOG COMPUTATION USING FLOATING-GATE ADAP-                  | 62  |

|              | 4.1 | The core device: floating-gate nFET                         | 63  |

|              | 4.2 | An FPAA with floating-gate adaptation                       | 66  |

|              | 4.3 | Software support- routing tool                              | 72  |

|              | 4.4 | Measured results- adaptive circuits                         | 73  |

| $\mathbf{V}$ | A L | EARNING-ENABLED NEURON ARRAY IC                             | 81  |

|              | 5.1 | Design paradigm and resulting architecture                  | 81  |

|              | 5.2 | Circuits for spiking network implementation                 | 85  |

|              | 5.3 | Characteristics of neuron behavior                          | 93  |

|              | 5.4 | Circuits for synaptic plasticity                            | 99  |

|              | 5.5 | System tools enabling network experiments                   | 106 |

|              | 5.6 | Power efficiency analysis                                   | 108 |

| VI           |     | MPUTING WITH SPIKING NETWORKS ON NEURON ARY IC              | 111 |

|              | 6.1 | Introduction                                                | 111 |

|              | 6.2 | Basic networks: "dot matrix" and synfire chain              | 112 |

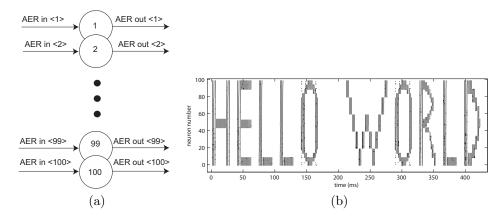

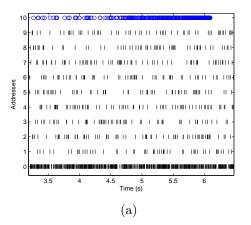

|              |     | 6.2.1 "Dot matrix" network                                  | 112 |

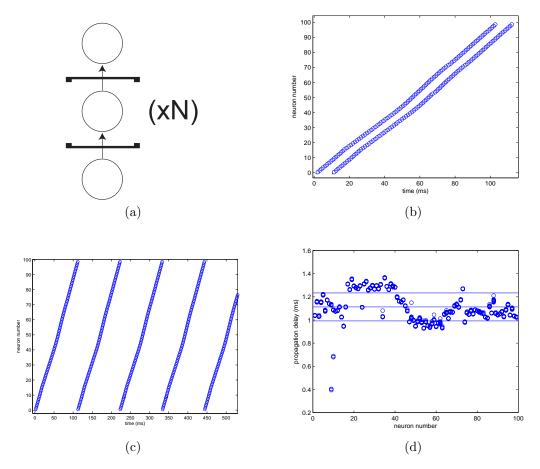

|              |     | 6.2.2 100-neuron synfire chain                              | 113 |

|              | 6.3 | Computational networks                                      | 115 |

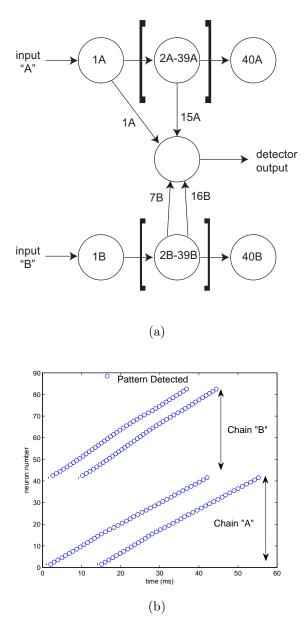

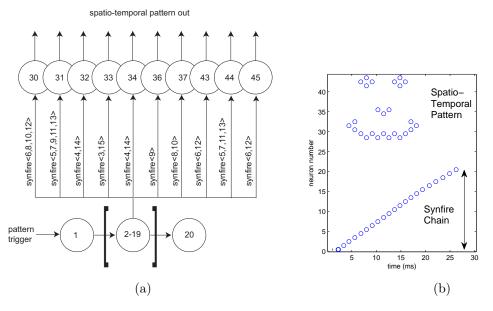

|              |     | 6.3.1 Spatiotemporal pattern generation and detection       | 115 |

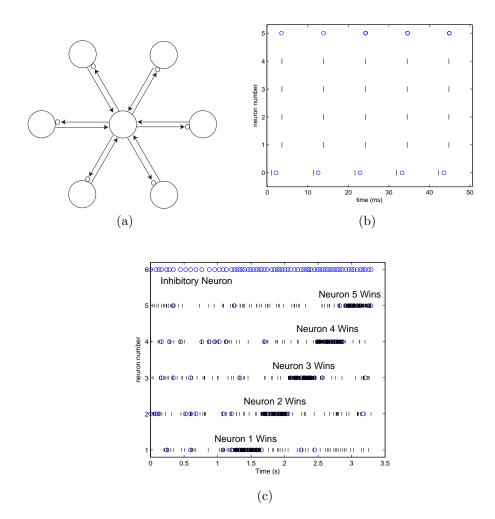

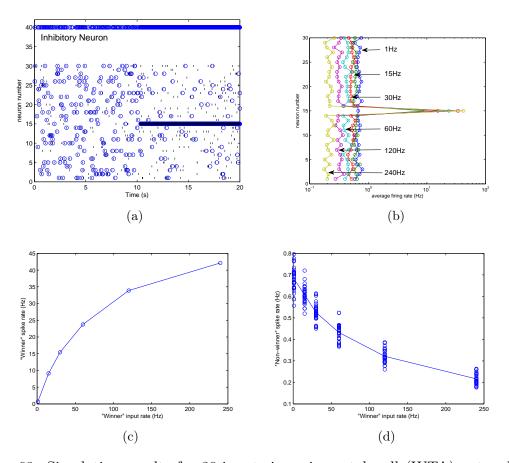

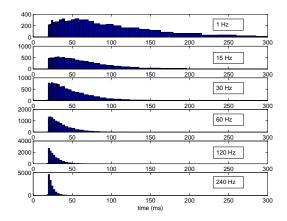

|         | 6.3.2    | Ring Winner-Take-All (WTA) network                                     | 117  |

|---------|----------|------------------------------------------------------------------------|------|

|         | 6.3.3    | Bistable oscillator                                                    | 122  |

| 6.4     | 4 Path 1 | planning                                                               | 124  |

| 6.5     | 5 Concl  | usion                                                                  | 131  |

| VII L   | EARNI    | NG IN SPIKING NETWORKS                                                 | 135  |

| 7.1     | l Two-s  | ynapse model                                                           | 135  |

| 7.2     | 2 Multi- | -synapse interactions                                                  | 136  |

|         | 7.2.1    | Methods: weight initialization and rate-coded input pattern generation | 137  |

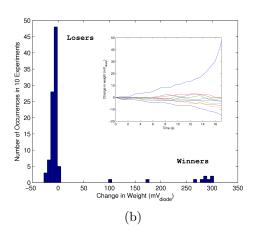

|         | 7.2.2    | Potentiation of synchronous inputs                                     | 138  |

|         | 7.2.3    | Competition among rate encoded inputs                                  | 139  |

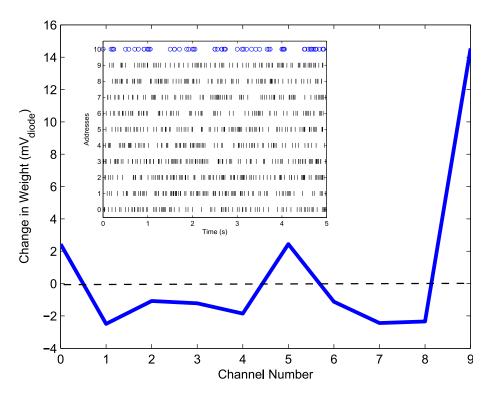

|         | 7.2.4    | Learning from correlations in the presence of noise                    | 142  |

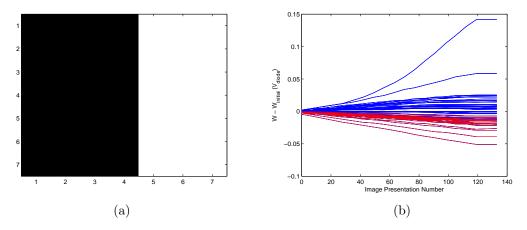

|         | 7.2.5    | Receptive field formation                                              | 142  |

| VIII (  | CONCL    | USIONS AND FUTURE DIRECTIONS                                           | 146  |

| REFE    | RENCE    | ES                                                                     | 151  |

| T/T/T/A |          |                                                                        | 1.01 |

# List of Tables

| 1 | Device parameters for two example devices characterized in this study. The capacitive coupling ratios for terminals of devices that share global terminal voltages for tunneling operations results in different floating gate voltages and therefore different tunneling rates for the different devices. Accounting for this effect is essential for achieving desired behavior from tunneling operations. The abbreviation "HC" (for high coupling) is used for the device whose gate capacitor is large, whereas "LC" is used for the other device | 41  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2 | Ranges of terminal voltages used for tunneling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43  |

| 3 | Optimal choice of tunneling parameters for 3 different realistic sets of constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 54  |

| 4 | Comparison of synapse density and function. The FACETS IC, Stanford STDP, INI IC 1, and INI IC 2 chips are described in detail in ([57, 56, 5, 38, 14]). The normalized synapse area is computed by dividing the synapse area by the square of the process feature size                                                                                                                                                                                                                                                                                | 91  |

| 5 | Estimated power consumption for a neuromorphic simulation of 100 neurons and 30,000 synapses, wherein each neuron spikes at an average rate of 10 Hz. The total power of 204 uW is about 6000 times smaller than the estimate of the power required for running the simulation using numerical integration                                                                                                                                                                                                                                             | 110 |

| 6 | Estimated energy to perform the network simulations presented in this work on this neuromorphic platform versus a numerical integration approach.                                                                                                                                                                                                                                                                                                                                                                                                      | 133 |

# List of Figures

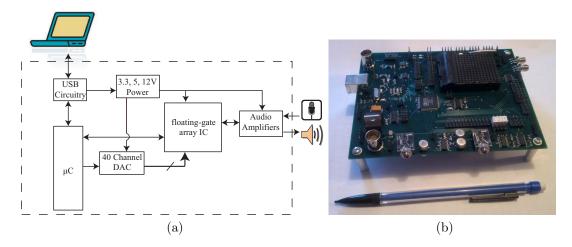

| 1 | Printed circuit board for programming and testing floating-gate array ICs. The block diagram is shown in a), and a photograph of the board is shown in b), with a pencil to show the scale                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15 |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

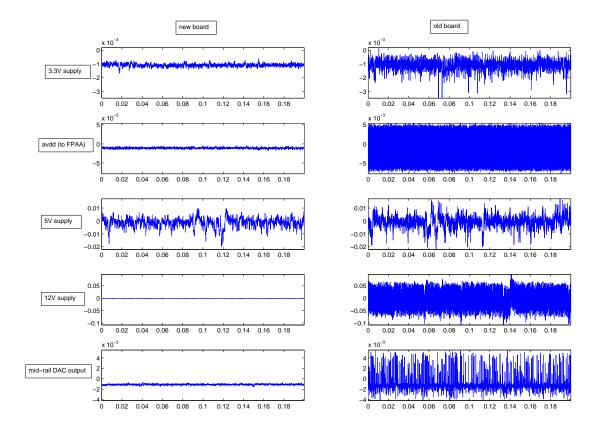

| 2 | Comparison of voltage supplies and DAC output on new PCB versus the previous version. All of the signals except for the 5V supply are dramatically improved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16 |

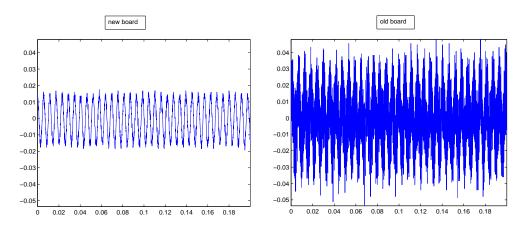

| 3 | Comparison of output of audio circuit on new PCB versus previous version. In both measurements, the input to the amplifier is a 30mV sine wave. The substantial improvement in the performance for the new board is due to the greatly reduced noise on the 12V supply, which powers the audio amplifiers                                                                                                                                                                                                                                                                                                                                      | 16 |

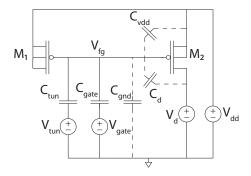

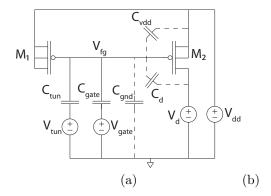

| 4 | Schematic of floating gate cell. Capacitors drawn with dashed lines represent parasitic capacitances.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20 |

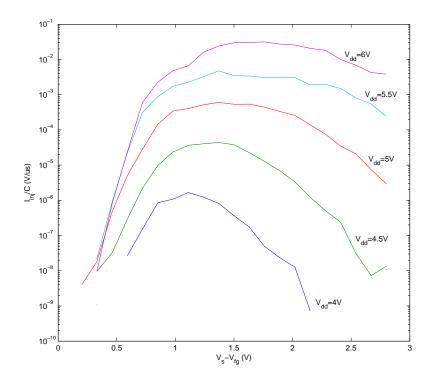

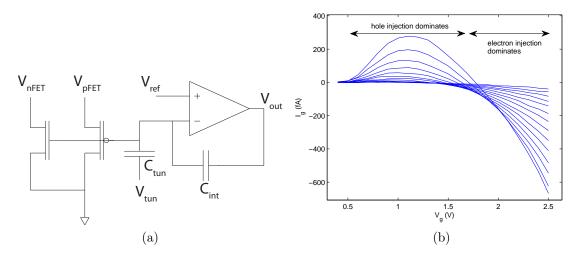

| 5 | Measured characteristics of hot electron injection for floating-gate pFET. In this measurement, the drain voltage is always 0 so $V_{dd} = V_{sd}$ . The current is normalized by the total capacitance at the floating gate, which was not known, and is generally a difficult parameter to measure experimentally                                                                                                                                                                                                                                                                                                                            | 21 |

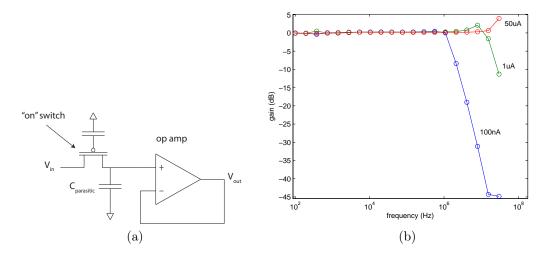

| 6 | Measurement of frequency response of on-chip op amp at various bias currents. The circuit diagram is shown in a) and the measured results are in b). As the bias current is increased, the amplifier's bandwidth increases while the phase margin decreases. The bias current that corresponds to critical damping (thus avoiding a resonant peak in the transfer function) is between 100nA and 1uA, and yields a corner frequency between 1 and 10MHz                                                                                                                                                                                        | 26 |

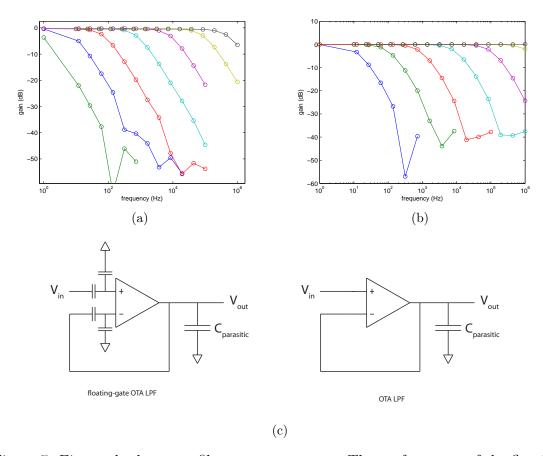

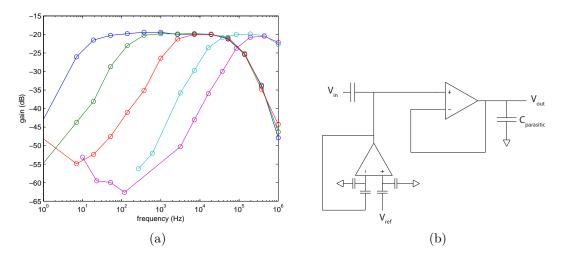

| 7 | First order low pass filters measurements. The performance of the floating-gate OTA based low pass filter is shown in a), while that of the conventional OTA based low pass filter is shown in b). Schematics of both circuits are shown in c). The capacitive attenuator in the floating-gate OTA yields an attenuation of about 10x, which reduces the transconductance, and therefore the low pass corner frequency. The fact that the corner frequency of a single circuit can be programmed over a range of 6 orders of magnitude illustrates the flexibility derived from using subthreshold circuit design techniques and floating gate |    |

|   | transistor technology.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29 |

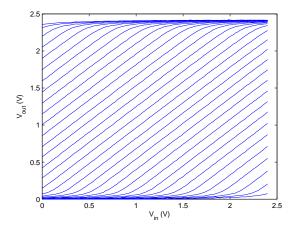

| 8  | Family of curves resulting from DC sweeps of the floating gate OTA depicted in Figure 7 with a range of differential offset voltages programmed on the inputs. With a signal on the input, this circuit functions as a programmable level shifter, and its range of programmability is such that with the input grounded it functions as a rail-to-rail programmable supply-independent bias voltage generator                                                                                                                                                                                                           | 30 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

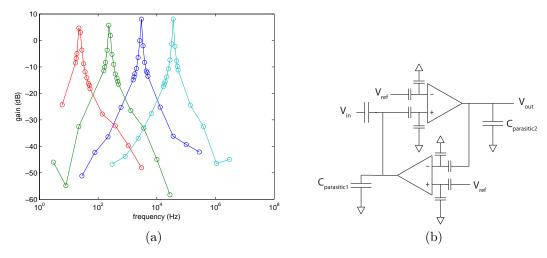

| 9  | High pass filter circuit and measurement results. Programming the floating gate biases for the OTAs over many decades of current yields a large range of tunability for the filter characteristics. Measured performance is shown in a) and the circuit topology is shown in b). The capacitive divider provides an attenuation factor of approximately 10x.                                                                                                                                                                                                                                                             | 30 |

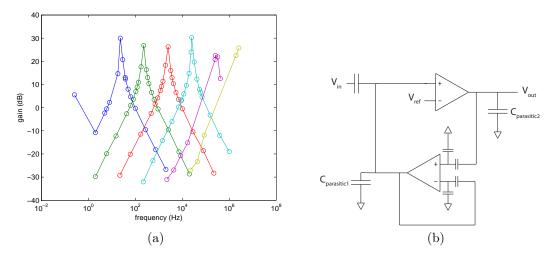

| 10 | Resonator topology for high-Q bandpass filter that can be used for spectral decomposition. Measured performance is shown in a) and circuit topology is shown in b). The capacitive dividers provide an attenuation factor of approximately 10x to each OTA                                                                                                                                                                                                                                                                                                                                                               | 31 |

| 11 | Capacitively coupled current conveyor (C4) topology for high-Q bandpass filter that can be used for spectral decomposition. Measured performance is shown in a) and circuit topology is shown in b). The capacitive dividers provide an attenuation factor of approximately 10x to each OTA                                                                                                                                                                                                                                                                                                                              | 32 |

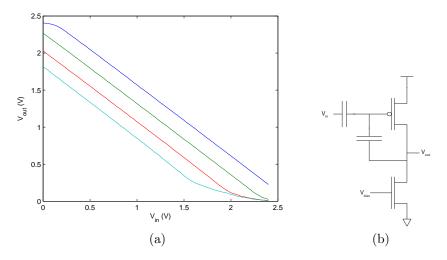

| 12 | Unity-gain inverting amplifier implemented with a floating gate and capacitive feedback. Measured performance for several bias voltages is shown in a), and the circuit topology is shown in b)                                                                                                                                                                                                                                                                                                                                                                                                                          | 33 |

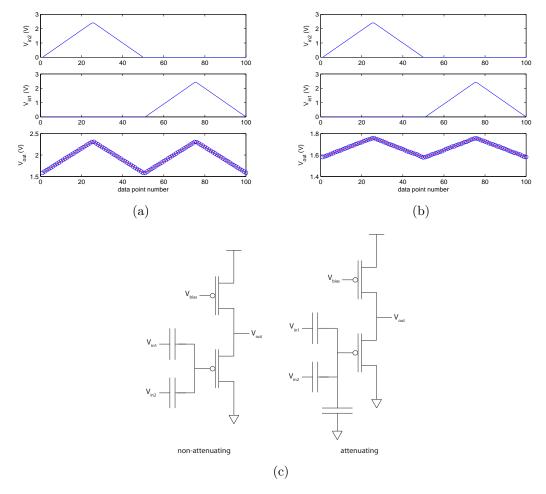

| 13 | Voltage-mode summing circuits that take advantage of capacitive summation at a floating node. In a) and b), the response of the circuit to consecutive triangle waves on the two inputs is shown. The measured output is plotted with open circles and a linear combination of the two inputs is plotted as a solid line. The coefficients in the linear combination are nearly equal, but not exactly (due to mismatch between the two input capacitors). In c), the circuit diagrams are shown for two different version of the summing circuit (one with a 6x capacitive attenuation and one without any attenuation) | 34 |

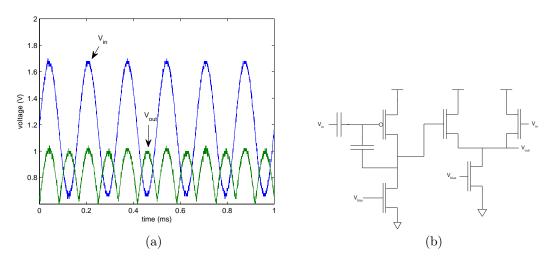

| 14 | Full-wave rectifier circuit. The response of the circuit to a sinusoidal input is shown in a), and the circuit topology is shown in b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35 |

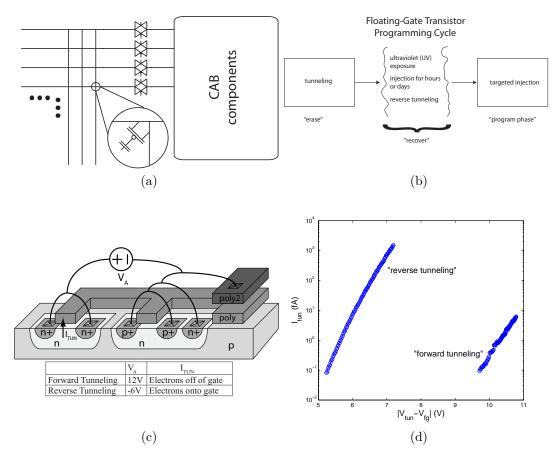

| 15 | Context and motivation for the study of tunneling with floating-gate transistor arrays. a) Structure of field-programmable analog arrays (FPAAs) wherein this work is applied. Such chips contain hundreds of thousands of floating-gate transistors, the charge of which is manipulated by global tunneling operations. b) Description of a single cycle of programming for the floating gates in such arrays. c) Cross-section view of floating-gate transistor with tunneling junction and gate coupling capacitor. Some example terminal conditions for forward and reverse tunneling are shown. d) Measured I-V relationship of the tunneling junction for both directions of tunneling. Reverse tunneling clearly requires much lower applied voltages to obtain similar currents. | 38 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

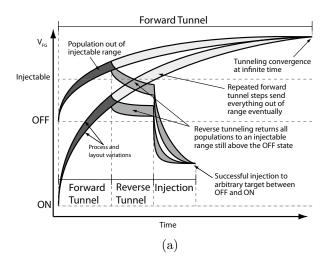

| 16 | Depiction of floating-gate voltages throughout the various phases of a programming cycle. The forward tunnel operation turns off all devices, but raises the voltage on some devices too far, making them impossible to inject reliably. The reverse tunnel operation then lowers the voltages back into the range wherein targeted injection can be done successfully. The trajectories of tunneling for infinite time illustrate what happens to un-injected devices in a floating-gate array that does not use bidirectional tunneling                                                                                                                                                                                                                                                | 39 |

| 17 | Details of the core floating-gate element. a) Schematic of floating-gate element. Parasitic capacitances are denoted with dashed lines. b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 40 |

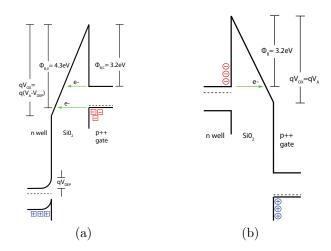

| 18 | Band diagrams depicting the tunneling processes. a) Reverse and b) forward Fowler-Nordheim tunneling band diagrams for a an n-well varactor with a degenerately p-doped gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43 |

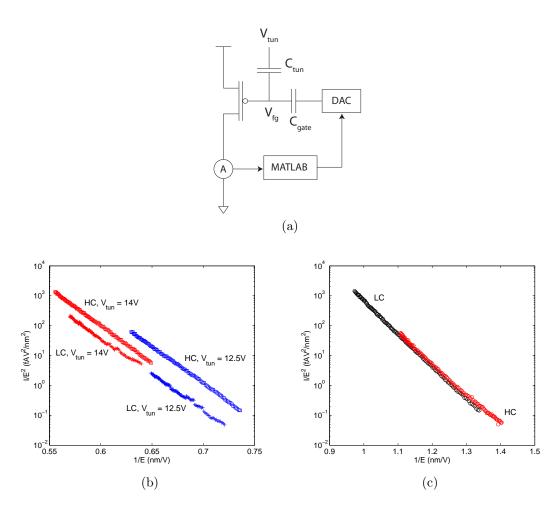

| 19 | Measured Fowler-Nordheim plots of forward and reverse tunneling characteristics. a) Setup for characterizing tunneling. Iteration with the control loop allows the tunneled charge to be calculated as $C_{gate}\Delta V_{DAC}$ . b) Forward tunneling characteristics for high coupling (HC) and low coupling (LC) devices, characterized with two different fixed tunneling voltages $V_{tun}$ . b)Reverse tunneling characteristics high coupling (HC) and low coupling (LC) devices                                                                                                                                                                                                                                                                                                  | 46 |

| 20 | Tunneling characterization with direct control of $V_{fg}$ . a) Test circuit used for measurements. b) Measured Fowler-Nordheim plots of the characteristic for 3 different voltages $V_{tun}$ . c) Example waveform measured at $V_{out}$ in the circuit shown in (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47 |

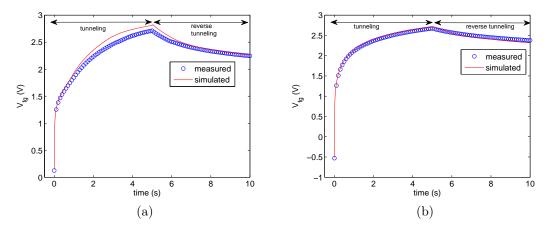

| 21 | Measured and simulated trajectories of floating-gate voltages during a 5-second tunneling pulse followed by a 5-second reverse tunneling pulse. a) Floating-gate voltage trajectory a) for low coupling (LC) device and b) for high coupling (HC) device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49 |

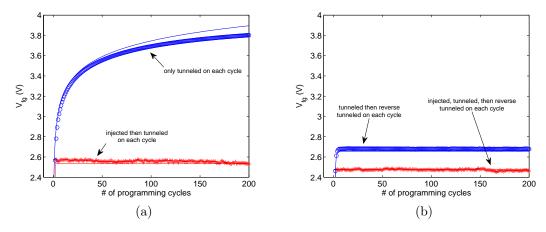

| Analysis of the distribution of the final floating gate voltages depicted in Figure 23, according to physical location on the array. In a), the values are plotted versus the column coordinate of the device. Because of the chip architecture, the switch devices are found at most column addresses, while the devices in the CABs (the OTA bias and differential pair devices) only exist on two column addresses in each of the 4 columns of CABs on the IC. The the OTA bias and differential pair devices found in the rightmost column of CABs tunneled significantly faster than the same types of devices in the rest of the array. In b), the OTA bias devices alone are plotted versus their location within a CAB (the local row address). Two of the locations in the cab (rows 38) | 22 | Measured and simulated $V_{fg}$ over many programming cycles comparing bidirectional tunneling to forward tunneling only. The floating gate voltage just prior to the targeted injection phase of programming is measured in each cycle. Modeled trajectories are shown as solid lines and measured trajectories are shown as crosses and open circles. a) Multi-programming cycle behavior when only forward tunneling is used in the programming cycle. b) Multi-programming cycle behavior when bidirectional tunneling is used                                                                                                                                                                                                                                                            | 51 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

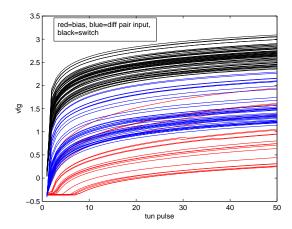

| in Figure 23, according to physical location on the array. In a), the values are plotted versus the column coordinate of the device. Because of the chip architecture, the switch devices are found at most column addresses, while the devices in the CABs (the OTA bias and differential pair devices) only exist on two column addresses in each of the 4 columns of CABs on the IC. The the OTA bias and differential pair devices found in the rightmost column of CABs tunneled significantly faster than the same types of devices in the rest of the array. In b), the OTA bias devices alone are plotted versus their location within a CAB (the local row address). Two of the locations in the cab (rows 38)                                                                           | 23 | device types during tunneling. The "switch" devices, shown in black, are the transistors that make up the switch matrix for routing in the FPAA. The "diff pair input" devices, shown in blue, are the input floating gates for the floating-gate based OTAs described in Chapter 2 (they are the same as the "HC" devices in this chapter). The "bias" devices, shown in red, are the programmable bias transistors for OTAs (they are the same as the "LC" devices in this chapter). The floating gate voltages spread significantly, and they also are seen to cluster by                                                                                                                                                                                                                  | 60 |

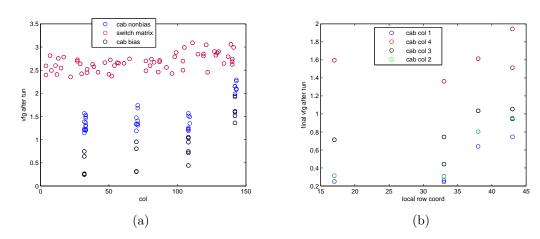

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 24 | in Figure 23, according to physical location on the array. In a), the values are plotted versus the column coordinate of the device. Because of the chip architecture, the switch devices are found at most column addresses, while the devices in the CABs (the OTA bias and differential pair devices) only exist on two column addresses in each of the 4 columns of CABs on the IC. The the OTA bias and differential pair devices found in the rightmost column of CABs tunneled significantly faster than the same types of devices in the rest of the array. In b), the OTA bias devices alone are plotted versus their location within a CAB (the local row address). Two of the locations in the cab (rows 38 and 43) are observed to tunnel faster than the other two locations (at | 61 |

- Characterization of hot carrier injection for the floating gate nFET. a) Circuit used for characterization. The amplifier is used to fix the floating gate voltage at  $V_{ref}$ , and the slew rate of  $V_{out}$  provides a measure of the current being injected to the floating gate. An nFET and pFET share the same floating gate so that the charge may be easily manipulated by tunneling or hot electron injection in the pFET. b) Measured injection currents in the nFET for a range of gate voltages from 0.3 to 2.5V, and drain voltages from 4.4 to 6V. As expected from the theory, hot hole injection is the dominant source of gate current when the channel current is low, and hot electron injection dominates when the channel current is sufficiently high. The maximum current over this range of terminal conditions is approximately 1000x smaller than the corresponding maximum for a floating gate pFET. . . . . . .

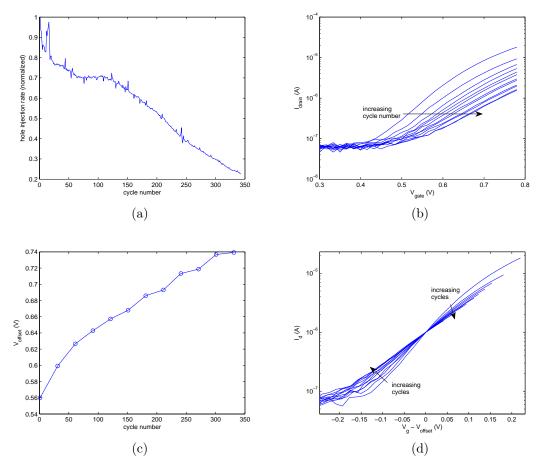

- Results from stress testing of floating gate nFET by 350 cycles of 7.5 pC hot hole injection. a) The rate of hole injection declines significantly with the amount of charge injected. Similar sweeps to those shown in Figure 25 were taken after the test in order to verify that the peak of injection had reduced in amplitude, not simply shifted. b) Gate sweeps taken every 30 cycles show a significant change in the I-V characteristic of the device. c,d) The curves in b) were shifted horizontally so as to coincide at a drain current of 1 uA. The required shifts are plotted versus cycle number in c) (This roughly corresponds to threshold voltage shift), and the shifted curves are plotted together in d), showing the reduction in the slope of the characteristic with increasing cycle number. 67

65

69

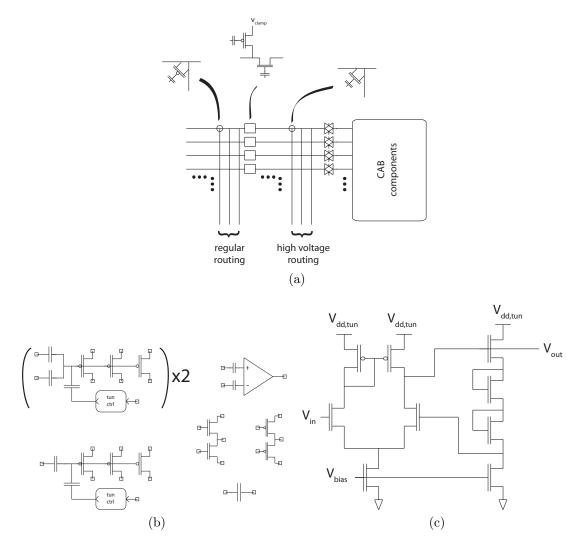

Overview of adaptive FPAA. a) Schematic of one tile (CAB and routing) of the array, highlighting the different floating gate FETs used for low voltage and high voltage routing, and for the disconnect switch between rows of high and low voltage routing. b) Schematic of all of the components found in a single CAB. The most important component in the CAB is the adaptive floating gate, which has a self-contained amplifier for tunneling, and multiple FETs that can be compiled into circuits through the routing. The tunneling amplifier allows a voltage in the routable range  $(0\text{-}V_{dd,inject})$  to control a higher tunneling voltage that is applied to the floating gate. c) Schematic of the tunneling amplifier. All of the transistors in the amplifier are 13.5V devices. . .

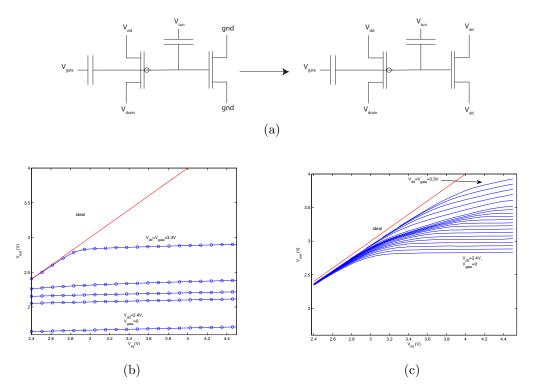

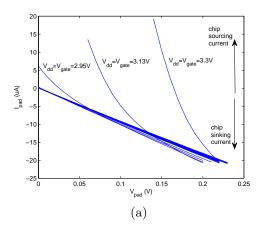

| 28 | Maximizing dynamic range of nFET switches by preventing unwanted reverse tunneling during array programming. a) The schematic of the nFET switch cell is shown before (left) and after (right) the metal mask change to the design. Keeping the terminals of the nFET switches at $V_{dd}$ during programming minimizes the unwanted reverse tunneling that takes place. The result of a voltage sweep of a single switch is shown b) before the change and c) after the change. The operating range of the high voltage nFETs is seen to be extended by about 1V, a substantial improvement that allows orders of magnitude higher hot electron injection currents in the adaptive pFET CAB element. In both b) and c), the sweeps are shown for a range of gate coupling voltages and supply voltages ( $V_{gate}$ 's and $V_{dd}$ 's), both of which can be used to globally increase the floating gate voltages, and thereby increase the maximum range of the floating gate nFETs | 71 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

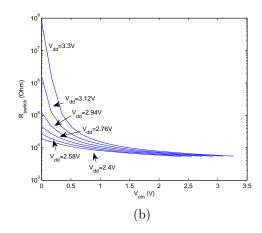

| 29 | Low voltage performance of a) nFET and b) pFET switches. The currents in the nFET switch sweeps at high floating gate voltages are indicative of parasitic currents coming from "off" nFET devices in the array, and the result in b) illustrates the degradation of the pFET switch conductance at low voltage as the floating gate voltage is raised. Both of these effects can be mitigated by choosing $V_{gate} = V_{dd} = 2.7V$ , which still results in acceptable high voltage nFET switch performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 72 |

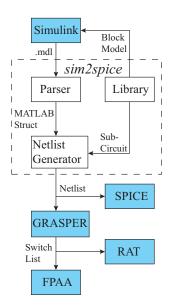

| 30 | System of software tools that constitute the design environment for typical FPAAs. For the adaptive FPAA, this framework was replaced with a more low level MATLAB tool that provides a compromise between software development time and ease of use for the system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 73 |

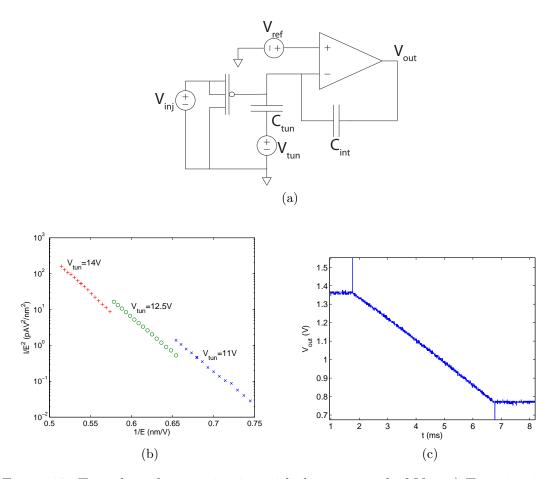

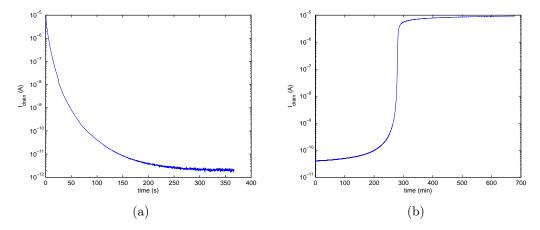

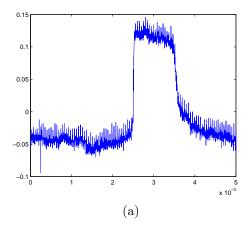

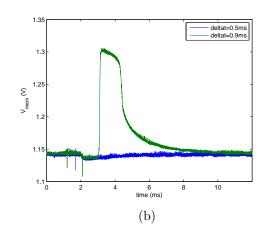

| 31 | Measured results from continuous-time a) tunneling and b) injection using the adaptive pFET element in the CAB of the adaptive FPAA. The qualitatively different dynamics of injection and tunneling are apparent. The rate of tunneling monotonically decreases over the course of the tunneling exposure, while the injection process is characterized by a positive feedback process that saturates at a large current level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 74 |

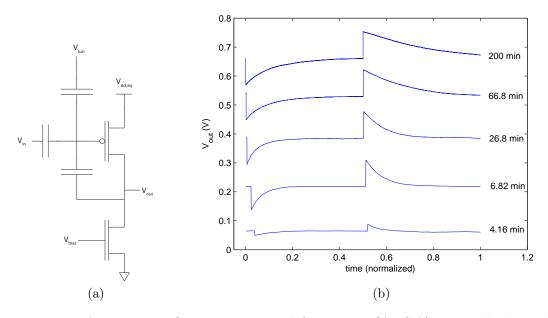

| 32 | Autozeroing floating gate amplifier circuit (AFGA) originally described in [33]. The circuit diagram is shown in a) and the measured step responses, demonstrating time constants from under a minute to about an hour, are shown in b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75 |

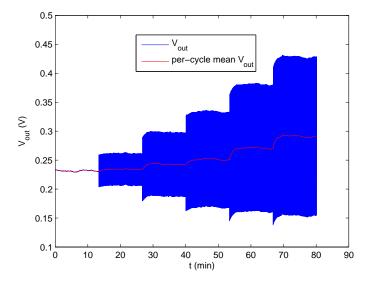

| 33 | Measured output of AFGA circuit when the input is a square wave with successively increasing amplitude. The nonlinearity of the amplifier is clearly seen to result in an encoding of the signal amplitude in the output DC level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75 |

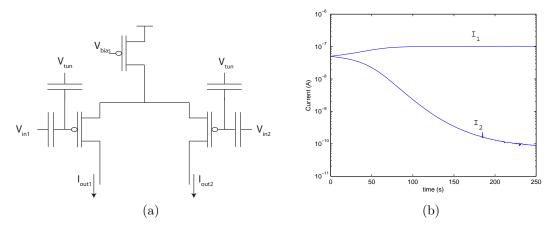

| 34 | Floating gate differential pair circuit. The circuit diagram is shown in a), and the continuous-time injection curve is shown in b). The unstable dynamics eventually results in a condition in which all of the current is being conducted through branch 1, and essentially no current is flowing through branch 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 76 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

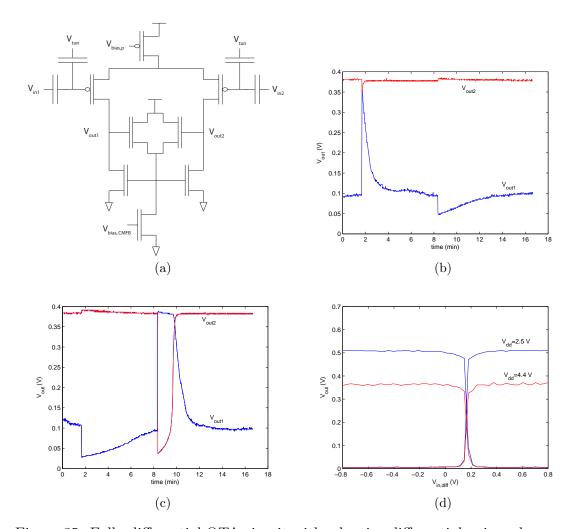

| 35 | Fully differential OTA circuit with adaptive differential pair and common-mode feedback. The circuit, shown in a), exhibits floating gate adaptation that is characterized by a stable equilibrium, which is independent of the differential mode of the input voltages. The settling back to this equilibrium after perturbations is illustrated by the step responses on b) $V_{in1}$ and c) $V_{in2}$ . The asymmetry of the step responses is due to mismatch between the injection, tunneling, and I-V characteristics of the two branches of the amplifier. The adaptation could be enabled to allow the circuit to compensate an input offset, then disabled to allow the differential amplifier to operate around that differential offset. This capability is verified by differential sweeps of the amplifier before and after the supply voltage is ramped down to a level that prevents adaptation. The result of these sweeps, shown in d), shows that the offset that results from the adaptation is preserved when the supply voltage is reduced | 78 |

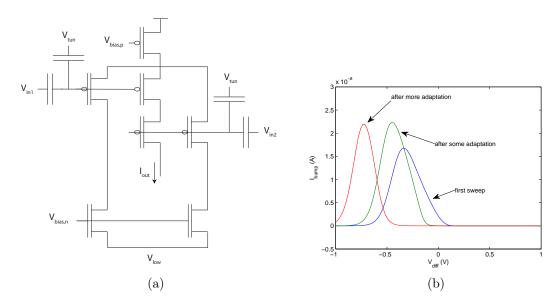

| 36 | Adaptive "bump" circuit. The schematic is shown in a) and differential sweeps are shown before and after two stages of adaptation in b). This circuit, under this bias condition, is another example of an unstable, diverging form of adaptation, much like the adaptive differential pair.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 79 |

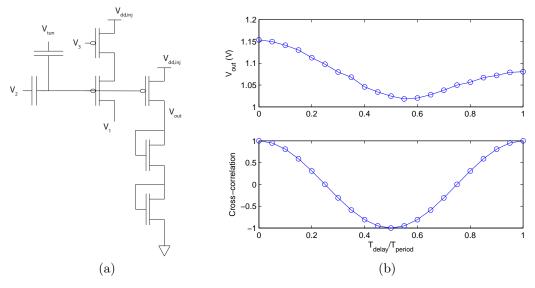

| 37 | Adaptive floating gate correlation detector. The circuit, shown in a), is based upon a pFET source follower, and a second pFET on the floating gate drives a current into two series diode-connected nFETs. The voltage across the nFETs provides a measure of the floating gate voltage, which is determined by a balance of injection and tunneling processes. If the input signals $V_1, V_2$ , and $V_3$ are highly correlated, the rate of injection increases, lowering the floating gate voltage. In b), the equilibrium output voltage is plotted versus the phase shift from $V_1$ to $V_2$ and $V_3$ . The output voltage is seen to track the cross-correlation of the inputs                                                                                                                                                                                                                                                                                                                                                                        | 80 |

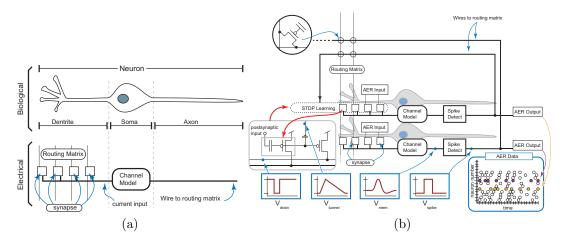

| 38 | Illustrations of the design paradigm and its parallels to biology. In a), the model for a single neuron is depicted. In b), the model for two neurons is shown, and cartoons of some of the signal waveforms give a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|    | qualitative appreciation for the signal flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 82 |

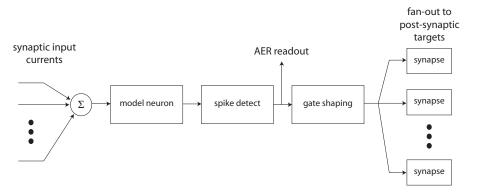

| 39 | Signal flow for a single neuron in the neuron array IC. The synaptic input currents are summed on a wire. When the synaptic input currents are sufficiently strong, the model neuron emits a spike, which is picked up by the spike detector block and transmitted to the AER system and a gate waveform shaping circuit. The gate waveform shaping circuit conditions the pulse from the spike detector to create the desired time course for the post-synaptic currents on all of the neuron's output synapses                                                                                                                                                                                             | 83 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 40 | Top level architecture of the IC. In a) the connectivity of the synapse array is shown, including the partition of synapses into recurrent connections, AER inputs, learning-enabled, fixed weight, and configurable excitatory/inhibitory synapses. All of the STDP synapses are excitatory. In b) a die micrograph shows the amount of die area dedicated to the neuron models (Soma Array), the synapse array, and the gate waveform shaping circuits (Triangle Circuits)                                                                                                                                                                                                                                 | 84 |

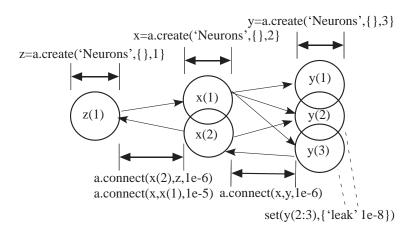

| 41 | PyNN-based Matlab code for setting up a network simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 85 |

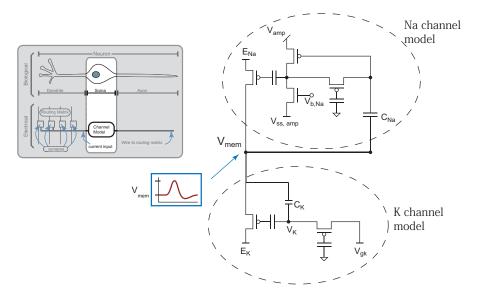

| 42 | Models for voltage gated channels that constitute a model neuron. The voltage supplies and biases $V_{amp}$ , $V_{ss,amp}$ , $E_{Na}$ , $E_K$ , $V_{gK}$ are shared by all neuron models in the array. The use of floating gate transistors in the models allow for their conductances and frequency responses to be programmed individually. This allows for networks of neurons with heterogeneous properties to be modeled                                                                                                                                                                                                                                                                                | 86 |

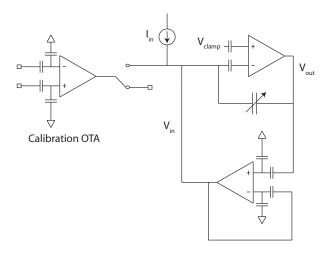

| 43 | Schematic of transimpedance amplifier for making voltage clamp measurements. The voltage $V_{clamp}$ is used to control the membrane voltage, and the channel model is represented by the current source $I_{in}$ . The voltage $V_{out}-V_{in}$ is proportional to the input current, so $V_{out}$ and $V_{in}$ are buffered out to pads (buffers not shown in this figure). There is a 5-bit programmable variable compensation capacitor and an OTA that can provide a range of known currents in order to calibrate the amplifier's characteristic precisely. Small squares are used to denote connections to pads, and the capacitive attenuators shown on two OTAs have about a 10x attenuation factor | 87 |

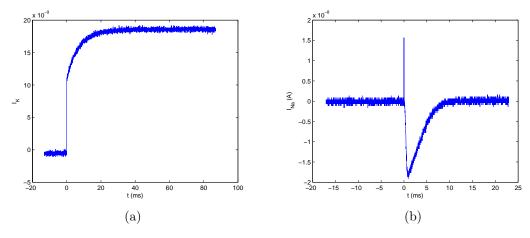

| 44 | Step responses in a voltage clamp experiment of a) the potassium channel model and b) the sodium channel model. Note the instantaneous step in the potassium channel's response. This is a result of the fact that the n-well of the potassium conductance is not connected to its source, as well as the fact that the capacitor $C_K$ does not dominate the total capacitance at the net labeled $V_K$ in Figure 42. The response in the sodium amplifier has a very short transient that is an artifact of the voltage clamp circuit.                                                                                                                                                                     | 88 |

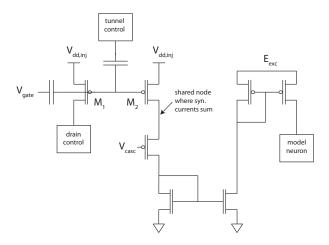

| 45 | Schematic for STDP-enabled synapses. The synapse consists only of the two transistors $M_1$ and $M_2$ and the capacitors connected to its gate. The gate voltage $V_{gate}$ is provided by the circuit shown in Figure 47. The current mirrors that level shift the synaptic current, the cascode pFET, and the tunnel and drain control blocks are all shared by all of the synapses that connect to a particular neuron. The cascode device prevents hot electron injection in $M_2$ , while the current mirrors allow the current to come from the voltage supply $E_{exc}$ . The tunnel control and drain control blocks, described later in this chapter in detail, mediate the hot electron injection and tunneling processes that implement the STDP learning rule.          | 89 |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

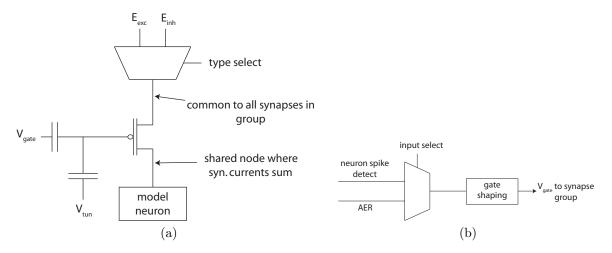

| 46 | Circuits for the fixed weight synapses. a) Diagram of the synapse and multiplexer for selecting the polarity of the synapse group (excitatory versus inhibitory). Changing the logic controlling this multiplexer changes the reversal potential of the synapse ( $E_{exc}$ for excitatory and $E_{inh}$ for inhibitory). The fact that this choice affects all of the synapses in a particular group was an architectural necessity, but it is exactly analogous to the fact that biological neurons produce only a single type of neurotransmitter at all of their synapses. b) Diagram of the circuit that selects the input for a group of fixed weight synapses. The polarity and input type are independently selectable for each of the 100 groups of fixed weight synapses. | 90 |

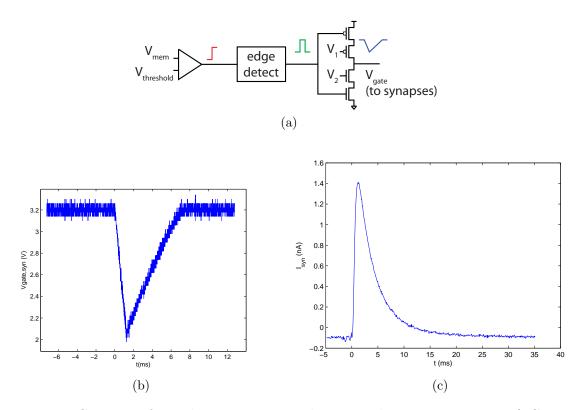

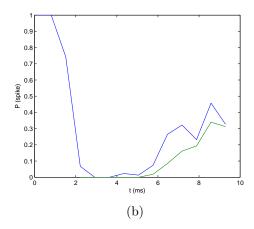

| 47 | Gate waveform shaping circuit and measured synaptic current. a) Circuit diagram for spike detector and gate waveform shaping circuit. The fall time of the gate waveform is set by the width of the pulse output from the edge detector (which is programmable by a floating gate voltage), and the rising and falling slopes are set by the voltages $V_1$ and $V_2$ , which are also set by floating-gate based bias voltage generators. b) Measured output from the gate waveform shaping circuit. c) Measured excitatory post synaptic current. The waveforms in b) and c) were not taken in the same experiment, so the time courses of the two waveforms are not the same.                                                                                                    | 91 |

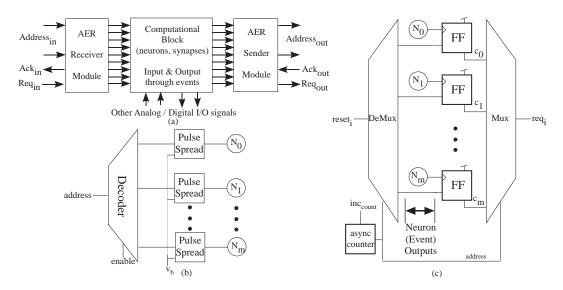

| 48 | Functional block diagram of the AER module on the IC. a) Top-level signal flow depicting the various channels of communication with the microcontroller. b) AER receiver diagram. c) AER transmitter diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 92 |

|    | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

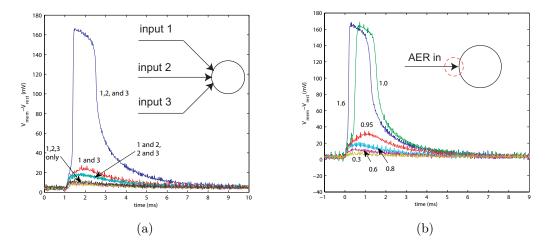

| 49 | Measurements of membrane voltage response to synaptic inputs, illustrating the excitatory threshold for spiking in the neuron model. All waveforms in this figure are averaged over about 20 captures in order to reduce the effect of power supply noise that is present in the measurement system. a) Three input synapses with approximately equal conductance are connected, and the response to various subsets of them are shown. b) The response to synaptic inputs of varying amplitudes is shown (the synaptic weight, normalized to the minimum weight that produced a spike, is shown)                                                               | 94 |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

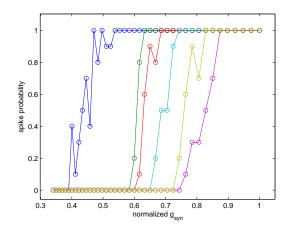

| 50 | Measured relationship between synaptic input amplitude and likelihood of the synaptic input stimulating an action potential in the neuron. If the input is sufficiently weak, there is no chance that it can cause an action potential. If it is sufficiently strong, it is certain to cause an action potential. There is a relatively narrow region of input amplitudes where the probability is seen to vary continuously between these two extremes. The family of curves shown here is this "p-I" characteristic that was measured for 6 different neurons                                                                                                 | 95 |

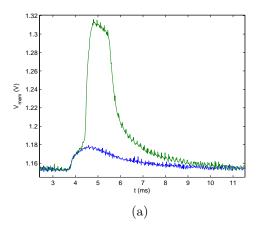

| 51 | Illustration of the paired pulse facilitation phenomenon that is observed in this system. The second pulse arrives before the gate waveform has recovered to its steady-state value, which results in a greater amplitude gate waveform. This makes the second input stronger than the first, and thus it is consistently able to produce a spike. While the second gate waveform pulse appears to clip at about 300mV, this is actually due to the nFET input buffer amplifier that drives this signal off chip. The signal that goes to the synapses can slew clear to ground. These data were averaged for 10 trials to reduce high frequency noise          | 96 |

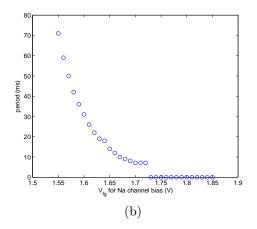

| 52 | Data illustrating the effects of temporal summation of inputs. In a), the membrane voltage is compared for a single synaptic input (shown in blue) and two successive inputs (shown in green). In b), the probability of eliciting a spike by providing a pair of sequential excitatory inputs is plotted as a function of the timing difference between the two inputs. The two curves shown are from two different trials of the experiment. There is a clear effect of enhanced spike probability for inputs that arrive within about 2 ms, and a suppression of spikes if the inputs arrive between 2 and 6 ms apart. This suppression is the result of the |    |

|    | underdamped characteristic of the sodium amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 97 |

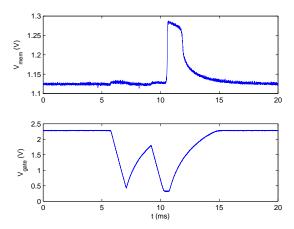

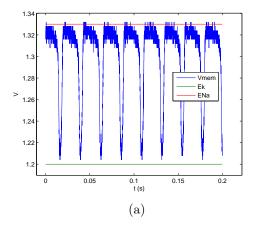

| 53 | Properties of the stable oscillations of the membrane voltage. a) Typical waveform for the stable oscillations. b) Variation of oscillation period with the pFET bias voltage that sets the bias current in the sodium bandpass amplifier. As the bias voltage goes up, the current goes down, which raises the DC operating point of the amplifier. This, in turn raises the high pass corner frequency, which shortens the period of oscillations. At some point, the high pass corner frequency becomes sufficiently high that the rebound from the falling edge of the spike is not sufficient to trigger another spike. At this point, the stable oscillations cease                                                                                                                                                               | 98  |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 54 | Responses of neuron model to inhibitory input. a) A very small amplitude inhibitory synaptic current can result in a spike if the inhibitory reversal potential is too low. This unwanted behavior can be eliminated by setting the inhibitory reversal potential sufficiently high (to a value of 30-50mV below $E_K$ ). b) With $E_{inh}$ set to an appropriate level, the effect of inhibition to prevent a spike can be observed. In this experiment, an excitatory input was delivered a short time after an inhibitory one. If the excitatory input arrives too soon after the inhibitory input (in this case, 0.5 ms), it fails to elicit a spike. If it arrives a little later, after the inhibitory conductance has begun to fall, then it causes a spike (both traces averaged over 10 trials to reduce high frequency noise) | 100 |

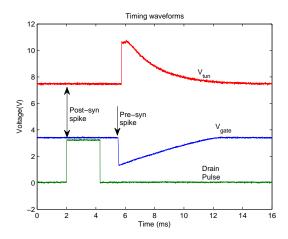

| 55 | Waveforms that orchestrate the STDP learning rule. Arrows indicate the timing of the pre and post-synaptic spikes, as well as the fact that the drain pulse and $V_{tun}$ are time-locked to the post-synaptic spike while $V_{gate}$ is time-locked to the pre-synaptic spike                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 101 |

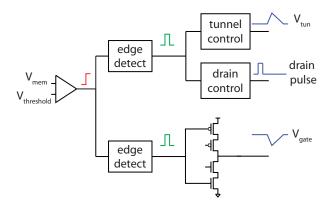

| 56 | Signal flow for pulse timing circuits, including the gate waveform circuits and the circuits that generate the signals for STDP. Note that the voltage $V_{gate}$ is driving the output synapses of the neuron that has just spiked, while the STDP signals ( $V_{tun}$ and the drain pulse) are connected to the input synapses of this neuron. The gate waveforms that influence the STDP rule on the input synapses of this neuron are the ones driving those synapses                                                                                                                                                                                                                                                                                                                                                               | 102 |

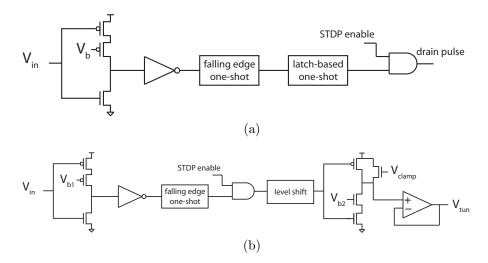

| 57 | Circuits for timing and shaping a) the drain pulse and b) the tunneling voltage $V_{tun}$ . The voltages $V_b$ and $V_{b1}$ are set by floating-gate transistors, and are used to set the delay between pre-synaptic spike and drain pulse or $V_{tun}$ waveform, respectively. The voltage $V_{b2}$ is also set by a floating-gate transistor, and it sets the fall time of the $V_{tun}$ waveform. The global bias voltage $V_{clamp}$ is used to set the baseline value for $V_{tun}$ . The input $V_{in}$ to these circuits is shared, and is the output of the edge detect block shown in Figure 56                                                                                                                                                                                                                                | 103 |

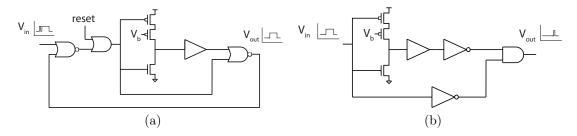

| 58 | Circuit diagrams of a) latch-based one-shot circuit and b) falling edge one-shot circuit. The latch-based one-shot produces a pulse with programmable width in response to a rising edge on its input. The latch-based circuit filters out glitches that accompany its input pulses. The falling edge one-shot produces a pulse with programmable width in response to a falling edge on its input, and it does not provide glitch filtering                                                                                                                                                                                                                                                                                | 104 |

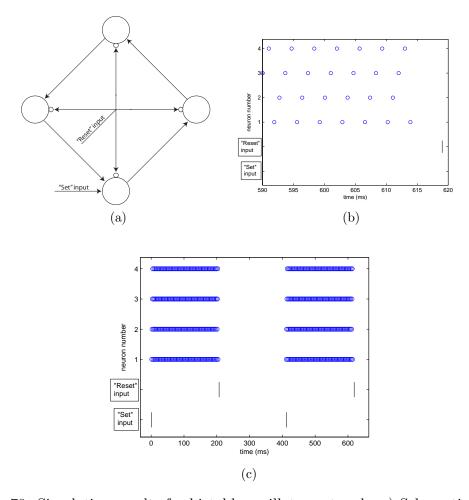

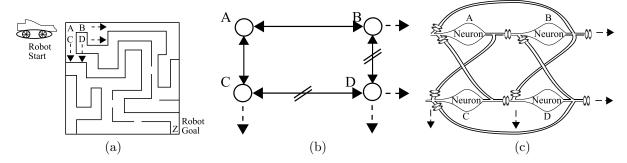

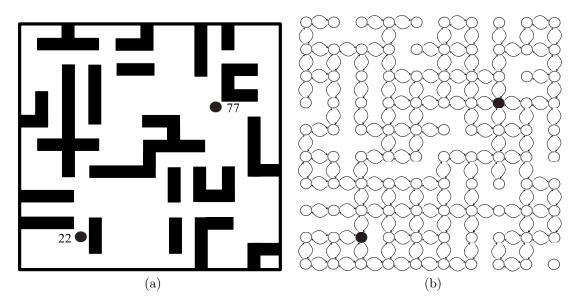

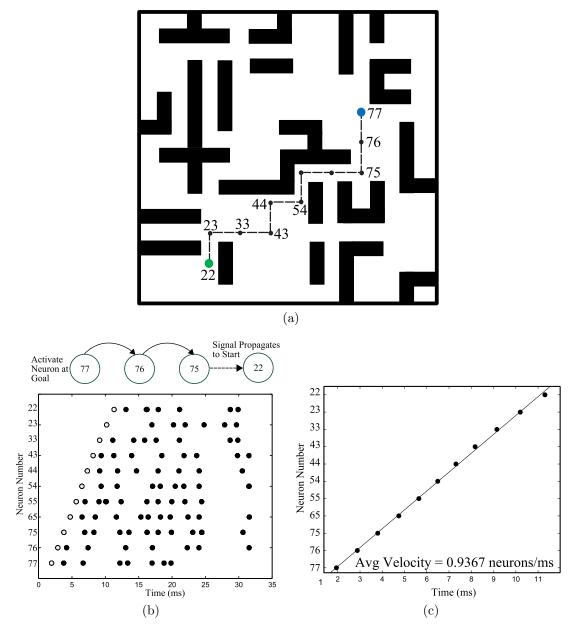

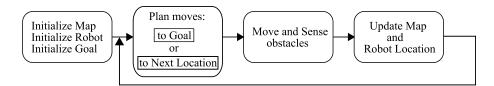

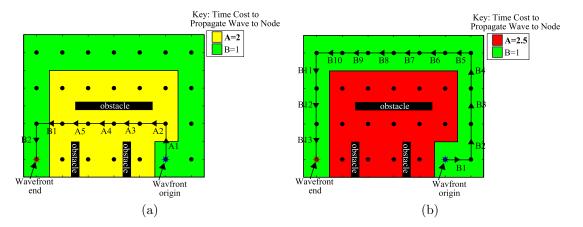

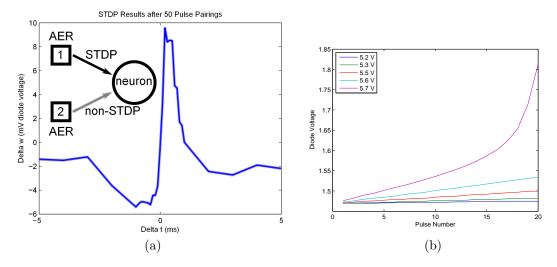

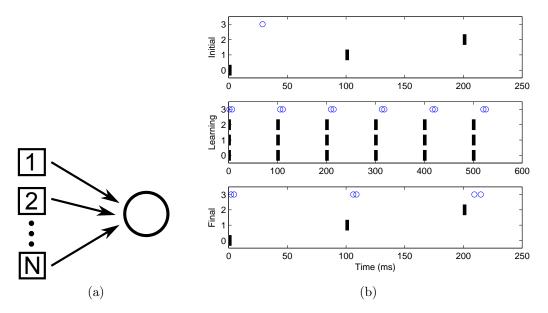

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|