Western SGraduate & Postdoctoral Studies

### Western University Scholarship@Western

Electronic Thesis and Dissertation Repository

December 2013

# Hardware Acceleration Technologies in Computer Algebra: Challenges and Impact

Sardar Anisul Haque The University of Western Ontario

Supervisor Dr. Marc Moreno Maza The University of Western Ontario

Graduate Program in Computer Science

A thesis submitted in partial fulfillment of the requirements for the degree in Doctor of Philosophy

© Sardar Anisul Haque 2013

Follow this and additional works at: https://ir.lib.uwo.ca/etd Part of the <u>Numerical Analysis and Scientific Computing Commons</u>, and the <u>Other Computer</u> <u>Sciences Commons</u>

#### **Recommended** Citation

Haque, Sardar Anisul, "Hardware Acceleration Technologies in Computer Algebra: Challenges and Impact" (2013). *Electronic Thesis and Dissertation Repository*. 1803. https://ir.lib.uwo.ca/etd/1803

This Dissertation/Thesis is brought to you for free and open access by Scholarship@Western. It has been accepted for inclusion in Electronic Thesis and Dissertation Repository by an authorized administrator of Scholarship@Western. For more information, please contact tadam@uwo.ca.

### Hardware Acceleration Technologies in Computer Algebra: Challenges and Impact

(Thesis format: Monograph)

by

Sardar Anisul Haque

Graduate Program in Computer Science

A thesis submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

The School of Graduate and Postdoctoral Studies The University of Western Ontario London, Ontario, Canada

© S. A. Haque 2013

# Abstract

The objective of *high performance computing (HPC)* is to ensure that the computational power of hardware resources is well utilized to solve a problem. Various techniques are usually employed to achieve this goal. Improvement of algorithm to reduce the number of arithmetic operations, modifications in accessing data or rearrangement of data in order to reduce memory traffic, code optimization at all levels, designing parallel algorithms with smaller span or reduced overhead are some of the attractive areas that HPC researchers are working on.

In this thesis, we investigate HPC techniques for the implementation of basic routines in computer algebra targeting hardware acceleration technologies. We start with a sorting algorithm and its application to sparse matrix-vector multiplication for which we focus on work on cache complexity issues. Since basic routines in computer algebra often provide a lot of fine grain parallelism, we then turn our attention to many-core architectures on which we consider dense polynomial and matrix operations ranging from plain to fast arithmetic. Most of these operations are combined within a bivariate system solver running entirely on a graphics processing unit (GPU).

**Keywords.** High Performance Computing, Cache complexity, Parallel algorithms, Many core machines, multi-core machines, Computer algebra.

# Acknowledgments

I would like to thank my thesis supervisor Dr. Marc Moreno Maza in the department of Computer Science at the University of Western Ontario. His helping hands toward the completion of this research work were always extended for me. He consistently helped me on the way of this thesis and guided me in the right direction whenever he thought I needed it. I am grateful to him for his excellent support to me in all the steps of successful completion of this research.

I want to thank Dr. Wei Pan of Intel Corporation for discussions around our CUDA implementation for condensation method in the finite field case. Many thanks to Dr. Jürgen Gerhard of Maplesoft for his help during my internship. My sincere thanks to Dr. Shahadat Hossain in the Department of Computer Science at the University of Lethbridge for taking the time to share his thoughts on sparse matrices with me.

I want to thank Dr. Yuzhen Xie, Dr. Changbo Chen in the Department of Computer Science at the University of Western Ontario for providing me help and sharing their knowledge.

All my sincere thanks and appreciation go to all the members from our Ontario Research Center for Computer Algebra (ORCCA) lab, Computer Science Department for their invaluable teaching support as well as all kinds of other assistance.

Many thanks to the members of my committee Dr. Éric Schost, Dr. Michael Bauer, Dr. Kenneth A. McIsaac of the University of Western Ontario and Dr. Yuxiong He of Microsoft Research for their reading of this thesis and comments.

Finally, I would like to thank all of my friends and family members for their consistent encouragement and support.

To you, I dedicate this thesis, Tuie.

# Contents

| Α             | bstra               | t                                                                        | ii   |  |  |

|---------------|---------------------|--------------------------------------------------------------------------|------|--|--|

| $\mathbf{A}$  | Acknowledgments iii |                                                                          |      |  |  |

| Ta            | able (              | Contents                                                                 | iv   |  |  |

| $\mathbf{Li}$ | ist of              | Algorithms                                                               | viii |  |  |

| $\mathbf{Li}$ | ist of              | Figures                                                                  | x    |  |  |

| $\mathbf{Li}$ | ist of              | Tables                                                                   | xii  |  |  |

| 1             | Intr                | duction                                                                  | 1    |  |  |

| <b>2</b>      | Bac                 | ground                                                                   | 4    |  |  |

|               | 2.1                 | Random access machine (RAM) model                                        | 4    |  |  |

|               | 2.2                 | The PRAM model                                                           | 5    |  |  |

|               |                     | 2.2.1 Parallel time, efficiency and speedup factor                       | 7    |  |  |

|               |                     | 2.2.2 Different types of PRAM models                                     | 7    |  |  |

|               | 2.3                 | The ideal cache model                                                    | 8    |  |  |

|               | 2.4                 | The multi-core machine model                                             | 10   |  |  |

|               | 2.5                 | The fork-join parallelism model                                          | 12   |  |  |

|               |                     | 2.5.1 The work law $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 13   |  |  |

|               |                     | 2.5.2 The span law                                                       | 13   |  |  |

|               |                     | 2.5.3 Parallelism                                                        | 13   |  |  |

|               |                     | 2.5.4 Performance bounds                                                 | 14   |  |  |

|               |                     | 2.5.5 Work, span and parallelism of classical algorithms                 | 14   |  |  |

|               | 2.6                 | Systolic arrays                                                          | 14   |  |  |

| 3        | Many-core Machine Model 10 |                      |                                                     |        |

|----------|----------------------------|----------------------|-----------------------------------------------------|--------|

|          | 3.1                        | Introdu              | uction                                              | 1      |

|          | 3.2                        | A man                | y-core machine model                                | ]      |

|          |                            | 3.2.1                | Many-core machine characteristics                   | ]      |

|          |                            | 3.2.2                | Many-core machine programs                          | 2      |

|          |                            | 3.2.3                | Complexity measures for the many-core machine model | د<br>4 |

|          |                            | 3.2.4                | A Graham-Brent theorem with overhead                | د<br>4 |

|          |                            | 3.2.5                | Justification of the many-core machine model        | 4      |

| 4        | Cac                        | he-obli <sup>.</sup> | vious Counting Sort Algorithm                       | د<br>4 |

|          | 4.1                        | Introdu              | action                                              | 4      |

|          | 4.2                        | The cla              | assical counting sort algorithm                     | -      |

|          | 4.3                        | Cache-               | oblivious counting sort algorithm                   |        |

|          | 4.4                        | Experi               | ments                                               |        |

|          | 4.5                        | Conclu               | sion                                                |        |

| <b>5</b> | Αľ                         | New Int              | eger Sorting Algorithm                              |        |

|          | 5.1                        | Introdu              | uction                                              |        |

|          | 5.2                        | Notatio              | ons                                                 |        |

|          | 5.3                        | Cost of              | f the comparand function for large integers         |        |

|          | 5.4                        | A new                | sorting algorithm                                   |        |

|          |                            | 5.4.1                | Creating $A^{k+1}$ from $A^k$                       |        |

|          | 5.5                        |                      | exity                                               |        |

|          | 5.6                        |                      | sion                                                |        |

| 6        | Cac                        | he Frie              | andly Sparse Matrix-vector Multiplication           | 4      |

|          | 6.1                        | Introdu              | action                                              |        |

|          | 6.2                        | Backgr               | ound                                                |        |

|          |                            | 6.2.1                | Compressed row storage scheme (CRS)                 |        |

|          |                            | 6.2.2                | SpMxV with CRS scheme                               |        |

|          |                            | 6.2.3                | Compressed column storage scheme (CCS)              |        |

|          |                            | 6.2.4                | Notations                                           |        |

|          |                            | 6.2.5                | Binary reflected Gray code                          |        |

|          |                            | 6.2.6                | Sorting of binary reflected Gray codes              |        |

|          | 6.3                        |                      | ed reordering method                                |        |

|          | -                          | -                    | Initial column ordering                             |        |

|          |                            |                      | Row ordering                                        |        |

|   |     | 6.3.3                | Algorithm $merge(A^1, b, m)$                                    | 54 |

|---|-----|----------------------|-----------------------------------------------------------------|----|

|   |     | 6.3.4                | Iterative column ordering                                       | 54 |

|   | 6.4 | Comp                 | lexity                                                          | 56 |

|   |     | 6.4.1                | Time complexity                                                 | 56 |

|   |     | 6.4.2                | Memory complexity                                               | 56 |

|   |     | 6.4.3                | Cache complexity                                                | 56 |

|   | 6.5 | Exper                | rimental results                                                | 59 |

|   | 6.6 | Concl                | usion                                                           | 60 |

| 7 | Imp | olemen               | tation of Determinant by Condensation Method on GPU             | 63 |

|   | 7.1 | Introd               | luction                                                         | 63 |

|   | 7.2 | The c                | ondensation method                                              | 64 |

|   |     | 7.2.1                | The formula of Salem and Said                                   | 65 |

|   |     | 7.2.2                | The algebraic complexity of the condensation method             | 65 |

|   |     | 7.2.3                | The cache complexity of condensation method $\ . \ . \ . \ .$ . | 66 |

|   | 7.3 | GPU                  | implementation: the finite field case                           | 67 |

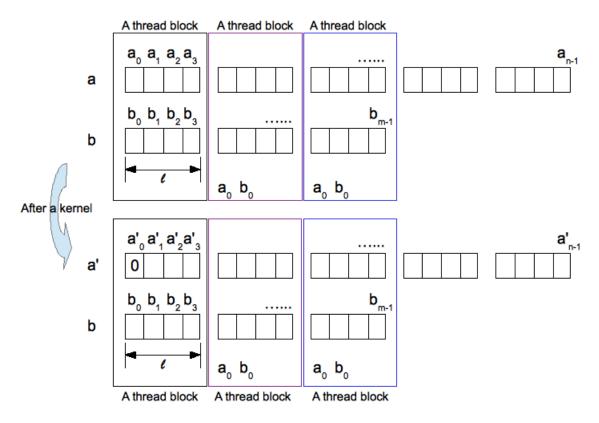

|   |     | 7.3.1                | Data mapping                                                    | 67 |

|   |     | 7.3.2                | Finite field arithmetic                                         | 68 |

|   |     | 7.3.3                | Experimental results                                            | 68 |

|   | 7.4 | GPU                  | implementation: the floating point case                         | 70 |

|   |     | 7.4.1                | Finding the pivots                                              | 70 |

|   |     | 7.4.2                | Multiplication of the successive pivots                         | 71 |

|   |     | 7.4.3                | Experimentation                                                 | 71 |

|   | 7.5 | Concl                | usion                                                           | 74 |

| 8 | Imp | olemen               | tation of Plain Multiplication for Univariate Polynomials       | 5  |

|   | on  | $\operatorname{GPU}$ |                                                                 | 77 |

|   | 8.1 | Introd               | luction                                                         | 77 |

|   |     | 8.1.1                | Elements of syntax                                              | 79 |

|   | 8.2 | Polyn                | omial multiplication algorithms                                 | 79 |

|   |     | 8.2.1                | Multiplication phase                                            | 80 |

|   |     | 8.2.2                | Addition phase                                                  | 80 |

|   |     | 8.2.3                | Arbitrary $x$                                                   | 82 |

|   |     | 8.2.4                | Comparison of running time estimates                            | 83 |

|   |     | 8.2.5                | Experimental results                                            | 83 |

|   | 8.3 | Concl                | usion                                                           | 84 |

| 9  | Imp   | lemen  | tation of the Euclidean Algorithm for Univariate Polyno                                                       | )-         |

|----|-------|--------|---------------------------------------------------------------------------------------------------------------|------------|

|    | mia   | l GCE  | Os on GPU                                                                                                     | 86         |

|    | 9.1   | Introd | luction                                                                                                       | 86         |

|    | 9.2   | Impor  | tance of plain division and Euclidean algorithm for polynomials                                               |            |

|    |       | with s | maller degrees                                                                                                | 88         |

|    | 9.3   | Plain  | division on the GPU $\ldots$ | 89         |

|    |       | 9.3.1  | Naive algorithm                                                                                               | 89         |

|    |       | 9.3.2  | Optimized algorithm $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$            | 91         |

|    |       | 9.3.3  | Comparison of running time estimates                                                                          | 92         |

|    |       | 9.3.4  | Experimental results of our optimized univariate division on                                                  |            |

|    |       |        | GPU                                                                                                           | 95         |

|    | 9.4   | Euclic | lean algorithm on GPU                                                                                         | 96         |

|    |       | 9.4.1  | Naive algorithm                                                                                               | 96         |

|    |       | 9.4.2  | Optimized algorithm                                                                                           | 97         |

|    |       | 9.4.3  | Comparison of running time estimates                                                                          | 101        |

|    |       | 9.4.4  | Experimental results of our optimized Euclidean algorithm on                                                  |            |

|    |       |        | GPU                                                                                                           | 102        |

|    | 9.5   | Concl  | usion                                                                                                         | 103        |

| 10 | Eva   | luatio | n and Interpolation of Univariate Polynomial by Subprod                                                       | <b>l</b> - |

|    | uct   | Tree 7 | Technique on GPU                                                                                              | 104        |

|    | 10.1  | Introd | luction                                                                                                       | 104        |

|    | 10.2  | Backg  | round                                                                                                         | 106        |

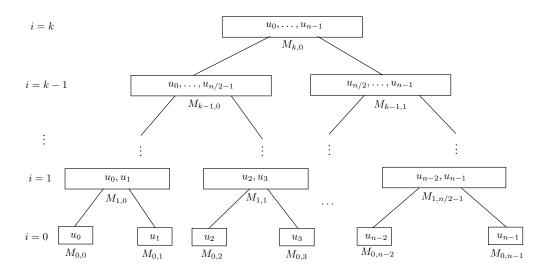

|    | 10.3  | Subpr  | oduct tree                                                                                                    | 110        |

|    | 10.4  | Subin  | verse tree                                                                                                    | 113        |

|    | 10.5  | Polyn  | omial evaluation $\ldots$    | 119        |

|    | 10.6  | Polyn  | omial interpolation                                                                                           | 121        |

|    | 10.7  | Exper  | imentation results                                                                                            | 124        |

|    | 10.8  | Concl  | usion                                                                                                         | 129        |

| 11 | Con   | clusio | n                                                                                                             | 130        |

| Cı | urric | ulum ` | Vitae                                                                                                         | 139        |

# List of Algorithms

| 1  | CountingSort(A, n, r)                                                                                               | 27  |

|----|---------------------------------------------------------------------------------------------------------------------|-----|

| 2  | $PreprocessingCounting(A, n, m, r)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                | 30  |

| 3  | $PartitionFurther(A, n, m, r, r')  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                 | 31  |

| 4  | $ExploreV(a_i.v, u, m)$                                                                                             | 38  |

| 5  | Create(L', n, k, m)                                                                                                 | 40  |

| 6  | $SpMxV(\mathtt{value}, \mathtt{colind}, \mathtt{rowptr}, x)$                                                        | 48  |

| 7  | BRGC(CRS(S), CCS(S), m, n, b, t)                                                                                    | 52  |

| 8  | $RowOrdering(A^1, CRS(S), CCS(S), m) \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $                                        | 54  |

| 9  | $RowPerm(A^1, R, \mathcal{R}, CRS(S)) \ . \ . \ . \ . \ . \ . \ . \ . \ . \$                                        | 55  |

| 10 | MulSuccPivot(X)                                                                                                     | 72  |

| 11 | $PlainMultiplicationGPU(a,b,d,x)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                  | 80  |

| 12 | MulKer(a, b, M, n, x)                                                                                               | 81  |

| 13 | AddKer(M, d, c, x, r, i)                                                                                            | 82  |

| 14 | Division(a,b)                                                                                                       | 87  |

| 15 | EuclideanGCD(a, b)                                                                                                  | 87  |

| 16 | NaivePlainDivisionGPU $(a, b)$                                                                                      | 91  |

| 17 | NaiveDivKernel(a, b, q, i, d)                                                                                       | 91  |

| 18 | OptimizePlainDivisionGPU(a, b, s)                                                                                   | 93  |

| 19 | OptDivKer(a, b, q, i, d, s)                                                                                         | 94  |

| 20 | NaivePlainGcdGPU $(a, b)$                                                                                           | 97  |

| 21 | $NaivePlainGcdKernel(a, b, st \ )  . \ . \ . \ . \ . \ . \ . \ . \ . \ .$                                           | 98  |

| 22 | OptimizedPlainGcdGPU(a, b, s)                                                                                       | 99  |

| 23 | OptGcdKer(a, b, s st)                                                                                               | 100 |

| 24 | $SubproductTree(m_0,\ldots,m_{n-1})$                                                                                | 107 |

| 25 | $Inverse(f,\ell)$                                                                                                   | 109 |

| 26 | $TopDownTraverse(f',k',h',M_n,F)$                                                                                   | 114 |

| 27 | OneStepNewtonIteration(f,g,i)                                                                                       | 116 |

| 28 | $EfficientOneStep(M'_{i,j},InvM_{i,j},i)  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $ | 116 |

| 29 | $InvPolyCompute(M_n,InvM_{i,j})$                                                                                                                                             | 117 |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 30 | SubinverseTree $(M_n, H)$                                                                                                                                                    | 117 |

| 31 | FastRemainder(a,b)                                                                                                                                                           | 121 |

| 32 | LinearCombination $(M_n, c_0, \ldots, c_{n-1})$                                                                                                                              | 122 |

| 33 | $FastInterpolation(u_0,\ldots,u_{n-1},v_0,\ldots,v_{n-1})\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots\ldots$ | 123 |

# List of Figures

| 2.1  | The PRAM model.                                                                | 6    |

|------|--------------------------------------------------------------------------------|------|

| 2.2  | The ideal-cache model                                                          | 8    |

| 2.3  | Scanning an array of $n = N$ elements, with $L = B$ words per cache line       | . 10 |

| 2.4  | A directed acyclic graph (dag) representing the execution of a multi-          |      |

|      | threaded program. Each vertex represents an instruction while each             |      |

|      | edge represents a dependency between instructions                              | 12   |

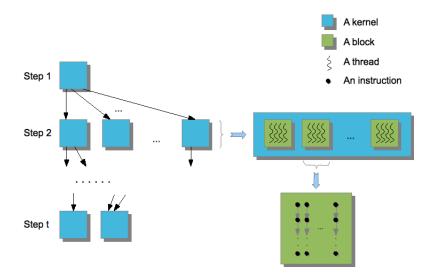

| 3.1  | Overview of a many-core machine program                                        | 20   |

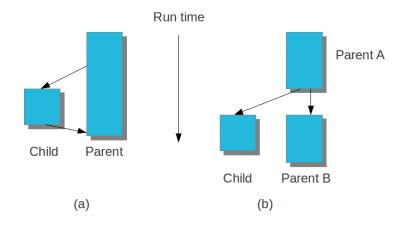

| 3.2  | Adjust any program into the DAG of many-core machine model                     | 25   |

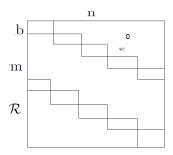

| 6.1  | After initial column ordering.                                                 | 51   |

| 6.2  | After row permutation                                                          | 52   |

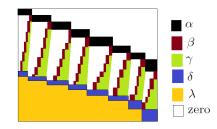

| 6.3  | The distribution of different types of non-zeros.                              | 57   |

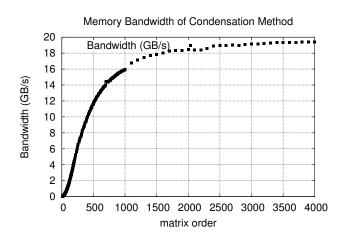

| 7.1  | Effective memory bandwidth of condensation method                              | 69   |

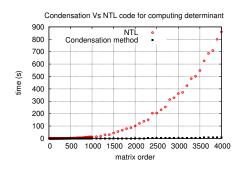

| 7.2  | CUDA code for condensation method and determinant on NTL over                  |      |

|      | finite field                                                                   | 71   |

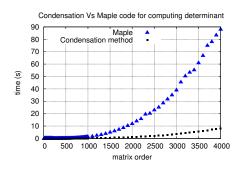

| 7.3  | CUDA code for condensation method and determinant on MAPLE                     |      |

|      | over finite field                                                              | 71   |

| 8.1  | Dividing the work of coefficient multiplication among threadblocks.            | 81   |

| 9.1  | A naive division step                                                          | 90   |

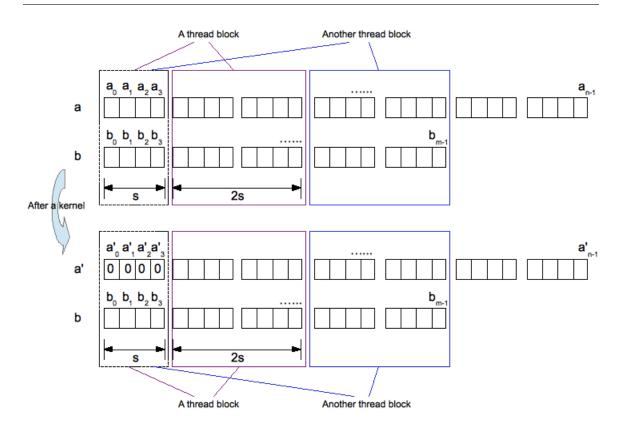

| 9.2  | Optimize division steps.                                                       | 93   |

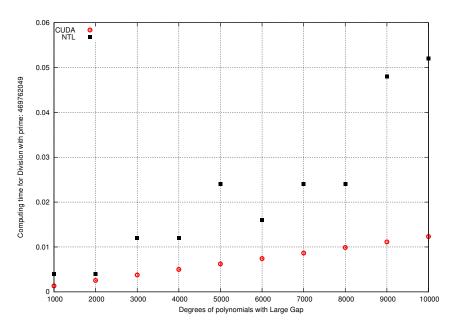

| 9.3  | Comparison between parallel plain division on CUDA and fast division           |      |

|      | in NTL for univariate polynomials with large degree gap                        | 95   |

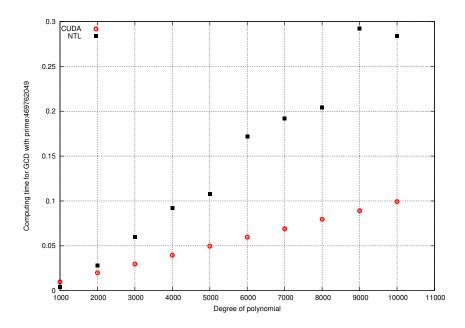

| 9.4  | Comparison between parallel GCD on CUDA and FFT-based GCD in                   |      |

|      | NTL for univariate polynomials, with the same degree $(n = m)$                 | 102  |

| 10.1 | Subproduct tree associated with the point set $U = \{u_0, \ldots, u_{n-1}\}$ . | 107  |

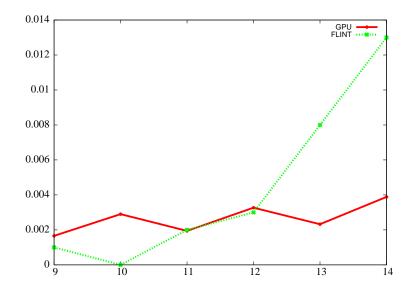

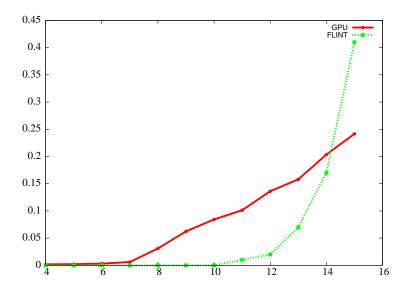

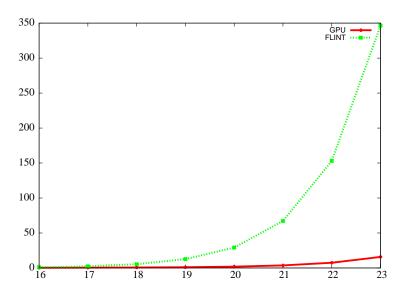

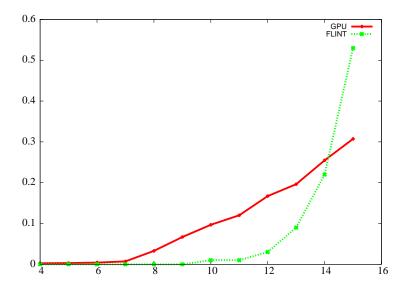

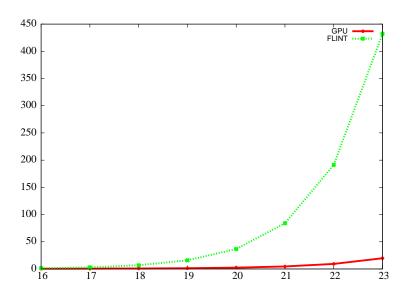

| 10.2 | Our GPU implementation versus FLINT for FFT-based polynom | ial |     |

|------|-----------------------------------------------------------|-----|-----|

|      | multiplication.                                           |     | 126 |

| 10.3 | Evaluation lower degrees                                  |     | 127 |

| 10.4 | Evaluation higher degrees                                 |     | 127 |

| 10.5 | Interpolation lower degrees                               |     | 128 |

| 10.6 | Interpolation higher degrees                              |     | 128 |

# List of Tables

| 2.1        | Work, span and parallelism of classical algorithms                                                                                                                                    | 15       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.1        | Algorithm parameters                                                                                                                                                                  | 23       |

| 4.1        | CPU times in seconds for both classical and cache-oblivious counting sort algorithm.                                                                                                  | 34       |

| 6.1<br>6.2 | Test matrices with the number of non-zeros of type $\alpha$ , $\beta$ and $\delta$<br>Normalized cache misses on ideal cache model simulator and normal-<br>ized CPU time for SpMxVs. | 60<br>61 |

| 6.3        | Preprocessing time                                                                                                                                                                    | 62       |

| 7.1        | Determinant of Hilbert matrix by MAPLE, MATLAB, and condensa-<br>tion method on both CPU and GPU.                                                                                     | 74       |

| 7.2        | Time(s) required to compute determinant of Hilbert Matrix by<br>MAPLE, MATLAB, and condensation method on both CPU and GPU.                                                           |          |

| 8.1        | Long multiplication $(n = m = 5)$                                                                                                                                                     | 78       |

| 8.2<br>8.3 | Comparison between plain and FFT-based polynomial multiplications<br>for balanced pairs $(n = m)$ on CUDA                                                                             | 84       |

| 0.0        | Computation time for plain multiplication on CUDA for unbalance<br>pairs $(n \neq m)$ .                                                                                               | 84       |

| 9.1        | GCD implementation on CUDA with two different values of $s.$                                                                                                                          | 101      |

| 10.1       | Computation time for random polynomials with different degrees $(2^K)$                                                                                                                |          |

|            | and points. All of the times are in seconds                                                                                                                                           | 125      |

| 10.2       | Execution times of multiplication                                                                                                                                                     | 125      |

| 10.3       | Execution times of polynomial evaluation and interpolation                                                                                                                            | 126      |

| 10.4       | Effective memory bandwidth                                                                                                                                                            | 129      |

# Chapter 1

# Introduction

This thesis deals with the implementation of basic routines in computer algebra targeting multi-core and many-core architectures. We consider routines from linear algebra (sparse and dense) and polynomial system solving. In contrast to their counterpart in numerical computing, these routines perform calculations in an exact and complete way. As a consequence, they are highly demanding in computer resources, time and memory. This often limits the impact of computer algebra software to problems of moderate size. However, the abundant computing power of hardware acceleration technologies suggests that much harder problems could be attacked with symbolic computation.

With respect to standard high-performance computing challenges, computer algebra low-level routines fall into the following categories.

- (P1): Memory access patterns are highly irregular and work count is essentially proportional to the number of memory accesses. Typical examples are sparse matrix arithmetic and sparse polynomial arithmetic.

- (P2): The amount of work is much larger than the amount of reads/writes while memory access patterns are rather regular. Typical examples are dense matrix arithmetic and dense polynomial arithmetic. While these routines allow for fine grain parallelism, certain complex memory access patterns (like for Fast Fourier Transform algorithms) make these operations not so suitable for multi-cores.

Problems of the first kind are more suitable for multicore architectures while problems of the second kind are eligible for many-core accelerators (like Graphics Processing Units).

In this thesis, we are interested in developing tools for analyzing algorithms and implementation techniques targeting hardware acceleration technologies. On multicores, we consider operations that are not suitable for many-cores, due to large data size (a frequent issue in computer algebra) and that pause challenges in terms of memory transfer. For such operations, we propose pre-processing techniques that reshape the input data so as to reduce memory transfer when those operations are applied to the reshaped data. Cache complexity analysis and experimentation confirm the effectiveness of the proposed techniques. To be more specific, our work is driven by classical problem from linear algebra: improving data locality in sparse matrix vector (SpMxV) multiplication. This problem is hard as the permutation of rows or columns of a sparse matrix to maximize locality in SpMxV multiplication is NP-hard [59]. In Chapter 6, we propose a reordering algorithm for sparse matrices that improves the data locality during (SpMxV) multiplication. In each test-case, we re-arrange the input data and show that the cost of this re-arrangement can be amortized against the cost of calculations with the input data, such as linear system solving by iterative methods (conjugate gradient, etc.). We provide cache complexity analysis whose favorable results are confirmed experimentally. As a by-product of this research, we propose a new integer sorting algorithm, which is suitable for large sparse objects. This algorithm is described in Chapter 5.

On many-cores, we consider operations that are both data intensive and compute intensive, which is another frequent feature of computer algebra calculations, as mentioned above. For such operations, we propose a computational model for designing algorithms targeting many-cores, with a focus on reducing parallelism overheads. We present a model of multithreaded computation namely many-core machine model (in Chapter 3) that combines the fork-join and SIMD parallelisms, with an emphasis on estimating parallelism overheads, so as to reduce scheduling and communication costs in GPU programs. We have applied this model and successfully reduced parallelism overheads for several basic routines in polynomial algebra. For polynomial multiplication, our theoretical analysis allows us to reduce parallelism overheads due not only to data transfer but also to code divergence, see Chapter 8. For the Euclidean algorithm, our running time estimates match those obtained with the Systolic VLSI Array Model ([9]). Meanwhile, our CUDA code implementing this optimized Euclidean algorithm runs within the same estimate analyzed by our model for input polynomials with degree up to 100,000. This is reported in Chapter 9.

In Chapter 10, we propose a parallel algorithms for performing subproduct tree construction, evaluation and interpolation and report on their implementation on many-core GPUs. We enhance the traditional algorithms for polynomial evaluation and interpolation based on subproduct-trees, by introducing the notion of a subinverse tree. For subproduct-tree operations, we demonstrate the importance of adaptive algorithms. That is, algorithms that adapt their behavior to the available computing resources. In particular, we combine parallel plain arithmetic and parallel fast arithmetic.

In Chapter 7, we present a GPU implementation of the condensation method for computing the determinant of a matrix. To the best of our knowledge, this is the first study of the parallelization of this algorithm. We consider both matrices with finite field coefficients and floating point number coefficients. Notably, the latter case exhibits favorable behavior in terms of numerical stability.

All our GPU code is freely available in source at www.cumodp.org.

# Chapter 2

# Background

Until the advent of multi-core and many-core architectures, algorithms subject to effective implementation on personal computers were often designed with *algebraic* complexity as the main complexity measure and with sequential running time as the main performance counter [40, 41, 42, 13, 20]. Nevertheless, during the past 40 years, the increasing gap between memory access time and CPU cycle time, in favor of the latter, brought another important and practical efficiency measure: cache complexity [36, 17]. In addition, with parallel processing becoming available on every desktop or laptop, the work and span of an algorithm expressed in the fork-join multithreaded model [18, 13] have become the natural quantities to compute in order to estimate parallelism.

These complexity measures (algebraic complexity, cache complexity, parallelism) are defined for computation models that largely simplify reality. On many-core architectures, several phenomena (parallelism overhead, synchronization among threads of all thread blocks, utilization of all multiprocessors, etc.) limit the performances of applications which, theoretically, have a lot of opportunities for concurrent execution.

## 2.1 Random access machine (RAM) model

The RAM is a simple model of computation which is used to measure the run time of an algorithm by counting up the number of steps it takes on a given problem instance. Unlike *Turing machine*, which could not access the memory immediately without accessing all intermediate cells, it can access the arbitrary memory in a single step process. The memory considered, in this model, is unbounded and has the capability to store arbitrarily large integers in each of its memory cells. This model can be programmed in some specified but arbitrary programming language. Some of the properties of this model are as follows:

- Each "simple operation" like addition, subtraction, multiplication, assign, branching, calling, etc. takes exactly 1 time step.

- Loops and procedures are considered to be the composition of many single-step operations.

- Each memory access takes exactly one time step, and we have as much memory as we need. The RAM model takes no notice of whether an item is in cache or on the disk, which simplifies the analysis.

A common problem of this model is that it is too simple, that is, these assumptions make the conclusions and analysis too hard to believe in practice. For instance, multiplying two numbers does not have the same cost as adding two numbers, which clearly violates the first assumption of the model. Memory access times also differ greatly depending on whether data are available in cache or on memory or on the disk, which violates the third assumption. However, in spite of having such restrictions, this model does not provide misleading results for the real world problems, since this only assumes a simple abstract model of computation. Furthermore, robustness of the RAM model enables us to analyze algorithms in a machine-independent way.

### 2.2 The PRAM model

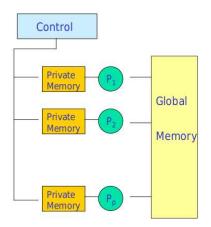

The Parallel Random Access Machine (PRAM) is a natural generalization of RAM. It has unbounded number of processors  $P_0, P_1, P_2, \cdots$ . Each of these processors has unbounded private local memory, which is a sets of registers. Unlike RAM model, it does not have tapes. The computing capability of each processor is the same as RAM. These processors can communicate with each other via shared memory (global memory)  $M[0], M[1], M[2], \cdots$ , which is also unbounded. Note that, it is the only way, by which a processor can communicate with another processor. Each processor can access shared memory in unit time, unless there is a conflict.

In Figure 2.1, a PRAM model is shown. The input of a PRAM program consists of n items stored in  $M[0], \ldots, M[n-1]$ . The output of a PRAM program consists of n' items stored in n' memory cells, say  $M[n], \ldots, M[n+n'-1]$ . A PRAM instruction executes in a 3-phase cycle:

- 1. *Read* (if needed) from a shared memory cell,

- 2. Compute locally (if needed),

Figure 2.1: The PRAM model.

3. Write in a shared memory cell (if needed).

All processors execute their 3-phase cycles synchronously. Processor  $P_0$  has a special activation register specifying the maximum index of an active processor. Initially, only  $P_0$  is active; it computes the number of required active processors and loads this number in the activation register. Then the corresponding processors start executing their programs. Computations proceed until  $P_0$  halts, at which time all other active processors are halted.

The PRAM Model is attractive for designing parallel algorithms because of the following reasons.

- It is *natural*: the number of operations executed per one cycle on p processors is at most p.

- It is *strong*: any processor can read or write any shared memory cell in *unit time*.

- It is *simple*: ignoring any communication or synchronization overhead.

This natural, strong and simple PRAM model can be used as a benchmark. If a problem has no feasible (or efficient) solution on a PRAM then it is likely that it has no feasible (or efficient) solution on any parallel machine. The PRAM model is an idealization of existing shared memory parallel machines. It ignores lower level architecture constraints (memory access overhead, synchronization overhead, intercommunication throughput, connectivity, speed limits, etc.)

#### 2.2.1 Parallel time, efficiency and speedup factor

The *Parallel Time*, denoted by T(n, p), is the time elapsed from the start of a parallel computation to the moment where the last processor terminates, on an input data of size n, and using p processors. T(n, p) takes into account computational steps (such as adding, multiplying, swapping variables), routing (or communication) steps (such as transferring and exchanging information between processors). The *parallel efficiency*, denoted by E(n, p), is

$$E(n,p) = \frac{\mathsf{SU}(n)}{pT(n,p)}$$

where SU(n) is a lower bound for a sequential execution. Observe that we have  $SU(n) \leq pT(n,p)$  and thus  $E(n,p) \leq 1$ . One also often considers the speedup factor defined by

$$S(n,p) = \frac{\mathsf{SU}(n)}{T(n,p)}$$

### 2.2.2 Different types of PRAM models

It is natural to have conflicts in accessing shared memory for some applications. To resolve this issue and synchronize the parallel execution, some mechanism has to be defined for concurrent read and write access conflicts to the same shared memory cell. Some of the basic submodels of PRAM are given below.

**Exclusive Read Exclusive Write (EREW).** No two processors are allowed to read or write the same shared memory cell simultaneously.

**Concurrent Read Exclusive Write (CREW).** Simultaneous reads of the same memory cell are allowed, but no two processors can write the same shared memory cell simultaneously.

**Concurrent Read Concurrent Write (CRCW).** Simultaneous reads and writes of the same memory cell are allowed. CRCW can be divided further based on concurrent writes.

**PRIORITY Concurrent Read Concurrent Write (PRIORITY CRCW).** Simultaneous reads of the same memory cell are allowed. Processors are assigned fixed and distinct priorities. In case of write conflict, the processor with highest priority is allowed to complete WRITE.

**ARBITRARY Concurrent Read Concurrent Write (ARBITRARY CRCW).** Simultaneous reads of the same memory cell are allowed. In case of write conflict, one

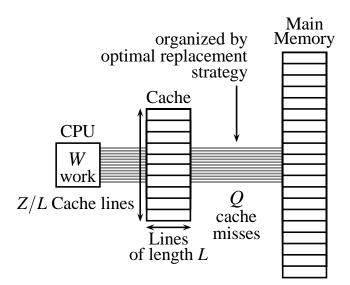

Figure 2.2: The ideal-cache model.

randomly chosen processor is allowed to complete WRITE. An algorithm written for this model should make no assumptions about which processor is chosen in case of write conflict.

**COMMON Concurrent Read Concurrent Write (COMMON CRCW).** Simultaneous reads of the same memory cell are allowed. In case of write conflict, all processors are allowed to complete WRITE iff all values to be written are equal. An algorithm written for this model should make sure that this condition is satisfied. If not, the algorithm is illegal and the machine state will be undefined.

### 2.3 The ideal cache model

The cache complexity of an algorithm aims at measuring the (negative) impact of memory traffic between the cache and the main memory of a processor executing that algorithm. Cache complexity is based on the *ideal-cache model* shown in Figure 2.2. This idea was first introduced by Matteo Frigo, Charles E. Leiserson, Harald Prokop, and Sridhar Ramachandran in 1999 [17]. In this model, there is a computer with a two-level memory hierarchy consisting of an ideal (data) cache of Z words and an arbitrarily large main memory. The cache is partitioned into Z/L cache lines where L is the length of each cache line representing the amount of consecutive words that are always moved in a group between the cache and the main memory. In order to achieve spatial locality, cache designers usually use L > 1 which eventually mitigates the overhead of moving the cache line from the main memory to the cache. As a result, it is generally assumed that the cache is *tall* and practically that we have

$$Z = \Omega(L^2).$$

In the sequel of this thesis, the above relation is referred as the *tall cache assumption*.

In the ideal-cache model, the processor can only refer to words that reside in the cache. If the referenced line of a word is found in cache, then that word is delivered to the processor for further processing. This situation is literally called a *cache hit*. Otherwise, a *cache miss* occurs and the line is first fetched into anywhere in the cache before transferring it to the processor; this mapping from memory to cache is called *full associativity*. If the cache is full, a cache line must be evicted. The ideal cache uses the optimal off-line cache replacement policy to perfectly exploit *temporal locality*. In this policy, the cache line whose next access is furthest in the future is replaced [5].

Cache complexity analyzes algorithms in terms of two types of measurements. The first one is the *work complexity*, W(n), where n is the input data size of the algorithm. This complexity estimate is actually the conventional running time in a RAM model [1]. The second measurement is its *cache complexity*, Q(n; Z, L), representing the number of cache misses the algorithm incurs as a function of:

- the input data size n,

- the cache size Z, and

- the cache line length L of the ideal cache.

When Z and L are clear from the context, the cache complexity can be denoted simply by Q(n).

An algorithm whose cache parameters can be tuned, either at compile-time or at runtime, to optimize its cache complexity, is called *cache aware*; while other algorithms whose performance does not depend on cache parameters are called *cache oblivious*. The performance of cache-aware algorithm is often satisfactory. However, there are many approaches which can be applied to design optimal cache oblivious algorithms to run on any machine without fine tuning their parameters.

Although cache oblivious algorithms do not depend on cache parameters, their analysis naturally depends on the alignment of data block in memory. For instance, due to a specific type of alignment issue based on the size of block and data elements (See Proposition 1 and its proof), the cache-oblivious bound is an additive 1 away

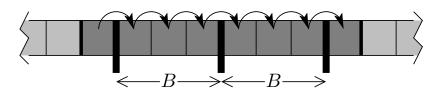

Figure 2.3: Scanning an array of n = N elements, with L = B words per cache line.

from the external-memory bound [36]. However, such type of error is reasonable as our main goal is to match bounds within multiplicative constant factors.

**Proposition 1.** Scanning n elements stored in a contiguous segment of memory with cache line size L costs at most  $\lceil n/L \rceil + 1$  cache misses.

**PROOF**  $\triangleright$  The main ingredient of the proof is based on the alignment of data elements in memory. We make the following observations.

- Let (q, r) be the quotient and remainder in the integer division of n by L. Let u (resp. w) be the total number of words in a fully (not fully) used cache line. Thus, we have n = u + w.

- If w = 0 then  $(q, r) = (\lfloor n/L \rfloor, 0)$  and the scanning costs exactly q; thus the conclusion is clear since  $\lfloor n/L \rfloor = \lfloor n/L \rfloor$  in this case.

- If 0 < w < L then (q, r) = (⌊n/L⌋, w) and the scanning costs exactly q + 2; the conclusion is clear since ⌈n/L⌉ = ⌊n/L⌋ + 1 in this case.</li>

- If  $L \leq w < 2L$  then  $(q, r) = (\lfloor n/L \rfloor, w L)$  and the scanning costs exactly q + 1; the conclusion is clear again.

$\triangleleft$

## 2.4 The multi-core machine model

A multi-core architecture consists of a multi-core processor, which is a single computing component with two or more independent processors called "cores". These cores are the basic units that perform read and execute program instructions. These instructions are ordinary CPU instructions like *add*, *move data*, and *branch*. But, importantly, the multiple cores can execute multiple instructions at the same time, which enhance the overall speed of the program execution in the way of parallel computing. A many-core processor is also a multi-core processor in which the number of cores is large enough that traditional multiprocessor techniques are no longer efficient. Manufacturers typically integrate the cores onto a single integrated circuit die, known as a chip multiprocessor or CMP, or onto multiple dies in a single chip package. The cores in a multi-core architecture can be connected *tightly* or *loosely*. For instance, cores may or may not share caches, and they may implement inter-core communication techniques such as message passing or shared memory. Common network topologies are used to interconnect cores, including bus, ring, two-dimensional mesh and crossbar. *Homogeneous* multi-core systems include only identical cores, whereas, *heterogeneous* multi-core systems have cores which are not identical in practice. Cores on multi-ore systems may implement architecture features such as instruction level parallelism (ILP), vector processing, SIMD or multithreading, similar to those of single-processor systems.

The advantages of multi-core architecture include the fact that *cache coherency* circuitry operates at a much higher clock-rate than in distributed systems where the signals have to travel off-chip. That is, signals between different CPUs (cores) travel shorter distances, and therefore those signals degrade less. As a result, these higher-quality signals with high frequency allow more data to be transferred within a short time period. Moreover, a multi-core processor usually uses less power than multiple coupled single-core processors, this is because of the reduced power required to drive off-chip signals. Furthermore, the cores share some circuitry, like the L2 cache and the interface to the front side bus (FSB). Also, multi-core design produces a product with lower risk of design error than devising a new wider core-design.

Although there are lots of advantages of multi-cores, writing multithreaded programs for this architecture remains quite challenging. Maximizing the utilization of the computing resources in this architecture requires adjustments both to the operating system (OS) support and to existing application software. Also, the performance of multi-core processors to execute applications depends on the use of multiple threads within applications. Finally, raw processing power is not the only constraint on system performance. Several processing cores sharing the same system bus and as a result memory bandwidth limits the real-world performance advantage. If a single core is about to consume whole memory-bandwidth, then for the dual-core, it improves only 30% to 70% of its performance. If memory bandwidth is not a problem, upto 90% improvement is possible. Moreover, if communication between the CPUs is the negligible factor, then it would be possible for an application to execute faster on two CPUs than on one dual-core, which would count as much as 100% improvement.

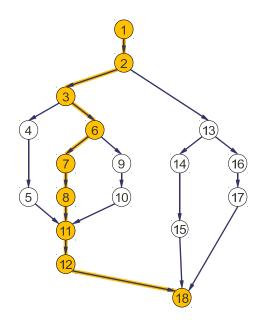

Figure 2.4: A directed acyclic graph (dag) representing the execution of a multithreaded program. Each vertex represents an instruction while each edge represents a dependency between instructions.

## 2.5 The fork-join parallelism model

The  $Cilk++^1$  concurrency platform [7, 18, 45, 15] provides a simple theoretical model called the *fork-join parallelism model* or *dag (direct acyclic graph) model* of multi-threading for parallel computation. This model represents the execution of a multi-threaded program as a set of nonblocking threads denoted by the vertices of a dag, where the dag edges indicate dependencies between instructions. See Figure 2.4.

In the Cilk++ terminology, a thread is a maximal sequence of instructions that ends with a spawn, sync, or return statement. These statements are used to denote respectively:

- an execution flow forking,

- a *synchronization point*, at which currently running threads must join before the execution flow proceeds further,

- the return point of a function.

A correct execution of a Cilk++ program must meet all the dependencies in the dag, that is, a thread cannot be executed until all the depending treads have completed. The order in which these dependent threads will be executed on the processors is determined by the *scheduler*.

<sup>&</sup>lt;sup>1</sup>http://www.cilk.com

Cilk++s scheduler executes any Cilk++ computation in a nearly optimal time, see [18] for details. From a theoretical viewpoint, there are two natural measures that allow us to define parallelism precisely, as well as to provide important bounds on performance and speedup which are discussed in the following subsections.

#### 2.5.1 The work law

The first important measure is the *work* which is defined as the total amount of time required to execute all the instructions of a given program. For instance, if each instruction requires a unit amount of time to execute, then the work for the example dag shown in Figure 2.4 is 18.

Let  $T_P$  be the fastest possible execution time of the application on P processors. Therefore, we denote the work by  $T_1$  as it corresponds to the execution time on 1 processor. Moreover, we have the following relation

$$T_p \ge T_1/P,\tag{2.1}$$

which is referred as the *work law*. In our simple theoretical model, the justification of this relation is easy: each processor executes at most 1 instruction per unit time and therefore P processors can execute at most P instructions per unit time. Therefore, the *speedup* on P processors is at most P since we have

$$T_1/T_P \le P. \tag{2.2}$$

#### 2.5.2 The span law

The second important measure is based on the program's *critical-path length* denoted by  $T_{\infty}$ . This is actually the execution time of the application on an infinite number of processors or, equivalently, the time needed to execute threads along the longest path of dependency. As a result, we have the following relation, called the *span law*:

$$T_P \ge T_{\infty}.\tag{2.3}$$

#### 2.5.3 Parallelism

In the fork-join parallelism model, *parallelism* is defined as the ratio of work to span, or  $T_1/T_{\infty}$ . Thus, it can be considered as the average amount of work along each point of the critical path. Specifically, the speedup for any number of processors cannot be

greater than  $T_1/T_{\infty}$ . Indeed, Equations 2.2 and 2.3 imply that speedup satisfies

$$T_1/T_P \le T_1/T_\infty \le P.$$

As an example, the parallelism of the dag shown in Figure 2.4 is 18/9 = 2. This means that there is little chance for improving the parallelism on more than 2 processors, since additional processors will often starve for work and remain idle.

#### 2.5.4 Performance bounds

For an application running on a parallel machine with P processors with work  $T_1$  and span  $T_{\infty}$ , the Cilk++ *work-stealing scheduler* achieves an expected running time as follows:

$$T_P = T_1/P + O(T_\infty), \tag{2.4}$$

under the following three hypotheses:

- each strand executes in unit time,

- for almost all parallel steps there are at least p strands to run,

- each processor is either working or stealing.

See [18] for details.

If the parallelism  $T_1/T_{\infty}$  is so large that it sufficiently exceeds P, that is  $T_1/T_{\infty} \gg P$ , or equivalently  $T_1/P \gg T_{\infty}$ , then from Equation (2.4) we have  $T_P \approx T_1/P$ . From this, we easily observe that the work-stealing scheduler achieves a nearly perfect linear speedup of  $T_1/T_P \approx P$ .

#### 2.5.5 Work, span and parallelism of classical algorithms

The work, span and parallelism of some of the classical algorithms in the fork-join parallelism model is shown in Table 2.1.

### 2.6 Systolic arrays

Systolic arrays are matrix-like regular rows of basic data processing units called cells. Each of these cells relies on arriving data from different directions in the array at regular intervals and being combined [11]. The data streams, which are entering and leaving the ports of the array, are generated by *auto-sequencing memory units* called ASMs. In embedded systems, it is also possible that these data streams be input from and/or output to external components.

| Algorithm             | Work                    | Span                    | Parallelism                                            |

|-----------------------|-------------------------|-------------------------|--------------------------------------------------------|

| Merge sort            | $\Theta(n \log_2(n))$   | $\Theta(\log_2(n)^3)$   | $\Theta(\frac{n}{\log_2(n)^2})$                        |

| Matrix multiplication | $\Theta(n^3)$           | $\Theta(\log_2(n))$     | $\Theta(\frac{n^3}{\log_2(n)})$                        |

| Strassen              | $\Theta(n^{\log_2(7)})$ | $\Theta(\log_2(n)^2)$   | $\Theta\left(\frac{n^{\log_2(7)}}{\log_2(n)^2}\right)$ |

| LU-decomposition      | $\Theta(n^3)$           | $\Theta(n \log_2(n))$   | $\Theta(\frac{n^2}{\log_2(n)})$                        |

| Tableau construction  | $\Theta(n^2)$           | $\Omega(n^{\log_2(3)})$ | $\Theta(n^{0.415})$                                    |

| FFT                   | $\Theta(n  \log_2(n))$  | $\Theta(\log_2(n)^2)$   | $\Theta(\frac{n}{\log_2(n)})$                          |

Table 2.1: Work, span and parallelism of classical algorithms.

Matrix multiplication might be a good example of the design of systolic algorithm, where one matrix is fed in a row at a time from the top of the array and is passed down the array. The other matrix is fed in a column at a time from the left hand side of the array and passes from left to right. In order to be seen each processor as a whole row and a whole column, dummy values are often passed in when they are not like so. Finally, the multiplication result is stored in the array and can now be output a row or a column at a time, flowing down or across the array.

Lots of applications of systolic arrays include faster input processing, scalability, high throughput etc. The cells are organized in such a way that it can simultaneously process the input, that is, its processing is faster than the conventional computing architecture. Also, this architecture can easily be extended to many more processors according to the requirements of the application. Moreover, systolic arrays offer a way to take certain exponential algorithms and use hardware to make them linear.

The disadvantages of systolic arrays include its complicated design and implementation of hardware and software, highly cost of hardware compared to uniprocessor system, highly specialized for particular applications, difficult to build the system etc.

In the perspective of this thesis, systolic arrays are important since they provide the best known work-efficient parallel algorithm for computing GCDs of univariate polynomials [10]. By work-efficient, we mean that the work is the same complexity class as the Euclidean Algorithm.

# Chapter 3

# Many-core Machine Model

We propose a model of computations which aims at capturing parallelism overheads (such as communication and synchronization costs) of programs written for modern GPU architectures. We establish a Graham-Brent theorem for this model so as to estimate running time of programs running on p streaming multiprocessors. We evaluate the benefits of our model with three applications. In each case, our model is used to optimize a program parameter controlling overhead.

This chapter is a joint work with M. Moreno Maza and N. Xie.

## 3.1 Introduction

Designing efficient algorithms targeting implementation on hardware acceleration technologies (multi-core processors, graphics processing units (GPUs), fieldprogrammable gate arrays) creates major challenges for computer scientists. A first difficulty is to define models of computations retaining the features of actual computers that have a dominant impact on program performance. This implies to specify not only the appropriate complexity measures for algorithms but also the relevant parameters for the theoretical machine executing those algorithms. Once different algorithmic solutions for a given problem and a given model of computations are available, a second difficulty is to combine those complexity measures in order to select the "best" algorithm.

In the fork-join parallelism model [6] two complexity measures (the work and the span) and one machine parameter (the number of processors) can be combined in results like the Graham-Brent theorem ([6, 24]) or the Blumofe-Leiserson theorem (Theorems 13 & 14 in [7]) so as to compare algorithm running time estimates. A

variant of this latter theorem is actually supporting successfully the implementation of the parallel performance analyzer called Cilkview [35] on multi-core architectures.

With many-core processors, in particular GPUs, one needs to integrate SIMD (Single Instruction Multiple Data) processing into the model. The PRAM model ([66, 22]) has this flavor but it does not have the task-parallelism dimension which is necessary to represent the relations between the different kernels of an application written with the Compute Unified Device Architecture (CUDA) [58]. In addition, the PRAM model fails to retain important features of actual computers related to memory traffic, such as cache complexity ([18, 19]). This latter notion has been proved to be very useful on single-core and multi-core multiprocessors.

An attempt to integrate memory contention into the PRAM model has been made with the QRQW (Queue Read Queue Write) PRAM, defined in [23] by Gibbons, Matias and Ramachandran. The Authors also enhance the Graham-Brent theorem. However, they unify in a single quantity time spent in arithmetic operations and time spent in read/write accesses. We believe that this unification is not appropriate for recent many-core processors, such as GPUs, for which the ratio between one read/write access to the global memory and one floating point operation can be in the 100's.

In a recent paper, Ma, Agrawal and Chamberlain [48] introduce the TMM (Threaded Many-core Memory) model which retains many important characteristics of GPU-type architectures, including several machine parameters such as throughput and coalesced granularity. Moreover, while their running time estimate on P cores is not a Graham-Brent theorem, TMM analysis can order algorithms from slow to fast for many different settings of those machine parameters.

Many works, such as [49, 47], targeting code optimization and performance prediction of GPU programs are related to our work, though these papers do not define an abstract model in support of algorithm analysis.

In this chapter, we propose a many-core machine model (MMM) which aims at optimizing algorithms targeting implementation on GPUs. We insist on the following aspects:

- *Two-level DAG programs.* Defined in Section 3.2, this feature captures the two levels of parallelism (fork-join and SIMD) of CUDA-like programs.

- *Parallelism overhead.* We introduce this complexity measure in Section 3.2.3 with the objective of analyzing communication and synchronization costs.

- A Graham-Brent theorem. We combine three complexity measures (work, span

and parallelism overhead) and two machine parameters (size of local memory and data transfer throughput) in order to estimate the running time of an MMM program on p streaming multiprocessors. This result is Theorem 1 in Section 3.2.4.

To demonstrate and evaluate the benefits of our model, we consider three applications for which we have realized an implementation reported in [31]. In each case, the parallelism overhead (and also the work, to a lesser extent) depends on a program parameter. For the first two applications, namely polynomial division and the Euclidean Algorithm (see Chapter 9),

this parameter controls the amount of data transfer between global memory and local memories. For the third application, polynomial multiplication (see Chapter 8)

this parameter controls the amount of branch divergence (see [25] for optimization techniques related to this performance issue) which can also be seen as a parallelism overhead.

For each of these three applications, we apply the following strategy.

- 1. We determine a value of this program parameter that minimizes parallelism overhead.

- 2. We check that the work overhead introduced by this optimization technique remains very low. In fact, this work overhead is typically 30% of the work of the non-optimized algorithm.

- 3. We use our version of Graham-Brent theorem to show that the estimated running time (on *p* streaming multiprocessors) of the optimized algorithm is asymptotically smaller than that of the non-optimized algorithm. In fact, this speedup is typically a factor of 2, which is confirmed by the experimental study of [31].

Finally, we observe that, in our model, the Euclidean Algorithm reaches the running estimates predicted by the Systolic VLSI Array Model [9]. At the same time, the CUDA code implementing the Euclidean Algorithm developed with our model runs within the same estimate for input polynomials with degree up to 100,000, as reported in [31].

### 3.2 A many-core machine model

A well-known method for optimizing CUDA programs is to transfer data from the global memory to the local memories in order to reduce redundant memory accesses with low latency and high throughput. One of the main reasons for this optimization is the fact that global memory latency is approximately 400 to 800 cycles, while local memory latency is only a few cycles. This memory latency difference, when not properly taken into account, may have a dramatic negative impact on program performance. As mentioned in the introduction, this hardware feature of GPUs cannot be captured by the well-studied PRAM model. Indeed, any memory access, as well as any integer arithmetic operation, is performed in *unit time* on a PRAM machine.

This and other limitations of the PRAM model have motivated variants of this model, including our work. Another motivation is the new programming model supported by NVIDIA<sup>1</sup> Kepler architecture, which allows algorithms to run entirely on the device (GPU) without host (CPU) interactions. The model of parallel computations presented in this paper aims at capturing communication and synchronization overheads of programs written for modern GPU architectures, such as NVIDIA Fermi and NVIDIA Kepler.

As specified in Sections 3.2.1 and 3.2.2 below, our many-core machine model (MMM) retains many of the key characteristics of modern GPU architectures and the CUDA programming model. However, in order to support algorithm analysis, with an emphasis on parallelism overheads, as defined in Section 3.2.3, an MMM machine admits a few simplifications and limitations with respect to an actual GPU device. We justify those choices in Section 3.2.5 and explain how more general models can be reduced to ours.

### **3.2.1** Many-core machine characteristics

**Architecture.** An MMM machine possesses an unbounded number of *streaming multiprocessors* (SMs) which are all identical. Each SM has a finite number of processing cores and a fixed-size local memory. An MMM machine has a 2-level memory hierarchy, comprising an unbounded global memory with high latency and low throughput while the SM local memories have low latency and high throughput.

**Programs.** An *MMM program* is a directed acyclic graph (DAG) whose vertices are kernels and where edges indicate dependencies, similarly to the instruction stream DAGs of the fork-join multithreaded parallelism model [6]. A *kernel* is a SIMD (single instruction multithreaded data) program decomposed into a number of thread-blocks. Each *thread-block* is executed by a single SM and each SM executes a single thread-block at a time. Similarly to a CUDA program, an MMM program specifies for each

<sup>&</sup>lt;sup>1</sup>http://www.nvidia.com/

Figure 3.1: Overview of a many-core machine program

kernel call the number of thread-blocks and the number of threads per thread-block. The different types of components of an MMM program are depicted on Figure 3.1.

Scheduling and synchronization. At run time, an MMM machine schedules threadblocks (from the same or different kernels) onto SMs, based on (1) the dependencies specified by the edges of the DAG and, (2) the hardware resources required by each thread-block. Threads within a thread-block can cooperate with each other via the local memory of the SM running the thread-block. Meanwhile, thread-blocks interact with each other via the global memory. In addition, threads within a thread-block are executed physically in parallel by an SM. Meanwhile, the programmer cannot make any assumptions on the order in which thread-blocks of a given kernel are mapped to the SMs. This restriction allows MMM programs to run correctly on any fixed number of SMs, similarly to a CUDA program.

Memory access policies. All threads of a given thread-block can access simultaneously any memory cell of the local memory or the global memory: read/write conflicts are handled by the CREW (concurrent read and exclusive write) policy. However, read/write requests to the global memory by two different thread-blocks cannot be executed simultaneously. In case of simultaneous request, one thread-block is chosen randomly and served first, then the other thread-block is served.

For the purpose of analyzing program performance, we define two *machine parameters*:

U: Time (expressed in clock cycles) to transfer one machine word between global memory and the local memory of any SM. Thus, 1/U is a throughput.

Z: Size (expressed in machine words) of the local memory of each SM.

To be precise, the throughput 1/U satisfies the following property. If r and w are the number of words respectively read and written to the global memory by one thread of a thread-block B, then the total time  $T_D$  spent in data transfer between the global memory and the local memory of an SM executing B satisfies

$$T_D \le (r+w)U. \tag{3.1}$$

We observe that most phenomena that ease or limit data transfer (coalesced accesses to global memory, local memory bank conflicts, partition camping, etc) have an impact on running time which is proportional to the amount of transferred data. This allows us to claim that the throughput 1/U combines (or unifies) these different phenomena.

Similarly, the local memory size Z unifies in one parameter different characteristics of an SM and, thus, of a thread-block. Indeed, each of the following quantities is necessarily at most equal to Z: the number of cores of an SM, the number of threads of a thread-block, the amount of words in a data transfer between the global memory and the local memory of an SM.

Relation (3.1) calls for another comment. One could expect the introduction of a third machine parameter, say V, such that, if  $\ell$  is the number of *local operations* (arithmetic operations, reads/writes in the local memory) performed by one thread of the thread-block B, then the total time  $T_A$  spent in local operations by an SM executing B would satisfy

$$T_A \le \ell V. \tag{3.2}$$

As a consequence, for the total running time T of the thread-block B, we would have

$$T = T_A + T_D \le \ell V + (r+w)U. \tag{3.3}$$

Instead of introducing this third machine parameter V, we let V = 1, which is equivalent to a change of coordinates.

#### **3.2.2** Many-core machine programs

As specified above, each MMM program  $\mathcal{P}$  is modeled by a directed acyclic graph  $(\mathcal{K}, \mathcal{E})$ , called the *kernel DAG* of  $\mathcal{P}$ , where each node  $K \in \mathcal{K}$  represents a kernel and each edge  $E \in \mathcal{E}$  represents a kernel call which must precede another kernel call. To

be precise, a kernel call can be executed provided that all its predecessors in the DAG  $(\mathcal{K}, \mathcal{E})$  have completed their execution.

Recall that each kernel decomposes into one or more thread-blocks and that all threads within a given kernel execute the same serial program, but with possibly different input data. In addition, all threads within a thread-block are executed physically in parallel by an SM. It follows that MMM kernel code needs no synchronization statement, like CUDA's \_\_\_syncthreads().

This has two consequences. First, each thread in a thread-block is either submitting read/write requests to the global memory or, executing local operations. This justifies Relation (3.3). A second consequence is the fact that the synchronization overheads of an MMM program are included in the scheduling costs of the threadblocks onto the SMs. We shall assume that those latter costs depend linearly on the number of thread-blocks and the sum over all thread-blocks of the amount of data transferred by one thread. Indeed, this second quantity can be used to estimate the size of the code of a thread-block. Therefore, synchronization overheads of an MMM program can be incorporated in the data transfer time. This *key observation* helps understanding the complexity measures introduced in Section 3.2.3.

Since each kernel of the program  $\mathcal{P}$  decomposes into a finite number of threadblocks, we map  $\mathcal{P}$  to a second graph, called the *thread block DAG* of  $\mathcal{P}$ , whose vertex set  $\mathcal{B}(\mathcal{P})$  consists of all thread-blocks of the kernels of  $\mathcal{P}$  and such that  $(B_1, B_2)$  is an edge if  $B_1$  is a thread-block of a kernel preceding the kernel of  $B_2$  in  $\mathcal{P}$ . This second graph is associated two important quantities:

- $N(\mathcal{P})$ : number of vertices in the thread-block DAG of  $\mathcal{P}$ ,

- $L(\mathcal{P})$ : critical path length (that is, the length of the longest path) in the thread-block DAG of  $\mathcal{P}$ .

For the purpose of analyzing program performance, we define five *program param*eters, summarized in Table 3.1.

We also define five algorithm parameters, shown in table 2: n is the input size of a many-core machine program; z is the maximum amount of the local memory per thread-block; q is the number of threads per thread-block; d is the number of thread-blocks needed during a parallel step; and  $\pi$  is the number of parallel steps of a many-core machine program.

| Parameter | Description                             |

|-----------|-----------------------------------------|

| n         | Input size in machine words             |

|           | Maximum number of words of local memory |

|           | allocated per thread-block              |

| q         | The number of threads per thread-block  |

| d         | The maximum number of thread-blocks     |

|           | in a parallel step                      |

| $\pi$     | The number of parallel steps            |

Table 3.1: Algorithm parameters

# 3.2.3 Complexity measures for the many-core machine model