# $\frac{\text{LIGHTWEIGHT AUTHENTICATED ENCRYPTION}}{\text{FOR FPGAS}}$

$\mathbf{b}\mathbf{y}$

Upendarreddy Mamidi A Thesis Submitted to the Graduate Faculty of George Mason University In Partial fulfillment of The Requirements for the Degree of Master of Science Computer Engineering

#### Committee:

|       | Dr. Jens-Peter Kaps, Thesis Director                                                |

|-------|-------------------------------------------------------------------------------------|

|       | Dr. Kris Gaj, Committee Member                                                      |

|       | Dr. Alok Berry, Committee Member                                                    |

|       | Dr. Monson H. Hayes, Chairman, Department<br>of Electrical and Computer Engineering |

|       | Dr. Kenneth S. Ball, Dean,<br>Volgenau School of Engineering                        |

| Date: | Spring Semester 2016<br>George Mason University<br>Fairfax, VA                      |

Lightweight Authenticated Encryption for FPGAs

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science at George Mason University

By

Upendarreddy Mamidi Bachelor of Technology VIT University, India, 2013

Director: Dr. Jens-Peter Kaps, Associate Professor Department of Electrical and Computer Engineering

> Spring Semester 2016 George Mason University Fairfax, VA

Copyright © 2016 by Upendarreddy Mamidi All Rights Reserved

## Dedication

I dedicate this thesis to my parents Siddiram Reddy and Manemma, brother Mahendar and sister Srilatha and beloved friends.

## Acknowledgments

I would like to express my gratitude to my advisor Dr. Jens-Peter Kaps for helping me with useful comments and remarks throughout the course of the thesis. Furthermore I would like to thank Dr. Kris Gaj, Pansayya Yalla and Ekawat Homsirikamol for their continuous support in getting the work done. Finally, I would like to thank Sangamitra without whose help, it would have been difficult to complete the thesis.

## Table of Contents

|      |       |           |                                                                                                             | Page |

|------|-------|-----------|-------------------------------------------------------------------------------------------------------------|------|

| List | of Ta | ables .   |                                                                                                             | viii |

| List | of Fi | igures .  |                                                                                                             | ix   |

| Abs  | tract |           |                                                                                                             | xi   |

| 1    | Intro | oductio   | n                                                                                                           | 0    |

|      | 1.1   | Securit   | ty Services of Cryptography                                                                                 | 0    |

|      |       | 1.1.1     | Confidentiality                                                                                             | 0    |

|      |       | 1.1.2     | Data Integrity                                                                                              | 1    |

|      |       | 1.1.3     | Authentication                                                                                              | 1    |

|      |       | 1.1.4     | Non-repudiation of Message                                                                                  | 1    |

|      | 1.2   | Confid    | entiality-only Modes of Operations of Block Ciphers                                                         | 2    |

|      |       | 1.2.1     | Electronic Code Book (ECB) Mode                                                                             | 2    |

|      |       | 1.2.2     | Cipher Block Chaining<br>(CBC) Mode $\hfill \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 3    |

|      |       | 1.2.3     | Cipher Feedback (CFB) Mode                                                                                  | 4    |

|      |       | 1.2.4     | Output Feedback(OFB) Mode                                                                                   | 5    |

|      |       | 1.2.5     | Counter (CTR) Mode                                                                                          | 6    |

|      | 1.3   | Auther    | ntication Techniques                                                                                        | 7    |

|      |       | 1.3.1     | Cryptographic Hash Functions                                                                                | 7    |

|      |       | 1.3.2     | Message Authentication Code(MAC)                                                                            | 8    |

|      | 1.4   | Auther    | nticated Encryption                                                                                         | 12   |

|      |       | 1.4.1     | What is Authenticated Encryption?                                                                           | 12   |

|      |       | 1.4.2     | Advantages of Authenticated Encryption                                                                      | 13   |

|      |       | 1.4.3     | Composition Schemes                                                                                         | 14   |

| 2    | Clas  | sificatio | on of the CAESAR Candidates                                                                                 | 16   |

|      | 2.1   | Introd    | uction                                                                                                      | 16   |

|      |       | 2.1.1     | Functional Requirements of the CAESAR Competition                                                           | 16   |

|      | 2.2   | Design    | Classification                                                                                              | 17   |

|      |       | 2.2.1     | Type                                                                                                        | 17   |

|      |       | 2.2.2     | Features                                                                                                    | 19   |

| 3    | Desi  | ign Dec   | isions                                                                                                      | 24   |

|   | 3.1  | Candidate Selection                                     |

|---|------|---------------------------------------------------------|

|   | 3.2  | Hardware Interface for Fullwidth Designs 24             |

|   | 3.3  | Lightweight Interface                                   |

|   | 3.4  | Design Methodology                                      |

|   | 3.5  | Functional Verification                                 |

|   | 3.6  | Results Generation                                      |

| 4 | SIL  | C: SImple Lightweight CFB                               |

|   | 4.1  | Introduction                                            |

|   |      | 4.1.1 Features                                          |

|   |      | 4.1.2 Recommended Parameter Set                         |

|   | 4.2  | Encryption and Decryption                               |

|   |      | 4.2.1 Functions Used in SILC 29                         |

|   |      | 4.2.2 Subroutines Used in SILC                          |

|   | 4.3  | Fullwidth Implementation    33                          |

|   |      | 4.3.1 Datapath Design                                   |

|   |      | 4.3.2 Design of Control Logic                           |

|   | 4.4  | Lightweight Implementation                              |

|   |      | 4.4.1 Datapath Design for Lightweight Implementation    |

|   |      | 4.4.2 Design of Controller                              |

| 5 | Jolt | ik                                                      |

|   | 5.1  | Introduction                                            |

|   |      | 5.1.1 Features                                          |

|   | 5.2  | Joltik-BC                                               |

|   |      | 5.2.1 S-box $43$                                        |

|   |      | 5.2.2 MDS Matrix                                        |

|   |      | 5.2.3 Generation of Subtweakeys                         |

|   | 5.3  | Encryption and Decryption                               |

|   |      | 5.3.1 Message Processing                                |

|   | 5.4  | Fullwidth Implementation                                |

|   |      | 5.4.1 Datapath Design                                   |

|   |      | 5.4.2 Design of Control Logic                           |

|   | 5.5  | Lightweight Implementation                              |

|   |      | 5.5.1 Lightweight Joltik-BC                             |

|   |      | 5.5.2 Optimized Datapath for Lightweight Implementation |

|   |      | 5.5.3 Controller Design                                 |

| 6 | AC   | ORN: A Lightweight Authenticated Cipher   58            |

| 0 | 6.1  | Introduction                                            |

|   | 0.1  | 6.1.1 Features                                          |

|   |      | 0.1.1 I GUULIO                                          |

|        | 6.1.2                                                                                                                  | Functions Used in ACORN                                                                                                                                                                                                                                                                    | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.2    | Encry                                                                                                                  | ption and Decryption                                                                                                                                                                                                                                                                       | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 6.2.1                                                                                                                  | The Initialization                                                                                                                                                                                                                                                                         | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 6.2.2                                                                                                                  | Processing the Associated Data                                                                                                                                                                                                                                                             | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 6.2.3                                                                                                                  | The Encryption                                                                                                                                                                                                                                                                             | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 6.2.4                                                                                                                  | The Finalization                                                                                                                                                                                                                                                                           | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 6.2.5                                                                                                                  | Decryption and Verification                                                                                                                                                                                                                                                                | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.3    | Fullwi                                                                                                                 | dth Implementation                                                                                                                                                                                                                                                                         | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 6.3.1                                                                                                                  | Datapath Design                                                                                                                                                                                                                                                                            | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 6.3.2                                                                                                                  | Design of Control Logic                                                                                                                                                                                                                                                                    | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6.4    | Lightv                                                                                                                 | veight Implementation                                                                                                                                                                                                                                                                      | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 6.4.1                                                                                                                  | Datapath Design                                                                                                                                                                                                                                                                            | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 6.4.2                                                                                                                  | Control Logic Design                                                                                                                                                                                                                                                                       | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Perf   | formand                                                                                                                | ce Evaluation                                                                                                                                                                                                                                                                              | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.1    | Our In                                                                                                                 | nplementation Results                                                                                                                                                                                                                                                                      | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 7.1.1                                                                                                                  | Throughput Computations                                                                                                                                                                                                                                                                    | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 7.1.2                                                                                                                  | Resource Utilization                                                                                                                                                                                                                                                                       | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 7.1.3                                                                                                                  | Throughput/Area                                                                                                                                                                                                                                                                            | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.2    | Analys                                                                                                                 | sis of the Results                                                                                                                                                                                                                                                                         | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 7.2.1                                                                                                                  | Area                                                                                                                                                                                                                                                                                       | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 7.2.2                                                                                                                  | Throughput/Area                                                                                                                                                                                                                                                                            | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 7.3    | Comp                                                                                                                   | arison with Other Published Results                                                                                                                                                                                                                                                        | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 7.3.1                                                                                                                  | Fullwidth Designs                                                                                                                                                                                                                                                                          | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | 7.3.2                                                                                                                  | Lightweight Designs                                                                                                                                                                                                                                                                        | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Con    | clusion                                                                                                                |                                                                                                                                                                                                                                                                                            | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.1    | Work                                                                                                                   | Accomplished                                                                                                                                                                                                                                                                               | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8.2    | Ranki                                                                                                                  | ng of Our Implementations                                                                                                                                                                                                                                                                  | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| liogra | aphy .                                                                                                                 |                                                                                                                                                                                                                                                                                            | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | <ul> <li>6.3</li> <li>6.4</li> <li>Perf<br/>7.1</li> <li>7.2</li> <li>7.3</li> <li>Con<br/>8.1</li> <li>8.2</li> </ul> | 6.2 Encry<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.3<br>6.2.4<br>6.2.5<br>6.3 Fullwi<br>6.3.1<br>6.3.2<br>6.4 Lightw<br>6.4.1<br>6.4.2<br>Performano<br>7.1 Our In<br>7.1.1<br>7.1.2<br>7.1.3<br>7.2 Analy<br>7.2.1<br>7.2.2<br>7.3 Comp<br>7.3.1<br>7.3.2<br>Conclusion<br>8.1 Work<br>8.2 Ranki | <ul> <li>6.2 Encryption and Decryption .</li> <li>6.2.1 The Initialization .</li> <li>6.2.2 Processing the Associated Data .</li> <li>6.2.3 The Encryption .</li> <li>6.2.4 The Finalization .</li> <li>6.2.5 Decryption and Verification .</li> <li>6.3 Fullwidth Implementation .</li> <li>6.3.1 Datapath Design .</li> <li>6.3.2 Design of Control Logic .</li> <li>6.4 Lightweight Implementation .</li> <li>6.4.1 Datapath Design .</li> <li>6.4.2 Control Logic Design .</li> <li>6.4.2 Control Logic Design .</li> <li>7.1 Our Implementation Results .</li> <li>7.1.1 Throughput Computations .</li> <li>7.1.2 Resource Utilization .</li> <li>7.2 Analysis of the Results .</li> <li>7.2.1 Area .</li> <li>7.3.1 Fullwidth Designs .</li> <li>7.3.2 Lightweight Designs .</li> <li>Conclusion .</li> <li>8.1 Work Accomplished .</li> </ul> |

## List of Tables

| Table |                                                                  | Page |

|-------|------------------------------------------------------------------|------|

| 2.1   | Classification of CAESAR Round Two candidates                    | . 21 |

| 2.2   | Classification of CAESAR Round One Candidates                    | . 22 |

| 4.1   | Recommended Parameter Set of SILC                                | . 29 |

| 5.1   | S-Box Used in Joltik-BC                                          | . 43 |

| 5.2   | H Permutation in Joltik-BC                                       | . 44 |

| 6.1   | Message and Control Bits in Initialization Process               | . 61 |

| 6.2   | Message and Control Bits for Processing Associated Data          | . 61 |

| 6.3   | Message and Control Bits for Encryption                          | . 62 |

| 6.4   | Message and Control Bits for the Finalization                    | . 62 |

| 7.1   | Notations                                                        | . 71 |

| 7.2   | Throughput formulae for our implementations of CAESAR candidates | . 72 |

| 7.3   | Resource Utilization                                             | . 73 |

| 7.4   | Throughput Results of Our Implementations                        | . 73 |

| 7.5   | Fullwidth Design Implementation Results Comparison               | . 76 |

| 7.6   | Lightweight Design Implementation Results Comparison             | . 77 |

## List of Figures

| Figure | ]                                             | Page |

|--------|-----------------------------------------------|------|

| 1.1    | Confidentiality                               | 0    |

| 1.2    | Integrity                                     | 1    |

| 1.3    | Authentication                                | 1    |

| 1.4    | ECB Encryption                                | 3    |

| 1.5    | ECB Decryption                                | 3    |

| 1.6    | CBC Encryption                                | 4    |

| 1.7    | CBC Decryption                                | 4    |

| 1.8    | CFB Encryption                                | 5    |

| 1.9    | CFB Decryption                                | 5    |

| 1.10   | OFB Encryption                                | 6    |

| 1.11   | OFB Decryption                                | 6    |

| 1.12   | CTR Encryption                                | 7    |

| 1.13   | CTR Decryption                                | 7    |

| 1.14   | Operation of a Hash Function                  | 8    |

| 1.15   | Operation of a MAC Function                   | 9    |

| 1.16   | Operation of a HMAC Function                  | 10   |

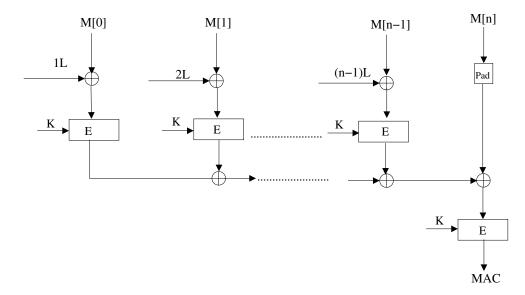

| 1.17   | Operation of the CBC-MAC Algorithm            | 11   |

| 1.18   | Operation of the PMAC Algorithm               | 12   |

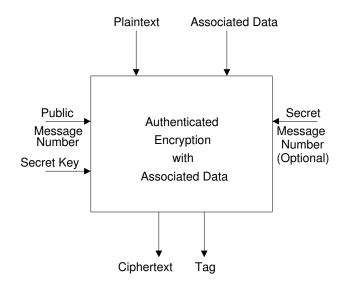

| 1.19   | Authenticated Encryption with Associated Data | 13   |

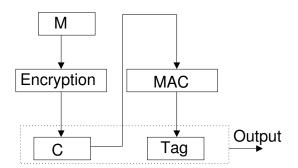

| 1.20   | Operation of EtM                              | 14   |

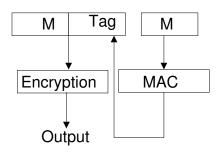

| 1.21   | Operation of MtE                              | 15   |

| 1.22   | Operation of E&M                              | 15   |

| 2.1    | Block Cipher                                  | 17   |

| 2.2    | Stream Cipher                                 | 18   |

| 2.3    | Tweakable Block Cipher                        | 18   |

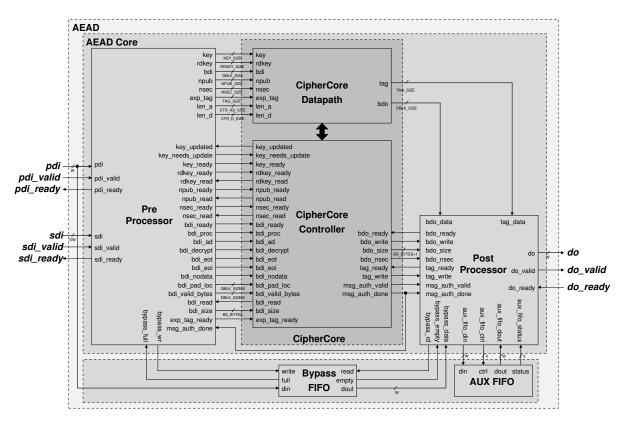

| 3.1    | Hardware Interface for Fullwidth Designs      | 25   |

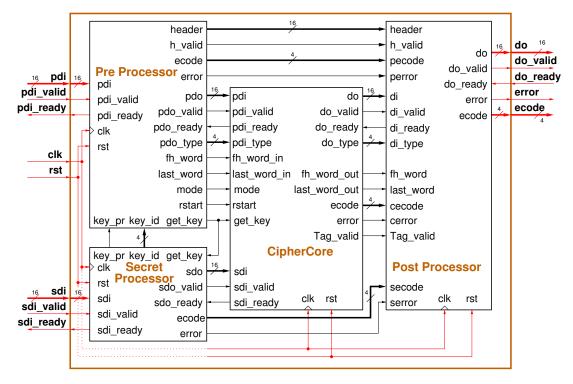

| 3.2    | Hardware Interface for Lightweight Designs    | 26   |

| 4.1    | HASH Function                                 | 30   |

| 4.2    | PRF Function                                  | 31   |

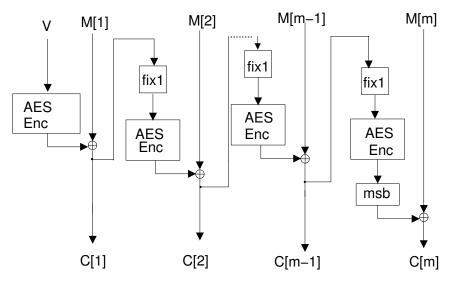

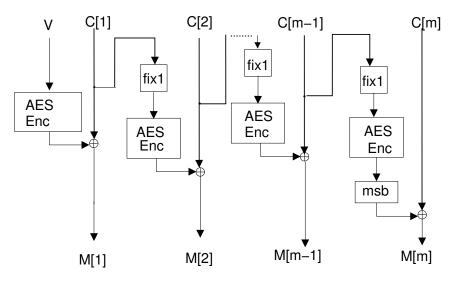

| 4.3  | ENC Function                                             | 32 |

|------|----------------------------------------------------------|----|

| 4.4  | DEC Function                                             | 33 |

| 4.5  | Datapath Design of SILC                                  | 34 |

| 4.6  | Toplevel State Machine of SILC                           | 36 |

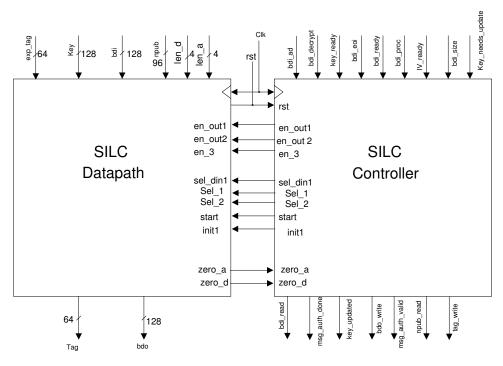

| 4.7  | Toplevel Structure of SILC                               | 37 |

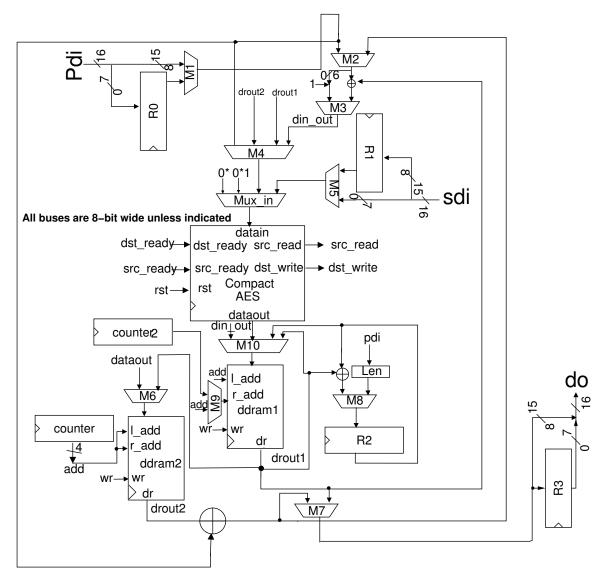

| 4.8  | Lightweight Design of SILC                               | 39 |

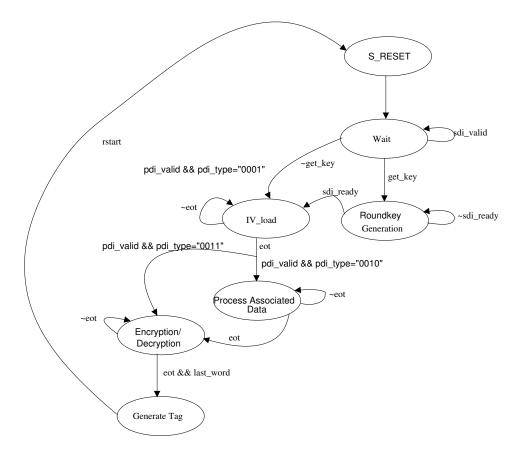

| 4.9  | Toplevel State Machine of Our Lightweight Design of SILC | 40 |

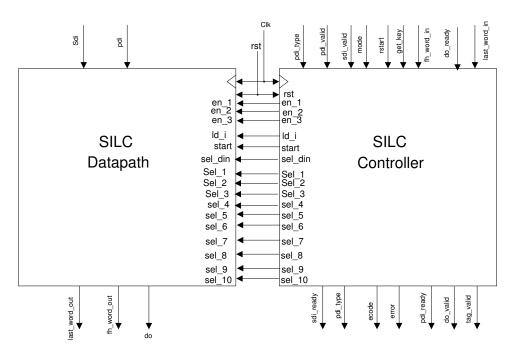

| 4.10 | Toplevel Structure of Our SILC Lightweight Design        | 41 |

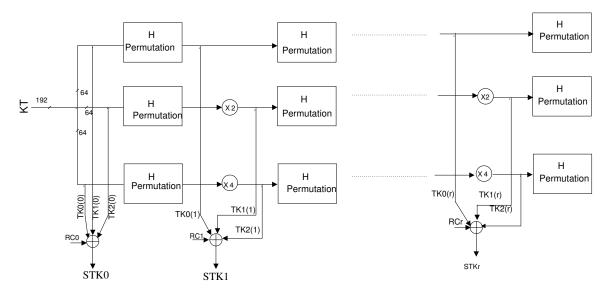

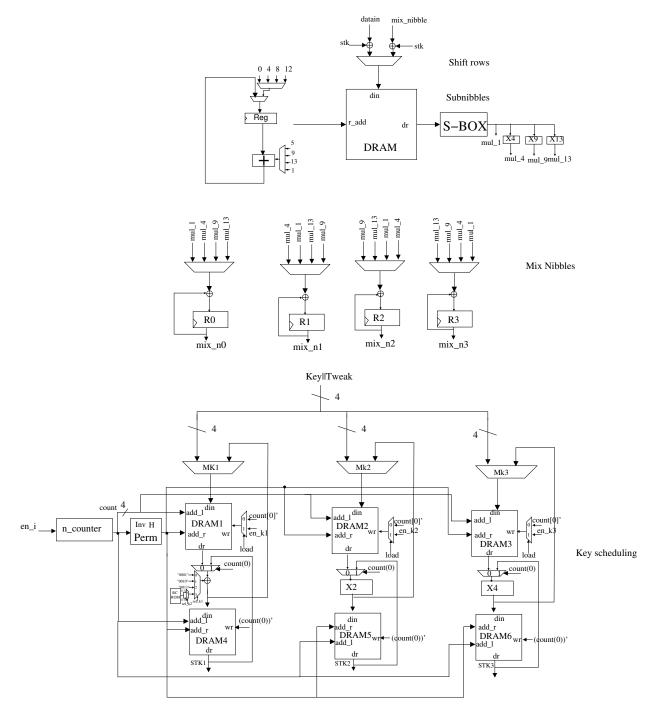

| 5.1  | Key Scheduling Algorithm of Joltik-BC 192                | 44 |

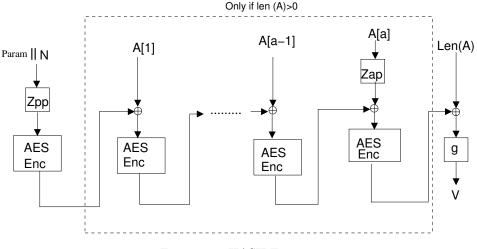

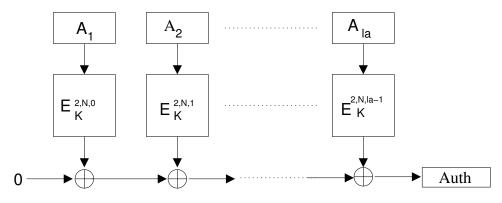

| 5.2  | Associated Data Processing Without Padding               | 45 |

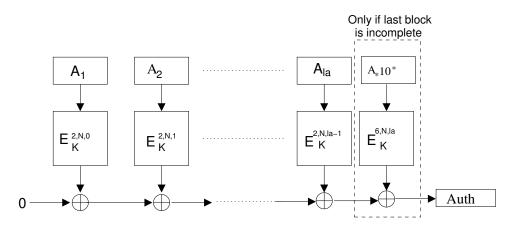

| 5.3  | Associated Data Processing with Padding                  | 46 |

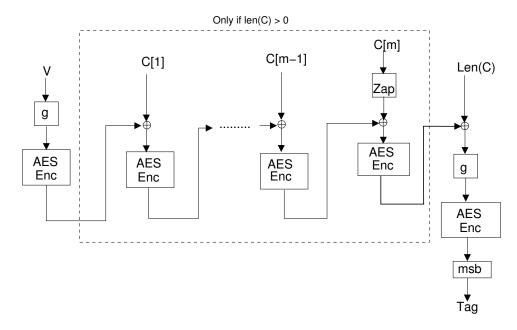

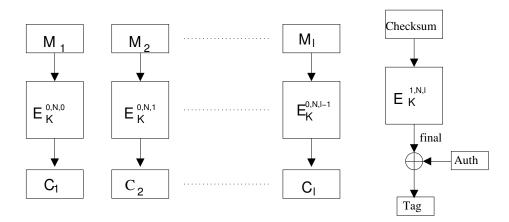

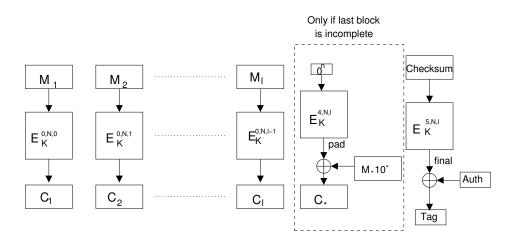

| 5.4  | Message Processing Without Padding in Joltik             | 47 |

| 5.5  | Message Processing With Padding in Joltik                | 47 |

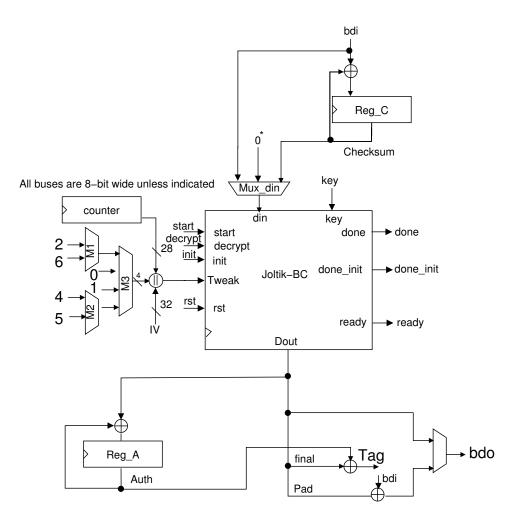

| 5.6  | Datapath Design of Joltik                                | 49 |

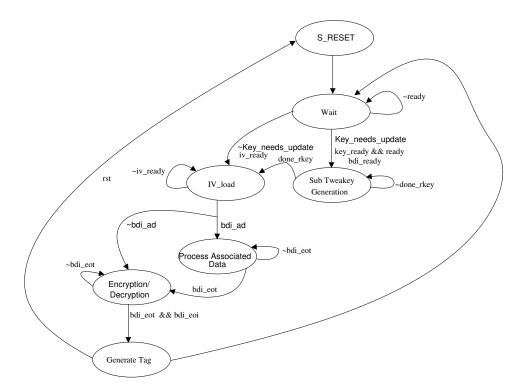

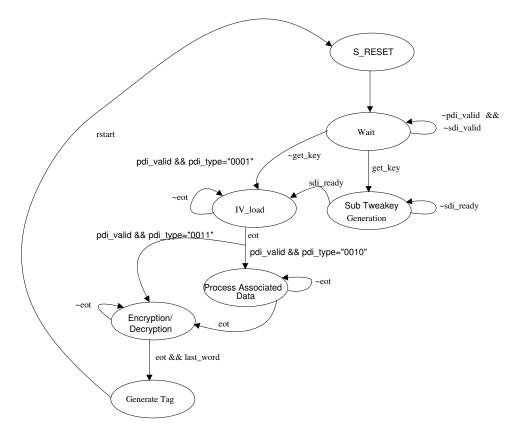

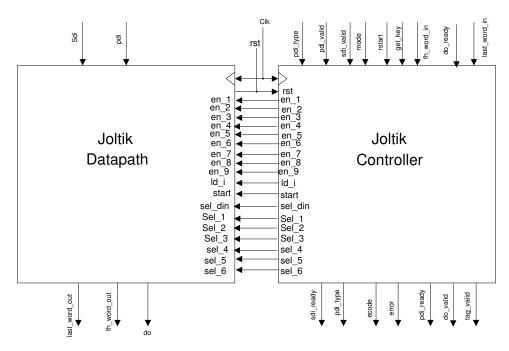

| 5.7  | Toplevel State Machine of Joltik                         | 50 |

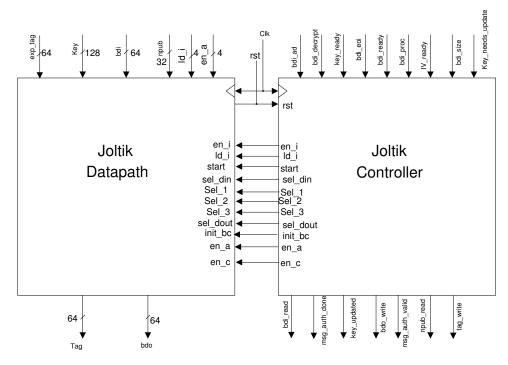

| 5.8  | Toplevel Diagram of Joltik                               | 51 |

| 5.9  | Optimized Datapath Design of Joltik-BC                   | 53 |

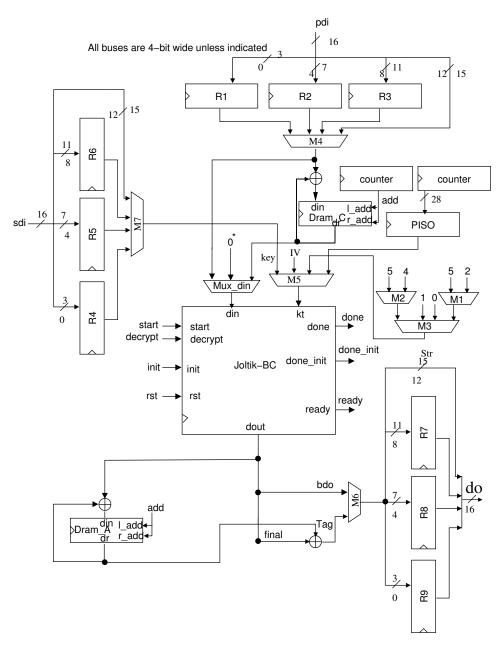

| 5.10 | Lightweight Datapath Design of Joltik                    | 55 |

| 5.11 | Toplevel State Machine of Our Lightweight Joltik Design  | 56 |

| 5.12 | Toplevel Structure of Joltik                             | 57 |

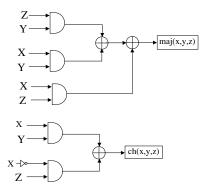

| 6.1  | Boolean Functions of ACORN                               | 58 |

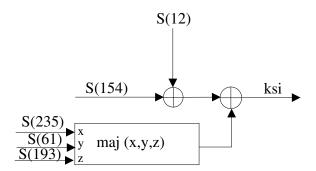

| 6.2  | KSG function                                             | 59 |

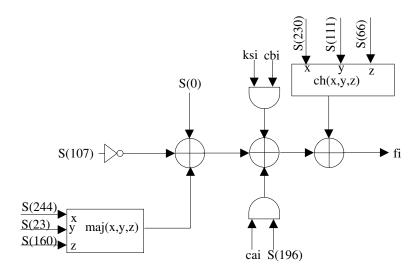

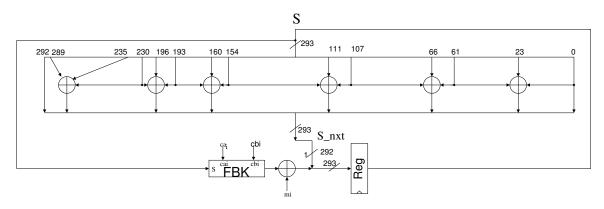

| 6.3  | FBK Function                                             | 59 |

| 6.4  |                                                          | 60 |

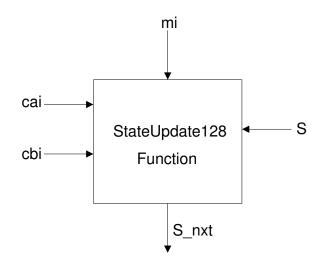

| 6.5  | State Update Function                                    | 60 |

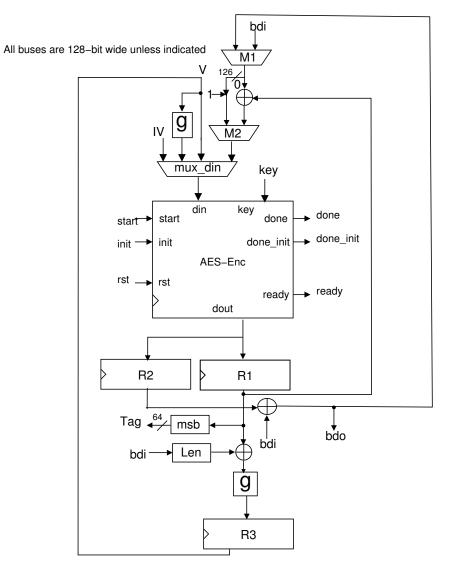

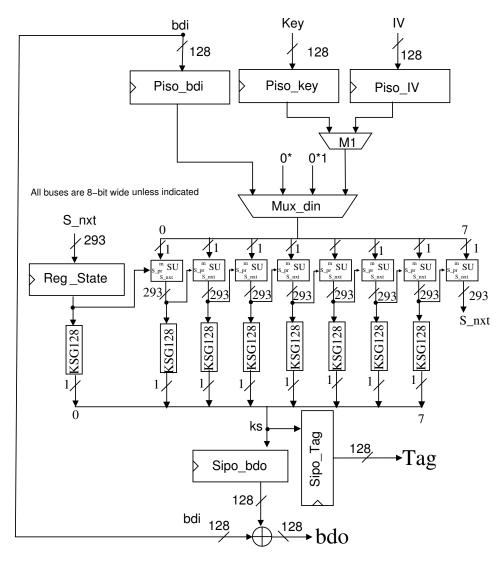

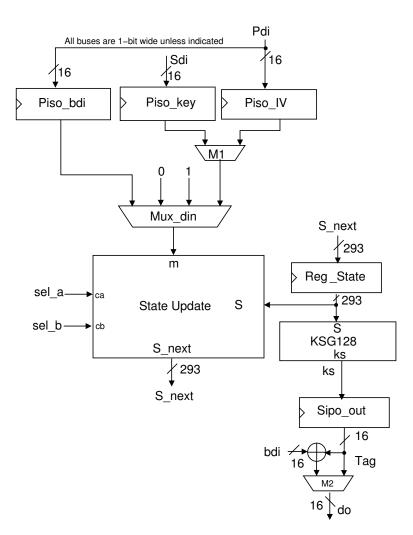

| 6.6  | Datapath Design of ACORN                                 | 64 |

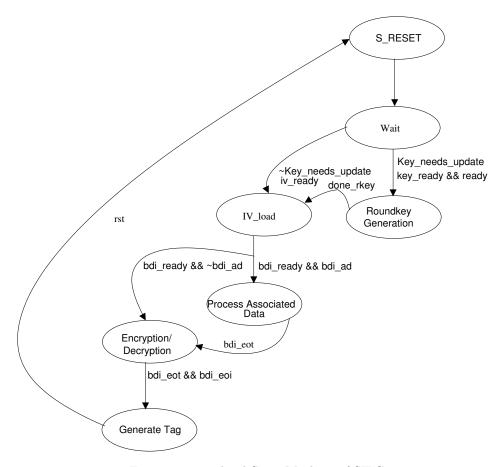

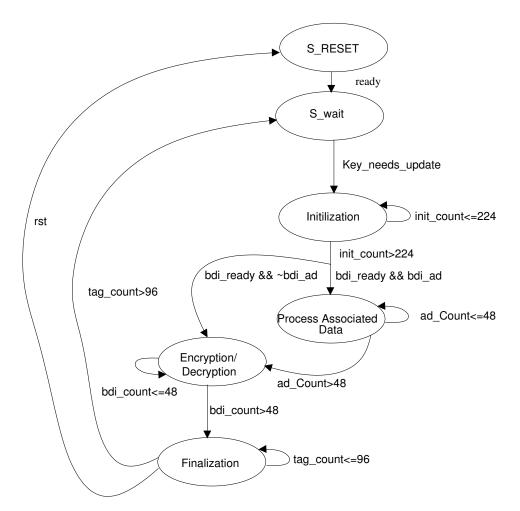

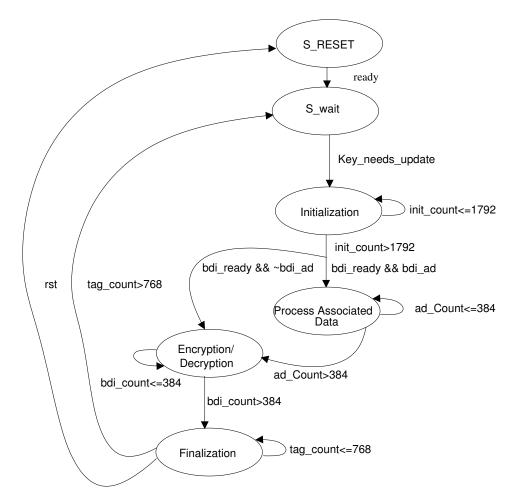

| 6.7  | Toplevel State Machine of ACORN    6                     | 66 |

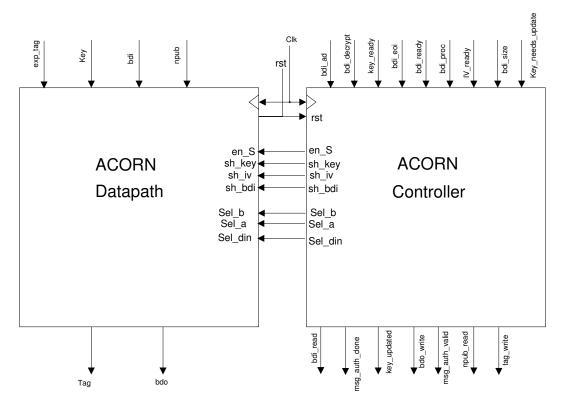

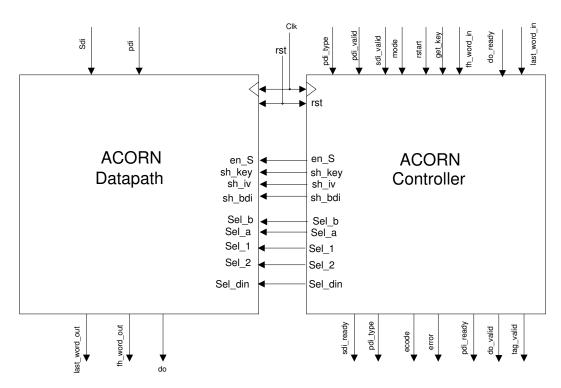

| 6.8  | Toplevel Design of ACORN    6                            | 67 |

| 6.9  | Light-Weight Datapath Design of ACORN                    | 68 |

| 6.10 | Toplevel State Machine of our ACORN Lightweight Design   | 69 |

| 6.11 | Toplevel Structure of ACORN our Lightweight Design       | 70 |

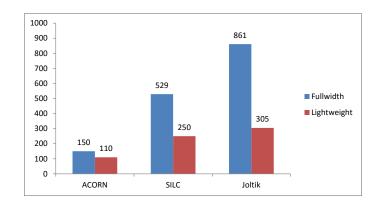

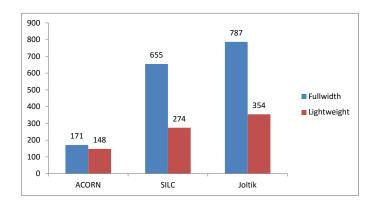

| 7.1  | Comparison of Slices                                     | 74 |

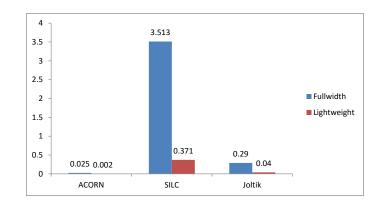

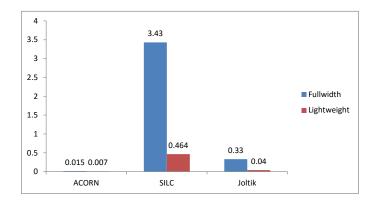

| 7.2  | Comparison of Throuhput/Area                             | 75 |

### Abstract

#### LIGHTWEIGHT AUTHENTICATED ENCRYPTION FOR FPGAS

Upendarreddy Mamidi, M.S.

George Mason University, 2016

Thesis Director: Dr. Jens-Peter Kaps

Traditionally, authenticated encryption was achieved by using two seperate algorithms for encryption and authentication. Recently, modes that combine encryption and authentication together are being proposed. This feature is especially beneficial in case of hardware implementations, as it allows for a substantial decrease in the circuit area and power compared to traditional schemes.

In this thesis, we first characterize candidates of the Competition for Authenticated Encryption: Security, Applicability, and Robustness (CAESAR). Then we discuss light-weight candidates from the round 1 submissions namely ACORN, SILC (SImple Lightweight CFB) and Joltik. We first implement the full width designs of these candidates targeting Xilinx Spartan-6 and Artix-7 FPGAs. Later, we optimize these designs for low-area applications. Lastly, we compare the results of the implementations with other published results.

## Chapter 1: Introduction

In this chapter we first discuss the basic security objectives of any cryptographic system and then the methods that assure the security objectives. Later, we introduce the topic of Authenticated Encryption and it's advantages over traditional schemes.

## 1.1 Security Services of Cryptography

There are four security objectives of cryptography that form the structure of security services, namely

- 1. Confidentiality.

- 2. Data Integrity.

- 3. Authentication.

- 4. Non-repudiation of Message.

#### 1.1.1 Confidentiality

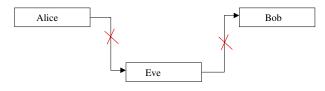

This is a service that protects the data from unauthorized disclosure. In simpler words, confidentiality is said to be ensured if and only if the sender and receiver of the message can get access to it. Figure 1.1 shows the confidentiality service. Confidentiality ensures that Eve, who is not a part of the communication and is unauthorized will not get access to the message that is sent by Alice to Bob.

Figure 1.1: Confidentiality

#### 1.1.2 Data Integrity

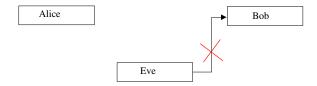

Data integrity can be defined as an assurance that the data received is unaltered or unchanged during transmission. Data modifications include insertion of bits, deletion of bits or substitutions. Figure 1.2 shows the integrity service. Integrity ensures that Bob detects the modification of data done by Eve, who is an unauthorized person.

Figure 1.2: Integrity

#### 1.1.3 Authentication

Authentication is a process of verifying the identity of a user who wishes to access the information, this type of authentication is called as peer-entity authentication. Another type of authentication is data origin authentication which ensures that the data is originally coming from the actual sender and not from any third party. Figure 1.3 shows the authentication service. Authentication guarantees for Bob that the message is originated from Alice who claims to be the author.

Figure 1.3: Authentication

#### 1.1.4 Non-repudiation of Message

Non-repudiation of a message is a service which prevents both communicating parties from denying sending or receiving the message. Digital signature technique is one way assuring Non-repudiation of a message.

In practice we often need both confidentiality and authentication for example, medical information sent my doctors has to be both confidential and authentic. Traditionally these two services are achieved using separate algorithms. Confidentiality is provided by encryption, various confidentiality-only modes of operations are explained in section 1.2. Authentication can be provided by message authentication codes (MACs). These authentication techniques are covered in section 1.3

## 1.2 Confidentiality-only Modes of Operations of Block Ciphers

A mode of operation of a block cipher is an algorithm that uses symmetric key block cipher algorithm to provide a cryptographic service such as confidentiality or authentication. This section covers the basic modes of operation provide only confidentiality

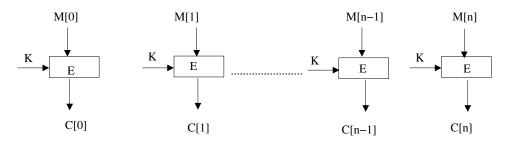

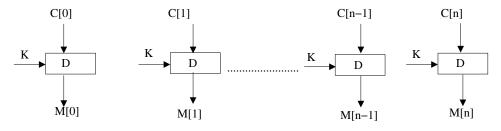

#### 1.2.1 Electronic Code Book (ECB) Mode

ECB is the most basic mode of operation. The input message is broken into blocks of length equal to the block size of the cipher. Each block is encrypted separately. In the same way at the receiver side the ciphertext is broken into blocks with block size length and each block of ciphertext is decrypted separately. Figures 1.4, 1.5 explain the operation of ECB encryption and Decryption respectively. The disadvantage of ECB mode is that it produces identical ciphertext blocks for identical input blocks and that the block cipher needs encryption and decryption modes.

Figure 1.4: ECB Encryption

Figure 1.5: ECB Decryption

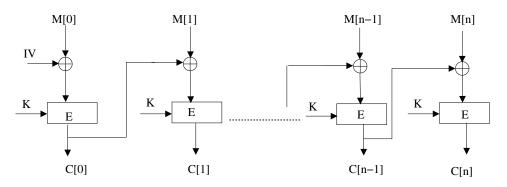

#### 1.2.2 Cipher Block Chaining(CBC) Mode

Each subsequent plaintext block is XORed with the previous ciphertext block. In order to make each message unique the first block of plaintext is XORed with an Initilization Vector(IV). At the receiver side, the plain text is obtained by decrypting the ciphertext and XORing it with IV for the first block of ciphertext and with previous plaintext for all subsequent ciphertexts. The main drawback of CBC is that it cannot be parallelized and needs a block cipher that can encrypt and decrypt. Figures 1.6, 1.7 explain the operation of CBC encryption and decryption respectively.

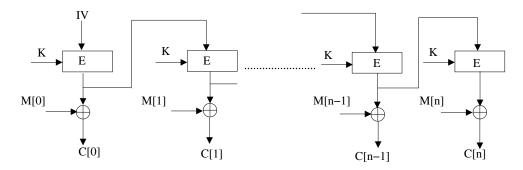

Figure 1.6: CBC Encryption

Figure 1.7: CBC Decryption

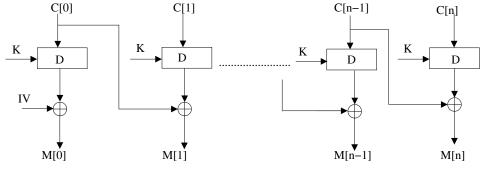

#### 1.2.3 Cipher Feedback (CFB) Mode

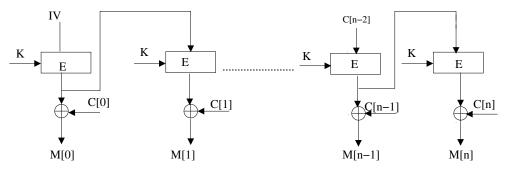

In CipherFeedback mode(CFB) the first block of ciphertext is obtained by encrypting an Initilization Vector (IV) and XORing it with a plaintext block. The resulting ciphertext block is supplied as the feedback for generating next block of ciphertext. CFB mode is inverse free which means that, an encryption algorithm alone is sufficient for both encryption and decryption. The advantage of CFB is that it doesn't need any padding. CFB is self-synchronizing which means that loss in a part of ciphertext will only affect a part of plaintext. Figures 1.8, 1.9 explain the operation of CFB encryption and decryption respectively.

Figure 1.8: CFB Encryption

Figure 1.9: CFB Decryption

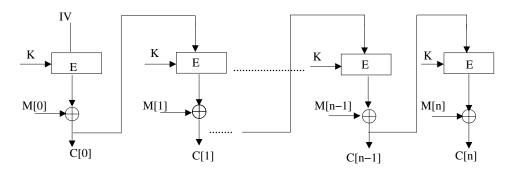

#### 1.2.4 Output Feedback(OFB) Mode

Operation of OFB is similar to that of CFB, however unlike CFB the feedback in OFB is the output of the encryption function. In OFB, every operation depends on previous operations there by it cannnot be parallized. OFB is inverse free, meaning both encryption and decryption operations can be performed using encryption algorithm alone. Figures 1.10,1.11 explain the operation OFB encryption and decryption respectively.

Figure 1.10: OFB Encryption

Figure 1.11: OFB Decryption

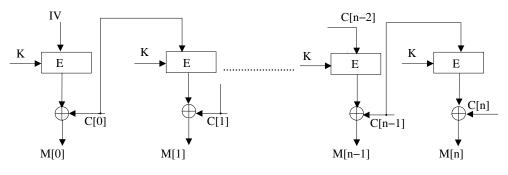

#### 1.2.5 Counter (CTR) Mode

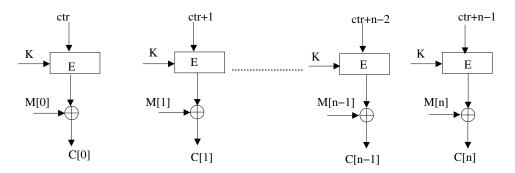

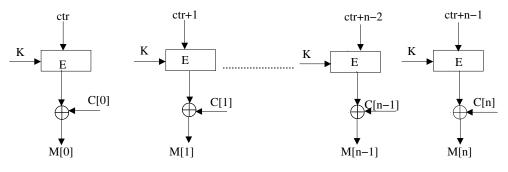

The inputs to an encryption function in CTR mode are a plaintext(M), key(K) and a counter (ctr) where ctr is an n-bit string. First, the ctr is encrypted and then the plaintext is XORed with the encrypted value to get the first block of ciphertext (C). Then ctr is incremented for generating the subsequent ciphertext blocks. The decryption is similar to encryption with M replaced by C. Figures 1.12,1.13 explain the operation of CTR encryption and decryption respectively.

Figure 1.12: CTR Encryption

Figure 1.13: CTR Decryption

## **1.3** Authentication Techniques

As explained earlier in 1.1.3, the purpose authentication is to ensure that the data comes from the person who claims to be the sender. This section covers a detailed explanation of authentication techniques.

#### 1.3.1 Cryptographic Hash Functions

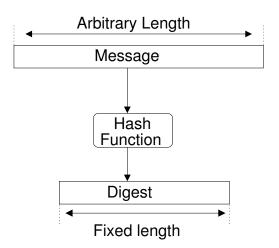

A hash function is basically a transformation that takes a variable size input and returns it's hash value, which is a fixed length string. Hash functions are used as components for MACs. The input to any hash function is called as message and the output is called as message digest. The length of the message is arbitrary but the length of the output is fixed. Figure 1.14 explain the operation of a hash function.

Figure 1.14: Operation of a Hash Function

The basic requirements of a hash function are as listed below.

- It is a one-way function.

- It must be easily computable.

- The output must be of fixed length.

### 1.3.2 Message Authentication Code(MAC)

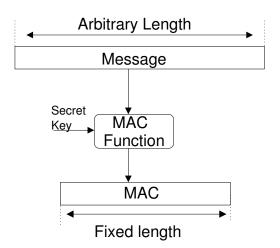

MAC is basically a function which takes a secret key and a message of arbitrary length as input and gives out a unique fixed length MAC as output. MACs help to assure the message's origin(authentication) and also detect any changes in the message(integrity). Operation of MAC is similar to that of a hash. Figure 1.15 explain the operation of a MAC algorithm

Figure 1.15: Operation of a MAC Function

The basic requirements of a MAC are as listed below

- It should contain a key.

- Fixed length output.

- It must be computationally easy.

The security requirement of a MAC algorithm is that it must be computationally infeasible to calculate m' and MAC(m) with m and MAC(m) given such that m', m are different.

#### **Construction of MACs**

A MAC can be built from a hash function or a block cipher. Based on the way they are built there are two types of MACs

- 1. Hash function based MACs.

- 2. Block cipher based MACs.

#### Hash Function Based MACs

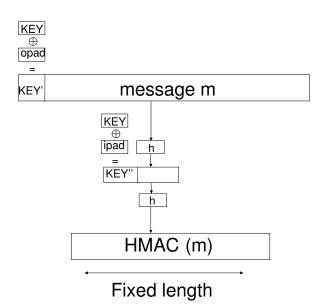

A hash function based MAC is a function that is constructed with a combination of cryptographic hash function and a secret key (K). It takes a message (m) of arbitrary length and a secret key as inputs and return the fixed length MAC as output. Figure 1.16 explain the operation of a HMAC function. Given a cryptographic hash function H, opad is the outer padding, ipad is the inner padding and | denotes concantenation then the definition of HMAC is

$HMAC(K,m) = H((K \text{ xor opad}) | H ((K \oplus ipad)|m)).$

Figure 1.16: Operation of a HMAC Function

#### Goals of HMAC

The goals of HMAC are listed below:

- The underlying hash function must be easily replaced with the latest and secure hash function.

- Use the hash functions that are readily available without any modifications.

#### **Block Cipher Based MACs**

A message authentication code can also be built using a block cipher as the underlying primitive.

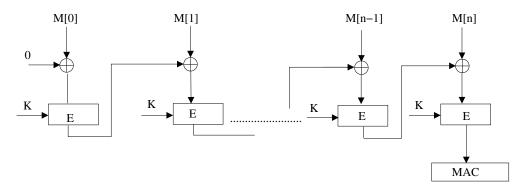

1. Cipher Block Chaining Message Authentication Code (CBC-MAC)

Figure 1.17: Operation of the CBC-MAC Algorithm

#### **Operation of CBC-MAC**

The MAC of the message is calculated by encrypting the message using a block cipher in CBC mode with an initialization vector of all zeros. The output of the first encryption is XORed with the next message block. This kind of structure ensures that a change in any bit of the plaintext will cause change in the final output. In CBC-MAC the length of the message has to be a multiple of n where n is the block size of the underlying block cipher. Figure 1.17 explain the operation of CBC-MAC.

#### 2. Parallelizable Message Authentication Code(PMAC)

Figure 1.18: Operation of the PMAC Algorithm

#### **Operation of PMAC**

The inputs to the PMAC algorithm are a key (K) with k bits length, message (M) of length n bits. It uses three operations which are addition, multiplication and final. L is calculated by encrypting a string of zeros of length n and adding the output with a string of all zeros and least significant bit fixed to zero and final (L) is 1's compliment of L. Each block of message is added with iL for  $i \ge 1$ . The operation of PMAC is illustrated in the figure 1.18

### **1.4** Authenticated Encryption

This section introduces the topic of Authenticated Encryption and focuses on it's advantages and different composition schemes.

#### 1.4.1 What is Authenticated Encryption?

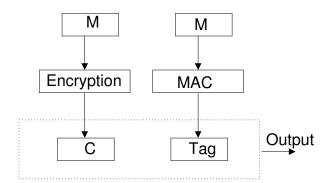

Authenticated encryption (AE) is primarily a combination of authentication and encryption that provides both privacy and authenticity of the data that is encapsulated. Any scheme that provides authenticated encryption takes the input plaintext (m), and key (K) and provides ciphertext (C) and a tag (T) as output. Tag is considered as a checksum of the message and is used to check whether the correct ciphertext is received. Another class of AE schemes is authenticated encryption with associated data (AEAD) which supports both data that needs encryption along with authentication and data that only needs authentication. Figure 1.19 shows the basic block of an AEAD algorithm.

Figure 1.19: Authenticated Encryption with Associated Data

#### 1.4.2 Advantages of Authenticated Encryption

Combining authentication and encryption into one single algorithm in hardware might possibly provide the advantages listed below.

- Area requirement could be smaller for a single algorithm there by reducing the cost.

- Designs with smaller area requirement consume less power there by it is a good solution for low-power applications.

- A combined algorithm needs only a single key and so has a slight advantage in the issues of key management and key storage.

#### 1.4.3 Composition Schemes

Any AE scheme is basically a combination of an encryption algorithm and an authentication algorithm. There are three types of composition schemes for achieving authenticated encryption and they differ in the way these two algorithms are combined.

#### 1. Encrypt-then-MAC(EtM)

In this scheme a message is first encrypted and the tag is calculated by taking the MAC over the obtained ciphertext. And on the receiver's side first the tag gets verified and if it matches decryption will take place to get the plaintext. Figure 1.20 shows the operation of EtM composition scheme.

Figure 1.20: Operation of EtM

#### 2. MAC-then-Encrypt(MtE)

In this scheme first the tag is calculated by taking the MAC over the message. The obtained is tag is then appended to the message and tjhe resultant is ecncrypted to generate the ciphertext. And on the receiver's side first decryption will takes place to get plaintext and tag pair and then verifies the tag. Figure 1.21 shows the operation of MtE composition scheme.

Figure 1.21: Operation of MtE

#### 3. Encrypt-and-MAC (E&M)

The message is encrypted to get the ciphertext and the tag is also calculated on the original message. And on the receiver's side first decryption takes place to get the plaintext and then verifies the tag. Figure 1.22 shows the operation of E&M composition scheme.

Figure 1.22: Operation of E&M

## Chapter 2: Classification of the CAESAR Candidates

In this chapter we first discuss CAESAR (Competition for Authenticated Encryption: Security, Applicability, and Robustness) and it's requirements. Later, we characterize all submissions under certain features.

## 2.1 Introduction

CAESAR has called for submissions of authenticated ciphers on 2/1/2014. The interest of the competition mainly lies in finding a cipher that has advantages over AES-GCM and is suitable for a very wide range of applications. The competition has certain requirements that every submission must comply with.

#### 2.1.1 Functional Requirements of the CAESAR Competition

The requirements of CAESAR competition are listed [2]:

- The cipher must provide both integrity and confidentiality to Plaintext and Secret message number and also integrity to Associated data and Public message number i.e., the cipher must be Authenticated Encryption with Associated Data(AEAD), which is a special case of Authenticated Ciphers.

- Ciphers must not leak any information other than the length of plain text via the length of cipher text.

- The submission must clearly specify the recommended parameters. The number of recommendations must not exceed 10.

- It must be possible to recover the plaintext and the secret message number from the ciphertext, associated data, public message number, and key.

### 2.2 Design Classification

The Round 1 submissions include a variety of designs. The characteristics of the candidates are discussed in this section.

#### 2.2.1 Type

An Authenticated Cipher can be based on Block Ciphers, Tweakable Block ciphers, Stream Ciphers or Permutations. Some submissions are a combination of two or more types.

#### **Block Cipher**

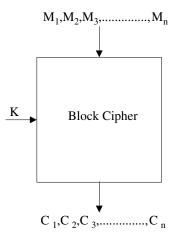

A block cipher is one of the methods of encrypting a plain text to produce the corresponding cipher text in which the key and algorithm are applied block wise rather than to single bit at a time. The block cipher takes key K and plaintext M as input and returns ciphertext C as the output. Figure 2.1 shows how a block cipher works.

Figure 2.1: Block Cipher

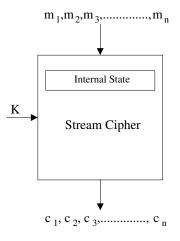

#### Stream Cipher

In a stream cipher a sequence of plaintext digits m is encrypted into a sequence of ciphertext c digits. Unlike block ciphers, the key K and algorithm are applied bit wise. Figure 2.2 shows how a stream cipher works.

Figure 2.2: Stream Cipher

#### **Permutation Based**

Few candidates of CAESAR uses a fixed length permutation as their underlying structure.

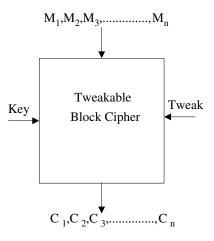

#### **Tweakable Block Cipher**

Tweak is formed by concatenating public parameters, block counters and some cipher dependent parameters, for example a string of bits. Tweak is often used to generate tweakey (formed by concatenating tweak with key), which is used for encryption. Figure 2.3 shows how a tweakable block cipher works.

Figure 2.3: Tweakable Block Cipher

#### 2.2.2 Features

- 1. An AE scheme can be called as *parallelizable* if they are not sequential and can offer a possibility for parallelizing the computations between distinct block cipher calls. In an AE scheme either the encryption, the decryption or both can be parallelizable.

- Parallelizable Encryption In any AE scheme, if processing of the  $i^{th}$  plaintext block doesn't depend on  $j^{th}$  plaintext block for  $i \neq j$  then the encryption of that particular AE scheme is parallelizable.

- Parallelizable Decryption In any AE scheme, if processing of the i <sup>th</sup> cipher text block doesn't depend on j<sup>th</sup> cipher text block for i ≠ j then the decryption of that particular AE scheme is parallelizable.

- Online: A cipher is called online if the encryption of *i*-th input block M<sub>i</sub> depends only on the previous blocks M<sub>1</sub>, ..., M<sub>i-1</sub> [4].

- 3. **Inverse free**: If an AE scheme only requires either encryption or decryption then it can be called as an Inverse free AE scheme. Inverse free schemes requires low memory and area.

- Masking: Some of the block cipher based AE schemes mask the inputs and output for additional security. There are three types of masking methods that are adopted by the AE schemes.

- AX: Addition and XOR arbitrary input.

- Doubling: Inputs and outputs are XORed with a variable which is key dependent and is incremented by doubling in Galois Field.

- Galois-Field Multiplication (GFM): Inputs and outputs are multiplied in Galois-Field with a variable that depends on the key.

- 5. **Passes**: The AE schemes can be classified into one pass and two pass depending on the way they treat the data:

**One-pass**: One pass mode executes encryption and authentication at the same time. **Two-pass**: Two-pass mode executes one algorithm first and then executes another.

- 6. Tag Verification type: There are two options to verify a tag, it can be done before the decryption or after the decryption is done. The verification type depends on the composition scheme they follow and there are three different composition schemes

- Encrypt-then-MAC (EtM) As discussed in 1 the tag is verified before the decryption if the tag doesn't match, the decryption will not take place.

- MAC-then-Encrypt (MtE) and Encrypt-and-MAC (EM) As discussed in 2.3 the tag is verified after the decryption is done.

Table 2.1 shows the classification of CAESAR Round 2 candidates and table 2.2 shows the Round1 candidates that did not advance to Round 2.

| Candidate                 | Type Primitive               | Modified                |          |             |             | Parameters       | ers         |           |                                         |                              | Ē      | Features   |             |        |              |

|---------------------------|------------------------------|-------------------------|----------|-------------|-------------|------------------|-------------|-----------|-----------------------------------------|------------------------------|--------|------------|-------------|--------|--------------|

|                           |                              |                         | gnistalv | 9ziZ 3cT    | Size Yey    | Block/State Size | əziS NMA    | əziS broW | əziz M\QA xsM                           | Rounds<br>Parallelizable E/D |        | C\A sulino | Inversefree | Passes | Verification |

| ACORN v1v2[50]            | SC LFSR                      | bit based FSR           | 1        | 128 1       | 128         | 1/293            | 128         |           | $<\!2^{64}/<2^{64}$                     | 10 •                         | - •/•  | -/-        | •           | 2      | MtE          |

| AEGIS v1[24]              | BC AES                       | last round not used     | 1        | 128 1       | 128         | 128              | 128         | 128       | $\leq 2^{64} / \leq 2^{64}$             | •`<br>6                      | •      | -          | •           | 2      | MtE          |

| AES-COPA v1v2[7]          | BC AES                       |                         | D 64     | 64 32 16 1  | 128         | 128              | 128         |           | V/V                                     | •                            | - •/•  | •/•        | •           | 2      | MtE          |

| AES-JAMBU v1v2[25]        | BC AES, JAMBU                |                         | U        | 64 1        | 128         | 128              | 64          |           | $<\!2^{64}/<2^{64}$                     | 1                            | -/-    | -          | •           | 2      | MtE          |

| AES-OTR v1v2[39]          | BC AES                       |                         | D        | 96 1        | 128         | 128              | 96          |           | $\leq 2^{64} / \leq 2^{64}$             | 0                            | - 0/0  | •          | •           | 1      | EM           |

| AEZv1v3v4[22]             | BC AES                       | key scheduling          | 1        | 128 1       | 128         | 128              | 96          |           | V/V                                     | ·                            | •      | -          | •           | 2      | MtE          |

| ASCON v1v1.1 [17]         | P Monkey Duplex              | own permutation         | 1        | 128 1       | 128         | 64/320           | 128         | 64        | $<\!2^{64}/<~2^{64}$                    | 20 -                         |        | •          | •           | 2      | MtE          |

| CLOC v1v2 [27]            | BC AES                       |                         | Ũ        | 64 1        | 128         | 128              | 96          | œ         | V/V                                     | ı^                           | J      | •          | •           | 2      | EtM          |

| CLOC v1v2 [27]            | BC TWINE                     |                         |          | 32 8        | 80          | 64               | 48          | ×         | V/V                                     | ı`                           | •<br>J | •          | •           | 2      | EtM          |

| Deoxys v1v1.3 [30]        | TBC Deoxys-BC                | Round tweakey operation | 1        | 128 128     | 128 256     | 128              | 64          | 128       | V/V                                     | 14 •                         |        | -/-        | 1           | 2      | MtE          |

| ELmD v1 v2.0 [16]         | BC AES                       | Encrypt-mix-Encrypt     | D 1      | 128 1       | 128         | 128              | 64          |           | $\leq 2^{64} / \leq 2^{64}$             | 12 •                         | •      | •          | •           | 2      | MtE          |

| HS1-SIV v1v2 [35]         | HS1 PRF                      |                         | -        | 128 2       | 256         | 256              | 96          | 32        | V/V                                     | 20                           | •      | -/-        | •           | 2      | MtE          |

| ICEPOLE v1v2 [40]         | P Sponge                     | own permutation         | 1        | 128 1       | 128         | 1280             | 128         | 64        |                                         | 12 •                         | •      | •          | •           | 2      | MtE          |

| Joltik v1v1.3 [31]        | TBC Joltik-BC                |                         | 0        | 64 1        | 128         | 64               | 32          | 4         | V/V                                     | 24 •/                        | •      | •          | 1           | 2      | MtE          |

| Ketje JR v1 [9]           | P KECCAK-p[200]              | variable tag length     | 1        | 128 <       | $\leq 182$  | 16/200           | 128         |           | V/V                                     | 12 -                         | J      | •          | •           | 2      | MtE          |

| Ketje SR v1 [9]           | P KECCAK-p[400]              | variable tag length     | 0.       | 96          | ≤382        | 32/400           | 80          |           | V/V                                     | 12 -                         | J      | ÷          | •           | 2      | MtE          |