# Portland State University PDXScholar

Dissertations and Theses

Dissertations and Theses

1-1-2010

# An Automata-Theoretic Approach to Hardware/Software Coverification

Juncao Li Portland State University

# Let us know how access to this document benefits you.

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds

#### **Recommended** Citation

Li, Juncao, "An Automata-Theoretic Approach to Hardware/Software Co-verification" (2010). Dissertations and Theses. Paper 12.

10.15760/etd.12

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. For more information, please contact pdxscholar@pdx.edu.

An Automata-Theoretic Approach to

Hardware/Software Co-verification

by

Juncao Li

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science

Dissertation Committee: Fei Xie, Chair Thomas Ball Jingke Li Suresh Singh Bryant W. York Fu Li

Portland State University © 2010

#### ABSTRACT

Hardware/Software (HW/SW) interfaces are pervasive in computer systems. However, many HW/SW interface implementations are unreliable due to their intrinsically complicated nature. In industrial settings, there are three major challenges to improving reliability. First, as there is no systematic framework for HW/SW interface specifications, interface protocols cannot be precisely conveyed to engineers. Second, as there is no unifying formal model for representing the implementation semantics of HW/SW interfaces accurately, some critical properties cannot be formally verified on HW/SW interface implementations. Finally, few automatic tools exist to help engineers in HW/SW interface development.

In this dissertation, we present an automata-theoretic approach to HW/SW coverification that addresses these challenges. We designed a co-specification framework to formally specify HW/SW interface protocols; we synthesized a hybrid Büchi Automaton Pushdown System, namely Büchi Pushdown System (BPDS), as the unifying formal model for HW/SW interfaces; and we created a co-verification tool, CoVer that implements our model checking algorithms and realizes our reduction algorithms for BPDS.

The application of our approach to the Windows device/driver framework has resulted in the detection of fifteen specification issues. Furthermore, utilizing CoVer, we discovered twelve real bugs in five drivers. These non-trivial findings have demonstrated the significance of our approach in industrial applications.

### DEDICATION

To the memory of my father, Bochun Li

To my mother, Jinping Cao

To my wife, Xiaojing Liu

#### ACKNOWLEDGMENTS

This dissertation could not have been accomplished without the help and influence by many generous people. I am sincerely grateful and deeply in debt to them.

First and foremost, thanks to my advisor, Prof. Fei Xie, who brought me on board to software engineering and formal methods. When I first met Fei, various wild ideas jumped out of my head, but I was never able to find the right track to approach the real problems. Fei always listened to my ideas with a patient smile and then pointed out the problems. While Ph.D. study is a long trip with enormous possible outcomes, I often plan for the worst. Fei has always encouraged me and cheered me up when I was frustrated. Fei taught me how to be a student, a researcher, and an educator.

Dr. Thomas Ball and Dr. Vladimir Levin were very generous to share their visions and ideas with me. The key idea of this research comes from a discussion with them. They spent lots of time and effort in helping me with this research. Every discussion with them was fruitful with ideas. They also helped me edit my papers and critiqued my talks. Vladimir hosted me during my two internships at Microsoft. He also helped me in writing the very first prototype of CoVer in order to deal with bitunion operations of SLAM.

Prof. Bryant W. York helped me in many different ways, from computer science to life philosophy. He has broad knowledge and always is ready to help me. He taught me the idea of cognitive science, so that I can understand how knowledge is acquired by people and, most importantly, by myself. He showed me how science in very different disciplines can be combined to serve each other. He taught me how to write technical papers and gave me feedback on my talks.

Con McGarvey was my mentor during my two internships at Microsoft. Con taught me various skills for working in Microsoft and discussed my research. For a rookie like me, he had to be very patient and responsible. There are many other friends from Microsoft who also gave me great help. They are Randy Aull, Jaivir Aithal, Albert Chen, Alessandro Forin, Nar Ganapathy, David Hargrove, Rahul Kumar, Shuvendu Lahiri, Jakob Lichtenberg, Arvind Murching, Onur Ozyer, Shaz Qadeer, Peter Shier, Peter Wieland, Eliyas Yakub, and Yue Zuo. Among those merits that I learned from them was their passion to make better software. This has inspired me during my dissertation work and is what wakes me up every morning and excites me every day.

My other dissertation committee members, Prof. Fu Li, Prof. Jingke Li, and Prof. Suresh Singh, made invaluable contributions to my dissertation. They offered their perspectives on my research and gave careful feedback on my dissertation.

While I did not study all by my own, it is always my pleasure to take classes from PSU faculties, such as Prof. Sergio Antoy's Programming Language, Prof. Andrew Black's Scholarship Skills, and Prof. David Maier's Algorithm Design and Analysis. I can hardly remember the last time when I blinked my eyes in Prof. Ivan Sutherland's lectures. They are too interesting for me to miss any.

Thanks to my fellow graduate students, Yan Chen, Tim Chevalier, Thanh Dang, Tom Harke, Chuan-kai Lin, Emerson Murphy-Hill, Nicholas T. Pilkington, Xiuli Sun, and Candy Yiu. Interactions with them have enriched my Ph.D. study and sometimes made my life much easier. For example, this dissertation's LATEX template would have costed me tons of time if it was not for Chuan-kai's work. Four years of Ph.D. study may be joyful to me; however, it cannot be pleasant to my wife, Xiaojing Liu. Thanks to her love and understanding, which have made me happy every day. At last, certainly, not least, thanks to my parents, Bochun Li and Jinping Cao. Their persistent and passionate characters have been the role model for me. Their early education of me has made me most who I am today.

# CONTENTS

| A            | bstra | ict     | · · · · · · · · · · · · · · · · · · ·                                                                           |

|--------------|-------|---------|-----------------------------------------------------------------------------------------------------------------|

| D            | edica | tion .  | ii                                                                                                              |

| $\mathbf{A}$ | cknov | wledgn  | nents                                                                                                           |

| Li           | st of | Tables  | s                                                                                                               |

| Li           | st of | Figure  | es                                                                                                              |

| 1            | Intr  | oducti  | ion                                                                                                             |

|              | 1.1   | Motiva  | ation and Problem Statement                                                                                     |

|              |       | 1.1.1   | Motivation                                                                                                      |

|              |       | 1.1.2   | Problem Statement                                                                                               |

|              |       | 1.1.3   | The Device/Driver Scenario                                                                                      |

|              | 1.2   | Contri  | ibutions $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 5                                       |

|              |       | 1.2.1   | Our Approach                                                                                                    |

|              |       | 1.2.2   | Device/Driver Development using Our Approach 9                                                                  |

|              | 1.3   | Relate  | ed Work                                                                                                         |

|              | 1.4   | Disser  | tation Outline                                                                                                  |

| <b>2</b>     | Bac   | kgrour  | nd                                                                                                              |

|              | 2.1   | State ' | Transition Systems                                                                                              |

|              |       | 2.1.1   | Büchi Automaton                                                                                                 |

|              |       | 2.1.2   | Pushdown System                                                                                                 |

|              |       | 2.1.3   | Concurrent System                                                                                               |

|              | 2.2   | Prope   | rty Specification Languages                                                                                     |

|              |       | 2.2.1   | Linear Temporal Logic (LTL) Formula                                                                             |

|              |       | 2.2.2   | Specification Language for Interface Checking (SLIC) 22                                                         |

|              | 2.3   | Model   | $Checking \ldots 22$ |

|              |       | 2.3.1   | SLAM Engine for C Programs                                                                                      |

|   | $2.4 \\ 2.5$ |          | Moped Engine for Pushdown Systems25I Order Reduction26ows Device/Driver Stack27                                                 |

|---|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------|

| 3 | Co-          | specifi  | cation                                                                                                                          |

|   | 3.1          | -        | ication Techniques for HW/SW Interfaces                                                                                         |

|   |              | 3.1.1    | Concurrency in a System                                                                                                         |

|   |              | 3.1.2    | Transaction Level Modeling (TLM) of Hardware                                                                                    |

|   |              | 3.1.3    | Relative Atomicity                                                                                                              |

|   |              | 3.1.4    | Non-determinism in Co-specification                                                                                             |

|   |              | 3.1.5    | The modelC Language                                                                                                             |

|   | 3.2          | Specifi  | ication of HW/SW Interface Protocols                                                                                            |

|   |              | 3.2.1    | HW/SW Interface Specification                                                                                                   |

|   |              | 3.2.2    | Hardware Specification                                                                                                          |

|   |              | 3.2.3    | Software Specification                                                                                                          |

|   |              | 3.2.4    | A Realization of Relative Atomicity                                                                                             |

|   |              | 3.2.5    | Summary and Generalization                                                                                                      |

|   | 3.3          | Applic   | eations and Evaluation Criteria                                                                                                 |

|   |              | 3.3.1    | Formalization Process from English Specifications 52                                                                            |

|   |              | 3.3.2    | Applications in the HW/SW Development Process 58                                                                                |

|   |              | 3.3.3    | Evaluation Criteria                                                                                                             |

| 4 | Co-          | verifica | $ation Model \dots \dots$ |

|   | 4.1          | Büchi    | Automaton as Hardware Model                                                                                                     |

|   | 4.2          | Labele   | ed Pushdown System as Software Model                                                                                            |

|   |              | 4.2.1    | Representing Software Design                                                                                                    |

|   |              | 4.2.2    | Accepting Inputs from Hardware                                                                                                  |

|   | 4.3          | Unifyi   | ng Model for Co-verification                                                                                                    |

|   |              | 4.3.1    | Preliminaries                                                                                                                   |

|   |              | 4.3.2    | Büchi Pushdown System (BPDS)                                                                                                    |

|   |              | 4.3.3    | BPDS Loop Constraint                                                                                                            |

|   | 4.4          | Symbo    | blic Representations                                                                                                            |

|   |              | 4.4.1    | Symbolic representation of BA                                                                                                   |

|   |              | 4.4.2    | Symbolic representation of LPDS                                                                                                 |

|   |              | 4.4.3    | Symbolic representation of BPDS                                                                                                 |

viii

| <b>5</b> | Co- | rerification Algorithm                                                                                                                   |

|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

|          | 5.1 | Model Checking Problems of BPDS                                                                                                          |

|          |     | 5.1.1 Reachability Analysis                                                                                                              |

|          |     | 5.1.2 LTL Checking                                                                                                                       |

|          | 5.2 | Reachability Analysis Algorithm                                                                                                          |

|          | 5.3 | LTL Checking Algorithm                                                                                                                   |

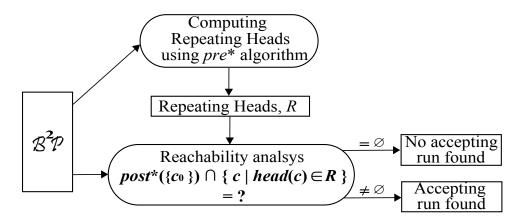

|          |     | 5.3.1 Computing the Repeating Heads                                                                                                      |

|          |     | 5.3.2 Computing the Reachability of Repeating Heads 112                                                                                  |

|          |     | 5.3.3 Summary                                                                                                                            |

|          | 5.4 | Optimization of Reachability Analysis                                                                                                    |

|          |     | 5.4.1 Reduction Algorithm $\ldots \ldots 113$ |

|          |     | 5.4.2 Correctness Argument                                                                                                               |

|          | 5.5 | Optimization of LTL Checking                                                                                                             |

|          |     | 5.5.1 Reduction Algorithm $\ldots \ldots 123$        |

|          |     | 5.5.2 Correctness Argument                                                                                                               |

|          | 5.6 | Symbolic Algorithms                                                                                                                      |

|          |     | 5.6.1 Reduction Algorithm for Reachability Analysis                                                                                      |

|          |     | 5.6.2 Reduction Algorithm for LTL Checking                                                                                               |

| 6        | Imp | $ementation \ldots 143$                |

|          | 6.1 | Reachability Analysis                                                                                                                    |

|          |     | 6.1.1 Cartesian Product via Code Instrumentation                                                                                         |

|          |     | 6.1.2 Specification of SLIC rules                                                                                                        |

|          |     | 6.1.3 Reduction                                                                                                                          |

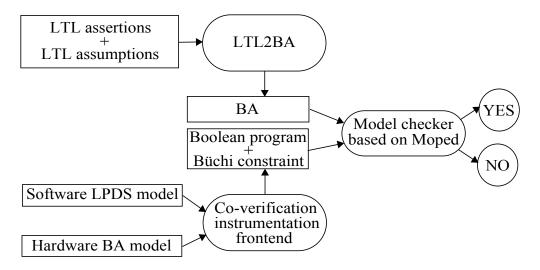

|          | 6.2 | LTL Checking                                                                                                                             |

|          |     | 6.2.1 A BPDS Model specified using Boolean programs 153                                                                                  |

|          |     | 6.2.2 Specification of LTL Properties                                                                                                    |

|          |     | 6.2.3 Reduction                                                                                                                          |

|          | 6.3 | Co-verification Tool, CoVer                                                                                                              |

| 7        | Eva | uation                                                                                                                                   |

|          | 7.1 | Co-specification                                                                                                                         |

|          | 7.2 | Co-verification                                                                                                                          |

|          |     | 7.2.1 Reachability Analysis                                                                                                              |

|          |     | 7.2.2 LTL Checking                                                                                                                       |

|          | 7.3 | Summary                                                                                                                                  |

| 8  | Con   | clusior | and Future Research                                       |

|----|-------|---------|-----------------------------------------------------------|

|    | 8.1   | Conclu  | sion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $181$   |

|    | 8.2   | Future  | Research                                                  |

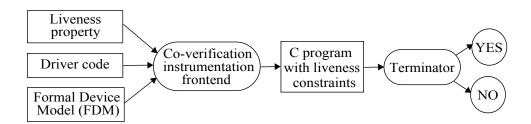

|    |       | 8.2.1   | Co-verification of Liveness Properties on Driver Code 184 |

|    |       | 8.2.2   | Co-simulation                                             |

|    |       | 8.2.3   | Co-monitoring                                             |

|    |       | 8.2.4   | Formal-model-guided Automatic Test Case Generation 188    |

| Re | efere | nces    |                                                           |

# LIST OF TABLES

| 7.1  | Formalization of the PIO-24 device/driver framework                    |

|------|------------------------------------------------------------------------|

| 7.2  | Formal model of the PIO-24 device/driver framework                     |

| 7.3  | Formalization of the Ethernet controller device/driver framework $166$ |

| 7.4  | Formal model of the Ethernet controller device/driver framework $167$  |

| 7.5  | Formalization of the USB 2.0 device/driver framework                   |

| 7.6  | Formal model of the USB 2.0 device/driver framework                    |

| 7.7  | Co-verification of the PIO-24 device/driver                            |

| 7.8  | Co-verification of the Ethernet controller device/driver               |

| 7.9  | Co-verification of the USB 2.0 OSRUSBFX2 device/driver 174             |

| 7.10 | Co-verification of the USB 2.0 USBSAMP device/driver 175               |

| 7.11 | LTL checking of BPDS <n></n>                                           |

| 7.12 | LTL checking of BPDS_Slow <n></n>                                      |

## LIST OF FIGURES

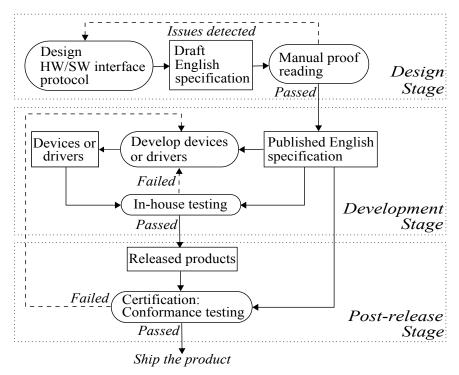

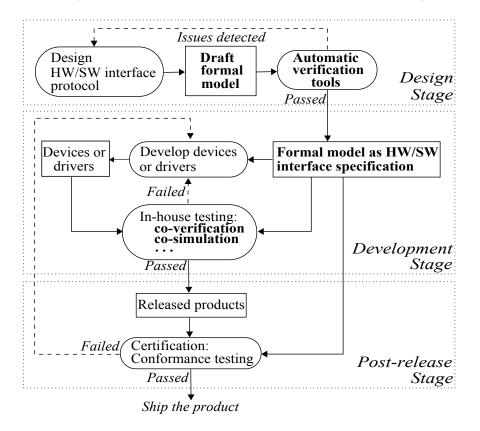

| 1.1  | Development process of device/driver frameworks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

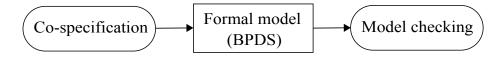

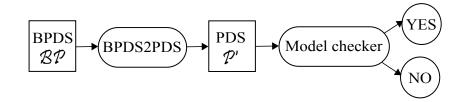

| 1.2  | Main components of our co-verification approach.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5  |

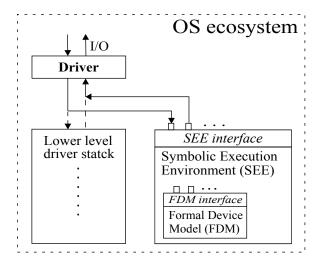

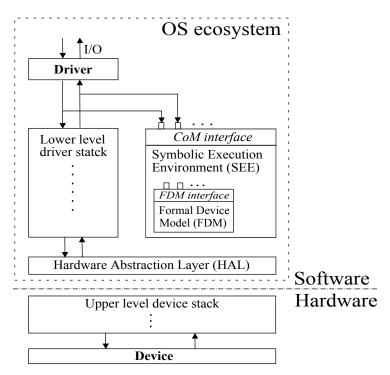

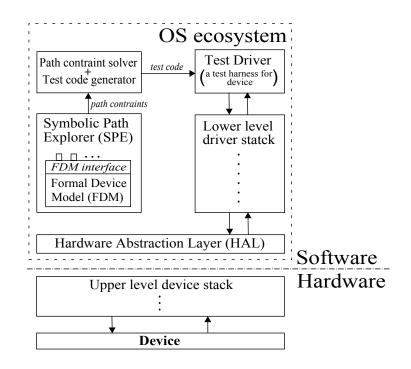

| 1.3  | Development process of device/driver frameworks using our approach.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9  |

| 2.1  | Denotations of a pushdown system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18 |

| 2.2  | Syntax of the SLIC language.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 23 |

| 2.3  | SLIC specification for a simple property of a global queue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24 |

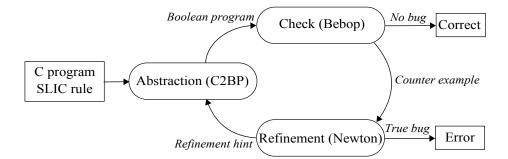

| 2.4  | The abstraction-check-refinement loop of SLAM $\hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \hfill \ldots \hfill \hfill \ldots \hfill \ldots \hfill \hfill \hfill \ldots \hfill \$ | 24 |

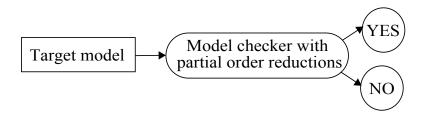

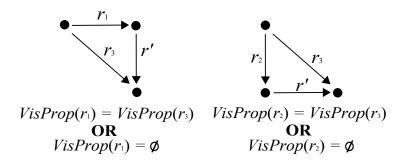

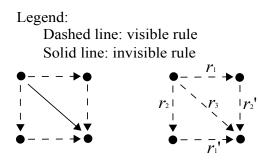

| 2.5  | Model checking with traditional partial order reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 27 |

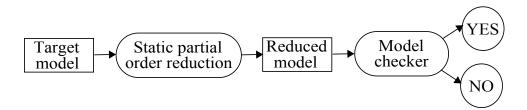

| 2.6  | Model checking with static partial order reduction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27 |

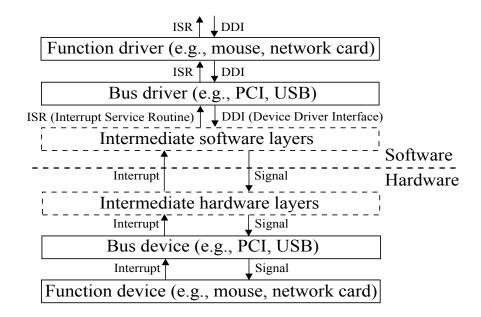

| 2.7  | A generic view of Windows device/driver stacks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28 |

| 2.8  | Driver sample code, Device Driver Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30 |

| 2.8  | Driver sample code, Interrupt Service Routine (ISR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31 |

| 2.8  | Driver sample code, Deferred Procedure Call (DPC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 32 |

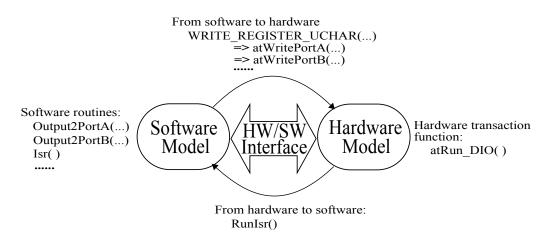

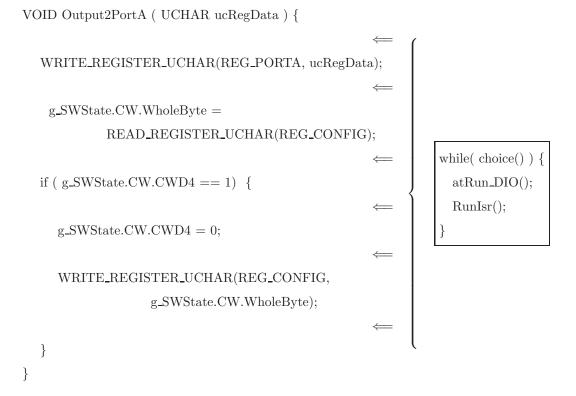

| 3.1  | Co-specification framework.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 42 |

| 3.2  | An implementation of a software interface event function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 44 |

| 3.3  | Relating register calls to software interface event functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45 |

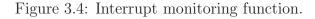

| 3.4  | Interrupt monitoring function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46 |

| 3.5  | Hardware transaction function of the PIO-24 device model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46 |

| 3.6  | A C function for outputting to Port A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47 |

| 3.7  | Execution model of relative atomicity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48 |

| 3.8  | An excerpt from Intel $10/100$ Mbps Ethernet Controller document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 50 |

| 3.9  | Excerpt of PIO-24 specification: hardware interface registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 53 |