# Portland State University PDXScholar

Dissertations and Theses

Dissertations and Theses

Spring 6-3-2015

# Post-silicon Functional Validation with Virtual Prototypes

Kai Cong Portland State University

# Let us know how access to this document benefits you.

Follow this and additional works at: https://pdxscholar.library.pdx.edu/open\_access\_etds Part of the <u>Other Computer Sciences Commons</u>, and the <u>Software Engineering Commons</u>

#### **Recommended** Citation

Cong, Kai, "Post-silicon Functional Validation with Virtual Prototypes" (2015). Dissertations and Theses. Paper 2333.

10.15760/etd.2330

This Dissertation is brought to you for free and open access. It has been accepted for inclusion in Dissertations and Theses by an authorized administrator of PDXScholar. For more information, please contact pdxscholar@pdx.edu.

### Post-silicon Functional Validation with Virtual Prototypes

by

Kai Cong

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Computer Science

Dissertation Committee: Fei Xie, Chair Suresh Singh Jingke Li Fu Li

Portland State University 2015

#### ABSTRACT

Post-silicon validation has become a critical stage in the system-on-chip (SoC) development cycle, driven by increasing design complexity, higher level of integration and decreasing time-to-market. According to recent reports, post-silicon validation effort comprises more than 50% of the overall development effort of an 65nm SoC. Though post-silicon validation covers many aspects ranging from electronic properties of hardware to performance and power consumption of whole systems, a central task remains validating functional correctness of both hardware and its integration with software. There are several key challenges to achieving accelerated and low-cost post-silicon functional validation. First, there is only limited silicon observability and controllability; second, there is no good test coverage estimation over a silicon device; third, it is difficult to generate good post-silicon tests before a silicon device is available; fourth, there is no effective software robustness testing approaches to ensure the quality of hardware/software integration.

We propose a systematic approach to accelerating post-silicon functional validation with virtual prototypes. Post-silicon test coverage is estimated in the presilicon stage by evaluating the test cases on the virtual prototypes. Such analysis is first conducted on the initial test suite assembled by the user and subsequently on the expanded test suite which includes test cases that are automatically generated. Based on the coverage statistics of the initial test suite on the virtual prototypes, test cases are automatically generated to improve the test coverage. In the postsilicon stage, our approach supports coverage evaluation of test cases on silicon devices to ensure fidelity of early coverage evaluation. The generated test cases are issued to silicon devices to detect inconsistencies between virtual prototypes and silicon devices using conformance checking. We further extend the test case generation framework to generate and inject fault scenario with virtual prototypes for driver robustness testing. Besides virtual prototype-based fault injection, an automatic driver fault injection approach is developed to support runtime fault generation and injection for driver robustness testing. Since virtual prototype enables early driver development, our automatic driver fault injection approach can be applied to driver testing in both pre-silicon and post-silicon stages.

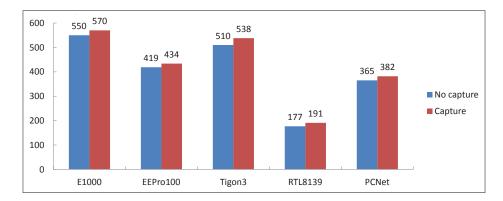

For preliminary evaluation, we have applied our coverage evaluation and test generation to several network adapters and their virtual prototypes. We have conducted coverage analysis for a suite of common tests on both the virtual prototypes and silicon devices. The results show that our approach can estimate the test coverage with high fidelity. Based on the coverage estimation, we have employed our automatic test generation approach to generate additional tests. When the generated test cases were issued to both virtual prototypes and silicon devices, we observed significant coverage improvement. And we detected 20 inconsistencies between virtual prototypes and silicon devices, each of which reveals a virtual prototype or silicon device defect. After we applied virtual prototype-based fault injection approach to virtual prototypes for three widely-used network adapters, we generated and injected thousands of fault scenarios and found 2 driver bugs. For automatic driver fault injection, we have applied our approach to 12 widely-used drivers. After testing all these drivers, we found 28 distinct bugs.

# DEDICATION

To my parents, Yizi Cong and Xiuqin Bi

To my wife, Jin Zhang

#### ACKNOWLEDGMENTS

This dissertation could not have been accomplished without the generous help and support from many professors, colleagues, friends and my family. I would like to express my sincere gratitude to all of them.

First and foremost, I would like to express my thanks to my advisor Prof. Fei Xie for his insightful guidance, continuous support and endless encouragement. He is a great advisor. He has given me not only tremendous freedom to explore my industrial and research interests, but also opportunities to present at different conferences and work with people from different industry companies. He is a wonderful researcher. He has provided me consistently good advice and challenges which are great driving force to my Ph.D. research. His professional expertise with positive attitude has been always an inspiration to me.

I'm grateful to my committee members, Prof. Suresh Singh, Prof. Jingke Li, and Prof. Fu Li. They have provided many inspirational feedbacks for my research and valuable comments for my dissertation. I also want to express sincere appreciation for their time and effort in service on my doctoral committee.

Thanks to my fellow graduate students, Juncao Li, Kecheng Hao, Li Lei, Zhenkun Yang, Disha Puri, Dejun Qian, Christopher Havlicek, and Sharookh Daruwalla. Discussions with them have accelerated my Ph.D. study and broadened my understanding of related research domains.

Finally, I especially wish to acknowledge and thank my family for their love,

support and constant encouragement. I am grateful to my parents, Yizi Cong and Xiuqin Bi, for all their love and guidance. Their diligent and optimistic characters have been always the role model for me. Last, but absolutely not least, I must thank my wife, Jin Zhang, for her unending love and encouragement. I can never thank her enough for her patience and understanding through the ups and downs of my Ph.D. study. I also would like to recognize the influence of my soon-to-be-born son, who has already brought me so much joy and hope.

# TABLE OF CONTENTS

| Abstra  | $\operatorname{ct}$                                                                                        | i   |

|---------|------------------------------------------------------------------------------------------------------------|-----|

| Dedica  | tion                                                                                                       | iii |

| Acknow  | wledgments                                                                                                 | iv  |

| List of | Tables                                                                                                     | x   |

| List of | Figures                                                                                                    | xi  |

| Chapte  | er 1 Introduction                                                                                          | 1   |

| 1.1     | Motivation and Problem Statement                                                                           | 1   |

|         | 1.1.1 Motivation $\ldots$ | 1   |

|         | 1.1.2 Problem statement                                                                                    | 2   |

| 1.2     | Proposed Solution                                                                                          | 3   |

| 1.3     | Dissertation Outline                                                                                       | 7   |

| Chapte  | er 2 Background                                                                                            | 8   |

| 2.1     | Virtual Prototypes and QEMU Virtual Devices                                                                | 8   |

| 2.2     | Symbolic Execution                                                                                         | 10  |

| 2.3     | Post-silicon Conformance Checking                                                                          | 11  |

| 2.4     | Driver Robustness Testing                                                                                  | 12  |

| 2.5     | Runtime Driver Fault Injection                                                                             | 13  |

| Chapte  | er 3 Symbolic Execution of Virtual Prototypes                                                              | 15  |

| 3.1     | Overview                                                                                                   | 15  |

| 3.2     | Harness Generation                                                                                         | 16  |

| 3.3     | Symbolic Execution Engine Adaptation                                                                       | 19  |

|         | 3.3.1 Path Explosion Problem                                                                               | 19  |

|         | 3.3.2 Environment Interaction Problem                                                                      | 19  |

|         | 3.3.3 Handling DMA                                                                                         | 20  |

| 3.4    | 3.3.4<br>Runtin<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4 | Sparse Function Pointer Array Problem                  | 20<br>22<br>22<br>24<br>24<br>24<br>26 |

|--------|-----------------------------------------------------|--------------------------------------------------------|----------------------------------------|

| Chapte | er 4 (                                              | Coverage Evaluation of Post-silicon Validation Tests   | 27                                     |

| 4.1    | Motiva                                              | ation and Overview                                     | 27                                     |

| 4.2    | Prelim                                              | ninary Definitions for Virtual Devices                 | 29                                     |

| 4.3    |                                                     | e-capture Offline-replay Coverage Evaluation           | 32                                     |

|        | 4.3.1                                               | Online-capture                                         | 32                                     |

|        | 4.3.2                                               | Offline-replay                                         | 33                                     |

|        | 4.3.3                                               | Coverage Computation and Conformance Checking in the   |                                        |

|        |                                                     | Post-silicon Stage                                     | 35                                     |

| 4.4    | Covera                                              | age Metrics                                            | 37                                     |

|        | 4.4.1                                               | Code Coverage                                          | 37                                     |

|        | 4.4.2                                               | Register Coverage                                      | 38                                     |

|        | 4.4.3                                               | Transaction Coverage                                   | 38                                     |

| 4.5    | Impler                                              | mentation                                              | 39                                     |

|        | 4.5.1                                               | Coverage on Different Levels                           | 39                                     |

|        | 4.5.2                                               | Implementation Details                                 | 40                                     |

| 4.6    | -                                                   | imental Results                                        | 40                                     |

|        | 4.6.1                                               | Online-capture and Offline-replay Overhead             | 41                                     |

|        | 4.6.2                                               | Coverage Results                                       | 42                                     |

|        | 4.6.3                                               | Coverage and Conformance Results in Post-silicon Stage | 44                                     |

| 4.7    |                                                     | ed Work                                                | 45                                     |

| 4.8    | Summ                                                | nary                                                   | 46                                     |

| Chapte | er 5                                                | Automatic Concolic Test Generation                     | 47                                     |

| 5.1    |                                                     | ation and Overview                                     | 47                                     |

| 5.2    |                                                     | lic Test Generation with Virtual Prototypes            | 49                                     |

|        | 5.2.1                                               | A Naïve Approach                                       | 49                                     |

|        | 5.2.2                                               | Concolic Test Generation Algorithm                     | 52                                     |

|        | 5.2.3                                               | Concolic Approach to Handling DMA Data                 | 54                                     |

|        | 5.2.4                                               | Transaction-based Test Selection Strategy              | 60                                     |

|        |                                                     |                                                        |                                        |

|   | ٠ | ٠ | ٠ |

|---|---|---|---|

| V | 1 | 1 | 1 |

| 5.3                         | Implei                                                                                                               | nentation $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62                                                                                                                                                                                    |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | 5.3.1                                                                                                                | ACTG Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 62                                                                                                                                                                                    |

|                             | 5.3.2                                                                                                                | Testing with Generated Test Cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 63                                                                                                                                                                                    |

| 5.4                         | Exper                                                                                                                | imental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65                                                                                                                                                                                    |

|                             | 5.4.1                                                                                                                | Evaluation of Transaction-based Test Selection Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 68                                                                                                                                                                                    |

|                             | 5.4.2                                                                                                                | Composition of Generated Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 70                                                                                                                                                                                    |

|                             | 5.4.3                                                                                                                | Evaluation of Optimization on Sparse Function Pointer Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71                                                                                                                                                                                    |

|                             | 5.4.4                                                                                                                | Coverage Improvement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 71                                                                                                                                                                                    |

|                             | 5.4.5                                                                                                                | Inconsistencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 73                                                                                                                                                                                    |

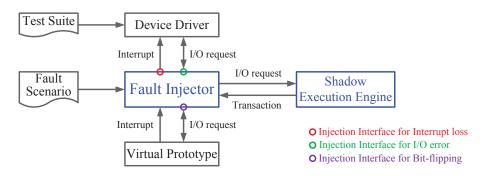

| 5.5                         | Fault                                                                                                                | Injection with Virtual Prototypes for Driver Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74                                                                                                                                                                                    |

|                             | 5.5.1                                                                                                                | Fault Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75                                                                                                                                                                                    |

|                             | 5.5.2                                                                                                                | Transaction-based Fault Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75                                                                                                                                                                                    |

|                             | 5.5.3                                                                                                                | Fault Injection Using Runtime Shadow Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77                                                                                                                                                                                    |

|                             | 5.5.4                                                                                                                | Preliminary Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78                                                                                                                                                                                    |

| 5.6                         | Relate                                                                                                               | d Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79                                                                                                                                                                                    |

|                             | 5.6.1                                                                                                                | Symbolic execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 79                                                                                                                                                                                    |

|                             | 5.6.2                                                                                                                | Concolic testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80                                                                                                                                                                                    |

|                             | 5.6.3                                                                                                                | Post-silicon validation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 80                                                                                                                                                                                    |

|                             |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                       |

| 5.7                         | Summ                                                                                                                 | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 81                                                                                                                                                                                    |

|                             |                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                       |

| Chapte                      | er 6                                                                                                                 | Automatic Driver Fault Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82                                                                                                                                                                                    |

| Chapte<br>6.1               | e <b>r 6</b> A<br>Motiva                                                                                             | Automatic Driver Fault Injection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>82</b><br>82                                                                                                                                                                       |

| Chapte                      | e <b>r 6</b><br>Motiva<br>Bound                                                                                      | Automatic Driver Fault Injection         ation and Overview         led Trace-based Iterative Fault Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>82</b><br>82<br>85                                                                                                                                                                 |

| Chapte<br>6.1               | er 6 A<br>Motiva<br>Bound<br>6.2.1                                                                                   | Automatic Driver Fault Injection         ation and Overview         led Trace-based Iterative Fault Generation         Preliminary Definitions                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>82</b><br>82<br>85<br>85                                                                                                                                                           |

| Chapte<br>6.1               | er 6 A<br>Motiva<br>Bound<br>6.2.1<br>6.2.2                                                                          | Automatic Driver Fault Injection         ation and Overview         led Trace-based Iterative Fault Generation         Preliminary Definitions         Challenges                                                                                                                                                                                                                                                                                                                                                                                                 | <b>82</b><br>82<br>85<br>85<br>88                                                                                                                                                     |

| Chapte<br>6.1               | er 6 A<br>Motiva<br>Bound<br>6.2.1<br>6.2.2<br>6.2.3                                                                 | Automatic Driver Fault Injection         ation and Overview         led Trace-based Iterative Fault Generation         Preliminary Definitions         Challenges         Trace-based Iterative Strategy                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>82</li> <li>82</li> <li>85</li> <li>85</li> <li>88</li> <li>89</li> </ul>                                                                                                    |

| <b>Chapte</b><br>6.1<br>6.2 | er 6 A<br>Motiva<br>Bound<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4                                                        | Automatic Driver Fault Injection         ation and Overview         ation and Overview         led Trace-based Iterative Fault Generation         Preliminary Definitions         Challenges         Trace-based Iterative Strategy         Bounded Generation Strategy                                                                                                                                                                                                                                                                                           | <ul> <li>82</li> <li>82</li> <li>85</li> <li>85</li> <li>88</li> <li>89</li> <li>92</li> </ul>                                                                                        |

| Chapte<br>6.1<br>6.2        | er 6 A<br>Motiva<br>Bound<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Permu                                               | Automatic Driver Fault Injection         ation and Overview         ation and Overview         led Trace-based Iterative Fault Generation         Preliminary Definitions         Challenges         Trace-based Iterative Strategy         Bounded Generation Strategy         Automatic Driver Fault Injection                                                                                                                                                                                                                                                  | <ul> <li>82</li> <li>82</li> <li>85</li> <li>85</li> <li>88</li> <li>89</li> <li>92</li> <li>95</li> </ul>                                                                            |

| Chapte<br>6.1<br>6.2        | er 6 A<br>Motiva<br>Bound<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Permu                                               | Automatic Driver Fault Injection         ation and Overview         ation and Overview         led Trace-based Iterative Fault Generation         Preliminary Definitions         Challenges         Trace-based Iterative Strategy         Bounded Generation Strategy         Automatic Driver Fault Injection Strategy                                                                                                                                                                                                                                         | <ul> <li>82</li> <li>82</li> <li>85</li> <li>85</li> <li>88</li> <li>89</li> <li>92</li> <li>95</li> <li>98</li> </ul>                                                                |

| Chapte<br>6.1<br>6.2        | er 6 A<br>Motiva<br>Bound<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Permu<br>Impler                                     | Automatic Driver Fault Injection         ation and Overview         ation and Overview         led Trace-based Iterative Fault Generation         Preliminary Definitions         Challenges         Trace-based Iterative Strategy         Bounded Generation Strategy         Automatic Driver Fault Generation         Automatic Driver Fault Generation         Preliminary Definitions         Challenges         Iterative Strategy         Automatic Driver         Bounded Generation Strategy         Intation-based Injection Strategy         Overview | <ul> <li>82</li> <li>82</li> <li>85</li> <li>85</li> <li>88</li> <li>89</li> <li>92</li> <li>95</li> </ul>                                                                            |

| Chapte<br>6.1<br>6.2        | er 6 A<br>Motiva<br>Bound<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Permu<br>Implen<br>6.4.1                            | Automatic Driver Fault Injection         ation and Overview         ation and Overview         led Trace-based Iterative Fault Generation         Preliminary Definitions         Challenges         Trace-based Iterative Strategy         Bounded Generation Strategy         Automatic Driver Fault Injection Strategy                                                                                                                                                                                                                                         | <ul> <li>82</li> <li>82</li> <li>85</li> <li>88</li> <li>89</li> <li>92</li> <li>95</li> <li>98</li> <li>99</li> </ul>                                                                |

| Chapte<br>6.1<br>6.2        | er 6 A<br>Motiva<br>Bound<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Permu<br>Impler<br>6.4.1<br>6.4.2<br>6.4.3          | Automatic Driver Fault Injection         ation and Overview         ation and Overview         led Trace-based Iterative Fault Generation         Preliminary Definitions         Challenges         Trace-based Iterative Strategy         Bounded Generation Strategy         Iteration-based Injection Strategy         Mutomatic Driver Fault Injection on Kernel API Interface                                                                                                                                                                               | <ul> <li>82</li> <li>82</li> <li>85</li> <li>85</li> <li>88</li> <li>89</li> <li>92</li> <li>95</li> <li>98</li> <li>98</li> <li>99</li> <li>100</li> </ul>                           |

| 6.1<br>6.2<br>6.3<br>6.4    | er 6 A<br>Motiva<br>Bound<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Permu<br>Impler<br>6.4.1<br>6.4.2<br>6.4.3          | Automatic Driver Fault Injection         ation and Overview         ation and Overview         led Trace-based Iterative Fault Generation         Preliminary Definitions         Challenges         Challenges         Trace-based Iterative Strategy         Bounded Generation Strategy         Itation-based Injection Strategy         Overview         Fault Injection on Kernel API Interface         Filter Mechanism                                                                                                                                     | <ul> <li>82</li> <li>82</li> <li>85</li> <li>85</li> <li>88</li> <li>89</li> <li>92</li> <li>92</li> <li>98</li> <li>99</li> <li>100</li> <li>101</li> </ul>                          |

| 6.1<br>6.2<br>6.3<br>6.4    | er 6 A<br>Motiva<br>Bound<br>6.2.1<br>6.2.2<br>6.2.3<br>6.2.4<br>Permu<br>Impler<br>6.4.1<br>6.4.2<br>6.4.3<br>Exper | Automatic Driver Fault Injection         ation and Overview         ation and Overview         led Trace-based Iterative Fault Generation         Preliminary Definitions         Challenges         Challenges         Trace-based Iterative Strategy         Bounded Generation Strategy         Itation-based Injection Strategy         Intertain         Overview         Fault Injection on Kernel API Interface         Filter Mechanism         imental Results                                                                                           | <ul> <li>82</li> <li>82</li> <li>85</li> <li>85</li> <li>88</li> <li>89</li> <li>92</li> <li>95</li> <li>98</li> <li>98</li> <li>99</li> <li>100</li> <li>101</li> <li>101</li> </ul> |

|        | 6.5.4          | Evaluation of Fault Generation and Injection Strategy 1                                                                                       | 07         |

|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|

|        | 6.5.5          | Coverage Improvement $\ldots \ldots \ldots$ | 10         |

|        | 6.5.6          | Evaluation against Other Fault Injection Techniques 1                                                                                         | 10         |

|        | 6.5.7          | Further Potentials                                                                                                                            | 10         |

| 6.6    | Related        | d Work                                                                                                                                        | 11         |

|        | 6.6.1          | Static Analysis                                                                                                                               | 11         |

|        | 6.6.2          | Reliability Testing                                                                                                                           | 12         |

|        | 6.6.3          | Fault Injection Techniques                                                                                                                    | 12         |

| 6.7    | Summa          | ary $\dots \dots \dots$                       | 13         |

| Chapte | er 7 C         | Conclusion and Future Research 1                                                                                                              | 15         |

| 7.1    | Conclu         | sion                                                                                                                                          | 15         |

| 7.2    | Datana         | Research                                                                                                                                      | 17         |

|        | ruture         |                                                                                                                                               | 11         |

|        | 7.2.1          | Conformance Checking between Virtual Prototype and Hard-                                                                                      | 11         |

|        |                |                                                                                                                                               |            |

|        |                | Conformance Checking between Virtual Prototype and Hard-                                                                                      |            |

|        | 7.2.1          | Conformance Checking between Virtual Prototype and Hard-<br>ware Design                                                                       | 17         |

|        | 7.2.1          | Conformance Checking between Virtual Prototype and Hard-<br>ware Design                                                                       | 17         |

|        | 7.2.1<br>7.2.2 | Conformance Checking between Virtual Prototype and Hard-<br>ware Design                                                                       | .17<br>.19 |

## LIST OF TABLES

| 4.1 | Time and Memory Usages for Offline Replay                                                                                                                |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 | Virtual Prototypes for Three Network Adapters                                                                                                            |

| 5.2 | Summary of Three Virtual Prototypes                                                                                                                      |

| 5.3 | Summary of Test Suite                                                                                                                                    |

| 5.4 | Comparison of Different Strategies                                                                                                                       |

| 5.5 | Time Usage of Transaction-based Selection Strategy                                                                                                       |

| 5.6 | Number of Branches Forked                                                                                                                                |

| 5.7 | Summary of Coverage Improvement                                                                                                                          |

| 5.8 | Preliminary Result of Fault Injection with Virtual Prototypes 79                                                                                         |

| 6.1 | Summary of Target Drivers                                                                                                                                |

| 6.2 | Summary of Workload                                                                                                                                      |

| 6.3 | Bug Results                                                                                                                                              |

| 6.4 | Results under Different MF (MSF = 1) $\dots \dots \dots$ |

| 6.5 | Summary of Coverage Improvement                                                                                                                          |

# LIST OF FIGURES

| 1.1 | Main Components of Our Approach                          | 4  |

|-----|----------------------------------------------------------|----|

| 2.1 | Excerpt of QEMU E1000 Virtual Device                     | 9  |

| 2.2 | An Example of Symbolic Execution                         | 11 |

| 2.3 | An Example with Kernel API Function Call                 | 12 |

| 2.4 | An Example with Error Handler                            | 13 |

| 2.5 | A Driver Fault Injection Example                         | 14 |

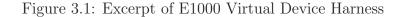

| 3.1 | Excerpt of E1000 Virtual Device Harness                  | 17 |

| 3.2 | An Example of A Sparse Function Pointer Array            | 21 |

| 3.3 | Framework for Runtime Analysis                           | 23 |

| 3.4 | Complete Harness for Runtime Monitor Mode                | 25 |

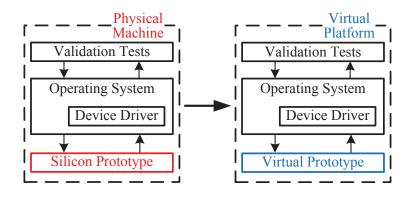

| 4.1 | From Physical to Virtual                                 | 28 |

| 4.2 | A Transaction Example                                    | 31 |

| 4.3 | A Graph Representation of State Transitions              | 32 |

| 4.4 | Workflow for Coverage Evaluation                         | 39 |

| 4.5 | Time Usage (Seconds) for Online Capture                  | 41 |

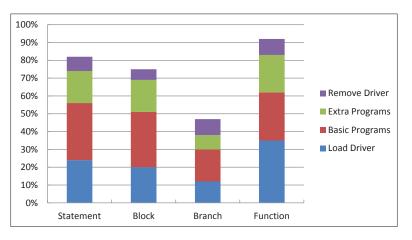

| 4.6 | Code Coverage Results for E1000                          | 42 |

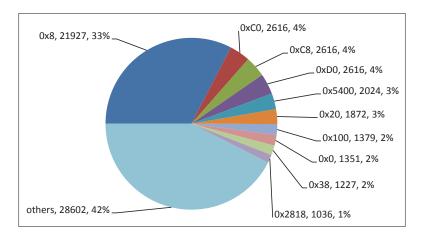

| 4.7 | Top Ten Accessed Registers for E1000                     | 43 |

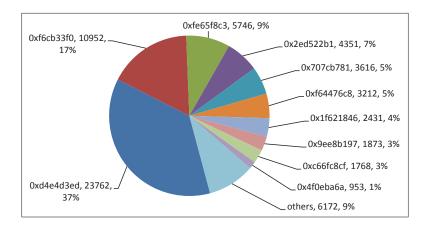

| 4.8 | Top Ten Transactions for E1000                           | 44 |

| 5.1 | Abstract Event-driven Model of QEMU E1000 Virtual Device | 50 |

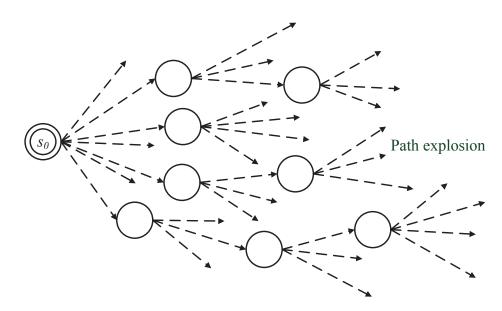

| 5.2 | Path Explosion Problem                                   | 51 |

| 5.3 | Concolic Test Generation using Virtual Devices           | 52 |

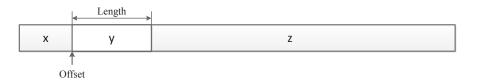

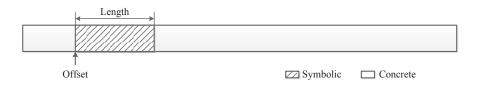

| 5.4 | An Example of QEMU DMA Data Structure                    | 55 |

| 5.5 | The Abstraction of a DMA Record                          | 56 |

| 5.6 | A Concolic DMA Example                                   | 56 |

| 5.7 | Automatic Concolic Test Generation Framework             | 62 |

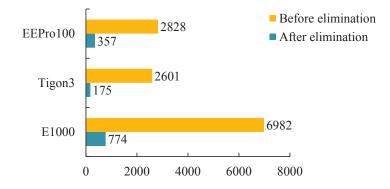

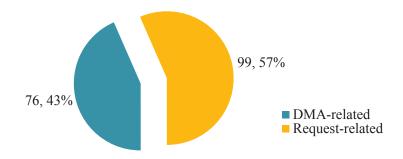

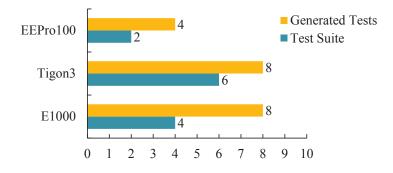

| 5.8 | Number of Generated Tests                                | 70 |

| 5.9  | Number of Generated DMA-related and Request-related Tests         | 70  |

|------|-------------------------------------------------------------------|-----|

| 5.10 | Number of Inconsistencies Detected by Test Suite and Generated    |     |

|      | Tests                                                             | 73  |

| 5.11 | Fault Injection Framework Using Runtime Shadow Execution $\ldots$ | 77  |

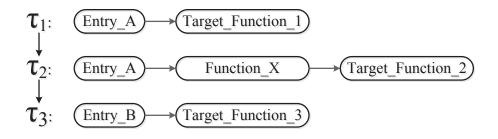

| 6.1  | A Driver Function Call Example                                    | 86  |

| 6.2  | Target Stack Trace Examples                                       | 86  |

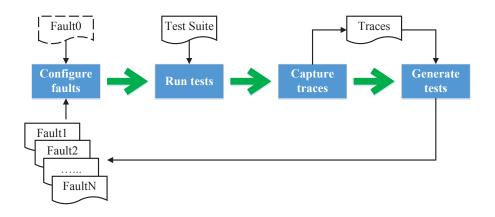

| 6.3  | The High-level Workflow                                           | 88  |

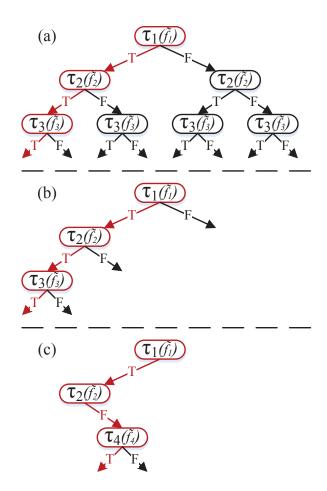

| 6.4  | Trace-based Iterative Generation Example                          | 91  |

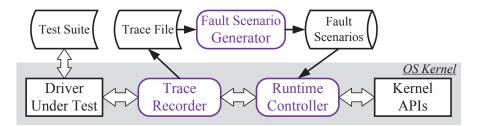

| 6.5  | Runtime Fault Injection Framework                                 | 98  |

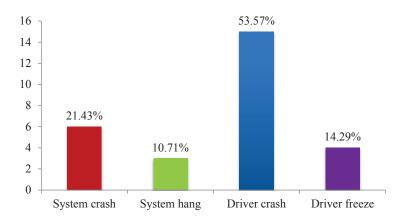

| 6.6  | Outcomes of Experiments                                           | 104 |

| 6.7  | A Sample Configuration                                            | 106 |

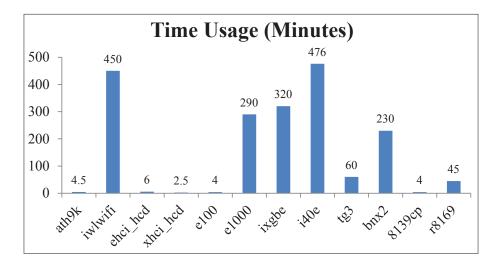

| 6.8  | Time Usage                                                        | 108 |

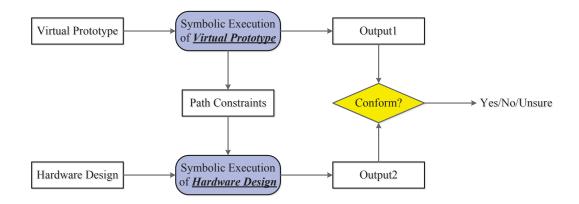

| 7.1  | Framework for Conformance Checking between Virtual Prototype      |     |

|      | and Hardware Design                                               | 118 |

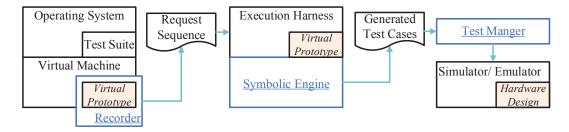

| 7.2  | Workflow of Automatic Test Generation for RTL Simulation          | 119 |

#### Chapter 1

#### INTRODUCTION

#### 1.1 MOTIVATION AND PROBLEM STATEMENT

#### 1.1.1 Motivation

New computer systems: smart phones, wearable devices, tablets, laptops, servers, etc. are entering the market place at an ever-accelerating pace. This brings enormous pressures on the product development teams to shorten the time-to-market. A recent study by International Business Strategies indicates that a 3-month delay to market reduces revenue by about 30% for chip manufacturers in general, and the penalty is even more severe for fast-evolving markets such as mobile devices [34]. To exacerbate the pressures, the complexities of these systems, both their hardware and software, are increasing significantly. Quoting a SoC architect for a mobile platform, "a state-of-the-art mobile platform is considered more complex than a server due to the many types of technologies it integrates while the product cycle is often as short as two years." A crucial stage in the product development cycle is post-silicon validation, i.e., validation conducted on actual devices or silicon prototypes with corresponding drivers. Post-silicon validation is a significant, fastest-growing component of validation cost. According to recent industry reports [59], post-silicon validation effort often consumes more than 50%of an 65nm SoC's overall design effort. This demands innovative approaches to

speed-up post-silicon validation and reduce its cost.

Though post-silicon validation covers many aspects ranging from electronics properties of hardware to performance and power consumption of whole systems, a central task remains validating functional correctness of both hardware and its integration with software. Recently virtual prototypes are increasingly used in hardware/software development to enable driver development and validation at an early stage even before silicon prototypes become available [70]. An example is how Intel used virtual prototypes to enable driver development for their 40G Ethernet adapter (E40G) before the silicon prototype became available [62]. An E40G virtual prototype was created and used to test and validate the E40G driver being developed. Bugs were found in the driver using the E40G virtual device, even before the real E40G device became available. Since virtual prototypes are utilized as a transaction-level replacement for silicon devices to support driver development and validation, it is greatly desired to extend the effectiveness of virtual prototypes into post-silicon functional validation so that the major efforts invested can be fully utilized. We see major potentials of virtual prototypes in post-silicon functional validation of both hardware and its integration with software.

#### 1.1.2 Problem statement.

This dissertation research is concerned with how to speed-up post-silicon functional validation with virtual prototypes for both hardware and software development. We observe four major challenges to achieving our goal:

• Limited Silicon Observability and Traceability. The silicon device is typically a black box. The amount of run-time information that can be retrieved from the device internal with build-in test circuitries and advanced logic analyzers is still quite limited. Such limited observability and traceability make postsilicon validation difficult.

- Lack of Good Test Coverage Estimation. There lacks good test coverage metrics over a silicon device. Therefore, it is difficult to assess the effectiveness of test cases and prioritize their application. In addition, coverage metrics rooted in hardware design are not well suited for testing the integration with software.

- Lack of Early Test Readiness. Test cases for post-silicon validation must be ready before a silicon device is available. The time-to-market after the device is first available can be as short as several weeks. Therefore, it is highly desired to avoid spending this precious time on preparing, debugging, and fixing test cases.

- Lack of Effective Fault Injection for Driver Testing. Device drivers are critical system components that operate or control devices. To ensure the system reliability, device drivers must tolerate all kinds of system situations, such as low resource situations, PCI bus errors and DMA failures. Therefore, it is necessary that different kinds of system scenarios and faults can be generated and injected to test the driver robustness.

#### 1.2 PROPOSED SOLUTION

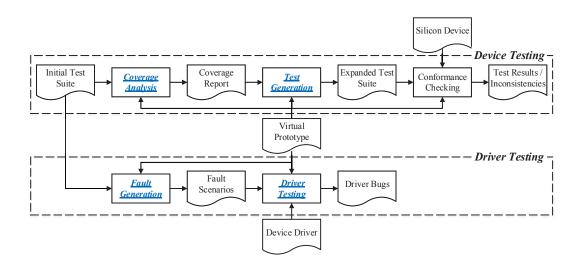

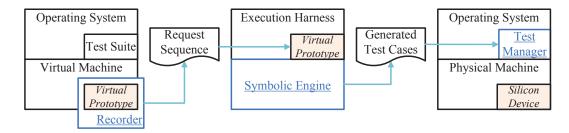

We propose an approach to accelerating post-silicon functional validation and reducing its cost with virtual prototypes. As shown in Figure 1.1, virtual prototypes play a central role in our approach which mainly support three components:

• *Coverage analysis:* While a silicon device is often a black box, its corresponding virtual prototype is a white box, i.e., its internal structures and workings

Figure 1.1: Main Components of Our Approach

are visible. The virtual prototype often models transaction-level behaviors of the silicon device. Therefore, the virtual prototype can be utilized to estimate the coverage of post-silicon validation tests on the functionalities of the silicon device.

- *Test generation:* Based on the coverage estimation, test cases can be automatically generated to specifically target silicon device functionalities that are yet covered. Test cases are particularly needed to trigger error handling conditions that are often hard to test with manually written tests. Expanded test suite can be used for testing silicon devices and supporting conformance checking.

- Effective fault generation for driver testing: Since virtual prototypes provide all device functionalities, many driver testing tasks can be conducted with virtual prototypes. We first develop a virtual prototype-based fault injection for driver robustness testing. Furthermore, we develop an automatic driver fault injection framework which can generate effective fault scenarios in a

modest amount of time. The automatic driver fault injection framework can be applied to both virtual and silicon devices.

For coverage analysis and test generation, we employ symbolic execution of virtual prototypes as the foundation. More details about these components are elaborated below:

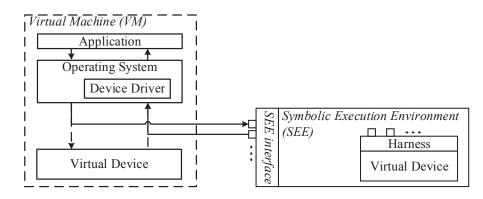

Symbolic Execution of Virtual Prototypes. The foundation of our approach is symbolic execution of virtual prototypes [20], utilized in calculating test coverage and generating new test cases. We have developed a symbolic execution environment (SEE) for QEMU virtual devices. Central to this environment is (1) how to encapsulate a virtual device in an execution harness that is sufficiently faithful to avoid crippling inaccuracy and sufficiently abstract to avoid prohibiting execution overheads and (2) how to reign in several limitations of symbolic execution by utilizing features of virtual devices.

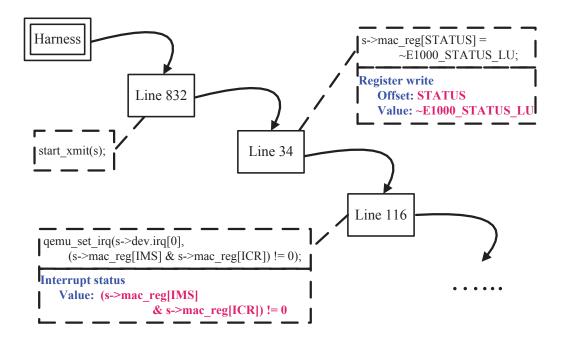

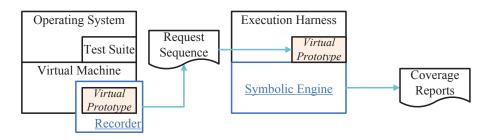

**Coverage Analysis of Post-silicon Tests.** Test coverage is an important metric for evaluating the quality and readiness of post-silicon tests. We propose an onlinecapture offline-replay approach to coverage analysis of post-silicon validation tests with virtual prototypes for estimating silicon device test coverage [18]. We first capture necessary data from a concrete execution of the virtual prototype within a virtual platform under a given test, and then compute the test coverage by efficiently replaying this execution offline on the virtual prototype itself. Our approach provides early feedback on quality of post-silicon validation tests before silicon is ready. To ensure fidelity of early coverage evaluation, our approach have been further extended to support coverage evaluation and conformance checking in the post-silicon stage. Automatic Concolic Test Generation. We present a concolic testing approach to generation of post-silicon tests with virtual prototypes [19]. This work is inspired by recent advances in concolic testing [30, 31]. Concolic (a portmanteau of concrete and symbolic) testing is a hybrid testing technique that integrates concrete execution with symbolic execution [39]. In our approach, we first identify device states under test from concrete executions of a virtual prototype using a transaction-based selection strategy, and then symbolically execute the virtual prototype from these states. Concrete tests are generated based on the symbolic path constraints obtained. We apply the generated test cases to both the silicon device and the virtual prototype, and check for inconsistencies between the real and virtual device states. Once an inconsistency is detected, we can replay the test case on the virtual prototype through symbolic execution to see whether it is a silicon device bug or a virtual prototype defect. The combination of virtual and silicon device execution brings three major benefits: (1) helping developers more easily and better understand a silicon device using its virtual prototype, (2) checking for defects in the silicon device, and (3) detecting bugs in the virtual prototype.

Effective Fault Injection for Driver Robustness Testing. Device drivers ought to be robust enough for handling different kinds of device faults instead of crashing or hanging the system. We first develop a virtual prototype-based fault injection approach by extending test case generation framework. The virtual prototype-based fault injection approach employs two fault models to generate device-related fault scenarios. After applying the approach to virtual prototypes of three widely-used network adapters, we have generated thousands of virtual prototype-based fault scenarios and triggered two driver crashes. Furthermore, to test the interfaces between device drivers and kernel API functions, we propose an automatic driver fault injection approach to generation and injection of fault scenarios with either virtual prototypes or silicon devices. Our approach runs a driver test and collects the corresponding runtime trace. Then we identify target functions which can fail from the captured trace, and generate effective fault scenarios on these target functions. Each generated fault scenario includes a fault configuration which is applied to guide further fault injection. Each fault scenario is applied to guide one instance of runtime fault injection and generate further fault scenarios. This process is repeated until all fault scenarios have been tested. To achieve systematic and effective fault injection, we have developed two key strategies. First, a bounded trace-based iterative generation strategy is developed for generating effective fault scenarios. Second, a permutation-based injection strategy is developed to assure the fidelity of runtime fault injection.

#### **1.3 DISSERTATION OUTLINE**

The remainder of this dissertation is organized as follows. Chapter 2 introduces a brief overview of background including virtual prototypes, symbolic execution and driver robustness testing. Chapter 3 presents symbolic execution of virtual prototypes which provides foundational support for our post-silicon functional validation. Chapter 4 elaborates coverage evaluation of post-silicon tests. Chapter 5 presents our approach to automatic concolic test generation. Chapter 6 illustrates automatic driver fault injection. Chapter 7 concludes and discusses future work.

#### Chapter 2

#### BACKGROUND

#### 2.1 VIRTUAL PROTOTYPES AND QEMU VIRTUAL DEVICES

Virtual prototypes are fast, fully functional software models of hardware systems, which enable unmodified execution of software code. QEMU is a generic, open source machine emulator and virtualizer [10, 27]. We adopt QEMU virtual devices as the virtual prototypes for our study due to the open-source nature of QEMU and its wide varieties of virtual devices. Technology developed on QEMU virtual devices can be readily generalized to other open-source or commercial virtual prototyping environments due to their similarity in virtualization concepts, despite their different levels of modeling details.

To better understand the concept of virtual prototype, we illustrate it with a QEMU virtual device for the Intel E1000 Gigabit network adapter. The E1000 adapter is a PCI (Peripheral Component Interconnect) device which communicates with its control software through interface registers and interrupts. The E1000 virtual device has corresponding functions to support such communication, for instance, interface register functions and interrupt functions. In order to realize the functionalities of silicon devices, the E1000 virtual device also needs to maintain the device state and implement functions that virtualize device transactions and environment inputs. As shown in Figure 2.1, the E1000 virtual device has the following components:

```

// 1. Device state

typedef struct E1000State_st {

PCIDevice dev; //PCI configuration

uint32_t mac_reg[0x8000]; //Interface registers

. . . . . .

uint32_t rxbuf_size; //Internal variables

. . . . . .

} E1000State;

// 2. Interface register function: write register

static void write_reg(void *opaque, uint64_t index, uint32_t value) {

E1000State *s = (E1000State *)opaque;

. . . . . .

if(index == TRANSMIT) {

s->mac_reg[index] = value;

start_xmit(s); //Invoking transaction function

}

. . . . . .

}

// 3. Device transaction function: transmit packets

static void start_xmit(E1000State *s) {

pci_dma_read(&s->dev, base, &desc, sizeof(desc)); //Invoking DMA functions

. . . . . .

set_irq(s->dev.irq[0],1); //Invoking interrupt function

}

// 4. Environment function: receive packets

static ssize_t receive(NetClientState *nc, const uint8_t *buf, size_t size) {

. . . . . .

pci_dma_write(&s->dev, base, &desc, sizeof(desc)); //Invoking DMA functions

. . . . .

set_irq(s->dev.irq[0],1); //Invoking interrupt function

7

```

- The device state, *E*1000*State*, which keeps track of the state of the E1000 device and the device configuration;

- The interface register functions such as *write\_reg* which are invoked by QE-MU to access interface registers and trigger transaction functions;

- The device transaction functions such as *start\_xmit* which are invoked by the interface register functions to realize the functionality;

- The environment functions such as *receive* which are invoked by QEMU to pass environment inputs such as a packet received to the virtual device.

Both the device transaction functions and environment functions may access DMA data by calling DMA functions *pci\_dma\_write* and *pci\_dma\_read*, as well as fire interrupts by calling interrupt function *set\_irq*. Both PCI interface functions and environment input functions are device entry functions which are invoked by QEMU to trigger device functionalities.

#### 2.2 SYMBOLIC EXECUTION

Symbolic execution executes a program with symbolic values as inputs instead of concrete ones and represents the values of program variables as symbolic expressions. Consequently, the outputs computed by the program are expressed as a function of input symbolic values. The symbolic state of a program includes the symbolic values of program variables, a path condition, and a program counter. The path condition is a boolean formula over the symbolic inputs; it accumulates constraints which the inputs must satisfy for the symbolic execution to follow the particular path. The program counter points to the next statement to execute. A symbolic execution tree captures the paths explored by the symbolic execution of a

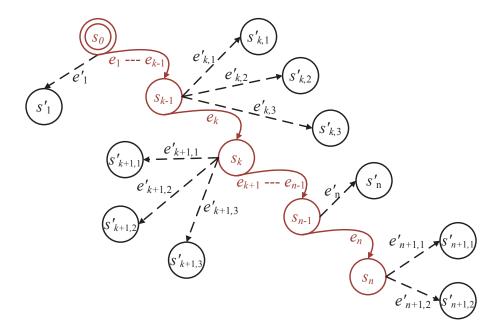

program: the nodes represent the symbolic program states and the arcs represent the state transitions.

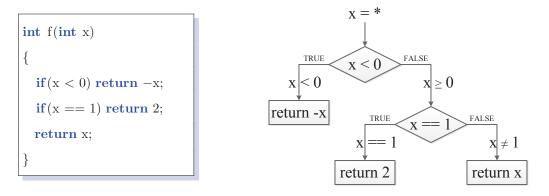

Figure 2.2: An Example of Symbolic Execution

We use the program in Figure 2.2 to illustrate how symbolic execution is conducted. At the entry, x has a symbolic value, i.e., any value allowed by its type (in this case, integer). At each branching point, the path condition is updated with conditions on the inputs to select between the two alternative paths. For this example, we can get three paths based on symbolic execution. Each path will have its own path condition, for example, x < 0 for the leftmost path.

#### 2.3 POST-SILICON CONFORMANCE CHECKING

In previous work [43, 44, 45], we have developed an approach to post-silicon conformance checking of a silicon device with its virtual device. The conformance between the silicon and virtual devices is defined over their interface states. The request sequence issued to the device is first captured on the silicon device, and then replayed on the virtual device to check if the interface states of the silicon and virtual devices are consistent.

In Chapter 4 and 5, we utilize conformance checking for ensuring fidelity of coverage evaluation and evaluating efficiency of test generation results.

#### 2.4 DRIVER ROBUSTNESS TESTING

According to the IEEE standard [1], robustness is defined as the degree to which a system operates correctly in the presence of exceptional inputs or stressful environmental conditions in software testing. The goal of robustness testing is to develop test cases and test environments where the robustness of a system can be assessed.

Kernel modules, especially device drivers, play a critical role in operating systems. It is important to assure that device drivers behave safely and reliably to avoid system crashes. Typically device drivers can work correctly under normal situations. However, it is easy for driver developers to mishandles certain corner cases, such as low resource situations, PCI bus errors and DMA failures.

```

int * p = (int *)kmalloc(size, GFP_ATOMIC);

p[10] = 3;

```

Figure 2.3: An Example with Kernel API Function Call

As shown in Figure 2.3, the *kmalloc* function is invoked to allocate a block of memory. After the function returns, the returned pointer is directly used without null pointer checking. Under normal system conditions, the *kmalloc* function returns successfully with a correct pointer to the allocated memory. However, when the *kmalloc* function returns a null pointer under a low resource situation, it is possible for the driver to crash the system. To handle such errors, the common approach is to add an error handling mechanism.

As shown in Figure 2.4, after the kmalloc function returns, the code checks whether the return value is a null pointer. If the kmalloc function returns a null pointer, the corresponding error handler is invoked to handle the error. However,

```

int * p = (int *)kmalloc(size, GFP_ATOMIC);

if(!p) goto error;

p[10] = 3;

.....

error: error_handler();

```

Figure 2.4: An Example with Error Handler

a further concern is whether the error is handled correctly and does not trigger other driver or system errors.

To improve driver robustness, a device driver should be tested to see whether there exist two kinds of bugs: (1) driver error handling code does not exist; (2) driver error handling mechanisms do not handle the error correctly or trigger other driver/system issues. The first kind seems to be easy to avoid as long as driver developers write and check the code carefully. However, it still happens in the real world. The second kind is usually difficult and expensive to test.

#### 2.5 RUNTIME DRIVER FAULT INJECTION

In driver robustness testing, all possible error conditions of a driver ought to be exercised. However, certain error conditions might be difficult and expensive to trigger, but efforts should be made to force or to simulate such errors to test the driver. Fault injection is a technique for software robustness testing by introducing faults to test code paths, in particular error handling code paths that, otherwise, might rarely be followed. Recently, fault injection techniques have been widely explored and studied for software testing and system robustness testing.

Runtime driver fault injection can be employed to simulate kernel interface failures to trigger and test error handling code. The common approach to driver

```

void * kmalloc(size_t size, int flags) {

// Memory allocation operations

}

void * kmalloc_fault(size_t size, int flags) {

return NULL;

}

```

Figure 2.5: A Driver Fault Injection Example

fault injection is to hijack the kernel function calls, such as kmalloc and vmalloc. By hijacking these functions, we can call the corresponding fault function to return a false result instead of invoking these functions. As shown in Figure 2.5, when kmalloc is invoked, the corresponding fault function  $kmalloc_fault$  is invoked to return a null pointer instead of a correct pointer to simulate an allocation error. In this way, we can test if device drivers can survive on different error handling code paths to improve driver robustness.

There are two main limitations with current driver fault injection. First, there is no automatic framework to support fault injection for different system function calls. Second, there is no a systematic test generation approach to generate effective fault scenarios. Currently most fault injections tools are using random fault injection which is facing major challenges in achieving desired effectiveness and avoiding duplicate fault scenarios.

In Chapter 6, we provide a framework which can automatically generate and inject fault scenarios at runtime. We have proposed a trace-based iterative generation strategy to produce unique and effective fault scenarios and developed a permutation-based replay mechanism to inject fault scenarios with high fidelity.

#### Chapter 3

#### SYMBOLIC EXECUTION OF VIRTUAL PROTOTYPES

#### 3.1 OVERVIEW

Symbolic execution of virtual prototypes is the foundation for our approach to coverage evaluation and test generation. In order to symbolically execute virtual prototypes, we must address the following technical challenges:

- Environment modeling. A virtual device is not a stand-alone program. There are two issues with this incompleteness. First, the virtual device needs to be properly initialized and its entry functions properly exercised. Second, the virtual device may invoke libraries in its environment. Therefore, we need a solution to enclose the virtual device so that the symbolic execution engine can consume it and perform accurate and efficient analysis.