### **IOWA STATE UNIVERSITY Digital Repository**

Graduate Theses and Dissertations

Iowa State University Capstones, Theses and Dissertations

2011

# Phase-based tuning: better utilized performance asymmetric multicores

Tyler Sondag Iowa State University

Follow this and additional works at: https://lib.dr.iastate.edu/etd

Part of the Computer Sciences Commons

### Recommended Citation

Sondag, Tyler, "Phase-based tuning: better utilized performance asymmetric multicores" (2011). Graduate Theses and Dissertations. 10416.

https://lib.dr.iastate.edu/etd/10416

This Dissertation is brought to you for free and open access by the Iowa State University Capstones, Theses and Dissertations at Iowa State University Digital Repository. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Iowa State University Digital Repository. For more information, please contact digirep@iastate.edu.

### Phase-based tuning: better utilized performance asymmetric multicores

by

### Tyler Sondag

A dissertation submitted to the graduate faculty in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

Major: Computer Science

Program of Study Committee:

Hridesh Rajan, Major Professor

Morris Chang

Soma Chaudhuri

Jack Lutz

Joseph Zambreno

Iowa State University

Ames, Iowa

2011

Copyright © Tyler Sondag, 2011. All rights reserved.

## TABLE OF CONTENTS

| LIST O | F TAB  | LES                                           | vi  |

|--------|--------|-----------------------------------------------|-----|

| LIST O | F FIGU | JRES                                          | vii |

| ACKN(  | OWLEI  | DGMENTS                                       | ix  |

| ABSTR  | ACT    | • • • • • • • • • • • • • • • • • • • •       | X   |

| СНАРТ  | TER 1. | Introduction                                  | 1   |

| 1.1    | Proble | ems Facing Efficient Use of AMPs              | 2   |

| 1.2    | Phase- | -based Tuning                                 | 3   |

|        | 1.2.1  | Compile Time Grouping and its Problems        | 5   |

|        | 1.2.2  | Lazy Grouping and its Benefits                | 6   |

| 1.3    | Benefi | its of Phase-based Tuning                     | 7   |

| 1.4    | Organ  | ization                                       | 8   |

| СНАРТ  | TER 2. | Phase-based Tuning with Compile Time Grouping | 10  |

| 2.1    | Static | Phase Transition Analysis                     | 11  |

|        | 2.1.1  | Static CFG Annotation                         | 12  |

|        | 2.1.2  | Phase Transition Marking                      | 19  |

|        | 2.1.3  | Determining block types                       | 22  |

| 2.2    | Dynar  | nic Analysis and Tuning                       | 23  |

| СНАРТ  | TER 3. | Analysis and Instrumentation Framework        | 26  |

| 3.1    | Disass | sembly                                        | 26  |

| 3.2    | Analy  | sis                                           | 27  |

|       | 3.2.1   | Control Flow Analysis                          | 27 |

|-------|---------|------------------------------------------------|----|

|       | 3.2.2   | Abstract Interpretation                        | 27 |

| 3.3   | Instrur | mentation                                      | 29 |

| СНАРТ | TER 4.  | Evaluation of Phase-based Tuning               | 31 |

| 4.1   | Experi  | imental Setup                                  | 32 |

|       | 4.1.1   | System Setup                                   | 32 |

|       | 4.1.2   | Workload Construction                          | 33 |

| 4.2   | Space   | and Time Overhead                              | 33 |

|       | 4.2.1   | Space Overhead                                 | 34 |

|       | 4.2.2   | Time Overhead                                  | 36 |

|       | 4.2.3   | Core Switches                                  | 39 |

| 4.3   | Throug  | ghput                                          | 41 |

|       | 4.3.1   | IPC threshold                                  | 41 |

|       | 4.3.2   | Clustering error                               | 42 |

|       | 4.3.3   | Minimum instruction size                       | 43 |

| 4.4   | Fairne  | ss                                             | 44 |

| 4.5   | Analys  | sis of Trade-offs                              | 46 |

| 4.6   | Summ    | ary of Results                                 | 46 |

| СНАРТ | TER 5.  | Practical and Future Use of Phase-based Tuning | 48 |

| 5.1   | Applic  | eability to Multi-threaded Programs            | 48 |

| 5.2   | Chang   | ring Application and Core Behavior             | 49 |

| 5.3   | Floatin | ng Point Emulation and IPC                     | 50 |

| 5.4   | Scalab  | oility for many-cores                          | 50 |

| СНАРТ |         | Lazy Grouping                                  | 51 |

| 6.1   |         | ile Time – Computing Similarity Metrics        | 52 |

|       | 6.1.1   |                                                | 53 |

|       | 6.1.2  | Instruction Cache                               | 54 |

|-------|--------|-------------------------------------------------|----|

|       | 6.1.3  | Data Cache                                      | 54 |

|       | 6.1.4  | Instruction Level Parallelism (ILP)             | 55 |

|       | 6.1.5  | Loop Size                                       | 56 |

| 6.2   | OS/Ma  | achine Install Time – Network Training          | 56 |

| 6.3   | Progra | m Install Time – Grouping                       | 59 |

| 6.4   | Summ   | ary of Benefits                                 | 59 |

| СНАРТ | TER 7. | Evaluation of Lazy Grouping                     | 60 |

| 7.1   | Experi | mental setup                                    | 60 |

|       | 7.1.1  | System Setup                                    | 60 |

|       | 7.1.2  | Computing Actual Behavior for Evaluation        | 61 |

|       | 7.1.3  | Accuracy Metrics                                | 62 |

| 7.2   | Compi  | ile Time vs. Lazy Grouping                      | 63 |

|       | 7.2.1  | Universal Compile Time Grouping                 | 63 |

|       | 7.2.2  | Target Machine Specific Compile Time Grouping   | 64 |

| 7.3   | Accura | acy of Lazy Grouping                            | 66 |

| 7.4   | Space  | Overhead                                        | 72 |

| 7.5   | Lazy C | Grouping in Phase-based Tuning                  | 72 |

|       | 7.5.1  | Impact of Lazy Grouping on Overheads            | 73 |

|       | 7.5.2  | Impact of Lazy Grouping on Speedup and Fairness | 75 |

| 7.6   | Summ   | ary                                             | 76 |

| СНАРТ | TER 8. | Related Work                                    | 77 |

| 8.1   | Relate | d Work: Phase-based Tuning                      | 77 |

| 8.2   | Relate | d Work: Lazy Grouping                           | 79 |

|       | 8.2.1  | Behavior Similarity                             | 79 |

|       | 8.2.2  | Machine Learning for Optimization               | 80 |

| CHAPT                  | ER 9.        | Future Work                           | 82 |

|------------------------|--------------|---------------------------------------|----|

| 9.1                    | Potenti      | al Applications of Phase-based Tuning | 82 |

|                        | 9.1.1        | JIT Optimizations                     | 82 |

|                        | 9.1.2        | Power Consumption                     | 83 |

| 9.2                    | Potenti      | al Applications of Lazy Grouping      | 84 |

|                        | 9.2.1        | Guide Optimization                    | 84 |

|                        | 9.2.2        | Benchmark Selection                   | 85 |

| 9.3                    | Small        | Improvements                          | 85 |

|                        | 9.3.1        | Phase-based Tuning                    | 85 |

|                        | 9.3.2        | Lazy Grouping                         | 86 |

| CHAPTER 10. Conclusion |              |                                       | 88 |

| RIRLIO                 | RIRLIOGRAPHV |                                       |    |

## LIST OF TABLES

| Table 4.1 | Space overhead of phase marks            | 35 |

|-----------|------------------------------------------|----|

| Table 4.2 | Time overhead of phase-based tuning      | 37 |

| Table 4.3 | Core switches per benchmark              | 39 |

| Table 4.4 | Phase-based tuning fairness              | 45 |

| Table 7.1 | Core types used for lazy grouping        | 61 |

| Table 7.2 | Lazy grouping accuracy per configuration | 67 |

## LIST OF FIGURES

| Figure 1.1 | Overview of phase-based tuning                                 | 4  |

|------------|----------------------------------------------------------------|----|

| Figure 1.2 | Compile time similarity dimension problem                      | 6  |

| Figure 2.1 | Overview of phase transition analysis                          | 12 |

| Figure 2.2 | Interval type summarization algorithm                          | 14 |

| Figure 2.3 | Interval summarization illustration                            | 15 |

| Figure 2.4 | Loop summarization illustration                                | 17 |

| Figure 2.5 | Loop type summarization algorithm                              | 18 |

| Figure 2.6 | Lookahead based phase marking                                  | 21 |

| Figure 2.7 | Lookahead based reduction of phase marks                       | 22 |

| Figure 2.8 | Algorithm for preferred core assignment                        | 24 |

| Figure 3.1 | Conversion from address to labels                              | 26 |

| Figure 3.2 | Abstract interpretation example                                | 28 |

| Figure 3.3 | Binary instrumentation example                                 | 30 |

| Figure 4.1 | Space overhead of phase marks                                  | 36 |

| Figure 4.2 | Time overhead of phase marks                                   | 38 |

| Figure 4.3 | Average cycles between core switches                           | 40 |

| Figure 4.4 | Throughput with variable IPC threshold (basic block technique) | 42 |

| Figure 4.5 | Throughput with variable IPC threshold (interval technique)    | 42 |

| Figure 4.6 | Impact of similarity precision                                 | 43 |

| Figure 4.7 | Throughput per technique                                       | 43 |

| Figure 4.8 | Speedup vs fairness: average time vs. max stretch                   | 47 |

|------------|---------------------------------------------------------------------|----|

| Figure 6.1 | Lazy grouping overview                                              | 51 |

| Figure 6.2 | Lazy grouping: compile and program install time                     | 53 |

| Figure 6.3 | Lazy grouping: OS install time                                      | 57 |

| Figure 7.1 | Compile time vs lazy grouping                                       | 64 |

| Figure 7.2 | Compile time grouping portability                                   | 65 |

| Figure 7.3 | Lazy group distribution (single core)                               | 68 |

| Figure 7.4 | Lazy group distribution (AMPs)                                      | 69 |

| Figure 7.5 | Per benchmark lazy grouping (i7-atom)                               | 71 |

| Figure 7.6 | Lazy grouping space overhead                                        | 72 |

| Figure 7.7 | Phase-based tuning space overhead with lazy grouping                | 73 |

| Figure 7.8 | Phase-based tuning time overhead with lazy grouping (per benchmark) | 74 |

| Figure 7.9 | Phase-based tuning time overhead with lazy grouping (summary)       | 75 |

#### ACKNOWLEDGMENTS

I would like to thank everyone who over the past several years has helped me with my studies and guided me in the right directions.

First and foremost, I would like to thank my adviser Dr. Hridesh Rajan for being a great mentor over the past years. It has truly been an honor to be his student. His advice and guidance have helped me grow tremendously as a researcher and as a person. I sincerely appreciate all the time, advice, and patience he has given me over the past five years.

I would also like to thank Dr. Kian Pokorny and Dr. Jim Feher who inspired me to go to graduate school, to pursue a career in research, and gave great advice throughout my undergraduate career and since.

Thanks to the members of the Laboratory for Software Design at ISU for their help throughout my graduate studies and for their constructive criticism and suggestions during all stages of my work. I also thank Patrick Carlson and Paul Murphy for their help developing and debugging parts of the analysis and instrumentation framework used for evaluating the ideas in this thesis.

I would like to thank my parents Brenda and Dale for their love and support throughout everything. Without them none of this would be possible. There is no way I can put into words how grateful I am to them. My brother Trevor for sparking my interest in mathematics at an early age and for being a great role model. My brother Trent letting me practice (and improve) my teaching and presentation skills on him.

Finally, I thank my wife Kasey for being supportive and understanding (especially before deadlines) and encouraging me when I needed it most. For being my best friend, and distracting me when I needed it most.

### **ABSTRACT**

The latest trend towards performance asymmetry among cores on a single chip of a multicore processor is posing new challenges. For effective utilization of these performance-asymmetric multicore processors, code sections of a program must be assigned to cores such that the resource needs of code sections closely matches resource availability at the assigned core. Determining this assignment manually is tedious, error prone, and significantly complicates software development. To solve this problem, this thesis describes a transparent and fully-automatic process called *phase-based tuning* which adapts an application to effectively utilize performance-asymmetric multicores. The basic idea behind this technique is to statically compute groups of program segments which are expected to behave similarly at runtime. Then, at runtime, the behavior of a few code segments is used to infer the behavior and preferred core assignment of all similar code segments with low overhead. Compared to the stock Linux scheduler, for systems asymmetric with respect to clock frequency, a 36% average process speedup is observed, while maintaining fairness and with negligible overheads.

A key component to phase-based tuning is grouping program segments with similar behavior. The importance of various similarity metrics are likely to differ for each target asymmetric multicore processor. Determining groups using too many metrics may result in a grouping that differentiates between program segments based on irrelevant properties for a target machine. Using too few metrics may cause relevant metrics to be ignored thereby considering segments with different behavior similar. Therefore, to solve this problem and enable phase-based tuning for a wide range of a performance-asymmetric multicores, this thesis also describes a new technique called *lazy grouping*. Lazy grouping statically (at compile and install times) groups program segments that are expected to have similar behavior. The basic idea is to use extensive

compile time analysis with intelligent install time (when the target system is known) group assignment. The accuracy of lazy grouping for a wide range of machines is shown to be more than 90% for nearly all target machines and asymmetric multicores.

### **CHAPTER 1. Introduction**

Increases in single processor performance through frequency scaling has hit a wall [66]. Improving performance for this class of processors is prohibitively expensive due to design complexity, space constraints, and heat dissipation [29]. Therefore, replicating cores has become commonplace in recent years in order to continue improving performance as suggested by Moore's law [29].

Many recent processor designs have been homogeneous multicore processors. These homogeneous designs have some drawbacks [4, 5, 31, 44, 53, 61]. Replicating fast complex cores results in fewer cores and thus less performance for highly parallel programs but good single-threaded performance. Replicating simpler less powerful cores results in improved performance for highly parallel programs, but reduced serial performance.

Amdahl's law states that the serial portion of the program limits the speedup achievable by parallelism [60]. Thus, recently researchers and vendors have advocated the need for heterogeneous multicore processors to achieve the best of both types of systems (high throughput for both parallel and sequential workloads) [4, 5, 31, 44, 53, 61]. A common trend is to have a few fast cores to improve serial performance, but many slow cores to achieve high parallel performance [31]. Other attractive options include specialized processors such as vector processors or GPUs to accelerate certain portions of execution [26, 39]. There is also a potential to eliminate excess hardware capabilities from certain cores in the system (e.g. dedicated floating point units, out-of-order execution, etc.) to use less power, reduce space, and decrease heat. Aside from improving throughput for multiple types of workloads, a major advantage is that heterogeneous multicore processors decrease power consumption and use less die space

compared to homogeneous multicores [44]. For these same reasons, they are also seen as a cost efficient alternative for supercomputing (especially for large data centers where power and heat are important concerns) [58].

Single-ISA performance-asymmetric multicore processors (AMPs) [4, 5, 31, 44, 53, 61] are an important class of these heterogeneous multicores. All cores in an AMP support the same instruction set, however, they are heterogeneous in terms of performance characteristics such as clock frequency, cache size, in-order vs. out-of-order execution, etc [31, 45, 61].

The technical contribution of this work is a hybrid (static and dynamic) program analysis and optimization technique called *phase-based tuning* for effectively utilizing AMPs. In this section, some of the major problems facing efficient use of AMPs are discussed. Then, an overview of phase-based tuning is given. Finally, benefits of phase-based tuning are outlined.

### 1.1 Problems Facing Efficient Use of AMPs

There are several problems that arise with the introduction of AMPs. First, application performance becomes unpredictable and scalability becomes increasingly difficult to ensure [6]. Additionally, programming languages are typically not designed to handle the increased complexity of heterogeneous multicore processors and programmers are not trained to understand their programs' behavior and hardware characteristics [16]. Furthermore, program behavior and/or system design may not be known statically. This necessitates new scheduling techniques to take full advantage of these new architectures [9].

In general, for effective utilization of AMPs, code sections of a program must be executed on cores such that the resource requirements of a section closely match the resources provided by the core [43, 53]. To match the resource requirements of a code section to the resources provided by the core, both must be known.

First, let us consider having the programmer manually perform such a mapping. This manual tuning has at least three problems.

- 1. First, the programmer must know the runtime characteristics of their code as well as the details of the underlying asymmetry. This increases the burden on the programmer. Further, both the resource requirements of processes and the resources provided by cores cannot be determined statically (code behavior may change with inputs, core characteristics may change between different platforms or if the workload on the system changes [49, 12]). This is troubling since utilization is heavily influenced by the accuracy of this knowledge [43, 53, 49].

- 2. Second, with multiple target AMPs this manual tuning must be carried out for each AMP, which can be costly, tedious, and error prone.

- 3. Third, as a result of this manual tuning a custom version must be created for each target AMP, which decreases re-usability and creates a maintenance problem. Further, the performance asymmetry present in the target AMP may not be known during development.

Next, consider an automated (or semi-automated) static technique. Such a technique has several problems. First, both the resource requirements of processes and the resources provided by cores cannot be determined statically (as discussed above). Also, like a manual approach, unknown target AMPs creates a significant problem.

Finally, consider a dynamic technique. At runtime, there is an advantage of being able to observe behavior of the program on each core type. Unfortunately, great care must be taken to avoid excessive overhead which can easily overshadow gains achieved by such a technique.

Effective utilization of AMPs is a major challenge. Finding techniques for automatic tuning is critical to address this challenge and to realize the full potential of AMPs [49].

### 1.2 Phase-based Tuning

To help solve the problem of effective utilization of AMPs, this thesis introduces a novel program analysis technique called *phase-based tuning* for matching resource requirements of

code sections to the resources provided by the cores of AMPs. Phase-based tuning builds on a well-known insight that programs exhibit phase behavior [35, 37, 51, 64, 73, 79, 82]. That is, programs go through phases of execution that show similar runtime characteristics compared to other phases [7, 18, 20, 21, 30, 75]. Based on this insight, phase-based tuning has two parts: static analysis which identifies likely *phase-transition points* (where runtime characteristics are likely to change) between code sections, and a lightweight dynamic analysis that determines section-to-core assignment by exploiting a program's phase behavior. The static analysis results are used to generate standalone binaries in which each phase-transition point is instrumented with a tiny code fragment for dynamic analysis. These fragments contain analysis code as well as phase information. This phase information reduces dynamic analysis costs by using the runtime behavior of previously executed sections to make future assignments.

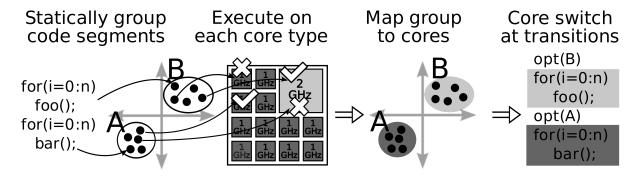

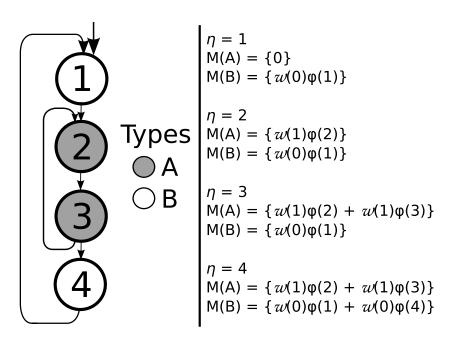

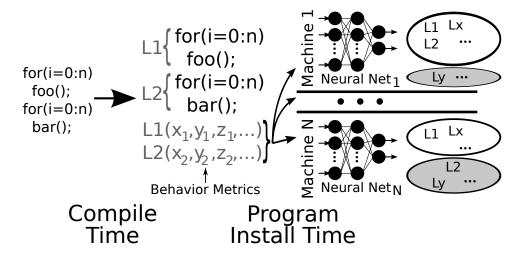

Figure 1.1 Overview of phase-based tuning. Segments are grouped statically. At runtime, a few segments from each group are run on each core type and their behavior is monitored. Using this observed behavior of only a few segments, entire groups are assigned to cores.

Figure 1.1 illustrates a simple overview of phase-based tuning. On the far left there is a simple function which contains two loops with different behaviors that are better suited for the different cores in the target AMP. Thus, these two loops are placed into separate *groups* (labeled A and B) which contain other code segments which should have similar resource requirements. Next, at runtime, a few program segments from each group are executed on each core type. After this, the expected best fit in terms of core type for the group is determined

(groups become shaded) and all segments in the group are mapped to this core type. Finally, the two loops considered initially now know which core they are likely to be best suited for and may make the decision to execute themselves on these cores. It is important to note that phase-based tuning did not require these loops to be executed on either core type.

Statically grouping similar program segments is a key component of phase-based tuning. Here, a brief overview of *lazy grouping*, a novel static (compile+install) similarity grouping technique is described. First, the limitations of a purely compile time grouping technique are shown. Then, lazy grouping, and how it solves these problems is discussed.

### 1.2.1 Compile Time Grouping and its Problems

A simple compile time technique could be used to statically group similar program segments. This technique could work as follows. First, behavior metrics (e.g., instruction latency, cache behavior) are statically computed for each program segment. For example, in Figure 1.1, each loop has two metrics calculated for it thus placing each loop somewhere in a two dimensional space. Using these metrics, all segments are grouped using the k-means clustering technique [55]. The figure shows two groups marked *A* and *B*. The goal is that all segments in a group have similar behavior.

For simple asymmetry such as difference in clock frequency, such compile time technique works remarkably well, however, as the variety of asymmetry increases, a more sophisticated approach is needed. For many different types of target machines, the analysis must compute metrics for several aspects of behavior (e.g. caching, instruction level parallelism, etc) and variations on each of these metrics (e.g. different cache sizes). Thus, there are many metrics to consider.

Such a compile time technique has no knowledge of the relevance of metrics for the target machines and thus will create the same groups for all machines. A metric (e.g. instruction level parallelism) may only be relevant for a subset of target machines, however, compile time grouping will differentiate based on this metric for all machines. Thus, it will likely create sep-

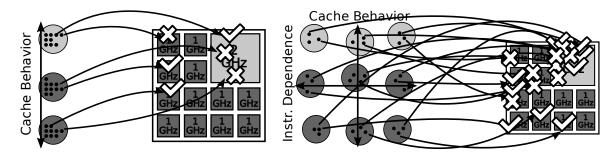

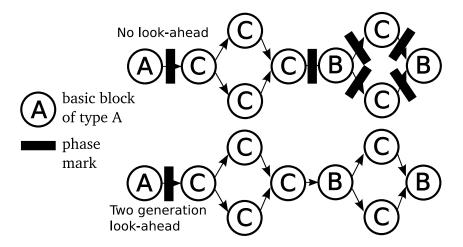

arate groups which do not differ on many target machines. Consider the example in Figure 1.2. On the left, a single metric relevant for this machine is used resulting in three groups. On the right, an additional metric is added which is not strongly relevant for this machine. In this case, this extra dimension hurts rather than helps. Total groups were tripled but those which vary only in this dimension are similar. Such differentiation may cause excessive overhead for phase-based tuning.

Figure 1.2 Left: Runtime behavior of phase-based tuning using one similarity metric. Right: The same process but with two metrics. The figure shows that with more metrics, benefits likely decrease.

Adding metrics is desirable in order to tackle more diverse types of AMPs. However, adding metrics into the existing approach creates too many groups, many of which may not differ. Thus, a new technique is needed to handle a significant amount of metrics but produce few, accurate groups.

### **1.2.2** Lazy Grouping and its Benefits

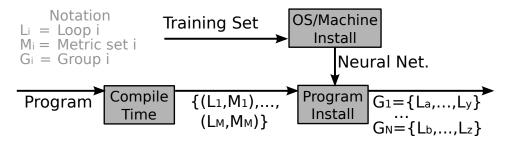

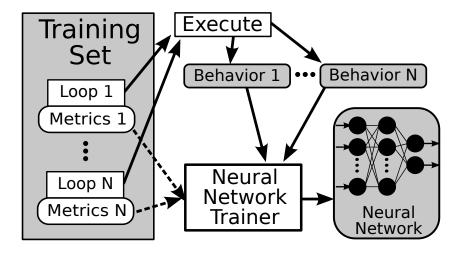

To address these problems, a novel technique is presented for accurately grouping similar program segments without running them. The basic idea is as follows. At compile time, several program behavior metrics are statically computed. At *program install time* (when the program is put on the target machine) code segments are assigned to groups using a neural network which takes as input the similarity metrics computed at compile time. This neural network is created and trained at *OS or machine install time* once for each machine. This approach

is called "lazy" since it waits till the target machine is known to compute the grouping rather than doing so immediately after metrics are computed at compile time.

Lazy grouping has several benefits. First, it is able to tackle the problem of computing program segment similarity for a wide variety of target machines since grouping is delayed until install time. Thus problems caused by an unknown target machine are avoided. Second, typical use of the technique (program install time) is very efficient since most of the overhead occurs at compile time and OS/machine install time. Third, phase-based tuning is more efficient (than when a purely compile time approach is used) for three reasons. First, the optimal number of output groups (e.g. number of core types) may be specified while accuracy is maintained. Second, group distribution may be tuned, through neural network training, to fit the target AMPs core distribution. Third, phase-based tuning no longer needs to perform runtime monitoring and analysis since lazy groups have knowledge of the approximate behavior of the code segments in each group.

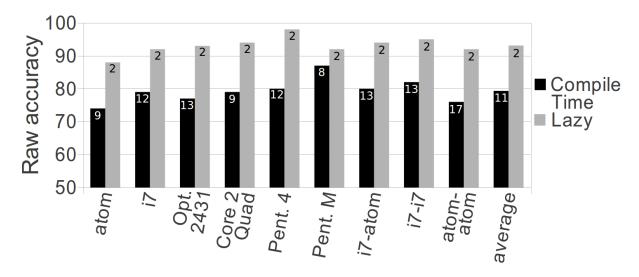

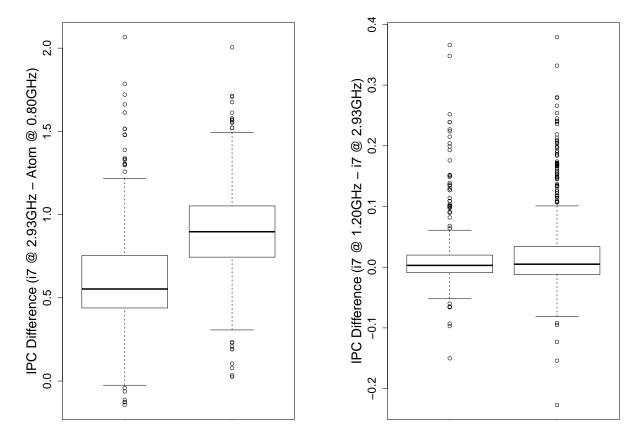

To evaluate lazy grouping, its accuracy with respect to single core program behavior as well as its use for AMPs is considered. This evaluation shows that lazy grouping is significantly more accurate than compile time grouping and requires fewer groups. Further, results show that lazy grouping is more than 90% accurate for nearly all target machines and AMPs tested. Finally, an evaluation of lazy grouping's impact on phase-based tuning is done. In this case, there is a 17% higher average process speedup when lazy grouping is used.

### 1.3 Benefits of Phase-based Tuning

Phase-based tuning has the following benefits:

• Fully Automatic: Since phase-based tuning determines core assignments automatically at runtime, the programmer need not be aware of the performance characteristics of the target platform or their application.

- Transparent Deployment: Programs are modified to contain their own analysis and core switching code. Thus, no operating system or compiler modification is needed.

Therefore, phase-based tuning can be utilized with minimal disruption in the build and deployment chain.

- Tune Once, Run Anywhere: The analysis and instrumentation makes no assumptions about the underlying AMP. Thus there is no need to create multiple versions for each target AMP. Also, by making no assumptions about the target AMP, interactions between multiple threads and processes are automatically handled.

- **Negligible Overhead:** It incurs less than 3% space overhead and less than 0.1% time overhead, i.e. it is useful for overhead conscious software and it is scalable.

- **Improved Utilization:** Phase-based tuning improves utilization of AMPs by reducing average process time by as much as 36% while maintaining fairness.

To evaluate the effectiveness of phase-based tuning, it was implemented as part of a custom binary static analysis and instrumentation framework and applied to workloads constructed from the SPEC CPU 2000 and 2006 benchmark suites which are standard for evaluating processors, memory and compilers. These workloads consist of a fixed number of benchmarks running simultaneously. These workloads, running on a simple AMP where clock frequencies differ, see as much as a 36% reduction in average process time while maintaining fairness and incurring negligible overheads.

### 1.4 Organization

The rest of this thesis is organized as follows. Chapter 2 describes the hybrid analysis and optimization technique called phase-based tuning for effectively utilizing AMPs. Next, Chapter 3 describes the static binary analysis and instrumentation framework used for the evaluation of phase-based tuning. Chapter 4 presents the experimental setup for evaluating phase-based

tuning and the results. Chapter 5 gives a brief discussion of relevant issues facing practical and future use of phase-based tuning. In Chapter 6, lazy grouping, a novel static behavior similarity grouping technique, is discussed. Next, Chapter 7 describes the experimental setup for evaluating the accuracy and effectiveness of lazy grouping and presents the evaluation results. Then, Chapter 8 describes related work. Finally, Chapter 9 discusses potential future work and Chapter 10 concludes.

### **CHAPTER 2.** Phase-based Tuning with Compile Time Grouping

In this chapter, phase-based tuning is described. The goal of phase-based tuning is to match resource requirements of code sections to the resources provided by the cores of a performance-asymmetric multicore processor.

The intuition behind phase-based tuning is the following. If static analysis can classify a program's execution into code sections and group these sections into clusters such that all sections in the same cluster are likely to exhibit similar runtime characteristics; then the actual runtime characteristics of a small number of representative sections in the cluster are likely to manifest the behavior of the entire cluster. Thus, the exhibited runtime characteristics of the representative sections can be used to determine the match between code sections in the cluster and cores without analyzing each section in the cluster.

Classifying a program's execution into sections and sections into clusters independent of the program's input, has several benefits. Most importantly, no development efforts for representative inputs are needed; and thread-to-core assignments for unanticipated use cases and varying architectures are automatically tackled.

Based on these intuitions, phase-based tuning works as follows. A static analysis is performed to identify phase-transition points. This analysis first divides a program's code into *sections* then classifies these sections into one or more *phase types*. The idea is that two sections with the same phase type are likely to exhibit similar runtime behavior characteristics. Third, the analysis identifies points in the program where the control flows [3] from a section of one phase type to a section with a different phase type. These points are called the phase-transition points.

Each phase-transition point is statically instrumented to insert a small code fragment which is called a *phase mark* $^{1}$ . A phase mark contains information about the phase type for the current section, code for dynamic performance analysis, and code for making core switching decisions.

At runtime, the dynamic analysis code in the phase marks analyzes the actual characteristics of a small number of representative sections of each phase type. These analysis results are used to determine a suitable core assignment for the phase type such that the resources provided by the core matches the expected resources for sections of that phase type. On determining a satisfactory assignment for a phase type, all future phase marks for that phase type reduce to simply making appropriate core switching decisions<sup>2</sup>. Thus, the actual characteristics of few sections of a given phase type are used as an approximation of the expected characteristics of all sections of that phase type. This allows phase-based tuning to significantly reduce runtime overhead and automatically tackle new architectures. The rest of this chapter describes components of phase-based tuning in detail.

### 2.1 Static Phase Transition Analysis

The aim of phase-based tunings static analysis is to determine points in the control-flow where behavior is likely to change, that is *phase-transition points*. The precision and the granularity of identifying such points is likely to determine the performance gains observed at runtime. To that end, the first step in this analysis is to detect similarity among basic blocks in the program and classify them into one or more phase types that are likely to exhibit similar runtime behavior. Then, three analysis techniques are examined for detecting and marking phase transitions with *phase marks*. The first is a basic block level analysis. The second builds upon this basic block analysis to analyze intervals [3]. The third also builds upon the basic block analysis to analyze loops inter-procedurally.

<sup>&</sup>lt;sup>1</sup>The idea of phase marking is similar to the work by Lau *et al.* [50], however, this technique does not use a program trace to determine phase marks and makes its selections based on a different criteria.

<sup>&</sup>lt;sup>2</sup> Huang *et al.* [38] show that basing processor adaptation on code sections (positional) rather than time (temporal) improves energy reduction techniques. Phase-based tuning also takes a positional approach.

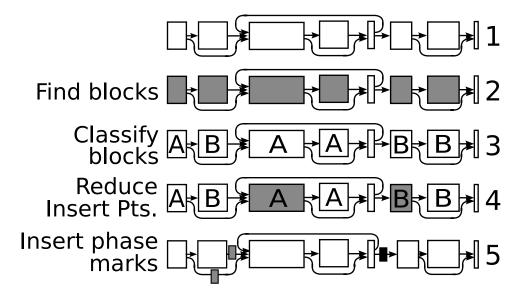

Figure 2.1 Overview of phase transition analysis

Figure 2.1 illustrates this process for a basic block level analysis. Step 1 represents the initial procedure. Blocks in the figure represent basic blocks and edges between them represent paths that may be taken at runtime. Step 2 finds the blocks which are larger than the threshold size (shaded). Next, step 3 finds the type for each block considered in the previous step. Then, the phase transition points are reduced using a lookahead, this is illustrated in step 4. Finally, step 5 shows the new control-flow graph for the procedure which now includes the phase transition marks.

In this section, first the analysis techniques for annotating control-flow graphs (CFGs) with types for all of these techniques are discussed. Next, how to use the annotated control-flow graphs to perform the phase transition marking is discussed.

#### 2.1.1 Static CFG Annotation

The three analysis techniques used to annotate a programs control-flow graph with type information are now discussed. First, the techniques used for basic block analysis are described. Then, this technique is expanded to include a technique for interval typing. Finally, an inter-procedural loop based technique is described.

This static analysis is performed using a custom framework for binary analysis and instrumentation that is described in Chapter 3. While there are limitations to constructing CFGs from a binary representation, since phase-based tuning does not require sound results (incorrect assumptions just result in code that may be less efficient), this technique can make many assumptions safely. For example, suppose part of a code segment has a branch or call with an unknown target. In the current implementation, code segments are typed while ignoring the missing target code's impact on the type. Another option is to skip typing this code segment. If the branch or call has several known potential targets, one could take the following approach. For each target, determine the type for the segment assuming this specific target is executed. If this type is the same for all potential targets, the segment receives this type. If different types are determined as the result of analyzing each different target, then look to see if a majority of the potential targets result in the same type. If they do, this most common type could be chosen, otherwise, the segment may be left untyped. If more precision is desired, a more sophisticated analysis may be used or information may be gathered from the source code.

#### 2.1.1.1 Attributed CFG Construction

The static analysis first divides a program into procedures  $(\mathcal{P})$  and each procedure  $p \in \mathcal{P}$  into basic blocks to construct the set of basic blocks  $(\mathcal{B})$  [3]. The classic definition of a basic block is used (that it is a section of code that has one entry point and one exit point with no jumps in between [3]). The analysis then assigns a type  $(\pi \in \Pi)$  to each basic block to construct the set of attributed basic blocks  $(\bar{\mathcal{B}} \subseteq \mathcal{B} \times \Pi)$ . The notion of type here is different from types in a program and does not necessarily reflect the concrete runtime behavior of the basic block. Rather it suggests similarity between expected behaviors of basic blocks that are given the same type. A strategy for assigning types to basic blocks statically is given in Section 2.1.3, however, other methods for classifying basic blocks can also be used.

Using the attributed basic blocks, attributed intra-procedural control-flow graphs for procedures are created. An attributed intra-procedural control-flow graph  $\mathcal{CFG}$  is  $\langle \mathcal{N}, \mathcal{E}, \eta_0 \rangle$ . Here,

$\mathcal{N}$ , the set of control-flow graph nodes is  $\bar{\mathcal{B}} \cup \mathcal{S}$ , where  $\mathcal{S}$  ranges over special nodes representing system calls and procedure invocations. The set of directed edges in the control-flow is defined as  $\mathcal{E} \subseteq \mathcal{N} \times \mathcal{N} \times \{b, f\}$ , where b, f represent backward and forward control-flow edges.  $\eta_0 \equiv (\beta, \pi)$  is a special block representing the entry point of the procedure, where  $\beta \in \mathcal{B}$  and  $\pi \in \Pi$ .

### 2.1.1.2 Summarizing Intervals

The goal of the intra-procedural interval [3] analysis is to summarize intervals into a single type. To perform the interval analysis, start with the attributed control-flow graph for each procedure created by the basic block analysis. Then use the basic block types to determine interval types.

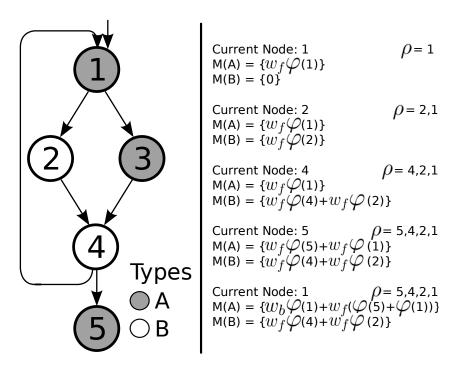

For each procedure, start by partitioning the attributed control-flow graph of the procedure into a unique set of *intervals* ( $\mathcal{I}$ ) using standard algorithms [3]. "An *interval* ( $i(\eta) \in \mathcal{I}$ ) corresponding to a node  $\eta \in \mathcal{N}$  is the maximal, single entry subgraph for which  $\eta$  is the entry node and in which all closed paths contain  $\eta$  [3, pp.6]." For each i, the analysis computes its dominant type (as defined in Figure 2.2) by doing a depth-first traversal of the interval starting with the entry node, while ignoring backward control-flow edges (marked with b) unless traversal gets stuck at a non-leaf node. The exit nodes of the interval represent the leaf nodes. This summarization algorithm is shown in Figure 2.2 and illustrated in Figure 2.1.1.2.

```

\begin{array}{l} \rho = \phi \\ \textbf{for all DFS(I) do} \\ \textbf{if } \eta \in \rho \textbf{ then} \\ M \oplus \{\pi \mapsto M(\pi) + w_b * \varphi(\eta)\} \\ \textbf{else} \\ M \oplus \{\pi \mapsto M(\pi) + w_f * \varphi(\eta)\} \\ \textbf{end if} \\ \rho = \eta + \rho \\ \text{return } \max(dom(M)) \\ \textbf{end for} \end{array}

```

Figure 2.2 Algorithm for interval summarization to find dominant type

Figure 2.3 Interval summarization illustration

During a depth-first traversal the analysis maintains a stack of control-flow nodes encountered thus far  $(\rho = \eta + \rho')$  with the entry node of the interval at the bottom of this stack and the currently visited node at the top of the stack. A type map for the interval  $(M : \Pi \mapsto \mathbb{R})$  is maintained. On visiting a control-flow node  $\eta$  in the interval, the type map M is changed to M' where M' is  $M \oplus \{\pi \mapsto M(\pi) + w_f * \varphi(\eta)\}$ . Here,  $\pi$  is the type of the control-flow node,  $w_f$  is the forward edge weight,  $\varphi$  maps nodes to node weights, and  $\oplus$  is the overriding operator for finite functions.

On reaching a control-flow node with an outgoing backward edge, if the backward edge has not previously been traversed, the target control-flow node  $(\eta')$  of the backward edge is computed. For each control-flow node  $\eta''$  from  $\eta'$  to  $\eta$  on the stack  $\rho$ , the type map M is changed to M' where M' is  $M \oplus \{\pi \mapsto M(\pi) + w_b * \varphi \eta\}$  and  $w_b$  is the backward edge weight. The values for  $w_f$  and  $w_b$  are heuristically decided, but intuitively it makes sense to have  $w_b$  greater than  $w_f$  (to give more weight to nodes in loops). The node weight function,

$\varphi: \mathcal{N} \mapsto \mathbb{R}$ , maps nodes to values based on a heuristic measure of the expected execution time of the block. Currently the number of instructions in the node is used as this measure.

On completion of the depth-first traversal, the dominant type of the interval is  $\pi$ , where  $\nexists \pi'.M(\pi') > M(\pi)$ . In case of a tie, a simple heuristic is used. Currently, the type with maximal number of control-flow nodes in the interval is used as a tiebreaker.

As a result of this process, the analysis obtains another control flow graph of the procedure where nodes are tuples of intervals and their types. To distinguish these from control-flow graphs of basic blocks, they are referred to as *attributed interval graphs*. It would be interesting to explore whether summarizing interval graphs again is useful [3], however, in this work only first-order intervals are considered. The initial intuition is that the value of applying n<sup>th</sup> order interval summarization will depend on the average size of procedures.

### 2.1.1.3 Summarizing Loops

The goal of the inter-procedural loop analysis is to summarize loops into a single type. The analysis starts with the attributed CFG for each procedure created by the basic block analysis. The analysis then uses the basic block types to determine loop types. A bottom-up typing is performed with respect to the call graph. In the case of indirect recursion, the analysis randomly chooses one procedure to analyze first then analyze all procedures again until a fixpoint is reached.

For each procedure, the analysis starts by partitioning the attributed CFG of the procedure into a unique set of  $loops(\mathcal{L})$  using standard algorithms [63]. For each loop,  $l \in \mathcal{L}$ , the analysis computes its dominant type starting with the inner-most loops. The analysis does a breadth-first traversal of the loop starting with the entry node, while ignoring backward edges. This algorithm is shown in Figure 2.5 and illustrated in Figure 2.4.

Throughout the loop traversal, a type map  $(M:\Pi\mapsto\mathbb{R})$  is maintained which maps types to weights. On visiting a control-flow node in the loop,  $\eta\in l$ , the type map M is changed to  $M'=M\oplus\{\pi\mapsto M(\pi)+w_n(\lambda)*\varphi(\eta)\}$ . Here,  $\pi$  is the type of the control-flow node  $\eta,w_n$

Figure 2.4 Loop summarization illustration

maps nodes to nesting level weights,  $\varphi$  maps nodes to node weights, and  $\oplus$  is the overriding operator for finite functions. Since loops are usually executed multiple times, nodes in nested loops should have more impact on the type of the overall loop. Thus, nodes which belong to inner loops are given a higher weight via the function  $w_n : \mathbb{N} \to \mathbb{R}$  which maps nesting levels to weights.

On completion of the breadth-first traversal, the dominant type of the loop l is  $\pi_l$ , where  $\nexists \pi$  s.t.  $M(\pi) > M(\pi_l)$ . In case of a tie, a simple heuristic is used (e.g. number of control-flow nodes). The analysis also has a *type strength*,  $\sigma$  which is simply the weight the type  $\pi_l$  over the sum of all other type weights  $(M(\pi_l)/\sum_{\pi \in dom(M)} M(\pi))$ . This strength is used for typing nested loops.

Suppose there is a loop l' which contains the current loop l. If both loops have the same type  $(\pi_{l'} = \pi_l)$ , it is not beneficial to incur the analysis and optimization code's overhead at each iteration of the outer loop. Instead, runtime analysis and optimization is performed before the outer loop, and eliminate any work done inside this loop. Thus, after the type for

the current loop, l, is determined, the analysis finds the type for the next largest nested loop, l'. If there is no such loop, then the analysis adds the current type information to the loop type map T. If the type of the nested loop (l') is the same as the current loop (l), then the analysis adds the current loop, l to the type map and remove the nested loop l'. If the types of the two loops differ, the analysis takes the type with the higher strength,  $\sigma$ , since it is more likely that the typing for such a loop is more accurate. Finally, there is a special condition (**else if**) to handle nesting where two disjoint loops, l' and l''', are nested inside a loop, l. In this case, the analysis types the loop l only if the two disjoint loops, l' and l''', have the same type which is also the same type as the outer loop l.

```

for all \eta \in BFS(l \in \mathcal{L}) do

\lambda := \left| \{ l' \in \mathcal{L} | l' \subset l \land \eta \in l' \} \right|

M \oplus \{\pi \mapsto M(\pi) + w_n(\lambda) * \varphi(\eta)\}\

end for

M(\pi_l) = \max_{\pi \in dom(M)} (M(\pi))

\sigma_l := M(\pi_l) / \sum_{\pi \in dom(M)} M(\pi)

if \exists l' \text{ s.t. } l' \subset l \land \nexists l'' \text{ s.t. } l' \subset l'' \subset l \land (\nexists l''' \text{ s.t. } l''' \subset l \land \nexists l'' \text{ s.t. } l''' \subset l) then

if (l', \pi_{l'}, \sigma_{l'}) \in T \land (\pi_{l'} = \pi_l \lor \sigma_{l'} < \sigma_l) then

T := T \cup \{(l, \pi_l, \sigma_l)\}

T := T \setminus \{(l', \pi_{l'}, \sigma_{l'})\}

end if

else if \exists l' s.t. l' \subset l \land \nexists l'' s.t. l' \subset l'' \subset l \land (\exists l''' s.t. l''' \subset l \land \nexists l'' s.t. l''' \subset l' \subset l) then

if (l', \pi_{l'}, \sigma_{l'}) \in T \land (l''', \pi_{l'''}, \sigma_{l'''}) \in T \land \pi_{l'} = \pi_{l'''} \land \pi_{l'} = \pi_l then

T := T \cup \{(l, \pi_l, \sigma_l)\}

T := T \setminus \{(l', \pi_{l'}, \sigma_{l'})\}

T := T \setminus \{(l''', \pi_{l'''}, \sigma_{l'''})\}

end if

else

T := T \cup \{(l, \pi_l, \sigma_l)\}

end if

```

Figure 2.5 Loop summarization to find dominant type. BFS ignores back edges

As a result of this process, the analysis obtains another control flow graph of the procedure where nodes are tuples of loops and their types. To distinguish these from control-flow graphs of basic blocks, they are referred to as *attributed loop graphs*.

#### 2.1.1.4 Phase Transitions

Once the analysis has determined types for sections (blocks, intervals, or loops) of the program's CFG, the analysis computes the phase transition points. Recall that a phase-transition point is a point in the program where runtime characteristics are likely to change. Since sections of code with the same type should have approximately similar behavior, phase-based tuning assumes that program behavior is likely to change when control flows from one type to another. The next section describes the techniques for marking these points in the application.

#### 2.1.2 Phase Transition Marking

Once the phase transitions are determined, phase marks are statically inserted in the binary to produce a standalone binary with phase information and dynamic analysis code fragments. These code fragments also handle the core switching. By instrumenting binaries, the need for compiler modifications is eliminated. Furthermore, by using standard techniques for core switching, no OS modification is required. Several variations of phase transition marking have been considered that are classified into three kinds based on whether it operates on the attributed control-flow graphs, the attributed interval graphs, or the attributed loop graphs. In all cases, phase marks are placed at the phase transitions.

### 2.1.2.1 Adding Phase Marks to Attributed CFG

The first class of methods all consider a section to be a basic block  $(\bar{\beta})$  in the attributed CFG  $(\mathcal{CFG})$ . The advantage of using basic blocks is that execution of a single instruction in a block implies that all instructions in the block will execute (and the same number of times). This means that the phase type for the section is likely to be accurate and the same as the corresponding basic block type  $\pi \in \Pi$ , where  $\bar{\beta}$  is  $(\beta,\pi)$ . This naïve phase marking technique marks all edges in the attribute CFG where the source and the target sections have different phase types. As is evident, this technique has a problem. The average basic block size is small (tens of instructions in the SPEC benchmarks). Phase marking at this granularity could

result in frequent core switches overshadowing any performance benefit. To avoid this, two techniques are used.

The first technique eliminates small sections of code. In other words, if the section has less than a threshold weight as defined by a node weight function,  $\varphi : \mathcal{N} \mapsto \mathbb{R}$ . This eliminates core switching for very small blocks of code. For example, a basic block may consist of a single instruction. Clearly it would not be cost effective to initiate a core switch so that a single instruction can execute more efficiently. Basic blocks are usually in the tens of instruction and often smaller. Even at this size the benefit of switching cores probably does not outweigh the cost of switching cores. So, better points for phase marks still must be chosen. The second technique addresses this problem by only marking a section if at least a fixed percentage of its successors up to a fixed depth have the same type (illustrated in Figure 2.7).

### 2.1.2.2 Lookahead based Phase Marking

This technique is presented in Figure 2.6 and illustrated in Figure 2.7. The intuition is the following. If the successors of a section have the same type, it is more likely that a core switch will be worth its cost. For small loops, when enough successors are considered, nodes begin to repeat. Thus, if a loop contains predominately one type of blocks, the technique can simply make a core switch before the loop begins. Furthermore, this technique serves to reduce the number of phase marks in a program. Since adding each phase mark translates to adding a small number of instructions to the footprint of the binary and the control-flow path, both the time overhead and space overhead of the technique will be reduced and will hopefully not eliminate much of its benefit.

### 2.1.2.3 Adding Phase Marks to Attributed Interval Graphs

The second class of methods consider sections to be intervals in the attributed interval graph. Using intervals for phase marking enables us to look at the program at a more coarse granularity than basic blocks. Even with  $1^{st}$  order interval graphs, the intervals frequently

```

Processed Nodes, \mathcal{D}

Get Successors to Depth, S : (\eta, \mathbb{N}) \to \{\mathcal{B}\}\

Lookahead depth: d, Successor threshold: e

Same type count: c, Total count: t

Grouping \mathcal{U} = \{ \pi \mapsto N | \forall \pi \in \Pi \}

Node list N = \{\nu\}.

for all p \in \mathcal{P} do

\mathcal{D} = \phi

for all (\eta, \pi) \in (\bar{\mathcal{B}} \setminus \mathcal{D}) do

c \leftarrow 0, t \leftarrow 0, S = \mathcal{S}(\eta, d)

for all (\eta', \pi') \in S do

if \pi' = \pi then

c \leftarrow c + 1

end if

t \leftarrow t + 1

end for

if c/t \ge e then

\mathcal{U} \oplus \{\pi \mapsto \mathcal{U}(\pi) \cup \{\eta\}

\mathcal{D} = \mathcal{D} \cup \{\eta\} \cup S

end if

end for

end for

```

Figure 2.6 Lookahead based phase marking

capture small loops. This is clearly advantageous for adding phase marks since it is not desired to have a core switch within a small loop because this would most likely result in far too frequent core switches. The disadvantage is that interval summarization to obtain dominant types introduces imprecision in the phase type information. As a result, statically computed dominant type may not to be actual exhibited type for the interval based on which instructions in the interval are executed and how many times they are executed.

#### 2.1.2.4 Adding Phase Marks to Attributed Loop Graphs

The third class of methods consider a section to be loops in the attributed loop graph. Using loops for phase marking has even more advantages than using intervals. Not only does it allow inserting outside of loops, it also allows better handling of nested loops by frequently

Figure 2.7 Lookahead based reduction of phase marks

eliminating phase-marks within loop iterations. This is an even more coarse view of the program than the interval based technique. Furthermore, since it is an inter-procedural analysis, transitions across function calls are handled. Just like interval typing, loop typing introduces some imprecision in the type information.

#### 2.1.3 Determining block types

This chapter and its corresponding evaluation focuses more on developing and evaluating (1) the various techniques and granularity for determining and marking phase transitions and (2) the dynamic analysis and optimization techniques. As a proof-of-concept, a simple static analysis for determining types of basic blocks is used.

This analysis involves looking at a combination of instruction types as well as a rough estimate of cache behavior (computation based on reuse distances [11]). Information describing these two components are used to place blocks in a two dimensional space. The blocks are then grouped using the k-means clustering algorithm [55].

The accuracy of this approach has been evaluated in combination with the loop based clustering technique as follows. Blocks are classified into groups by using this simple analysis. Next, the dominant type of the loops are determined using the algorithm from Section 2.1.1. This loop typing is compared with the actual observed behavior of the loops.

In summary, experimentation shows that this technique miss-classifies only about 15% of loops. As the results show in Chapter 4, this is accurate enough for phase-based tuning. A more precise analysis (such as lazy grouping which is described in Chapter 6) may simply be substituted to improve overall performance.

### 2.2 Dynamic Analysis and Tuning

After phase transition marking is complete, the program binary contains phase marks at appropriate points in the control flow. These phase marks contain an executable part and the phase type for the current section. The executable part contains code for dynamic performance analysis and section-to-core assignment. During the static analysis, this dynamic analysis code is customized according to the phase type of the section to reduce overhead.

The code in the phase mark either makes use of previous analysis to make its choice of core types or it observes the behavior of the code section. A variety of analysis policies could be used and any desirable metric for determining performance could be used as well. In this section, the lightweight analysis and similarity metric used for evaluating phase-based tuning is described.

For this case, the code for a phase mark serves two purposes: First, during a transition between different phase types, a core switch is initiated. The target core is the core previously determined to be a good fit for this phase type. Second, if a good fit for the current phase type has not been determined, the current section is monitored to analyze its performance characteristics. The decision about the preferred core for that phase type is made by monitoring representative sections from the cluster of sections that have the same phase type. By performing this analysis at runtime, phase-based tuning does not require the programmer to have any knowledge of the target architecture. Furthermore, the asymmetry is determined at runtime removing the need for multiple program versions customized for each target architecture. Since the static technique ensures that sections in the same cluster are likely to exhibit similar

runtime behavior, the assignment determined by just monitoring few representative sections will be valid for most sections in the same cluster. Thus, monitoring all sections will not be necessary. This helps to reduce the dynamic overhead of phase-based tuning.

For analyzing the performance of a section, instructions per cycle (IPC) is measured (similar to [81, 9]). IPC correlates to throughput and utilization of AMPs. For example, cores with a higher clock frequency can efficiently process arithmetic instructions whereas cores with a lower frequency will waste fewer cycles during stalls (e.g. cache miss). IPC is monitored using hardware performance counters prevalent in modern processors. The preferred core assignment is determined by comparing the observed IPC for each core type.

The technique for determining core assignment is shown in Figure 2.8. The intuition is that cores which execute code most efficiently will waste fewer clock cycles resulting in higher observed IPC. Since such cores are more efficient, they will be in higher contention. Thus, the algorithm picks a core that improves efficiency but aims to not overload the efficient cores.

```

select(\pi, \delta): best core for phase type \pi, with threshold \delta

C := \{c_0, c_1, \dots, c_n\} \text{ (set of cores)}

Sort C s.t. i > j \Rightarrow f(c_i, \pi) > f(c_j, \pi).

f(c_i, \pi) \text{ - the actual measured IPC of block type } \pi \text{ on core } c_i.

d \leftarrow c_0

for all c_i \in C \setminus \{c_n\} do

\theta = f(c_{i+1}, \pi) - f(c_i, \pi)

if \theta > \delta \land f(c_{i+1}, \pi) > f(d, \pi) then

d \leftarrow c_{i+1}

end if

end for

\text{return } d

```

Figure 2.8 Algorithm for expected optimal core assignment for n cores

This algorithm first sorts the observed behavior on each core and sets the preferred core to the first in the list. Then, the algorithm steps though the sorted list of observed behaviors. If the difference between the current and previous core's behavior is above some threshold, the preferred core is set to the current core. The intuition is that when the difference is above

the threshold, executing on the efficient core will save enough cycles to justify taking the space on the more efficient core. By doing the performance analysis at runtime, this algorithm for computing the preferred core assignment *does not require knowledge of the program or underlying architecture*.

### **CHAPTER 3.** Analysis and Instrumentation Framework

To evaluate the ideas in this thesis, a custom static binary analysis and instrumentation framework was developed. In this chapter, a brief overview of this framework is given.

### 3.1 Disassembly

At the lowest level, the tool uses code and libraries from GNU BinUtils to translate programs from binary to machine opcodes and operands. Next, a custom analysis converts this assembly like representation to an object oriented representation of the program.

First, addresses must be converted to labels. That is, instead of knowing that an instruction may jump to a specific address, the tool must know what instruction this address refers to. Consider the small example in Figure 3.1. On the left side of this figure, we have the unprocessed assembly representation of the program. On line 4, there is a conditional jump to the address corresponding to the instruction on line 2. The same code after translation is shown on the right side of the figure. The figure shows that now, the conditional jump operand is a new label instead of an address. Also, the target instruction now has a label associated with it.

```

1...

2 add $0x1, %eax

; at address 0x804896ab

3...

4 jne 0x804896ab

5...

1 ...

2 newLabel1: add $0x1, %eax

3 ...

4 jne $newLabel1

5 ...

```

Figure 3.1 Conversion from address to labels. The left side shows a few instructions before conversion. The right shows the same instructions after conversion.

The tool must also correctly lay out the data sections (e.g. .rodata, .data, and .bss) including translating address values which occur in these data sections (.rodata and .data) and special symbols which also occur in these sections (e.g. stderr, stdout, stdin).

This representation is capable of being output as assembly code which is able to be assembled (i.e. converted back to a binary) by a standard assembler. However, the main reason behind this representation is to enable analysis and instrumentation of the program.

### 3.2 Analysis

The largest and most complex components of this framework are the various static analysis techniques. An overview of each of these components is now described.

### 3.2.1 Control Flow Analysis

The tool includes a range of control flow analysis techniques including intra-procedural analyses for finding basic blocks and intervals. Further the tool can identify various control structures (e.g. while loops, do-while loops, if-then, and if-then-else) and, if desired, graphically present these structures [77]. The targets of calls are also determined in order to perform inter-procedural loop analysis as is used for phase-based tuning (and other static analysis described later).

### 3.2.2 Abstract Interpretation

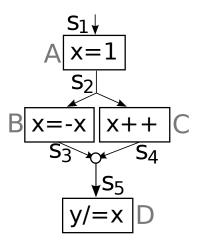

Abstract interpretation is a sound static program analysis framework for analyzing programs with respect to all possible program paths [19].

For example, the analysis may choose to analyze a property such as the sign of values contained by variables. Consider the example in Figure 3.2. The analysis starts by analyzing the first block, A, resulting in the state  $S_2$  that contains the knowledge that x is positive. Next, the analysis reaches the branch (in this case an if-then-else structure). Since the analysis knows

Figure 3.2 Example of simple abstract interpretation based analysis for variable sign.

that the sign of the variable x is positive each branch is analyzed with this information. For the left path (block B) the sign is flipped (x becomes negative). So, state  $S_3$  knows that x will be negative at this point. For the right path (block C), x is incremented. Since addition of two positive numbers (1 and x) results in another positive number, x remains positive for this path. So, state  $S_4$  knows that x will be positive at this point. Next, the analysis needs to analyze the next block, x no analyze this block, an input state is needed. To create this input state, the states x and x (the results for each potential path) must be merged or "joined". One case says that x is negative and the other says it is positive. Thus the resulting joined state x says that x may be either positive or negative (or "top" may be used, which means unknown).

This tool contains an abstract interpretation framework for analyzing both sequential and parallel programs. To implement such an analysis, one simply creates their analysis class inheriting from a base "Abstraction" class. Then, the user must only implement a few simple functions, "step" which defines how an individual instruction is analyzed, "join" which defines how two combine to states, and "equals", "copy", and "destruct" methods which have the standard meaning. For analyzing parallel programs, a "parallelCombine" method must also be defined which handles merging the results from two threads.

On top of this framework, several specific analyses are provided. This includes analysis for multi-level cache behavior and cache coherency behavior. Analysis for ILP and cache

behavior based on reuse distance [11] (described later) are also provided which are similar to the abstract interpretation based analyses, but do not guarantee soundness.

### 3.3 Instrumentation

The tool also has the ability to instrument (or modify) the input program. That is, at a point on the control flow path (assuming enough information is available) user supplied code may be added.

The main goal of this feature is to output programs that execute efficiently. This is a major goal since low overhead of instrumentation is crucial to reduce the overhead of phasemarks for phase-based tuning. Compared to a similar static instrumentation tool, ATOM [80], binaries instrumented with this tool execute 10 times faster<sup>1</sup>. This is because this tool uses a binary instrumentation strategy that is finely tuned for specific optimizions compared to that of a general strategy used by ATOM. Further, the tool ignores instrumentation for cases where instrumentation is especially difficult due to insufficient static information.

Instrumentation occurs as follows. The user writes their own (or uses an existing) tool that chooses points for insertion (similar to ATOM [80] or Pin [54]). Consider the input program on the left side of Figure 3.3. Suppose the user wants to insert some code before the second instruction.

For each such insertion point, the user specifies a function name to insert. This function must exist in a user supplied binary file. Though each piece of code to be inserted is contained in a function the entire function is not inserted into the resulting binary. The tool inserts the body of this function along with the necessary context saving and restoring before and after the inserted code. On the right side of the figure (the output program) the code to be inserted has been added (toward the bottom) along with the necessary context saving and restoring code around it.

<sup>&</sup>lt;sup>1</sup>These experiments were done by inserting code before every basic block for SPEC CPU2000 benchmarks.

```

1 0x80488800: mov %eax,%edx

2 0x80488802: jmp $newLabell

3 0x80488806: nop

4 0x80488807: lea (%edx,%eax,1),%eax

5 ...

6 newLabell:

7; code to save context

8; insert function

9; code to restore context

10 mov 0xefla2fb3,%eax

11 jmp 0x80488807

```

Figure 3.3 Example of binary instrumentation (idea based on fast break-points [41]). Left: input program. Desired insertion point is before the second instruction. Right: output program. Instructions from the input program are shaded. The second instruction was replaced with padding and a jump to the inserted code plus the replaced instruction.

Now, control flow must be modified to reach this new code. Also, in doing so, the tool must not "break" indirect branches which occur in the program being modified. The technique used for solving this problem is similar to the idea of fast break-points [41]. Recall that the user wanted to insert the code before the second instruction. Notice in the figure that this instruction has been relocated (original instructions are shaded). In its original place, a jump instruction is inserted as well as padding to make sure that the modified code takes up the same space (so that indirect branches still target the correct instruction). This jump target goes to the context save code which occurs before the inserted function code. Additionally, after the context restore code (which is after the inserted function code), the relocated instruction and another jump are inserted. This jump returns back to the point after the relocated instruction. If desired, call/return could be used instead of jumps and code duplication to potentially improve cache behavior and space overhead. However, this has the disadvantage of being unable to optimize the inserted code based on the "caller".

By analyzing and instrumenting binaries rather than source code, compiler modification is not required and the analysis techniques are applicable to any binary rather than a single language or set of languages.

### **CHAPTER 4.** Evaluation of Phase-based Tuning

The aim of this chapter is to evaluate the five claims made in Chapter 1 regarding phase-based tuning. First, it was claimed that phase-based tuning requires no knowledge of program behavior or performance asymmetry. Phase-based tuning is completely automatic and requires no input from the programmer. In these experiments, workloads are generated randomly and without any knowledge of behavior of the benchmarks. Second, it was claimed that the technique allows for transparent deployment. Since the analysis and instrumentation framework operates on binaries, no modification to compilers is necessary. Furthermore, since standard techniques are used for switching cores, no OS modifications are necessary. For example, in these experiments, the standard build scripts and compilers for the SPEC CPU benchmarks are used with an unmodified Linux OS. Third, it was claimed that with phase-based tuning one can "tune once and run anywhere". The static analysis makes no assumptions about the underlying asymmetry. Since performance analysis and section-to-core assignment are done dynamically, the same instrumented applications may be run on varying asymmetric systems. The final two claims are those related to performance: negligible overhead and improved utilization. In the rest of this chapter, experimental results are used to evaluate these two claims.

First, it is shown that phase-based tuning has low overhead, second, that phase-based tuning significantly improves the throughput of processes compared to standard Linux scheduler, and third that it maintains fairness among processes compared to the standard Linux scheduler. Finally, techniques are compared to show how different variations are applicable for various scheduling goals.

### 4.1 Experimental Setup

This section describes the experimental setup including both hardware and software platforms. It is also discussed how workloads were constructed for these experiments.

### 4.1.1 System Setup

The system consists of an AMP with 4 cores. This setup uses an Intel Core 2 Quad processor with a clock frequency of  $2.4 \, \text{GHz}$ . To create an asymmetric system, two cores underclocked to  $1.6 \, \text{GHz}$ . There are two L2 caches shared by two cores each. The cores running at the same frequency share an L2 cache. An unmodified Linux 2.6.22 kernel (which uses the O(1) scheduler) is used with standard compilers. Thus, the transparent deployment benefit of phase-based tuning is demonstrated.

There are two main benefits of using a physical system instead of a simulated system. First, porting the implementation to another system is trivial since it does not require any modifications to the standard Linux kernel. Second, phase-based tuning is analyzed in a realistic setting. Others have argued that results gathered through simulation may be inaccurate [57]. This is because all aspects of the system are not considered. Therefore, a full system simulator is desired. This setup is limited in hardware configurations to test. However, this platform is sufficient to show the utility of phase-based tuning.

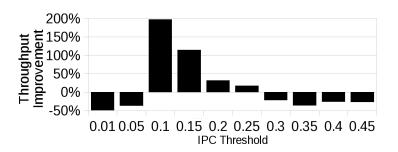

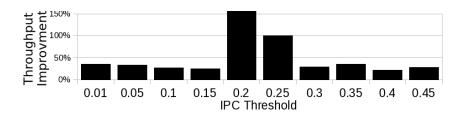

The perfmon2 monitoring interface [25] is used to measure the throughput of workloads. For evaluation purposes, to determine basic block types for the static analysis with little to no error, an execution profile from each core is used. Using the observed IPC, basic blocks are assigned types. The *difference* in IPC between the core types is compared to an *IPC threshold* to determine the typing for basic blocks.

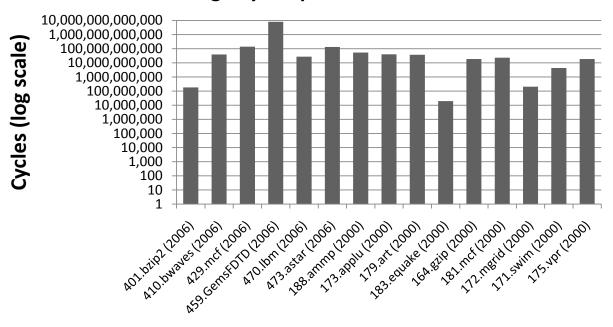

#### 4.1.2 Workload Construction

Many systems receive a nearly constant feed of jobs to run [10]. Improving the overall throughput of such a system will increase the amount of jobs the machine can complete in an interval of time. This increase will in turn enable the system to handle larger workload sizes. Phase-based tuning is targeting these systems, with maximizing throughput as its key objective. Similar to Kumar et al. [45] and Becchi et al. [9] the workloads range in size from 18 to 84 randomly selected benchmarks from the SPEC CPU 2000 and 2006 benchmark suites. For example, when testing a workload of size 18 there are 18 benchmarks running simultaneously. Such a workload is referred to as having 18 slots for benchmarks. Like Kumar et al. [45] the system receives jobs periodically, except rather than jobs arriving randomly, workloads maintain a constant number of running jobs. To achieve this constant workload size, upon completion of a benchmark, another benchmark is immediately started. If one were to simply restart the same benchmark upon completion, the same benchmarks may continuously complete if the technique favors a single type of benchmark. Thus, a job queue is maintained for each workload slot. That is, for a workload of size 18 then there are 18 queues (one for each slot in the workload). These 18 queues are each created individually from randomly selected benchmarks from the benchmark suites. When a workload is started, the first benchmark in each queue is run. Upon completion of any process in a queue, the next job in the queue is immediately started. When comparing two techniques, the same queues were used for each experiment. This ensures more accurate capture of the behavior of an actual system.

# 4.2 Space and Time Overhead

Statically, phase marks (consisting of data and code) are inserted in the program to enable phase-based tuning. Since insertion of large chunks of code may destroy locality in the instruction cache, low space overhead is desired. This section first describes the overhead in terms of the increase in binary size caused by insertion of phase marks. Also, a phase mark's

execution time is added to the execution of the original program. Thus, it must be ensured that the overhead does not overshadow the gains achieved by phase-based tuning. Therefore, the time overhead is described in terms of increase in execution time over the uninstrumented version. Finally, the average number of cycles per core switch is observed for the benchmarks (this can be thought of as the average cycles between core switches rather than the cost of core switch in cycles).

### 4.2.1 Space Overhead

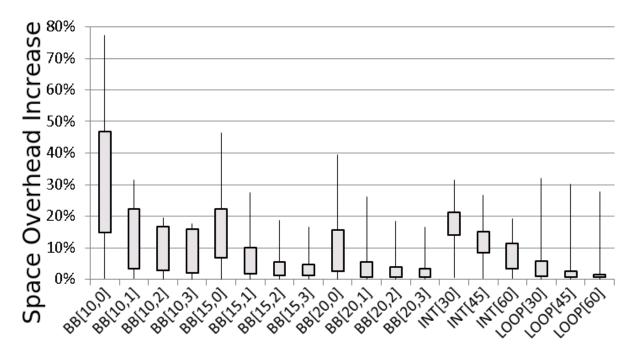

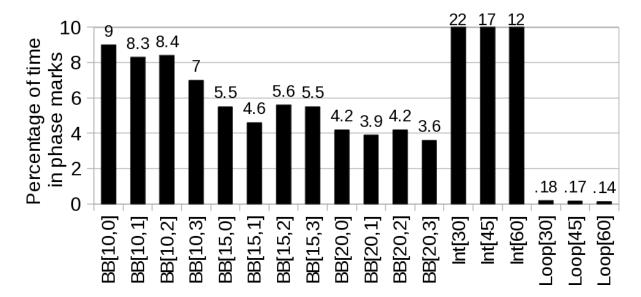

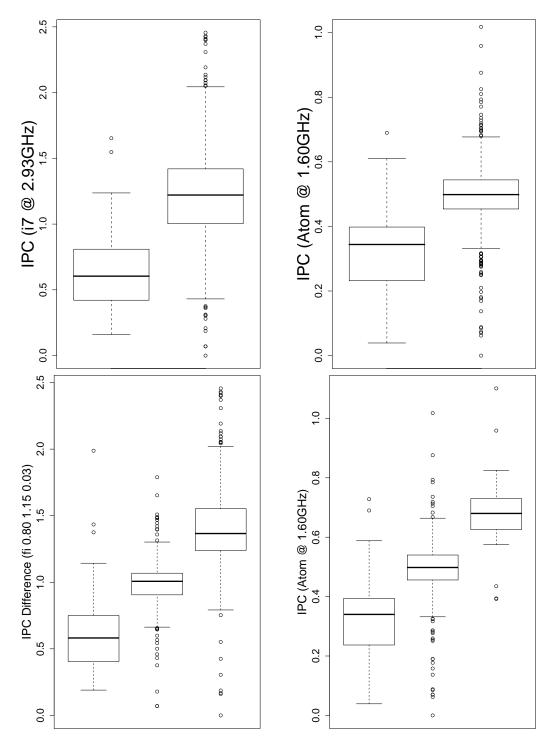

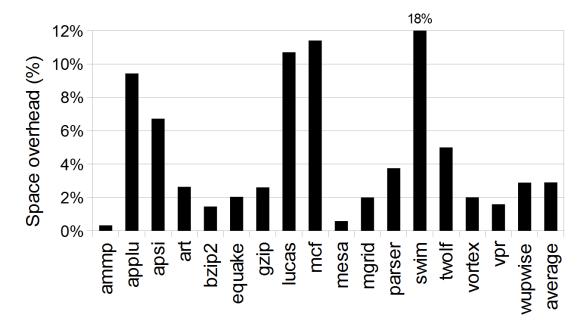

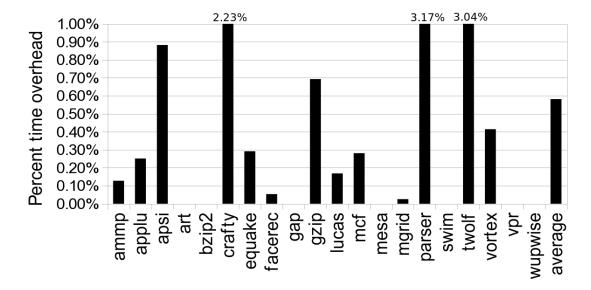

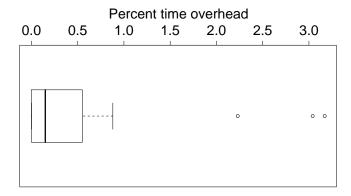

To measure space overhead, the sizes of the original and modified binaries are compared for variations of phase-based tuning. Table 4.1 shows summary statistics and Figure 4.1 shows a box plot for the measurements taken from the benchmarks in the SPEC CPU 2000 and 2006 benchmark suites. The box represents the two inner quartiles and the line extends to the minimum and maximum points. These results are presented in terms of what percentage of the instrumented application is made up of phase marks. The trends are expected. As the minimum size increases, space overhead decreases. Similarly, as lookahead depth increases, space overhead generally decreases. For individual programs this is not always the case because by adding another depth of lookahead, the percentage of blocks belonging to the same type may be pushed over the threshold causing another insertion point.

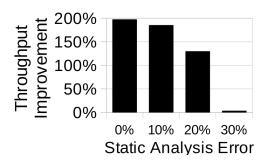

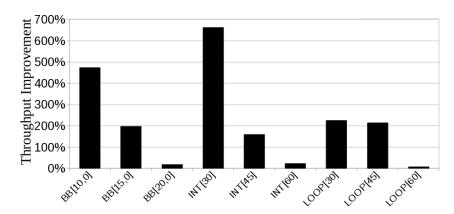

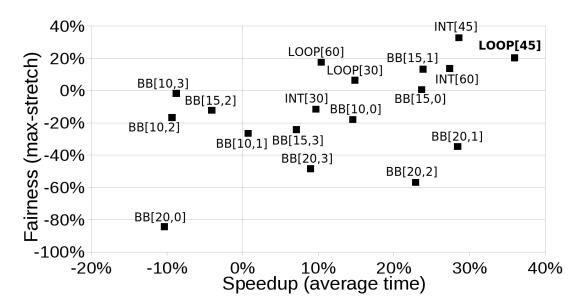

These results confirmed the intuition that less phase marks will be inserted for larger minimum sizes and lookahead depths. The results for interval graph-based phase marking are interesting in that they show significantly large increase in binary size. This is primarily because interval summarization results in the grouping of smaller basic blocks into intervals creating more sections above the instruction size threshold. The trends in space overhead offer insight into trends in time overhead.