# University of South Carolina **Scholar Commons**

Theses and Dissertations

1-1-2013

## PLC Code Vulnerabilities Through SCADA Systems

Sidney E. Valentine, Jr. *University of South Carolina*

Follow this and additional works at: http://scholarcommons.sc.edu/etd

#### Recommended Citation

Valentine, Jr., S. E. (2013). *PLC Code Vulnerabilities Through SCADA Systems*. (Doctoral dissertation). Retrieved from http://scholarcommons.sc.edu/etd/803

This Open Access Dissertation is brought to you for free and open access by Scholar Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact SCHOLARC@mailbox.sc.edu.

#### PLC CODE VULNERABILITIES THROUGH SCADA SYSTEMS

By

#### Sidney E Valentine

Bachelor of Science West Virginia University Institute of Technology 1995 Master of Science The University of South Carolina 2000

Submitted in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy in

Computer Science and Engineering

College of Engineering and Computing

University of South Carolina

2013

#### Accepted by:

Dr. Csilla Farkas, Major Professor

Dr. Manton Matthews, Committee Member

Dr. John Bowles, Committee Member

Dr. Wenyuan Xu, Committee Member

Dr. Herbert Ginn, Committee Member

Dr. Lacy Ford, Vice Provost and Dean of Graduate Studies

© Copyright by Sidney E Valentine, 2013 All Rights Reserved.

#### **DEDICATION**

I would like to dedicate this work to my wife Amanda, my son Jake and my parents Sid and Ruth Valentine. To my wife and son, you have helped me more in this endeavor than you will ever know. I appreciate the patience and support that each of you have shown in allowing me to pursue this dream. It takes a strong support system to be able to contend with continual hurdles and still come out successful on the other side. Without the both of you, I don't know that this would have been possible.

To mom and dad, it is through your guidance, throughout my life, that has shown me how to continuously persevere, never stop reaching for my goals and succeed in spite of the odds. You have molded me into the person that I am today, and for that I will always be thankful.

#### ACKNOWLEDGMENTS

I would like to thank my advisor, Dr. Csilla Farkas, for allowing me the opportunity to pursue this research and providing countless hours of assistance and guidance. I am truly grateful to have had the opportunity to work with you, as well as learn from you, throughout my graduate studies. Through our time together you have taught me how to be a better researcher and writer; and for that I will always be thankful. I look forward to our collaborations in the future and the continued development of this, and many other, projects. As I take this next step in my professional career, I take it not only with you as a colleague, but as a friend as well.

I would like to thank Dr. Manton Matthews for all of his help from the time I began this journey, until its completion.

I would like to thank Dr. John Bowles, Dr. Wenyuan Xu and Dr. Herbert Ginn for their support through involvement in my dissertation committee. I realize that a dissertation committee takes extensive time and effort, and I truly appreciate all of your willingness to serve.

I would like to thank Mr. Jyron Baxter, through his assistance and 'code development mind' we were able to turn the Static Analysis Tool into a tangible object. I am thankful that I had the opportunity to work with you and am honored to call you a colleague and a friend. I look forward to working with you in the future, and am anxious to see what the future of the Static Analysis Tool holds.

Finally, I would like to thank Randi Baldwin, Barb Ulrich, Jewell Rodgers and Sherri Altizer for their assistance in helping me 'take care of the details' even when that needed to be accomplished from three states away.

#### Abstract

Supervisory Control and Data Acquisition (SCADA) systems are widely used in automated manufacturing and in all areas of our nation's infrastructure. Applications range from chemical processes and water treatment facilities to oil and gas production and electric power generation and distribution. Current research on SCADA system security focuses on the primary SCADA components and targets network centric attacks. Security risks via attacks against the peripheral devices such as the Programmable Logic Controllers (PLCs) have not been sufficiently addressed. Our research results address the need to develop PLC applications that are correct, safe and secure. This research provides an analysis of software safety and security threats. We develop countermeasures that are compatible with the existing PLC technologies. We study both intentional and unintentional software errors and propose

• Develop a taxonomy of software errors and attacks in ladder logic

methods to prevent them. The main contributions of this dissertation are:

- Model ladder logic vulnerabilities

- Develop security design patterns to avoid software vulnerabilities and incorrect practices

- Implement a proof of concept static analysis tool which detects the vulnerabilities in the PLC code and recommend corresponding design patterns.

## CONTENTS

| DEDICATION                                                            | . iii  |

|-----------------------------------------------------------------------|--------|

| Acknowledgments                                                       | . iv   |

| Abstract                                                              | . v    |

| List of Tables                                                        | . viii |

| List of Figures                                                       | . ix   |

| List of Abbreviations                                                 | . xii  |

| Chapter 1 Introduction                                                | . 1    |

| Chapter 2 Related Work                                                | . 4    |

| 2.1 SCADA and PLC Overview                                            | . 9    |

| 2.2 SCADA and PLC Security                                            | . 17   |

| 2.3 Secure Software Verification Methods and Software Code Review To- | ols 20 |

| 2.4 Limitations of SCADA/PLC Security Research                        | . 21   |

| CHAPTER 3 PROPOSED PLC SECURITY FRAMEWORK                             | . 22   |

| 3.1 PLC Code Analysis (PLC-SF)                                        | . 22   |

| 3.2 Malicious Entry Points                                            | . 25   |

| Chapter 4 Vulnerabilities Analysis                                    | . 28   |

| 4.1 Attack Severity Analysis                                          | . 28   |

| 4.2 Examples of Severity Level Effects                                | . 31   |

| 4.3      | Potential Exploitation of Coding Errors                           | 32  |

|----------|-------------------------------------------------------------------|-----|

| 4.4      | Building the Vulnerability Taxonomy                               | 36  |

| 4.5      | Modeling PLC Vulnerabilities                                      | 50  |

| Снарт    | er 5 Supporting Correct Software Development                      | 65  |

| 5.1      | PLC Security Design Patterns                                      | 66  |

| 5.2      | Selection of Design Patterns to Mitigate Software Vulnerabilities | 102 |

| Снарт    | er 6 Static Analysis Tool                                         | 104 |

| 6.1      | Overview of the Static Analysis Tool                              | 104 |

| 6.2      | Static Analysis Tool Implementation Examples                      | 106 |

| Снарт    | ER 7 CONCLUSIONS AND FUTURE RESEARCH                              | 120 |

| Ribi 100 | CDADHY                                                            | 19/ |

## LIST OF TABLES

| Table 4.1 | Severity Chart                           | 29 |

|-----------|------------------------------------------|----|

| Table 4.2 | Severity Rating vs. Attacker's Knowledge | 33 |

| Table 4.3 | Development Error vs. Opportunity        | 35 |

|           |                                          |    |

| Table 5.1 | Pattern: Comparative Functions Miscoded  | 70 |

| Table 5.2 | Pattern: Trigger Bit Missing             | 76 |

| Table 5.3 | Pattern: Timer Race Condition            | 81 |

| Table 5.4 | Pattern: Scope and Linkage Errors        | 84 |

| Table 5.5 | Pattern: Duplicate Objects Installed     | 90 |

| Table 5.6 | Pattern: Unused Objects Instantiated     | 94 |

| Table 5.7 | Pattern: Hidden Software Jumpers         | 98 |

## LIST OF FIGURES

| Figure 2.1  | Standard Hardware Relay                                          | 10 |

|-------------|------------------------------------------------------------------|----|

| Figure 2.2  | Standard Set of PLC Components                                   | 11 |

| Figure 2.3  | Standard Ladder Logic Diagram                                    | 12 |

| Figure 2.4  | Block Style PLC Configuration                                    | 14 |

| Figure 2.5  | Rack Mount PLC Configuration                                     | 14 |

| Figure 2.6  | Standard SCADA System Configuration                              | 17 |

| Figure 3.1  | Proposed Security Framework PLC-SF                               | 23 |

| Figure 3.2  | SCADA System Control Flow                                        | 26 |

| Figure 3.3  | SCADA System Control Flow Possible Malicious Entry Points        | 27 |

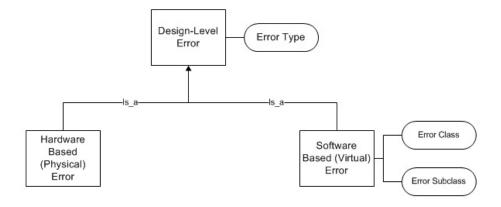

| Figure 4.1  | Vulnerability Taxonomy                                           | 36 |

| Figure 4.2  | Ladder Logic Vulnerability Taxonomy: Design Level Error          | 37 |

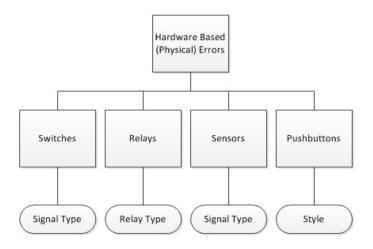

| Figure 4.3  | Ladder Logic Vulnerability Taxonomy: Hardware                    | 38 |

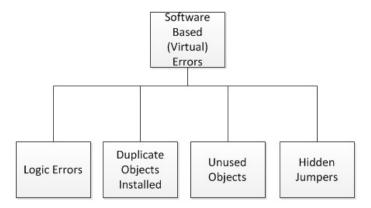

| Figure 4.4  | Ladder Logic Vulnerability Taxonomy: Software                    | 39 |

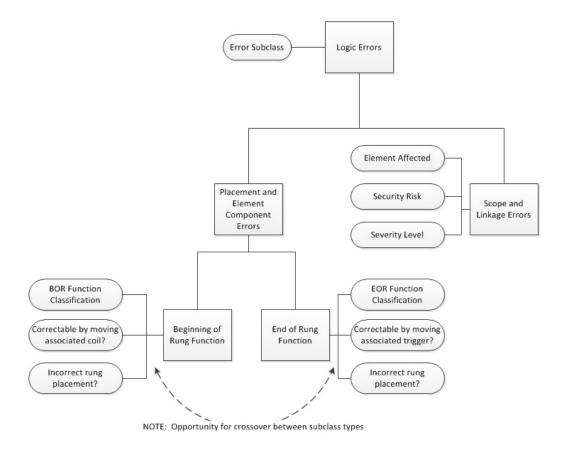

| Figure 4.5  | Ladder Logic Vulnerability Taxonomy: Logic Errors                | 41 |

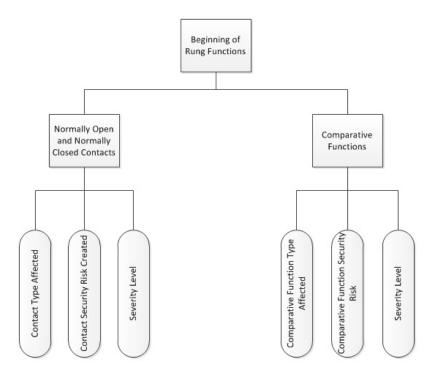

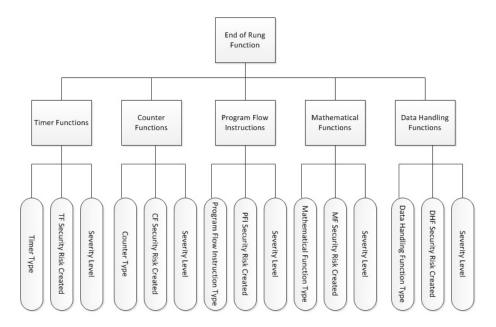

| Figure 4.6  | Ladder Logic Vulnerability Taxonomy: Beginning of Rung Functions | 43 |

| Figure 4.7  | Ladder Logic Vulnerability Taxonomy: End of Rung Functions       | 44 |

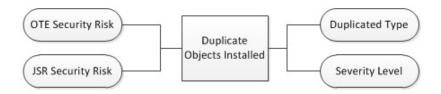

| Figure 4.8  | Ladder Logic Vulnerability Taxonomy: Duplicate Objects Installed | 47 |

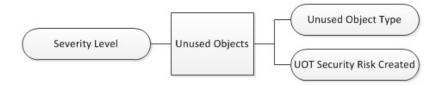

| Figure 4.9  | Ladder Logic Vulnerability Taxonomy: Unused Objects Installed .  | 47 |

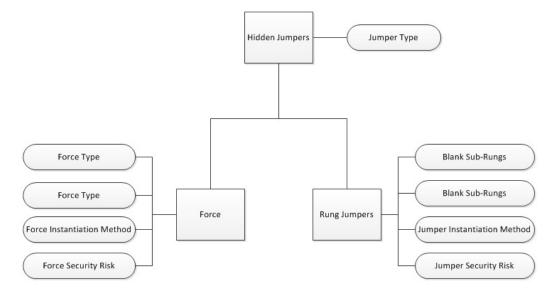

| Figure 4.10 | Ladder Logic Vulnerability Taxonomy: Hidden Jumpers              | 48 |

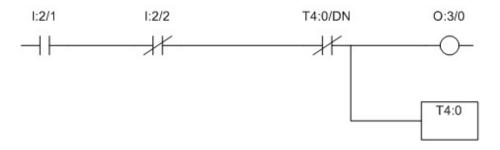

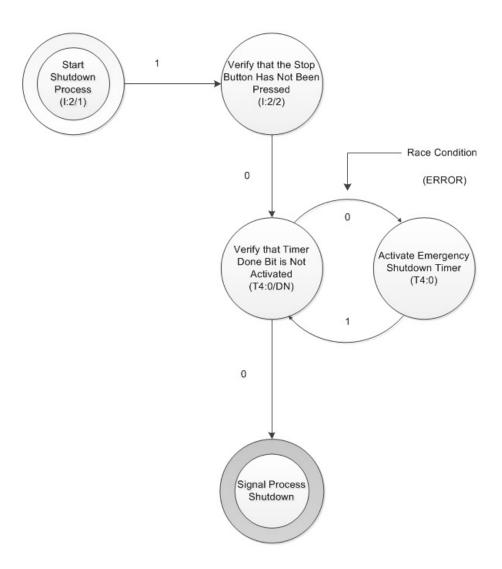

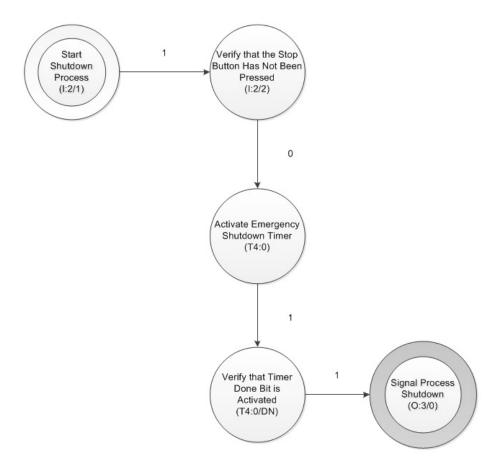

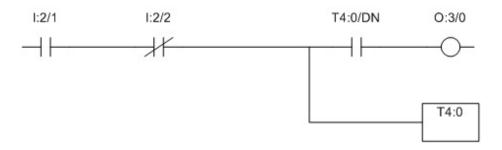

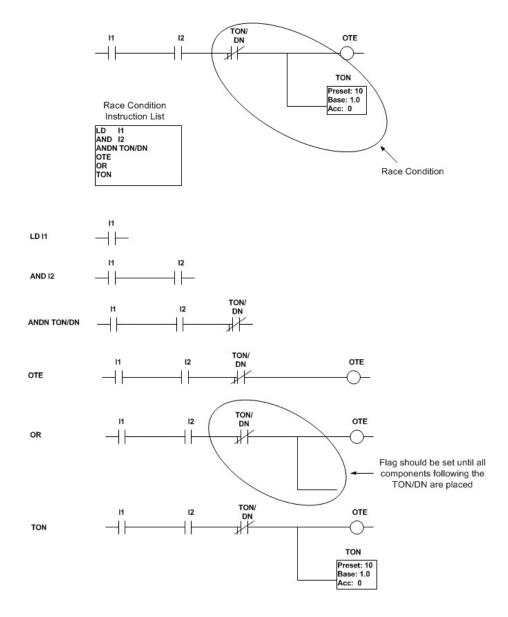

| Figure 4.11 | Race Condition: Ladder Logic Incorrect                           | 52 |

| Figure 4.12 | State Transition Diagram: Existing Race Condition                | 53 |

| Figure 4.13 | State Transition Diagram: Elimination of Race Condition          | 54 |

| Figure 4.14 | Ladder Logic: Elimination of Race Condition                     | 55 |

|-------------|-----------------------------------------------------------------|----|

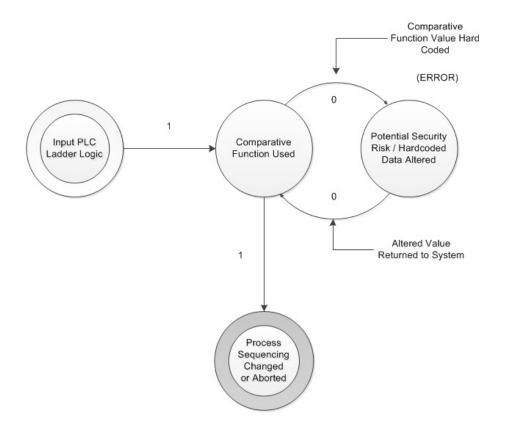

| Figure 4.15 | State Transition Diagram: Comparative Function Risk             | 56 |

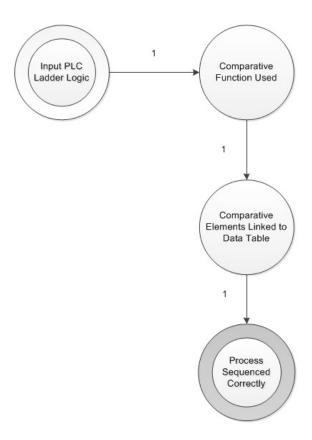

| Figure 4.16 | State Transition Diagram: Comparative Function Risk Eliminated  | 57 |

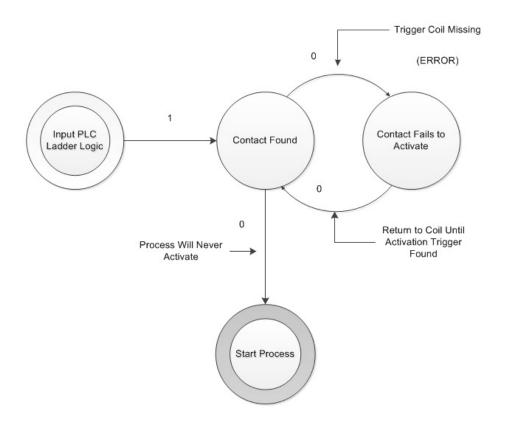

| Figure 4.17 | State Transition Diagram: Missing Trigger Coil                  | 58 |

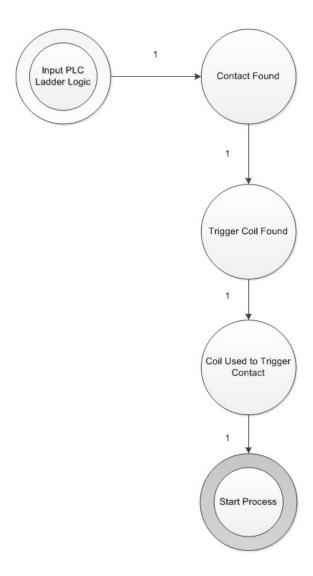

| Figure 4.18 | State Transition Diagram: Missing Trigger Coil Error Eliminated | 59 |

| Figure 4.19 | State Transition Diagram: Scope and Linkage Risk                | 60 |

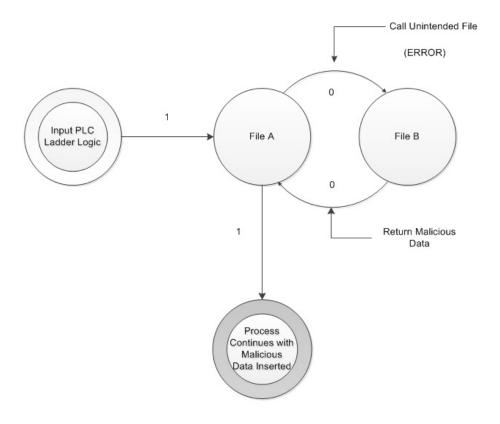

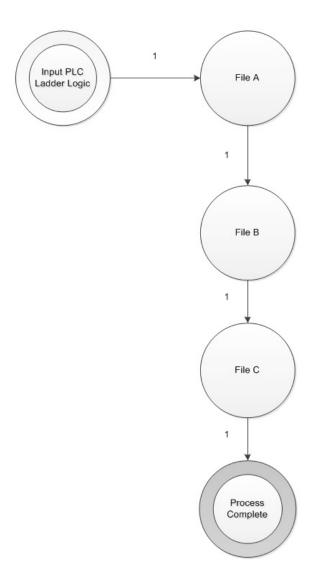

| Figure 4.20 | State Transition Diagram: Scope and Linkage Risk Eliminated     | 61 |

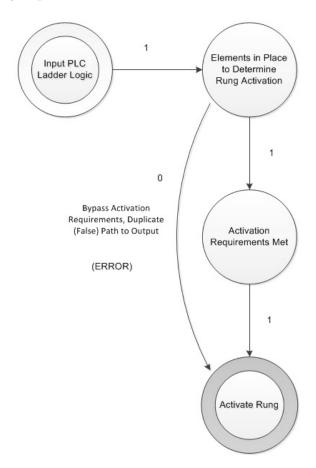

| Figure 4.21 | State Transition Diagram: Hidden Jumper Risk                    | 62 |

| Figure 4.22 | State Transition Diagram: Hidden Jumper Risk Eliminated $\ \ .$ | 63 |

| Figure 4.23 | State Transition Diagram: Duplicate Object Inserted Risk        | 64 |

| Figure 5.1  | Design Pattern Relationships                                    | 67 |

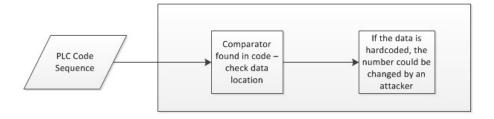

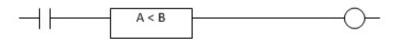

| Figure 5.2  | Pattern: Hard Coded Value Vulnerability                         | 72 |

| Figure 5.3  | Comparator with Hard Coded Element                              | 73 |

| Figure 5.4  | Pattern: Elimination of Hardcoded Value Vulnerability           | 74 |

| Figure 5.5  | Compartor with Data Table Directed Elements                     | 75 |

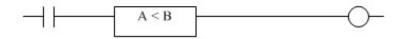

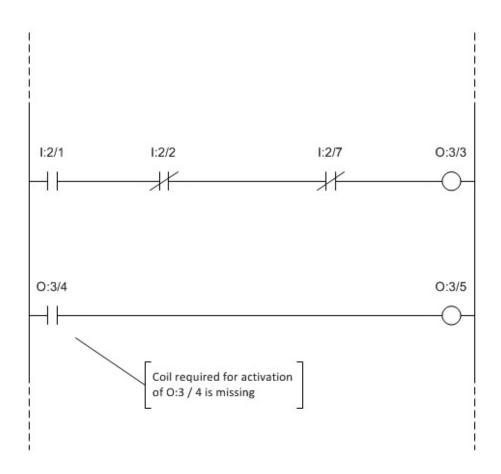

| Figure 5.6  | Pattern: Missing Trigger Bit Vulnerability                      | 78 |

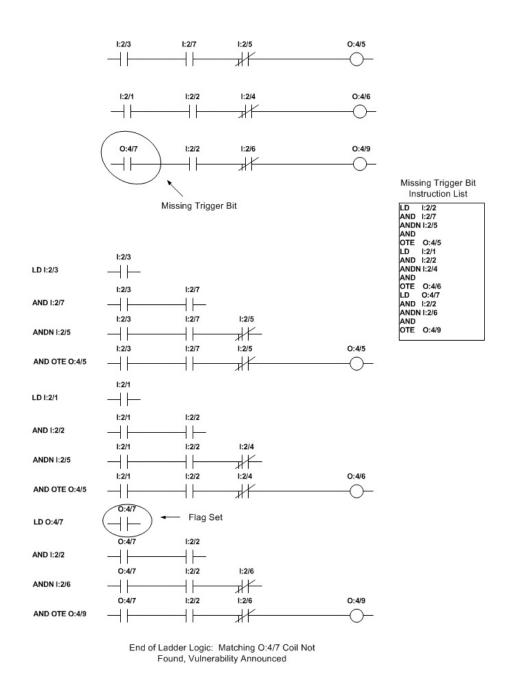

| Figure 5.7  | Missing Trigger Bit Ladder Logic                                | 78 |

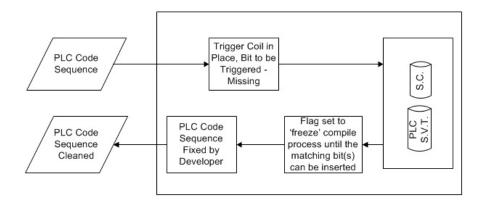

| Figure 5.8  | Pattern: Elimination of Missing Trigger Bit Vulnerability       | 79 |

| Figure 5.9  | Missing Trigger Bit Corrected                                   | 80 |

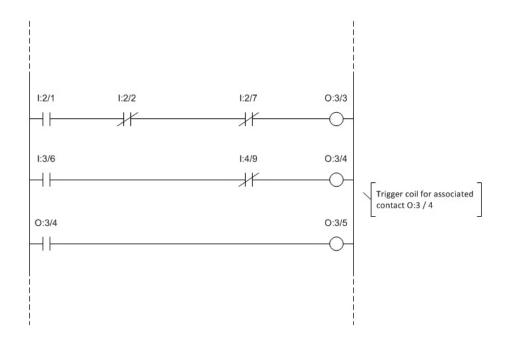

| Figure 5.10 | Timer Race Condition Vulnerability                              | 82 |

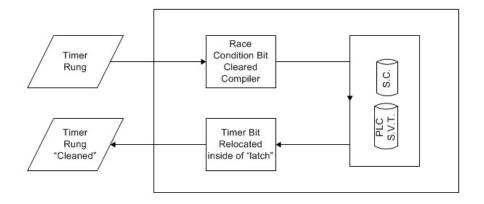

| Figure 5.11 | Pattern: Timer Race Condition                                   | 83 |

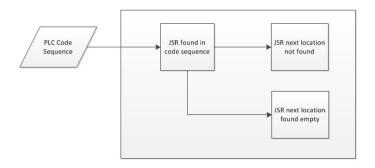

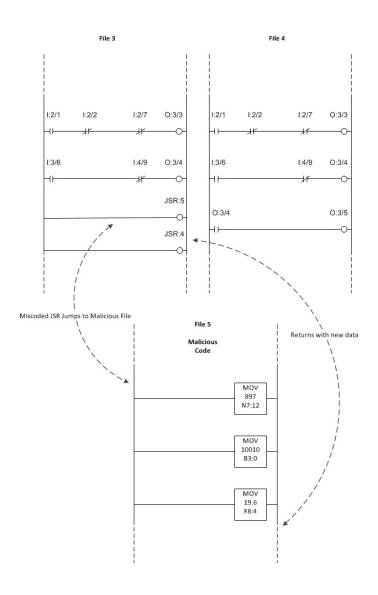

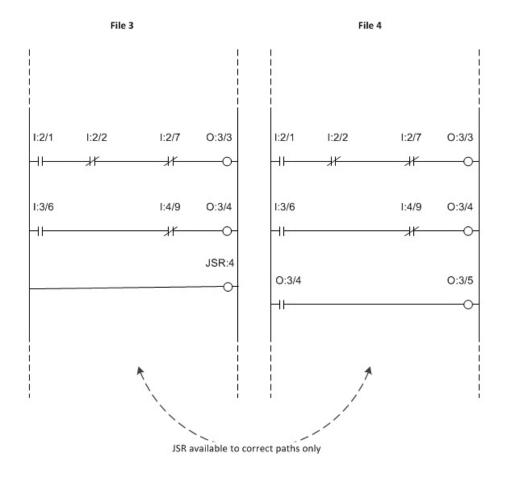

| Figure 5.12 | Pattern: JSR Vulnerability                                      | 86 |

| Figure 5.13 | JSR Man in the Middle Attack                                    | 87 |

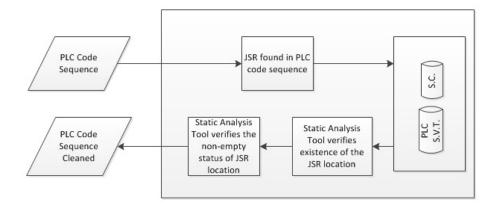

| Figure 5.14 | Pattern: Elimination of Incorrect JSR                           | 88 |

| Figure 5.15 | PLC Code After Elimination of Security Risk                     | 89 |

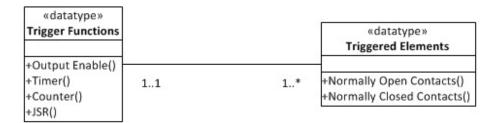

| Figure 5.16 | Trigger Function to Element Relationship                        | 91 |

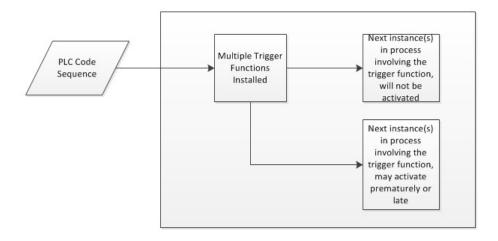

| Figure 5.17 | Pattern: Duplicate Objects Installed Vulnerability              | 92 |

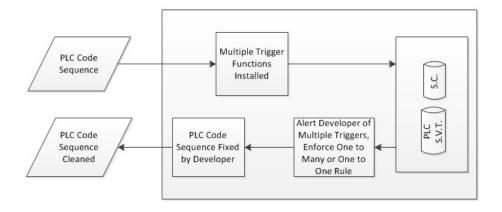

| Figure 5.18 | Pattern: Elimination of Duplicate Objects                         | 93  |

|-------------|-------------------------------------------------------------------|-----|

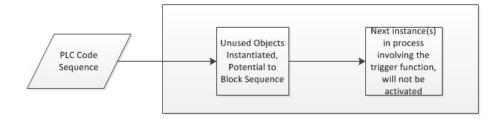

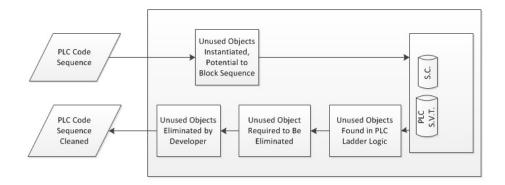

| Figure 5.19 | Pattern: Unused Objects Installed Vulnerability                   | 96  |

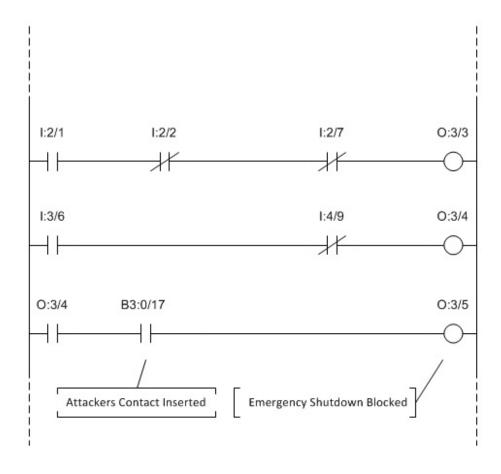

| Figure 5.20 | Blocking Contact Inserted                                         | 96  |

| Figure 5.21 | Pattern: Elimination of Unused Objects                            | 97  |

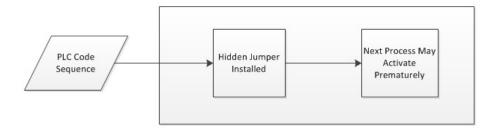

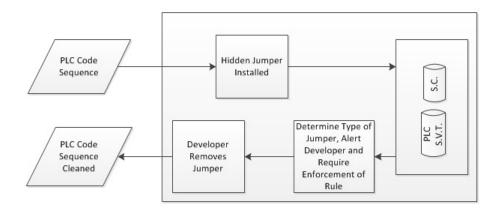

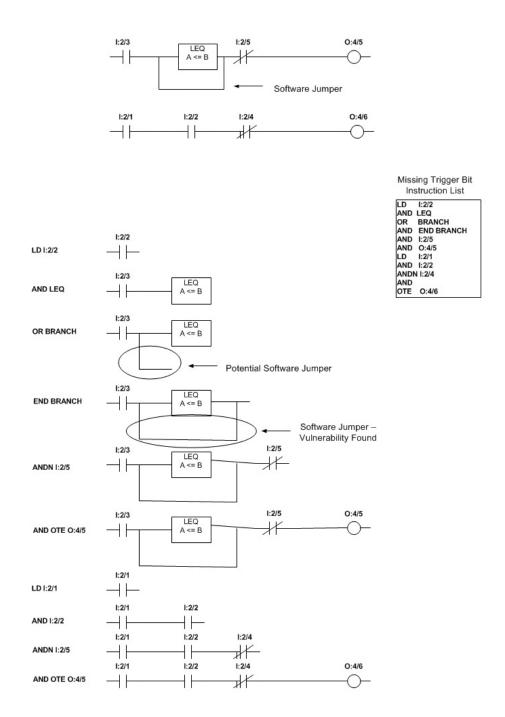

| Figure 5.22 | Pattern: Hidden Jumper Installed Vulnerability                    | 99  |

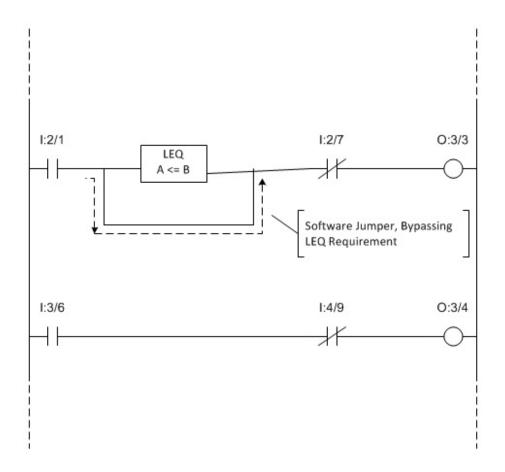

| Figure 5.23 | Software Jumper Installed                                         | 100 |

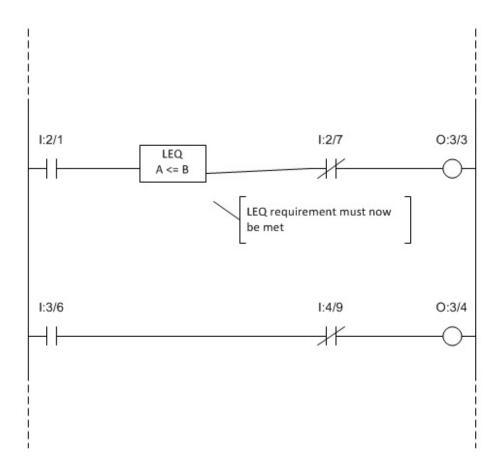

| Figure 5.24 | Pattern: Elimination of Hidden Jumpers                            | 101 |

| Figure 5.25 | Elimination of Software Jumper                                    | 101 |

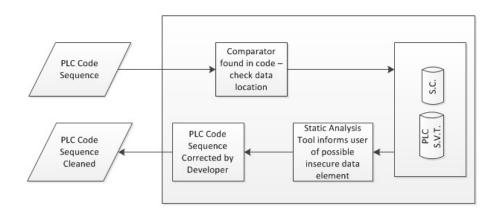

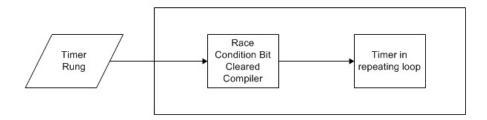

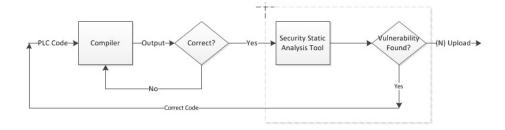

| Figure 6.1  | PLC Compiler Work Flow with Static Analysis Tool                  | 105 |

| Figure 6.2  | Timer Race Condition (Ladder Logic Example)                       | 108 |

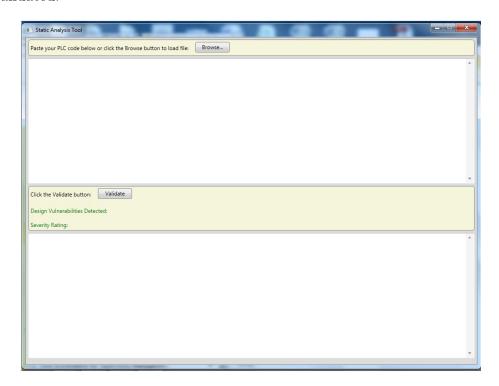

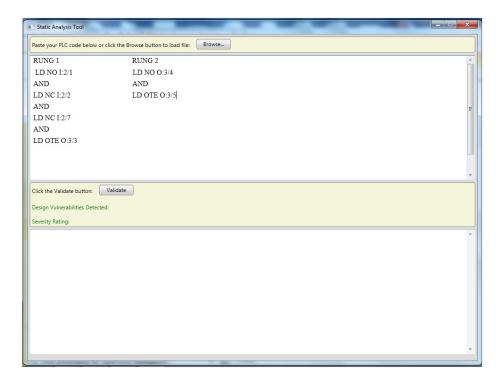

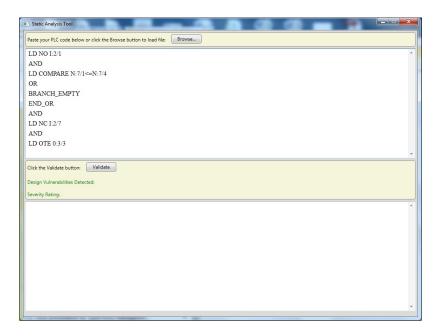

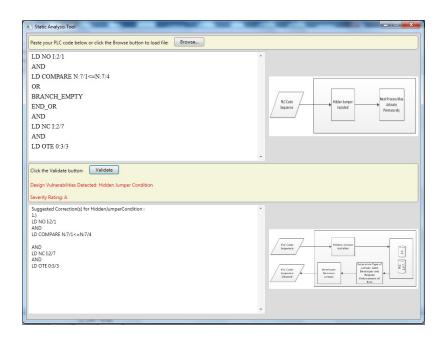

| Figure 6.3  | Static Analysis Tool: Initialization                              | 110 |

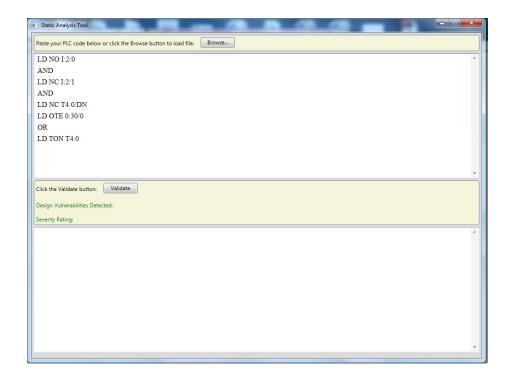

| Figure 6.4  | Static Analysis Tool: Race Condition Error                        | 111 |

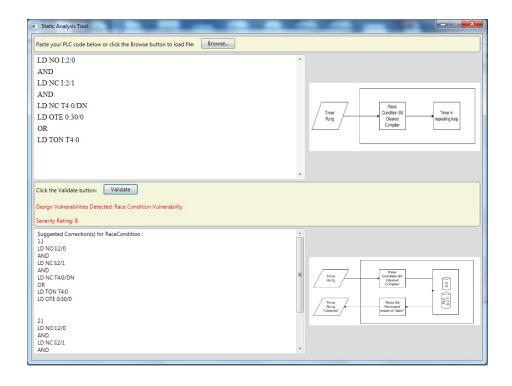

| Figure 6.5  | Static Analysis Tool: Mitigation of the Race Condition Error      | 112 |

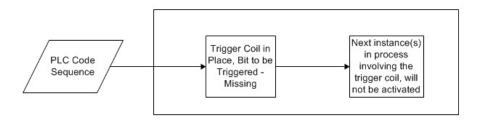

| Figure 6.6  | Missing Trigger Bit (Ladder Logic Example)                        | 114 |

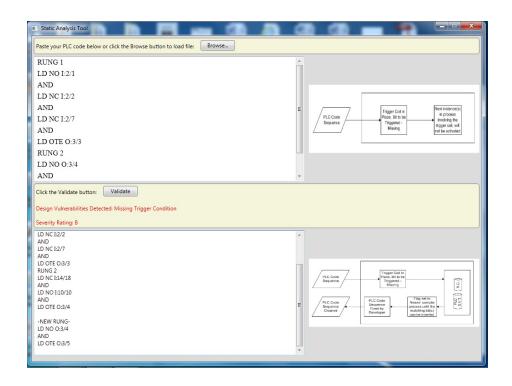

| Figure 6.7  | Static Analysis Tool: Missing Trigger Bit Error                   | 115 |

| Figure 6.8  | Static Analysis Tool: Mitigation of the Missing Trigger Bit Error | 116 |

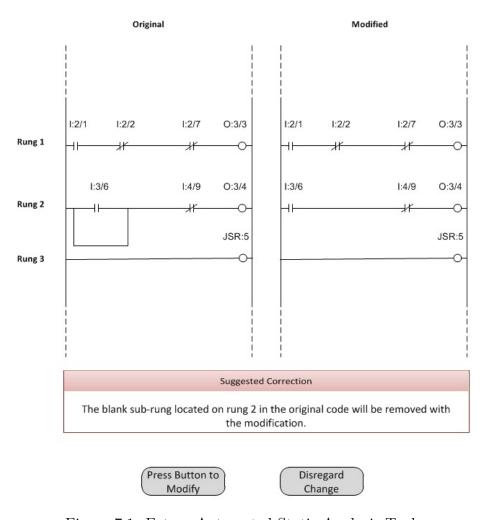

| Figure 6.9  | Hidden Jumper (Ladder Logic Example)                              | 118 |

| Figure 6.10 | Static Analysis Tool: Hidden Jumper Error                         | 119 |

| Figure 6.11 | Static Analysis Tool: Mitigation of the Hidden Jumper Error       | 119 |

| Figure 7.1  | Future Automated Static Analysis Tool                             | 122 |

## LIST OF ABBREVIATIONS

| CIPCritical Infrastructure Protection |                           |

|---------------------------------------|---------------------------|

| COPCopy                               |                           |

| CPU                                   |                           |

| CTD                                   | Count Down Counter        |

| CTU                                   | Count Up Counter          |

| EQU                                   | Equals                    |

| FLL                                   | File Fill                 |

| GEQ                                   | Greater Than or Equal To  |

| GRT                                   | Greater Than              |

| HMI                                   | Human Machine Interface   |

| ICS                                   | Industrial Control System |

| IO                                    | Input / Output            |

| JMP                                   | Jump                      |

| JSR                                   | Jump to Subroutine        |

| LBL                                   | Label                     |

| LEQ                                   | Less Than or Equal To     |

| LES                                   | Less Than                 |

| LIM                                   | Limit                     |

| MOV                                   | Move                      |

| NEQ                                   | Not Equal                 |

| OTE                                   | Output Enable             |

| PC                                    | Personal Computer         |

| Proportional-Integral-Derivative         | PID   |

|------------------------------------------|-------|

| Reset                                    | RES   |

| Return                                   |       |

|                                          |       |

| Supervisory Control and Data Acquisition | SCADA |

| Timer Off                                |       |

| Timer On                                 | TON   |

| Exclusive OR                             | XOR   |

#### CHAPTER 1

#### Introduction

Lack of peripheral device protection in a SCADA system is a problem in that it is the basis by which most 'control based' attacks on the nations' infrastructure could be carried out. Most current work on industrial control system protection is directed toward the graphical monitoring software, as opposed to the devices from which its data is controlled. Network attacks on these peripheral devices, by design, are not required to go through the personal computer (PC) hosting the SCADA software directly. As most programmable logic controllers (PLC's) are now equipped with Ethernet communications cards, an attacker could access the PLC hardware and its programming tools, directly. The traditional SCADA problem in which an attacker enters the system through the PC housing the SCADA software only adds to the issue of protection, but never fully addresses protection of the system at the operational level. This issue is further compounded when you take into consideration internal attackers as well as external attackers and cross reference those two subgroups against malicious attacks verses unintentional coding errors. In this dissertation, we address multiple fundamental errors in the PLC programming platform and present methods by which to defend against, or correct, these errors. These errors are broken down by attackers knowledge, type of attack, severity of the attack performed or intended, internal or external attackers (to determine practical knowledge of the system) and the degree to which a given attack could be achieved intentionally or unintentionally. Rules will be presented to address these scenarios in an open format which would allow for their implementation regardless of controller type.

The research that we are proposing addresses the issue of industrial control system infrastructure at the programmable device level. This can only be properly addressed if the problem is looked at from multiple perspectives and severity levels, both of which are missing from current research in the field. We plan to develop multiple attack models and scenarios, giving real world coding examples and providing a means to address each. This would allow the current device manufacturers, as well as OEM's, to address these issues prior to being placed in 'live scenarios', thereby leaving their systems open for control level attacks. To accomplish my dissertation research, the following tasks are anticipated to be required:

- 1. Create a table of errors (vulnerabilities) outlining the knowledge of the attacker, or unintentional error, against the probability of the attack occurring. We provide coding examples of 'entry methods' of the vulnerabilities into the system. We will develop a PLC software security taxonomy to model and conceptualize the vulnerabilities we identify. This taxonomy forms the basis to represent mitigation methods of the detected vulnerabilities.

- 2. Create severity measurements and a severity chart which will outline the severity of the possible attacks and/or unintentional errors in the PLC system and in SCADA. We will present evaluations and examples of these attacks in a manner similar to the attack descriptions of the Open Web Application Security Project.

- 3. The results of tasks 1 and 2, along with application specific logic (state-transition diagrams) are used to develop formal models of these vulnerabilities. These models are used to identify these vulnerabilities in PLC code and to develop mitigation strategies.

- 4. Prevention, detection, and removal of software vulnerabilities:

- Prevention: software design methodologies leading to best practices guidelines, represented as design patterns

• Detecting vulnerabilities: static analysis tools "screening" the PLC code for vulnerabilities modeled in step 3. We propose a rule-based code analysis tool that 1) detects known vulnerability and 2) identifies the source of the vulnerability. Our aim is to develop a tool with low false positive and false negative occurances.

• Removal of vulnerability: We will link the detected vulnerabilities with the appropriate PLC security design patterns. This will allow the system developer to modify the code in a manner that removes the vulnerabilities. At this point, we are not proposing an automated system to remove the vulnerability because the main focus of this research is to aid the detection of the software vulnerability and to provide guidelines to the developer.

#### 5. Proof-of-concept implementation.

- State-transition-diagram/rule-based detection

- Input: PLC code that has passed the PLC compilation successfully

- Output: List of vulnerabilities and associated design patterns

#### Chapter 2

#### Related Work

Currently, most facilities that use factory automation are turning to SCADA systems to track and control those factory automation devices. This includes not only manufacturing facilities but also those major infrastructure facilities such as power, water and natural gas [23]. By using a SCADA system to track and control these systems, it leaves them extremely vulnerable to both those individuals with malicious intent as well as those that made unintentional mistakes.

It appears that the research on the problem domain as a whole (SCADA technology as it relates, in general, to the public and private sectors) is slowly beginning to make its way to the forefront [44]. During the last decade, we have seen an increased national awareness of critical infrastructure incidents. Assessing and mitigating the cyber security vulnerabilities of SCADA systems are in the focus of academia, government, and industry research. Nicholson et al. [34] give a survey of the security concerns in SCADA systems. The authors present the change of focus in SCADA security, provide and overview of the know attacks and the type of malicious users, current and future threats, and discuss current best practices. This is a result of the potential impact that SCADA technology could have on the national infrastructure arena. The related research that we have found spans multiple areas of interest pertaining to the specific job function of the researcher. These related works, to date, range from utility company consortiums and working groups to government level directives and studies. For example, there currently are working groups that have been created for the various infrastructure sectors of water, electricity and nat-

ural gas [4,11,29]. Furthermore, the national agencies such as the US Departments of Energy and Homeland Security each have published white papers and begun initiatives to begin investigations into the problem domain of SCADA systems in general [2,36]. The White House has released "Presidential Directive 63" as well as "The National Strategy to Secure Cyberspace" both of which discuss SCADA systems as a direct threat to national security [24]. The vendor specific publications suggest that increased security may adversely affect their products performance and, therefore, strongly encourage the end user to disable or bypass certain security features [5,6].

Academia research to strengthen SCADA security falls in two general categories: 1) overview of SCADA security risks and the need for new security technologies to strengthen security [9, 16, 19, 26, 32, 34, 43, 45] and 2) developing new methods to support security analysis and technologies [12, 15, 21, 30, 31, 33, 38, 39]. For example, Cardenas et al. give an overview of the cyber security risk in industrial control systems and emphasize the importance of distinguishing these systems from general purpose IT systems [9]. The authors present detailed overview of government and industry regulation, such as North American Electric Reliability Corporation (NERC) cybersecurity standards for control systems [35] and the NIST Guide to Industrial Control System (ICS) Security [46] to improve SCADA security. Cardenas et al. argue that the knowledge of the physical system enables malicious attackers to change system behavior, therefore indicating control device vulnerabilities. Several unique SCADA security requirements, e.g., real-time requirements, need for continuity of operations, and large number of legacy systems, over traditional information security are discussed in the paper. Miller and Rowe present a comprehensive overview of SCADA and critical infrastructure incidents in [32]. They propose a standardized taxonomy of SCADA incidents to support comparison of known incidents.

Until recently, SCADA security focused on network-based security threats, assuming that preventing unauthorized external access to the SCADA system provides

sufficient security. However, this approach will not prevent attacks exploiting other SCADA components, for example malicious control code for PLC components. In their 2007 publication, pre-Stuxnet, Valentine and Farkas [50] argued that the Programmable Logic Controllers (PLCs) are vulnerable to intentional software-based attacks by malicious users. The authors discuss the inability of PLC code compilers to detect such software errors. In their followup publications [51, 52], the authors provide a taxonomy of coding errors, recommend detection and mitigation methods.

The widely publicized Stuxnet [53] attack has shifted national attention to address software vulnerabilities of control devices [12,30,31,38,45]. Schaefer [45] discusses the disconnection between modern PLCs and the physical world these devices control. In particular, the author points out several important aspects of ladder logic execution that may create unsafe conditions, such as race condition. Olmstead et al. [38] and Minn at al. [31] survey PLC security concerns and provide guidelines to mitigate threats. The authors study software-based vulnerabilities among the important threats against SCADA. Several publications address the need for monitoring software process controllers [12, 33]. While these approaches are useful to detect anomalous activities of malware, they do not prevent the initial execution and propagation of such malware. The closest to our work is the attack presented by McLaughlin and McDaniel [30]. The authors developed an automated tools, called SABOT, that is capable of generating PLC code that, when executes, creates system behavior according to the attackerâĂŹs specification. For this, the tool must have access to the control logic bytecode from the targeted PLC. The authors demonstrate that contrary to general belief that attacks against SCADA systems may be launched by attackers without any specific knowledge about the system. In our work, we address the threat of malicious PLC code uploads by requiring that all PLC code uploads must be evaluated by our static analysis tool. Therefore, the malicious code, generated by SABOT, would be detected and prevented from execution.

The current research appears to focus more on the data monitored by the SCADA system itself and the malicious means available to shut down or slow down the SCADA system when used as a controller interface [8, 17, 18, 23, 40, 41, 46]. Ongoing research needs to consider the topic of SCADA systems from the viewpoint of the negative impact that breaching the SCADA system terminal could have on the PLC ladder logic itself. By addressing this problem you would then begin to develop a basis for the overall protection of automated control systems. This would begin to allow for a layered approach in protection. The SCADA PC would be protected, for example possibly by IPSec, while implementing a second layer directly into the PLC compiler would begin to track changes in the PLC code and look for known vulnerable statements that could cause severe issues in intended functionality. We believe that the available research using this approach is somewhat limited at this point due to a lack of understanding of possible fault scenarios in the ladder logic itself. We believe that by expanding the research to include investigation of protection of the PLC ladder logic through fundamental changes in the way that the logic is compiled and tracked will begin to address a more solid foundation for automation security as a whole.

Currently, there is no existing 'complete' solution to this problem. This explains why many private sector working groups are being formed to better understand the problem of developing safe and secure systems. For example, the beginnings of a document currently in the formation process by the The American Gas Association [4] published an overview and recommendations on secure SCADA communications, policies and plans. This work, similar to other publications, focuses on network level security. It fails to take into consideration the protection of system level components such as the PLC's. We argue that while it is critical that appropriate security safeguards are implemented, they cannot protect against exploitation of code-level vulnerabilities.

The subject of SCADA system security is at the forefront of discussions involving the protection of the national infrastructure. These processes include those elements critical to everyday life such as water, power and natural gas. This can be seen in documentation from various US government agencies. The Homeland Security Act of 2002 [2], specifically addresses the concept of infiltration of a SCADA system from a network level. Furthermore, The US Department of Energy [36], in their working document, "21 Steps to Improve Cyber SCADA Security", proposed guidelines for improving cyber security for SCADA systems. These guidelines are intended to help alleviate some of the most common "hacking" problems related to SCADA system. The main focus of these documents is the accessibility of SCADA components through IT. The guidelines do not address the hardware components used to supply information to the SCADA system, such as the PLC or its subsequent devices. These elements are critical in the creation of any plan which is intended to fully protect automated systems currently and into the future. To further solidify the need for a more complete solution, we refer to an article published by the US Department of Homeland security as recently as October 31, 2012 [49]. This article describes a buffer overflow vulnerability which resulted in a denial of service attack. This article suggests the following solutions:

- "Minimize network exposure for all control system devices. Critical devices should not directly face the internet."

- "Locate control system networks and remote devices behind firewalls, and isolate them from the business network."

- "When remote access is required, use secure methods, such as Virtual Private Networks (VPNs), recognizing that VPN is only as secure as the connected devices."

These solutions are not practical, given the current state of modern control systems. Current control system devices such as PLC's, have on board networking capability and as such have potential to "directly face the internet". To minimize this capability may, in certain instances, minimize the ability of the device to deliver data optimally. To the second point, although all industrial control system users and developers are strongly encouraged to separate the business network functions from the control systems functions, this may not always be practical or possible based on availability of resources. Finally, to address the third and final point, "VPNs are only as secure as the connected devices." PLC's, in particularly legacy systems were not designed as, nor intended to be, secure devices. Therefore, it is imperative that solutions, such as those addressed throughout the remainder of this work, be considered as a probable solution to a practical scenario. This problem is magnified, when you consider that tools are readily available, and generally free, which allow hackers into internet facing control systems [48]. Each of these reports continue to address the problem from a network security perspective. As such, our research expands on the current concerns by addressing the problem of software application security.

### 2.1 SCADA and PLC Overview

This section will give a general SCADA and PLC overview. Section 2.1.1 begins by giving an introduction to ladder logic. Section 2.1.2 describes the PLC hardware, specifically as it pertains to the hardware configuration types, PLC CPU, and input and output cards. Section 2.1.3 gives an overview of SCADA systems and their relation to PLC's and the automation process.

#### 2.1.1 Overview of Ladder Logic

Ladder logic is the basis behind all PLC programming, regardless of the hardware manufacturer. While each manufacturer may have their own programming tool, fundamentally, each have the same hardware and software requirements. In this section, we will give a brief overview of ladder logic and its components.

Ladder logic programming is based on graphical symbols intended to mirror the hardware which was once solely used in automated processes. The backbone behind the entire concept of this language is the hardware relay. Prior to PLC's, hardware relays were used as the switching mechanism of choice in automated systems. The problem with this approach was the size and adaptability of the processes. If it became necessary to alter the way that a given process functioned, it required additional hardware and generally space for expansion. Figure 2.1 shows a standard hardware relay.

Figure 2.1: Standard Hardware Relay

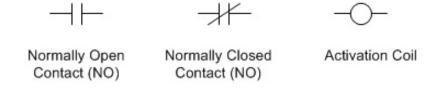

In the diagram, points (1) and (3) represent the hardwire points for a normally closed contact, points (2) and (4) the hardwire points for a normally closed contact and points (5) and (6) the hardwire points for the activation coil. Each hardware relay generally had one normally open contact, one normally closed contact and one

latching coil. As a general functional overview, a standard relay would operate as follows: the normally open and normally closed contacts are in the original (resting) state until which point the control coil becomes activated. Once this control coil becomes activated, the normally open and normally closed contacts change from their resting state to their activate state. When this occurs a normally open contact becomes closed and similarly, a normally closed contact opens. To bring a relay panel to the level of scalability of a modern day PLC system, it would require roughly 20,000 hardware relays to do the work of one small PLC system. This takes into consideration that the PLC has functionality built in to use internal binary points as well as the hardware relay system, each relay had to be manually rewired as needed. With the modern day PLC system, the functionality can be changed, including the hardware, based purely on software tools. This ease of alteration becomes the basis behind this work.

As stated, PLC ladder logic code was designed around the concept of these hard-ware relays. As such, PLC ladder logic software has graphical components for normally open contacts, normally closed contacts and latching mechanisms (coils). Figure 2.2 shows a basic set of PLC components.

Figure 2.2: Standard Set of PLC Components

As PLC systems began to expand, the functional components grew from only using contacts and coils, such that would be found in a relay, to the incorporation of other hardware components such as timer and counter mechanisms. These devices were followed by the addition of mathematical functions, comparative routines and

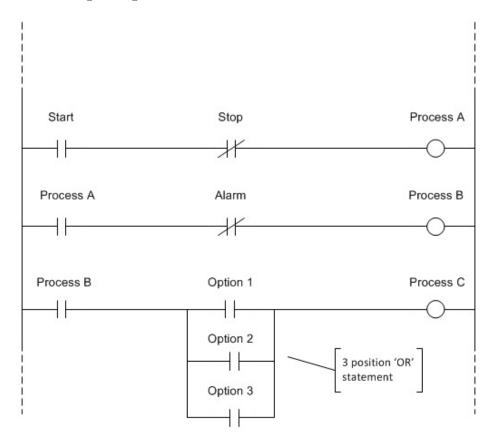

proportional integral differential (PID) loop controllers. The modern day PLC system can perform any of the functionality of a traditional system with features that exceed those that were available to purely hardware based systems [3]. Figure 2.3 shows a standard ladder logic diagram.

Figure 2.3: Standard Ladder Logic Diagram

This programming style is referred to as ladder logic, due to the fact that each line shown represents one 'rung' on the ladder. The flow of a standard ladder logic program is left to right, top to bottom. This flow will continue until which point a command is encountered that would move the pointer to a different location in the code, such as a jump, return or jump to subroutine. In the example shown, the ladder logic would read as follows: once the start command is activated (closed), the stop command is verified not to be activated (remains closed). If both of these conditions are true, then the 'process A' coil is activated. Once the 'begin process' coil

is activated, it's associated 'process A' coil on the second rung is activated (closed). When this contact has been activated, the alarm command is verified not to be activated (remains closed) and the 'process B' coil is activated. Finally, once the 'process B' coil is activated, it's associated 'process B' contact is activated (closed). At this point, we move to the section of the third rung where we encounter the 'OR' statements. This section of the ladder allows for a decision to be made between options 1, 2 or 3 as to which will allow 'process C' to activate. Note, as we have worked through this example, that the contact and coil operations of PLC ladder logic are identical to the functionality of the traditional hardware relay previously described.

#### 2.1.2 Overview of PLC Hardware

The hardware that makes up a standard PLC unit can be found in one of two configurations / styles: 'rack mount' or 'block'. The major difference between either of these available configurations lies in the ability to alter the input and output devices available to each. We will now give a general overview of each configuration:

#### 2.1.2.1 Available Configuration Types

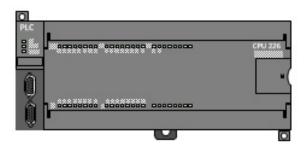

Block Configuration: When a PLC is considered a 'block configuration', the hardware itself comes as a standard package that is purchased with a preset amount of input and output points, a specific communication protocol and the CPU. This configuration comes as one complete unit and cannot be physically altered. The only means available to expand this configuration is by chaining the devices together using the available communication protocol and adding more blocks to the chain. This would allow the user to expand the number of input and output points, in very small chunks. Figure 2.4 shows a standard block style PLC hardware device.

Figure 2.4: Block Style PLC Configuration

Rack Mount Configuration: A 'rack mount configuration', PLC configuration allows the user to select, and interchange, everything in the PLC control system. This includes the CPU type, the number and type of input and output cards and the communications protocol. All of the hardware involved in a rack mount configuration passes data between the input and output cards by way of a slot based chassis. This chassis serves a two fold purpose: 1) to supply power to the entirety of the rack and 2) transmit data across a hardware back plane. Figure 2.5 shows a standard rack mount configuration.

Figure 2.5: Rack Mount PLC Configuration

#### 2.1.2.2 PLC CPU

The PLC CPU unit is the repository for ladder logic program as well as the processor for the information gathered from, and delivered to, the external devices being controlled by the PLC. The CPU contains all of the pertinent information required to fully automate the process in which it is involved. The number of input and output

cards and their types, the communication protocol, and all information contained within the PLC data tables are located in the PLC CPU. There is only one CPU module allowed in the rack mount configurations of the legacy systems currently available by all of the PLC manufacturers (legacy systems represent over 80 percent of those PLC's currently in infrastructure areas). The most current systems allow the designer to incorporate multiple CPU modules in the hardware design of their process. This has the potential of allowing the software (ladder logic) designer to split the process across multiple computing devices making code integrity even more crucial from a security perspective.

#### 2.1.2.3 Input and Output Cards

The external information which is transmitted to and from the PLC occurs over various input and output (I/O) cards. These I/O cards can contain numerous connection points, depending on the need of the user, and can be either digital or analog in relation to the type of information sent and received. We will now give a brief overview of input and output cards and the devices they control.

Input Cards: As noted, PLC input cards can come equipped with multiple connection points, this is solely at the discretion of the developer. A single PLC input card generally comes with its connections points in multiples of 8, with the largest being 64 (8, 16, 24, ..... 64). The PLC input cards gather their information from their associated control devices such as temperature sensors, level sensors, proximity switches, and variable frequency drives.

Output Cards: Just as with PLC input cards, PLC output cards can come equipped with multiple connection points. The number available within any manufacturer generally mirror those available for the input cards. The PLC output cards send out control information in the form of analog and digital signals. These signals are used by the various control devices as an activation mechanism or as a set point.

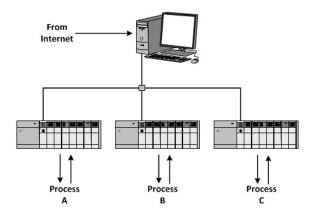

#### 2.1.3 SCADA and Automation System Overview

The PLC is the backbone of the system architecture of an industrial network. The information which is transmitted by the PLC to the SCADA system is collected by the PLC's input and output cards (rack mount configuration) or provided input and output points (block configuration). The SCADA system PC is the information terminal through which the control room operator, and anyone else with intended, or unintended, access can view the real time functionality of the automated system. This terminal is generally connected via Ethernet to the facilities existing network. The SCADA system receives its information directly from the PLC CPU by way of the ethernet connection provided. This could be in the form of a physical communication card, in the case of a rack mount configuration or an internal communication protocol if a block configuration is used. Also, it is now possible to share this information via wireless communications cards as well, which only adds another layer to the security issue.

A standard SCADA system [Figure 2.6] serves as the oversight device which is connected to one or many PLC units throughout a given infrastructure system. The SCADA computer itself is no more than a standard industrial grade computer, running a vendor specific piece of software, which is used to monitor and track the states and conditions of all of the device's connected to its associated controllers. These devices are generally calibrated with the PLC and SCADA system computer upon initial installation and assumed to be accurate thereafter. This assumption is critical to understanding the severity of compromising the PLC. Since the control room operator is taught to rely on data being received by the PLC system and the devices are calibrated using the PLC itself as the calibration method, any individual that gains access to the PLC can potentially directly affect the system and falsify the data that is reported to the SCADA system.

Figure 2.6: Standard SCADA System Configuration

#### 2.2 SCADA and PLC Security

Most of the SCADA system security research addresses security issues raised by network centric operation, such as secure communication, without addressing the security needs in PLC's. As shown in a joint report by the US Department of Energy and the Presidents' Critical Infrastructure Protection Board [36], the current SCADA infrastructure protection focus is on the hardware housing the SCADA software itself and not the programmable devices that are responsible for controlling all of the processes. This report states that "Most older SCADA systems (most systems in use) have no security features whatsoever. SCADA system owners must insist that their system vendor implement security features in the form of product patches or upgrades. Some newer SCADA devices are shipped with basic security features, but these are usually disabled to ensure ease of installation." It continues by stating that "additionally, factory default security settings (such as in computer network firewalls) are often set to provide maximum usability, but minimal security." Current capabilities that permit wireless communications cards in PLC controllers and SCADA systems, makes it necessary to evaluate security needs of each components.

The increased risk of access of malicious users to SCADA components, increases the risk to the PLC code itself. Since the PLC dictates the functionality of the process, even if functional commands may be given through the SCADA computer, it is crucial that it functions correctly and securely. Unfortunately, attacks against the PLC components, as we will demonstrate in the following sections, are easy to carry out by a sophisticated attacker. For example, just by looking at the ladder logic code it is possible to determine the most likely points of entry into the PLC CPU from an outside source, such as a SCADA system. To the best of our knowledge, there is no related work that addresses the implementation of a best practices guide to correctly writing PLC code which, in itself, could alleviate certain security concerns.

Although, protecting the system on which the SCADA backbone resides may eliminate some of the PLC security threats it does not remove all PLC vulnerabilities. Once access is granted though either the SCADA backbone, or any other network medium, then the entire PLC network is open for an attack. Sophisticated attackers, with working knowledge of the system and ladder logic, may be able to access the PLC system directly. From the PLCs, the attacker can gain access to the SCADA terminal. In 2003, the Davis-Besse Nuclear Power Plant was crashed by a slammer worm that infiltrated the SCADA network. It was stated that the Safety Parameter Display System (SPDS) "monitors the most crucial safety indicators at a plant, like coolant systems, core temperature sensors, and external radiation sensors. Many of those continue to require careful monitoring even while a plant is offline." [42] More recently, a Stuxnet attack was performed on a nuclear reactor station in Iran, this attacked directly targeted the PLC hardware to access and alter the ladder logic used to control the facility.

In a recent ISA article [53] on the Stuxnet attack, it is stated that "prior to Stuxnet, it was believed any cyber attack (targeted or not) would be detected by IT security technologies such as firewalls or intrusion detection systems and defense-in-depth would prevent damage to physical processes. However, previous actual control system cyber incidents (malicious and unintentional) have demonstrated that many

ICS cyber incidents are not readily detectable, and they can cause physical damage even with existing defense-in-depth designs." The article goes on to say "it is important to note the use of the term SCADA, as these same technologies have not been employed on many legacy non-SCADA devices such as programmable logic controllers (PLCs), electronic drives, process sensors, and other field devices. Another implicit assumption in the standards being developed such as ISA99 and the North American Electric Reliability Corporation (NERC) Critical Infrastructure Protection (CIP) standards is they would be comprehensive enough to address cyber attacks against ICSs including sophisticated attacks. The inadequacy of these assumptions against a sophisticated attack such as Stuxnet requires a detailed reassessment of ICS cybersecurity assumptions. Stuxnet is more than data filtration, it is the first rootkit targeted at PLCs. It is essentially a weaponized attack against a process. It has the ability to take advantage of the programming software to upload its own code to the PLC."

In addition to the sophisticated attackers, novice users also represent considerable risks. The basic problems of learning bad habits and applying those bad habits into logic diagrams could cause larger security and functionality concerns. It is imperative that a standard be implemented that would at least provide a mechanism for a novice, or experienced users to be able to verify and validate their programs against a defined set of rules.

The tool and methodology we are proposing would allow the code to be easily verified and validated as often as required. This validation would be against a known set of suspect coding practices. Furthermore, this tool, when aligned with a vulnerabilities ranking mechanism, could allow for early alerts into possible points of entry with which to be concerned.

# 2.3 Secure Software Verification Methods and Software Code Review Tools

The 24 Deadly Sins of Software Security: Programming Flaws and How to Fix Them [25] outlines best practices for generalized software development. We cross reference these methods to expand and validate our table of vulnerabilities. SOA Design Patterns [13] outlines various methods for creating correct design patterns. We use the methods found within this text as a framework for the creation of the design patterns which support secure software development. Furthermore, there are other code security and static analysis tools currently in existence for traditional software development. However, none of these tools are capable of handling ladder logic software. Moreover, the recommended best practices are too general to provide valuable guidance in the complex context of SCADA control systems [27]. Taxonomies of software errors can be used to model PLC ladder logic vulnerabilities. Seven Pernicious Kingdoms: A Taxonomy of Software Security Errors [10] suggests a methodology for building a taxonomy to "help developers and security practitioners understand common types of coding errors that lead to vulnerabilities. By organizing these errors into a simple taxonomy, we can teach developers to recognize categories of problems that lead to vulnerabilities and identify existing errors as they build software." We believe a similar solution can be developed which specifically addresses PLC ladder logic software. Our intention is to assist the practitioner in understanding the common types of errors as stated above, while providing a methodology to mitigate these errors. This, in turn, will provide a means to mitigate the security risk created by the errors documented in the vulnerability taxonomy. Furthermore, Landwehr [1]

classified security flaws based on three dimensions, genesis, time of introduction and location. The genesis classification creates two subcategories for flaws, intentional and inadvertent. The Severity Chart that we create provides a similar grouping for the development of the Severity Engine within the Static Analysis Tool: novice and malicious users.

## 2.4 Limitations of SCADA/PLC Security Research

The current SCADA / PLC security research is limited, due to three critical areas. Lack of understanding of all of the exposed entry points into the automation system, which leads to more SCADA software centric research. The lack of sufficient training by current PLC code developers. This creates a culture of trial and error programming, which is due to a lack of best practices standards. The current research in this field does very little to address the training component and development of a best practices approach to PLC coding. Most importantly, there is a lack of tools which can be implemented and used to test current and future code, both after and during development. This network-centric approach, which is important, has become a network biased approach. That is, the research focuses more on the commonly accepted remote access component and seems to ignore the vulnerability created by the existence of insecure application software [47, 48, 49].

#### Chapter 3

#### PROPOSED PLC SECURITY FRAMEWORK

## 3.1 PLC Code Analysis (PLC-SF)

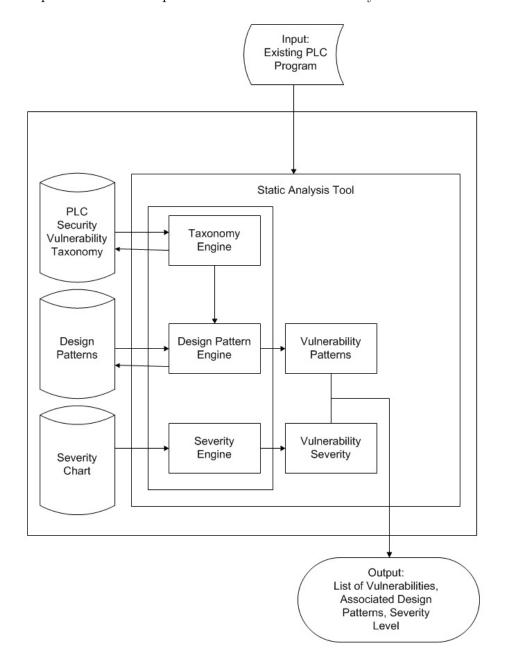

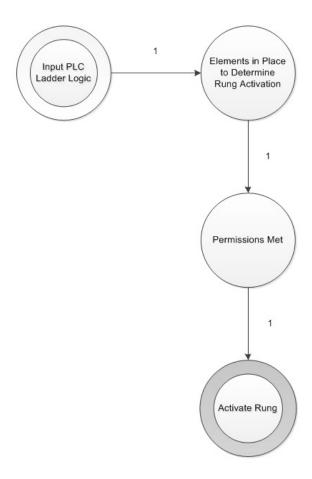

In this work, we address the vulnerabilities in the PLC code itself. The components of our work are shown in Figure 3.1. The input of the PLC Security Framework (PLC-SF) is PLC code that has passed and been accepted by the ladder logic compiler. The Static Analysis Tool, we have developed [51], uses the following three components: PLC Security Vulnerability Taxonomy, Severity Chart and Design Patterns. The output of PLC-SF is list of vulnerabilities and associated design patterns to remove the vulnerabilities.

Currently PLC (ladder logic) code compilers announce any of three states (or a combination or a combination thereof) after the code is compiled. These states are 'compiled without errors', 'compiled with warnings', and 'compiled with errors.' It is assumed by both novice and experienced coders that if the compiler announces 'compiled without errors' that the code is correct. Code that is 'compiled with warnings' may have minor bugs that do not restrict the compilation and the execution of the code by the PLC. Code that is 'compiled with errors' indicates the error, and this code cannot be uploaded to the PLC as long as those error(s) exist. We do not address these errors in this work. However, we anticipate that our Static Analysis Tool will also eliminate some of these errors. The Static Analysis Tool uses the vulnerability taxonomy and the severity chart to detect and rank ladder logic vulnerabilities. It will then compare these vulnerabilities against a set of known design patterns, to

determine a corrective action which would alleviate the vulnerability. We now give a brief description of each component within the Static Analysis Tool.

Figure 3.1: Proposed Security Framework PLC-SF

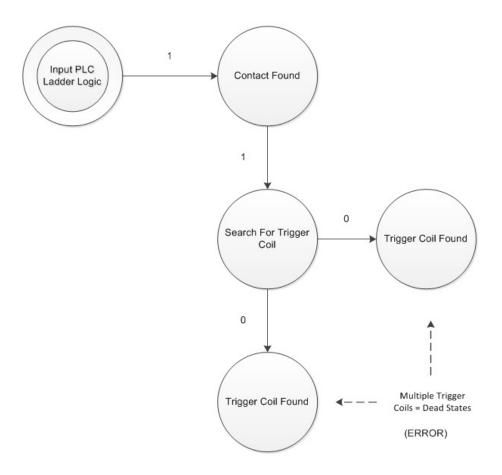

PLC Security Vulnerability Taxonomy: The vulnerability taxonomy is used to conceptualize the vulnerabilities. These vulnerabilities are then depicted using state transition diagrams. Using both the Vulnerability Taxonomy and the associ-

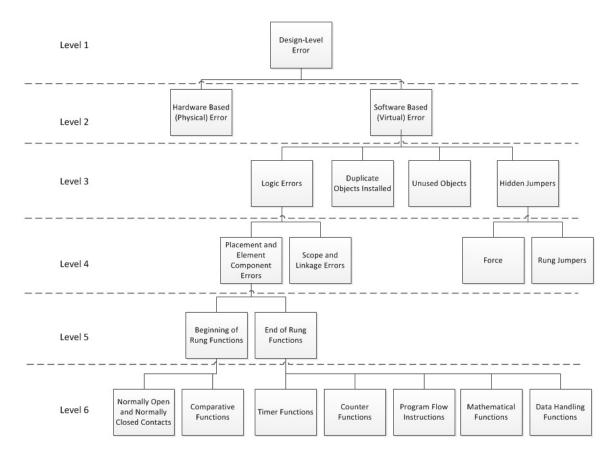

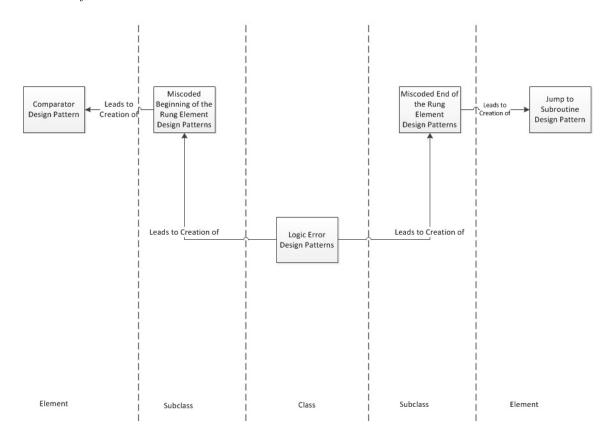

ated state transition diagrams, a Vulnerability Engine was created. This Vulnerability Engine will determine the existence of a vulnerability within the various levels of the taxonomy. The taxonomy that we have created categorizes potential PLC vulnerabilities, as initially depicted in Figures 4.2 through 4.10. The taxonomy is intended to help answer the following questions: "How did this vulnerability occur, and how can it be exploited?" This will then allow for the formulation of detection and prevention methods. Our approach to model PLC vulnerabilities is extensible, representing an initial characterization methodology which can be continually expanded as new vulnerabilities surface. Initially, the taxonomy verifies that, in fact the vulnerability in question is a design-level vulnerability. It is then determined rather the perceived vulnerability is hardware (physical) or software (virtual) based. If it is determined to be hardware based, then the specific subclass is added to the taxonomy, and its physical characteristics mapped. If it is determined to be software-based, then it is determined if a class should be created, or if a subcategory already exists to insert the vulnerability. The Vulnerability Taxonomy will be discussed in detail in Chapter 4, Section 4.4.

Design Patterns: Design patterns show methods of mitigating the vulnerabilities encountered in PLC ladder logic code. We have created design patterns to mitigate the various vulnerabilities listed in the Vulnerability Taxonomy. The design patterns which were modeled, were used to create the Design Pattern Engine. Once a vulnerability is determined to exist, the vulnerability is cross referenced against a list of design patterns in the Design Pattern Engine. The Design Pattern Engine generates design patterns to be given to the user during the output phase of the Static Analysis Tool. The design patterns which were created will be shown and explained in Chapter 5.1.

Table of Vulnerabilities: The table of vulnerabilities groups the vulnerabilities based on the potential consequences of an exploitation. We have assigned a severity

rating to each vulnerability based on the impact of the outcomes to the PLC and SCADA system. Each vulnerability is linked to the table based on the severity level assigned. This will allow the defense to rank the vulnerabilities.

**Severity Chart:** The Severity Chart links the severity level assigned from the table of vulnerabilities to potential effects in both the PLC and SCADA system platforms. The Severity Chart is the basis on which the Severity Engine is created. The Severity Chart is shown in Table 4.1.

Static Analysis Tool: As previously stated, the Static Analysis Tool takes as its input PLC ladder logic code, determines the existence of a vulnerability within that code, the severity level, or levels, that exist within that vulnerability and the design pattern, or patterns, that can be used to map the best probable solution. This is accomplished by the Static Analysis Tool using three different engines to represent the three distinct internal components. These are the taxonomy, design pattern and severity engines and will be explained in Chapter 6.

List of Vulnerabilities and Associated Design Patterns: The output will consist of a list of the vulnerabilities and their associated design patterns as determined by the static analysis tool. The Static Analysis Tool will determine the existence of the vulnerability, the severity level and the associated design pattern based on the existence of certain strings in regular expressions. This will be explained in detail in Chapter 6.

# 3.2 Malicious Entry Points

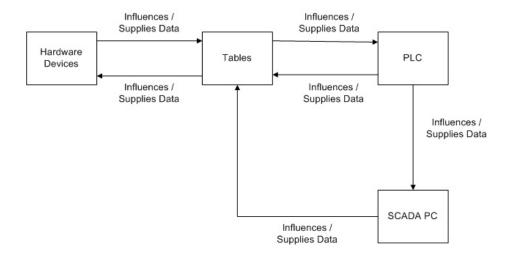

We also studied the interaction between the PLC and other SCADA components. The data input source for the PLC ladder logic are numeric tables that store sensor (device) data. Figure 3.2 demonstrates the standard control flow of a SCADA system. The numeric tables, which consist of binary, floating point, and integer data are the

control repository for the entire system. Erroneous data in these tables may corrupt PLC execution and, therefore, the entire SCADA system. In addition to direct access, there are three ways to modify table entries; data from hardware devices, the PLC ladder logic, and the SCADA PC.

Figure 3.2: SCADA System Control Flow

Hardware devices are devices that monitor or initiate process execution such as variable frequencies drives, proportional-integral-derivative (PID) controllers and Human Machine Interface (HMI) devices. This classification includes all of the physical devices that have the ability to directly receive from, or deliver data to, the PLC. Although wireless communications mediums are available for certain hardware devices and more recent PLC controllers, the communication medium of choice is still the hardwired approach. Using the hardwired approach as our basis of communication, hardware devices can be further classified as those devices which are wired directly to a PLC input or output card.

The PLC Ladder logic, has a direct link to the data tables. The ladder logic code, as well as the data tables are embedded into the CPU on the PLC once they are uploaded. Therefore, there is no external communication necessary to maliciously alter the data, directly or via PLC code, if someone accesses the PLC CPU.

The SCADA PC is used not only to view data but can also be configured to allow the user to input data directly into the PLC, by way of the control tables. This ability is through the database that is resident on the SCADA PC itself. This database is part of the front end of the SCADA package that is installed on the PC. The SCADA PC database, not unlike the data tables on the PLC, not only holds information in the form on numeric data, but also data location information for write and read purposes into the data tables.

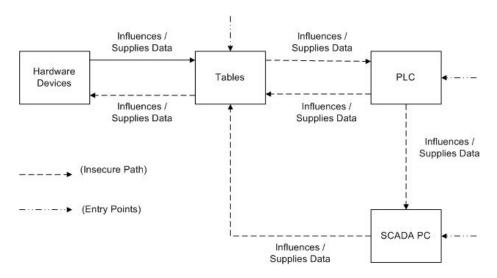

Figure 3.3 illustrates the four data entry points that may be exploited by malicious users. Users may exploit these points of entry, directly or indirectly, to modify control data. The dashed lines represent the insecure pathways that exist between each SCADA component. We do not generalize the hardware devices into a specific group that can be accessed directly. This is due to the existence of multiple devices, currently in use in the field, that do not have the capability of direct network access.

Figure 3.3: SCADA System Control Flow Possible Malicious Entry Points

## Chapter 4

# Vulnerabilities Analysis

Current ladder logic compilers are not designed to detect security vulnerabilities or subtle logic errors. PLC code, that was compiled without error, may still contain vulnerabilities. These vulnerabilities can be subtle enough that the novice user would not be aware of the possible security risks they represent. Malicious users may exploit these vulnerabilities and cause severe damage. In this chapter, we outline the vulnerability taxonomy and the consequences of their exploitation.

We also associate the vulnerability taxonomy, a severity chart and potential actions that can be carried out by malicious users. Each attack (error) has severity ratings assigned to it, as shown in Table 4.2. Section 4.3 develops a classification mechanism for process critical and nuisance errors as previously defined. The categories shown are broad in scope so as not to be process limiting or process specific. Table 4.3 lists the error type, error classification and opportunities presented to a malicious user through the existence of each error.

## 4.1 Attack Severity Analysis

This section outlines the attack severity chart as well as the novice and malicious users ability to create each level of severity.

We will present detailed descriptions of the severity classifications and examples of their associated effects. These classifications will allow for the foundation of a best practices guide. Table 4.1 gives a general and functional overview of each of

the severity rankings created [50]. This table outlines the severity level which would be applied under each of the scenarios shown. Each row of the table represents a different level of security, 'A' being the most severe and 'D' being the least. Each column represents the effects in the PLC and the SCADA system, respectively.

Table 4.1: Severity Chart

| Severity | Effects in PLC                 | Effects in SCADA             |

|----------|--------------------------------|------------------------------|

| A        | PLC code will not perform      | Will not allow for remote    |

|          | the desired tasks              | operation of the process     |

| В        | Serious hindrance to the       | The process may appear       |

|          | process                        | to be operating correctly,   |

|          |                                | but given optimal condi-     |

|          |                                | tions, the machine could be  |

|          |                                | thrown into an unexpected    |

|          |                                | process failure              |

| С        | Adversely effects PLC code     | Data shown on the SCADA      |

|          | performance. A minimal         | screen is most likely false. |

|          | cost effect to the project but |                              |

|          | a "quick fix" is possible.     |                              |

| D        | Effects the credibility of the | Incorrect data could ran-    |

|          | system, but PLC code is op-    | domly be reported causing    |

|          | erable.                        | a lack of confidence in the  |

|          |                                | system and therefore caus-   |

|          |                                | ing the system to be "disre- |

|          |                                | garded" even if the informa- |

|          |                                | tion is relevant.            |

## 4.1.1 Severity Classifications

It is critical that each severity level depicts not only the outcomes that can be detrimental to the SCADA system as a whole, but the effect on the individual components as well. These individual components can be any of the automated components which are PLC controlled. We will now give a description of each of severity level.

#### Severity Level 'A'

• A concern is considered as severity level 'A' if its existence could potentially cause all, or part, of a critical process to become non-functional. Furthermore, residual effects may include malfunctioning of other processes who's outcomes are determined by the process at risk. For example, consider the situation when the mechanism that causes heat to be released from a process is no longer functional. However, the heat continues to be generated into the process. If this situation were not corrected expediently then the device that stores the energy may be damaged, even destroyed.

#### Severity Level 'B'

• A concern is considered as severity level 'B' if its existence could potentially cause all, or part, of a critical process to perform erratically. This differs from severity level 'A' in terms of the absolution of the result. Severity level 'A' concerns have the potential to cause permanent process failure, whereas level 'B' concerns would cause incremental process interruptions.

#### Severity Level 'C'

• Severity level 'C' concerns are denoted as quick fixes. The errors are most likely created by 1) a novice user without a good fundamental knowledge of PLC programming components or 2) a malicious user who wishes to cause functional problems.

#### Severity Level 'D'

• Severity level 'D' concerns involve providing false or misrepresented information to the SCADA terminal itself.

# 4.2 Examples of Severity Level Effects

In this section, we present examples of each of the severity levels defined in section 4.1.1. We will use the data from table 4.3 as the basis for each.

#### Example of Severity Level 'A':

Hidden Jumpers: A hidden jumper could involve either a force, an empty branch, or a branch with a normally closed contact that has no trigger coil associated with the contact. Hidden jumpers have the potential to be a severity level 'A' concern in that they could cause all, or part, or a given rung to be inoperable.

#### Example of Severity Level 'B':

Duplicate Objects: If a duplicate object is installed in the ladder logic, it presents the potential for the occurrence of two distinct issues. First, the duplicate object could fail to let either rung, in which the logic is installed, to activate. Second, duplicate objects can operate on an incremental trigger basis. In this scenario, the logic would randomly select one of the objects to activate.

#### Example of Severity Level 'C':

Logic Errors: A logic error could involve any element or number of elements within the context of the PLC program itself. We will show this error, in context, using a timer element. The concern lies in the alteration of the timer preset. Initially, the timer preset would be set to a certain value. If a novice or malicious user alters this preset value positively or negatively, severe damage could occur within the process. Assuming the process is programmed based on time delay and not on physical sensor technology, placing one timer out of sequence potentially could alter the entire process.

#### Example of Severity Level 'D':

Creation of false information: Information that is incorrectly transmitted due to incorrect implementation of specific functions such as timers or math functions.

## 4.3 Potential Exploitation of Coding Errors

We start the section with a discussion on the effect of the PLC users' knowledge. Then, we present a collection of coding errors and intentional attacks against PLCs and SCADA networks.

## 4.3.1 Knowledge of the User

As shown in Table 4.2, we outline a set of criteria based on the knowledge of the user. We define a user both in terms of a novice user as well as a malicious user. We acknowledge that a novice user could be malicious and a malicious user could make unintended mistakes just as a novice user. Our contention for these two initial knowledge level classifications is not to disregard the possibilities of crossover, but only to serve as a basis for preliminary data development. Recognizing the advanced level of a malicious user as opposed to a novice user, Table 4.2 makes the assumption that any function that can be performed by a novice user could also be performed by a malicious user. Under this criteria, we will apply the following definitions throughout the remainder of this dissertation: A novice user is considered to be an individual that is authorized to work on and view the system, but lacks the correct training or experience. A Malicious user is considered as both an authorized user with malicious intent as well as an individual that is not authorized to access the system.

Typically a malicious user is capable of performing all of the functions that would be expected of a novice user. An unauthorized malicious user may also have the capability to hack into the SCADA system, or any computer that would have the programming software required to view, or alter, the PLC ladder logic program. Furthermore, a malicious user would most likely have an advanced knowledge of control systems and their integrated components which were explained in Section 3.2 and shown in Figure 3.3.

Table 4.2: Severity Rating vs. Attacker's Knowledge

| Severity | Novice User                  | Malicious User                        |

|----------|------------------------------|---------------------------------------|

| A        | Inserts incorrect code.      | Inserts hidden IO reference           |

|          | Fails to remove unused ta-   | points as a potential back            |

|          | ble locations prior to com-  | door into the program.                |

|          | pilation.                    |                                       |

|          | Incorrect IP addressing of   |                                       |

|          | PLC network components.      |                                       |

| В        | Lack of knowledge of cor-    | Uses advanced knowledge               |

|          | rect implementation of       | of software and hardware              |

|          | certain software compo-      | implementation to correctly           |

|          | nents.                       | place ladder logic code and           |

|          | Lack of knowledge of cor-    | IO reference points in <i>incor</i> - |

|          | rect implementation of       | rect locations.                       |

|          | certain hardware compo-      |                                       |

|          | nents.                       |                                       |

|          |                              |                                       |

| С        | Detailed labeling of rungs,  | Uses the current notation             |

|          | components and devices.      | system to incorrectly label           |

|          |                              | rung and component func-              |

| _        |                              | tionality.                            |

| D        | Incorrectly scales values to | Everything that a novice              |

|          | be sent to the SCADA dis-    | user may unintentionally              |

|          | play                         | perform.                              |

We give a brief overview of the coding errors and potential exploitation by malicious users. In Table 4.3, these errors are organized into two main categories, process critical errors and nuisance errors.

Process Critical Errors represent those errors that could cause a severe failure in the process operation and can be affected once access is gained to the PLC CPU.

Nuisance Errors represent those errors that would cause minimal process issues and are relatively easy to find.

### 4.3.2 Process Critical Errors

We have identified the following process critical error categories. We also show examples of how to exploit of some of these errors.

- Duplicate Objects: Objects that have been defined more than once. These objects could include things such as coils, timers and counters. Using our proposed severity rating system, this would have a severity rating of 'A' based on the potential for total process failure.

- Unused Objects: Objects which were defined in the initial database, but were never used in the ladder logic. These pre-loaded variables can be used for random functions. This is given a severity rating of 'A' since the extent to which the unused objects are employed will determine the extent of the consequences.

- Scope and Linkage Errors: Such errors deal with the deletion of, or failure to install, a communication block between two or more separate ladders in a PLC program. This would have a severity rating of 'A' based on the potential for total process failure.

- Logic Errors: Errors that could occur result in state transition, timing, control and data flow issues. This error could be classified as 'A–C', depending on the extent of the logic error and the specific device effected.

- Syntax Errors (or warnings): Warnings that were problematic in compilation, but compilation was not restricted. This code is downloaded to the processor with no more than a warning to the individual downloading to the device. This error is classified as a level 'B' concern due to the fact that initially, no symptoms were present and intermittent failure could occur.

### 4.3.3 Nuisance Errors

We have identified the following nuisance error categories:

Hidden Jumpers: These software jumpers effectively bypass a portion of a rung

in a ladder logic routine. These are easily hidden to the untrained eye, and are

not searchable utilizing the current PLC platforms. This error has the potential

to be classified at any level. The severity and consequences depends solely on

the location of the jumper.

Table 4.3: Development Error vs. Opportunity

| Error Type                  | Taxonomy Classification     | Malicious User Opportu-        |

|-----------------------------|-----------------------------|--------------------------------|

|                             |                             | nity                           |

| Process Critical / Nuisance | Duplicate objects installed | Alteration of one or more of   |

|                             |                             | the duplicate objects          |

| Process Critical            | Unused objects              | Pre-loaded variables allow for |

|                             |                             | an immediate entry point into  |

|                             |                             | the system with no additional  |

|                             |                             | requirements on the database   |

| Process Critical            | Scope and linkage errors    | Installation of jump to sub-   |

|                             |                             | routine command which          |

|                             |                             | would alter the intended file  |

|                             |                             | to file interaction            |

| Process Critical            | Logic errors                | Immediate entry point to       |

|                             |                             | logic level components such    |

|                             |                             | as timers, counters and arith- |

|                             |                             | metic operations               |

| Process Critical            | Syntax Errors               | Could cause the system to act  |

|                             |                             | intermittently erratic, there- |

|                             |                             | fore causing future alarms to  |

|                             |                             | be ignored                     |

| Process Critical / Nuisance | Hidden Jumpers              | Could allow a placement point  |

|                             |                             | for system bypass scenario to  |

|                             |                             | occur                          |

# 4.4 Building the Vulnerability Taxonomy