#### ISSUES OF ESD PROTECTION IN NANO-SCALE CMOS

by

Yang Yang A Dissertation Submitted to the Graduate Faculty of George Mason University In Partial fulfillment of The Requirements for the Degree of Doctor of Philosophy Electrical and Computer Engineering

Committee:

Dr. Dimitris E. Ioannou, Dissertation Director

Dr. Qiliang Li, Committee Member

Dr. Rao V. Mulpuri, Committee Member

Dr. Dimitrios A. Papaconstantopoulos, Committee Member

Dr. Andre Manitius, Chair, Electrical and Computer Engineering Department

Dr. Lloyd J. Griffiths, Dean, The Volgenau School of Information Technology and Engineering

Summer 2010 George Mason University Fairfax, VA

#### Issues of ESD protection in nano-scale CMOS

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at George Mason University

By

Yang Yang Master of Science Queen's University Belfast, 2005 Bachelor of Science Beihang University, 2004

Director: Dr. Dimitris E. Ioannou, Professor Department of Electrical and Computer Engineering

> Summer 2010 George Mason University Fairfax, VA

Copyright © 2010 by Yang Yang All Rights Reserved

# Dedication

I dedicate this dissertation to my parents and my fiancee, Juan Wang, for their patience, tolerance and constant support during the completion of this dissertation.

## Acknowledgments

This work could not have been completed without the support of several people.

First, I would like to express my deepest gratitude to my advisor, Prof. Dimitris E. Ioannou, for his insight, guidance, encouragement and support during my graduate study at George Mason University. His critical thinking skills and clarity of thinking made working with him an enjoyable and rewarding experience. I consider myself extremely fortunate to have Prof. Ioannou as my academic advisor.

I would also like to express my thanks to Akram A. Salman who was an ESD engineer with Advanced Micro Devices, for his guidance and suggestions on the project of field-effect-diode at the initial stage of my graduate study. His continued encouragement and motivation during that project helped me a lot.

Most of the experimental work related to this thesis was done at the IBM Microelectronics Div. Semiconductor Research & Development Center, Essex Junction, VT-05452 while on a student internship. I would like to express my sincere thanks to my manager at IBM, Robert J. Gauthier Jr. and other colleagues, Junjun Li, Kiran Chatty, Souvick Mitra, Rahul Mishra, James Di Sarro, Ralph Halbach and Christopher Seguin for their support and insightful discussions.

My special thanks to Prof. Qiliang Li, Prof. Rao V. Mulpri and Prof. Dimitrios A. Papaconstantopoulos for accepting to serve in my doctoral advisory committee and the valuable knowledge I learned from them during the courses they taught.

The financial support of my research by National Science Foundation is gratefully acknowledged.

Finally, I would like to thank my parents and my fiancee Juan Wang, whose support and love made this work possible.

# Table of Contents

|     |        |          |                                                                                                   | Page |

|-----|--------|----------|---------------------------------------------------------------------------------------------------|------|

| Lis | t of [ | Tables   |                                                                                                   | viii |

| Lis | t of I | Figures  |                                                                                                   | ix   |

| Ab  | strac  | t        |                                                                                                   | XV   |

| 1   | Intr   |          | pn                                                                                                |      |

|     | 1.1    |          | ation                                                                                             |      |

|     | 1.2    |          | tation Organization                                                                               |      |

| 2   | Rev    | riew of  | ESD and gate dielectric breakdown and degradation $\ldots \ldots$                                 | 10   |

|     | 2.1    | ESD (    | Characterization Models                                                                           | 11   |

|     |        | 2.1.1    | Human Body Model                                                                                  | 11   |

|     |        | 2.1.2    | Machine Model                                                                                     | 12   |

|     |        | 2.1.3    | Charged Device Model                                                                              | 14   |

|     | 2.2    | Trans    | mission Line Pulsing method                                                                       | 15   |

|     | 2.3    | ESD I    | protection strategy                                                                               | 16   |

|     |        | 2.3.1    | Double diode based ESD protection strategy                                                        | 17   |

|     |        | 2.3.2    | Local clamp device based ESD protection strategy                                                  | 18   |

|     |        | 2.3.3    | CDM protection strategy                                                                           | 19   |

|     |        | 2.3.4    | Necessity of Local Clamping                                                                       | 21   |

|     | 2.4    | Backg    | round on gate dielectric degradation and breakdown $\ldots$                                       | 21   |

|     |        | 2.4.1    | Necessity of introducing high-k gate dielectrics                                                  | 22   |

|     |        | 2.4.2    | Physical models for gate dielectric degradation and breakdown                                     | 24   |

|     |        | 2.4.3    | Gate oxide breakdown statistics                                                                   | 25   |

|     |        | 2.4.4    | Post breakdown mode                                                                               | 29   |

|     |        | 2.4.5    | TDDB and latent oxide damage under ESD-like stress $\ . \ . \ .$                                  | 30   |

|     | 2.5    | Summ     | nary                                                                                              | 35   |

| 3   | Cha    | racteriz | zation of High-k/Metal Gate Stack Breakdown in the Time Scale                                     |      |

|     | of E   | SD Eve   | $\mathrm{nts}$                                                                                    | 37   |

|     | 3.1    | Introd   | luction $\ldots$ | 37   |

|   | 3.2  | Typical stress conditions on gate dielectric during ESD Events $\ . \ . \ .$ | 38 |

|---|------|------------------------------------------------------------------------------|----|

|   |      | 3.2.1 Input receiver under ESD stress                                        | 39 |

|   |      | 3.2.2 Output Driver under ESD Stress                                         | 41 |

|   | 3.3  | Device Selection                                                             | 43 |

|   | 3.4  | High-k gate dielectric breakdown with stress applied on the gate $\ . \ .$   | 44 |

|   |      | 3.4.1 Experimental details                                                   | 45 |

|   |      | 3.4.2 Gate oxide breakdown detection                                         | 46 |

|   |      | 3.4.3 Gate oxide failure: hard or soft?                                      | 51 |

|   |      | 3.4.4 Effect of stress interruption on high-k gate dielectric breakdown      | 53 |

|   |      | 3.4.5 Time-to-breakdown of high-k gate dielectric                            | 55 |

|   |      | 3.4.6 Comparison of high-k gate dielectric with SiON gate dielectric         | 59 |

|   | 3.5  | High-k gate dielectric breakdown with stress applied on the drain $~$ .      | 60 |

|   | 3.6  | Comparison between CVS and TLP method $\ldots \ldots \ldots \ldots \ldots$   | 62 |

|   | 3.7  | Method to improve the circuit immunity to GOX breakdown induced              |    |

|   |      | failure                                                                      | 66 |

|   | 3.8  | Summary                                                                      | 69 |

| 4 | Deg  | gradation of High-k/Metal Gate NMOSFETs under ESD-like Stress $$ .           | 71 |

|   | 4.1  | Introduction                                                                 | 71 |

|   | 4.2  | Experiment Details                                                           | 72 |

|   | 4.3  | Effects of ESD-like stress applied on the gate                               | 73 |

|   |      | 4.3.1 Threshold voltage shift and drain current degradation                  | 73 |

|   |      | 4.3.2 Degradation of the gate dielectric/Si interface                        | 78 |

|   |      | 4.3.3 Comparison of SiON and high-k NMOSFETs                                 | 82 |

|   |      | 4.3.4 Effect on gate leakage current                                         | 83 |

|   |      | 4.3.5 Effect on device PBTI kinetics                                         | 85 |

|   | 4.4  | Effects of ESD-like stress applied on the drain                              | 86 |

|   | 4.5  | Summary                                                                      | 88 |

| 5 | Des  | sign and Optimization of the SOI Field Effect Diode (FED) for ESD            |    |

|   | Prot | ection                                                                       | 90 |

|   | 5.1  | Introduction                                                                 | 90 |

|   | 5.2  | Simulation of FED                                                            | 93 |

|   | 5.3  | FED Design Space and Discussion                                              | 94 |

|   | 5.4  | Experimental verification                                                    | 99 |

|     | 5.5    | Summary                                                    | 100 |

|-----|--------|------------------------------------------------------------|-----|

| 6   | Con    | clusions and future work                                   | 102 |

|     | 6.1    | Conclusions                                                | 102 |

|     | 6.2    | Future work                                                | 104 |

| А   | App    | pendix: Relationship between $V_{BD,CVS}$ and $V_{BD,TLP}$ | 107 |

| Bil | oliogr | aphy                                                       | 109 |

# List of Tables

| Table |                                                                                   | Page |

|-------|-----------------------------------------------------------------------------------|------|

| 1.1   | A general scaling rule leading to an integrated circuit with a faster             |      |

|       | speed, and enhanced functionalities have been the major success of the            |      |

|       | past history of microelectronics $[1]$                                            | 3    |

| 1.2   | Scaling of power supply voltage, oxide thickness and oxide field in               |      |

|       | several CMOS technology generations [2]. $^{\ast}$ this data is taken from the    |      |

|       | latest 32 nm technology.                                                          | 4    |

| 2.1   | Dielectric materials and their relative permittivities [3]. $\ldots$ $\ldots$     | 24   |

| 4.1   | Breakdown voltages $(V_{BD})$ for time-to-breakdown $t_{63\%} = 100$ ns at $63\%$ |      |

|       | cumulative failure rate for SG and EG NMOSFETs in both inversion                  |      |

|       | (inv) and accumulation (acc). The data were obtained by Constant                  |      |

|       | Voltage Stress (CVS) measurements.                                                | 73   |

|       |                                                                                   |      |

# List of Figures

| Figure |                                                                                                                          | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------|------|

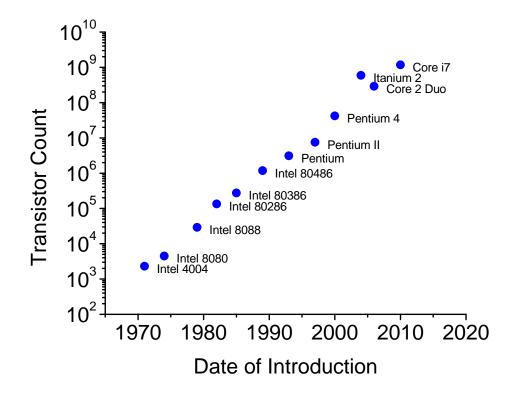

| 1.1    | Plot of transistor counts against dates of introduction [4]. $\ldots$ .                                                  | 2    |

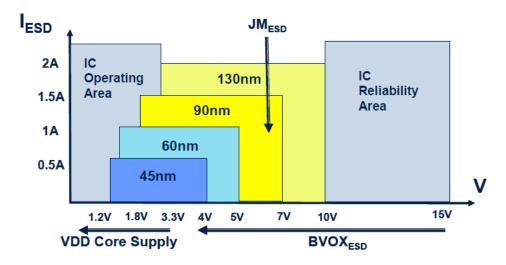

| 1.2    | Impact of technology scaling on ESD design window [5]. $\ldots$ .                                                        | 5    |

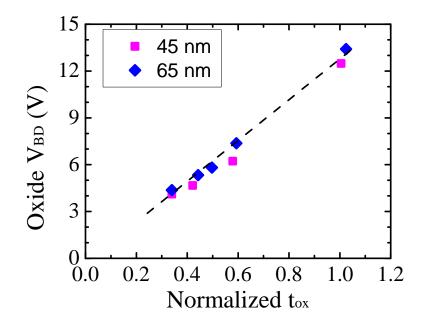

| 1.3    | Reduction of gate oxide breakdown voltage as the gate dielectric thick-                                                  |      |

|        | ness scales down. The data correspond to a breakdown time of $100$                                                       |      |

| 2.1    | ns                                                                                                                       | 6    |

|        | charged to the test voltage, $V_{ESD}$ , and then discharged through $R_s$ to                                            |      |

|        | the device under test (DUT) by closing the switch. Parasitic circuit                                                     |      |

|        | elements are represented by series inductance $L_s$ , stray capacitance $C_s$ ,                                          |      |

|        | and test-board capacitance $C_t$ . The typical circuit parameters are (a)                                                |      |

|        | $C_C = 100 \text{ pF}, L_s = 7.5 \ \mu\text{H}, R_S = 1500 \ \Omega \text{ and } C_s = 1 \text{ pF} \text{ for HBM and}$ |      |

|        | (b) $C_C = 200 \text{ pF}, L_s \approx 2.5 \ \mu\text{H}, R_S = 5 \ \Omega \text{ and } C_s = 1 \text{ pF} [6].$         | 11   |

| 2.2    | A typical waveform for a 2000 V HBM event [6]                                                                            | 12   |

| 2.3    | A typical waveform for a 200 V MM event with two different series                                                        |      |

|        | inductance $[6]$                                                                                                         | 13   |

| 2.4    | The equivalent circuit model for CDM. $C_{CDM}$ is the sum of all ca-                                                    |      |

|        | pacitances in the DUT and the package with respect to ground and                                                         |      |

|        | $R_{CDM}$ is the total resistance of the discharge path. $C_{CDM}$ , $R_L$ and $L_S$                                     |      |

|        | represent the DUT [7]. The device under test is charged and then dis-                                                    |      |

|        | charged through a pin to ground. For 500 V CDM, the typical model                                                        |      |

|        | parameters are $C_{CDM} = 10 \text{ pF}, R_{CDM} = 10 \Omega, R_L = 10 \Omega \text{ and } L_s = 10$                     |      |

|        | $\mathrm{nH}.\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .$                                                                    | 14   |

| 2.5    | A typical waveform for a 500 V CDM event                                                                                 | 15   |

| 2.6    | TLP uses a series of square wave pulses of varying magnitude and a                                                       |      |

|        | constant pulse width to stress the device                                                                                | 16   |

| 17<br>19<br>20<br>23 |

|----------------------|

| 19<br>20             |

| 19<br>20             |

| 19<br>20             |

| 19<br>20             |

| 20                   |

|                      |

| 23                   |

| 23                   |

|                      |

|                      |

|                      |

|                      |

| 27                   |

| 27                   |

|                      |

| 28                   |

|                      |

|                      |

| 30                   |

|                      |

| 31                   |

|                      |

| 33                   |

|                      |

| 35                   |

| 40                   |

| 42                   |

|                      |

| 44                   |

| 45                   |

|                      |

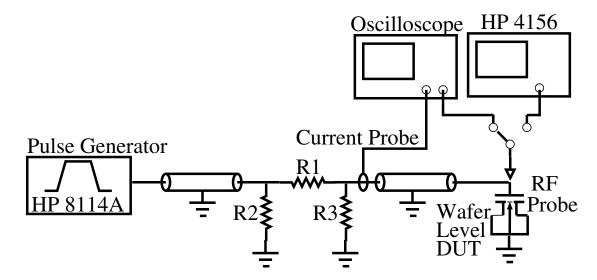

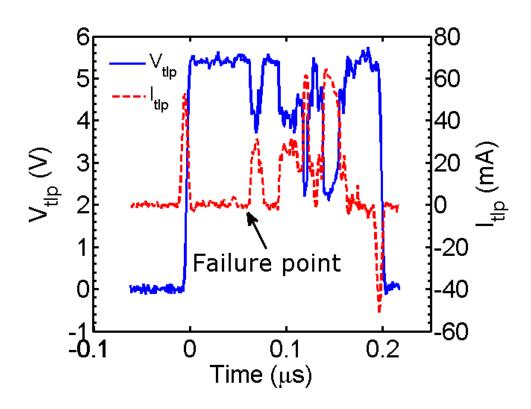

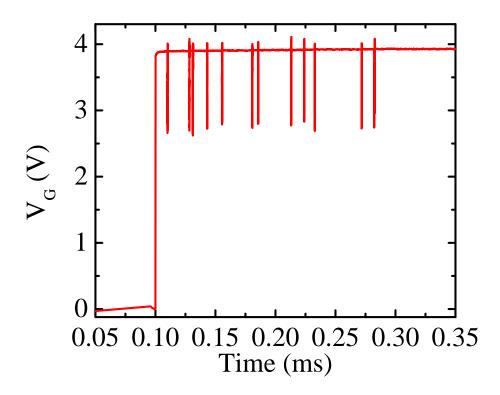

| 3.5  | Typical gate voltage waveform for an NMOSFET with high-k gate                                                    |    |

|------|------------------------------------------------------------------------------------------------------------------|----|

|      | dielectric illustrating the feature of gate dielectric breakdown                                                 | 47 |

| 3.6  | Voltage drop and then recovery forms multiple spikes on the captured                                             |    |

|      | voltage waveform. The number of spikes is well correlated with the                                               |    |

|      | number of gate fingers                                                                                           | 48 |

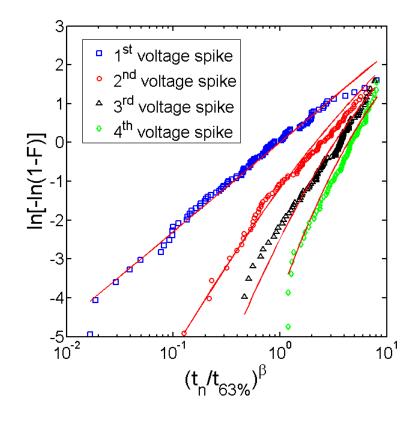

| 3.7  | The cumulative distributions of $t_1$ , $t_2$ and $t_3$ , where $t_n$ represents the                             |    |

|      | time when the $n^{th}$ voltage drop occurs                                                                       | 49 |

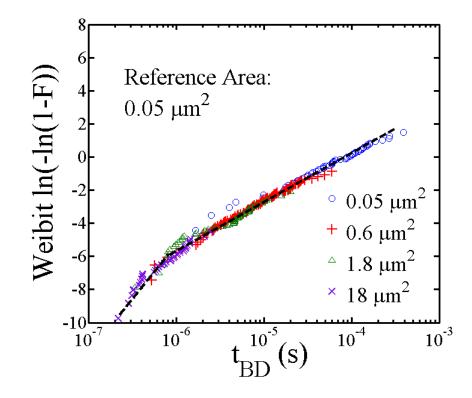

| 3.8  | Gate oxide failure follows the area scaling law, indicating that the                                             |    |

|      | breakdown follows the intrinsic breakdown process                                                                | 50 |

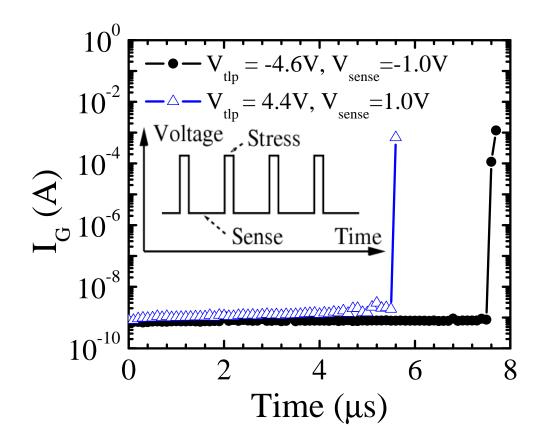

| 3.9  | RCVS shows that gate leakage current changes slightly before the hard                                            |    |

|      | failure. The breakdown features an abrupt increase in $I_G$                                                      | 51 |

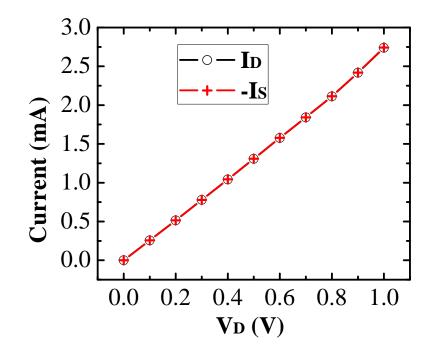

| 3.10 | The drain to source current after gate oxide breakdown under either                                              |    |

|      | positive or negative stresses showed a resistor-like characteristics for                                         |    |

|      | devices with different channel lengths (SG: 50 nm and EG: 150 nm) $$ .                                           | 52 |

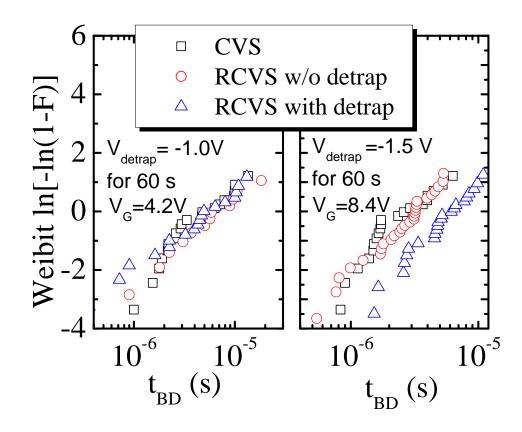

| 3.11 | Effect of stress interruption and charge detrapping on the $t_{BD}$ of thin                                      |    |

|      | (left) and thick (right) oxide devices. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                             | 53 |

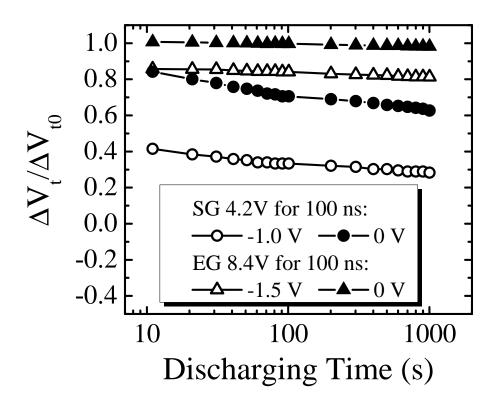

| 3.12 | Recovery of threshold voltage at different gate voltages indicates that                                          |    |

|      | the trapped electrons inside the gate stack were detrapped during the                                            |    |

|      | period when the stress was interrupted                                                                           | 54 |

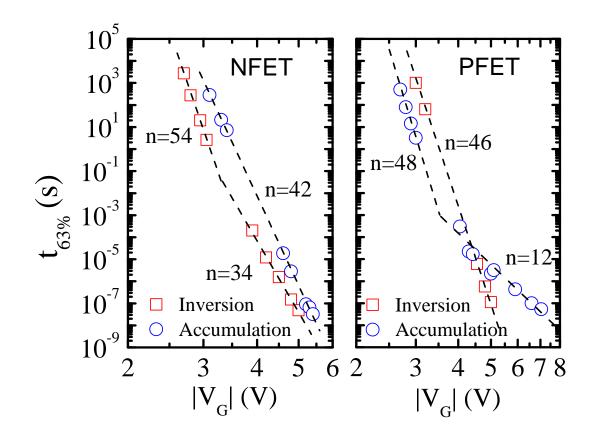

| 3.13 | $\label{eq:constraint} \ensuremath{\text{Time-to-breakdown of thin-oxide MOSFETs with high-k gate dielectrics},$ |    |

|      | obtained using the CVS method.                                                                                   | 56 |

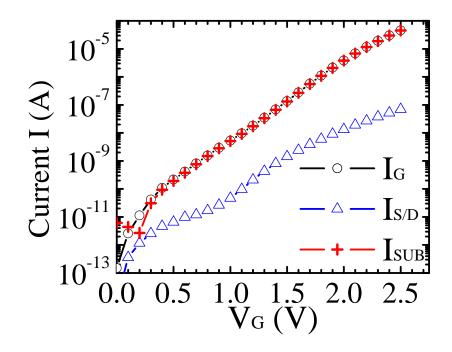

| 3.14 | Terminal currents measured on a PMOSFET in accumulation (posi-                                                   |    |

|      | tive stress).                                                                                                    | 57 |

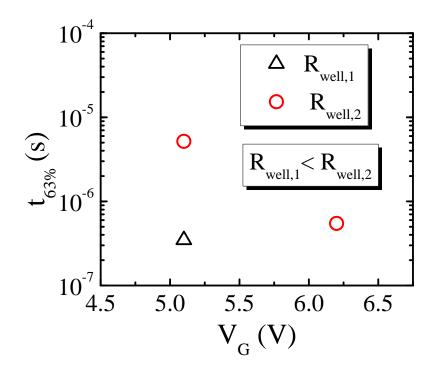

| 3.15 | The effect of well resistance on $t_{63\%}$ of PMOSFETs in accumulation                                          | 58 |

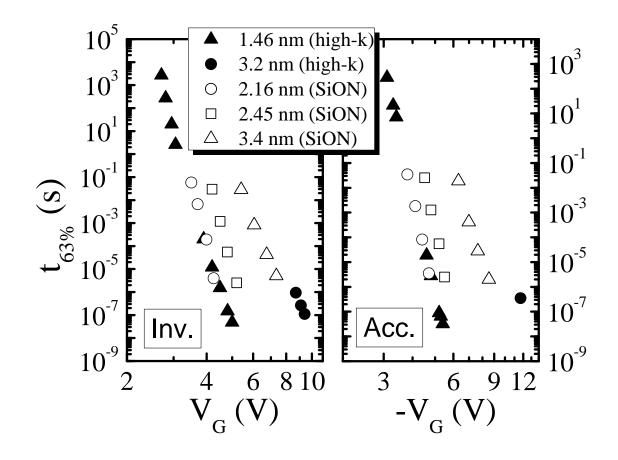

| 3.16 | Comparison of $t_{63\%}$ between high-k and SiON gate dielectrics                                                | 59 |

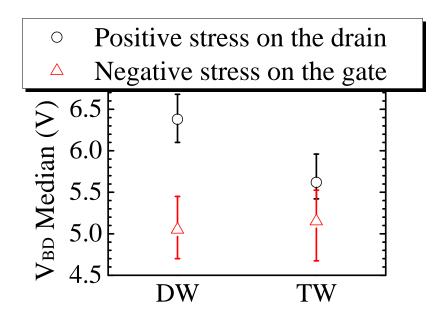

| 3.17 | Gate dielectric $V_{BD}$ for positive stress on the drain with gate grounded                                     |    |

|      | and substrate/source floating, in comparison with the VBD for nega-                                              |    |

|      | tive stress on the gate with other terminals grounded                                                            | 62 |

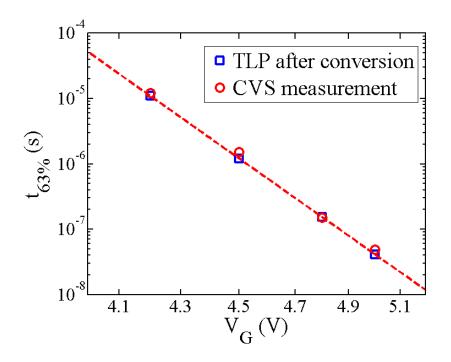

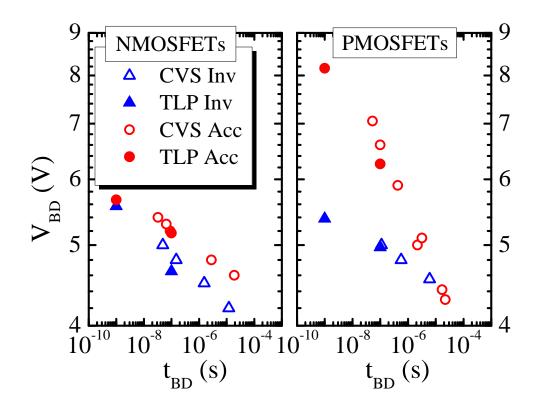

| 3.18 | Data collected using the TLP method can be converted to $t_{63\%}$ , which                                       |    |

|      | is comparable to $t_{63\%}$ measured using the CVS method                                                        | 63 |

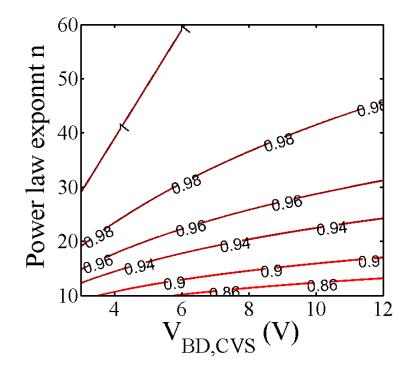

| 3.19 | Contour plot of $V_{BD,TLP}/V_{BD,CVS}$ as a function of power law exponent                                                                             |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | (n) and the breakdown voltage from CVS $(V_{BD,CVS})$ with TLP voltage                                                                                  |     |

|      | increment step $\Delta V = 0.1$ V                                                                                                                       | 64  |

| 3.20 | Comparison between $V_{BD,CVS}$ and $V_{BD,TLP}$ experiment data. $V_{BD,CVS}$                                                                          |     |

|      | is directly from Fig. 3.13. $t_{BD}$ from the TLP method is the pulse width                                                                             |     |

|      | $t_{pw}$                                                                                                                                                | 65  |

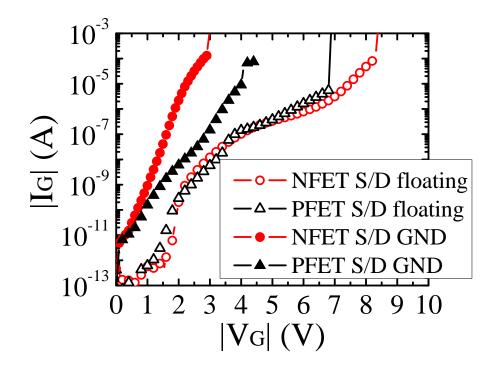

| 3.21 | DC gate leakage current of NFET and PFET in inversion with source/drain                                                                                 | n   |

|      | grounded or with source/drain floating                                                                                                                  | 66  |

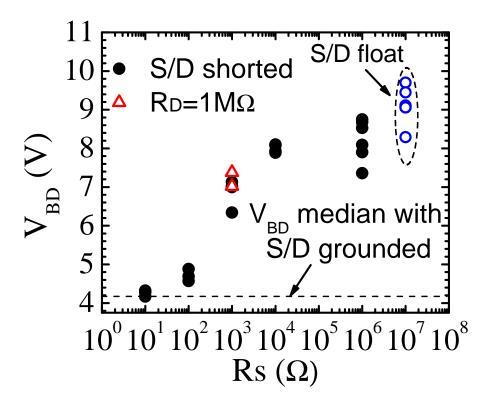

| 3.22 | Breakdown voltage of NFET in inversion is increased when source/drain                                                                                   |     |

|      | resistance is increased.                                                                                                                                | 67  |

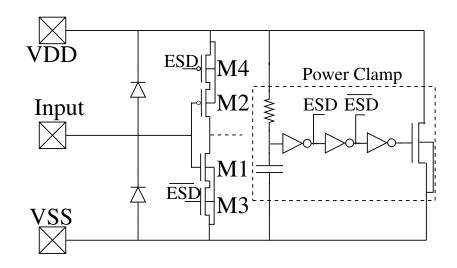

| 3.23 | Additional transistors M3 and M4 are used so as to increase the break-                                                                                  |     |

|      | down voltage of NMOSFET and PMOSFET in inversion                                                                                                        | 69  |

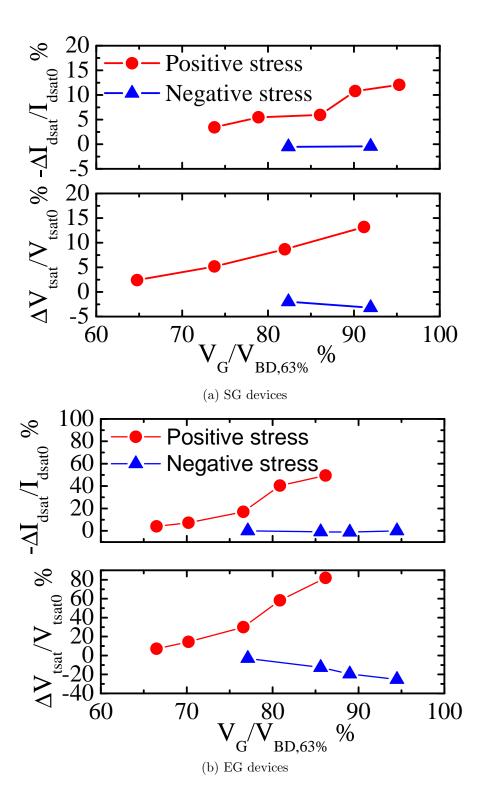

| 4.1  | Positive and negative pulsed stress induced degradation on drain sat-                                                                                   |     |

|      | uration current and threshold voltage for: (a) SG and (b) EG devices.                                                                                   |     |

|      | Each device was stressed by a single pulse of 100 ns long                                                                                               | 74  |

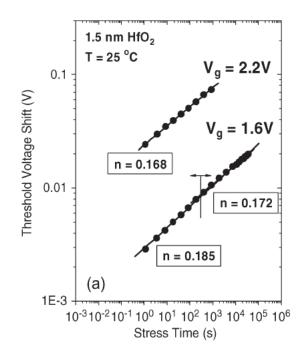

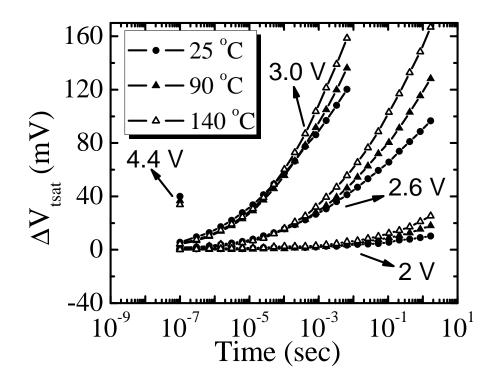

| 4.2  | Temperature dependence of the stress induced threshold voltage shift                                                                                    |     |

|      | at different stress levels as a function of cumulative stress time. A                                                                                   |     |

|      | pulse sequence with constant voltage amplitude and increasing pulse                                                                                     |     |

|      | width was used to stress the device gate. $I_D$ - $V_G$ curve was measured                                                                              | 75  |

| 19   | after each pulse to extract the threshold voltage                                                                                                       | 75  |

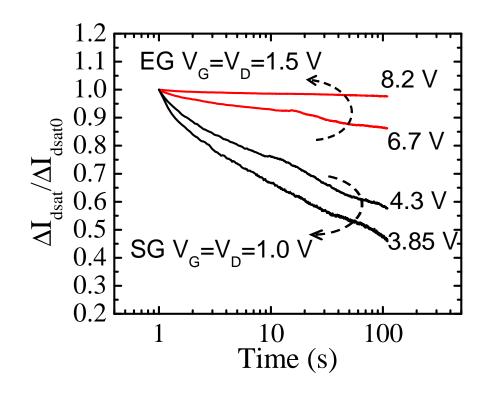

| 4.3  | $I_{dsat}$ transients following positive pulsed stresses at different stress lev-<br>els for both SG and EG devices. The relaxation rate depends on the |     |

|      | oxide thickness and the stress voltage                                                                                                                  | 77  |

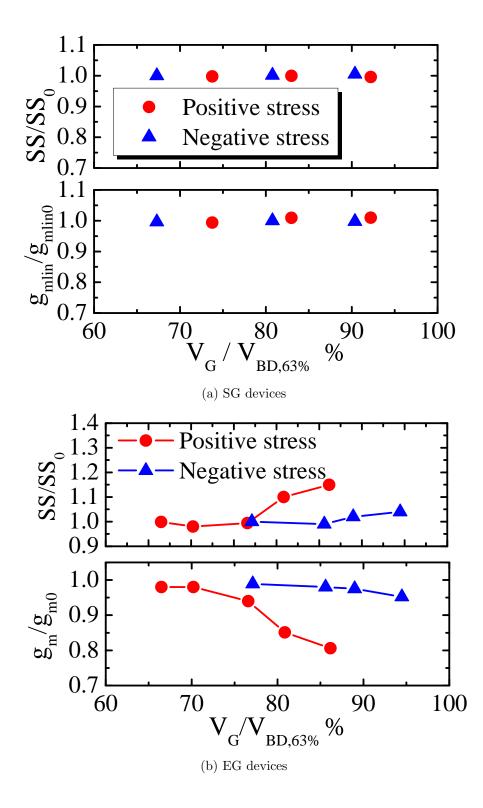

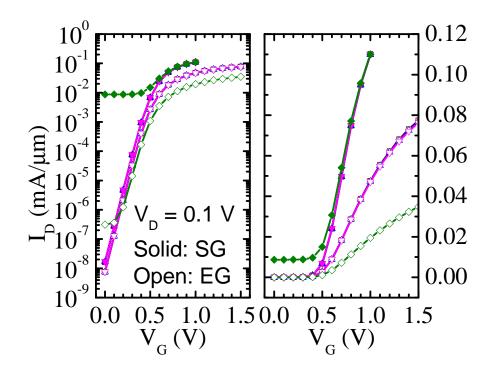

| 4.4  | Transconductance $(g_m)$ and subthreshold swing (SS) degradation in-                                                                                    | 11  |

| 4.4  |                                                                                                                                                         | 79  |

| 4 5  | duced by positive and negative stress for (a) SG and (b) EG devices.                                                                                    | 19  |

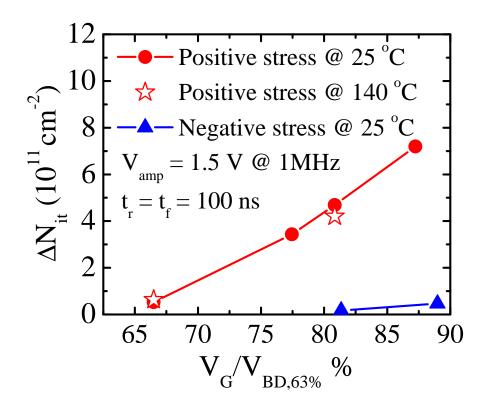

| 4.5  | Increase of the interface state density $(N_{it})$ in EG devices after pos-                                                                             |     |

|      | itive and negative stress on the gate, obtained by charge pumping                                                                                       |     |

|      | measurements. Only one stress pulse was applied to each device, and                                                                                     |     |

|      | the devices were stressed at either 25 °C or 140 °C. All the charge                                                                                     | 0.0 |

|      | pumping measurements were made at 25 °C                                                                                                                 | 80  |

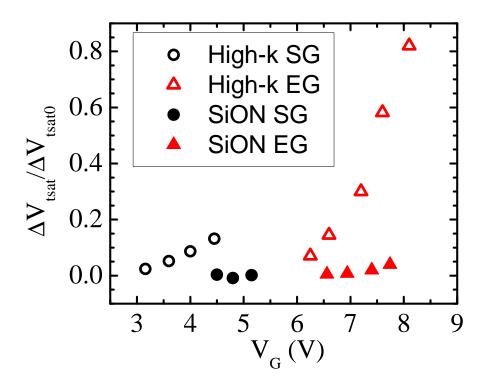

| 4.6  | Comparison of the degradation of NMOSFETs with SiON and high-                                              |    |

|------|------------------------------------------------------------------------------------------------------------|----|

|      | k gate under positive ESD-like stresses. More considerable $V_{tsat}$ shift                                |    |

|      | was observed in devices with high-k gate, presumably due to the large                                      |    |

|      | amount of electron traps inside the high-k gate dielectric                                                 | 82 |

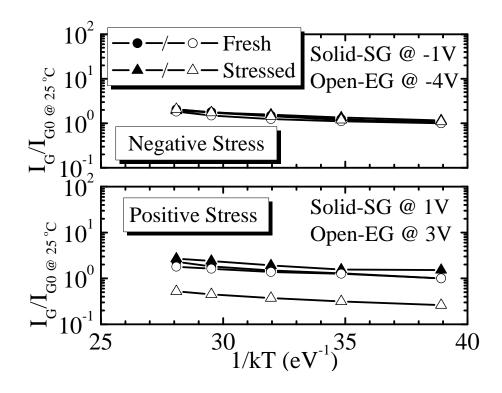

| 4.7  | Temperature dependence of gate leakage current for fresh (control)                                         |    |

|      | devices and devices stress at 90% of $V_{BD}$ . The stress was applied at                                  |    |

|      | 25 $^{\circ}\mathrm{C}$ in all cases while the gate currents were measured at different                    |    |

|      | temperatures                                                                                               | 84 |

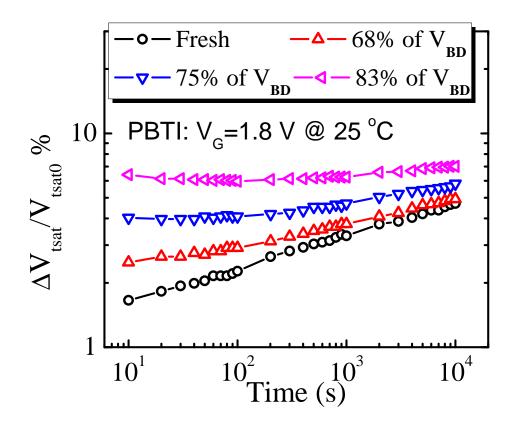

| 4.8  | Effect of positive pre-stress on the subsequent PBTI degradation ki-                                       |    |

|      | netics of SG devices. No pre-stress induced acceleration of the PBTI                                       |    |

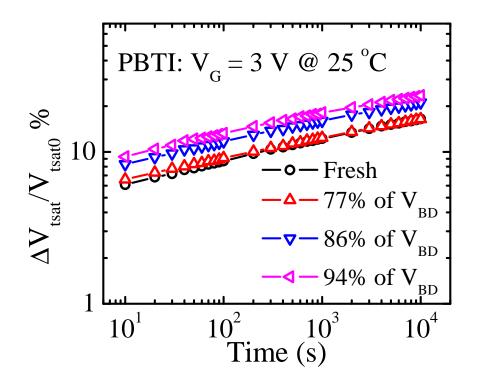

|      | degradation kinetics was observed. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 86 |

| 4.9  | Effect of negative pre-stress on the subsequent PBTI degradation ki-                                       |    |

|      | netics of EG devices. No pre-stress induced acceleration of the PBTI                                       |    |

|      | degradation kinetics was observed.                                                                         | 87 |

| 4.10 | The effect of positive ESD-like stresses on the transfer characteristics of                                |    |

|      | SG and EG devices in logarithmic (left) and linear (right) scales. The                                     |    |

|      | stress was applied on the drain with gate, source and body grounded.                                       |    |

|      | No significant device degradation was observed as the stress voltage                                       |    |

|      | was ramped up until the device failed.                                                                     | 88 |

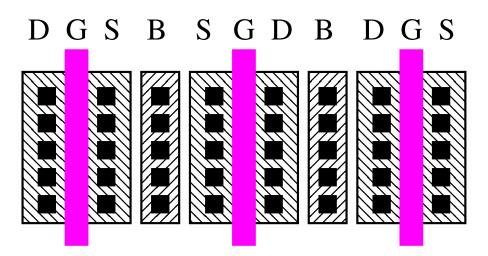

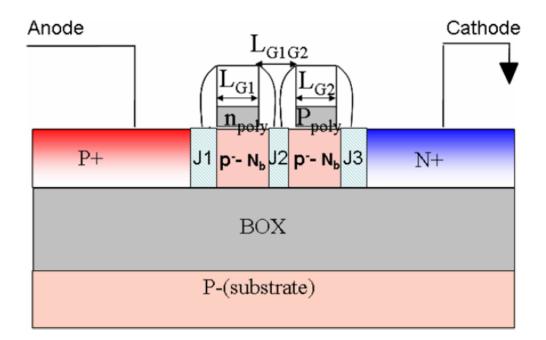

| 5.1  | Cross-section of the two-gate FED with gates denoted as G1 and G2.                                         |    |

|      | J2 is induced by positive $V_{G1}$ . It is clear that the structure resembles a                            |    |

|      | pin diode, augmented by two gates between the anode and the cathode.                                       | 91 |

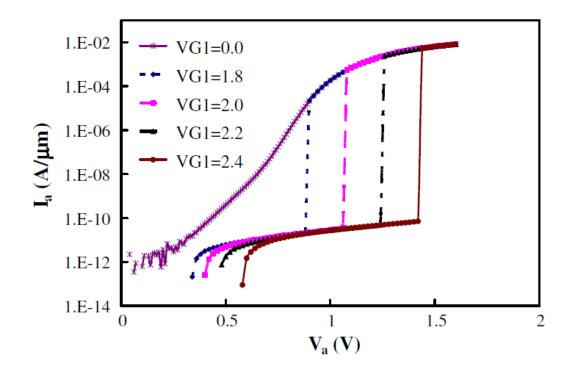

| 5.2  | Measured DC ICV curves for the two-gate FED ( $N_b = 6e16$ cm <sup>-3</sup> p-                             |    |

|      | type, $T_{soi} = 70$ nm, $L_{G1} = L_{G2} = 0.5 \mu$ m) with varying gate voltage                          |    |

|      | $V_{G1} (V_{G2} = 0 \text{ V}).$                                                                           | 92 |

| 5.3  | Schematic of an I/O circuit using a regular lateral diode for negative $% \mathcal{A}$                     |    |

|      | ESD pulse protection and FED for positive ESD pulse protection (a                                          |    |

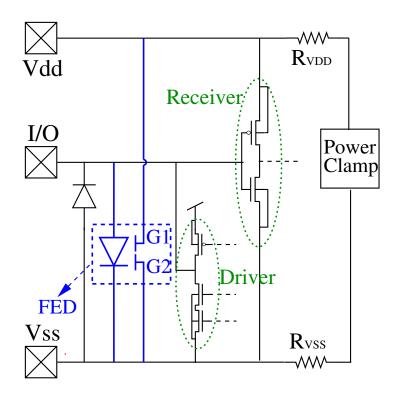

|      | local clamping scheme).                                                                                    | 93 |

| 5.4  | Effect of carrier lifetime on the simulated I-V curves of the "standard"                                   |    |

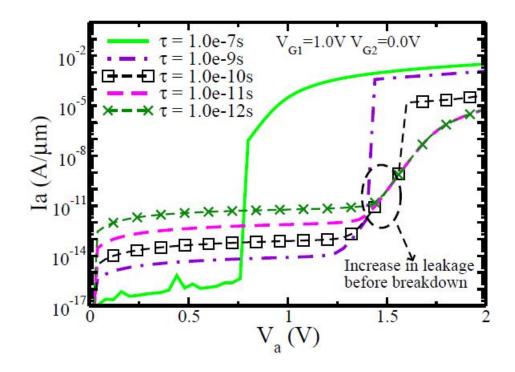

|      | two gate FED                                                                                               | 94 |

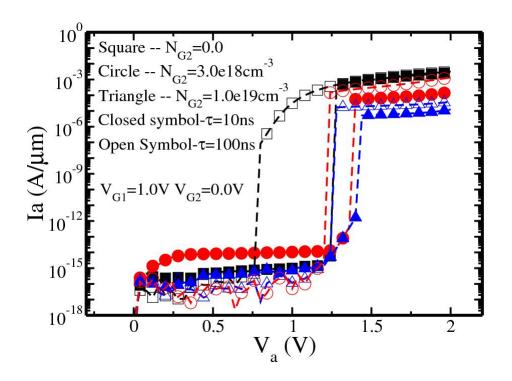

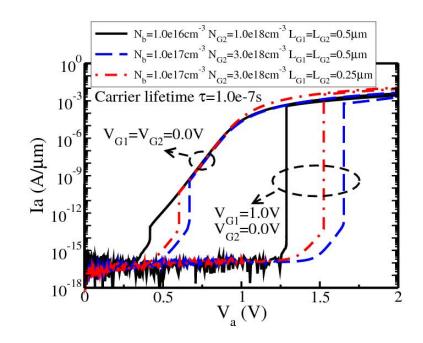

| 5.5  | Effect of doping concentration $N_{G2}$ beneath G2 on the I-V curves of                                    |    |

|      | the FED                                                                                                    | 95 |

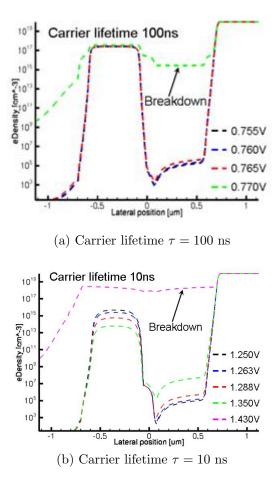

| 5.6 | Simulated electron densities $0.01 \mu m$ below the Si/SiO <sub>2</sub> interface in the  |     |  |

|-----|-------------------------------------------------------------------------------------------|-----|--|

|     | "standard" FED with different carrier lifetimes. Voltage ranges from                      |     |  |

|     | $0.755~\mathrm{V}$ to $0.77~\mathrm{V}$ in (a) and from 1.25 V to 1.43 V in (b). As shown |     |  |

|     | in (b), electron density decreases significantly near breakdown                           | 96  |  |

| 5.7 | Simulated I-V curves for the two-gate FED with uniform n-type body                        |     |  |

|     | doping under G1                                                                           | 97  |  |

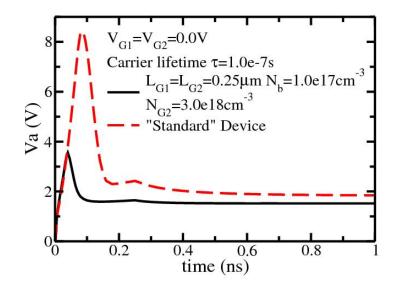

| 5.8 | Transient behavior of different device structures subjected to current                    |     |  |

|     | pulses                                                                                    | 99  |  |

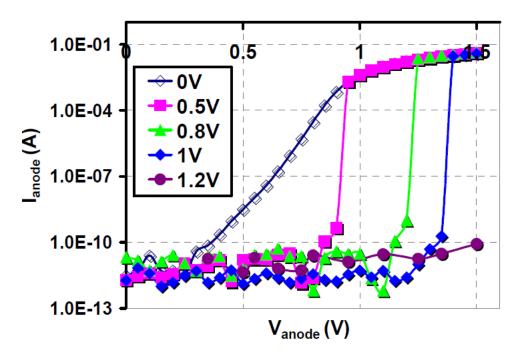

| 5.9 | Measured DC I-V of FED with increased p-type doping concentration                         |     |  |

|     | under G2, with different G1 biasing                                                       | 100 |  |

## Abstract

ISSUES OF ESD PROTECTION IN NANO-SCALE CMOS Yang Yang, PhD George Mason University, 2010 Dissertation Director: Dr. Dimitris E. Ioannou

Aggressive downsizing of individual transistors continues to improve the performance of integrated circuits. However, as the transistors get smaller, they become more vulnerable to damage by high current and high voltage Electrostatic Discharges (ESD). As technology scales down, among other things, new materials such as high-k gate dielectrics are incorporated into the modern chip fabrication technologies and Silicon-on-Insulator (SOI) technology is gaining acceptance. These technology advances make ESD protection of silicon chips ever more necessary and challenging. Consequently, the present dissertation focuses on ESD related issues in nano-scale CMOS technologies.

The thesis begins with the investigation of high-k gate dielectric breakdown under ESD-like stress. The stress configuration for transistors in the input receiver will be considered first. It is confirmed that high-k gate oxide breakdown is catastrophic under ESD-like stress. Using the constant voltage stress (CVS) method, the gate oxide breakdown voltages ( $V_{BD}$ ) of NMSOFETs and PMOSFETs are compared under different stress polarities, in order to identify the worst case scenario. The results are also compared with SiON gate dielectric devices. Next, high-k gate breakdown in the output driver is explored. The results imply that the input receiver is more susceptible (than output driver) to failure due to ESD induced gate dielectric breakdown. Measurement results also show that  $V_{BD}$  obtained by the transmission line pulsing method (TLP) is only slightly smaller than that obtained by the CVS method. Methodologies to improve the breakdown immunity are then proposed with the support of experimental results.

The dissertation then focuses on the degradation of NMOSFETs with high-k gate under non-destructive ESD-like stress. For the stress configuration emulating the output driver, little degradation was observed until the device failed by drain-tosource filamentation. By contrast, for the stress configuration emulating the input receiver, degradations of threshold voltage  $(V_t)$ , drain saturation current  $(I_{dsat})$  and Si/gate oxide interface were observed. The degradations increase with the effective gate oxide thickness and are more severe under positive stress polarity. Different from Positive Bias Temperature Instability (PBTI) stress, the threshold voltage shift depends on temperature rather weakly, indicating a new dominant charge trapping mechanism active on the time scale of ESD events. These results are then compared with those obtained for transistors with SiON gate dielectric. In addition to  $V_t$ ,  $I_{dsat}$ and interface degradation, the impact of the stress on the gate leakage current and on the subsequent PBTI degradation kinetics is also studied.

Finally, the dissertation presents a thorough investigation of the field effect diode (FED) with the aim to explore its potential for ESD protection applications in SOI technology. It is shown that the doping type and concentration under the two gates has an important impact on the device operation. By careful sizing and doping, FED devices with reasonable breakdown voltage values can be achieved at gate voltage values compatible with the latest technology.

## Chapter 1: Introduction

With the concept brought up in 1930 [14] and later put into practice using Si-SiO<sub>2</sub> by Kahng and Atala in 1960 [15], Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET) has been the workhorse of the microelectronic industry for the past three decades. The ever-increasing demand for faster and multi-functional integrated circuits (ICs) has led to significant advances in semiconductor manufacturing techniques. Microprocessor clock frequencies have been increasing from about 2 MHz (Intel 8080), made in 1974, to over 2 GHz today (2010) with the smallest feature size on the order tens of nanometers. The number of transistors in ICs has been increased from a few thousand to more than one billion today as shown in Fig. 1.1.

The advances of the microelectronic industry have been achieved mainly by the persistent downsizing of transistors. Decreasing the feature size of the individual transistor not only improves the overall circuit performance (improvements in density, speed and power consumption) but also reduces the manufacturing cost [1, 16, 17]. However, the reduction in MOSFET channel length leads to the undesirable short channel effects, which cause a reduction in the threshold voltage at which the device turns on, especially at high drain voltages [2]. To keep proper function of the transistors, the scaling of transistors should follow certain rules. The common scaling rules for important transistor parameters and their technological or physical constraints are listed in Table 1.1 [1].

Dennard *et al.* proposed the constant-field scaling rule in 1974 [18] (as shown in the second column of Table 1.1) that one can keep short-channel effects under control by scaling down the vertical dimensions (gate insulator thickness, junction depth,

Figure 1.1: Plot of transistor counts against dates of introduction [4].

etc) along with the horizontal dimensions, while also proportionally decreasing the applied voltages and increasing the substrate doping concentration (decreasing the depletion width). As all the voltages and dimensions are reduced by the same factor of k, the electric field in the small-sized devices will remain the same as the large devices. This ensures that the reliability of the small device is not worse than the large one. However, some nonscaling factors prohibit reducing the power supply voltage by the same factor as the device dimension. The primary nonscaling factors include the thermal voltage kT/q and the silicon band gap  $E_g$  [2]. The former factor prohibits the scaling of subthreshold current and leads to the non-scalability of the threshold voltage, while the constant silicon bandgap results in the non-scalability of the junction built-in potential, depletion layer width and the short channel effects [2]. Table 1.2 lists the power supply voltage and the device dimensions for several

Table 1.1: A general scaling rule leading to an integrated circuit with a faster speed, and enhanced functionalities have been the major success of the past history of microelectronics [1]

| Parameter                         | Constant field | Generalized    | Limiting factors          |

|-----------------------------------|----------------|----------------|---------------------------|

|                                   | scaling factor | scaling factor |                           |

| Voltage, $V_{DD}$                 | 1/k            | $\epsilon/k$   | Thermal voltage,          |

|                                   |                |                | quantum confinement       |

| Electric field                    | 1              | $\epsilon$     |                           |

| Channel length $L_G$              | 1/k            | 1/k            | Lithography accuracy      |

| Drain current $I_D$               | 1/k            | $\epsilon/k$   | Punchthrough, tunneling   |

|                                   |                |                | between source and drain  |

| Gate capacitance                  | k              | k              | Physical thickness limit, |

| $C_{ox}$                          |                |                | gate leakage current      |

| Intrinsic delay                   | 1/k            | $\epsilon/k$   | Non-scalable $V_{DD}$     |

| $CV/I_D$                          |                |                |                           |

| System clock                      | k              | k              | Parasitic capacitance     |

| frequency $f_c$                   |                |                | Interconnect R and C      |

| Chip area                         | 1              | 1              | Yield, delay              |

| # of transistors                  | $k^2$          | $k^2$          | Interconnect complexity,  |

| per chip n                        |                |                | yield                     |

| Power density                     | 1              | $\epsilon^2$   | Gate leakage, frequency   |

| $P \propto f_c n C_{ox} V_{DD}^2$ |                |                | # of transistors,         |

|                                   |                |                | over heating              |

technology nodes, which clearly shows the less drastic scaling of supply voltage and the increasing oxide field.

As the voltage cannot scale as fast as the device dimensions, a more generalized scaling rule was proposed by Baccarani *et al.* [19] as shown in the third column of Table 1.1. In this rule, it is proposed that the lateral and the vertical electric fields should be scaled by the same factor so that the shape of the field pattern is preserved. This keeps the two dimensional effects, such as short-channel effects, under control. However, the higher electric field in aggressively scaled MOSFETs does cause serious reliability concerns. For every technology node to be successful, a thorough reliability analysis is required. Within the scope of these requirements, the motivation for this thesis is given in the following section.

Table 1.2: Scaling of power supply voltage, oxide thickness and oxide field in several CMOS technology generations [2]. \* this data is taken from the latest 32 nm technology.

| Feature size $(\mu m)$ | Power supply<br>voltage (V) | Gate oxide<br>thickness (Å) | Oxide field<br>(MV/cm) |

|------------------------|-----------------------------|-----------------------------|------------------------|

| 2                      | 5                           | 350                         | 1.4                    |

| 1.2                    | 5                           | 250                         | 2.0                    |

| 0.8                    | 5                           | 180                         | 2.8                    |

| 0.5                    | 3.3                         | 120                         | 2.8                    |

| 0.35                   | 3.3                         | 100                         | 3.3                    |

| 0.25                   | 2.5                         | 70                          | 3.6                    |

| 0.1                    | 1.5                         | 30                          | 5.0                    |

| $0.032^{*}$            | 1.0                         | 14                          | 7.1                    |

## 1.1 Motivation

Gate oxide thickness is reduced for every technology node to maintain the necessary gate capacitance so that the drive current is adequate for improved circuit operation. This gate insulator which is used to block channel current from gate electrodes has already approached the range of 1-2 nm. Besides the huge increase in the gate tunneling current due to gate oxide thinning, the increased gate oxide electric field also poses serious concerns on the reliability of these ultra-thin gate insulators. One aspect of the reliability concern is related to the damage caused by the high-current, high-voltage electrostatic discharge (ESD) events.

Integrated circuits are protected against ESD events through protection networks at each pin of the chip. The protection network should remain in the off-state (with high resistance) during the normal operation conditions and be triggered into the onstate (with low resistance) during ESD events to clamp the pin voltage low enough and avoid damage to the internal circuitry. The normal operation region of the IC and the gate oxide breakdown voltage (and junction breakdown voltage) define the lower and upper bounds of the operation window of the ESD protection network respectively. Fig. 1.2 [5] shows the evolution of this design window as the technology

Figure 1.2: Impact of technology scaling on ESD design window [5].

scales down. Although the power supply voltage is decreasing with the technology, the oxide breakdown voltage decreases far more drastically with the scaling of thickness, as shown in Fig. 1.3 which are taken from 45 nm and 65 nm technology. As a result, the lateral dimension of the design window is significantly reduced with scaling.

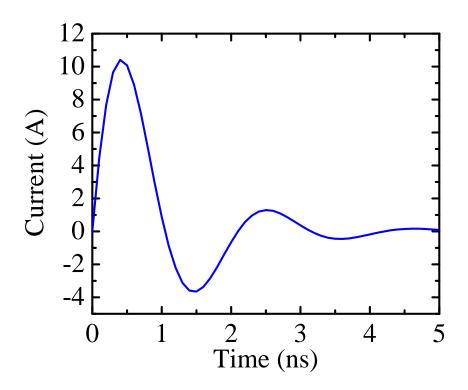

The shrinking design window challenges the ESD protection robustness and significantly increases the importance of understanding gate dielectric breakdown under ESD-like stress. Especially for charged device model (CDM)-type ESD events, the current can be even higher than 10 A and consequently the IR drop will cause a large voltage drop and overstress the gate oxide of transistors in the input/output (I/O) circuits.

Further complicating matters, new materials with high permittivities (called highk materials) are introduced to replace the conventional materials such as  $SiO_2$  and SiON to make the gate dielectric. The thickness of  $SiO_2$  or SiON gate dielectric has already approached its physical limit. Further scaling will result in excessively large quantum mechanical tunneling current, which increases the standby power consumption to an intolerable level. High-k materials are helpful to reduce the leakage current

Figure 1.3: Reduction of gate oxide breakdown voltage as the gate dielectric thickness scales down. The data correspond to a breakdown time of 100 ns.

while keeping the benefits brought by scaling <sup>1</sup>. The impact of the new gate dielectric materials on the ESD design robustness is still an open question.

One way to mitigate the above problem is to improve the current protection device or design new device structures which offer more effective ESD protection. This is especially challenging for Silicon-On-Insulator (SOI) technology. The buried oxide (BOX) layer between the active device and the silicon substrate provides the advantages such as low parasitic capacitance, no body effect and high immunity to soft error [2]. However, the BOX layer leads to increased self heating due to its low thermal conductivity and precludes simple integration of common bulk ESD protection devices relying on vertical junctions. For example, silicon-controlled-rectifier (SCR) is not easily feasible in SOI technology. The Lateral diode has been widely used to construct P-N junctions in the silicon layer above the BOX [20]; but it is not capable of providing

<sup>&</sup>lt;sup>1</sup>The details will be described in Sec. 2.4.1.

local clamping <sup>2</sup>. Although silicide blocked gate-grounded NMOSFET is able to provide local clamping, it has a relatively low failure current. It is therefore desirable to design a new device structure which can provide robust local protection in the SOI technology.

The present thesis investigates high-k gate dielectric breakdown as well as degradation under ESD-like stress. The study is essential for robust ESD design of the latest technology. The results are compared with the conventional  $SiO_2$  and SiON gate dielectric and the impact of transitioning to high-k gate dielectric on the ESD-design robustness are evaluated. For efficient and accurate characterization of gate oxide failure under ESD-like stress, different test methods are compared as well. Based on the experimental results, methods to increase the immunity to oxide breakdown in the I/O circuits are proposed.

To achieve robust ESD design in SOI technology, this thesis also explores a new ESD protection device called Field Effect Diode (FED) [21]. The original FED proposed in [21] does not have a large enough anode breakdown voltage ( $V_{FB}$ ) under the bias voltage compatible with power supply voltage in the latest technology. As a result, the protection device may turn on during normal operation conditions. For real application, the anode breakdown voltage has to be increased. Based on Technology Computer Aided Design (TCAD) simulation results, the physics of device operation is investigated. A method to increase the anode breakdown voltage is proposed, which makes its applications for ESD protection feasible in the SOI technology.

$<sup>^{2}</sup>$ The concept of local clamping and non-local clamping will be introduced in Sec. 2.3.1

## **1.2** Dissertation Organization

The dissertation is organized as follows:

Chapter 2 presents the preliminary information, including ESD and gate dielectric degradation and breakdown, for a better understanding of the dissertation. The chapter presents a brief introduction on the ESD phenomena, followed by the description of various ESD models, characterization methods and different ESD protection strategies. This chapter also points out the necessity of introducing high-k gate dielectric, covers the basic physics of gate dielectric degradation and breakdown and reviews the literature results about gate dielectric breakdown and degradation under ESD-like stress.

Chapter 3 will focus on the high-k gate dielectric breakdown under ESD-like stress. This chapter starts with a discussion of the stress configurations on gate dielectric in the context of some real I/O circuits. The characterization results of high-k gate breakdown under similar stress configurations are then presented and compared with SiON gate dielectric from an older technology node. For efficient and accurate characterization, different test methods are discussed and compared as well. Finally, methods to improve the immunity of the I/O circuits to gate dielectric breakdown are proposed.

Chapter 4 reports the degradation of NMOSFETs under different levels of nondestructive ESD-like stresses. The effects of both positive and negative stress applied on the gate are discussed first, which emulate ESD events on the input receiver pin. The effect of the stress on threshold voltage  $V_t$  and drain saturation current  $I_{dsat}$ and the stress induced damage to the gate dielectric/Si interface are presented. The performance degradation is compared with devices with SiON gate. Moreover, the impacts of the stress on the high-k gate leakage current and on the positive-biastemperature instability degradation kinetics <sup>3</sup> are also covered. Finally, the effects of positive stress applied on the drain are discussed, which emulates ESD events on output pins.

Chapter 5 discusses the design and optimization of the SOI field effect diode (FED), using a TCAD simulation based approach. TCAD simulations help identify important device parameters. Based on the simulation results, methods to increase the anode breakdown voltage ( $V_{FB}$ ) to the level which is compatible with supply voltage in the current technology are proposed. This chapter concludes with a brief discussion on the experimental verification of the proposed methods conducted by another research group.

Finally, Chapter 6 summarizes the contributions of this dissertation and discusses the scope of future work.

<sup>&</sup>lt;sup>3</sup>Please refer to Sec. 2.4.5 for details.

# Chapter 2: Review of ESD and gate dielectric breakdown and degradation

Electrostatic Discharge (ESD) is a single-event, rapid transfer of electrostatic charge between two objects, usually resulting when two objects at different potentials come into direct contact with each other. ESD can also occur when a high electrostatic field develops between two objects in close proximity. A familiar example of electrostatic charging and discharging is when someone walks across a carpet and then touches a metal door knob. The charging level can be as high as 35000 V in a dried environment. The ESD events are usually harmless in everyday life since the total amount of charge is typically small. However, they are one of the most serious reliability concerns in the semiconductor industry. ESD damage due to handling and testing is directly responsible for approximately 10% of the total failure returns [22,23]. It has negative influence on product yield [23] and becomes more prevalent as the device dimension keeps scaling down. To protect ICs from these undesirable ESD events, ESD protection networks are required at every pin of the chip.

There are several organizations such as electrostatic discharge association (ESDA), electronic industries alliance/joint electron device engineering council (EIA/JEDEC) that issue ESD test standards to predict the ESD immunity level. The most common industrial models used to measure ESD robustness are the human body model (HBM), the machine model (MM) and the charged device model (CDM). This chapter begins with a discussion of these models, followed by a detailed description of the transmission-line pulsing (TLP) characterization method. An overview of the basic

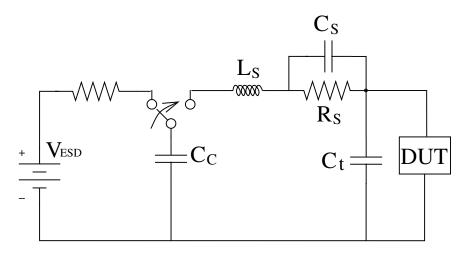

Figure 2.1: The lumped circuit model for the HBM and MM. Capacitor  $C_c$  is charged to the test voltage,  $V_{ESD}$ , and then discharged through  $R_s$  to the device under test (DUT) by closing the switch. Parasitic circuit elements are represented by series inductance  $L_s$ , stray capacitance  $C_s$ , and test-board capacitance  $C_t$ . The typical circuit parameters are (a)  $C_C = 100$  pF,  $L_s = 7.5 \ \mu\text{H}$ ,  $R_S = 1500 \ \Omega$  and  $C_s = 1$  pF for HBM and (b)  $C_C = 200$  pF,  $L_s \approx 2.5 \ \mu\text{H}$ ,  $R_S = 5 \ \Omega$  and  $C_s = 1$  pF [6].

ESD protection strategies will be discussed next. Finally, the physics of the ESD related reliability issues including gate dielectric breakdown and latent damage will be reviewed.

## 2.1 ESD Characterization Models

### 2.1.1 Human Body Model

The human body can be charged and then transfer the charge to a semiconductor device through normal handling or assembly operations. To evaluate the effectiveness of the protection circuitry in an integrated circuit, Human Body Model (HBM) ESD testing is performed. This model represents an ESD event from a charged human body to the pin of an integrated circuit.

The circuit used to model the HBM event is shown in Fig. 2.1 [6,24,25]. The pulse is generated by charging the capacitor ( $C_C$ ) of 100 pF and then discharge it through

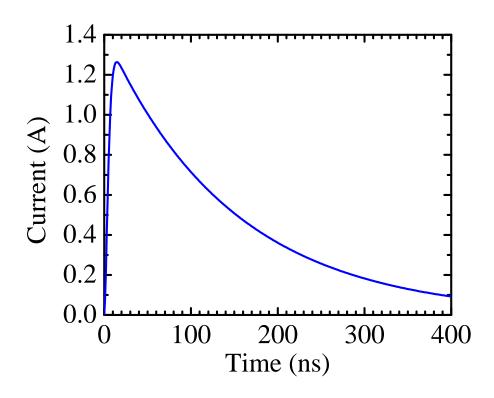

Figure 2.2: A typical waveform for a 2000 V HBM event [6].

a 1.5 k $\Omega$  resistor ( $R_s$ ) into the Device Under Test (DUT). Because of the large series resistance  $R_s$  in the HBM, this ESD event can be modeled as a current source with the typical peak value of 1.20-1.48 A for 2 kV HBM ESD stress. The rise time is 2-10 ns and the decay time is 130-170 nm. Testing specifications usually require circuits to be able to have a minimum threshold of +/- 2kV HBM ESD stress on all pins. HBM is the longest ESD event of the three primary models, but it has the lowest current. A typical HBM pulse is shown in Fig. 2.2, obtained from SPICE simulation using the circuit model shown in Fig. 2.1.

### 2.1.2 Machine Model

The Machine Model (MM) is similar to the human body model. A capacitor is charged to a certain voltage and then discharge through the device. The equivalent lumped

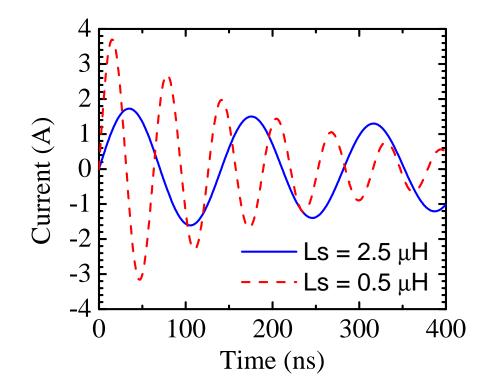

Figure 2.3: A typical waveform for a 200 V MM event with two different series inductance [6].

circuit model is similar to the shown in Fig. 2.1 with modified component parameters. The capacitor  $C_C$  is increased to 200 pF, the parasitic resistance  $R_s$  is decreased to a few ohms and a series inductance  $L_s$  of 1  $\mu$ H is used. A typical waveform is shown in Fig. 2.3 using the typical parameter values shown in Fig. 2.1. This model is intended to simulate the type of damage caused by equipment used in manufacturing. As shown by the equivalent circuit model, the higher charging capacitance and lower impedance of the path result in higher discharging current densities during the MM discharge an a shorter rise time compared to the HBM event. The very low series resistance also implies that the dynamic impedance of the device under test and the values of the parasitic capacitance and inductance have a large effect on the MM waveform, as illustrated by Fig. 2.3. Changing the series inductance  $L_s$  from 0.5

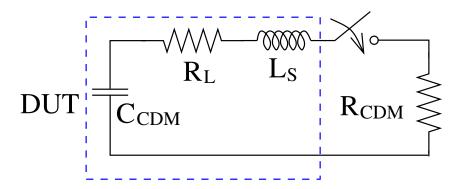

Figure 2.4: The equivalent circuit model for CDM.  $C_{CDM}$  is the sum of all capacitances in the DUT and the package with respect to ground and  $R_{CDM}$  is the total resistance of the discharge path.  $C_{CDM}$ ,  $R_L$  and  $L_S$  represent the DUT [7]. The device under test is charged and then discharged through a pin to ground. For 500 V CDM, the typical model parameters are  $C_{CDM} = 10$  pF,  $R_{CDM} = 10 \Omega$ ,  $R_L = 10$  $\Omega$  and  $L_s = 10$  nH.

$\mu$ H to 2.5  $\mu$ H leads to drastic changes in the rise time and peak current. The pass threshold for the MM required for the commercial ICs is ~ 200 V.

#### 2.1.3 Charged Device Model

The Charged-Device Model (CDM) is intended to simulate the situation when the packaged IC gets charged up and then the stored energy is discharged through a low-inductance, low-impedance path when one of the pins is grounded. The equivalent circuit model is shown in Fig. 2.4 [7]. This model is major concern today because of its very fast rise time which is about 100-200 ps and its large peak current value which is typically several amps. Fig. 2.5 is a typical CDM waveform, obtained using the typical parameter values shown in Fig. 2.4. Since the turn-on time of the protection circuits is on the order of 1 ns, pad voltages may become too high during a CDM event and thus damage the thin oxides of the MOSFETs. Therefore the turn-on speed and the on-resistance of the ESD clamp device are very important for robust CDM ESD protection as the CMOS scaling continues.

Figure 2.5: A typical waveform for a 500 V CDM event.

## 2.2 Transmission Line Pulsing method

The classical ESD models (HBM, MM and CDM) have many limitations to characterizing ESD robustness of circuits. The complex pulses of these models make the response of the circuit complex and thus difficult to measure. Therefore these models offer only restricted insight in how the protection circuits work and how and where they fail.

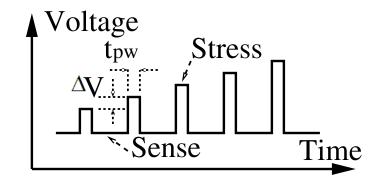

To avoid these difficulties, the Transmission Line Pulsing method (TLP) was introduced by Maloney and Khurana [26] as a new electrical analysis tool to test the many single elements used as ESD protection structures. Instead of duplicating the real life ESD events such as HBM, MM or CDM, a series of square wave pulses of varying magnitude and a constant pulse width, as shown by Fig. 2.6, are applied to

Figure 2.6: TLP uses a series of square wave pulses of varying magnitude and a constant pulse width to stress the device.

stress the DUT and the current through and voltage across the device are measured. As TLP uses a reliable and repeatable sqaure waveform to stress the device, it can be used to obtain current-voltage relationship for the semiconductor devices and circuits under different ESD conditions. After the application of each ESD stress pulse, the DC leakage current of the DUT is recorded. The TLP I-V along with the DC leakage current (or, device I-V) data provide electrical indications of where damage begins, and how rapidly it can evolve from soft to hard failure. The rectangular TLP pulse simulates the energy of different ESD events. Different pulse widths can be used to simulate different events. Typically, a 100 ns pulse corresponds to HBM, and a 30 ns pulse is used to simulate MM and 1 ns to simulate CDM.

## 2.3 ESD protection strategy

ESD event can occur between any two pads/pins of an IC. Therefore ESD protection devices are required for all pads/pins. These devices remain off during the normal operation conditions and have negligible effects on the circuit operation. During ESD events, these devices turn on and form a low resistive path. As a result, the ESD current is shunt to ground through these protection devices and hence reduces the flow of ESD current through the driver or receiver circuit components. Most ESD

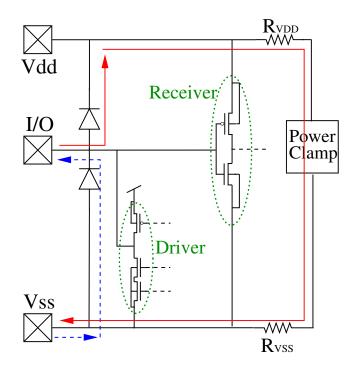

Figure 2.7: An input/output circuit based on double-diode ESD protection strategy. Solid lines with arrows indicate the designed ESD discharge path under positive ESD events, while dashed lines represent the designed discharge path under negative ESD events. The arrows indicate the direction of the current flow.  $R_{VSS}$  and  $R_{VDD}$  are the resistance of the supply bus and ground bus respectively.

solutions rely on shunting current from an I/O pin to a power supply rail and then the charge can be distributed to other I/O pins or supplies [27]. These solutions fall into two categories: (a) Vss-based ESD protection that shunt current to the negative supply rail and (b) Vdd-based ESD protection that shunt current to the positive supply rail. As an example, the ESD related charges are assumed to be shunted to the negative supply rail (the Vss rail) in the following discussions.

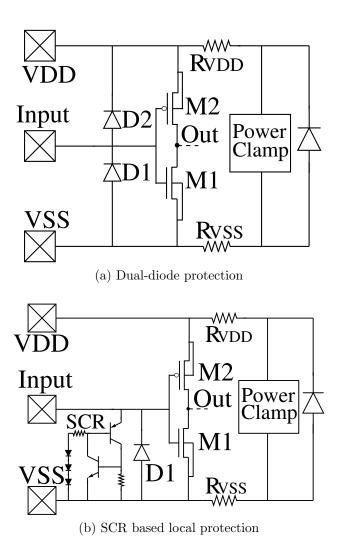

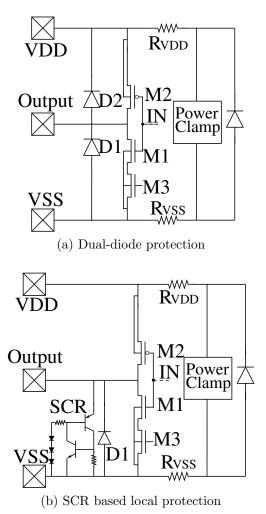

#### 2.3.1 Double diode based ESD protection strategy

One of the most commonly used ESD protection strategies is to connect two diodes to the pin, one to the positive supply bus and the other to the negative supply bus, as shown by Fig. 2.7. The current paths in the chip for the possible discharges between the pin and its negative supply bus are also shown in this figure. The solid lines with arrows represents the designed discharge paths under positive ESD events. For positive pulse with respect to Vss, the current passes through the upper diode, along the positive supply rail to the power clamp, through the clamp and to the Vss supply rail. The dashed lines with arrows indicate the designed discharge paths under negative ESD events. For a negative pulse with respect to Vss, the current passes through the lower diode and out the signal pin.

Good ESD results are achieved when the discharge paths are confined to these routes. If the resistance of the wiring, the power clamp or the protection devices (i.e. the diodes here) causes the signal pad or Vdd bus to rise too high in voltage, the discharge path may be rerouted through I/O or internal circuitry. Therefore the discharge path must not only be able to handle the current, it must be also able to do so without allowing large voltages to develop across the parallel circuitry due to I-R effects. Because the diodes appear as parasitic capacitance on the I/O node, the designer may have to balance ESD protection against circuit performance. The above two points are the general rules which should be followed in the design of all ESD protection networks.

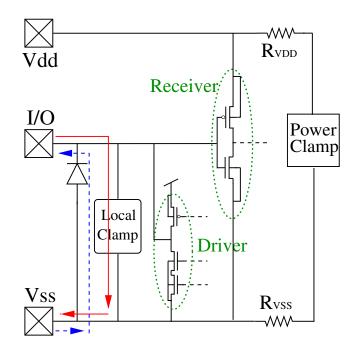

#### 2.3.2 Local clamp device based ESD protection strategy

Another typical ESD protection circuit topology is based on a local clamp device, as shown in Fig. 2.8. The local clamp devices are typically snap-back devices, including non-silicided grounded gate NMOSFET, silicon controlled rectifier (SCR), etc. They are connected between the I/O pad and the Vss rail. For a positive pulse with respect to Vss, the local clamp device turns on and shunts the current directly to the Vss rail. For a negative pulse on the I/O pad with respect to Vss, the current passes through the ESD diode in parallel with the local clamp device and then out

Figure 2.8: Local clamp device based ESD protection strategy.

the I/O pad. An advantage of this topology is that the I/O pad can rise above the power supply voltage without forward-biasing the upper diode, which is useful for mixed voltage interface applications or hot-pluggable interface applications. Another important advantage of the local clamp based ESD protection will be discussed in the Sec. 2.3.4. However, when implementing this protection strategy, it is necessary to ensure that the protection device's turn-on voltage is higher than Vdd so as to avoid accidental turn-on and reduce leakage current during normal operation.

### 2.3.3 CDM protection strategy

During a CDM event, the entire chip is charged and then discharged through a single pin. For the circuit shown in Fig. 2.7, assume the chip is charged to a negative voltage and then discharges through the I/O pin and all the buses and devices are at the same potential (the circuit is unpowered). The preferred charge flow path is through the upper diode, along the Vdd bus to the power clamp, through the clamp to the Vss

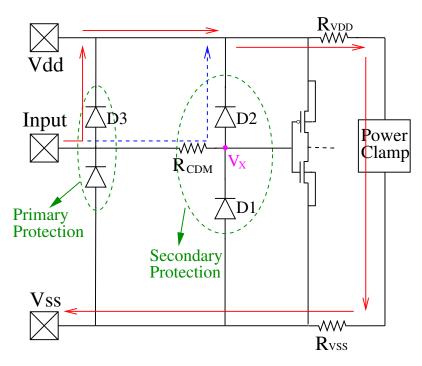

Figure 2.9: Basic CDM protection strategy

rail. For a very robust ESD protection diode, the on-resistance is about 1  $\Omega$ . The CDM current can be in the range of 10 A. This leads to a 10 V drop across the upper diode, also across the gate dielectric the MOSFETs in the receiver. This voltage is large enough to break down the gate oxide and destroy the receiver.

To improve the CDM robustness, a two-stage protection scheme, a primary protection stage along with a secondary protection stage as shown in Fig. 2.9, is normally used. Consider the same condition as described in the previous paragraph. The majority of the discharge current will flow through the diode D3, while a small portion will flow through the CDM resistor  $R_{CDM}$  and the diode D2. Although the voltage drop across the diode D3 is still large (~ 10 V), the voltage ( $V_x$ ) at the receiver MOSFET gate is small because of the voltage divider formed by  $R_{CDM}$  and D2. In this way, the gate oxide is protected against CDM events.

#### 2.3.4 Necessity of Local Clamping

The double-diode based clamping scheme is becoming insufficient to protect the gate dielectric especially during the high-current CDM event. The ESD current path in this case is very long, involving the Vss and Vdd bus resistance, the power-clamp, and the ESD diodes. The excess voltage buildup along this long path may overstress the transistor gate dielectric and induce damage or failure. To improve the protection effectiveness against the high-current CDM events demands the exploration of new design strategies and devices to avoid high voltage at the I/O pad. The local clamping protection strategy shown in Fig. 2.8 is more appropriate for CDM protection compared to Fig. 2.7. By connecting a local clamp device directly between the pad and Vss, the protection circuit allows ESD current to flow from the pad to Vss rail without going through the Vdd power buses and the power clamp between the positive and negative supply rails. Consequently, the discharge path resistance is appreciably reduced and the pad voltage build-up is minimized.

## 2.4 Background on gate dielectric degradation and breakdown

Catastrophic failures under ESD stress include gate dielectric failure, metal melting and junction filamentation. In these cases, the device is permanently damaged due to the high power dissipation. In contrast to catastrophic failure, ESD stress may also degrade device performance and thus degrade the circuit performance. We will discuss the gate dielectric breakdown and device degradation of MOSFETs with high-k gate under ESD like stress in Chapter 3 and Chapter 4. In this section, a brief introduction to the gate dielectric breakdown and degradation will be presented.

#### 2.4.1 Necessity of introducing high-k gate dielectrics

Because of the excellent quality of SiO<sub>2</sub> grown on a Si substrate (SiO<sub>2</sub>/Si) with optimized fabrication processes, SiO<sub>2</sub> has been used predominantly for the gate insulator of MOSFETs over the last 40 years. The large barrier height (~ 3 eV) of the SiO<sub>2</sub>/Si interface leads to much reduced leakage current for sufficiently thick films. The high melting temperature of SiO<sub>2</sub> makes it very compatible with CMOS processing steps performed after the formation of the SiO<sub>2</sub>-based gate dielectrics.

The MOSFET on-current can be expressed as

$$I_{ON} = \frac{\mu_{eff} C_{ox}}{2} \frac{W}{L} (V_{GS} - V_t)^2, \qquad (2.1)$$

where  $\mu_{eff}$  is the effective channel mobility, W is the width of the device, L is the lenght of the channel,  $V_{GS}$  is the gate voltage with respect to source and  $V_t$  is the threshold voltage of the MOSFET.  $C_{ox}$  is the capacitance per unit area of the gate dielectric expressed as

$$C_{ox} = \frac{\kappa \epsilon_0}{t_{ox}}.$$

(2.2)

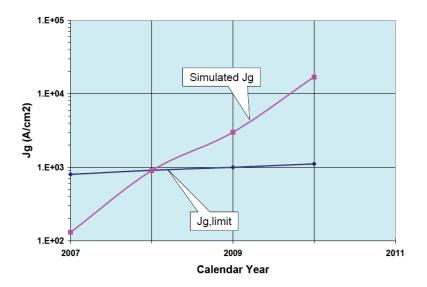

$\epsilon_0$  is the vacuum permittivity and  $\kappa$  is the relative permittivity of the gate dielectric. Based on the constant voltage scaling rule shown in Table 1.1, for every successive technology node, the device dimensions (W, L,  $t_{ox}$ ) are scaled by a factor of k; the voltage is also scaled by the same factor. Eq. (2.1) and Eq. (2.2) indicate that the intrinsic delay time  $CV/I_{ON}$  is decreased by a factor of k with technology scaling. Therefore for better performance,  $t_{ox}$  has been scaled down for many years. However, the reduced thickness of SiO<sub>2</sub> results in excessively large gate leakage current originating from the quantum mechanical tunneling effects. Further scaling the oxide thickness will make the gate leakage current intolerably large, as shown in Fig. 2.10

Figure 2.10: High-Performance Logic: gate current density limit versus simulated gate leakage current density for SiON gate dielectric [8].

predicted by [8]. This large gate leakage current stops further scaling of  $t_{ox}$ .

Eq. 2.2 also indicates that the targeted  $C_{ox}$  can be also achieved by increasing the relative permittivity of the dielectric material  $\kappa$  while further reducing the thickness  $t_{ox}$ . Consequently, to keep improving circuit performance, there has been substantial efforts to develop high permittivity, or high-k, dielectric materials to replace SiO<sub>2</sub>. Table 2.1 compared the potential high-k materials and their relative permittivities to SiO<sub>2</sub>. The hafnium-oxide-based materials (HfO<sub>2</sub>, HfSi<sub>x</sub>O<sub>y</sub>, HfO<sub>x</sub>N<sub>y</sub>, HfSi<sub>x</sub>O<sub>y</sub>N<sub>z</sub>) have already been used in the 32 nm technology node to replace SiO<sub>2</sub>. However, none of these materials have been found to possess the quality as good as SiO<sub>2</sub>. To improve the Si/gate dielectric interface, a thin SiO<sub>2</sub> layer is typically grown as the buffer layer (or interfacial layer-IL) before the deposition of the high-k material to form the final gate stack.

| Material           | Relative permittivity $\kappa$ |

|--------------------|--------------------------------|

| $\mathrm{SiO}_2$   | 3.9                            |

| $Al_2O_3$          | 9                              |

| $\mathrm{HfO}_{2}$ | 25                             |

| $Ta_2O_5$          | 26                             |

| $\rm ZrO_2$        | 29                             |

| $La_2O_3$          | 30                             |

| $Pr_2O_3$          | 31                             |

| $\mathrm{TiO}_2$   | 95                             |

| $\rm SrTiO_3$      | 200                            |

Table 2.1: Dielectric materials and their relative permittivities [3].

### 2.4.2 Physical models for gate dielectric degradation and breakdown

Under electrical stress for a certain period of time, gate dielectric will wear out and then breakdown. In other words, the dielectric film loses its insulating properties and becomes conductive. This phenomenon was first observed more than three decades ago [28, 29]. The gate conduction can cause malfunction of circuits employing field effect transistors. It is currently widely accepted that oxide breakdown is related to defects generated in the oxide during electrical stress.

A variety of phenomena related to the oxide degradation have been observed, such as positive charge trapping; generation of neutral electron traps (and the related trapping of electrons); generation of Si/gate dielectric interface states and increase of the low-field leakage current. All of these effects have been used to monitor the degradation of gate dielectrics under different stress conditions. However, the exact physical mechanisms that determine the degradation and the eventual breakdown are still unclear. There are still many open questions about the actual physics involved. Several different physical models have been proposed to explain defect generation, for example:

- The Thermochemical Model [3, 30–34];

- Anode Hole Injection model (AHI) [35–39];

- Anode Hydrogen Release model (AHR) [40–42].

For the thermochemical model, the defect generation is attributed to the high electric field across the gate dielectric. The electric field interacts with the local dipole moment and reduces the activation for chemical bond breakage. This leads to enhanced defect generation during stress. However, this physical picture fails to explain many recent experimental results. For example, the thermochemical shows that the breakdown is a field- and time-driven process while the contribution from the tunneling current and the carrier energy is not important. However, compelling experimental evdicences [38, 43, 44] indicates that both electron fluence and energy play an important role in the breakdown process. These observations have led to the other two models based on the injection of carriers through the oxide and on the dissipation of electron energy near the anode interface. The hot electrons release some specie (hydrogen assumed in AHR and hole assumed in AHI) near the anode. Part of the released species diffuse or drift back through the gate dielectric and react with defect precursors to form oxide defects.

#### 2.4.3 Gate oxide breakdown statistics

As the breakdown is due to random defect generation, the breakdown process is a stochastic process, rather than a deterministic phenomenon, which means that the values of breakdown field, breakdown voltage, or time-to-breakdown will be different if we repeat the same stress experiment in nominally identical samples. In the literature, it is generally accepted that the dielectric breakdown process follows the two-parameter Weibull distribution,

$$F(t_{BD}) = 1 - \exp\left(-\frac{t_{BD}}{t_{63\%}}\right)^{\beta},$$

(2.3)

where F is the cumulative failure probability and  $t_{BD}$  is the time-to-breakdown. The distribution has two important parameters:  $\beta$  is the shape factor and  $t_{63\%}$  is the characteristic time-to-breakdown at the failure percentile of 63.2%. Rearranging Eq. (2.3) into the following form:

$$W = \ln\left[-\ln(1 - F(t_{BD}))\right] = \beta \times (\ln t_{BD} - \ln t_{63\%}), \qquad (2.4)$$

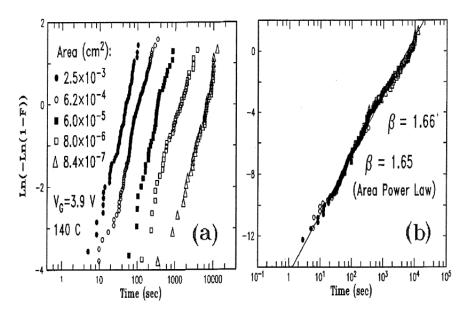

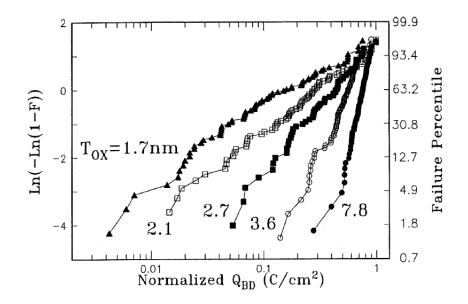

and plotting W versus  $\ln(t_{BD})$  yield a straight line with slope  $\beta$ , as shown in Fig 2.11(a). To assure the reliability of the product, accurate data at the low failure percentile, for example F = 0.01%, is of crucial importance. However, it is impractical to measure a large amount samples to approach the low failure percentile range. It is crucial to predict  $t_{63\%}$  and  $\beta$  precisely based on a limited sample size. Various methods have been proposed for this purpose [9, 45]. Reducing the gate dielectric thickness not only decreases the characteristic breakdown time but also reduces the slope  $\beta$  as shown in Fig. 2.12. On the one hand, smaller  $\beta$  implies the breakdown data becomes more widely spread, which makes characterization more difficult. On the other hand, smaller  $\beta$  means shorter lifetime for the same  $t_{63\%}$ . Therefore, the reliability margin of the gate dielectric significantly reduces with scaling.

Oxide failure probability can also be described well by randomly distributed defects following the Poisson model [9]

$$F = 1 - \exp(-DA), \tag{2.5}$$

Figure 2.11: Demonstration of Weibull plot and the area scaling law [9]. (a)  $t_{BD}$  distributions of SiO<sub>2</sub> gate dielectric with the same insulator layer thickness (2.66 nm) but different gate dielectric areas. (b) $t_{BD}$  distributions after being scaled using Eq. (2.6) to the reference area of 8.4e-7 cm<sup>2</sup>.

Figure 2.12: Weibull shape factor (Weibull slope) increases with oxide thickness. [9].

Figure 2.13: Oxide breakdown can be divided into 3 stages: (1) Defect creation; (2) Percolation path created; (3) Wearout of the percolation paths.

where A is the gate oxide area and D is the defect density. From Eq. (2.5) and Eq. (2.3) can be seen that the characteristic breakdown times  $t_{63\%,1}$  and  $t_{63\%,2}$  of two distributions follow the area scaling law

$$\ln\left[-\ln\left(1-F_{1}\right)\right] - \ln\left[-\ln\left(1-F_{2}\right)\right] = \ln(A_{1}/A_{2}). \tag{2.6}$$

An example of area scaling is shown in Fig. 2.11. As the reliability measurement is usually performed on individual transistors, this law is very useful for the lifetime prediction of a whole chip of which the gate dielectric under stress corresponds to the gate area of thousands of transistors.

The origin of the breakdown statistics described above can be explained by the percolation theory [46–50], which states that the breakdown occurs when the created defects form a conduction path (a percolation path) linking the gate electrode to the silicon substrate. The properties of the the breakdown statistics, such as the Weibull distribution, area scaling and oxide thickness dependent Weibull shape factor  $\beta$ , as predicted by the percolation model agrees very well with the experimental results.

#### 2.4.4 Post breakdown mode

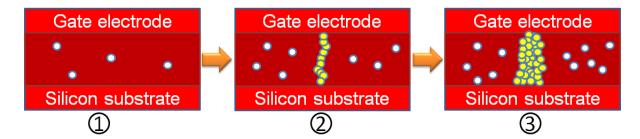

The breakdown process described by the percolation theory can be divided into three stages as shown in Fig. 2.13:

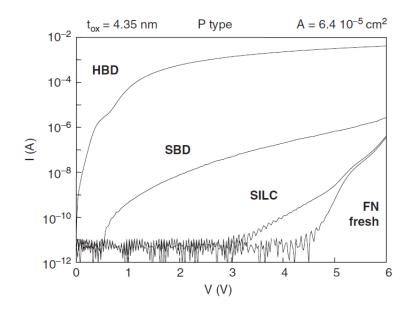

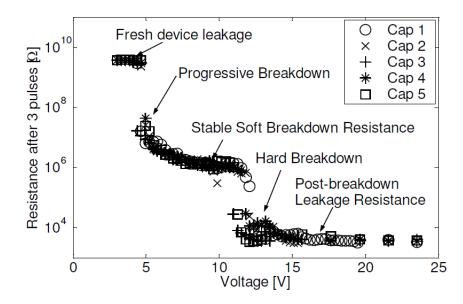

- Defect creation: as the stress starts, defects are created at random locations inside the gate oxide. These defects increase the gate leakage current slightly (Stress Induced Leakage Current, SILC) as shown in Fig. 2.14.

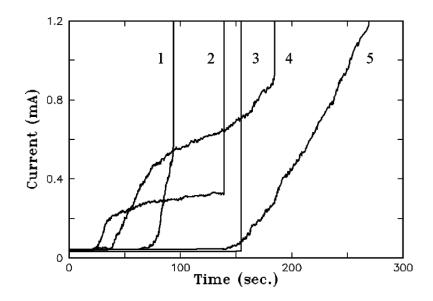

- 2. Breakdown path creation: breakdown occurs when the created defects form a conduction path linking the Si substrate to the gate electrode.

- 3. Breakdown path wearout: the created breakdown path wears out, leading to an abrupt increase in the gate leakage current or a progressively increased gate leakage current.