## University of Massachusetts Amherst ScholarWorks@UMass Amherst

**Doctoral Dissertations**

Dissertations and Theses

2018

## A Study of High Performance Multiple Precision Arithmetic on Graphics Processing Units

Niall Emmart

Follow this and additional works at: https://scholarworks.umass.edu/dissertations\_2

Part of the <u>Information Security Commons</u>, <u>Numerical Analysis and Scientific Computing Commons</u>, and the <u>Theory and Algorithms Commons</u>

#### Recommended Citation

Emmart, Niall, "A Study of High Performance Multiple Precision Arithmetic on Graphics Processing Units" (2018). *Doctoral Dissertations*. 1164.

$https://scholarworks.umass.edu/dissertations\_2/1164$

This Open Access Dissertation is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# A STUDY OF HIGH PERFORMANCE MULTIPLE PRECISION ARITHMETIC ON GRAPHICS PROCESSING UNITS

A Dissertation Presented

by

NIALL EMMART

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

February 2018

College of Information and Computer Sciences

© Copyright by Niall Emmart 2018

All Rights Reserved

# A STUDY OF HIGH PERFORMANCE MULTIPLE PRECISION ARITHMETIC ON GRAPHICS PROCESSING UNITS

A Dissertation Presented

by

NIALL EMMART

| Approved as to style and content by: |           |             |             |  |

|--------------------------------------|-----------|-------------|-------------|--|

|                                      |           |             |             |  |

| Charles C. Weems, Chair              |           |             |             |  |

|                                      |           |             |             |  |

| J. Eliot B. Moss, Member             |           |             |             |  |

|                                      |           |             |             |  |

| David A. Mix Barrington, Member      |           |             |             |  |

|                                      |           |             |             |  |

| Israel Koren, Member                 |           |             |             |  |

|                                      |           |             |             |  |

|                                      | Iames All | an Chair of | the Faculty |  |

College of Information and Computer Sciences

## **DEDICATION**

To Zoya

#### ACKNOWLEDGMENTS

I want to express my deeply-felt thanks to my thesis advisor, Professor Charles Weems, for his enthusiasm and warm encouragement. This thesis would not have been possible without his generosity and thoughtful guidance throughout my graduate studies. I also thank the other members of my committee: Professor J. Eliot B. Moss, for his encouragement, and careful reading of the text, and Professors David A. Mix Barrington and Israel Koren for their feedback and helpful comments.

I am grateful to Justin Luitjens, Cliff Woolley, and the team at NVIDIA for their support and sharing their deep knowledge of GPU architectures, compilers and software tuning and to Professor Yang Chen for putting me on the path toward research on multiple precision arithmetic. Thanks to Arjun Jayadev for his advice and encouragement and to Fabricio Murai Ferreira and Mostafa Dehghan for their comradery.

Finally, I wish to thank my family: to my parents, Martini Niedbalski-Emmart and Bob Niedbalski for their encouragement and for instilling an interest in academics, and to my wife and daughter, Sunitha and Zoya, for giving me the time and unwavering support to pursue a Ph.D.

This thesis is based in part upon work supported by the National Science Foundation under Award Numbers CCF-1217590 and CCF-1525754.

#### **ABSTRACT**

## A STUDY OF HIGH PERFORMANCE MULTIPLE PRECISION ARITHMETIC ON GRAPHICS PROCESSING UNITS

#### FEBRUARY 2018

#### **NIALL EMMART**

B.A., UNIVERSITY OF MASSACHUSETTS, AMHERST M.Sc., UNIVERSITY OF MASSACHUSETTS, AMHERST Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Charles C. Weems

Multiple precision (MP) arithmetic is a core building block of a wide variety of algorithms in computational mathematics and computer science. In mathematics MP is used in computational number theory, geometric computation, experimental mathematics, and in some random matrix problems. In computer science, MP arithmetic is primarily used in cryptographic algorithms: securing communications, digital signatures, and code breaking. In most of these application areas, the factor that limits performance is the MP arithmetic. The focus of our research is to build and analyze highly optimized libraries that allow the MP operations to be offloaded from the CPU to the GPU. Our goal is to achieve an order of magnitude improvement over the CPU in three key metrics: operations per second per socket, operations per watt, and operation per second per dollar. What we find is that the SIMD design and balance of compute, cache, and bandwidth resources on the GPU is quite different from the CPU, so libraries such as GMP cannot simply be ported to the GPU. New

vi

approaches and algorithms are required to achieve high performance and high utilization of GPU resources. Further, we find that low-level ISA differences between GPU generations means that an approach that works well on one generation might not run well on the next.

Here we report on our progress towards MP arithmetic libraries on the GPU in four areas: (1) large integer addition, subtraction, and multiplication; (2) high performance modular multiplication and modular exponentiation (the key operations for cryptographic algorithms) across generations of GPUs; (3) high precision floating point addition, subtraction, multiplication, division, and square root; (4) parallel short division, which we prove is asymptotically optimal on EREW and CREW PRAMs.

## TABLE OF CONTENTS

|            |            |                |                                                                | Page                                                                                            |

|------------|------------|----------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| <b>A</b> ( | CKN(       | OWLED          | GMENTS                                                         | S                                                                                               |

| AI         | BSTR       | ACT            |                                                                | vi                                                                                              |

| LI         | ST O       | F TABI         | LES                                                            | xii                                                                                             |

| LI         | ST O       | F FIGU         | JRES                                                           | xv                                                                                              |

| CI         | НАРТ       | ER             |                                                                |                                                                                                 |

| 1.         | INT        | RODU           | CTION                                                          | 1                                                                                               |

|            | 1.1<br>1.2 |                |                                                                | s for Multiple Precision Arithmetic                                                             |

| 2.         | LIT        | ERATU          | RE SURV                                                        | YEY 5                                                                                           |

|            | 2.1<br>2.2 |                | _                                                              | ntation                                                                                         |

|            |            | 2.2.1<br>2.2.2 |                                                                | and Subtraction                                                                                 |

|            |            |                | 2.2.2.1<br>2.2.2.2<br>2.2.2.3<br>2.2.2.4<br>2.2.2.5<br>2.2.2.6 | Grade School7Karatsuba7Toom-Cook8FFT Multiplication9Schönhage-Strassen10Faster Multiplication11 |

|            |            | 2.2.3<br>2.2.4 | Division                                                       | rring                                                                                           |

|            |            |                | 2.2.4.1<br>2.2.4.2                                             | Grade School                                                                                    |

|            |                                  | 2.2.4.3                                             | Newton-Raphson                                                                                                                               | 4              |

|------------|----------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|            | 2.2.5                            | Specializ                                           | red Division Algorithms                                                                                                                      | 6              |

|            |                                  | 2.2.5.1<br>2.2.5.2                                  | Exact Division                                                                                                                               |                |

|            | 2.2.6                            | Remaind                                             | er / Modulo Reduction                                                                                                                        | 8              |

|            |                                  | 2.2.6.1<br>2.2.6.2                                  | Barrett Reduction                                                                                                                            |                |

|            | 2.2.7                            | Special N                                           | Moduli                                                                                                                                       | !4             |

|            |                                  | 2.2.7.1<br>2.2.7.2<br>2.2.7.3<br>2.2.7.4<br>2.2.7.5 | Special Modulus $2^k - 1$ 2Special Modulus $2^k + 1$ 2Special Modulus $2^{2k} - 2^k + 1$ 2Generalized Mersenne Moduli2Single Word Remainder2 | 24<br>24<br>25 |

|            | 2.2.8<br>2.2.9                   |                                                     | Coot Algorithms       2         Exponentiation Algorithms       2                                                                            |                |

|            |                                  | 2.2.9.1<br>2.2.9.2<br>2.2.9.3                       | Exponentiation by Squaring2Fixed Window Exponentiation2Sliding Window Exponentiation2                                                        | 27             |

| 2.3        | Paralle                          | l Algorith                                          | ms for Multiple Precision Arithmetic                                                                                                         | 28             |

|            | 2.3.1<br>2.3.2<br>2.3.3          | Multiplic                                           | and Subtraction / Carry Resolution                                                                                                           | 29<br>29       |

|            |                                  | 2.3.3.2                                             | Parallel Short Division                                                                                                                      | 0              |

| 2.4<br>2.5 |                                  |                                                     | Precision Implementations on CPUs                                                                                                            |                |

|            | 2.5.1                            |                                                     | raphic Operations Requiring Multiple Precision                                                                                               | , 7            |

|            | 2.5.2<br>2.5.3<br>2.5.4<br>2.5.5 | GPU Bas<br>GPU Bas                                  | metic                                                                                                                                        | 10<br>16<br>50 |

|            | 2.5.6                            | Parallel A                                          | Algorithms                                                                                                                                   | 52             |

|            | 2.5.7                            | Asymme                                              | tric Cryptography Primitives on the GPU                                                                                                      | 13             |

|    |                                 | 2.5.8                     | MP Libraries on the GPU                                                                                                              | 53             |

|----|---------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3. |                                 |                           | OTICALLY OPTIMAL PARALLEL SHORT DIVISION / ON BY CONSTANTS                                                                           | 55             |

|    | 3.1                             | Prior V                   | Work                                                                                                                                 | 57             |

|    |                                 | 3.1.1<br>3.1.2<br>3.1.3   | Division By Constants                                                                                                                | 57             |

|    | 3.2                             | Short 1                   | Division Algorithm                                                                                                                   | 58             |

|    |                                 | 3.2.1                     | Proof of Correctness                                                                                                                 | 62             |

|    | 3.3<br>3.4                      |                           | ections to Parallel Prefix/Suffix Sum                                                                                                |                |

|    |                                 | 3.4.1<br>3.4.2            | Asymptotic lower bound for REMPAR on a CREW PRAM Asymptotic lower bounds for short division on a CREW PRAM                           |                |

|    |                                 | 3.4.3                     | Short division algorithm is asymptotically optimal for all $d$                                                                       |                |

|    | 3.5                             | Experi                    | iments and Results                                                                                                                   | 73             |

|    |                                 | 3.5.1<br>3.5.2<br>3.5.3   | Parallel Short Division Algorithms Tested  Experimental Setup  Results and Discussion                                                | 74             |

| 4. | HIG                             | H PRE                     | CCISION FLOATING POINT ARITHMETIC                                                                                                    | 78             |

|    | 4.1<br>4.2<br>4.3<br>4.4<br>4.5 | Impler<br>Experi<br>Compa | y Feature Overview and API mentation and Important Algorithms imental Testing and Results arison to Prior Work usion and Future Work | 81<br>92<br>95 |

| 5. |                                 |                           | NSIGNED INTEGER ADDITION, SUBTRACTION AND PLICATION                                                                                  | 99             |

|    | 5.1<br>5.2                      | _                         | Integer Addition and Subtraction                                                                                                     |                |

|    |                                 | 5.2.1<br>5.2.2<br>5.2.3   | Fast Modulo                                                                                                                          | 113            |

|    |      |         | <ul><li>5.2.3.1 Avoiding Transpose Operations</li></ul> |     |

|----|------|---------|---------------------------------------------------------|-----|

|    |      | 5.2.4   | CUDA Implementation and Optimizations                   |     |

|    |      | 5.2.5   | Experimental Setup and Results                          |     |

|    |      | 5.2.6   | Conclusion and Future Work                              | 125 |

| 6. |      |         | R EXPONENTIATION ACROSS MULTIPLE GENERATIO              |     |

|    |      | OF GPU  | U                                                       | 127 |

|    | 6.1  | Backg   | ground                                                  | 129 |

|    |      | 6.1.1   | Code Generator                                          | 131 |

|    | 6.2  | Relate  | ed Work                                                 | 133 |

|    | 6.3  | Three   | N Model                                                 | 134 |

|    | 6.4  | Two N   | N Plus Local Model                                      | 136 |

|    | 6.5  | Sampl   | led Model                                               | 138 |

|    | 6.6  | Distrib | buted Model                                             | 140 |

|    | 6.7  | Experi  | imental Setup and Results                               | 142 |

|    |      | 6.7.1   | Utilization                                             | 143 |

|    |      | 6.7.2   | Results and Discussion                                  | 147 |

|    | 6.8  | Comp    | arison to Prior Work                                    | 150 |

|    | 6.9  | Conclu  | usions                                                  | 153 |

| 7. | МО   | DULAI   | R EXPONENTIATION USING DOUBLE PRECISION                 |     |

|    | ]    | FLOAT   | TING POINT ARITHMETIC                                   | 155 |

|    | 7.1  | New A   | Approach Using Wide Samples                             | 156 |

|    | 7.2  |         | rmance Estimates for Various Cards                      |     |

|    | 7.3  |         | mentation of Modular Exponentiation using Wide Samples  |     |

|    | 7.4  | _       | imental Setup and Results                               |     |

|    | 7.5  |         | usions and Future Work                                  |     |

| 8. | CO   | NCLUS   | SION                                                    | 171 |

|    |      |         |                                                         |     |

| Al |      |         | PERFORMANCE ACROSS A RANGE OF CPUS AND                  |     |

|    |      | GPUS.   |                                                         | 175 |

| ΒI | RI I | )CR A P | PHV                                                     | 180 |

## LIST OF TABLES

| Table | P                                                                                                                   | age  |

|-------|---------------------------------------------------------------------------------------------------------------------|------|

| 2.1   | Dominant computations at the heart of important cryptography algorithms                                             | . 37 |

| 2.2   | Operations in the finite field $\mathbf{F}_{\mathbf{M}}$ EC point doubling, addition, and scalar multiplication     | . 39 |

| 3.1   | Run time results for algorithms where $n=2p\ldots$                                                                  | . 76 |

| 4.1   | Arrays based floating point library API for the GPU                                                                 | . 80 |

| 4.2   | Special value handling for floating point addition                                                                  | . 82 |

| 4.3   | GPU running time in milliseconds                                                                                    | . 93 |

| 4.4   | CPU running time in milliseconds                                                                                    | . 94 |

| 4.5   | Speedup table: CPU running time / GPU running time                                                                  | . 95 |

| 4.6   | A comparison of this work to Honda, Ito, and Nakano's                                                               | . 95 |

| 4.7   | A comparison of this work to Nakayama and Takahashi's                                                               | . 96 |

| 4.8   | Performance of the Hénon map implmented with CAMPARY running on a Tesla C2075 GPU                                   | . 97 |

| 5.1   | XOR kernels and memory bandwidth achieved                                                                           | 102  |

| 5.2   | Bandwidth achieved by the Large Adder kernels, the XOR kernels, and the CUDA memory copy routines for various sizes | 107  |

| 5.3   | Effect of long carry chains on achieved bandwidth                                                                   | 109  |

| 5.4   | Large integer multiplication performance on the GTX 980 and a Core i5-7400                                          | 125  |

| 6.1 | Instruction counts to perform modular exponentiation                                                     |

|-----|----------------------------------------------------------------------------------------------------------|

| 6.2 | Instructions/Cycles for each madc.lo, madc.hi and add/sub across the generations of GPU cards            |

| 6.3 | Impact of Karatsuba on Performance - 512 bits with $w=5$ and a launch geometry of 128 threads per block  |

| 6.4 | Impact of algorithms on Performance - 512 bits with $w=5$ and a launch geometry of 128 threads per block |

| 6.5 | Impact of Launch Geometry on Performance - GTX 580, 512 bits with $w=5$                                  |

| 6.6 | Impact of Register Max allocation on Performance - GTX 580, 512 bits with LG=128, $w=5\ldots\ldots150$   |

| 6.7 | Best Performing Model by Size and Card                                                                   |

| 7.1 | Cycles required to dispatch a 52-bit sampled or 32-bit integer FPACS to a warp of 32 threads             |

| 7.2 | NVIDIA Driver / GPU card settings                                                                        |

| 7.3 | Parameter that deliver the best performane on 1024, 1536 and 2048 bit modular exponentiation             |

| 7.4 | Performance results for three sizes and different warm up counts and timing run counts                   |

| 8.1 | Speedup table: Throughput / Xeon E5-2690 Throughput                                                      |

| 8.2 | Speedup table: Throughput / Core i5-7400 Throughput                                                      |

| A.1 | Parallel MPFR on a Core i5-7400 (running time in milliseconds) 176                                       |

| A.2 | Parallel MPFR on a Xeon E5-2690v3 (running time in milliseconds) 176                                     |

| A.3 | Our FP library on a GTX Titan Black (running time in milliseconds)177                                    |

| A.4 | Our FP library on a GTX 980 (running time in milliseconds) 177                                           |

| A.5 | Our FP library on a P100 card (running time in milliseconds)                                             |

| A.6 | Our FP library on a V100 card (running time in milliseconds)                                             |

| A.7 | Parallel GMP <i>mpz_powm</i> throughput (operations per second) 179                       |

|-----|-------------------------------------------------------------------------------------------|

| A.8 | GPU <i>modexp</i> throughput (ops/sec) using the code generation approach (see Chapter 6) |

| A.9 | GPU <i>modexp</i> throughput (ops/sec) using wide samples (see Chapter 7)                 |

## LIST OF FIGURES

| re Pa                                                                         | ige |

|-------------------------------------------------------------------------------|-----|

| Product terms to be summed for an $n$ -word by $n$ -word multiply             | . 7 |

| 2.2 Computation using Montgomery Representation                               | 19  |

| 2.3 Montgomery Product Algorithm                                              | 21  |

| 2.4 Product terms in the word-by-word approach to a Montgomery reduction      | 22  |

| 2.5 Summary of SOS, CIOS, FIOS, FIPS                                          | 23  |

| 2.6 Short Division Example                                                    | 30  |

| 2.7 Takahashi's parallel remainder sequence algorithm                         | 32  |

| Example division and remainder sequence for $X=9935631, d=7,$ and $\beta=100$ | 58  |

| 3.2 Parallel short division algorithm                                         | 60  |

| 3.3 X represented as an array of bits                                         | 68  |

| REMPAR $_{l,d_o}(V)$ algorithm implemented using short division               | 71  |

| 1.1 Computing the guard bits for floating point addition                      | 83  |

| 1.2 Correct rounding for floating point addition                              | 83  |

| 1.3 Comparing unsigned MP values represented as slices                        | 85  |

| 4.4 Count the leading zeros of an unsigned MP integer represented as slices   | 86  |

| 5 Increment an unsigned MP integer represented as slices                      | 86  |

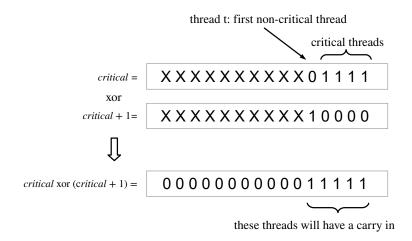

| 4.6  | Carry propagation across critical threads                                               |

|------|-----------------------------------------------------------------------------------------|

| 4.7  | Low-level implemation of increment                                                      |

| 4.8  | Negate an unsigned MP integer represented as slices                                     |

| 4.9  | Resolve the carry words across a warp                                                   |

| 4.10 | Multiplication algorithm for two MP values represented as slices 89                     |

| 4.11 | Construct an approximation of the inverse of a 32-bit value90                           |

| 4.12 | 64 bits divided by 32 bits                                                              |

| 4.13 | Division algorithm for two MP values represented as slices                              |

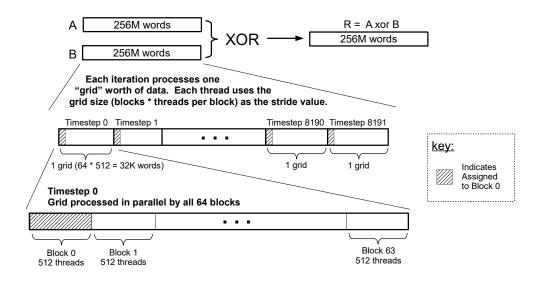

| 5.1  | Grid Stride Loop processing using 64 blocks and 512 threads per block                   |

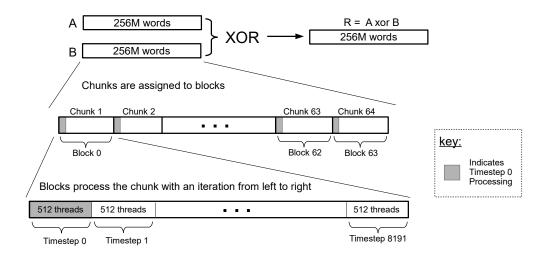

| 5.2  | Block Stride Loop processing using 64 blocks and 512 threads per block                  |

| 5.3  | Large addition using two kernels: Parallel Chunk Addition followed by  Carry Resolution |

| 5.4  | Parallel Chunk Addition kernel pseudo-code                                              |

| 5.5  | Parallel Chunk Resolution kernel pseudo-code                                            |

| 5.6  | Strassen's FFT Multiplication Algorithm                                                 |

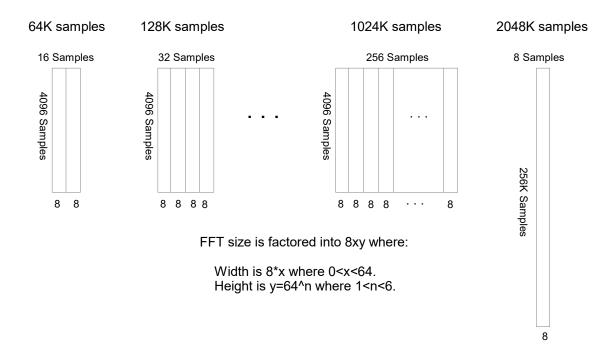

| 5.7  | FFT layouts as the number of samples is doubled                                         |

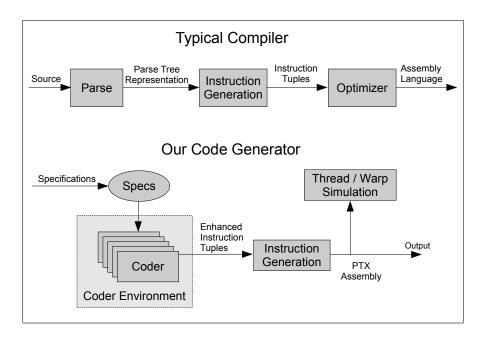

| 5.8  | 64K-Point Convolution using the Cooley-Tukey 4-step algorithm 115                       |

| 5.9  | 64K-Point Convolution using the Cooley-Tukey 4-step algorithm, without transposes       |

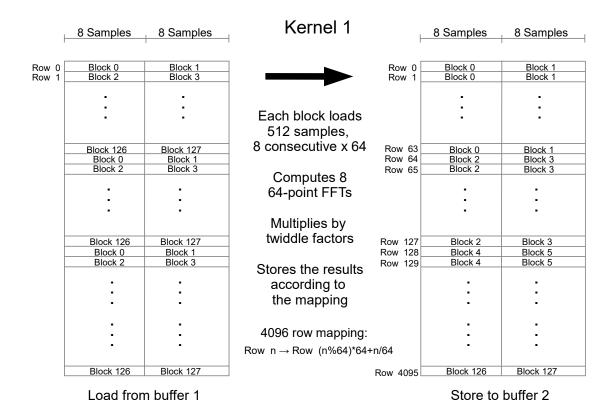

| 5.10 | 64K-Point FFT example: Column FFTs - Step 1                                             |

| 5.11 | 64K-Point FFT example: Column FFTs - Step 2                                             |

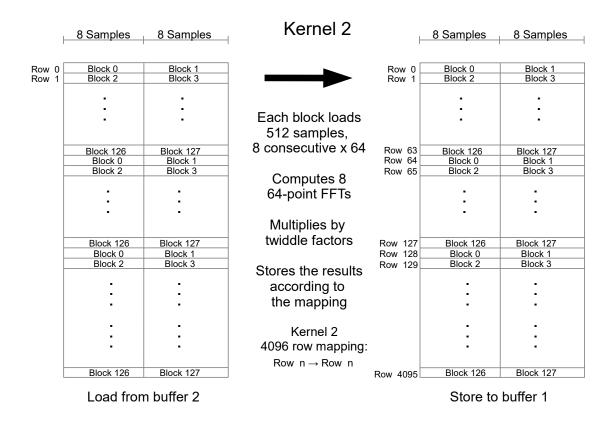

| 5.12 | 64K-Point FFT example: Row FFTs                                                         |

| 5.13 | Exponentiation by Squaring                                                              |

| 5.14 | Unrolled Exponentiation by Squaring                                                                                                                    | 120 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.15 | Unrolled Exponentiation, 2-bits at a Time                                                                                                              | 121 |

| 5.16 | Transpose - 5 Shared Memory Cycles per warp per sample                                                                                                 | 121 |

| 5.17 | Optimum - 4 Shared Memory Cycles per warp per sample                                                                                                   | 122 |

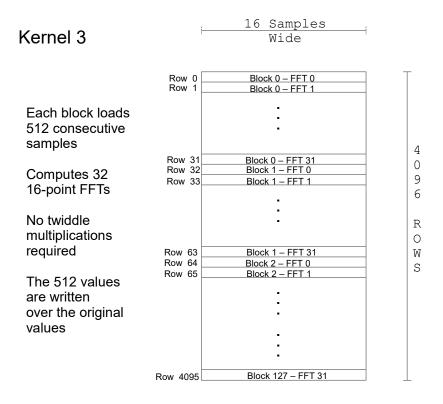

| 6.1  | Typical Compiler vs. Our Code Generator                                                                                                                | 132 |

| 6.2  | Fixed Window Exponentiation                                                                                                                            | 133 |

| 6.3  | The API methods of the ExponentiationModel interface                                                                                                   | 134 |

| 6.4  | Three N Multiplication                                                                                                                                 | 135 |

| 6.5  | Local Model Almost Montgomery Reduction                                                                                                                | 137 |

| 6.6  | 48-bit Dot Product                                                                                                                                     | 138 |

| 6.7  | Sampled Multiplication                                                                                                                                 | 139 |

| 6.8  | Distributed Multiply and Reduce                                                                                                                        | 141 |

| 7.1  | Compute the high and low product of two samples using fused multiply and add                                                                           | 157 |

| 7.2  | Normalized high and low products. Note, this algorithm <b>requires</b> rounding towards zero. Rounding towards nearest will produce incorrect results. | 158 |

| 7.3  | MP Sampled Product Algorithm                                                                                                                           | 159 |

| 7.4  | Compute the initial value for a column sum                                                                                                             | 159 |

| 7.5  | 52-bit sampled row multiplier                                                                                                                          | 162 |

| 7.6  | 52-bit sampled modular multiplication based on a CIOS Montgomery product                                                                               | 163 |

| 77   | 52-bit sampled carry resolution routine                                                                                                                | 165 |

#### CHAPTER 1

#### INTRODUCTION

Multiple precision (MP) arithmetic is a field of growing importance. It is a key component in cryptography (e.g., securing communications, digitial signatures, and next generation secure internet architectures), experimental mathematics (e.g., finding integer relations in real-valued infinite series), computational number theory (e.g., prime testing, prime proving, factoring), random matrix theory (e.g., least eigenvalues), quantum field theory (e.g., zeta function identities), analysis of chaotic functions (e.g., logistic map), and computing high precision constants.

A significant increase in the speed of MP calculations is needed to enable breakthroughs in these areas. In addition, if a significant performance boost can be achieved with a modest increase in cost and power, then we open the door to both commercial applications (such as enabling wider use of encrypted communication channels and longer keys) and to a larger community of researchers who can make use of MP arithmetic on affordable platforms.

Graphics processors (GPUs) have been applied in a wide range of areas of high performance computing because their performance considerably exceeds CPU performance for certain kinds of fine-grained data-parallel algorithms, at costs far lower than custom processors, and with a very attractive performance per watt. Their performance is such that 65 machines in the November 2016 TOP500 list use NVIDIA GPU accelerators. The major problem is that it can be difficult to write and tune the software to fully exploit the potential performance.

Developing and maintaining an MP library for GPUs faces a major hurdle in that successive generations of GPU architecture change in ways that necessitate non-standard

optimizations and alternate algorithmic approaches. To be useful, a library must be upwards portable so that users can continue to rely on it as they upgrade hardware. In addition, it must support a wide range of MP value sizes, which imposes significant variations in the demands that are placed on the limited resources of the GPU's thread engines. These challenges are further complicated by aspects of the vendor supplied development tools that stand in the way of the necessary optimizations. Even so, developing a scalable, portable MP arithmetic library for GPUs offers the potential for performance increases of up to two orders of magnitude.

### 1.1 Application Areas for Multiple Precision Arithmetic

Multiple precision arithmetic is one of the fundamental building blocks of cryptographic algorithms from key exchange (RSA, Diffie-Hellman, ECHD) to digitial signature standards (DSA, ECDSA), to prime testing (Miller-Rabin) and proving (AKS), and factoring (ECM, QS, SNFS, GNFS). These algorithms are used to secure communications and to authenticate authorship/ownership of data, and underpin significant areas of the modern economy: e-commerce, secure WWW browsing through Public Key Infrastructure (PKI), secure inter-bank transfers, peer-to-peer networking, crypto-currencies, smart cards, digital signatures for software (e.g., apps), secure utility grids, command and control systems, military communications, etc. Significantly reducing the cost and increasing the performance of cryptographic algorithms could lead to wider deployment of cryptography with better privacy and security, and entirely new applications with the potential for widespread benefits.

New internet architectures such as content centric networking (CCN) [63], which use a digital signature with each packet, will require very high performance, low power, and low cost modular exponentiation support. In addition, research into fully homomorphic encryption (FHE) [51] depends on very high precision arithmetic.

Experimental mathematics is yielding high-value results using MP arithmetic. In particular, integer relation algorithms were named among the top ten algorithms of the 20<sup>th</sup> century. The most widely used, PSLQ [45], searches for relations between high precision real values for a costly function, such as an infinite series, and a set of mathematical constants, to establish the likelihood of a closed form expression of the function. Among its well known applications was finding a formula to compute any digit of pi in base two [3]. It has also found closed forms for multiple zeta functions from quantum field theory, and for identifying bifurcation points in the chaotic logistic map function. Accelerating very high precision arithmetic with GPUs will enable more extensive searches for a wider range of functions.

Multiple precision arithmetic is essential in computational number theory research, aiding in the search for and proving of new primes, and for factorization. Certain problems in random matrix theory, such as our recent work in finding the least eigenvalues of ill-conditioned Hankel matrices, depend on extreme levels of precision to produce meaningful results. Lastly, of course, our package will be useful in the computation of high precision values for mathematical constants.

These are compelling applications and a number of researchers have attempted to build MP libraries for the GPU, but none of them meet all the important criteria: high performance, multiple generations of GPU, and support for a wide range of sizes.

#### 1.2 The Thesis

The thesis that this dissertation will address is:

"Offloading multiple precision arithmetic computations from the CPU to the GPU will result in an order of magnitude boost in performance across three metrics: operations per second per socket, operations per watt, and operations per second per dollar. However, due to the SIMD design and different balance of compute, cache, and bandwidth resources

on the GPU, achieving such a high level of performance requires new approaches and algorithms."

We will validate this thesis by building and testing three multiple precision GPU libraries. The first will implement multiple precision floating point addition, subtraction, multiplication, division, and square root with mantissas that can range in size from 1024 bits to 8192 bits. The second will implement modular exponentiation using integer operations on sizes that range from 256 bits to 2048 bits. The third will implement modular exponentiation using double precision floating point arithmetic. We will compare the GPU libraries to GMP [54] and MPFR [48] two high performance libraries on the CPU.

#### **CHAPTER 2**

#### LITERATURE SURVEY

The literature survey is organized as five sections. Section 2.1 covers number representation. Section 2.2 covers the relevant sequential multiple precision arithmetic algorithms, giving both the literature review and an overview of how the algorithms work. These algorithms serve as core background knowledge for the proposal. In Section 2.3 we cover the relevant parallel multiple precision algorithms that operate in a manner that is different from their sequential counterparts. Section 2.4 covers parallel CPU implementations of multiple precision arithmetic and Section 2.5 covers GPU implementations.

### 2.1 Number Representation

There are two common number representations for unsigned high precision positive integers, positional fixed radix number systems (FRNS) and residue number systems (RNS). In an FRNS the radix  $\beta$  is typically chosen to be power of two, such as  $2^{32}$  on 32-bit machines or  $2^{64}$  on 64-bit machines. A high precision number, X is then represented as a sequence of n values (computer words)  $x_0, x_1, \dots, x_{n-1}$  where  $X = \sum_{i=0}^{n-1} x_i \beta^i$ , and  $0 \le x_i < \beta$ . The  $x_i$  values are ofted referred to as limbs. The range of X that can be uniquely represented by n-words is  $0 \dots \beta^n - 1$ . In an RNS, a set of pair-wise coprime moduli,  $\{m_i\}$  are chosen. Then X is represented as a sequence of moduli,  $x_i = X \mod m_i$ . The range of X that can be uniquely represented is  $0 \dots \left(\prod_{i=1}^n m_i\right) - 1$ . In an RNS, addition, subtraction and multiplication are all linear time operations, computed component-wise:

$$(X \pm Y)_i = (x_i \pm y_i) \mod m_i$$

$$(X \cdot Y)_i = (x_i \cdot y_i) \mod m_i$$

Due to the component-wise nature, these operations are inherently parallel, requiring no communication between the components. However, other common arithmetic operations, such as comparison, division, and modulo (by arbitrary values) are much slower. In effect, what the implementations do is convert the RNS representation to an FRNS representation and use standard algorithms. RNS representations also suffer from two other drawbacks. First, the representation is not as compact as FRNS representations on binary computers. Second, it's quite easy to extend the range of X in an FRNS, just by adding another word and increasing n. In an RNS, one must dynamically construct an extra modulus for the set  $\{m_i\}$  on the fly and precompute various constants needed to support the new modulus. For much more on conventional and unconventional number representations, we refer the reader to *Computer Arithmetic Algorithms* by Koren [75].

For the remainder of this proposal, we will use the convention that capital letters represent unsigned multiple precision values, represented in an FRNS (with radix  $2^w$  where w is the machine word size) unless otherwise stated. Lower case letters represent single word values in the range of 0 to  $\beta - 1$ .

## 2.2 Sequential Algorithms

There are several textbooks with good introductory material on sequential multiple precision algorithms. These include Knuth's *The Art of Computer Programming, Volume 2, Seminumerical Algorithms* [73], Koren's *Computer Arithmetic Algorithms* [75] and Brent and Zimmermann's *Modern Computer Arithmetic* [16].

#### 2.2.1 Addition and Subtraction

Addition and subtraction of two n-word multiple precision (MP) values,  $A \pm B$ , are performed with the traditional grade school algorithm, going from the least significant word to the most significant word, pushing the carry/borrow along. These algorithms run in O(n) time and there are no faster algorithms, because all n words of A and B must be read.

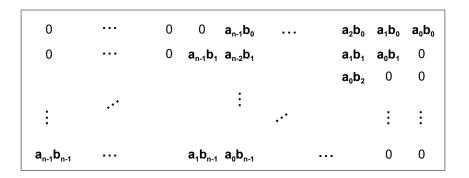

**Figure 2.1.** Product terms to be summed for an *n*-word by *n*-word multiply.

#### 2.2.2 Multiplication

For multiplication there are six main algorithms for computing the product of two n-word MP values, A and B. These algorithms are presented below. The five general purpose algorithms form a ladder, with decreasing asymptotic complexity, but unfortunately, as we move up the ladder, the asymptotic notation hides increasing constants. Thus, for small n, it's actually faster to use the algorithms at the lower rungs of the ladder than the algorithm at the top. A good multiple precision library usually implements several of these algorithms, and will have some kind of tuning procedure to determine the best sizes of n (crossover points) to switch between algorithms.

**2.2.2.1 Grade School:** the grade school is the simplest algorithm, where the  $n^2$  product terms of Figure 2.1 are summed along the columns from the right to the left. This algorithm runs in  $O(n^2)$  time.

**2.2.2.2 Karatsuba:** the Karatsuba multiplication algorithm [69] is an asymptotically faster recursive divide and conquer approach. It works by splitting the A and B value into upper and lower halves,  $A = A_H \beta^{\lceil n/2 \rceil} + A_L$  and  $B = B_H \beta^{\lceil n/2 \rceil} + B_L$ . Computing the product  $A \cdot B$  requires computing three sub-products,  $A_H \cdot B_H$ ,  $A_L \cdot B_L$ , and  $(A_H + A_L) \cdot (B_H + B_L)$ . If the length of the sub-products is short enough, it's faster to compute them with the grade school multiplier. If they are still large, then the code recursively calls the Karatsuba multiplier. The product,  $A \cdot B$  is easily computed from the three sub-products.

Since Karatsuba is a recursive divide and conquer algorithm and computing the final product from the sub-products runs in time O(n), we can express the Karatsuba run time as  $K(n) = 3K(\lceil n/2 \rceil) + \Theta(n)$  and by the Master Theorem (see for example [27]), the run time is  $\Theta(n^{log_23})$ , i.e.,  $\Theta(n^{1.58})$ .

There are a few variants of the Karatsuba approach, such as using  $A_H - A_L$  and/or  $B_H - B_L$  (instead  $A_H + A_L$  and  $B_H + B_L$ ) and using different split points instead of  $\lceil n/2 \rceil$ . These are described in Knuth [73] and Brent and Zimmermann [16].

**2.2.2.3 Toom-Cook:** proposed by Toom [105] and improved by Cook [24], Toom-Cook multiplication is also a divide and conquer algorithm. But instead of Karatsuba's approach of dividing A and B into halves, Toom-Cook divides them into 3 or more pieces. Toom-Cook is not a single algorithm, rather it is a family of algorithms: Toom-Cook 3-way, 4-way, 5-way, etc, depending on the split count, k.

Toom-Cook works by mapping A and B to k-1 degree polynomials, S(x) and T(x), such that  $S(\beta^{\lceil n/k \rceil}) = A$  and  $T(\beta^{\lceil n/k \rceil}) = B$ . For example, when k=3, we have

$$S(x) = S_2 x^2 + S_1 x + S_0$$

and

$$S(\beta^{\lceil n/3 \rceil}) = S_2 \beta^{2\lceil n/3 \rceil} + S_1 \beta^{\lceil n/3 \rceil} + S_0 = A$$

thus  $S_0, S_1, S_2$  split A into thirds.  $S_0$  is the least significant  $\lceil n/3 \rceil$  words of A,  $S_1$  is the middle third and  $S_2$  is the remaining most significant third. The S and T coefficients are analogous to the Karatsuba  $A_h, A_l, B_h$ , and  $B_l$  terms.

Next, Toom-Cook determines the product polynomial,  $P(x) = S(x) \cdot T(x)$ , with polynomial interpolation via a Vandermonde matrix. Since P(x) is degree 2k-2 we'll need 2k-1 evaluation points for the interpolation. These interpolation points can be arbitrarily chosen, for example:  $P(0) = S(0) \cdot T(0)$ ,  $P(1) = S(1) \cdot T(1)$ ,  $P(2) = S(2) \cdot T(2)$ ,  $\cdots$ ,  $P(2k-2) = S(2k-2) \cdot T(2k-2)$ . Performing the interpolation thus requires computing 2k-1 sub-products, but these sub-products are much shorter than

A and B because for small x, S(x) and T(x) will be roughly n/k words in length. If the lengths of the sub-products are small enough, then it's faster to compute them with the grade school multiplier. If they are still large, the code calls the Toom-Cook multiplier recursively.

The next step is to determine the coefficients of P(x), which requires solving the Vandermonde system of 2k-1 linear equations. Since a general linear solver would be quite slow, in practice, Toom-Cook implementations fix a set of evaluation points for each k, and implement a custom piece of code to solve the resulting specific linear system. Thus, a fast multiple precision library tends to have a few implementations of Toom-Cook, for specific values of k, rather than a general solver that works for any k. Once P(x) is in hand, the product  $A \cdot B$  can be computed by evaluating  $P(\beta^{\lceil n/k \rceil})$ .

The running time of Toom-Cook can be expressed as  $TC(n) = (2k-1)TC(\lceil n/k \rceil) + \Theta(n)$ , and again by the Master Theorem, we have  $TC(n) = \Theta(n^{\log_k 2k-1})$ .

The actual performance of a Toom-Cook implementation depends heavily on the interpolation points used. For small k, the best interpolation points have been extensively researched by Cook [24], Knuth [73], Zuras [114], Zimmermann, and Bodrato [13, 14]. Further, it has been shown (see for example Chung and Hasan [21]) when  $k \geq 3$ , the interpolation step requires an exact division by a non-power of two constant. Thus an efficient Toom-Cook implementation requires an efficient short division implementation.

For unbalanced multiplication, where the length of A is longer or shorter than the length of B, different split counts can be used on A and B. See Section 1.3.5 of Brent and Zimmermann [16] for details.

**2.2.2.4 FFT Multiplication:** FFT Multiplication splits the A and B values into fixed length pieces,  $A = (a_0, a_1, \cdots, a_{k-1}), B = (b_0, b_1, \cdots, b_{k-1})$ . The  $a_i$  and  $b_i$  terms can be thought of as "digits" or as "samples". The grade school algorithm tells us that the product sum of the i<sup>th</sup> column is  $\sum_{j=0}^{i} a_j \cdot b_{i-j}$  when i < k and  $\sum_{j=i-k}^{k} a_j \cdot b_{i-j}$  when  $i \ge k$ . These sums are exactly the convolution of the a and b samples. It is well known that FFTs

can be used to compute convolutions efficiently, as follows:

$$\operatorname{conv}(\hat{a}, \hat{b}) = \operatorname{FFT}^{-1}(\operatorname{FFT}(\hat{a}) * \operatorname{FFT}(\hat{b}))$$

where  $\hat{a}$  and  $\hat{b}$  represent the vector of samples, asterisk represents component-wise multiplication.

The challenge for FFT multiplication is that the FFT computations must be performed in a ring, with a  $k^{\text{th}}$  primitive root of unity. The choice of ring is very important. One possibility is to use complex numbers with floating point representations. This approach is used in some FFT multiplication algorithms, but the error analysis of the round-off errors in the floating point computations is very complicated. Another option, which we use in our research, is to use finite rings or fields, represented as integers or multiple precision integers. The computations will be exact. However, for a given finite ring/field, there is a limit to the maximum length A and B that can be multiplied without the column sum overflowing the maximum ring value. Thus, FFT multiplication is not a general multiplication algorithm that can multiply any size numbers, like the previous algorithms. However, given this limitation, it is very efficient with a running time of  $O(n \log n)$ .

**2.2.2.5 Schönhage-Strassen:** In 1971 Schönhage and Strassen [94] published a fast algorithm for multiplying arbitrary length numbers, based on FFT multiplication. Here we present a slightly simplified version of the Schönhage-Strassen algorithm. Given two n-bit numbers, A and B, split A and B into k pieces where k is chosen according to a heuristic that ensures  $k = \Theta(\sqrt{n})$ . Next run FFT multiplication on the pieces, using the finite ring  $\mathbf{R}$  consisting of the integers modulo  $2^{2k} + 1$ . The number 2 is a  $4k^{th}$  primitive root of unity in  $\mathbf{R}$ . Thus a 2k-point FFT can be run in  $\mathbf{R}$  using  $\omega = 2^2$ .

The FFTs and FFT<sup>-1</sup> each run in  $O(k \log k)$  operations in  $\mathbf{R}$  and each operation (addition, subtraction, and multiplication by  $\omega^i$ ) in  $\mathbf{R}$  runs in  $\Theta(k)$  bit operations. Thus the total time to run the FFTs and FFT<sup>-1</sup> is  $\Theta(k \cdot k \log k)$  which is  $\Theta(n \log n)$ . However, the convolution algorithm still requires performing k component sub-products of

2k-bits times 2k-bits each. If k is small enough, these are done using a base case algorithm (such as grade school). If not, they are done with recursive calls to the Schönhage-Strassen algorithm. Thus the total running time of the algorithm can be expressed as  $T(n) = k \cdot T(2k) + \Theta(n \log n)$ , where  $k = \Theta(\sqrt{n})$ . By the substitution method, we find that  $T(n) = O(n \log n \log \log n)$  bit operations. Further, the Schönhage-Strassen algorithm takes advantage of the cyclic nature of FFTs, which allows the sub-products to be computed in 2k-bits rather than 4k-bits. This explanation of the algorithm and its time complexity is somewhat terse; for a full description and analysis, please refer to [94], [73], or [16].

For practical implementations, there are some helpful tricks to improve the performance described by Gaudry, Kruppa and Zimmerman [50].

**2.2.2.6 Faster Multiplication:** In 2007 Martin Fürer published [49] an algorithm with a running time of  $O(n \log n \ 2^{O(\log^* n)})$ , which is asymptotically faster than Schönhage-Strassen. In 2016 Harvey, van der Hoeven, and Lecerf published a related algorithm [56], but with a slightly better complexity of  $O(n \log n \ K^{\log^* n})$ , where K=8. If certain conjectures about the distribution of Mersenne primes hold, then their algorithm can be shown to have complexity  $O(n \log n \ K^{\log^* n})$ , where K=4.

However, these algorithms are mostly of theoretical interest because the constant hidden in the O-notation is very large. So in practice, Schönhage-Strassen is faster except for "astronomically" large values of A and B.

#### 2.2.3 Fast Squaring

Computing the square of an n-word MP value A is often faster than computing the product of two n-word MP values  $A \cdot B$ . Here we briefly present some of the approaches. For small n, we will want to use the grade school algorithm, but we can take advantage of symmetry. Considering Figure 2.1, if a column has a term  $a_i b_j$ , then the column will also have a term  $a_j b_i$  when  $i \neq j$ . Since we're squaring, these two terms will be equal, which

leads to a fast algorithm, namely, add the terms above the slew diagonal, double the value then add in the diagonal terms.

For larger n, in the Karatsuba range, we note that  $A_L + A_H = B_L + B_H$  so this sum need only be computed once, and the sub-products are all squares, which can be computed by recursively calling the square routine and once the values are small enough, will take advantage of fast grade school squaring.

For Toom-Cook, S(x) and T(x) will be the same, which eliminates a lot of calculations. Also, like Karatsuba, all the sub-problems will be squares, and finally, Chung and Hasan [21] prove that unlike Toom-Cook multiplication, Toom-Cook squaring can be performed using only division by powers of two, thus eliminating the need for short division, which represents a significant percentage of the running time for Toom-Cook multiplication.

For large n, using the FFT based algorithms, the convolution becomes FFT  $^{\text{-1}}(\text{FFT}(\hat{a})^2)$  which saves an FFT.

For the rest of this dissertation, we will refer to these algorithms as "fast-squaring".

#### 2.2.4 Division

As with multiplication, there are a many algorithms for doing division. The algorithms generally fall into two categories: slow quadratic algorithms which produce a fixed number of bits of quotient per iteration, and fast sub-quadratic algorithms. Karp and Markstein's literature reivew in [21] covers many approaches to division, including some obscure ones, such as Chebyshev polynomial approximations, CORDIC methods, Sweeney, Robertson, and Tocher (SRT) division [92, 104], and Goldschmidt's sub-quadratic algorithm [53].

Here we discuss in detail some of the algorithms presented by Brent and Zimmermann in [16]. For each of these algorithms we wish to divide an n-word number, A, by an m-word divisor, B, with n > m. We assume that B is normalized, meaning that the most significant word of B is at least  $\beta/2$ . If this is not the case, we can construct A' and B' by shifting A and B by k bits to the left. k is chosen such that B' is normalized. Then the

quotient A/B is A'/B' and the remainder of A/B is the remainder of A'/B' shifted k bits to the right.

Like multiplication, the following three division algorithms form a ladder, with decreasing asymptotic complexity, but with increasing constants hidden by the Big-O notation. A good multiple precision library will typically implement all three algorithms and have a tuning routine to determine the best crossover points.

**2.2.4.1 Grade School:** For grade school division, we iterate over j from n-m down to 0. At each iteration, we compute an estimate for the next quotient word as  $q_j^* = \min\left(\left\lfloor (a_{m+j}\beta + a_{m+j-1})/b_{n-1}\right\rfloor, \ \beta-1\right)$ . This estimate is guaranteed to be greater than or equal to  $q_j$ , the next quotient word. The next step is to correct the estimate: while  $A-q_j^*\cdot B\cdot \beta^j<0$ , decrement  $q_j^*$ . After this loop,  $q_j^*$  is correct and we set  $q_j=q_j^*$ , and update  $A=A-q_j^*\cdot B\cdot \beta^j$ .

Brent and Zimmermann [16] prove the correction step happens at most twice. Knuth [73] notes that if  $q_i^*$  is chosen as

$$q_j^* = \lfloor (a_{m+j}\beta^2 + a_{m+j-1}\beta + a_{m+j-2})/(b_{n-1}\beta + b_{n-2}) \rfloor$$

then only one correction step is needed and it's extremely rare.

The running time is O(nm), and when  $m \approx n/2$ , the running time is  $O(n^2)$ , so the algorithm is quadratic.

**2.2.4.2 Burnikel-Ziegler:** The next algorithm is a recursive divide and conquer approach to division, due to Burnikel and Ziegler [17]. The basic idea is that instead of computing a single word estimate  $q^*$ , we should go to longer, multiword estimates. Then when we do the correction step,  $A - q^* \cdot B \cdot \beta^j$ , we can take advantage of asymtotically fast multiplication to compute  $q^* \cdot B$ . Without loss of generality, let's assume that A is exactly twice as long as B. We can split A into four pieces and B into two pieces as follows:

$$A = A_3 \beta^{3(n/4)} + A_2 \beta^{2(n/4)} + A_1 \beta^{n/4} + A_0 \quad \text{and} \quad B = B_1 \beta^{n/4} + B_0$$

Further, we can represent the quotient, Q = A/B as  $Q = Q_1\beta^{n/4} + Q_0$ . We can estimate  $Q_1$  by calling the division routine recursively,  $Q_1^* = \text{divide}(A_3\beta^{n/4} + A_2, B_1)$ . The estimate will not be exact, but it will be close and the exact value is easily obtained with a few correction steps using the full values of A and B.

Next, construct  $A' = A - Q_1 \cdot B \cdot \beta^{n/4}$ . A' can be represented as:

$$A' = A_2' \beta^{2(n/4)} + A_1' \beta^{n/4} + A_0'$$

$Q_0$  can then be estimated by calling the division routine recursively again,  $Q_0^* = \operatorname{divide}(A_2'\beta^{n/4} + A_1', B_1)$ . The estimate will be close to the exact value, which can be determined with a few more correction steps. The final Q is just  $Q_1\beta^{n/4} + Q_0$ .

This algorithm outperforms grade school in two ways. First, it takes advantage of asymptotically fast multiplication. Second, the total number of words affected by corrections is greatly reduced.

The running time analysis of this algorithm is complicated and depends on the multiplication algorithm being used. Brent and Zimmermann show that the running time to divide an n-word number by a n/2-word number is roughly 2 to 3 times the running time to multiply two n/2-word numbers.

Finally, as with Knuth's observation about the grade school algorithm, the correction steps can be greatly reduced by using one more word for both numerator and denominator in the recursive calls.

**2.2.4.3 Newton-Raphson:** For very large numbers, the fastest approach to division is to use a Newton iteration to find the reciprocal of B. The approach is similar to Burnikel-Ziegler in that it splits A into 4 pieces  $(A_0, A_1, A_2, A_3)$ , and B and Q into two pieces  $(B_0, B_1)$  and  $(B_0, A_1)$  and computes  $(B_0, B_1)$  and  $(B_0, A_1)$  and  $(B_0, A_1)$

The algorithm first uses a Newton iteration to compute an integer R (the reciprocal) such that  $R = \left\lfloor \frac{\beta^{2n/4}}{B_1} \right\rfloor$ . The algorithm follows the steps of Burnikel-Ziegler, except instead

of the recursive calls, the estimates of  $Q_1^*$  and  $Q_0^*$  come from computing the high n/4 words of the product  $Q_1^* = high(A_3 \cdot R)$  and  $Q_0^* = high(A_2' \cdot R)$ .

Here we present some background on Newton's iteration. Suppose we are given a real number  $0.5 \le x < 1$ , and an initial estimate  $y_0$  for 1/x, where  $|y_0 - 1/x| < \epsilon$  and  $1 < y_0 \le 2$ , then the following sequence:  $y_{k+1} = y_k + y_k(1 - xy_k)$  which will rapidly converge to 1/x. It can be proven that  $|y_k - 1/x| < 4^k \epsilon^{2^k}$  (see for example Brent and Zimmermann's Section 3.4.1). In practice, this means that if an estimate  $y_k$  is accurate to c bits of precision, then  $y_{k+1}$  will be accurate to 2c - 2 bits of precision.

Earlier we had described  $R = \left\lfloor \frac{\beta^{2n/4}}{B_1} \right\rfloor$  as the "reciprocal" of  $B_1$ , which seems strange because they are both integers. Here's the story. There is a duality here:  $B_1$  and R can be viewed as integers, but they can also be viewed as fixed point numbers with n/4 words after the decimal point. In the fixed point context, R and  $B_1$  are reciprocals. Further, because B is normalized,  $B_1$  as a fixed point number is between 1/2 and 1 and the Newton iteration applies. Thus we can write a fixed point version Newton's iteration as follows. We start out by setting  $R_0 = \beta^2/B_{m-1} \cdot \beta^{n/4-1}$  and iterate  $\log m$  times:

$$R_{j+1} = R_j + R_j \cdot (\beta^{n/4} - B_1 \cdot R_j / \beta^{n/4}) / \beta^{n/4}$$

This is exactly the Newton iteration translated into fixed point arithmetic.  $R_0$  is accurate to 1 word, and after each iteration, the number of words of accuracy approximately doubles. We note that we've done one more iteration than is strictly necessary, which is to handle the  $4^k$  term that crops up in the Newton iteration. Finally we note that the fixed point representation is just an approximation to the real numbers used in Newton's iteration. Thus, in addition to the error analysis of Newton's method, there are round off errors to contend with, and up to two correction steps may be required to get the correct final value for R.

This implementation of Newton's iteration is inefficient because the early iterations are computing with much more precision than required. Brent and Zimmermann give a more complicated, but more efficient implementation in Section 3.4.1 of [16].

Computing the Newton reciprocal R to n/4-words and doing the division in two steps  $(Q_1 \text{ followed by } Q_0)$  is significantly faster than computing R to 2n/4-words and computing all of Q in a single step and is due to Karp and Markstein [70]. It is sometimes called the "Karp and Markstein trick".

#### 2.2.5 Specialized Division Algorithms

In some cases, there are special properties about the division that we can take advantage of. We use the same notation, A is the dividend and B is the divisor. However, in next two algorithms we do not assume B has been normalized.

**2.2.5.1 Exact Division:** Given an n-bit dividend, A, and an m-bit divisor B that exactly divides A, find Q such that  $A = Q \cdot B$ .

The division algorithms presented thus far all work by finding a  $Q^*$  that when multiplied by B and shifted, cancels off the most significant bits (left side) of the dividend, A. Then these algorithms construct a smaller dividend, A', such that A'/B equals the remaining bits of the quotient still to be computed. Exact division, due to Jebelean [65] works in the opposite direction. It determines the least significant bits of the quotient and cancels them off the right side of the dividend. For now, let's assume that the divisor, B is odd. We can determine  $Q_k$ , the k least significant bits of Q, as follows:

$$A = Q \cdot B \implies A \equiv Q \cdot B \pmod{2^k} \implies Q \equiv A \cdot B^{-1} \pmod{2^k}$$

and therefore

$$Q_k = Q \mod 2^k = A \cdot B^{-1} \pmod{2^k} = (A \mod 2^k \cdot B^{-1} \mod 2^k) \mod 2^k$$

where  $A \mod 2^k$  is just the least significant k bits of A and the inverse,  $B^{-1} \mod 2^k$  will exist because B was assumed to be odd.

With this computation we can compute the least significant k bits of Q. Next we want to find a smaller A' such that A'/B are the remaining high order bits of Q still to be

discovered. Thus we want  $A'/B = (Q - Q_k)/2^k$ . Multiplying both sides by B gives:

$$A' = \frac{Q \cdot B - Q_k \cdot B}{2^k} = \frac{A - Q_k \cdot B}{2^k}$$

We keep iterating this process, finding the next k bits of Q, until A' is zero, at which time all of Q has been determined.

This algorithm requires an efficient technique for computing  $B^{-1} \mod 2^k$ . Jebelean gives an algorithm: set  $I_1 = 1$  and iterate:

$$I_{j+1} = I_j(2 - B \cdot I_j) \mod 2^{2^{j-1}}$$

$B^{-1} \mod 2^k$  is  $I_j \mod 2^k$  when  $2^{2^{j-1}} \ge k$ . This algorithm is very similar to Newton's iteration in that the accuracy doubles on each iteration, which can shown as follows. Suppose  $I_j$  is a k bit modular inverse of B. Then we have  $B \cdot I_j = C \cdot 2^k + 1$  for some integer C, and we have:

$$B \cdot I_{j+1} = B \cdot I_j \cdot (2 - B \cdot I_j) = (C \cdot 2^k + 1)(1 - C \cdot 2^k) = -C^2 \cdot 2^{2k} + 1$$

Thus  $B \cdot I_{j+1} \mod 2^{2k} = 1$ , and therefore  $I_{j+1}$  is a 2k bit modular inverse of B. The origin of this approach can be traced back to Kurt Hensel's work on p-adic numbers, circa 1897.

We have assumed that B is odd. Suppose B is divisible by  $2^p$  but not  $2^{p+1}$  for some p>0. Then because the division is exact,  $2^p$  also divides A and we can compute  $Q=\mathrm{exact\_divide}(A/2^p,\ B/2^p)$  where  $B/2^p$  will be odd. Dividing by  $2^p$  to ensure that  $B/2^p$  is odd is the "least significant bit first" equivalent of normalizing the divisor.

Exact division is very efficient for a number of reasons. First, it can take advantage of asymptotically fast multiplication. Second, the modular inverse step is faster than Newton reciprocal computation. Third, there are no correction steps as there are with the prior division algorithms.

**2.2.5.2 Short Division / Division by Single Word Constants:** In short division the divisor B is only a single word value, i.e.,  $B < \beta$ . If the division is exact, the fastest approach is to use exact division, with k equal to the machine word size. Exact short division is required to implement Toom-Cook.

If the division is not exact, then there are two approaches. If the machine has a fast division instruction, then the grade school division algorithm will be fast and efficient, and no correction steps are required. However, some architectures, such as GPUs, do not have fast division instructions. In this case, it is often faster to compute  $r = A \mod b_0$  followed by  $Q = \operatorname{exact\_divide}(A - r, b_0)$ . A fast single word remainder algorithm is given at the end of Section 2.2.7.

#### 2.2.6 Remainder / Modulo Reduction

The division algorithms of Section 2.2.4 compute both the quotient and the remainder. However, there are a few applications where just the remainder is required. In most cases, there is a fixed modulus, M, and repeated computations modulo M are required. This is the case for modulo exponentiation and computations in a finite field  $\mathbb{F}_P$ , where P is a prime or a prime raised to the k<sup>th</sup> power.

**2.2.6.1 Barrett Reduction:** The Barrett reduction is due to Paul Barrett [5]. Given a 2n-word value X, and an n-word value M, where  $\beta/2 \leq M_{n-1} < \beta$ , find  $X \mod M$ . Since M will be used repeatedly, we precompute I such that  $I \cdot M \leq \beta^{2n} < (I+1) \cdot M$ . The precomputation can be done using a Newton iteration as described in Section 2.2.4.

The algorithm computes  $Q = \lfloor \lfloor X/\beta^n \rfloor \cdot I/\beta^n \rfloor$ , then computes  $R = X - Q \cdot M$ . This algorithm can be viewed in terms of fixed point representation, where I has n words of precision after the decimal point, and is the reciprocal of M. With some careful analysis, it can be shown that  $0 \leq R < 4M$ . Thus, at most three correction steps are required to compute the final remainder.

The Barrett reduction is quite fast in practice because, after the precomputation step, the algorithm doesn't require any division instructions, which are quite slow on many architectures. Further, the correction steps are outside of the multiplication loops and are done at most thrice per reduction.

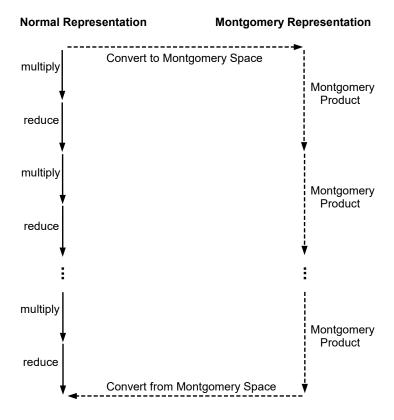

Figure 2.2. Computation using Montgomery Representation

**2.2.6.2 Montgomery Reduction:** The main idea of a Montgomery reduction is to transform the input to a different representation (Montgomery Representation), perform the computation in the new representation and at the end transform the output back to the original FRNS representation. This process is shown in Figure 2.2, where the dashed lines represent computation in Montgomery representation.

The mapping is straightforward. In the FRNS domain, we have an n-word MP value, A. In the Montgomery domain, it's the n-word MP value  $A \cdot \beta^n \mod M$  where M is the common modulus for the reductions. We note that M must be odd and less than  $\beta^n$ . We also use the convention that  $\overline{A}$  means the value A mapped to the Montgomery domain.

We define two functions,  $\mathrm{ToMont}_{\mathrm{M}}(A)$  maps values from FRNS representation to Montgomery representation and  $\mathrm{FromMont}_{\mathrm{M}}(\overline{A})$  maps them back. Formally:

$$\overline{A} = \operatorname{ToMont}_{\mathbf{M}}(A) = A \cdot \beta^n \operatorname{mod} M$$

and

$$A = \operatorname{FromMont}_{\mathcal{M}}(\overline{A}) = \overline{A} \cdot \beta^{-n} \operatorname{mod} M$$

Next, we wish to define the product in the Montgomery domain  $\operatorname{MontProd}_{\operatorname{M}}(\overline{A}, \overline{B})$  such that it preserves modular multiplication, i.e.,

$$\operatorname{MontProd}_{\operatorname{M}}(\overline{A},\ \overline{B}) = \operatorname{ToMont}_{\operatorname{M}}(A \cdot B \operatorname{mod} M)$$

because  $A = \overline{A} \cdot \beta^{-n} \mod M$  and  $B = \overline{B} \cdot \beta^{-n} \mod M$ , we have:

$$\begin{aligned} \operatorname{MontProd}_{\operatorname{M}}(\overline{A},\ \overline{B}) &= \operatorname{ToMont}_{\operatorname{M}}(A \cdot B \operatorname{mod} M) \\ &= \operatorname{ToMont}_{\operatorname{M}}(\overline{A} \cdot \beta^{-n} \cdot \overline{B} \cdot \beta^{-n} \operatorname{mod} M) \\ &= \overline{A} \cdot \beta^{-n} \cdot \overline{B} \cdot \beta^{-n} \beta^{n} \operatorname{mod} M \\ &= \overline{A} \cdot \overline{B} \cdot \beta^{-n} \operatorname{mod} M \end{aligned}$$

In [83] Montgomery gives two efficient algorithms for computing  $\operatorname{MontProd}_{\mathrm{M}}(\overline{A}, \overline{B})$ . The clever idea behind the Montgomery algorithm is to note that if we can find Q such that  $\overline{A} \cdot \overline{B} + M \cdot Q$  is exactly divisible by  $\beta^n$  where  $0 \leq Q < \beta^n$ , then we can define  $\overline{P} = \frac{\overline{A} \cdot \overline{B} + M \cdot Q}{\beta^n}$  and we have:

$$\operatorname{MontProd}_{\mathcal{M}}(\overline{A}, \overline{B}) \equiv \overline{A} \cdot \overline{B} \cdot \beta^{-n} \pmod{M}$$

$$\equiv (\overline{A} \cdot \overline{B} + M \cdot Q) \cdot \beta^{-n}$$

$$\equiv \overline{P} \cdot \beta^{n} \cdot \beta^{-n}$$

$$\equiv \overline{P}$$

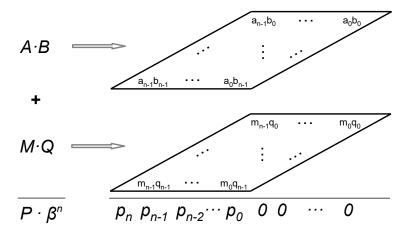

and if we assume  $\overline{A} < M$  and  $\overline{B} < M$ , then  $\overline{P} = \frac{\overline{A} \cdot \overline{B} + M \cdot Q}{\beta^n} < \frac{M^2 + \beta^n \cdot M}{\beta^n} < 2M$ . At a high level, the Montgomery algorithm runs the steps given in Figure 2.3.

- 1. Compute  $P = \overline{A} \cdot \overline{B}$

- 2. Find Q such that  $P + Q \cdot M$  is evenly divisible by  $\beta^n$

- 3. Compute  $\overline{P} = (P + M \cdot Q)/\beta^n$

- 4. If  $\overline{P} > M$  then  $\overline{P} = \overline{P} M$  (correction step)

- 5. Return  $\overline{P}$

Figure 2.3. Montgomery Product Algorithm

Montgomery gives two versions of the algorithm to find Q. The first, which we'll call the "three-products" approach, precomputes  $I = \beta^n - \left(M^{-1} \bmod \beta^n\right)$ . Then  $Q = \overline{A} \cdot \overline{B} \cdot I \bmod \beta^n$  and  $\overline{P} = \frac{\overline{A} \cdot \overline{B} + M \cdot Q}{\beta^n}$ . This algorithm does three n-word by n-word multiplies and can be implemented with asymptotically fast multiplications.

The second algorithm uses a quadratic "word-by-word" approach. It first precomputes  $i = \beta - (M^{-1} \mod \beta)$ , then sets  $\overline{P}_0 = \overline{A} \cdot \overline{B}$  and loops for j = 1 to n:

$$q_j = \overline{P}_{j-1} \cdot i \operatorname{mod} \beta$$

$$\overline{P}_j = \frac{\overline{P}_{j-1} + q_j \cdot M}{\beta}$$

the final result is  $\overline{P} = \overline{P}_n$ . This algorithm is implemented using an n-word by n-word multiplication to compute  $\overline{P}_0$  and then  $n^2 + n$  word multiplications to reduce it. For very large n, the three-products approach is faster. For small to moderate size n, the word-byword approach is faster.

There are a few implementation tricks. Conversion to and from Montgomery representation can be implemented by precomputing  $C = \beta^{2n} \mod M$ , then  $\mathrm{ToMont}_{\mathrm{M}}(A) = \mathrm{MontProd}_{\mathrm{M}}(A, C)$  and  $\mathrm{FromMont}_{\mathrm{M}}(\overline{A}) = \mathrm{MontProd}_{\mathrm{M}}(\overline{A}, 1)$ . The modular inverse can be computed using the *p-adic* algorithm from Section 2.2.5.

The correction step is slow and can lead to non-uniform running times (which is a serious issue in cryptosystems). Several papers explore relaxing the normalization requirement that  $\overline{X}$  be less than M. In [110] Yanik, Savaş and, Koç show that if  $\overline{X}$  is allowed to range

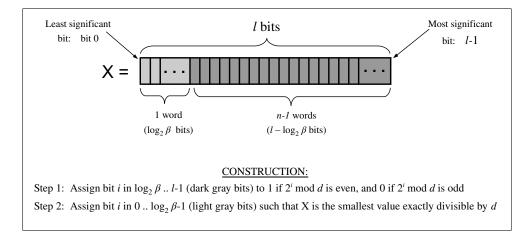

Figure 2.4. Product terms in the word-by-word approach to a Montgomery reduction

from 0 to  $\beta^n-1$ , then the correction step can be simplified to if  $\overline{P} \geq \beta^n$  then  $\overline{P} = \overline{P} - M$ . Allowing  $\overline{X}$  to range from 0 to  $\beta^n-1$  is sometimes referred to as *Almost Montgomery* representation. Orup [87] and later Walter [107] show that if  $\overline{X}$  is allowed to range from 0 to 2M-1 then the correction step can be removed entirely. Walter also shows that if  $\overline{X} < 2M$ , then  $\mathrm{FromMont}_{\mathrm{M}}(\overline{X}) < M$  provided that  $M < \beta^n-1$ .

In [74] Koc, Acar, and Kaliski look at five different strategies for ordering the summation of the terms in the Montgomery word-by-word approach. The terms are shown in Figure 2.4. The authors call these five strategies: Separated Operand Scanning (SOS), Coarsely Integrated Operand Scanning (CIOS), Finely Integrated Operand Scanning (FIOS), Finely Integrated Product Scanning (FIPS) and Coarsely Integrated Hybrid Scanning (CIHS). In the *separated* approach, the product  $A \cdot B$  is computed in full and then reduced by adding  $M \cdot Q$ . Shifting off the n zeros is always the last step. In the *coarsely integrated* approach, we alternate computing a row or column of the product,  $A \cdot B$ , followed by a row or column of the reduction,  $M \cdot Q$ . In the *finely integrated* approach, we alternate, adding a single term

<sup>&</sup>lt;sup>1</sup>CIHS is rarely used and we omit it for brevity

SOS:

$$P = \underbrace{b_0 A + b_1 A \beta + \cdots}_{A \cdot B} + \underbrace{q_0 M + q_1 M \beta + \cdots}_{M \cdot Q}$$

CIOS:  $P = \underbrace{b_0 A}_{\text{row}} + \underbrace{q_0 M}_{\text{row}} + \underbrace{b_1 A \beta}_{\text{row}} + \underbrace{q_1 M \beta}_{\text{row}} + \cdots$

FIOS:  $P = \underbrace{b_0 a_0 + q_0 m_0}_{\text{row}} + \underbrace{b_0 a_1 \beta}_{\text{row}} + q_0 m_1 \beta + \cdots}_{\text{finely integrated row}} + \underbrace{b_1 a_0 \beta}_{\text{finely integrated row}} + \underbrace{b_1 a_0 \beta}_{\text{finely integrated row}} + \underbrace{c_0 b_0 + q_0 m_0}_{\text{finely integrated col}} + \underbrace{a_0 b_1 \beta}_{\text{finely integrated col}} + \underbrace{a_1 b_0 \beta}_{\text{finely integrated col}} + \cdots$

Figure 2.5. Summary of SOS, CIOS, FIOS, FIPS

of the product and single term of the reduction. In *operand scanning* the outermost loop moves through the words of one of the arguments (usually *B*) and in *product scanning* the outer loop moves through the words of the product. Geometrically, *operand scanning* goes across the rows of Figure 2.4 from right to left in top to bottom order, while *product scanning* goes down the columns from right to left. Figure 2.5 summarizes the computations for SOS, CIOS, FIOS, and FIPS. The importance of [74] is not so much for its particular experimental results, but that it raises awareness of the different ways to organize the Montgomery computation and these will turn out to be very important in GPU implementations. The best strategy is highly dependent on the features of the underlying hardware, and performance can vary significantly between strategies.

For moderately large n, Montgomery reductions can be accelerated using Svoboda preconditioning, also known as Montgomery folding. This is well described by Brent and Zimmermann [16] in their Section 2.4.2. For very large n, Montgomery reductions can be significantly accelerated using clever FFT multplication tricks as discovered by McLaughlin [88].

The Montgomery reduction is very popular because it is fairly easy to implement and is quite fast. It doesn't require any division instructions after the precompute phase and there is at most one fast correction step per reduction.

### 2.2.7 Special Moduli