# University of Massachusetts Amherst ScholarWorks@UMass Amherst

**Open Access Dissertations**

5-2013

# Transiently Powered Computers

Benjamin Ransford University of Massachusetts Amherst, ben@ransford.org

Follow this and additional works at: https://scholarworks.umass.edu/open\_access\_dissertations Part of the <u>Computer Sciences Commons</u>

#### **Recommended** Citation

Ransford, Benjamin, "Transiently Powered Computers" (2013). *Open Access Dissertations*. 761. https://scholarworks.umass.edu/open\_access\_dissertations/761

This Open Access Dissertation is brought to you for free and open access by ScholarWorks@UMass Amherst. It has been accepted for inclusion in Open Access Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# TRANSIENTLY POWERED COMPUTERS

A Dissertation Presented

by

BENJAMIN RANSFORD

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

May 2013

School of Computer Science

© Copyright by Benjamin Ransford 2013 All Rights Reserved

# TRANSIENTLY POWERED COMPUTERS

A Dissertation Presented

by

BENJAMIN RANSFORD

Approved as to style and content by:

Kevin Fu, Chair

Emery D. Berger, Member

Wayne P. Burleson, Member

Deepak Ganesan, Member

Lori A. Clarke, Chair School of Computer Science For Ilse and Linus and Megan.

#### ACKNOWLEDGMENTS

First and most germane to this document, I owe my most profound gratitude to my advisor, Kevin Fu, for his advice, ideas, funding, and unfailing optimism since before I arrived in Amherst. Quod erat demonstrandum.

I thank my coauthors for their efforts and for only rarely chiding me for committing yet another change to the Makefile.

I thank my peers in the SPQR group at UMass: Shane Clark, Mastooreh Salajegheh, Andrés Molina-Markham, Amir Rahmati, Shane Guineau, and Hong Zhang, plus all of our friends in ECE under Wayne Burleson's guidance. Thanks to Tom Benjamin for his bright-eyed mentorship during my first months as a graduate student. Lately, Denis Foo Kune ushered in an unstanchable flow of doughnuts.

I thank the recent UMass graduates who have helped me navigate these last few steps: Jacob, Aruna, Negin, Andrés, and a few others. Plus of course the front-office staff, especially Leeanne, for keeping everyone—including me—on track.

Brian Levine has been a spiritual advisor; without his advice on teaching, my students in CS660 would have suffered more deeply. To the students in that class: thanks for your patience, and remember to seed your PRNGs.

A fusillade of thanks to Dr. Bryan Renne and Dr. Chris Erway for helping me keep my dream of a terminal degree alive. Dr. Michael J. Poiesz, M.D. provided something resembling moral support during my Syracuse years.

Thanks to Dan Halperin and Shyam Gollakota, the Federer and Nadal of SIG-COMM, for teaching me everything I know about wireless networking. Thanks to the National Science Foundation for the Graduate Research Fellowship that kept me off the Hobbesian streets of Northampton; thanks also to the Isenbergs for their support, and to Mike Malone for being such a mensch.

Thanks to the insightful Partha Ranganathan of HP Labs for his thoughts on potential broader impacts during the ASPLOS 2012 Doctoral Workshop.

Thanks to Alanson Sample for permission to use figures from one of his fine papers [138].

For necessary distractions during the last few years, I thank Justin and the rest of the Desperados for hitting all those tennis balls back to me, Thom and Seth for being my beer-brewing buddies, and everyone whose kids mine have played with.

Now the good stuff. I thank my inimitable parents, Steve Ransford and Pat Rector, for teaching me about decency by example.

Finally, I owe an unremunerable debt to the three most important people in the world: my immediate family, Megan, Linus, and Ilse. I shudder to imagine the kind of miserable, stunted, depraved bachelor I would be without you.

Thanks to the many people who contributed to this thesis's constituent publications via shepherding, feedback on drafts, and technical labor, and thanks to the entities that funded the research. Portions of this thesis appeared in the following publications:

- "Getting Things Done on Computational RFIDs with Energy-Aware Checkpointing and Voltage-Aware Scheduling" by Benjamin Ransford, Shane S. Clark, Mastooreh Salajegheh and Kevin Fu. USENIX Workshop on Power Aware Computing and Systems (HotPower), San Diego, CA, December 2008.

- "Mementos: System Support for Long-Running Computation on RFID-Scale Devices" by Benjamin Ransford, Jacob Sorber and Kevin Fu. In Proceedings of the 16th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS-XVI), Newport Beach, CA,

March 2011. Another version appeared in October 2010 as Tech Report UM-CS-2010-060 of the University of Massachusetts Amherst Department of Computer Science.

- "CCCP: Secure Remote Storage for Computational RFIDs" by Mastooreh Salajegheh, Shane S. Clark, Benjamin Ransford, Kevin Fu and Ari Juels. In Proceedings of the 18th USENIX Security Symposium, Montreal, Ontario, Canada, August 2009.

- "Pacemakers and implantable cardiac defibrillators: Software radio attacks and zero-power defenses" by Daniel Halperin, Thomas S. Heydt-Benjamin, Benjamin Ransford, Shane S. Clark, Benessa Defend, Will Morgan, Kevin Fu, Tadayoshi Kohno and William H. Maisel. In Proceedings of the 29th IEEE Symposium on Security and Privacy (Oakland), Berkeley, CA, May 2008.

- "Design Challenges for Secure Implantable Medical Devices" by Wayne P. Burleson, Shane S. Clark, Benjamin Ransford, and Kevin Fu. In Proceedings of the 49th Design Automation Conference (DAC), San Francisco, CA, June 2012.

#### ABSTRACT

### TRANSIENTLY POWERED COMPUTERS

May 2013

BENJAMIN RANSFORD B.S., CORNELL UNIVERSITY M.S., UNIVERSITY OF MASSACHUSETTS AMHERST Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Kevin Fu

Demand for compact, easily deployable, energy-efficient computers has driven the development of general-purpose *transiently powered computers* (TPCs) that lack both batteries and wired power, operating exclusively on energy harvested from their surroundings.

TPCs' dependence solely on transient, harvested power offers several important design-time benefits. For example, omitting batteries saves board space and weight while obviating the need to make devices physically accessible for maintenance. However, transient power may provide an unpredictable supply of energy that makes operation difficult. A predictable energy supply is a key abstraction underlying most electronic designs. TPCs discard this abstraction in favor of *opportunistic* computation that takes advantage of available resources. A crucial question is how should a software-controlled computing device operate if it depends completely on external en*tities for power and other resources?* The question poses challenges for computation, communication, storage, and other aspects of TPC design.

The main idea of this work is that **software techniques can make energy harvesting a practicable form of power supply for electronic devices.** Its overarching goal is to facilitate the design and operation of *usable* TPCs.

This thesis poses a set of challenges that are fundamental to TPCs, then pairs these challenges with approaches that use software techniques to address them. To address the challenge of computing steadily on harvested power, it describes Mementos, an energy-aware state-checkpointing system for TPCs. To address the dependence of opportunistic RF-harvesting TPCs on potentially untrustworthy RFID readers, it describes CCCP, a protocol and system for safely outsourcing data storage to RFID readers that may attempt to tamper with data. Additionally, it describes a simulator that facilitates experimentation with the TPC model, and a prototype computational RFID that implements the TPC model.

To show that TPCs can improve existing electronic devices, this thesis describes applications of TPCs to implantable medical devices (IMDs), a challenging design space in which some battery-constrained devices completely lack protection against radio-based attacks. TPCs can provide security and privacy benefits to IMDs by, for instance, cryptographically authenticating other devices that want to communicate with the IMD before allowing the IMD to use any of its battery power. This thesis describes a simplified IMD that lacks its own radio, saving precious battery energy and therefore size. The simplified IMD instead depends on an RFID-scale TPC for *all* of its communication functions.

TPCs are a natural area of exploration for future electronic design, given the parallel trends of energy harvesting and miniaturization. This work aims to establish and evaluate basic principles by which TPCs can operate.

# TABLE OF CONTENTS

| ACKNOWLEDGMENTS v  |

|--------------------|

| ABSTRACT           |

| LIST OF TABLESxiv  |

| LIST OF FIGURESxvi |

### CHAPTER

| 1.                               | . INTRODUCTION 1                  |                            |                                                                                                        |  |

|----------------------------------|-----------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------|--|

|                                  | $1.1 \\ 1.2 \\ 1.3 \\ 1.4 \\ 1.5$ | Challe<br>Thesis<br>Contri | round and Motivation1nges2Statement and Summary3butions4Outline6                                       |  |

| 2.                               | SIM                               | ULAT                       | ING TRANSIENTLY POWERED COMPUTERS 8                                                                    |  |

|                                  | 2.1<br>2.2<br>2.3                 | Repro                      | Itational RFIDs9ducibility and Simulation11ing Energy Harvesting in MSPsim15                           |  |

|                                  |                                   | 2.3.1<br>2.3.2             | Energy-Harvesting Traces17Simulating Power Loss18                                                      |  |

| 2.4 Profiling Energy Consumption |                                   | ng Energy Consumption19    |                                                                                                        |  |

|                                  |                                   | $2.4.1 \\ 2.4.2 \\ 2.4.3$  | Instruction-Level Energy Measurements19Capacitor Leakage and Quiescent Current21Current Measurements22 |  |

|                                  | $2.5 \\ 2.6$                      |                            | d Work                                                                                                 |  |

| 3.                        | CO                             | MPUT                      | ING UNDER TRANSIENT POWER                                                                                       | 27           |  |

|---------------------------|--------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------|--------------|--|

|                           | 3.1<br>3.2                     |                           |                                                                                                                 |              |  |

|                           |                                | 3.2.1                     | Challenges                                                                                                      | . 32         |  |

|                           | 3.3                            | 3.3 Power Loss and CRFIDs |                                                                                                                 |              |  |

|                           |                                | 3.3.1                     | Experimental Results                                                                                            | . 35         |  |

|                           | 3.4                            | 4 Design of Mementos      |                                                                                                                 |              |  |

|                           |                                | 3.4.1<br>3.4.2<br>3.4.3   | Compile-Time InstrumentationRun-Time Energy EstimationRun-Time Checkpointing                                    | . 41         |  |

|                           | $3.5 \\ 3.6$                   | -                         | nentation                                                                                                       |              |  |

|                           |                                | 3.6.1                     | Mementos in Simulation                                                                                          | . 49         |  |

|                           |                                |                           | 3.6.1.1Test cases3.6.1.2Baselines and Metrics for Comparison3.6.1.3Energy Oracle3.6.1.4Performance and Overhead | . 51<br>. 52 |  |

|                           |                                | $3.6.2 \\ 3.6.3$          | Mementos on Hardware<br>Extension: Adaptive Checkpointing                                                       |              |  |

|                           |                                |                           | 3.6.3.1Minimizing Failed Checkpoints3.6.3.2Results                                                              |              |  |

|                           | 3.7 Discussion and Future Work |                           |                                                                                                                 | . 63         |  |

|                           |                                | 3.7.1<br>3.7.2<br>3.7.3   | Alternative approachesFuture HardwareFuture Work                                                                | . 65         |  |

|                           | 3.8<br>3.9                     |                           | d Workary                                                                                                       |              |  |

| 4.                        |                                |                           | NICATION AND STORAGE UNDER TRANSIENT                                                                            | 74           |  |

| 4.1 Backscattering CRFIDs |                                |                           |                                                                                                                 | . 77         |  |

|                    |                                                                               | 4.1.1                                                           | Challenges From Energy Scarcity                                                                                                                   | . 80         |

|--------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 4.2 Design of CCCP |                                                                               | of CCCP                                                         | . 82                                                                                                                                              |              |

|                    |                                                                               | $\begin{array}{c} 4.2.1 \\ 4.2.2 \\ 4.2.3 \\ 4.2.4 \end{array}$ | Design Goal: Computational Progress on CRFIDs<br>Checkpointing Strategies: Local vs. Remote<br>Threat Model<br>Secure Storage in CCCP             | . 83<br>. 85 |

|                    |                                                                               |                                                                 | <ul><li>4.2.4.1 Keystream Precomputation</li></ul>                                                                                                |              |

|                    |                                                                               |                                                                 | IntegrityIntegrity4.2.4.3Stream Cipher for Confidentiality4.2.4.4Hole Punching for Counters Stored in Flash4.2.4.5Extension for Long-Term Storage | . 89<br>. 89 |

|                    |                                                                               | 4.2.5                                                           | Power Seasons                                                                                                                                     | . 92         |

|                    | 4.3                                                                           | Impler                                                          | nentation                                                                                                                                         | . 92         |

|                    |                                                                               | 4.3.1                                                           | Communication Protocol                                                                                                                            | . 94         |

| 4.4 CCCP E         |                                                                               | CCCP                                                            | Evaluation                                                                                                                                        | . 97         |

|                    |                                                                               | $ \begin{array}{r} 4.4.1 \\ 4.4.2 \\ 4.4.3 \end{array} $        | Security Semantics<br>Experimental Setup & Methods<br>Performance                                                                                 | . 99         |

|                    |                                                                               |                                                                 | 4.4.3.1 System Overhead                                                                                                                           | 101          |

|                    | $   \begin{array}{r}     4.5 \\     4.6 \\     4.7 \\     4.8   \end{array} $ | Relate<br>Future                                                | ations<br>d Work<br>Work<br>ary                                                                                                                   | 104<br>106   |

| 5.                 |                                                                               |                                                                 | WER SECURITY FOR IMPLANTABLE MEDICAL                                                                                                              | 109          |

|                    | $5.1 \\ 5.2$                                                                  |                                                                 | cound                                                                                                                                             |              |

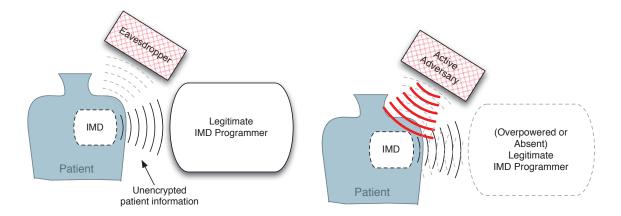

|                    |                                                                               | 5.2.1                                                           | Threat model                                                                                                                                      | 112          |

|                    | 5.3                                                                           | Zero-P                                                          | Power and Sensible Defenses for IMD Security and Privacy                                                                                          | 114          |

|                    |                                                                               | $5.3.1 \\ 5.3.2$                                                | Detection: Zero-Power Notification for Patients<br>Prevention: Zero-Power Authentication                                                          |              |

|    |                                           |           | ro-Power Sensible Key Exchange                         |           |

|----|-------------------------------------------|-----------|--------------------------------------------------------|-----------|

|    | $5.4 \\ 5.5$                              |           | Vork                                                   |           |

| 6. |                                           | -         | NG MEDICAL DEVICES WITH TRANSIENTLY<br>D COMMUNICATION | 25        |

|    | 6.1                                       | Implantab | ble Medical Devices and Power                          | 25        |

|    |                                           | 6.1.1 Co  | ntribution                                             | 27        |

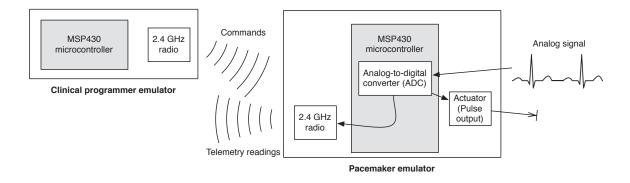

|    | 6.2                                       | Emulating | g a Pacemaker                                          | 27        |

|    |                                           |           | seline: Radio-Based Pacemaker Emulator                 | 29        |

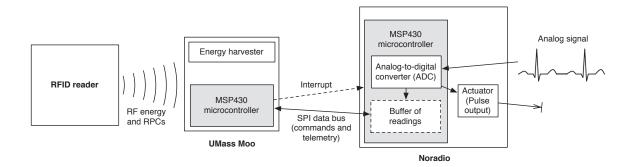

|    |                                           |           | (Noradio)                                              | 31        |

|    | $\begin{array}{c} 6.3 \\ 6.4 \end{array}$ | Related W | n                                                      | 35        |

|    | $6.5 \\ 6.6$                              |           | ork                                                    |           |

| 7. |                                           | Č.        | DNS 13                                                 |           |

| BI | BLI                                       | OGRAPH    | IY 14                                                  | <b>40</b> |

# LIST OF TABLES

| Table | Page                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1   | Comparison of simulator features                                                                                                                                                                                                                                                                                                                                                                          |

| 2.2   | Mapping of Intel WISP and UMass Moo hardware properties to<br>simulator mechanisms                                                                                                                                                                                                                                                                                                                        |

| 2.3   | Energy required per instruction varies on the TI MSP430F1232. Each figure is the average of 5 measurements (smallest and largest discarded) on a WISP (Rev. 1)                                                                                                                                                                                                                                            |

| 3.1   | Terms used in our discussion of Mementos40                                                                                                                                                                                                                                                                                                                                                                |

| 3.2   | Metrics for evaluation                                                                                                                                                                                                                                                                                                                                                                                    |

| 3.3   | Cycle counts (and percentage of cycles spent in Mementos code) for<br>three Mementos test cases under an <i>unlimited-energy</i> scenario,<br>i.e., voltage always above $V_{\text{thresh}}$ . This table illustrates the base<br>cost of Mementos's energy checks at run time, when its<br>instrumentation runs but never results in a state checkpoint to<br>nonvolatile memory                         |

| 3.4   | Oracle-mode lower bounds [CPU cycles (lifecycles)] for three test cases against ten voltage traces and decay-only mode. For the crc test case, the mean proportion of cycles spent in Mementos code was $24.5 \pm 1.3\%$ ; for sense, $49.1 \pm 11.0\%$ ; for rsa64, $56.6 \pm 5.6\%$                                                                                                                     |

| 3.5   | In decay-only mode (top half) and against a voltage trace (#9, bottom half), the <b>sense</b> test case exhibits behavior that is dependent on the voltage threshold $V_{\text{thresh}}$ and, in timer-aided mode, the timer interval. $\% M$ refers to the portion of CPU cycles spent within Mementos code. This table illustrates the key differences among Mementos's various instrumentation modes56 |

| 3.6 | For the <b>sense</b> test case with loop-latch instrumentation, against the same voltage trace used for Table 3.5, adaptive checkpointing reduces the fraction of wasted cycles and the number of lifecycles. For the <i>Adaptive</i> runs, the $V_{\text{thresh}}$ values in the left column were initial values rather than fixed values                                                 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.7 | Comparison of oracle-mode predictions and adaptive-checkpointing<br>performance for the crc test case. (Note that the lifecycle counts<br>in the left column may be overestimates, as mentioned in<br>Section 3.6.1.3.)                                                                                                                                                                    |

| 4.1 | CCCP's design goals and techniques for accomplishing each of<br>them                                                                                                                                                                                                                                                                                                                       |

| 4.2 | Variables CCCP stores in nonvolatile memory                                                                                                                                                                                                                                                                                                                                                |

| 4.3 | Comparison of energy required for flash operations on an<br>MSP430F2274. Hole punching often allows CCCP to use a<br>single-word write (2 bytes on the MSP430) instead of a segment<br>erase when incrementing a complemented unary counter90                                                                                                                                              |

| 6.1 | Comparison of our emulator to typical commercial pacemakers.<br>Because the designs of cardiac devices are closely held secrets, the<br>entries marked with $\star$ are estimates based on a 1999 book on<br>real-time systems [44]. The radio specification (marked with †) is<br>based on public information from a semiconductor manufacturer<br>that serves IMD manufacturers [134]129 |

| 6.2 | Current consumption of the radio-equipped emulated pacemaker<br>versus that of Noradio, when not communicating with the<br>emulated clinical programmer ( <i>Unlinked</i> row) and when<br>communicating with it ( <i>Linked</i> row)                                                                                                                                                      |

| 6.3 | Projected battery life of both the radio-equipped and Noradio<br>versions of the emulated pacemaker with a 1.5 Ah pacemaker<br>battery                                                                                                                                                                                                                                                     |

# LIST OF FIGURES

| Figure | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

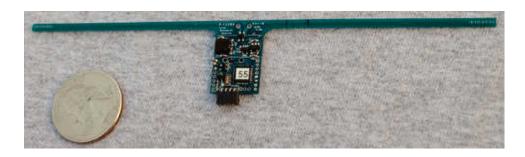

| 2.1    | Photo of DL WISP 4.1 [138]11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2    | Photo of UMass Moo [175]11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

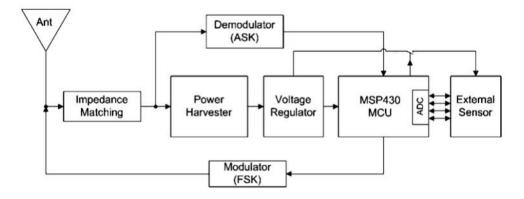

| 2.3    | Block diagram of DL WISP 4.1. Reproduced from Sample et al. [138]<br>with permission16                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

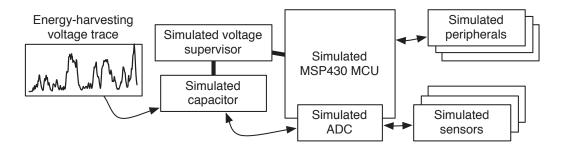

| 2.4    | Block diagram of our simulation environment based on MSPsim16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

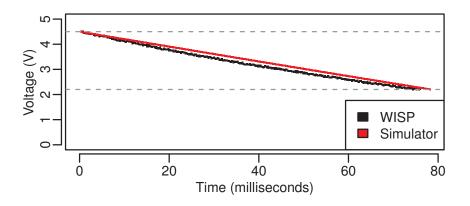

| 2.5    | Simulated capacitor's voltage approximates the discharge time and<br>voltage drop of a hardware WISP's capacitor. Both were charged<br>to 4.5 V and allowed to discharge while executing an infinite loop<br>at 1 MHz in active mode. Both traces end at 2.2 V, the nominal<br>minimum voltage for flash writes on an MSP430                                                                                                                                                                                                                     |

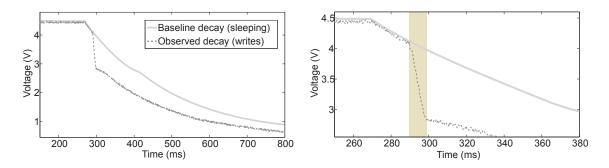

| 2.6    | Measuring instruction energy for 64 flash writes, taking leakage into account. The right figure is a detailed view of the left figure21                                                                                                                                                                                                                                                                                                                                                                                                          |

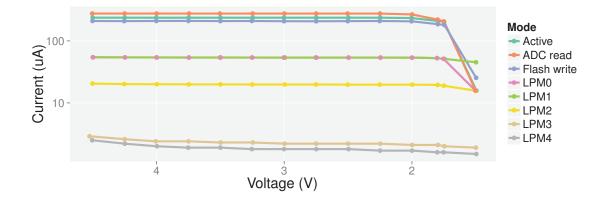

| 2.7    | Current consumption versus voltage for the MSP430F2132<br>microcontroller on a DL WISP 4.1 [138] CRFID in distinct power<br>modes. We model each of these modes in our simulation<br>environment                                                                                                                                                                                                                                                                                                                                                 |

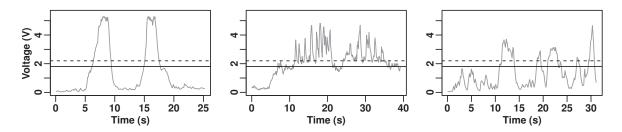

| 3.1    | Energy availability under RF harvesting is difficult to predict on a transiently powered computer (TPC), threatening the successful completion of long-running programs. These plots show the output of a prototype TPC's energy-harvesting frontend during three different smooth movements within 2 m of an RFID reader. The dashed line at 2.2 V represents this prototype's nominal minimum voltage for flash writes. The solid line at 1.8 V depicts the prototype's nominal minimum operating voltage, below which it loses volatile state |

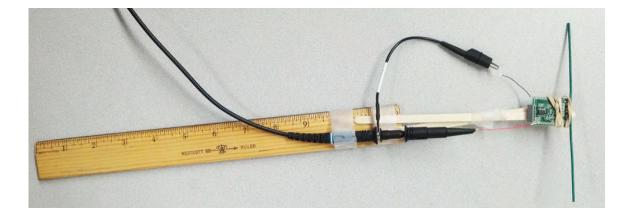

| 3.2    | Test harness for testing the frequency of reboots on a UMass Moo.<br>An oscilloscope probe observes the voltage of a pin that the Moo<br>raises and lowers on each boot                                                                                                                                                                                                                                                                                                                                                                          |

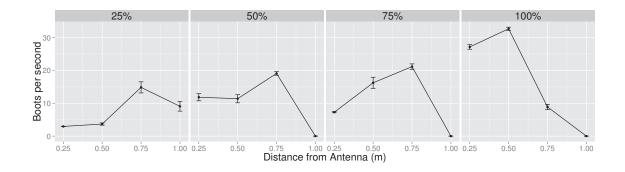

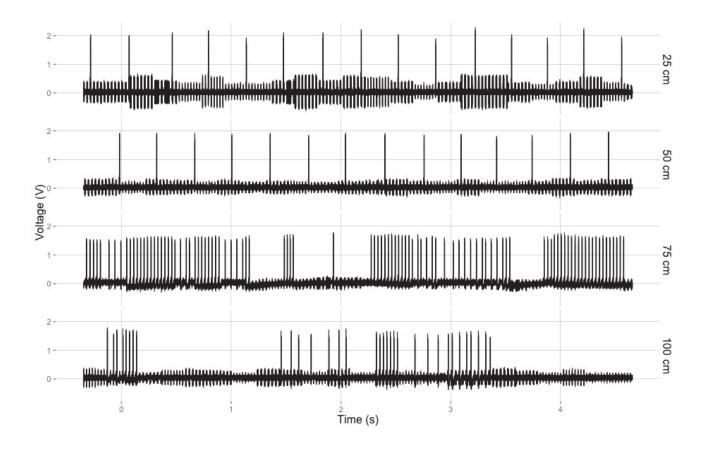

| 3.3 | Boots per second for a UMass Moo for all four test workloads (25% duty cycle to 100% duty cycle)36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4 | Boot events for a single workload (25% duty cycle) as we vary the<br>UMass Moo CRFID's distance from an RFID reader37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

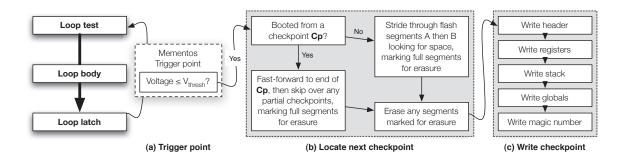

| 3.5 | Overview of run-time checkpointing in Mementos. This diagram<br>depicts the <i>loop-latch mode</i> in which Mementos instruments loop<br>back-edges with energy checks that conditionally trigger<br>checkpointing                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3.6 | A state checkpoint in Mementos. The length of the entire checkpoint<br>can be calculated from the two-byte header                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

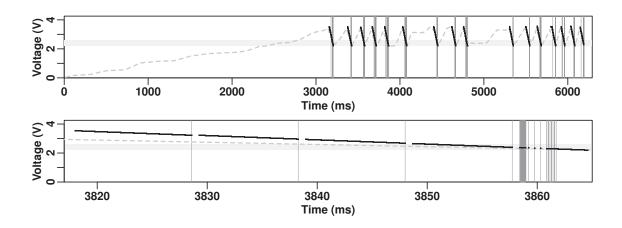

| 3.7 | Simulated voltage versus time as Mementos spreads the execution of<br>the crc test case across 17 power lifecycles (16 resets) against a<br>voltage trace (#9). The bottom plot highlights a single power<br>lifecycle from the top plot                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3.8 | A state checkpoint in the <i>adaptive</i> version of Mementos. As in the non-adaptive version, the length of the entire checkpoint can be calculated from the two-byte header. Mementos uses an additional four bytes of metadata (shown in bold) to decide whether to adjust its checkpointing voltage threshold $V_{\rm thresh}$ up or down60                                                                                                                                                                                                                                                                                                         |

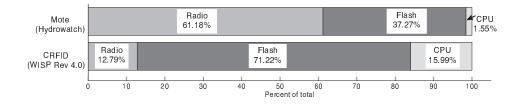

| 4.1 | Per-component maximum power consumption of two embedded<br>devices. Radio communication on the WISP requires less power<br>than writes to flash memory. The relative magnitudes of the<br>power requirements means that a sensor mote favors shifting<br>storage workloads to local flash memory instead of remote storage<br>via radio, while a computational RFID favors radio over flash.<br>The numbers for the mote are calculated based on the current<br>consumption numbers given by Fonseca et al. [52]. For the<br>CRFID, we measured three operations (radio transmit, flash<br>write, and register-to-register move) for a 128-byte payload |

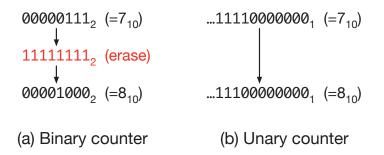

| 4.2 | Illustration of hole punching. While incrementing a binary counter<br>(a) in flash memory may require an energy-intensive erase<br>operation, complemented unary representation ((b), with the<br>number of zeros, or "holes," representing the counter value) allows                                                                                                                                                                                                                                                                                                                                                                                   |

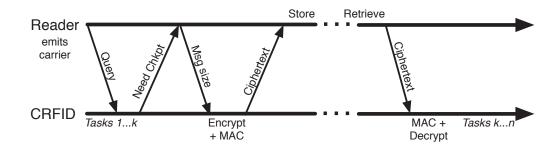

| 4.3 | Application-level view of the CCCP protocol. The CRFID sends a<br>request to checkpoint state while in the presence of a reader, and<br>the reader specifies the maximum size of each message. The<br>CRFID then prepares the checkpoint and transmits it in a series<br>of appropriately sized messages. The reader stores the checkpoint<br>data for later retrieval by the CRFID. All messages from the<br>reader to the CRFID also supply power to the CRFID if the latter<br>is within range |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

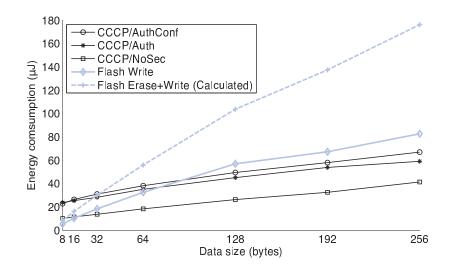

| 4.4 | Energy consumption measurements from a WISP (Revision 4.0) prototype for all considered checkpointing strategies. Under our experimental method, we are unable to execute flash writes larger than 256 bytes on current hardware because larger data sizes exhaust the maximum amount of energy available in a single energy lifecycle. The average and maximum percent error of the measurements are 5.85% and 14.08% respectively                                                               |

| 5.1 | Two kinds of adversaries for IMD applications: a passive<br>eavesdropper (left) and an active adversary with a radio<br>(right)                                                                                                                                                                                                                                                                                                                                                                   |

| 5.2 | The WISP with attached piezo-element                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.3 | "Alice." To simulate implantation in a human, we placed WISPer in<br>a bag containing bacon and ground beef (left and middle). This<br>method of tissue simulation is deprecated. Section 5.3.4<br>suggests a preferable method of tissue simulation (right)117                                                                                                                                                                                                                                   |

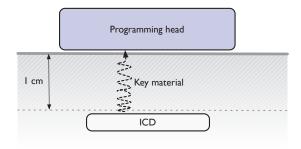

| 5.4 | Zero-power sensible key exchange: a nonce is transmitted from the ICD to the programmer using acoustic waves. It can be clearly picked up only if the programmer is in contact with the patient's body near the implantation site, and can be used as the secret key in the authentication protocol from the previous section. (1 cm is a typical implantation depth. Diagram is not to scale.)                                                                                                   |

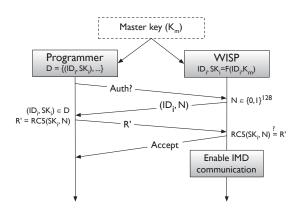

| 5.5 | The protocol for communication between an ICD programmer and a zero-power authentication device (a WISP RFID tag, in the case of our prototype)                                                                                                                                                                                                                                                                                                                                                   |

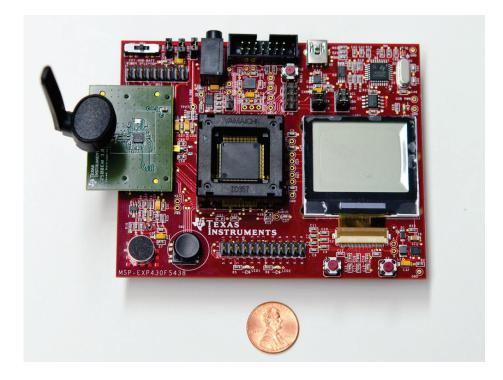

| 6.1 | Photo of an MSP-EXP430F5438 board with a CC2500 2.4 GHz<br>daughterboard implementing the radio-equipped version of our<br>emulated pacemaker                                                                                                                                                                                                                                                                                                                                                     |

| 6.2 | Block diagram of the <i>radio-equipped</i> version of an emulated<br>pacemaker. The pacemaker reads an analog signal (e.g., a<br>heartbeat) and transmits a representation of it to an emulated<br>clinical programmer                                                                                                                                      |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6.3 | Noradio, the Moo-augmented version of the emulated pacemaker. $\dots 132$                                                                                                                                                                                                                                                                                   |

| 6.4 | Block diagram of the <i>radioless</i> version of the Noradio prototype.<br>When an RFID reader provides power, a UMass Moo CRFID<br>triggers an interrupt on the Noradio board's CPU, causing it to<br>read commands from the Moo. In response to an appropriate<br>command, Noradio drains its buffer of stored ADC readings over<br>a data bus to the Moo |

# CHAPTER 1 INTRODUCTION

Designers of computing devices constantly run into barriers when the time comes to consider power. Tethered AC power is not available everywhere and requires relatively large switching circuitry to obtain the needed DC power. Batteries are an appealing alternative to tethered power, but they have failed to keep pace with trends in chip and circuit scaling. Consequently, many electronic devices have their size, weight, and therefore mobility determined by the batteries that power them.

This thesis posits a world in which *energy harvesting* allows electronic devices to operate only on the energy they harvest, without batteries. Some such devices already exist; others will appear as the building blocks for energy harvesting circuits become more widely used and more efficient.

Depending on harvested energy can be challenging for devices. They rely on external parties (or phenomena) instead of themselves. The performance of energy harvesting can fluctuate, leading to inconvenient power losses or unpredictable power. Technical limitations of harvesting impose an upper bound on device specifications such as maximum current. These are the problems that afflict what we call *transiently powered computers*; addressing them is the focus of this thesis.

#### **1.1** Background and Motivation

Demand for small, easily embedded computers and sensors is driving the development of general-purpose *transiently powered computers* (TPCs) that lack both batteries and wired power and that operate exclusively on energy harvested from external supplies or environmental phenomena. Such devices range from *computational* RFIDs (CRFIDs) [30], which are microcontroller-based devices that harvest energy from RFID readers via radio (RF) waves, to general-purpose batteryless sensor devices [169] powered by solar panels, to platforms powered by RF–solar hybrid harvesting [62], to "interaction-powered" wireless user-interface devices [164]. Academic and industrial research continues to produce new energy-harvesting mechanisms, generating power from phenomena as diverse as vibration [7], heat differentials [71], and stomach fluids [43].

Without batteries—which require periodic replacement, are relatively heavy, and dominate board layouts—TPCs require virtually no maintenance and can be embedded in situations for which battery-powered computers are unsuitable, such as inside building materials or living tissue.

#### 1.2 Challenges

The transient manner of TPCs' operation has burdensome implications for system design, which manifest as the following challenges:

- 1. **Power.** TPCs that operate on harvested energy may operate very close to their minimum requirements, resulting in constant losses of power that result in the disappearance of volatile state and increased risk of soft errors.

- 2. Communication. On unpredictable power, a TPC cannot depend on being able to schedule, or even initiate, communications—which may break protocol participation or other application assumptions. Additionally, TPCs' power budgets may preclude them from having active radios, depending instead on other less flexible forms of communication (e.g., backscatter radiation for CRFIDs).

- 3. Security. TPCs completely depend on entities that are external to them to provide power. For some TPCs such as CRFIDs that also use the power link for

data exchange, this complete dependence raises the question of trust: how can such a TPC offer any kind of application-level guarantees of data integrity or confidentiality if the tag will communicate with any entity that agrees to power it?

4. **Storage.** Nonvolatile memories such as NOR flash are available on-chip in many microcontrollers, but these memories require two orders of magnitude more energy than volatile memories per byte written. Applications that require persistent storage must use nonvolatile memory judiciously, if at all.

Each of these challenges limits the suitability of energy harvesting as the sole supply of power for devices. However, software-based approaches can provide solutions that correct or ameliorate each of these problems.

#### **1.3** Thesis Statement and Summary

The motivating idea of this thesis is:

Software techniques on simple energy-harvesting hardware can make energy harvesting a practicable way to power computing devices, and can expand the capabilities of electronic devices without imposing extra energy costs.

The software techniques in this thesis are meant to complement, not replace, energy-harvesting hardware. Rather than posing the question of how to harvest energy most effectively, the thesis focuses on how to build capable, trustworthy systems from components that are unreliably powered, energy constrained, and dependent on possibly untrustworthy external devices.

The thesis comprises two main thrusts, summarized below. The first describes problems that are peculiar to TPCs and evaluates software systems that are designed to address the challenges listed at the beginning of this section. The second explores a specific application of TPCs to demonstrate empirically that introducing a TPC can materially improve an existing system.

- 1. Thrust #1: Addressing TPC challenges. In light of the challenges described above, I describe and demonstrate the effectiveness of Mementos, a software system designed to make computation on TPCs robust against frequent power failures. In particular, I perform end-to-end evaluation with a cycle-accurate, energy-accurate simulator to show that Mementos enables TPCs to run applications that fail to run without it. I also describe CCCP, a communication mechanism that provides cryptographically protected off-board storage for CRFIDs that is *less energy intensive* than on-board flash storage for data sizes above 32 bytes.

- 2. Thrust #2: Improving devices with TPCs. This thrust focuses on an application area for TPCs: medical devices that operate inside body tissue. I first offer a template for augmentation of a device with a TPC, in the form of a challenge–response protocol for CRFIDs that endows an implantable cardiac device with an authentication mechanism. Cardiac devices such as pacemakers are particularly good candidates for augmentation with TPCs because (1) the total implanted size depends largely on battery capacity and (2) battery capacity depends largely on non-life-supporting functions such as wireless communication and signal processing. Extending the aforementioned template for augmentation with a TPC, I implement Noradio, a simplified pacemaker, and show how to decompose its functions into therapeutic sensing and actuation, on one hand, and communication and storage, on the other. For the communication subsystem, I use a UMass Moo CRFID to replace the pacemaker's on-board radio.

#### **1.4** Contributions

To address the problem of constant power loss destroying volatile state, I describe *Mementos*, a system that instruments programs with energy checks that induce energy-aware state checkpoints [124]. Designed for use on CRFIDs but applicable to other TPCs, Mementos continually monitors the voltage of an energy buffer (e.g., a storage capacitor) at run time. When the voltage drops below a programmer-specified threshold value, a checkpointing routine writes all of the program's volatile state (registers, stack, and globals) to nonvolatile memory, where it survives during a power loss. At next boot, a checkpoint-restoration routine copies the state from nonvolatile memory back to volatile memory and resumes execution. Mementos thereby spreads computations across multiple power lifecycles. Compared to previous checkpointing systems, Mementos is designed for tighter resource constraints and a finer, configurable granularity of checkpointing based on energy available at run time.

Additionally, I describe a CRFID simulator, originally designed for use with Mementos, that couples an architectural cycle-accurate MSP430 microcontroller simulator [49] with an energy-trace-driven simulated energy-harvesting front end that governs execution. Unlike most architectural or circuit simulators, this CRFID simulator incorporates inputs from the analog *and* digital domains.

A second contribution is a mechanism for secure outsourced storage for CRFIDs. A system called CCCP—for *cryptographic computational continuation passing* [135] addresses the challenges of security and storage and partially addresses the challenge of communications. CCCP is software that provides CRFIDs with an off-tag storage facility layered on existing radio protocols. As data size increases, CCCP requires less energy than local storage on flash memory.

A third contribution is a "zero-power" security mechanism that endows a medical devices with enhanced security properties without requiring any of the medical device's limited battery power. Modern implantable medical devices (IMDs) are sensing and actuation devices that depend on a nonrechargeable battery for power. Unfortunately, IMDs designed without security as a design goal are vulnerable to battery-depletion attacks that can significantly reduce the device's availability over time. I present *WISPer*, a mechanism designed to augment an IMD with security features missing from its original design: authentication of external parties, and a "sensible" key-exchange mechanism that enables patients to sense security-sensitive events.

A final contribution is an extension of WISPer that outsources *all* the communications of a medical device to a TPC in order to save energy versus an active radio. Extending the example of WISPer, I design and implement *Noradio*, a prototype simulated pacemaker, and evaluate its energy use both with a radio—when it resembles cardiac IMDs on the market—and with all of its communication outsourced to a connected CRFID. The most salient novel component of this preliminary work is the method of completely outsourcing communication, turning synchronous protocol participation into asynchronous, query-oriented data collection. Restructuring telemetry transmissions as an asynchronous, CRFID-driven task results in a 44% reduction of current consumption during communication. The techniques I develop to build Noradio are applicable to other devices that are battery powered and use radios to communicate.

#### 1.5 Thesis Outline

The remainder of this thesis is structured as follows.

Chapter 2 describes computational RFIDs, a kind of TPC that is powered by harvested radio frequency energy. Reproducibility of experiments is problematic on CRFIDs, and existing simulation tools are not well suited to simulating them, so the chapter develops a simulation framework that accurately captures the behavior of a CRFID.

Chapter 3 considers the problem of computing steadily on TPCs. It describes Mementos [124], a system that protects computations from power failures with energyaware state checkpointing. Chapter 4 addresses communication and storage on CRFIDs. It describes CCCP [135], a mechanism for outsourced storage that improves energy efficiency for CRFIDs storing state checkpoints.

Chapter 5 summarizes the security problems inherent in an implantable medical device [27, 69], then describes WISPer, a TPC-based communication subsystem that uses lightweight cryptography and a simple challenge–response protocol to address several of the security problems.

Chapter 6 describes an emulated cardiac pacemaker that couples with a TPC to obviate the need for any radio—typically an energy-hungry component—on board the pacemaker at all.

Chapter 7 discusses the implications of this work's improvements to and study of TPCs—in particular, ways in which they can enable new kinds of devices and improve battery-powered devices.

#### CHAPTER 2

## SIMULATING TRANSIENTLY POWERED COMPUTERS<sup>1</sup>

Modeling and simulation together provide a convenient way to experiment on the design of computing systems. A typical research approach is to change designs in simulation before fabricating hardware. System designers can choose tools that model computers from the circuit level to the OS level—but these models typically do not span the analog and digital domains.

Transiently powered computers are difficult to model with conventional analog- or digital-domain tools because analog-domain inputs (specifically, the amount of energy available from the power supply) govern execution in the digital domain. Digitaldomain simulators' abstraction of the power supply as a bottomless resource therefore does not apply.

This chapter's contribution is a simulator for TPCs that incorporates both digital-domain and analog-domain inputs—a computer program and an energy trace against which to run the program. The simulator is an extension of MSPsim [49], a cycle-accurate simulator for the MSP430 family of microcontrollers, that newly incorporates models of energy harvesting and consumption. We tuned and evaluated the model according to empirical measurements of two *computational RFIDs* (CRFID, Section 2.1) that perform sensing and computation tasks solely on harvested radio frequency (RF) energy.

<sup>&</sup>lt;sup>1</sup>This chapter describes extensions to a simulator developed for the Mementos system presented in Chapter 3 and in an earlier paper by Ransford, Sorber, and Fu [124].

To simulate the running of a program on a CRFID under energy harvesting, the simulator adjusts current consumption to match empirical measurements of hardware MSP430 microcontrollers. An input energy trace, collected with an analog RF-harvesting front end from a CRFID, charges a simulated capacitor that models a CRFID's storage capacitor. The simulated microcontroller executes instructions from the input program, drawing an empirically calibrated simulated current according to its activity mode, thereby discharging the capacitor. When the capacitor's simulated voltage declines to a certain level, a simulated power loss occurs, and components of the simulator reset—all in-progress operations stop, all volatile memory is zeroed, and the program counter is reset to the beginning of code memory.

#### 2.1 Computational RFIDs

Computational RFIDs (CRFIDs) are a class of programmable, batteryless computers that operate solely on harvested energy, much like widespread passive RFID tags used in supply-chain applications [23, 22, 122, 124].

The key difference between supply-chain RFID tags and CRFIDs is that CRFIDs use general-purpose microprocessors that allow them to execute general-purpose programs; the former are typically implemented as application-specific integrated circuits (ASICs), resulting in low power consumption but fixed functionality that is tightly coupled to certain applications. Supply-chain ASICs often implement only an RFID protocol state machine and a chunk of memory containing static information. This static information is particularly useful for tracking retail objects.

The first instance of a CRFID is the Wireless Identification and Sensing Platform, or WISP [138], Figure 2.1, a prototype device slightly smaller than a postage stamp (discounting its antenna, which is several centimeters long). The WISP is built around an off-the-shelf TI MSP430 microcontroller, as are many of its descendants, such as the UMass Moo [175], Figure 2.2. The WISP and its descendants share physical attributes and, to an extent, circuit designs. The common elements of these prototype CRFIDs are:

- a low-power microcontroller such as the TI MSP430 [155];

- on-chip RAM;

- flash memory (on or off the microcontroller);

- energy-harvesting circuitry tuned to a certain frequency (e.g., 913 MHz for EPC Gen 2 RFID);

- an antenna;

- a transistor between the antenna and the microcontroller to modulate the analog front end's impedance;

- a capacitor for storage of harvested energy;

- optional sensors for physical phenomena such as acceleration, heat, or light; and

- one or more analog-to-digital converters (ADCs) for measuring voltage (and interacting with sensors).

The energy-harvesting circuitry, antenna, and transistor comprise the CRFID's *analog front end*. The microcontroller, memory, sensors, and other digital components together comprise the *digital back end*. The analog front end provides power (by charging the capacitor) and information to the digital back end, which can in turn transmit its outputs via the analog front end.

CRFIDs combine properties of supply-chain RFID tags with those of sensor motes such as the Telos [117]. Like passive RFID tags but unlike motes, CRFIDs are powered solely by harvested RF energy and lack active radio components (dedicated radio circuits or chipsets that require their own power). Instead of active radios, CRFIDs

Figure 2.1. Photo of DL WISP 4.1 [138].

Figure 2.2. Photo of UMass Moo [175].

use *backscatter* communication: in the presence of incoming radio waves, a CRFID electrically modulates its analog front end's impedance using a transistor, encoding binary information by varying the amount of signal the antenna reflects. While the omission of active radio circuitry saves energy, it gives up the tag's autonomy; a CRFID can send and receive information only at the command of an RFID reader.

The small size and low maintenance requirements of CRFIDs make them especially appealing for adding computational capabilities to contexts in which placing or maintaining a conventional computer would be infeasible or impossible. However, CRFID systems require that nearby, actively powered RFID readers provide energy whenever computation is to occur, a requirement that may not suit all applications.

#### 2.2 Reproducibility and Simulation

A key concern in system design and evaluation is the classic scientific goal of *reproducibility*: People other than the researcher should be able to achieve the same

results under similar conditions, and the researcher herself should be able to achieve the same results multiple times.

A typical approach to enabling reproducible experiments is *simulation*, in which a computer program models all or part of a system to predicts its behavior under given input conditions. For computers, traditional simulation methods fall into two categories. *Architectural* simulators such as Simics [145] or gem5 [56, 99] implement the target architecture's instruction set and model pipelines, memory, and various other hardware features at the digital level. In contrast, *circuit-level* simulators such as those based on SPICE [100] model hardware components at the analog level, enabling accurate predictions of electrical behavior, thermal behavior [147], or component reliability [12] under a variety of conditions.

In contrast to conventional computers that are continuously powered, a TPC's behavior can be difficult to predict because energy harvesting can be unpredictable. RF harvesting, in particular, depends on factors such as the physical orientation of the harvesting antenna in relation to the energy source, the distance from the source, the variety of paths an electromagnetic wave can take from the source to the harvester, and the physical properties of materials in the vicinity of the source and harvester. Other harvesting modalities come with similar complications—light levels for solar panels, elasticity and reverberations for vibration harvesters, heat dissipation for thermal harvesters, and so on.

Because TPCs' behavior depends so much on environmental factors, traditional simulators used to model continuously powered computers are a poor match for simulating TPCs. Traditional simulators are designed for *deterministic* simulations in which the same inputs—either analog or digital—produce the same outputs. In the case of a TPC, both kinds of inputs matter. Nondeterministic energy harvesting results in pauses or stoppages of computation, re-execution of instructions, and loss of computational state at inconvenient times, and it is unlikely that any two runs of a

| Feature                    | Analog sim.<br>(e.g., SPICE) | Digital sim.<br>(incl. MSPsim) | $egin{array}{c} { m MSPsim} + \ { m this} \ { m work} \end{array}$ |

|----------------------------|------------------------------|--------------------------------|--------------------------------------------------------------------|

| Electrical simulation      | (o.g., 01101)<br>✓           |                                |                                                                    |

| Instruction-set emulation  |                              | $\checkmark$                   | 1                                                                  |

| Can run compiled programs  |                              | $\checkmark$                   | $\checkmark$                                                       |

| Accurate memory timing     | $\checkmark$                 | $\checkmark$                   | $\checkmark$                                                       |

| Cycle-accuracy             | $\checkmark$                 | $\checkmark$                   | $\checkmark$                                                       |

| Simulation of power supply | $\checkmark$                 |                                | $\checkmark$                                                       |

| Radio-wave simulation      |                              |                                |                                                                    |

Table 2.1. Comparison of simulator features.

program on a TPC will have exactly the same energy conditions. Even "full-system" simulators such as  $FeS_2$  [51] abstract away analog-domain details such as power and temperature. This abstraction is reasonable for many scenarios, but for TPCs, ignoring analog effects on digital computations may result in incorrect or misleading conclusions.

This chapter describes a set of modifications to MSPsim [49], a cycle-accurate simulator for the MSP430 family of microcontrollers, to capture the peculiarities of transiently powered computers. MSPsim models mote-class sensor devices by simulating an MSP430 microcontroller [155] and a variety of input/output devices (including active radio hardware and serial peripherals). MSPsim's microcontroller simulation implements the 16-bit MSP430 (and 20-bit MSP430X) instruction set architecture, allowing it to accept MSP430 object code and execute it in a cycle-accurate manner.

Our modifications to MSPsim fall into two categories: modeling energy harvesting and simulating power loss and restoration. The result is a simulation that incorporates inputs from the analog and digital domains and enables reproducible, realistic behavior for a TPC under simulation. Table 2.1 compares this work to conventional analog and digital simulators.

<sup>&</sup>lt;sup>a</sup>Our tools simulate a *subset* of the electrical components on a CRFID, most crucially the storage capacitor that buffers incoming energy and obeys the standard capacitor equations.

#### CRFID property Simulator mechanism

| MSPsim fully supports MSP430 ISA                             |

|--------------------------------------------------------------|

| Accept voltage traces recorded on a hardware CRFID's analog  |

| front end                                                    |

| Recognize programmatic transitions to low-power mode; change |

| simulated MCU's current consumption                          |

| Use empirically determined mapping of MCU power mode and     |

| voltage to current                                           |

| Obey capacitor equations for charging and discharging under  |

| load                                                         |

| Obey capacitor equations for exponential decay (leakage)     |

| Use empirically measured time and current per operation      |

| Support bit-banging transmissions onto GPIO                  |

|                                                              |

**Table 2.2.** Mapping of Intel WISP and UMass Moo hardware properties to simulator mechanisms.

For a concrete choice of TPC to simulate, the system described in this chapter models the DL WISP 4.1 [138], an RF-harvesting TPC with an MSP430F2132 microcontroller and a  $10 \,\mu\text{F}$  storage capacitor, and its descendant the UMass Moo [175], which resembles the WISP but features an MSP430F2618 microcontroller with increased RAM and flash memory. Table 2.2 maps specific hardware properties of these CRFIDs to their simulations.

The simulation models most properties of the WISP and Moo, but its treatment of backscatter communication merits special description. Backscatter modulation operates on the same radio waves that provide energy, making synchronous uplink communication effectively "free"—modulo the negligible cost of switching a single transistor—on backscattering devices. Our simulation therefore models only the time and cycle count of the backscatter modulation. The simulator also makes no attempt to account for certain environmental parameters such as temperature because the variations they induce are typically small under laboratory conditions (and predictable otherwise).

#### 2.3 Modeling Energy Harvesting in MSPsim

Like the traditional simulators described above, MSPsim models computing components in the digital domain, abstracting away analog components such as the power supply. In MSPsim's simulation of a mote, the digital components are conceptually backed by an imaginary battery that provides sufficient voltage and current to every subsystem. Unlike the continuously powered motes MSPsim models, a CRFID may lose power several times per second as it simultaneously computes and harvests RF energy, and the available energy may not be enough to support the components that should run. To match the behavior of a CRFID simulated in MSPsim to that of a real CRFID, we extended MSPsim to model the WISP's energy harvesting. (The Moo shares the WISP's energy-harvesting components, so we did not model it separately.)

The WISP's energy-harvesting hardware, depicted in Figure 2.3 and described in detail in Sample et al. [138], comprises a dipole antenna, a charge pump, and a (manually) tuned impedance-matching network that optimizes the transmission of power from the antenna to the charge pump. The charge pump increases the voltage coming from the antenna—which is small at distance from an RFID reader and charges a storage capacitor that smooths and buffers the supply. The storage capacitor powers the microcontroller via a voltage regulator that maintains a constant voltage.

From the microcontroller's perspective, the storage capacitor hides the details of the analog energy-harvesting front end. By measuring the capacitor's voltage  $V_c$ , an application on the microcontroller can learn several things [124]:

- If  $V_c \gg V_{reg}$ , the regulator's target voltage, then there is likely enough voltage to continue computing; the CRFID may be near a reader.

- If  $V_c$  is slightly greater than  $V_{reg}$ , the CRFID's power consumption may be outpacing its energy harvesting, or the CRFID may be at such a distance from the reader that harvesting is difficult.

Figure 2.3. Block diagram of DL WISP 4.1. Reproduced from Sample et al. [138] with permission.

Figure 2.4. Block diagram of our simulation environment based on MSPsim.

• If  $V_c < V_{reg}$ , a power outage may be imminent.

Because the capacitor effectively isolates the analog front end from the digital back end, our simulation approach is to abstract away the harvesting hardware and simulate the storage capacitor rather than the harvesting components—effectively *emulating*, rather than simulating, the analog front end. Figure 2.4 is a block diagram depicting the simulation environment.

The main loop of the simulator consumes instructions from the input executable. At each iteration of the main loop (i.e., after each instruction is executed), it recalculates the capacitor's voltage. Being a cycle-accurate simulator with a known clock rate, the simulator keeps track of time via its cycle counter; from this source the simulated capacitor derives its notion of time for use in its voltage calculations, described in the following paragraph.

The simulated capacitor follows the time-dependent equations that govern a real capacitor's operation. The equation for a charging capacitor is:

$$V(t) = V_0(1 - e^{-t/RC}), (2.1)$$

where R and C are the load and capacitance of the circuit, and  $V_0$  is the "initial" charge. Each time the simulator recalculates the capacitor's voltage (i.e., with each CPU instruction),  $V_0$  is the voltage calculated at the previous check, R depends on the power mode, and C is the storage capacitor's (constant) capacitance, which dominates the overall circuit's capacitance. The discharge equation is

$$V(t) = V_0 e^{-t/RC} (2.2)$$

where  $V_0$ , R, and C are defined in a similar manner.

#### 2.3.1 Energy-Harvesting Traces

We modified MSPsim to accept a voltage trace that governs energy availability over time. On a hardware CRFID, the capacitor's voltage is a proxy for energy availability and usage—it increases as the analog front end gathers energy from RF waves, and decreases as a factor of both time (via leakage) and current consumption (via computation).

To capture voltage traces from real hardware, we physically isolated a WISP's RFharvesting analog front end by cutting its connections to other parts of the circuit, attached it to a  $\sim 10 \text{ K}\Omega$  resistor that approximated the electrical load of the WISP's

Figure 2.5. Simulated capacitor's voltage approximates the discharge time and voltage drop of a hardware WISP's capacitor. Both were charged to 4.5 V and allowed to discharge while executing an infinite loop at 1 MHz in active mode. Both traces end at 2.2 V, the nominal minimum voltage for flash writes on an MSP430.

microcontroller during active computation,<sup>2</sup> and connected an Agilent U2541A data acquisition unit sampling at 1 KHz. With this measurement setup, we recorded traces of voltage across the resistor (sequences of *time, voltage* pairs) as the measurement setup moved within the read range of an RFID reader. Figure 3.1 [p. 29] shows several of these traces.

### 2.3.2 Simulating Power Loss

To model the frequent losses of power that afflict CRFIDs under normal circumstances, we extended MSPsim with an MSP430 microcontroller's shutdown and reset behavior (documented in its datasheet [156]).