## University of Massachusetts Amherst ScholarWorks@UMass Amherst

Masters Theses 1911 - February 2014

2013

# A Novel Reconfiguration Scheme in Quantum-Dot Cellular Automata for Energy Efficient Nanocomputing

Madhusudan Chilakam University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/theses

Part of the <u>Electronic Devices and Semiconductor Manufacturing Commons</u>, <u>Nanotechnology</u> <u>Fabrication Commons</u>, <u>Power and Energy Commons</u>, and the <u>VLSI and Circuits</u>, <u>Embedded and</u> <u>Hardware Systems Commons</u>

Chilakam, Madhusudan, "A Novel Reconfiguration Scheme in Quantum-Dot Cellular Automata for Energy Efficient Nanocomputing" (2013). *Masters Theses 1911 - February 2014*. 1028. Retrieved from https://scholarworks.umass.edu/theses/1028

This thesis is brought to you for free and open access by ScholarWorks@UMass Amherst. It has been accepted for inclusion in Masters Theses 1911 -February 2014 by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# A NOVEL RECONFIGURATION SCHEME IN QUANTUM-DOT CELLULAR AUTOMATA FOR ENERGY EFFICIENT NANOCOMPUTING

A Thesis Presented

by

MADHUSUDAN CHILAKAM

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

May 2013

Electrical and Computer Engineering

# A NOVEL RECONFIGURATION SCHEME IN QUANTUM-DOT CELLULAR AUTOMATA FOR ENERGY EFFICIENT NANOCOMPUTING

A Thesis Presented

by

### MADHUSUDAN CHILAKAM

Approved as to style and content by:

Neal G. Anderson, Chair

Russell Tessier, Member

Eric Polizzi, Member

C.V. Hollot, Department Chair Electrical and Computer Engineering

## ABSTRACT

## A NOVEL RECONFIGURATION SCHEME IN QUANTUM-DOT CELLULAR AUTOMATA FOR ENERGY EFFICIENT NANOCOMPUTING

MAY 2013

MADHUSUDAN CHILAKAM

# B.Tech, VELLORE INSTITUTE OF TECHNOLOGY UNIVERSITY, VELLORE M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Neal G. Anderson

Quantum-Dot Cellular Automata (QCA) is currently being investigated as an alternative to CMOS technology. There has been extensive study on a wide range of circuits from simple logical circuits such as adders to complex circuits such as 4-bit processors. At the same time, little if any work has been done in considering the possibility of reconfiguration to reduce power in QCA devices. This work presents one of the first such efforts when considering reconfigurable QCA architectures which are expected to be both robust and power efficient. We present a new reconfiguration scheme which is highly robust and is expected to dissipate less power with respect to conventional designs. An adder design based on the reconfiguration scheme will be presented in this thesis, with a detailed power analysis and comparison with existing designs. In order to overcome the problems of routing which comes with reconfigurability, a new wire crossing mechanism is also presented as part of this thesis.

# TABLE OF CONTENTS

| ABSTRACT i        | ii |

|-------------------|----|

| LIST OF TABLES    | /i |

| LIST OF FIGURES v | ii |

## CHAPTER

| 1. | INT          | RODU                      | UCTION AND MOTIVATION 1                   |

|----|--------------|---------------------------|-------------------------------------------|

| 2. | TEC          | CHNIC                     | CAL BACKGROUND 5                          |

|    | $2.1 \\ 2.2$ |                           | Basics                                    |

|    |              | $2.2.1 \\ 2.2.2 \\ 2.2.3$ | Binary Wire8Inverter9Majority Gate Voter9 |

|    | 2.3          | Clocki                    | ng in QCA10                               |

|    |              | $2.3.1 \\ 2.3.2$          | Landauer Clocking15Bennett Clocking15     |

|    | $2.4 \\ 2.5$ |                           | Crossings in QCA                          |

|    |              | $2.5.1 \\ 2.5.2$          | Reconfigurability and Nanocomputing       |

| 3. | PRO          | OPOSI                     | ED RECONFIGURATION SCHEME 21              |

|    | $3.1 \\ 3.2$ | -                         | ity Gate Voter Reconfiguration            |

| 4. | PO                  | VER ANALYSIS AND METHODOLOGY 32                                                                                                                                      | 2 |

|----|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|    | $4.1 \\ 4.2 \\ 4.3$ | Upper Bound Power Dissipation Model       33         Lower Bound Power Dissipation Model       35         Power Analysis of Proposed Reconfiguration Scheme       35 | 5 |

| 5. | QC.                 | ADDERS 42                                                                                                                                                            | 2 |

|    | $5.1 \\ 5.2$        | Background on QCA Adders                                                                                                                                             |   |

|    |                     | 5.2.1Carry Ripple Adder445.2.2Carry Look Ahead Adder51                                                                                                               |   |

| 6. | RES                 | ULTS AND COMPARATIVE ANALYSIS                                                                                                                                        | 7 |

|    | 6.1                 | Upper and Lower Bound Energy Dissipation                                                                                                                             | 3 |

|    |                     | 6.1.1Analysis of Carry Ripple Adder586.1.2Analysis of Carry Look Ahead Adder616.1.3Analysis of existing Adders62                                                     | 1 |

|    | $6.2 \\ 6.3 \\ 6.4$ | Area and Cell Count64Latency65Speed with respect to Area and Power (SwAP) Analysis66                                                                                 | 5 |

| _  |                     |                                                                                                                                                                      |   |

| 7. | CO                  | ICLUSION AND FUTURE WORK 69                                                                                                                                          | J |

|    | $7.1 \\ 7.2$        | Summary70Future71Future71                                                                                                                                            |   |

## APPENDICES

| A. RECONFIGURABILITY AND NANOCOMPUTING | <b>72</b> |

|----------------------------------------|-----------|

| B. POWER DISSIPATION MODELS            | 77        |

|                                        |           |

|                                        |           |

| BIBLIOGRAPHY                           | 82        |

# LIST OF TABLES

| Table | Page                                                                                    |

|-------|-----------------------------------------------------------------------------------------|

| 3.1   | Truth Table of XOR Gate                                                                 |

| 4.1   | Truth Table of Half Adder                                                               |

| 5.1   | Truth Table of Full Adder45                                                             |

| 6.1   | Cell Count per Unit Area Comparison                                                     |

| 6.2   | Latency Comparison                                                                      |

| 6.3   | SwAP Analysis                                                                           |

| B.1   | Bloch Hamiltonian before and after a change in clock or the<br>neighboring polarization |

# LIST OF FIGURES

| Figure | Page                                                                       |

|--------|----------------------------------------------------------------------------|

| 1.1    | Performance Evaluation for Emerging Logic Device Technologies              |

| 2.1    | Simple 4-dot Unpolarized QCA cell                                          |

| 2.2    | Polarization States of a 4-dot QCA cell7                                   |

| 2.3    | Transfer of Polarization between adjacent QCA cells                        |

| 2.4    | Binary Wire Representation in QCA                                          |

| 2.5    | Inverter Representation in QCA9                                            |

| 2.6    | Majority Gate Voter Representation in QCA10                                |

| 2.7    | The QCA clock, it's stages and it's effects on a cell's energy<br>barriers |

| 2.8    | Example of QCA Clock Transitions                                           |

| 2.9    | Landauer and Bennett clocking of QCA circuits                              |

| 2.10   | Traditional Wire Crossing Model16                                          |

| 2.11   | p-QCA device structure: QCA layer with clocking circuitry                  |

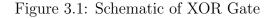

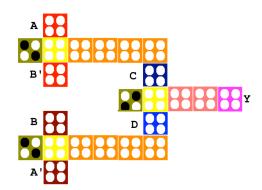

| 3.1    | Schematic of XOR Gate                                                      |

| 3.2    | Conventional XOR Gate Design                                               |

| 3.3    | Proposed XOR Gate Design                                                   |

| 3.4    | Clocking Scheme of Proposed XOR Gate Design                                |

| 3.5    | Circuit Schematic of Boolean Function (A+B)+(B.C)26                        |

| 3.6  | QCA representation of Boolean Function $(A+B)+(B.C)$                                                                                                                                     |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.7  | Clocking Scheme of the Proposed Wire Crossing Technique                                                                                                                                  |

| 3.8  | Timing Diagram of the Proposed Wire Crossing Technique                                                                                                                                   |

| 3.9  | Implementation of the Proposed Wire Crossing Technique until the<br>Pipeline Zones                                                                                                       |

| 3.10 | Implementation of the Proposed Wire Crossing Technique within and<br>after the Pipeline Zones                                                                                            |

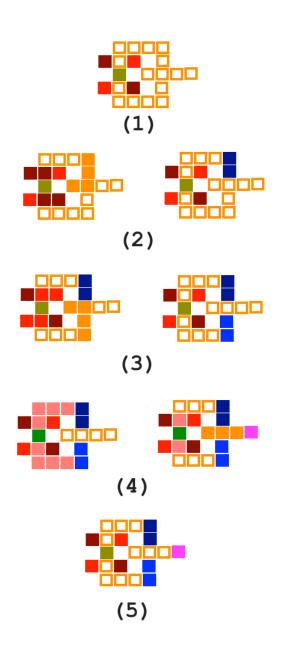

| 4.1  | Schematic, QCA Layout and Clocking Scheme of a Half Adder32                                                                                                                              |

| 4.2  | Timing Diagram of the XOR gate based on proposed Reconfiguration<br>Scheme                                                                                                               |

| 4.3  | Timing Diagram of the XOR gate based on conventional design<br>methodology                                                                                                               |

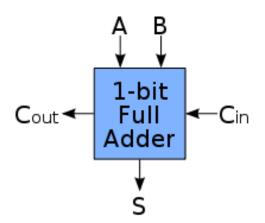

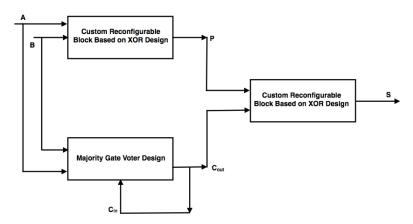

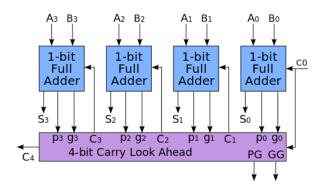

| 5.1  | Block Diagram of Full Adder                                                                                                                                                              |

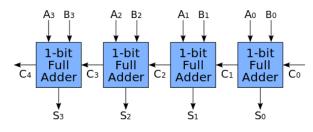

| 5.2  | Block Diagram of Carry Ripple Adder45                                                                                                                                                    |

| 5.3  | Block Diagram of Proposed Carry Ripple Adder46                                                                                                                                           |

| 5.4  | QCA Representation of Proposed Carry Ripple Adder47                                                                                                                                      |

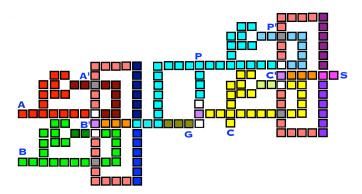

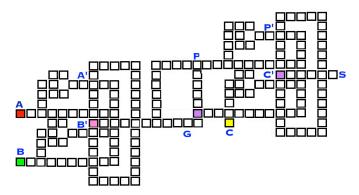

| 5.5  | Initial State of Proposed Carry Ripple Adder                                                                                                                                             |

| 5.6  | Clocking Scheme of the Carry Ripple Adder until computation of $A \otimes B \dots \dots$ |

| 5.7  | Clocking Scheme of the Carry Ripple Adder until computation of<br>Sum                                                                                                                    |

| 5.8  | Block Diagram of Carry Look Ahead Adder                                                                                                                                                  |

| 5.9  | Block Diagram of Proposed Carry Look Ahead Adder                                                                                                                                         |

| 5.10 | QCA Representation of Proposed Carry Look Ahead Adder                                                                                                                                    |

| 5.11 | Initial State of Proposed Carry Look Ahead Adder                                                                                                                                         |

| 5.12 | Clocking Scheme of the Carry Look Ahead Adder until computation<br>of Propagate |

|------|---------------------------------------------------------------------------------|

| 5.13 | Clocking Scheme of the Carry Look Ahead Adder until computation<br>of Sum       |

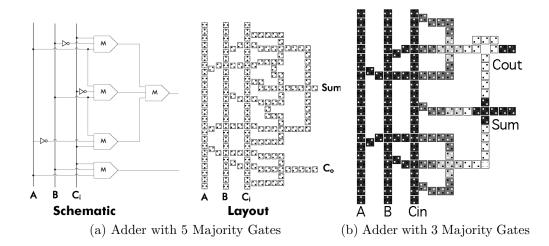

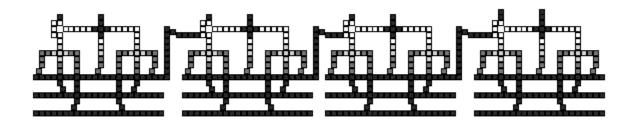

| 6.1  | QCA representation of existing adders                                           |

| 6.2  | Existing 4-bit adder                                                            |

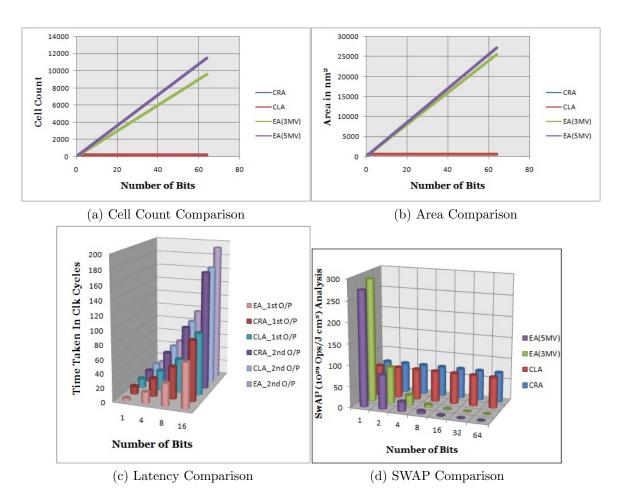

| 6.3  | Graphs comparing the proposed adders with existing adders                       |

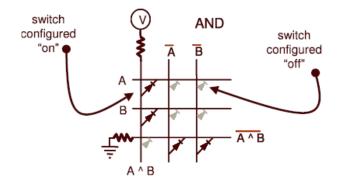

| A.1  | AND gate using reconfigurable CAEN grid73                                       |

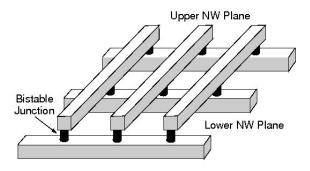

| A.2  | Typical NanoWire Crossbar Architecture                                          |

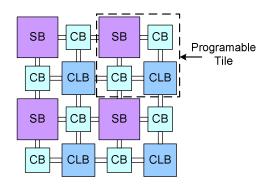

| A.3  | Island Style FPGA Architecture                                                  |

## CHAPTER 1

## INTRODUCTION AND MOTIVATION

It was as early as 1965 when Gordon Moore predicted that the number of transistors that can be integrated on to a single chip will double every 18 months [46]. This law put forth by Moore has been a benchmark for semiconductor scaling for more than four decades. The IC industry which has been primarily driven by CMOS technology scaling is now forced to look into other alternatives as the scaling is fast approaching its fundamental limits. The International Technology Roadmap for Semiconductors (ITRS) has predicted that size limit of CMOS technology will be limited to about 5 nm to 10 nm and believes this limit will be reached as early as 2017 [3]. Shrinking transistors have been helpful in achieving high speed and low power circuits. As the devices are exponentially scaled down various factors including power dissipation, gate leakage current, interconnection noise (introduction of crosstalk and hot electron effect) and stray capacitances have become potential bottlenecks that has led to the degradation of circuit performance.

In the last few years as the technology has scaled down to sub 45nm, power dissipation has been a major area of concern for researchers around the world. Fred Pollack of Intel Corporation was one of the first to note the alarming rate at which power density is increasing with the shrinking geometry [52]. Thus power management is a critical issue which needs to addressed at the earliest.

Nanotechnology is touted to be the solution to the problem of device shrinking where the performance is degraded due to increasing quantum effects and to overcome the existing power dissipation. There are many possible candidates which are being considered as a possible replacement to CMOS such as Quantum Dot Cellular Automata [40], Silicon Nano-wires [18], Carbon Nanotubes based Transistors [5, 61], Spin Wave Transistors [71, 54], Superconducting Electronics [66], Resonant Tunneling devices [45, 47] among others. Fig. 1.1 portrays a critical review of some these emerging devices at the nanoscale level.

Quantum - Dot Cellular Automata (QCA) is one such nano computing paradigm that exploits some of the unavoidable nanoscale issues such as quantum effects and device integration for performing useful computation. Some of the potential advantages of QCA include the lack of interconnects, high clock frequency, and since QCA doesn't involve transfer of electrons or flow of current, it has the potential to perform low power computing. One of the most striking features of this emerging technology is that it has the ability to dynamically reconfigure or redesign the functionality of the system which makes the system more powerful and more efficient in terms of computational speed and power dissipation.

Field Programmable Gate Arrays (FPGAs) have always been an attractive low cost option for designers since it offers flexibility in terms of hardware. Researchers have been very successful in establishing that FPGAs have outperformed the implementation of a number of real time applications in terms of computational performance and cost [68]. Reconfigurability represents an attractive application of QCA technology [21, 50]. With the help of reconfiguration, the inbuilt low power nature of QCA can be exploited to design various low power circuits which are not only efficient in terms of power but are also efficient in terms of area and computation.

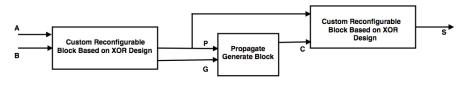

In this thesis, we explore one possible approach to realize reconfigurability in QCA that is based on the change in polarization of electrons in a QCA cell. This novel reconfiguration scheme which is based on majority gate voter is best suited for complex circuit design which have high fan-outs and require the intermediate computation results. We introduce a new custom wire crossing technique which is

| A 11 1 11 12 C                                   |                                  | Table 1. Emer                                                                   |                                                                                |                                                                         | -                                            |                                                                                                                                                               |                                                               | 6                                                                                               |

|--------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Availability Sequen                              | ce                               | 1                                                                               | 2                                                                              | 2–3                                                                     | 2–3                                          | 4                                                                                                                                                             | 5                                                             | 6                                                                                               |

| Device                                           | -                                | $\bigcirc$                                                                      |                                                                                |                                                                         |                                              |                                                                                                                                                               |                                                               |                                                                                                 |

|                                                  | ccz (0)                          | D050[2 5]                                                                       |                                                                                | Resonant<br>Tunneling                                                   | 007 (20 21)                                  |                                                                                                                                                               |                                                               |                                                                                                 |

|                                                  | FET <sup>[2]</sup>               | RSFQ <sup>[3-5]</sup>                                                           | 1-D structures                                                                 | Devices                                                                 | SET <sup>[30,31]</sup>                       | Molecular                                                                                                                                                     | QCA <sup>[39,40,49]</sup>                                     | Spin transist                                                                                   |

| Types                                            | • Si CMOS                        | لل •                                                                            | CNT FET     NW FET     NW hetero-<br>structures     Crossbar     nanostructure | • RTD-FET<br>• RTT                                                      | • SET                                        | <ul> <li>2-terminal</li> <li>3-terminal</li> <li>FET</li> <li>3-terminal</li> <li>bipolar</li> <li>transistor</li> <li>NEMS</li> <li>Molecular QCA</li> </ul> | • E: QCA<br>• M: QCA                                          | <ul> <li>Spin FET<br/>(SFET)</li> <li>Spin-valve<br/>transistor<br/>(SVT)</li> </ul>            |

| Supported<br>Architectures                       | <ul> <li>Conventional</li> </ul> | <ul> <li>Pulse</li> </ul>                                                       | <ul> <li>Conventional</li> <li>Cross-bar</li> </ul>                            | <ul> <li>Conventional</li> <li>CNN</li> </ul>                           | • CNN                                        | <ul> <li>Memory-based</li> <li>QCA</li> </ul>                                                                                                                 | • QCA                                                         | <ul> <li>Quantum</li> <li>Programmab<br/>logic</li> </ul>                                       |

| Cell Size<br>(spatial pitch)                     | 150 nm*                          | 0.3 $\mu$ m                                                                     | 150 nm*                                                                        | 150 nm*                                                                 | 40 nm                                        | Not known                                                                                                                                                     | 60 nm                                                         | 150 nm*                                                                                         |

| Density<br>(device/cm <sup>2</sup> )             | 4.5E9                            | 1E6                                                                             | 4.5E9                                                                          | 4.5E9                                                                   | 6E10                                         | 1E12                                                                                                                                                          | 3E10                                                          | 4.5E9                                                                                           |

| Switch Speed                                     | 9 THz                            | 1.2 THz                                                                         | Not known                                                                      | 1 THz [26]                                                              | 1 GHz                                        | Not known                                                                                                                                                     | 30 MHz                                                        | 700 GHz                                                                                         |

| Circuit Speed                                    | 53 GHz                           | 250–800 GHz                                                                     | 53 GHz                                                                         | 53 GHz                                                                  | 1 GHz                                        | <1 MHz (NEMS)                                                                                                                                                 | 1 MHz                                                         | 53 GHz                                                                                          |

| Switching<br>Energy, J***                        | 3 × 10 <sup>-18</sup>            | 2×10 <sup>-19</sup> [Nb]<br>{>1.4×10 <sup>-17</sup> }                           |                                                                                | > 3 × 10 <sup>-18</sup>                                                 | 1 × 10 <sup>-18</sup>                        | Not known<br>{> 1.5 × 10 <sup>-17</sup> }**                                                                                                                   | E :> 1×<br>10 <sup>_18[48]</sup><br>M: 10 <sup>-17 [49]</sup> | 3 × 10 <sup>-18</sup>                                                                           |

| Binary<br>Throughput,<br>GBit/ns/cm <sup>2</sup> | 238                              | 0.4                                                                             | 238*                                                                           | 238*                                                                    | 10                                           | N/A                                                                                                                                                           | 0.06                                                          | 238*                                                                                            |

| Gain                                             |                                  |                                                                                 | Must be ≫1 for a                                                               | all devices. See Ta                                                     | ble 2 for experin                            | nental values                                                                                                                                                 |                                                               |                                                                                                 |

| Operational<br>Temperature                       | RT                               | <ul> <li>4 K (Nb)</li> <li>77 K (HTS)</li> <li>20 K(MgB<sub>2</sub>)</li> </ul> | RT                                                                             | RT                                                                      | 20 K                                         | RT                                                                                                                                                            | E: QCA<br>Cryogenic<br>M: QCA RT                              | <ul> <li>Cryogenic<br/>(SFET)</li> <li>RT (SVT)</li> </ul>                                      |

| CD Tolerance                                     | Critical                         | Not critical                                                                    | Not critical                                                                   | Very critical                                                           | Very critical                                | Not critical                                                                                                                                                  | Very critical<br>< 2% (M: QCA)                                | Critical                                                                                        |

| Materials                                        | Si                               | Nb                                                                              | CNT                                                                            | III–V                                                                   | III–V                                        | Organic                                                                                                                                                       | AI/Al <sub>2</sub> O <sub>3</sub>                             | • III-V (SFET)                                                                                  |

| System                                           |                                  | HTS                                                                             | Si<br>III–V                                                                    | Si-Ge                                                                   | Si                                           | molecules                                                                                                                                                     | (E: QCA)                                                      | • Si/FM (SVT)                                                                                   |

| Advantages                                       |                                  | <ul> <li>Very high<br/>circuit speed</li> </ul>                                 |                                                                                | • Density<br>(smaller cell<br>size)                                     |                                              | <ul> <li>Identity of<br/>individual<br/>switches on<br/>sub-nm level</li> <li>Potential<br/>solution to<br/>interconnect<br/>problem</li> </ul>               | <ul> <li>Morphologica<br/>simplicity</li> </ul>               | al                                                                                              |

| Challenges                                       |                                  | <ul> <li>Cryogenic<br/>operations</li> </ul>                                    |                                                                                | <ul> <li>Stand-by<br/>power</li> <li>Process<br/>integration</li> </ul> | <ul> <li>Cryogenic<br/>operations</li> </ul> |                                                                                                                                                               |                                                               | <ul> <li>Low spin<br/>injection<br/>efficiency</li> <li>Short<br/>coherence<br/>time</li> </ul> |

Figure 1.1: Performance Evaluation for Emerging Logic Device Technologies. (From. ref. [2])

used to overcome the traditional problems of routing in any reconfiguration based design. The design exploits the inherent pipeline nature of QCA which can lead to an enormous reduction in area since the entire computation can be computed in a single block. One can design highly energy efficient circuits as QCA doesn't involve the physical movement of any charge particles. This design will be highly energy efficient along with added advantages of pipelining and area.

The major contributions of this thesis are

- We present our vision for low power computation based on QCA.

- We introduce the concept of reconfigurability in QCA for constructing energy efficient logic devices.

- Design of simple arithmetic circuits like full adders using the proposed reconfiguration scheme.

- We address the problems in routing with a custom wire crossing technique.

- We evaluate benefits of our designs vs. existing designs.

The rest of the thesis is organized as follows: the background on QCA and reconfigurability in nano computing and in particular in QCA are presented in Chapter 2. The concept of proposed reconfiguration scheme along with the wire crossing techniques are discussed in Chapter 3. Analysis of the proposed designs and the power dissipation models considered in the design analysis is presented in Chapter 4. Chapter 5 outlines the existing adder design and introduces the proposed adder design based on the reconfiguration scheme. A detail analysis of the proposed adder design along with the comparative analysis is presented in Chapter 6 and the thesis is concluded in Chapter 7.

# CHAPTER 2 TECHNICAL BACKGROUND

Quantum Cellular Automata are models used in quantum computation which are analogous to conventional models of cellular automata suggested by Von Neumann [48]. The first step towards quantizing the existing models of cellular automata was suggested by Richard Feynman [31, 30]. The word Quantum Cellular Automata was defined by Gerhard Grossing and Anton Zeilinger to a model [34] which they developed in the year 1988. However, the model proposed by them had little or no relation to the concepts developed in quantum computation by David Deutsch, hence their model has not been developed as a model of computation [22]. John Watrous was the first to do an in-depth research on the models based on Quantum Cellular Automata [70]. Craig Lent and Doug Tougaw proposed implementation of systems based on the classical cellular automata designed using quantum dots [40] as a replacement for the classical computation using CMOS. In order to differentiate this proposal and the models of cellular automata which are used for performing quantum computation, many authors refers to this subject as Quantum-dot Cellular Automata (QCA).

#### 2.1 QCA Basics

Quantum-dot Cellular Automata (QCA) is a new nano computing paradigm which encodes binary information by charge configuration within a cell instead of the conventional current switches. There is no current flow within the cells since the coulombic interaction between the electrons is sufficient for computation. This paradigm provides one of many possible solutions for transistor-less computation at the nanoscale.

The standard QCA cells have four quantum dots and two electrons [64]. There are various kinds of QCA cells proposed which include a six-dot QCA cell and an eight-dot QCA cell. In a QCA Cell, two electrons occupy diagonally opposite dots in the cell due to mutual repulsion of like charges. An example of a simple unpolarized QCA cell consisting of four quantum dots arranged in a square is as shown in Fig. 2.1. Dots are simply places where a charge can be localized. There are two extra electrons in the cell those are free to move between the four dots. Tunneling in or out of a cell is suppressed.

Figure 2.1: Simple 4-dot Unpolarized QCA cell. (From. ref. [59])

The numbering of the dots in the cell goes clockwise starting from the dot on the top right. A polarization P in a cell, that measures the extent to which the electronic charge is distributed among the four dots, is therefore defined as:

$$P = \frac{(\rho_1 + \rho_3) - (\rho_2 + \rho_4)}{\rho_1 + \rho_2 + \rho_3 + \rho_4}$$

(2.1)

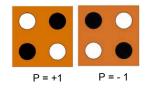

Where  $\rho_i$  is the electronic charge in each dot of a four dot QCA cell. Once polarized, a QCA cell can be in any one of the two possible states depending on the polarization of charges in the cell. Because of coulombic repulsion, the two most likely polarization states of QCA can be denoted as P = +1 and P = -1 as shown in Fig. 2.2. The two states depicted here are called most likely and not the only two polarization states because of the small (almost negligible) likelihood of existence of an erroneous state.

Figure 2.2: Polarization States of a 4-dot QCA cell.(From. ref. [59])

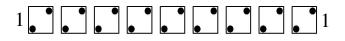

In QCA architecture information is transferred between neighboring cells by mutual interaction from cell to cell. Hence, if we change the polarization of the driver cell (left most cell also know as input cell), first it's nearest neighbor changes it's polarization, then the next neighbor and so on. Fig. 2.3 depicts the transfer of polarization between neighboring QCA cells. When the driver cell (input) is P = -1 (or P = +1), a linear transfer of information amongst it's neighboring cells leads to all of them being polarized to P = -1 (or P = +1).

Figure 2.3: Transfer of Polarization between adjacent QCA cells when the polarization changes from P = +1 to P = -1. (From. ref. [59])

As we can see, a change in polarization of the driver cell prompts all the neighboring cells to change polarization in order to attain the most stable configuration. The example illustrated in Fig. 2.3 shows how information can be transferred in a linear fashion over a line of QCA cells. Such a line of cells is used as interconnects between various QCA logic components that we will see in the following section. The speed of change in polarization of a QCA cell depends on a number of factors such as temperature, kink energy which represents the energy required to place adjacent cells in opposite polarization, clock energy which takes into account the energy from the clock to the signal and vice versa, and the quantum relaxation time which refers the minimum time required for the electrons to overlook their particular spin direction in which they are oriented.

### 2.2 Logical Devices in QCA

As seen in the previous sections, the information in QCA cells is transferred due to coulombic interactions between the neighboring QCA cells, the state of one cell influences the state of the other. The basic logic devices in QCA are:

- Binary Wires.

- Inverter.

- Majority Gate Voter

#### 2.2.1 Binary Wire

A binary wire can be viewed as a horizontal series of cells to transmit information from one cell to another. An example of a QCA wire is as shown in Fig. 2.4. A binary wire is typically divided into various clock zones, to ensure that the signal doesn't deteriorate as signals generally tend to degrade with a long chain of cells in the same clocking zone.

Figure 2.4: A binary wire which propagates information through the line. (From. ref. [44])

#### 2.2.2 Inverter

Two diagonally aligned cells will have the opposite polarization. Henceforth, inverters can be implemented with lines of diagonally aligned cells. An example of a QCA Inverter is as shown in Fig. 2.5.

Figure 2.5: An inverter which uses the interaction of diagonally aligned cells to invert bits. (From. ref. [44])

From Fig. 2.5, we can clearly observe that the signal from a binary wire splits into two parallel wires. The corner cells of the parallel wires are responsible for the change in polarization of the cells diagonal to them in the opposite direction. This causes the signal to be inverted. This anti-aligning behavior of standard cells in diagonal orientation can be useful in the implementation of the large circuits where crossover of wires is unavoidable. One can produce an inverted signal by placing a standard cell and aligning it halfway between an even and odd numbered rotated cell while placing it halfway between an odd and even numbered cell will lead to a buffered signal.

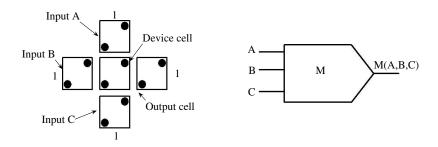

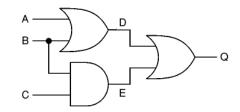

#### 2.2.3 Majority Gate Voter

Majority Gate Voter (MV) is the fundamental logic block in any QCA design. A majority gate can be built with the help of five cells. The top, left and bottom cells are inputs. The device cell in the center interacts with the three inputs and its result (the majority of the input bits) will be propagated to the cell on the right. An example of an MV representation in QCA is as shown in Fig. 2.6. The logic function implemented by the MV is

$$f(A, B, C) = A.B + B.C + C.A$$

(2.2)

Figure 2.6: A three input majority gate. The output is the majority vote of the three inputs. (From. ref. [44])

A majority gate is the basic logic gate in QCA, as it can function as an OR gate with one of the inputs fixed to 1 and function as an AND gate with one of the inputs fixed to 0.

$$MV(A, B, C) = A.B \quad when \quad C = 0 \tag{2.3}$$

$$MV(A, B, C) = A + B \quad when \quad C = 1 \tag{2.4}$$

More complex circuits like full adders and memories can be constructed hierarchically in QCA with appropriate layout.

#### 2.3 Clocking in QCA

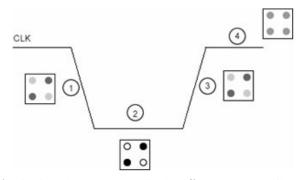

Unlike FET based circuits, QCA circuits have no predefined flow of direction of current or electrons, in a QCA circuit information tends to flow in all directions. Thus, clocking plays a very important role in the synchronization and flow of information in a particular direction. QCA circuits typically use a clock that comprises of four clocking phases. It can essentially be viewed as a pump that's constantly pumping out data sequentially. As a result of this, QCA circuits are inherently pipelined. A QCA clock induces four phases in the tunneling barriers of the cells above it. In the first phase, the *switch phase*, the tunneling barriers start to rise. The second phase, the *hold phase* is reached when the tunneling barriers are high enough to prevent electrons from tunneling. The third phase, *release phase* occurs when the high barrier starts to lower, and finally, in the fourth phase, the *relax phase*, the tunneling barriers allow electrons to freely tunnel again. In simple words, when the clock signal is high, electrons are free to tunnel. When the clock signal is low, the cell becomes latched.

Figure 2.7: The QCA clock, it's stages and it's effects on a cell's energy barriers (From. ref. [1])

Fig. 2.7 shows a clock signal with it's four phases and the effects on a cell at each clock phase. A typical QCA design requires four clock phases, each of which is cyclically 90 degrees out of phase with the prior clock phase. The first pair of cells will stay latched until the second pair of cells gets latched and so forth. In this way, data flow direction is controllable through clock phases.

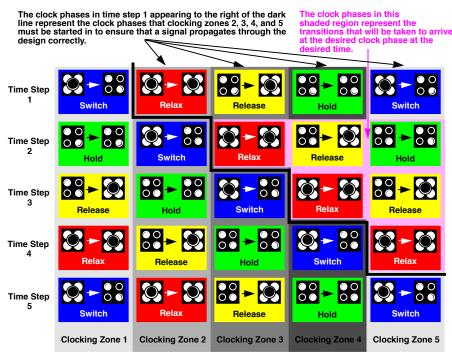

In order, to understand the actual working of a QCA clock, consider the example as shown in Fig. 2.8 where a value is being transmitted across a QCA wire. Initially, let's assume that a frozen input cell polarization with P = -1 is to be propagated through the length of the wire. Such a propagation would take place as follows where in the cells to the left of the input cell (clocking zone 1) would be in the switch phase in the first time step. As seen earlier, in this phase, the tunneling barrier will be raised and the cells will be polarized in accordance to the driver cell, here in this case, it's the input cell with polarization P=-1.

The clock phases to the left of the dark line show the propagation of a binary 0 (polarization P = -1) (assumed to come from an input cell with frozen polarization).

Figure 2.8: Example of QCA Clock Transitions (From. ref. [49])

As we step in to the second time step, we can see a changeover of the phases in the clocking zones. Clocking zone 1 will have a phase change from the switch phase to the hold phase while clocking zone 2 would change over to the switch phase. Once in the hold phase, the tunneling barriers are held high and thus clocking zone 1 will serve as input to clocking zone 2, as a result of which the cells in clocking zone 2 will be polarized in accordance to the cells in clocking zone 1.

In the third time step, the passage of the phases continues and now the clocking zone 1 will be in release phase, clocking zone 2 in hold phase and finally clocking zone 3 in the switch phase. Once in the release phase, the tunneling barrier is lowered for cells in clocking zone 1 and will be in a neutral state while clocking zones 2 and 3 interact with each other in the same manner as clocking zone 1 and 2 in the previous time step.

And in the fourth time step, clocking zone 1 would have witnessed a transition from the release phase to the relax phase, clocking zone 2 to the release phase and clocking zone 3 to the hold phase. The switch phase doesn't follow the release phase instead follows the relax phase due to the fact that the switch phase could affect the cell polarizations of the release phase. Finally, in the fifth time step, the clocking zone 1 returns to the switch phase and re-polarizes such that a new transmission could occur across the wire. At this point we can safely conclude that there is some inherent pipelining built into the QCA technology. After every 4 time steps, it is possible to put a new value onto a QCA wire [49].

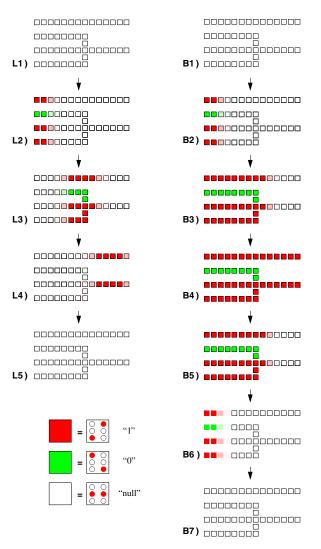

There are basically two different clocking mechanism in QCA namely Landauer and Bennett clocking [7, 38, 43, 8]. Fig. 2.9 illustrates Landauer and Bennett clocking of QCA circuits. The figure shows a QCA shift register, implemented by a single line of cells, and a three-input majority gate. The left column  $(L1)\rightarrow(L5)$  represents snapshots of the circuit at different times as it is clocked using the Landauer clocking scheme and the right column  $(B1)\rightarrow(B7)$  shows snapshots using the Bennett clocking scheme. It is assumed that the input signals come from other QCA circuitry to the left of the circuit shown and that the output signals are transported to the right to other QCA circuits [41].

Bit erasure is the simplest logically irreversible process. It is logically irreversible, in that it requires a one bit input and always returns the null state as the output, so it is impossible to recover the input value from just the output value. It has been experimentally proved that during bit erasure one needs to dissipate some amount of energy to the surroundings, and in case of an irreversible bit erasure where information is lost, then the amount of energy dissipated to the environment is always considerably larger than  $k_B Tln(2)$  [63].

Figure 2.9: Landauer and Bennett clocking of QCA circuits. Each figure represents a snapshot in time as the clocking fields move information across the circuit. The left column  $(L1)\rightarrow(L5)$  represents Landauer clocking. We can clearly observe the flow of information across the circuit as the clocking field causes different cells to switch from null to active. The circuit shown includes a shift register on top and a three-input majority gate on the bottom. The right column  $(B1)\rightarrow(B7)$  represents Bennett clocking for a computational block. Here as the computational edge moves across the circuit intermediate results are held in place. When the computation is complete (B4), there is back tracking of information, undoing the effect of the computation. This approach yield the minimum energy dissipation. (From. ref. [41])

#### 2.3.1 Landauer Clocking

All the cells are initially in the null state(L1). As the clocking signal is activated, information is propagated from left to right(L2). The clocking can be assumed to have a header and a trailer. As information is passed on from left to right, the header copies one bit to the other while the trailer erases the bit to null. Because this erasure is being done in the presence of a copy of the information (i.e., no information is being lost), it can be accomplished without dissipating  $k_BTln(2)$ . This forms the basis for reversible computation proposed by Landauer [38].

#### 2.3.2 Bennett Clocking

Bennett-clocked operation is shown in Fig. 2.9 (B1) $\rightarrow$ (B7). The difference in the Bennett clocking is the absence of trailer i.e. cells remain held in their respective active states as the information is being passed from left to right. If we consider the example of majority voter, the cells of the loser in majority voter i.e. green signal remains in the active state until the final output is computed. At that time, the output states can be copied to the next stage of computation and the clock begins to lower cells back to the null state from right to left (B4) $\rightarrow$ (B7). In this part of the cycle, erasure of intermediate results does occur but always in the presence of a copy. Thus no minimum amount of energy ( $k_BTln(2)$ ) needs to be dissipated. At the end of the back-cycle the inputs to the computation must either be erased or copied. If they are erased, then an energy of at least  $k_BTln(2)$  must be dissipated as heat for each input bit. This is unavoidable but the energetic cost of erasing each of the intermediate results have been avoided [7, 43, 8].

The Bennett clocking scheme has its own benefits and costs which are part of the design of the circuit. The principal benefit is lower power dissipation but the costs include increasing the latency to allow the forward and reverse cycles  $(B1)\rightarrow(B4)$  and  $(B4)\rightarrow(B7)$ . In addition, the amount of pipelining is reduced because for a given

block of computation only one computational edge at a time can be moving across the circuit. In Landauer clocking, by contrast, several computational waves can be traversing the same block at the same time. Finally, the circuitry that provides the clocking signal has to be somewhat more complex to handle the forward and the backward clocking of the cells [41].

#### 2.4 Wire Crossings in QCA

Wire-crossing in traditional QCA cells is done by using a "plus-sign" pattern, as shown in Fig. 2.10. The distances between a plus-sign pattern and a square pattern are exactly the same, allowing for the same Coulombic interactions between electrons in a cell. Thus, when a wire of square cells crosses a wire of plus-sign cells, they do not interact, thus the signals on each wire are preserved.

Figure 2.10: Basic Wire Crossing Technique used in traditional QCA cells (From. ref [64])

The traditional QCA circuits have relied on the coplanar wire crossing model presented but Lent et al [64], where they have proposed a unique combination of 45 degree and 90 degree crossovers. This works fine but fabrication of cells with two different orientations poses fabrication problems and also there are lots of chances of interference or cross talk owing to the weak coupling in the cells. This weak coupling makes the cells sensitive to various physical and environmental parameters such as temperature , etc. Ottavi et al [9] proposed a novel architectural design to overcome the problems posed by this weak coupling such as temperature by coming out with a more thermally robust design. They came up with three designs based on orientation of the cells, the majority gate voting and the interaction between the cells. Even though these proposed techniques was able to solve some of the design issues, there were overheads in area associated with it which is generally not preferred in a computing paradigm tipped to replace CMOS which had an efficient usage of area. Rajeswari et al tried to minimize the area overhead introduced by those complex design flows and presented the first clocking based wire crossings [23] based only on one type of cell. Even though they were successful in implementing their proposed methodology, there were few constraints with regard to the timing, where they proposed a custom eight zones based clocking scheme which reduces the computational speed.

#### 2.5 Reconfiguration in QCA

Reconfigurable computing is a computer paradigm which bridges general purpose microprocessors and application specific integrated circuits with mix of both hardware and software. It uses runtime reconfiguration to perform the intended function. This allows us to configure a hardware system to implement a particular circuit. The underlying hardware functions like an application specific hardware, thereby providing the computational performance of custom hardware. However, since the reconfiguration happens at runtime, reconfigurable computing provides the capability to re-program the underlying hardware to implement different circuits and hence approaches the flexibility of a general purpose microprocessor. This property has been exploited to rake in better performance and lower power dissipation. Before we get into the details of reconfiguration in QCA, we look into reconfiguration in nano computing and how it could help us build energy efficient systems.

#### 2.5.1 Reconfigurability and Nanocomputing

As physical limitations of feature size reduction and heat dissipation in CMOS are reached, nanotechnology provides an approach to overcome these limitation. It has been further envisioned that the amount of power dissipated in a given computational cycle will reduce drastically as we operate our circuits in the nano region. We can exploit this feature of nano-computing to come up with better energy efficient systems. Because nanotechnology could lead to inexpensive production of highly reconfigurable computer hardware, it is natural to exploit the current framework to this emerging technology. Research strongly suggests that reconfigurable architectures, if efficient, will provide a better fit and thus improved performance for general purpose computation [16, 6]. We discuss the various post CMOS and nano - computing paradigms which have been successfully implemented as a programmable device and the outcome of such an implementation in Appendix A.

#### 2.5.2 Application of Reconfiguration in QCA's

From the previous subsection, we have seen that use of programmable logic and reconfigurability in the nano scale level has led to the design of various low power and energy efficient systems which is the need of the hour. Before we get into the application of reconfiguration in QCA, we need to understand what an FPGA is and why it is easier to implement an FPGA in QCA when compared to other nanoscale devices.

FPGA's can be in general classified as a system consisting of a logic functions which are arranged in a well defined interconnect network. A typical CMOS interconnection scheme involves signals entering an FPGA circuit via some input buffers which are then transferred to horizontal wires. These horizontal wires cross with vertical wires throughout the FPGA and programmable connections can usually be made at crossings to facilitate data routing. While long wires work well in CMOS, the nature of the clock makes them a much more difficult task in QCA. Unlike the standard CMOS clock, the QCA clock is not a signal with a high or low phase which has been discussed in detail in the earlier sections.

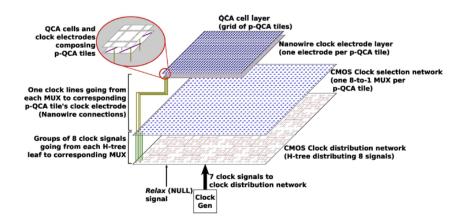

Niemer et al [50] have presented a FPGA based on QCA's where in they have tried to adhere to the design of a CMOS FPGA and tried implementing it in QCA's. They have built a logic block based on the NAND gate based Majority voter design and used a programmable multiplexor design for the interconnects instead of the common SRAM based design in CMOS. The basic problem which has been addressed is the complex routing of the clock signals involved in QCA. But this work just presents a simple implementation of QCA FPGA on the lines of CMOS FPGA. Jazbec et al [37] improved the routing and the interconnect network by proposing a Programmable Switching Matrix based on the crossing of the QCA Binary wires. There has been considerable work also done on implementing various QCA based configurable logic blocks which are based on SRAM design, Multiplexor design etc [4, 39]. They have made use of the clocking phase to their advantage to enable the crossing of two QCA binary wires. Recently Devadoss et al [24] have come up with a programmable tile based architecture based on the clocking mechanism. Simple tiles were proposed as the building blocks of this programmable QCA (p-QCA) architecture where in they have retained the 3-input majority gate as the primary logic element unlike existing architectures, which typically use 2-input NAND gates. Any part of the proposed p-QCA device can be programmed to function as a logic element, a routing element, or a memory element. A simple p - QCA device structure is as shown in Fig. 2.11

Thus, we have seen a detailed survey about the different aspects of reconfiguration which has been extended to nano computing in this section and in particular to QCA's which is the filed of interest with regard to this thesis. While we find that most of the work has been targeted on implementing a programmable design, but very few researchers have stressed upon the aspect of saving power through reconfiguration

Figure 2.11: p-QCA device structure: QCA layer with clocking circuitry. (From. ref. [24])

which forms the basis for our research. Some of the work that focussed on saving power [12, 10] and increasing computational speed through reconfiguration in nano - computing has clearly shown that power dissipation can be considerably reduced and there are many avenues available for power saving in reconfiguration. Previous work in QCA have focussed on implementing a FPGA design for QCA but significant amount of work has not been done on exploiting the clocking mechanism or the cell configuration for reconfiguration which could open up several avenues for power savings in QCA.

### CHAPTER 3

### PROPOSED RECONFIGURATION SCHEME

As seen towards the end of the previous chapter, the number of researchers who have stressed upon the usage of reconfiguration for energy efficient computing are very few but the research that has been carried out by them have given a clear indication that there are avenues for power savings. Our aim is to come upon with a reconfigurable architecture using QCA which makes use of the majority gate logic and the clocking mechanism which reduces the power considerably in comparison to the existing architectures. The major driving force behind the idea of coming up with a reconfigurable architecture in QCA is that it's a relatively unexplored topic, there are strong possibilities that a reconfigurable QCA can lead to even lesser power dissipation since both reduced power dissipation and dynamic reconfigurability is a natural phenomenon that is observed in QCA. Therefore we can quantify the power dissipated during the process of reconfiguration in QCA easily when compared to other paradigms.

As seen earlier, it's feasible to achieve substantially lower power dissipation with the help of reconfigurability in QCA cells. In this chapter, we introduce a custom QCA design based on reconfiguration where we can reconfigure the majority gate voter to perform the functionality of more than one gate i.e. by changing the polarity of the majority gate voter, the same gate can be used either as an AND gate or as an OR gate. If successful, this research could pave way for custom circuit designs which were not feasible in other computing technologies.

#### 3.1 Majority Gate Voter Reconfiguration

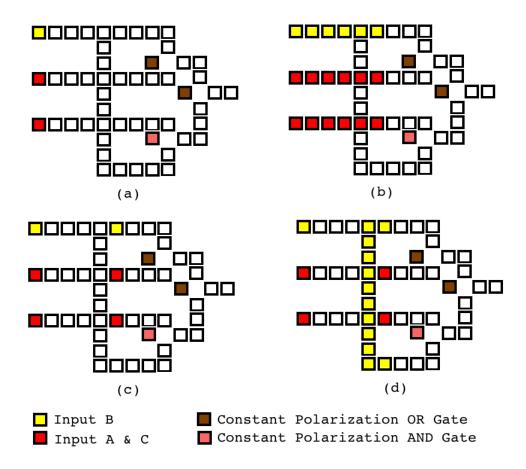

By exploiting the majority gate voter in QCA where a majority gate can be made to function as both AND and OR gate by fixing the polarization of one of the cells, we present a reconfigurable scheme where the same QCA cell is being made to function as both AND and OR gate by changing the polarization of electrons. In order to illustrate the proposed idea we use a simple conventional XOR gate which consists of AND and OR gates which are clocked using the Bennett clocking scheme. Such a design is expected to have lower power dissipation when compared to the existing schemes owing to the reversible logical computation offered by Bennett clocking.

An XOR gate can be basically viewed as a series of AND gates whose outputs are given to an OR gate. The schematic and the truth table of the XOR gate is shown Fig. 3.1 and Table 3.1 respectively.

| A  | В' | A' |   |   | D                | Y |

|----|----|----|---|---|------------------|---|

| 0  | 1  | 1  | 0 | 0 | 0                | 0 |

| 0  | 0  | 1  | 1 | 1 | 0                | 1 |

| 1  | 1  | 0  | 0 | 0 | 0<br>0<br>1<br>0 | 1 |

| _1 | 0  | 0  | 1 | 0 | 0                | 0 |

Table 3.1: Truth Table of XOR Gate

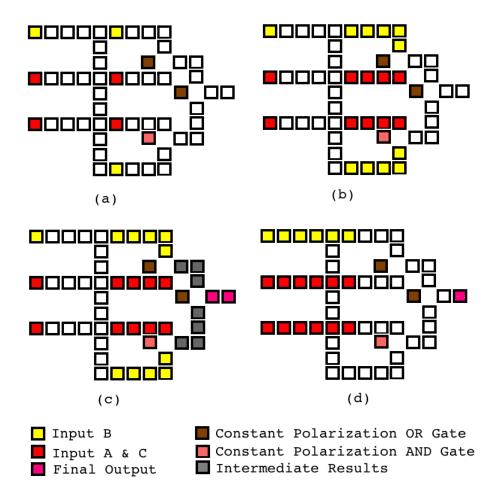

Figure 3.2: Conventional XOR Gate Design Figure 3.3: Proposed XOR Gate Design

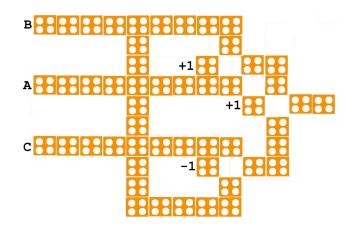

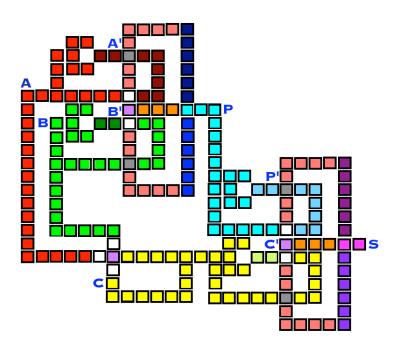

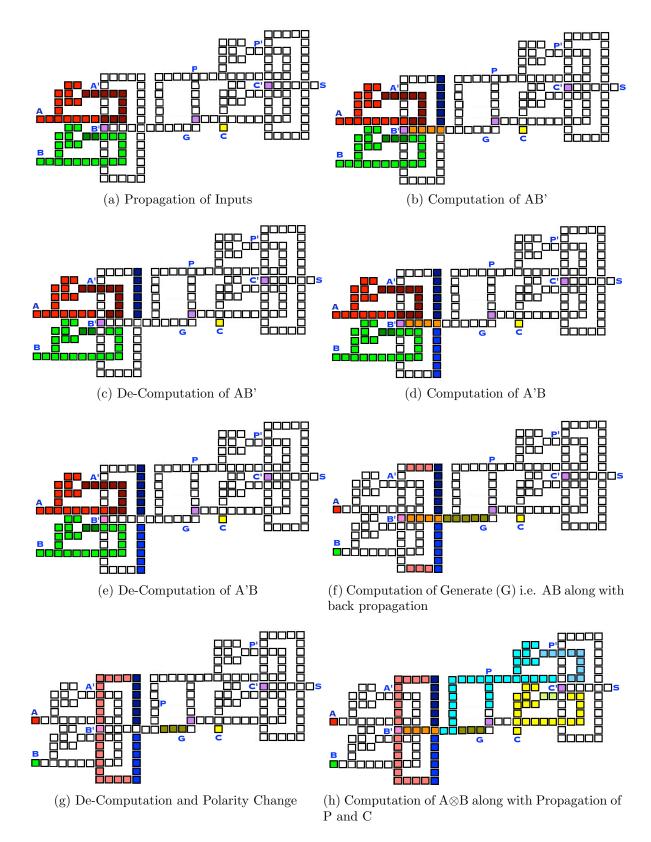

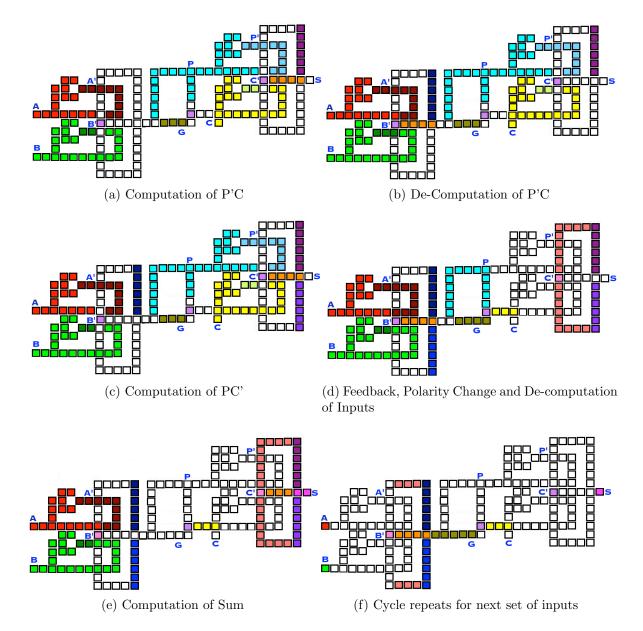

QCA implementation of a standard XOR gate is presented in Fig. 3.2. In our proposed methodology (Fig. 3.3), we find that we have only one majority gate as opposed to three majority gates in the conventional approach (Fig. 3.2). The polarization of one the inputs of the majority gate (X) can be switched from +1 to -1 and vice versa in order to switch between an AND and OR gate. The QCA representation of the proposed architecture is as shown in Fig. 3.3.

In our proposed methodology, a single majority gate voter is made to behave as both AND and OR gate. This is achieved by changing the polarity of one of the input cells to +1/-1. We compute the result of the first AND operation (i.e., C is computed as shown in the Fig. 3.4(2)) and store the intermediate results. Once the de-computation of this AND operation is completed, the second AND (i.e., D is computed as shown in the Fig. 3.4(3)) operation is performed whose intermediate results are also stored. Thus the intermediate results are stored in the series of cells forming a shift registers before the output cell Y.

During the de-computation cycle, we activate the feedback path on to the inputs and polarization of the majority gate voter is reversed in order for it to behave as an OR gate(Fig. 3.4(4)). Finally, we start output computation, along with the decomputation of the feedback path. Thus we find that, we have a stored value of the intermediate AND results which can be used as inputs as part of a large and complex circuitries along with the final XOR result (Fig. 3.4(5)).

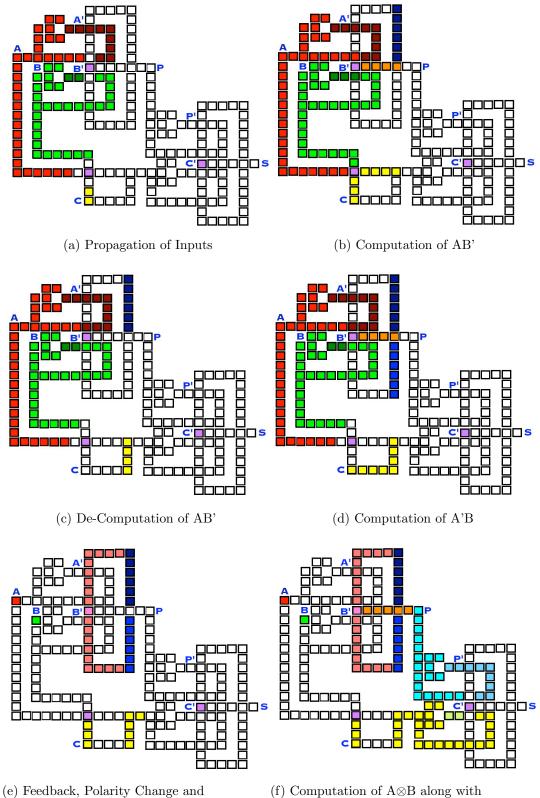

The Bennett clocking scheme of our proposed reconfiguration design is clearly indicated in Fig. 3.4. The figure represents the final state of the cells where the colors are used to indicate the presence of data in a given cell. Different colors are used for inputs, the shift registers, the majority gates, output and data propagation. The initial state of cells is assumed to be in Null state (Fig. 3.4(1)) and it's assumed that the inputs (both true and complementary form) are available and initially the majority gate voter is polarized to perform AND operation. As the computation

Figure 3.4: Clocking Scheme of Proposed Design XOR Gate Design.

- (1) Initial State of the cells

- (2) Computation and De-computation of the 1st AND operation.

- (3) Computation and De-computation of the 2nd AND operation.

- (4) Feedback and Computation and De-computation of the final result.

- (5) Final State of cells

begins the true form of input A and the complementary form of input B is fed into the cell.

As the computation progresses, the output is stored in the shift registers. During the de-computation, the inputs are restored and just the outputs are stored in the shift register whereby there is no power dissipation (Fig. 3.4(2)). Once the decomputation is completed we repeat the same procedure but with the true form of B and the complementary from of A as the inputs. If one takes a closer look at the proposed design, one can clearly find that true and complementary form of inputs are being written into the same cell. This implies that, there won't be any power dissipation since at any given point of time, we write into the input cell in the presence of a copy. At the end of computation and de-computation cycle the outputs are stored in the bottom shift register as shown in Fig. 3.4(3). Finally during the de-computation cycle, we change the polarization of the majority gate voter so that it can perform as an OR gate now instead of an AND gate. Also, the outputs are fed back as inputs. (Fig. 3.4(4)). During this computation, there is power dissipation when we tend to write the feedback data as inputs and also when we try to change the polarization of the majority gate voter. Finally, we compute the XOR output by computing the OR function of the intermediate results. Thus we find that we have the final output along with the intermediate results which can be used as fan-in to some other circuits when they are part of a large complex circuit as shown in Fig. 3.4(5).

The fundamental assumption in any reconfigurable implementation is the fact that, we have the ability to clock the cells individually. But, keeping in mind the practical constraints of such an assumption we are assuming that we can dynamically cut off the clocking to the feedback path during computation and activate it during the de-computation cycle i.e. we have restricted control over a group of cells and not over individual cells. Future research in this direction could pave way for more realistic and feasible designs.

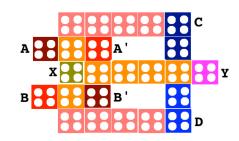

### 3.2 Wire Crossing Scheme based on Bennett Clocking

The previous section has established the proposed reconfiguration approach but in any reconfigurable system, routing is a major problem. In a QCA based reconfigurable design also, coplanar wire crossings is an area of major concern since it requires more than one cell. We have discussed in detail with regard to the drawbacks of traditional wire crossing designs in the previous chapter. In this work, we propose coplanar wire crossings based on only one type of QCA cells by taking advantage of dead time during the de-computation cycle of Bennett clocking scheme.

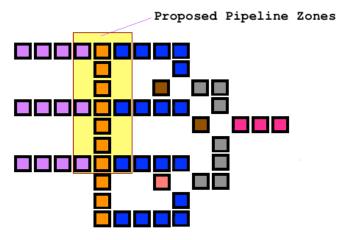

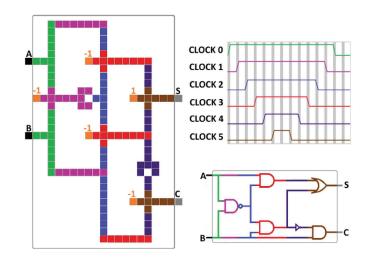

In our proposed clocking scheme, we try to take advantage of the dead time during the de-computation cycle of Bennett Clocking. We propose to break down the entire circuit into different pipeline zones [51]. The pipeline zones are under the control of the designer and may be used only where is wire crossing taking place. One of the fundamental assumptions in our design is the flow of information in both the vertical and the horizontal direction. For simplicity, let us consider a simple design which consist of AND and OR gates as shown in Fig. 3.5.

Figure 3.5: A simple circuit that implements the Boolean equation (A+B)+(B.C)

From the circuit, we can see that input B is being fed into both the AND and OR gate. This is a simple wire crossing problem in QCA. A QCA representation of the same circuit is shown in Fig. 3.6. From the figure, we can clearly see that input B

has to crossover both the inputs A and C in order to reach the other end of circuitry, this is a simple example of wire crossing on which the proposed Bennett clocking with pipeline zones is implemented.

Figure 3.6: QCA representation of a circuit that implements the Boolean equation [(A+B)+(B,C)]

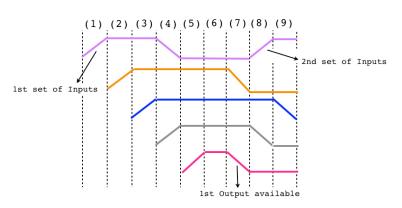

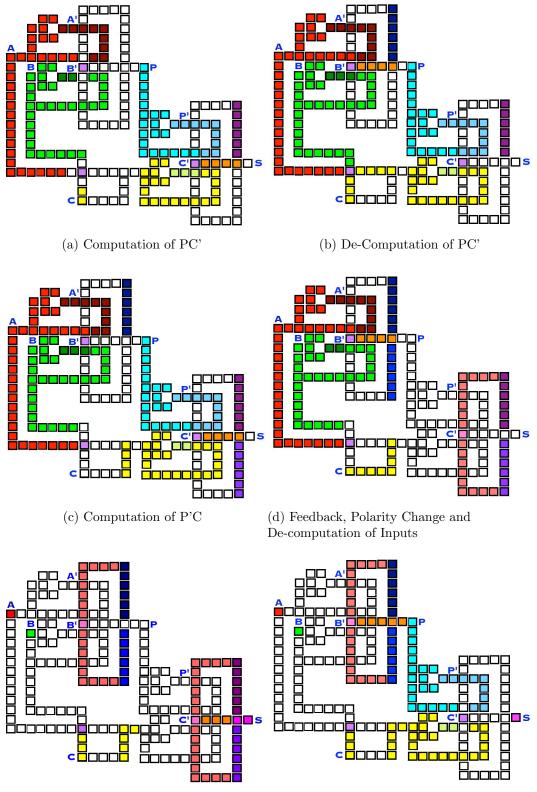

The same QCA structure along with the proposed pipeline zones and the clocking scheme is clearly shown in Fig. 3.7. From the figure, we can see the different clocks controlling the cells, there are 5 different clocks and the timing diagram of the proposed clocking scheme is as shown in Fig. 3.8. We propose to compute and decompute the data through Bennett clocking before and after the pipeline zones. The basic idea behind this implementation is that we try to clock the data till the pipeline zone and we latch it up within the zone. Once it starts to de-compute, we clock the data that needs to be propagated vertically. Thereby, we eliminate the problem of wire crossing. Once the data has crossed over, we start with the computation of the remaining part of the circuit. A detailed explanation of our proposed approach is presented below.

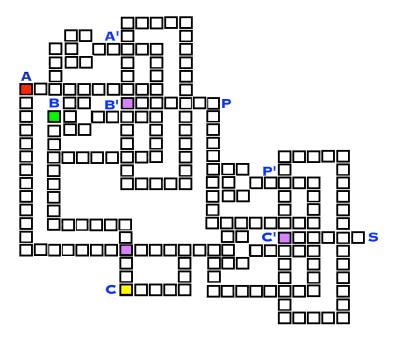

Initially we assume that all the cells are in a null state. In our approach it's assumed that we compute and de-compute on either side of the pipeline zones. In the first stage of our computation, the input data is sent until the pipeline stage where it's latched. Fig. 3.9 gives a clear picture of this implementation where the final state

Figure 3.7: Clocking Scheme of the Proposed Wire Crossing Technique

Figure 3.8: Timing Diagram of the Proposed Wire Crossing Technique

Figure 3.9: Implementation of the Proposed Wire Crossing Technique until the Pipeline Zones

of the cells is shown at the end of every clock cycle while the colors in the figure represent the propagation of data through various cells.

Initially, all the three inputs namely A, B and C are propagated until the pipeline zone which is clearly illustrated in Fig. 3.9(a) and (b). Then the input B which needs to cross over is sent through vertically as shown in Fig. 3.9(d) while the decomputation of inputs takes place (Fig. 3.9(c)). From the Fig. 3.9 we can see that 3.9(c) and 3.9(d) happen simultaneously. Once the input data are latched on in the pipeline zones, the input B begins to propagate in the vertical direction i.e. computation begins along the 2nd clock zone (Clock zones are indicated in Fig. 3.7and Fig. 3.8). During this computation, the de-computation of the inputs takes place since the inputs are already latched on in the pipeline zone which is represented by Fig. 3.9(c) and Fig. 3.9(d). Its assumed that the time taken for the computation of Input B along the vertical direction is less than or equal to the de-computation of the remaining inputs since vertical direction flow is the natural directional flow of data. In case the computation time is more than the de-computation time, then we need to wait until the computation gets over in order to start the next set of computation on the other side of the pipeline zones which are illustrated in Fig. 3.10.

Fig. 3.10 gives us a clear picture about the computation and de-computation that takes place within the proposed pipeline zone and after the proposed pipeline zone until the output. At first, the data that latched in the pipeline zone is propagated till the majority gate voting. Simultaneously the data within the pipeline zone is being de-computed as shown in Fig. 3.10(a) and Fig. 3.10(b). The computation of the data continues till the output after the intermediate results have been computed. Computation of output is done when the de-computation within the pipeline zone is in progress. Thus we have the computed output by the time, the pipeline zone has been de-computed as illustrated in Fig. 3.10(c). Finally, the new input starts propagating towards the pipeline zone while de-computation from the output until the pipeline zone starts. By the time we have latched the new data in the pipeline zone, de-computation would be complete and the next phase of computation beyond the pipeline zone can take place (Fig. 3.10(d)).

Figure 3.10: Implementation of the Proposed Wire Crossing Technique within and after the Pipeline Zones

# CHAPTER 4

# POWER ANALYSIS AND METHODOLOGY

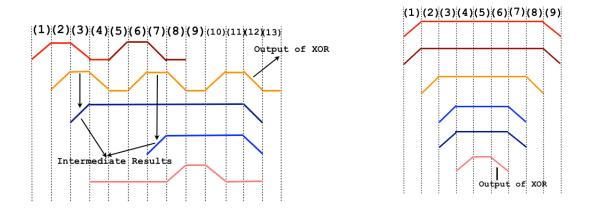

In this chapter, we present a detailed power analysis of our proposed approach and compare it with the results obtained for the existing designs. We have considered both the upper bound and lower bound limits of power in order to capture the advantages posed by our approach more accurately. Before we get ahead with the comparison of the proposed approach with the existing designs, we need to understand the upper and lower bound limits of power. The fundamental limits of upper and lower bounds of power are explained by taking an example of Bennett clocking based half adder (Fig. 4.1).

Figure 4.1: A Schematic of Half Adder along with it's QCA implementation. The required clocking signals for Bennett Clocking are shown in the graph. (From. ref [29])

## 4.1 Upper Bound Power Dissipation Model

In thermodynamics, adiabatic process refers to a process in which there is no net transfer of heat to or from the environment. Earlier researchers considered the clocking switching activity to be a quasi-adiabatic process where in a system goes through a sequence of events that are infinitesimally slow such that the entire process is reversible.

Timer et al have proposed a power dissipation model [62, 63] in general to estimate power dissipation in case of a quasi adiabatic switching event. They have presented a detailed quantum mechanical power model, where in they have showed that the power dissipation can be made as low as possible when the clock changes are nearly adiabatic. They identified three components of power: clock power, cell to cell power gain and power dissipation. Even though this model gives us a detailed physical estimates, it's computationally very intensive and difficult to calculate. The power dissipation for a QCA circuit can expressed as the sum of power estimates computed on a per-cell basis. Each cell in a QCA circuit sees three types of events: (i) clock going from low to high i.e. depolarization of the cell, (ii) input or cells in previous clock zone switching states, and (iii) clock changing from high to low, latching and holding the cell state to the new state.

The fundamental power dissipation model which computes the upper bound is based on this quantum mechanical model [58, 57]. Such upper bound represents the worst case power dissipation, which happens in the presence of non-adiabatic clocking. The authors have developed a probabilistic Bayesian model where the probabilities directly maps on to the quantum - mechanical steady state probabilities which are nothing but the density matrix and the cell polarizations. The fundamental upper bound is given by:

$$E_{diss} < \frac{h}{2} \overrightarrow{\Gamma}_{+} \cdot \left( -\frac{\overrightarrow{\Gamma}_{+}}{|\overrightarrow{\Gamma}_{+}|} \tanh\left(\frac{h|\overrightarrow{\Gamma}_{+}|}{k_{B}T}\right) +\frac{\overrightarrow{\Gamma}_{-}}{|\overrightarrow{\Gamma}_{-}|} \tanh\left(\frac{h|\overrightarrow{\Gamma}_{-}|}{k_{B}T}\right) \right)$$

$$(4.1)$$

where  $\overrightarrow{\Gamma}$  is the Hamiltonian vector,  $k_B$  is Boltzmann Constant, h represent the Planck Constant and T is the temperature.

The entire dissipation bound model has been derived in Appendix B.

Now consider the half adder circuit shown in Fig. 4.1. Since it undergoes reversible computation through Bennett clocking, the information lost in the circuit is only during the switching of inputs. Consider the truth table of the half adder shown in Table. 4.1.

Table 4.1: Truth Table of Half Adder

| А | В | S | С |

|---|---|---|---|

| 0 | 1 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

|   |   |   |   |

Now, from the above derivation we find that, the energy dissipated whenever there is a change in inputs is  $E_{diss}$  if there is no copy available. The power dissipation occurs only when we try to rewrite the input cells with the next set of inputs. From the truth table, we find that the power dissipation owing to the switching of inputs is  $4E_{diss}$ . This is obtained from the fact that the there are 4 sets of inputs possible namely [00, 01, 10, 11]. The values are rewritten as inputs four times while implementing the truth table as shown in Table. 4.1 while the rest of the times, the previous data already exists in the input registers and we don't rewrite. i.e. if there is switching from 1 to 0 or from 0 to 1, then there is power dissipation but it's not the case when there is switching from 1 to 1 or from 0 to 0. Thus we find that the upper bound of Energy Dissipation for the implementation of the presented truth table is  $4E_{diss}$ .

# 4.2 Lower Bound Power Dissipation Model

Lower bound power is the minimum amount of power that is dissipated whenever there is a computation taking place in a circuit. There are mainly two types of computation namely reversible and irreversible computation. Lower bound will differ based on the type of computation that is taking place. Any logically irreversible computation such as erasure and rewriting of inputs will have to dissipate certain amount of power. The methodology followed for the estimation of this lower bound is as suggested by Ercan and Anderson[28, 29]. The proposed methodology assumes the circuit to be an ideal circuit and heat dissipation is estimated using the physical information theoretic analysis. The fundamental lower bounds is ideally a four step process which consist of physical decomposition, process abstraction, operational decomposition and cost analysis.

The basic principle behind the computation of the bounds is to decompose the given circuitry and it's surroundings into key circuit elements which consist of information with regard to their physical states as well as their relevant external subsystems. Once the decomposition of the circuit is done, it requires the identification of the circuit states i.e. the circuit elements and the external subsystems, which interact with one another during the computational cycle.