# University of Massachusetts Amherst ScholarWorks@UMass Amherst

Masters Theses 1911 - February 2014

2013

# Online Nbti Wear-out Estimation

Mehernosh H. Dabhoiwala University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/theses Part of the <u>Computer Engineering Commons</u>, and the <u>Electrical and Computer Engineering</u> <u>Commons</u>

Dabhoiwala, Mehernosh H., "Online Nbti Wear-out Estimation" (2013). *Masters Theses 1911 - February 2014*. 1117. Retrieved from https://scholarworks.umass.edu/theses/1117

This thesis is brought to you for free and open access by ScholarWorks@UMass Amherst. It has been accepted for inclusion in Masters Theses 1911 -February 2014 by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

## **ONLINE NBTI WEAR-OUT ESTIMATION**

A Thesis presented

by

MEHERNOSH H. DABHOIWALA

Submitted to the Graduate School of the University of Massachusetts in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

September 2013

ELECTRICAL AND COMPUTER ENGINEERING

© Copyright by Mehernosh H. Dabhoiwala 2013

All Rights Reserved

# ONLINE NBTI WEAR-OUT ESTIMATION

A Thesis presented

by

## MEHERNOSH H. DABHOIWALA

Approved as to style and content by:

Wayne Burleson, Chair

Russell Tessier, Member

Sandip Kundu, Member

C.V. Hollot, Department Head Electrical and Computer Engineering

#### ACKNOWLEDGEMENTS

To begin with, I would like to sincerely thank my advisor, Prof. Wayne Burleson for all his support, faith in my abilities and encouragement throughout my tenure as a graduate student. Without his guidance, this thesis wouldn't have been possible. I am also very thankful to Justin Lu, who has been my constant tutor throughout this project. I couldn't have asked for a better teammate to work with. His focus and dedication to this project despite his own research is something I will always appreciate. I extend my gratitude towards Prof. Russell Tessier and Prof. Sandip Kundu, and would like to thank them for being on my thesis committee.

Next, I would like to thank all my wonderful current and former lab mates— Hari, Deepak, Kekai, Cory, Justin, Sandesh, Zach and Novak, for making me feel comfortable in the lab. I thank Zach for proof reading this document. I would also like to thank all my other friends that I have made over the past 2 years in Amherst, for making my stay so enjoyable. The town and its people have made my stay a truly worthwhile experience.

No acknowledgement is complete without expressing your gratitude and thankfulness towards one's family. They have always been, and will always be there through my best and worst of times. I deeply thank them for their support and faith in me. I feel truly blessed to have them in my life.

#### ABSTRACT

# ONLINE NBTI WEAR-OUT ESTIMATION SEPTEMBER 2013 MEHERNOSH H. DABHOIWALA B.E., SARDAR PATEL UNIVERSITY, INDIA M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS AMHERST Directed By: Professor Wayne Burleson

CMOS feature size scaling has been a source of dramatic performance gains, but it has come at a cost of on-chip wear-out. Negative Bias Temperature Instability (NBTI) is one of the main on-chip wear-out problems which questions the reliability of a chip. To check the accuracy of Reaction-Diffusion (RD) model, this work first proposes to compare the NBTI wear-out data from the RD wear-out model and the reliability simulator - Ultrasim RelXpert, by monitoring the activity of the register file on a Leon3 processor. The simulator wear-out data obtained is considered to be the baseline data and is used to tune the RD model using a novel technique time slicing. It turns out that the tuned RD model NBTI degradation is on an average 80% accurate with respect to RelXpert simulator and its calculation is approximately 8 times faster than the simulator. We come up with a waveform compression technique, for the activity waveforms from the Leon3 register file, which consumes 131KB compared to 256MB required without compression, and also provides 91% accuracy in NBTI degradation, compared to the same obtained without compression. We also propose a NBTI  $\Delta V_{th}$  estimation/prediction technique to reduce the time consumption of the tuned RD model threshold voltage calculation by an order of  $10^2$ with one day degradation being 93% within the same of the tuned RD model. This work further proposes to a novel NBTI Degradation Predictor (NDP), to predict the future NBTI degradation, in a DE2 FPGA for WCET benchmarks. Also we measure the  $\Delta V_{th}$  variation across the 4 corners of the DE2 FPGA running a single Leon3, which varies from 0.08% to 0.11% of the base  $V_{th}$ .

# TABLE OF CONTENTS

| ACKNOLEDGEMENTSiv                                                                       |

|-----------------------------------------------------------------------------------------|

| ABSTRACTv                                                                               |

| LIST OF TABLES                                                                          |

| LIST OF FIGURESix                                                                       |

| CHAPTER                                                                                 |

| 1. MOTIVATION                                                                           |

| 2. INTRODUCTION                                                                         |

| 2.1 Organization of the document:7                                                      |

| 3 . BACKGROUND WORK                                                                     |

| 3.1 Wear-out Sensors8                                                                   |

| 3.1.1 Delay sensors                                                                     |

| 3.1.2 Canary based sensors10                                                            |

| 3.1.3 Dummy devices based sensors11                                                     |

| 3.2 Wear-out Estimation:12                                                              |

| 4. REACTION-DIFFUSION (RD) MODEL                                                        |

| 4.1 The Reaction-Diffusion (RD) Model16                                                 |

| 4.2 Effects of PVT variations on NBTI using RD model17                                  |

| 5. ONLINE NBTI WEAR-OUT ESTIMATION TECHNIQUE                                            |

| 5.1 Time Slicing Technique20                                                            |

| 5.2 Online NBTI Wear-out Estimation Technique22                                         |

| 5.3 Results                                                                             |

| 5.3.1 Online NBTI Wear-out Estimation technique running Dhrystone benchmark on Leon 324 |

| 6. WAVEFORM COMPRESSION AND $\Delta V_{th}$ ESTIMATION/PREDICTION TECHNIQUE | 26 |

|-----------------------------------------------------------------------------|----|

| 6.1. Waveform Compression Technique                                         | 26 |

| 6.1.1 Results                                                               | 27 |

| 6.2 $\Delta V_{th}$ estimation/prediction technique                         | 29 |

| 6.2.1 Results                                                               |    |

| 6.2.1.1 Why we use logarithmic curve fitting                                | 32 |

| 6.3 NBTI degradation Predictor on Leon 3 FPGA                               |    |

| 6.3.1 Architecture                                                          |    |

| 6.3.2 Function of each blocks                                               | 40 |

| 7. DESIGN AND IMPLEMENTATION OF THE NBTI DEGRADATION PRIDICTOR (NDP)        | 42 |

| 7.1 Design of NDP                                                           | 42 |

| 7.1.1 Online Activity Monitor                                               | 42 |

| 7.1.2 $\Delta V_{th}$ Estimation/Prediction                                 | 45 |

| 7.1.3 History for NBTI $\Delta V_{th}$ estimation/prediction                | 45 |

| 7.1.4 Variation in $\Delta V_{th}$ across the FPGA                          | 49 |

| 7.2 Implementation of NDP on the Leon3 in a DE2 FPGA                        | 52 |

| 7.2.1 Altera DE2 Development and Education board                            | 53 |

| 7.2.2 Benchmarks used                                                       | 54 |

| 7.2.3 Debugger to enter the DE2 FPGA environment                            | 55 |

| 7.2.4 Loading and running the Leon3 core and benchmarks onto the FPGA board | 56 |

| 7.2.5 Displaying calculated statistics onto the debugger screen             | 57 |

| 8. RESULTS OF NDP AND MEASURING PROCESS VARIATION TECHNIQUE                 | 58 |

| 8.1 Measuring History for NBTI $\Delta V_{th}$ estimation/prediction        | 59 |

| 8.2 NBTI degradation estimation/prediction for WCET benchmark suite         | 61 |

| 8.3 Variation in $\Delta V_{th}$ across the FPGA                            | 64 |

| 9. FUTURE WORK                                                              | 66 |

| 10. CONCLUSION                                                              | 68 |

| REFERENCES                                                                  | 69 |

## LIST OF TABLES

# TABLE

| 1. $V_{th}$ degradation with Varation in Vt and T with V=0.55V                                                         | 18 |

|------------------------------------------------------------------------------------------------------------------------|----|

| 2.Vth degradation with Varation in Vt and T with V=1.1V                                                                | 18 |

| 3. Memory consumption for activity waveforms with and without COMPRESSION                                              | 29 |

| 4. 93% accuracy is achieved in $\Delta V_{th}$ , for 1 day NBTI, after $\Delta V_{th}$ Estimation/Prediction Technique | 32 |

| 5. $R^2$ values for different functions used to fit $\Delta V_{th}$ data points                                        | 37 |

| 6. $\Delta V_{th}$ history at t60 and t120                                                                             | 60 |

| 7. ΔVth-initial for 4 FPGA corners                                                                                     | 65 |

# LIST OF FIGURES

# FIGURE

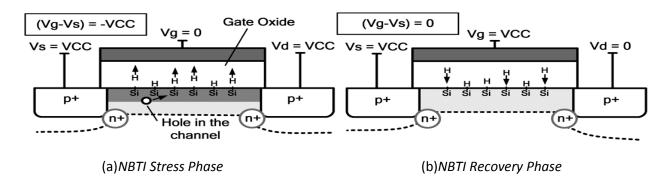

| 2-1. NBTI stress (a) and recovery (b) phases [8]                                                       | 4    |

|--------------------------------------------------------------------------------------------------------|------|

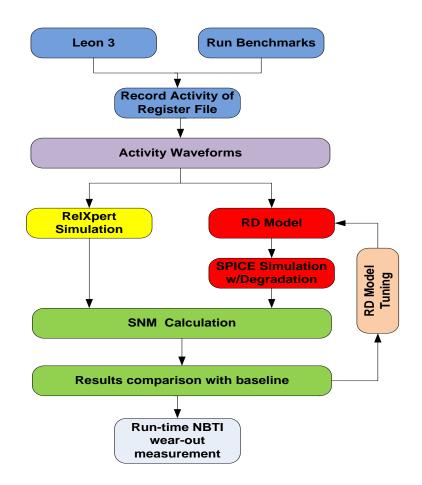

| 2-2. Flow of the proposed work                                                                         | 5    |

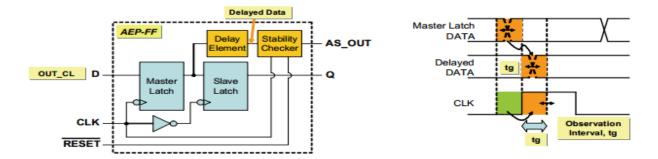

| 3-1. NBTI degradation measuring sensor placed at selected FFs [3]                                      | 9    |

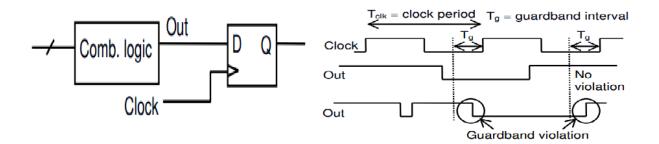

| 3-2. Detection in Change in 'Out' will be regarded as a Guardband violation [5]                        | . 10 |

| 3-3. Built-in proactive tuning system [6]                                                              | . 10 |

| 3-4. Sensor [7] and its working                                                                        | . 12 |

| 3-5. % NBTI IDDQ degradation with Vdd and T [9]                                                        | . 13 |

| 3-6. (a)Max. allowable delay of CL and FFs (b) Time borrowing by CL using setup margin of FF in the ne | ext  |

| stage [29]                                                                                             | . 15 |

| 4-1. Degradation in V <sub>th</sub> at voltage of 0.55V                                                | . 18 |

| 4-2. Degradation in Vth at input voltage of 1.1V                                                       | . 19 |

| 5-1(a). RD mechanism is frequency independent                                                          | . 20 |

| 5-1(b). RD model is frequency dependent                                                                | . 21 |

| 5-2. Time Slicing                                                                                      | . 22 |

| 5-3. Online NBTI wear-out estimation technique                                                         | . 23 |

| 5-4. SNM degradation measurement of SRAM cell [21]                                                     | 24   |

| 5-5. SNM degradation calculation for Bit 31                                                            | 24   |

| 5-6. SNM degradation for RelXpert, RD model and tuned RD model                                         | . 25 |

| 6-1. Waveform Compression Technique                                                                    | 27   |

| 6-2. $\Delta V_{th}$ degradation for RD model, compressed (retrieved using mean and SD) and compressed                    |    |

|---------------------------------------------------------------------------------------------------------------------------|----|

| (retrieved using just mean) giving an average accuracy of 91%                                                             | 28 |

| 6-3. Logarithmic nature of RD model for a square wave with 2s period and 50% duty cycle                                   | 30 |

| 6-4. $\Delta V_{th}$ Estimation/Degradation Technique for $\Delta V_{th}$ prediction after plotting few data points. Here |    |

| $y=\Delta V_{th}$ and $x=time=t$                                                                                          | 30 |

| 6-5. Curve Fitting for bit 3 for Dhrystone                                                                                | 31 |

| 6-6. $\Delta V_{th}$ for second stress phase is smaller compared to that of first                                         | 34 |

| 6-7. RD model trend for 1Hz square wave for 1 year degradation (similar to logarithmic)                                   | 35 |

| 6-8. Residuals in curve fitting                                                                                           | 36 |

| 6-9. Logarithmic function fit has 99.47% accuracy                                                                         | 37 |

| 6-10. Proposed design of NBTI Degradation Predictor on the Leon 3 FPGA                                                    | 39 |

| 6-11. Proposed NDP module Architecture                                                                                    | 40 |

| 7-1. Inserting our Activity Monitor in the Leon3 VHDL core                                                                | 43 |

| 7-2. Register File Activity Monitor design flow                                                                           | 44 |

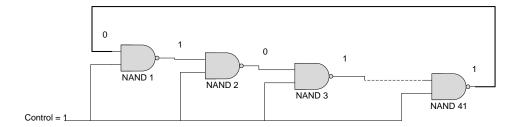

| 7-3. NAND gate closed loop circuit working as RO                                                                          | 46 |

| 7-4. NAND gate closed loop circuit which holds a value                                                                    | 46 |

| 7-5. Chip Planner in Altera II Quartus showing the RF and the RO placed next to it                                        | 47 |

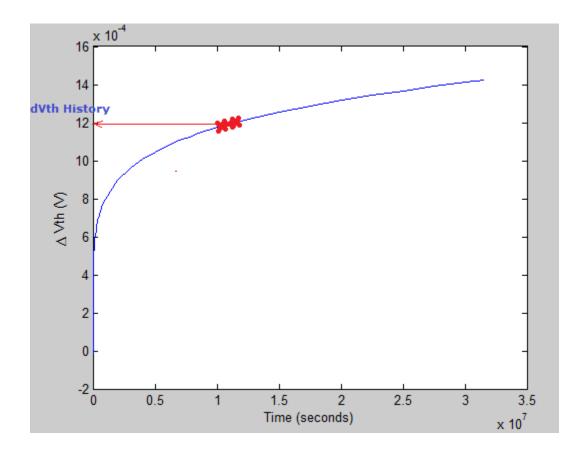

| 7-6. Matching r0-60 with the 1Hz RD model degradation curve                                                               | 49 |

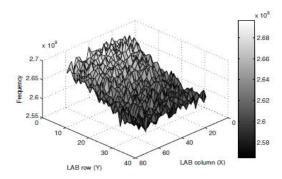

| 7-7. The observed frequency of each RO in a single EP2C35 device [34]                                                     | 50 |

| 7-8. Finding $\Delta_{Vth-inital}$ across the 4 corners of the FPGA                                                       | 52 |

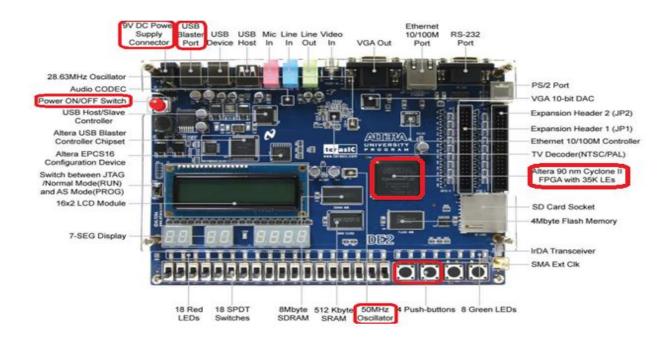

| 7-9. Layout of Altera DE2 Development and Education Board [39]                                                            | 53 |

| 7-10. Debug window using Aeroflex Gaisler GRMON2 debugger                                                                 | 56 |

| 7-11. Register window 7 using the debugger                                                                                | 57 |

| 7-12. Shadow Register displaying statistics in the register window                                                        | 58 |

| 8-1. Matching r0-60 with the 1Hz RD model degradation curve                                   | . 60 |

|-----------------------------------------------------------------------------------------------|------|

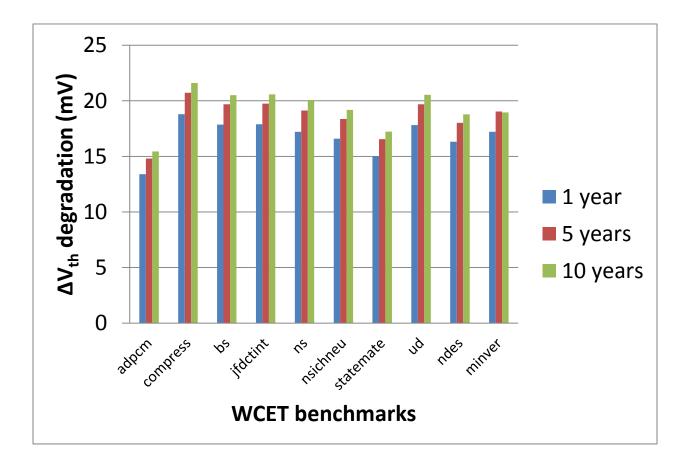

| 8-2. NBTI degradation for bit 0 of the Leon3 register file                                    | . 62 |

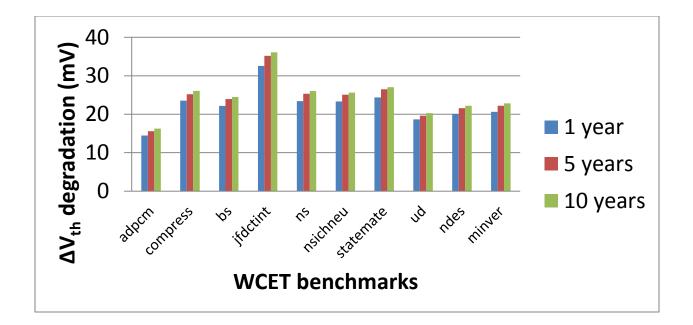

| 8-3. NBTI degradation for bit 31 of the Leon3 register file                                   | . 63 |

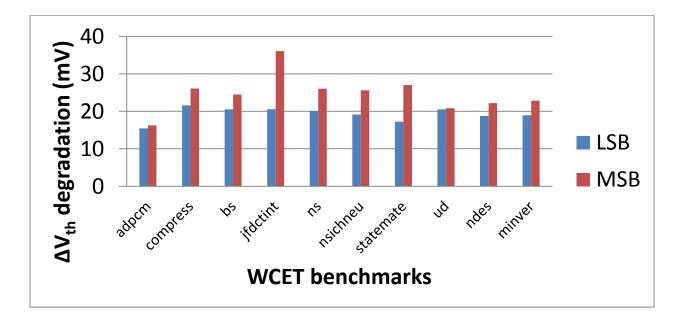

| 8-4. NBTI degradation LSB and MSB of the Leon3 register file for 10 years                     | . 64 |

| 8-5. Frequency and $\Delta V_{th}$ degradation of the ROs placed in the 4 corners of DE2 FPGA | . 64 |

| 8-6. Technique to match the rate of the RO degradation with 1HZ RD model degradation curve    | . 65 |

| 9-1. A technique to bring the average ZBP to 0.5                                              | . 67 |

#### **CHAPTER 1**

#### MOTIVATION

Continuous transistor scaling leads to an increase in current density and temperature, which results in high on-chip wear-out. This wear-out results in need for wear-out sensing or wear-out estimation. Sensing can be characterized using delay, canary and dummy devices (discussed in Section 3.1). Delay sensors [1-5] provides a continuous aging report of the module they monitor. They only work well for combinational logic and fail to provide wear-out information for storage units like SRAM cells. Canary based [6] and dummy device based [7] wear-out sensors provide just a binary report, and not one during the course of degradation for carrying out some management to slow down wear-out and prolong the lifetime of the device. Thus wear-out estimation becomes necessary for wear-out management.

Negative Bias Temperature Instability (NBTI) is the main reliability concern for CMOS circuits [28]. The Reaction-Diffusion (RD) model [1] (explained in Section 4.1) is a widely used model NBTI prediction. To the best of our knowledge, no work has been done to explain how the RD model is implemented. This work proposes to use the RD model to predict NBTI degradation on the register file of a Leon3 processor. The same analysis is performed using the Ultrasim - RelXpert simulator [22], which is regarded as the baseline. Comparing these results would give an idea of how accurate the RD model is. Results from this more time consuming simulator are used to tune the RD model and calibrate its results. Using design time simulation tools, such as RelXpert, at run-time is slow and impracticable. The RD model, based on run-time waveforms, has the potential to be fast and feasible.

1

Run-time wear-out prediction requires the run-time activity information to be stored at run-time which increases the cost and complexity. This work presents a novel *waveform compression* technique which minimizes the memory cost from 256MB to 131KB for a Leon 3 processor register file.

Wear-out occurs over a long time period. The RD model cannot be used to calculate the threshold voltage degradation due to NBTI over a long time period , as it would take a long time to simulate the equations (presented in Section 4), say in hours, which is infeasible at run-time and would degrade the system performance. In this work a novel  $\Delta V_{th}$  estimation/prediction technique is proposed, which would not require the RD model to run for the length of the degradation, but only for a fraction of the time, to provide an accurate degradation result. This work shows that for the Dhrystone benchmark running on a Leon3 processor,  $\Delta V_{th}$  Estimation/Prediction Technique would reduce the run-time NBTI prediction by an order of 10<sup>2</sup> with 93% accuracy, compared to the tuned RD model, for a period of one day.

To the best of our knowledge no online NBTI predictor has been designed which can predict the future NBTI  $\Delta V_{th}$  degradation on a real system. This prediction can be used to do task management which can reduce the future degradation and increase the system's lifetime. Here we design a novel NBTI Degradation Predictor (NDP) running on a Leon3 in a DE2 FPGA. This predictor is designed to predict the future  $\Delta V_{th}$  degradation of the Leon3 register file cells. This design also shows how we can measure the actual on-chip degradation history of the Leon3 register file, which is necessary for implementing the RD model. This prediction can be used to estimate how the processor would behave in coming years, and necessary management steps can be taken to prevent it from crashing. Lastly, we present a novel technique to measure the process variation across the 4 corners of the DE2 FPGA, running a Leon3 processor, using ring oscillators.

2

#### CHAPTER 2

#### INTRODUCTION

Microprocessors have been designed with worst case operating conditions in mind, and manufacturers have employed guardbands to make sure that the processors will meet a predefined lifetime qualification. However shrinking feature size has made process variation extremely difficult to mitigate simply by provisioning for the worst case. This makes a necessity for designers to provide on-chip wear-out sensors [1-7] or perform out wear-out estimation [9,10]. These sensors provide fresh online wear-out data over a period of time. The run-time degradation can be estimated using degradation models, like the RD model, which are faster than simulation tools, and can work with activity data. Negative Bias Temperature Instability (NBTI) is the main reliability concern which limit a circuit's lifetime [28]. Storage devices, like the register file, have a biased value at the input of its PMOS transistors for a quite long time, which results in more NBTI degradation.

In CMOS fabrication, during the hydrogen passivation process that follows oxidation, dangling Si bonds are transformed into Si-H bonds. These bonds are weak enough to break during device operation, causing H atoms to diffuse into gate oxide, and the broken bonds that remain become traps (called interface traps), effectively degrading the drive current of PMOS transistors. NBTI is caused by this trap generation in the Si–SiO<sub>2</sub> interface of PMOS transistors. Structural mismatch at the Si-SiO<sub>2</sub> interface causes dangling bonds, which act as interfacial traps. NBTI is characterized by a positive shift in the absolute value of the PMOS threshold voltage  $|V_{tp}|$ , which occurs when the device is stressed ( $V_{gs}$ = -VCC). When the stress conditions are removed (i.e.  $V_{gs}$ =0), the device enters a recovery phase, where H atoms diffuse back towards the Si–SiO2 interface and anneal the broken Si–H bonds, thereby reducing  $|V_{tp}|$ [Fig. 2-1(a) and (b)]. It has been observed that NBTI can increase  $V_{th}$  by as much as 50mV for devices operating at 1.2V or below [11] and the circuit performance degradation may reach upwards of 20% in 10 years [12]. When the input of the PMOS is '0', i.e.  $V_{gs}$ = -VCC, it is on and  $|V_{th}|$  increases, which is known as the stress phase. When its input is '1', i.e.  $V_{gs}$ =0, it is off and  $|V_{th}|$  decreases, which is known as the recovery phase.

Figure 2-1. NBTI stress (a) and recovery (b) phases [8]

The Reaction-Diffusion (RD) Model [8], is a predictive NBTI model used to predict the effect of NBTI in the form of an increase in the Threshold Voltage ( $V_{th}$ ). It provides two equations (mentioned in Section 4.1) to calculate  $V_{th}$  change during multiple NBTI stress and recovery periods.  $V_{th}$  is believed to exhibit a power-law dependency on time and is an exponential function of the stress voltage level as well as temperature. The RD model is discussed in section 4.1.

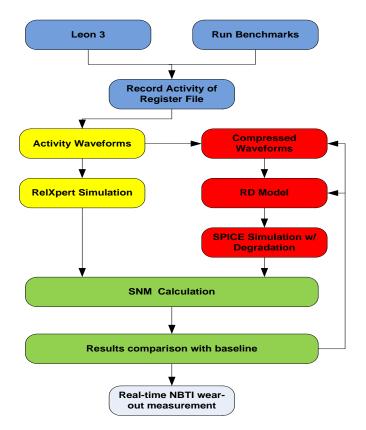

A question arises. How accurate is this model? If it is not accurate, how do we improve the model to capture the actual degradation? This work first proposes to compare the performance degradation due to NBTI wear-out, obtained from the RD model and RelXpert [22], the inbuilt reliability simulator in Ultrasim. This is carried out by monitoring the activity of the register file by running Dhrystone benchmark on a Leon3 processor. The reliability simulator, RelXpert, uses the same RD model for carrying out NBTI calculations. The RD mechanism is frequency independent [16], but the RD model is frequency dependent, which questions its accuracy and needs to be tuned. Our proposed tuning

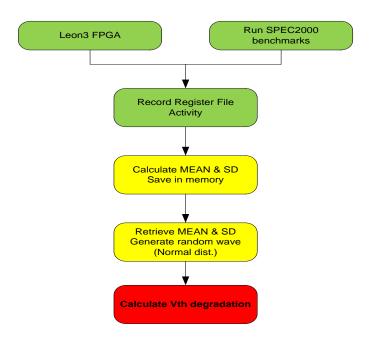

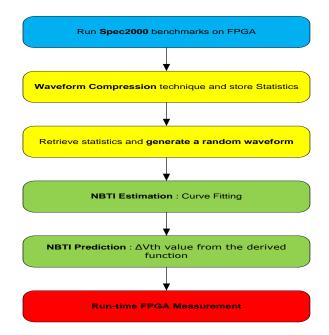

method is mentioned in Section 5. The RD model is tuned, using a *time slicing technique*, to match the RelXpert simulator. The tuned RD model can be used to perform wear-out management on the Leon 3 processor. Figure 2-2 shows the flow of the proposed work. This method provides 80% accuracy with respect to the RelXpert simulator and is also 8 times faster than the simulator.

Figure 2-2. Flow of the proposed work

The next question is - "What is the performance and cost of the above proposed technique?" While monitoring the activity of the register file, the waveforms need to be stored into memory which would increase the cost. Also running the RD model to predict a long term V<sub>th</sub> degradation could affect the runtime performance.

Monitored register file activity waveforms need to be stored in memory to carry out NBTI wear-out estimation. Storing these activity waveforms from a 256 32-bit register file in Leon3 in memory is very

costly. Thus we develop a *waveform compression technique* which stores only the statistics, mean and standard-deviation (SD), of the activity waveforms which occupy 131KB memory instead of 256MB (for Dhrystone benchmark running once, i.e. 58ms), and at the same time provide 91% accuracy with respect to the tuned RD model. To predict the long term degradation, say 1 day, running the RD model is infeasible due to the huge amount of time it takes. For Dhrystone benckmark running on Leon3, it takes nearing 4 hours to predict  $\Delta V_{th}$  of a single bit, for 1 day prediction, using the tuned RD model. So we come up with a  $\Delta V_{th}$  estimation/prediction technique that can predict the threshold voltage degradation due to NBTI, running the RD model just for a small duration of time. We show that our technique is faster than the RD model, running for a time period of 1 day, by an order of  $10^2$  with 93% accuracy (93% within the tuned RD model results).

The above proposed techniques need to be implemented online on a real system. Predicting what is going to happen ahead would allow the system to carry out online task management which can reduce the future degradation and increase it's lifetime. For example, in a 4-core multi-core system, from its current degradation characteristics, core-2 predicts a high future degradation which would hamper its lifetime. So the system can allocate the tasks of core-2 to another core, say core-4, whose future degradation prediction is less.

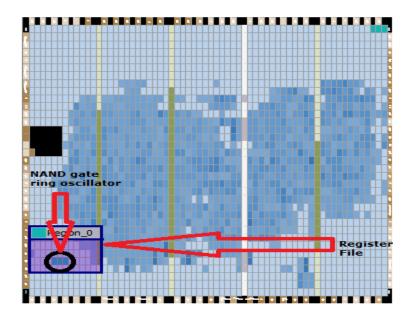

This work also proposes to implement a NBTI degradation predictor on Leon 3 in a DE2 FPGA that carries out waveform compression, and  $\Delta V_{th}$  estimation and prediction, to predict the future NBTI  $\Delta V_{th}$  degradation, for the WCET benchmark suite [39]. We compare the NBTI degradation of the Leon3 register file bits, MSB and LSB, by running WCET benchmarks. We will see that the WCET benchmarks result in an average of 19.39mV NBTI degradation for LSB and 27.75mV for MSB, over a period of 10 years, for the Leon3 register file. We obtain the  $\Delta V_{th}$  history by placing 41-stage NAND gate ring

oscillators besides the Leon3 register file in a DE2 FPGA, and measuring the worst case NBTI degradation.

We know that there process, temperature and voltage variations exist across any chip. Process variations are due to variation in manufacturing process. This variation problem is a big concern for technology beyond 90nm [33], and it gets worse with scaling. Here we present a method to measure the initial  $\Delta V_{th}$  across the four corners of the DE2 FPGA running a single Leon3 core. We achieve a 0.08% to 0.11% variation in  $\Delta V_{th}$ , from the base  $V_{th}$ , across the four corners of the FPGA.

## 2.1 Organization of the document:

The rest of the document is organized as follows. Section 3 describes the background of NBTI wear-out sensing and estimation. The RD model and the Time Slicing technique are explained in Section 4 and Section 5 respectively. Section 6 explains the novel waveform compression and  $\Delta V_{th}$  estimation/prediction techniques, and discusses the proposed work for defense, i.e. designing and implementing the NDP on a Leon3 processor in a DE2 FPGA. Section 7 discusses the design and implementation of the NDP and measuring the process variation across the FPGA; while Section 8 discusses its results. Section 9 and 10 are future work and conclusion respectively.

#### CHAPTER 3

#### **BACKGROUND WORK**

Feature size scaling has resulted in considerable gains in area and performance, but it has come at a cost of reliability. Reliability budgeting can no longer be considered an afterthought and should be considered as important as power and area by the designer. Technology shrinking has caused a considerable increase in power density and temperature. Thus wear-out sensing or wear-out estimation should be considered.

## 3.1 Wear-out Sensors

Various wear-out sensors have been designed to measure the on-chip degradation. They can be classified into delay, canary based and dummy device sensors. The following sub-section discusses these wear-out sensors.

#### 3.1.1 Delay sensors

Delay sensors measure the on-chip wear-out using the performance degradation metric as 'delay'. Maximum wear-out sensors come into this category. This sub-section describes two of them.

An adaptive error prediction flip-flop architecture with built-in aging sensor is proposed in [3], performing on-line monitoring of long-term performance degradation of CMOS synchronous digital circuits in 65nm CMOS technology. The sensor is out of the signal path. Performance error prediction is implemented by the detection of late transitions at flip-flop data input, caused by NBTI. It also shows that the impact of aging degradation and/or PVT (process, power supply voltage and temperature) variations on the sensor enhance error prediction. Such sensors are inserted at selected Flip-flops (FF) on the chip. Figure 3-1 represents the proposed design in [3]. The delay element introduced an observation (or guard-banding) interval, t<sub>g</sub>, at the end of the clock cycle. With the sensor's architecture,

its sensitivity (measured by t<sub>g</sub>) increases with its PVT variations. This way, the sensor FF will adapt and increase the guard-band, as circuit variability increases with aging.

Figure 3-1. NBTI degradation measuring sensor placed at selected FFs [3]

As shown in Figure 3-1, the Delay Element (DE) delays data signals captured at the Master Latch output, during the CLK low state. The Stability Checker (SC) analyzes data transitions during the CLK high state. The DE propagation delay is the effective observation (or guardband) interval, t<sub>g</sub>, used by the sensor. Late transitions at the FF data input (propagated to the Master Latch output) will be identified by the SC.

A mechanism of detecting degradation in delay due to NBTI (in 90nm and 65nm technologies), by placing sensors in selected Flip Flops across the chip is proposed in [5]. This design provides an initial short guard banding interval to the circuit design. Figure 3-2 shows the idea behind the design. The output of a combinational logic is fed to the input of the flip flop. If there is a transition in the combinational logic's output during the guardbanding interval,  $t_g$ , it results in guardband violation, and an error is detected. There is a stability checker inbuilt into the FFs which checks whether guardband violation has occurred or not. As shown in Figure 3-2, if the stability checker senses a transition during the guardbanding interval,  $t_g$ , error is detected.

Figure 3-2. Detection in Change in 'Out' will be regarded as a Guardband violation [5]

#### 3.1.2 Canary based sensors

Canary circuits degrade faster to provide an early warning alarm for wear-out.

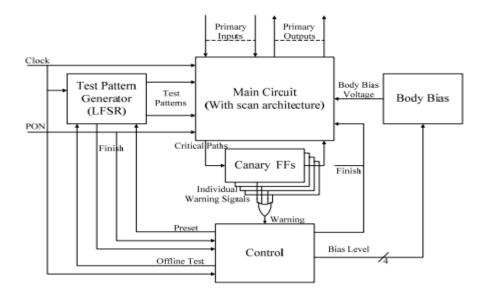

A Built-In Proactive Tuning (BIPT) System consisting of the existing main circuit augmented with a Test Pattern Generator (TPG), Body Bias Circuitry, Canary Circuit and Control circuit is proposed in [6]. At power-on or periodically, the BIPT system can launch test vectors from the Test Pattern Generator (TPG) and then tune the circuit body voltage according to the observations from the canary circuit. The canary circuit plays the role of predicting aging-induced performance degradations. A warning signal is generated by the canary flip-flops when the timing constraint is tight on one or more of the few critical paths where these circuits are inserted. The top-level warning signal is the OR of all the individual canary flip-flop warning signals. The control circuit is used to generate control signals to tune the body bias of the main circuit. Compared to DVS, BIPT can achieve the same aging resilience with about 30% less power dissipation. Figure 3-3 shows the BIPT design.

Figure 3-3. Built-in proactive tuning system [6]

#### 3.1.3 Dummy devices based sensors

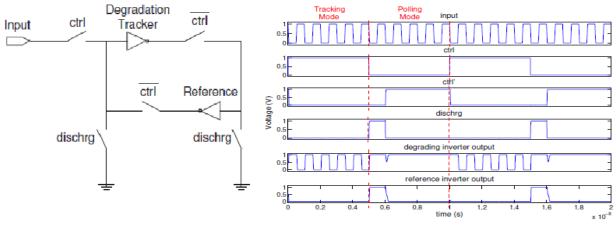

Some sensors [7] are designed having dummy devices. When the main device gets worn-out, the dummy device comes into picture, like the degradation tracking inverter gets worn out switches to the reference inverter in Figure 3-5. This switch in device can indicate NBTI degradation.

This design (as shown in Figure 3-4(a) [7]) is similar to the design of a SRAM cell. Here two inverters are cross-coupled with one having a stronger PMOS than the other. The inverter with a stronger PMOS (by  $\Delta$ I%) is called the tracking inverter and the other is called reference inverter. During normal operation, a critical path signal is fed into the design with the degradation inverter disconnected from the reference inverter through the pass-transistor with input CTRL(bar). This mode of operation is called tracking mode. This mode degrades the PMOS of the tracking inverter, due to NBTI, and makes it weak. When the PMOS of the tracking inverter becomes weak than the one of the reference inverter, due to NBTI, the circuit switches and the reference inverter starts working. During polling mode the input is disconnected from the tracking inverter and the two inverters are cross-coupled. If the PMOS of the tracking inverter and the one of the reference, the tracking inverter will pull the

reference inverter down. In the opposite case the reference inverter will pull the tracking inverter down. Figure 3-4(b) shows the Timing Diagram of the signals in the two modes in 65nm technology.

## 3.2 Wear-out Estimation:

Delay sensors provide a continuous aging report of the module they monitor and they only work well for combinational logic. They fail to provide wear-out scenario for storage units like SRAM cells. Canary based and dummy device based wear-out sensors provide just a binary report, i.e. a device reaches the degradation limit or not. The warning does not occur during the course of degradation to assist carrying out management to stop wear-out. Implementing the run-time wear-out models with run-time waveforms would give us very accurate information about the current scenario of the on-chip wear-out. Also, implementing run-time wear-out models is much faster than implementing design-time tools. In Section 5.3 we show that RD model, which is a widely used run-time wear-out model, is 8 times faster than design-time RelXpert simulator, for Dhrystone benchmark running on a Leon 3 processor.

Wear-out estimation can be used to predict wear-out in order to start doing management to overcome it. To the best of our knowledge, very little work has been done on wear-out estimation, and the work done does not into account the online on-chip degradation.

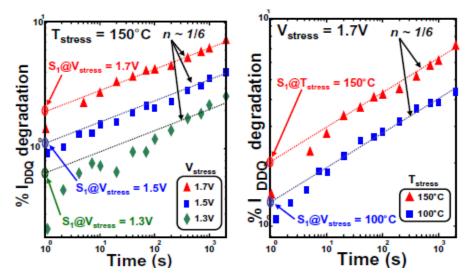

The temporal NBTI degradation in static noise margin (SNM) of an SRAM array and  $f_{MAX}$  of random logic circuits are highly correlated to the standby leakage current ( $I_{DDQ}$ ) measurement, and this relationship can be used to predict long term circuit reliability [9]. This reference proposes an efficient NBTI characterization technique based on the  $I_{DDQ}$  measurement. Since increase in threshold voltage ( $V_{th}$ ), due to NBTI, decreases  $I_{DDQ}$ , this information can be used to carry out on-chip wear-out prediction. A test chip is fabricated in 130nm 1.2V CMOS technology and a simple 1000 stage inverter chain was selected as target circuitry. NBTI stress was controlled by both voltage and temperature. During stress period, the input to the PMOS in the inverter chain is  $V_{in}=V_{stress}=1.7V$ , 1.5V, 1.3V (Figure. 3-5). During  $I_{DDQ}$ measurement  $V_{in}$  is set to 0, so that the leakage can be measured.  $V_{in}$  is flipped back to  $V_{stress}$  after the 0.2s measurement period.

Figure 3-5. % NBTI I<sub>DDQ</sub> degradation with Vdd and T [9]

SNM degradation of SRAM assuming the input storage nodes of an SRAM being stressed at 50% signal probability is measured [9]. It shows that there is a 53mV V<sub>th</sub> degradation after a period of 3 years.

A gate level simulation methodology which can accurately model NBTI degradation of digital circuits is developed in [10]. The research shows that their proposed model can be almost as accurate as the PTM NBTI models [27] developed at Arizona State University. It presents a two-state model for circuits having PMOS transistors parallel and connected to the supply (example, NOT and NAND), and a three-state model for circuits having PMOS transistors in a stack (example, NOR). Here the model is implemented for various ISCAS'85 and MCNC'91 circuits, having an input of f=1GHz at T=100°C and VDD=1.2V. The proposed model is validated for an inverter in 45nm, 65nm and 90nm technology nodes, for a period of 10 years, at different temperature and duty cycles.

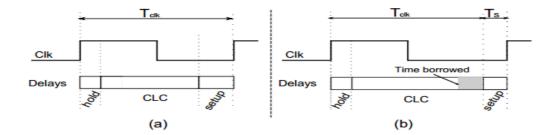

In both [9] and [10], no use of run-time waveforms (input/activity) has been made which is necessary to obtain the real picture of NBTI degradation on a core. Also, these works have not been done online. Carrying out degradation prediction offline would require the user to bring the device to a service station every time the degradation needs to be predicted increasing the burden on the user. The current degradation characteristics need to be extracted, from the device being tested. This extraction would increase the time consumption and prediction cost. Reference [29] presents ReverseAge, an online NBTI combating technique. Suppose there are few combinational logic circuits separated from one another by flip-flops. If any of the combinational logics fail to meet the setup time of its successive flip-flop, a warning alarm rings. This delay is due to NBTI degradation. Figure 3-6 shows how this problem is solved using time borrowing.

14

Figure 3.6 (a)Max. allowable delay of CL and FFs (b) Time borrowing by CL using setup margin of FF in the next stage [29]

Time borrowing is performed by relaxing the setup time of the succeeding FF, i.e. shifting the edge later as shown in Figure 3-7(b). The time (Ts) represented by the shaded block is the time borrowed from the succeeding stage and is achieved by shifting (i.e. delaying) the clock rising edge into the FF of the next stage. This technique carries out NBTI sensing but does not predict the future degradation. Predicting the NBTI future would allow the system to carry out NBTI management, like task migration in a multicore architecture. This will not overcome degradation, but stop it from occurring at the first place.

In this work, we propose to make use of run-time register-file activity of Leon3 in a DE2 FPGA [24] by running various SPEC2000 benchmarks, to predict online the future NBTI degradation.

#### **CHAPTER 4**

## **REACTION-DIFFUSION (RD) MODEL**

The Reaction-Diffusion (RD) model is one of the widely used wear-out models used to predict NBTI degradation over a period of time. It is designed based on the Reaction-Diffusion process which takes place during stress of a PMOS transistor. As discussed in Section 2, a PMOS is stressed when its gate-source input,  $V_{gs}$ = -VCC, and recovered when  $V_{gs}$ =0V.

#### 4.1 The Reaction-Diffusion (RD) Model

The RD model [8] helps us predict the NBTI degradation over a period of time. Equations 1 & 2 show us the stressed V<sub>th</sub> and recovered V<sub>th</sub> respectively. The two critical steps that occur in NBTI degradation over time are Reaction and Diffusion. Reaction is where some Si–H or Si–O bonds at the substrate/gate oxide interface are broken under the electrical stress. The holes trigger this reaction. Consequently, interface charges are induced, which cause the increase of  $V_{th}$ . In diffusion reaction-generated species diffuse away from the interface toward the gate, driven by the gradient of the density.

$$K_{v} = \left(\frac{q \times t_{ox}}{\varepsilon_{ox}}\right)^{3} K_{1}^{2} C_{ox} \left(V_{gs} - V_{th}\right) \sqrt{C} \exp\left(\frac{2E_{ox}}{E_{01}}\right)$$

$C = \exp\left(\frac{-\operatorname{E}_a / kT}{T_0}\right)$

where *t* is the time a which the stress and recovery periods end,  $t_0$  is the time at which the stress period begins and  $t_1$  is the time at which the recovery period begins.  $n = \frac{1}{6}$ ,  $t_{ox}$  is the oxide thickness and  $t_e = t_{ox}$ .  $\delta$ ,  $\xi_1$  and  $\xi_2$  are constants.

## 4.2 Effects of PVT variations on NBTI using RD model

NBTI is a time-dependent degradation, but this section presents how the process, voltage and temeperature parameters effect it. The  $V_{th}$  stress and recovery equations (1 & 2) from RD model, have the initial P, V and T parameters which can be varied and their effect can be studied.

Here we measure the worst and best corners of P, V and T for NBTI wear-out. We provide a stress time of 80us and a recovery time of 20us to equations 1 & 2 (in Section 4.1). The degradation is measured after 1, 2, 3 and 4 days. Equations 1 & 2 are implemented in Matlab [26].

Results were measured with:

- T at 25°C and 100°C

- Vt varying ±20%

- V at 1.1V and 0.55V

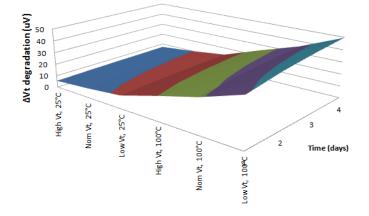

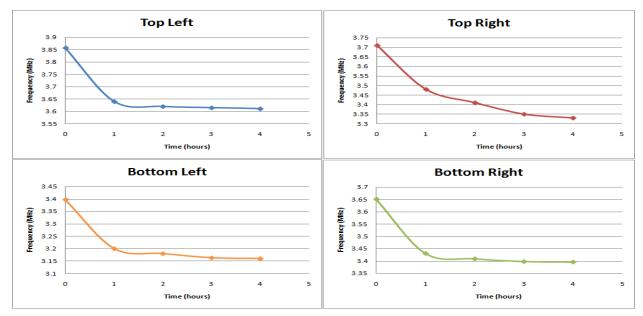

Tables 1 & 2 and Figures 4-1 & 4-2 show the the variation in  $V_{th}$  degradation with variation in V, T and  $V_t.$

Table 1. presents the  $V_{th}$  degradation values achieved for time period of one day to four days under different initial  $V_t$  and temperature values at a supply of 0.55V. From Figure 4-1. we see that maximum  $V_{th}$  degradation is achieved at low initial  $V_t$  and high temperature.

| Time (days) | High Vt,  | Nom Vt,   | Low Vt, 25°C | High Vt,   | Nom Vt,    | Low Vt,    |

|-------------|-----------|-----------|--------------|------------|------------|------------|

|             | 25°C (uV) | 25°C (uV) | (uV)         | 100°C (uV) | 100°C (uV) | 100°C (uV) |

| 1           | 5.51      | 7.83      | 10.9         | 19.89      | 28.26      | 39.35      |

| 2           | 6.2       | 8.81      | 12.26        | 22.3       | 31.7       | 44.2       |

| 3           | 6.64      | 9.43      | 13.13        | 23.9       | 34         | 47.3       |

| 4           | 6.97      | 9.9       | 13.8         | 25.1       | 35.7       | 49.66      |

Table 1.  $\,V_{th}$  degradation with Varation in Vt and T with V=0.55V

## Degradation in Vth at input voltage of 0.55V

Figure 4-1. Degradation in  $V_{th}$  at voltage of 0.55V

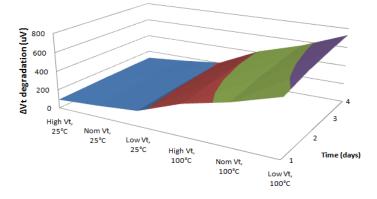

Table 2. presents the  $V_{th}$  degradation values achieved for time period of one day to four days under different initial  $V_t$  and temperature values at a supply of 1.1V. From Figure 4-2. we can say that maximum  $V_{th}$  degradation is achieved at low initial  $V_t$  and high temperature.

| Time (days) | High Vt,  | Nom Vt,   | Low Vt, 25°C | High Vt,   | Nom Vt,    | Low Vt,    |

|-------------|-----------|-----------|--------------|------------|------------|------------|

|             | 25°C (uV) | 25°C (uV) | (uV)         | 100°C (uV) | 100°C (uV) | 100°C (uV) |

| 1           | 91.3      | 121       | 160.92       | 329.35     | 437.72     | 580.6      |

| 2           | 102.65    | 136.4     | 180.97       | 369.79     | 491.4      | 651.92     |

| 3           | 109.92    | 146.09    | 193.78       | 395.69     | 525.89     | 697.59     |

| 4           | 115.38    | 153.34    | 203.4        | 415.16     | 551.76     | 731.9      |

Table 2.  $V_{th}$  degradation with Varation in Vt and T with V=1.1V

# Degradation in Vth at input voltage of 1.1V

Figure 4-2. Degradation in  $V_{th}$  at input voltage of 1.1 V

From Tables 1 & 2 and Figures 4-1 & 4-2 it is clear that NBTI degradation is worst at the corner: **P low**, **V** high and **T high** and best at **P high**, **V low and T low**.

#### **CHAPTER 5**

## ONLINE NBTI WEAR-OUT ESTIMATION TECHNIQUE

This work proposes to perform NBTI wear-out estimation of the register file on a Leon 3 processor using run-time data from benchmarks. This is done by monitoring its 256 32-bit register file. The NBTI wearout estimation is obtained from the RelXpert simulator [22], our baseline, and the RD model [8]. These values are then compared. The RD model is then tuned, using *time slicing* technique, to match the simulator.

#### 5.1 Time Slicing Technique

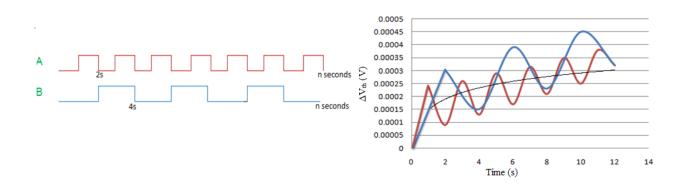

The threshold voltage degradation over a period of 10 years is 50mV [14]. Our experiments show that implementing the RD model without tuning does not lead to this degradation. The reaction-diffusion process is frequency independent [16]. The same number of interface traps is generated (as discussed in Section 2) irrespective of the frequency of the PMOS's input. For example, if a periodic wave with time period of 1s and another with 2s, having same duty cycle, are applied as PMOS input for n seconds, they both will generate the same interface traps and thus cause the same V<sub>th</sub> degradation (as shown in Figure 5-1(a)). The wave with period of 1s will initially generate less interface traps per cycle, but at the end of n seconds the number of interface traps generated will be same as the wave with period of 2s.

Figure 5-1(a) RD mechanism is frequency independent

The RD model is frequency dependent. Figure 5-1 (b) shows the plot when the  $V_{th}$  degradation was measured using the RD model (equations 1 & 2), inputs to the PMOS being the same as in Figure 5-1(a). It is clearly visible in Figure 5-1(b) that more  $V_{th}$  degradation is observed for the wave with less activity.

Figure 5-1 (b). RD model is frequency dependent

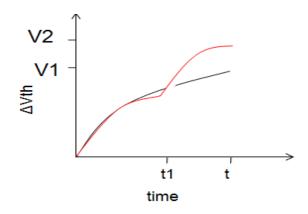

This shows that the RD model is somewhat imperfect and needs to be improved. Here a novel technique is presented which tunes the RD model that improves it and provides more accurate results. The RD model has an important property of being non-additive [15]. For example, if stress exists for time t and the stress equation is implemented in two ways, one for time 0 to t and other for 0 to t1 and t1 to t (in

two steps), where t1< t, the latter will give a higher threshold voltage degradation. For the latter case, at t1, it takes the history and then carries out stress from t1 to t. This is because more interface traps are generated as it takes the history at t1. As shown in Figure 5-2, V2 > V1, where V2 and V1 are the  $\Delta V_{th}$  values resulted from the above two cases. We term this technique as *time slicing*, resulting in degradation near to [14]. This concludes that increasing the granularity of applying stress on a PMOS increases its NBTI degradation. This technique is used to tune to RD model to match the RelXpert Simulator.

Figure 5-2. Time Slicing

## 5.2 Online NBTI Wear-out Estimation Technique

This section describes the flow of our methodology of Online NBTI Wear-out Estimation.

- Run benchmarks on Leon 3 processor

- Obtain Register File activity

- Carry out waveform compression

- Regenerate a random wave using the stored statistics

- Calculate V<sub>th</sub> degradation for all the PMOS transistors in the register file using the RD model

- The activity waveforms go as input to the Ultrasim (for RelXpert) and SPICE (RD model) netlists

- The degraded V<sub>th</sub> values also go into SPICE netlist

- Simulate both netlists and compare performance degradation (SNM)

- Tune the RD model, by time slicing, simulate, and match the Simulator

Figure 5-3. Online NBTI wear-out estimation technique

## 5.3 Results

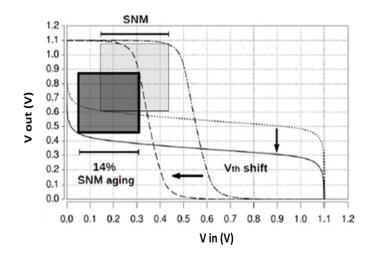

This section presents results carried out on the Leon 3 DE2 design running Dhrystone benchmark on Modelsim [25]. The Leon3 has 256 32-bit register file, and we design them in SPICE Virtuoso using 6-T SRAM cells. The degradation measuring metric for our experiment is the Signal-to-Noise Ratio (SNM).

SNM is the minimum DC noise voltage necessary to change the state of a SRAM cell. It can be computed as the side of the length of the maximum square enclosed in the butterfly curve of a SRAM cell. Figure 5-4 shows the butterfly curves for a SRAM cell [8]. The length of the side of light grey square represents the fresh SNM. The length of the side of the dark grey square represents the degraded SNM. When the PMOS degrades, or becomes weak due to NBTI, the butterfly curve of the SRAM cell shifts to the left. It shows that there is 14% SNM degradation due to NBTI.

Figure 5-4. SNM degradation measurement of SRAM cell [21]

#### 5.3.1 Online NBTI Wear-out Estimation technique running Dhrystone benchmark on Leon 3

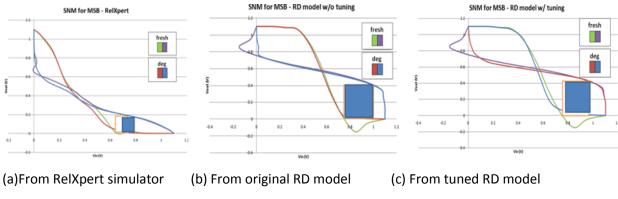

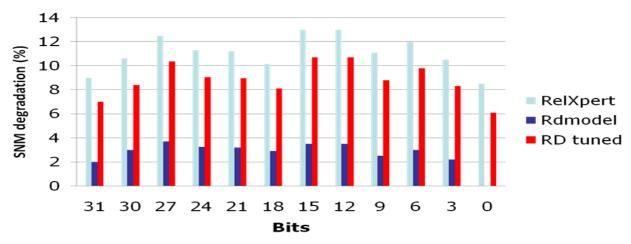

We run the Dhrystone Benchmark (for time it runs once, i.e. 58ms) on Leon 3 DE2 design on Modelsim [25] and monitor the activity waveforms of its Register File. We calculate  $\Delta V_{th}$  values, using equations 1 & 2 (discussed in Section 4.1), for both original and tuned RD models. Figure 5-5 shows the SNM degradation calculation from RelXpert simulator, the original RD model and the tuned RD model for bit 31 of Leon 3 register file. The RelXpert Simulator shows 9% SNM degradation, the original RD model with 2% and the tuned RD model shows 7% SNM degradation. This is carried for all bits of the Register File.

Figure 5-5. SNM degradation calculation for Bit 31

Figure 5-6 shows the SNM degradation comparison between the RelXpert simulator, original RD model and the tuned RD model, for 1 year degradation, for few bits of the register file. It shows that the tuned RD model achieves about 80% accuracy with respect to the RelXpert simulator. The simulator takes an average of 48 hours for the simulation of each bit compared to 6 hours (5 hours for  $\Delta V_{th}$  calculation and 1 hour for SPICE simulation) average with RD model. Thus carrying out NBTI wear-out estimation with RD model is 8 times faster than doing the same on the simulator.

Figure 5-6. SNM degradation for RelXpert, RD model and tuned RD model

#### **CHAPTER 6**

### WAVEFORM COMPRESSION AND $\Delta V_{th}$ ESTIMATION/PREDICTION TECHNIQUE

Section 5 presented a novel online NBTI wear-out estimation technique and showed how time slicing improves the accuracy of the RD model. The question is - "How this technique is going to impact the performance and cost of the system?" Monitoring the register file activity on a Leon 3 processor requires it to be stored in memory. Running the Dhrystone benchmark on the Leon 3 would require storing nearly 256MB memory for this activity, which greatly increases the cost of the system. NBTI is a long term mechanism, and the online prediction needs to be predicted after a long time period, say in years. Implementing equations 1 & 2 (discussed in Section 4.1) for such a long period would degrade the performance of the system. The dhrystone benchmark, running on the Leon 3, would take around 4 hours to predict  $\Delta V_{th}$  for a day for a single bit, which is impracticable at run-time.

This section first presents *waveform compression* and  $\Delta V_{th}$  *estimation/prediction* techniques, to overcome the huge cost and performance impact, respectively, caused by the online NBTI wear-out estimation technique presented in Section 5. Online NBTI wear-out prediction needs to be implemented on a real system. This section then proposes to implement a NBTI degradation predictor (NDP) on the Leon 3 in a DE2 FPGA [24], which predicts NBTI  $\Delta V_{th}$  degradation for different Spec2000 benchmarks. This section further proposes to compare the actual on-chip degradation on the Leon3 in a DE2 FPGA, with the RD model. We do so by designing a n-stage (n is odd) Ring Oscillator on the Leon3 in a DE2 FPGA and measuring the frequency degradation due to NBTI. This is then compared to the RD model.

## 6.1. Waveform Compression Technique

As mentioned above, we need to overcome the huge memory cost resulting from the technique in Section 5. Here we propose a waveform compression technique which will significantly reduce this memory cost.

26

In this technique we propose to store just the statistics, i.e. mean and standard deviation, of the activity waveforms in the memory rather than storing the entire waveforms. Storing the entire waveforms (nearing 125K cycles) would take approximately 250KB of memory, for each register file bit. For the waveform compression technique, we need to store only the mean and standard deviation of 0s and 1s of the activity waveform for each bit. Here the mean and standard deviation values are stored in IEEE floating point single precision format (32 bits for each value). This only takes 128bits/register-bit (4x32).

For calculation of NBTI  $V_{th}$  degradation, these statistics are retrieved from the memory and a random wave is generated, on the fly, using random normal distribution. This wave should have good  $V_{th}$  degradation accuracy with respect to the  $V_{th}$  degradation obtained with original waveforms. Figure 6-1 shows the flow of the proposed waveform compression technique.

Figure 6-1. Waveform Compression Technique

## 6.1.1 Results

We carry out the Waveform Compression Technique experiment using the Register File activity waveforms derived by running Dhrystone Benchmark on the Leon3 using Modelsim [25].

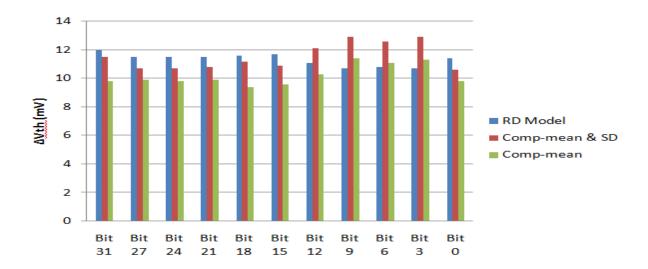

We calculate the Mean and standard-deviation (SD) of the activity waveforms for each bit of the Register File. These statistics are calculated from the activity waveforms obtained by running the Dhrystone benchmark once (58ms) and can be stored in the memory. For V<sub>th</sub> degradation calculation these statistics are retrieved from the memory and a random waveform is generated, on the fly, using random normal distribution. This randomly generated waveform is used to calculate V<sub>th</sub> degradation. In our experiment this waveform provides 91% accuracy in V<sub>th</sub> degradation calculation with respect to the tuned RD model. Figure 6-2 shows the V<sub>th</sub> degradation for a few bits of the 256 32-bit register file of the Leon3, for uncompressed, compressed (retrieved with mean and standard-deviation) and compressed (retrieved with just mean) waveforms. The compressed waveforms generated using both mean and standard deviation provide a more accurate result compared to the one with just the mean.

Figure 6-2. ΔV<sub>th</sub> degradation for RD model, compressed (retrieved using mean and SD) and compressed (retrieved using just mean) giving an average accuracy of 91%

Storing the entire waveforms would take approximately 250KB of memory (i.e. the waveform flips 250K times or has 125K cycles), for each register bit. For the waveform compression technique, we need to store the mean and standard deviation of 0s and 1s of the activity waveform for each bit, which only takes 128bits/register-bit (4x32) or 16bytes/register-bit. For the whole register file it will consume

128x32x256 = 131KB of memory compared to 250Kx32x256 = 256MB of memory for the activity waveform without compression. Table 3 shows the comparison of memory needed to store activity with and without compression.

| Туре                | Without COMPRESSION | With COMPRESSION |

|---------------------|---------------------|------------------|

| One Register Bit    | 31KBytes            | 16 Bytes         |

| One Register        | 1MBytes             | 512 Bytes        |

| Whole Register File | 256MBytes           | 131KB            |

Table 3. Memory consumption for activity waveforms with and without COMPRESSION

# $6.2 \Delta V_{th}$ estimation/prediction technique

Running the RD model for a long time, say 1 day, with fine granularity, during run-time would consume a lot of time, 4 hours for Dhrystone to predict  $\Delta V_{th}$ , and degrade the performance of the system. Thus we need to come up with a technique which would predict the future NBTI V<sub>th</sub> degradation by running the RD model only for a small period of time.

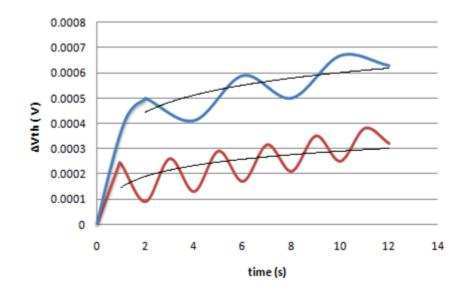

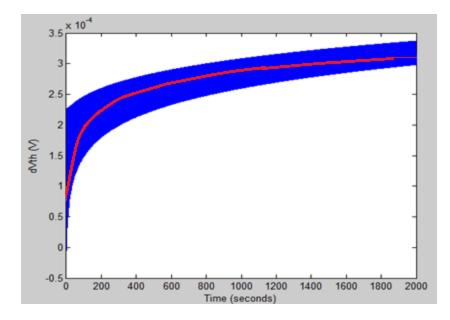

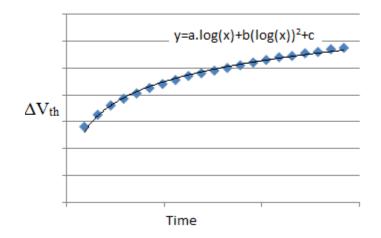

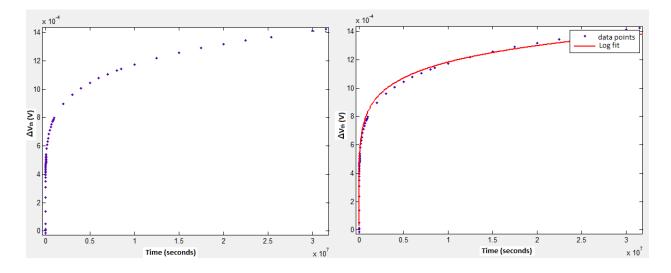

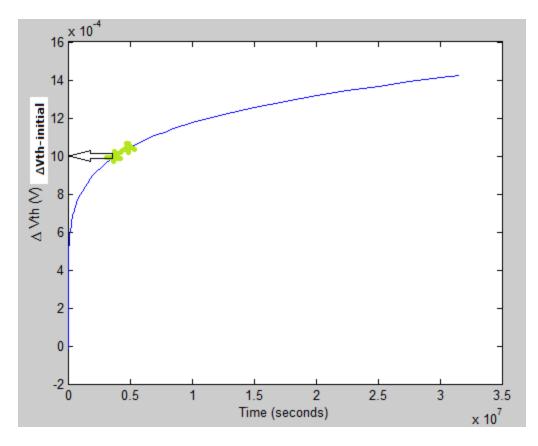

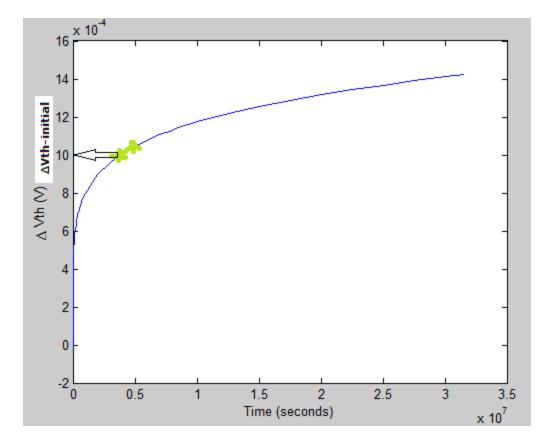

References [7,8,17,18,19,20] show that RD model works best in the range of 0s to  $10^5$  seconds. Thus, by running the RD model for a small period (say the time to run the application once), we can obtain degraded V<sub>th</sub> values at selected points. Using  $\Delta V_{th}$  Estimation/Prediction Technique we can build a curve and derive its function. The RD model exhibits a logarithmic trend due to continuous stress-recovery cycles. Figure 6-3. shows its logarithmic nature when a square wave with a period of 0.5s and a duty cycle of 50% is the PMOS's input. Thus a logarithmic function is preferable. We will prove that a second order logarithmic curve is the best fit to the  $\Delta V_{th}$  points obtained from running the RD model.

Figure 6-3. Logarithmic nature of RD model for a square wave with 2s period and 50% duty cycle

Just plugging in the number of years we can get the respective  $V_{th}$  degradation. Figure 6-4 shows Curving Fitting and obtaining the function to calculate future  $V_{th}$  degradation.

Figure 6-4.  $\Delta V_{th}$  Estimation/Degradation Technique for  $\Delta V_{th}$  prediction after plotting few data points. Here  $y=\Delta V_{th}$  and x=time=t

# 6.2.1 Results

The flow of our experiment is as below;

- We run the RD model, for bit 3, for a duration of time the Dhrystone benchmark runs once (i.e. 58ms) and note down 21  $V_{th}$  degradation values at regular time intervals and the respective time

- We plot these data points using a 'scatter plot'

- We use the Curve Fitting feature in to plot a fitting curve and derive an equation for the same

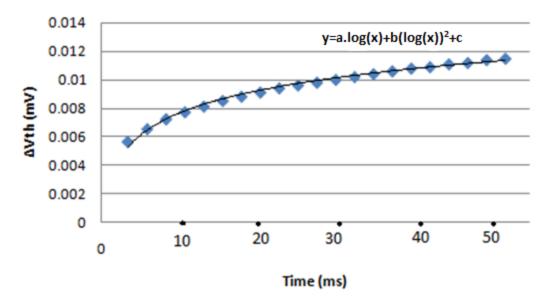

- The equation for bit 3 is  $\Delta V_{th}=a.log(x)+b.(log(x))^2+c$  (Figure 6-5)

- We plug in any value of t and get the respective  $\Delta V_{th}$

# **Curve Fitting**

Figure 6-5. Curve Fitting for bit 3 for Dhrystone

Table 4. shows the % accuracy in  $\Delta V_{th}$  after 1 day degradation, for few register file bits, after  $\Delta V_{th}$ Estimation/Prediction Technique, by running Dhrystone benchmark on the Leon3.

| BITS | ΔV <sub>th</sub> (mV) (original RD<br>Model) | ΔV <sub>th</sub> (mV) (after<br>Est./Pred.) | % Accuracy |

|------|----------------------------------------------|---------------------------------------------|------------|

| 0    | 44                                           | 47                                          | 93.5       |

| 3    | 44                                           | 47                                          | 93.5       |

| 6    | 46                                           | 50                                          | 92         |

| 9    | 42                                           | 47                                          | 89         |

| 12   | 49                                           | 51                                          | 96         |

| 15   | 49                                           | 52                                          | 94         |

| 18   | 41                                           | 47                                          | 87         |

| 21   | 47                                           | 49                                          | 96         |

| 24   | 48                                           | 50                                          | 96         |

| 27   | 53                                           | 55                                          | 96         |

| 31   | 40                                           | 44                                          | 91         |

Table 4. 93% accuracy is achieved in  $\Delta V_{th}$ , for 1 day NBTI, after  $\Delta V_{th}$  Estimation/Prediction Technique

From Figure 6-5 plugging in x=t=1year we get  $\Delta V_{th}$ =47mV for bit 3. Running the RD model simulation without this technique provides  $\Delta V_{th}$ =44mv. This results in 93.5% accuracy. Thus we get an average **accuracy of 93%** (from Table 4) for 21 data points, with respect to running RD model equations for a year.

Running the RD model for a period of 1 day would take approximately 4 hours to calculate  $V_{th}$  degradation. With this technique we can achieve the  $\Delta V_{th}$  value in approximately **10 seconds**.

Thus the  $\Delta V_{th}$  estimation/prediction technique is faster by an order of  $10^2$  with 93% accuracy with 21 data points.

#### 6.2.1.1 Why we use Logarithmic curve fitting?

Once the  $\Delta V_{th}$  data points are obtained by running the RD model for the duration Dhrystone runs once, we need to implement curve fitting to obtain the function to predict the future NBTI degradation. The question is, which function will best fit the these  $\Delta V_{th}$  data points? Also how can we prove that the function we use is appropriate on physical basis, i.e. does the RD model/process trend follow the same of the chosen function, and also how accurate is it? First we find the trend of the RD model/process using NBTI physics and conclude which function follows this trend, so that it can be used to carry out curve fitting. Then we perform data analysis to measure accuracy.

We know that  $H_2$  ions are released when the Si-H bonds at the Si-SiO<sub>2</sub> interface break under operation [8]. During stress these  $H_2$  ions diffuse into the oxide in the reaction phase and do so in the poly-Si in the diffusion phase. The diffusion of  $H_2$  ions in oxide is faster compared to that in the poly-Si. Due to the widely different diffusivity of  $H_2$  in the oxide and poly-Si, the recovery becomes a two-step process, with fast recovery driven by  $H_2$  in the oxide, followed by slow recovery of  $H_2$  by backdiffusion from the poly-Si. The number of annealed traps can be due to two parts: 1) recombination of  $H_2$  in the oxide and 2) backdiffusion of  $H_2$  in the poly-Si. Due to this not all the  $H_2$  ions are able to bond again with Si, to form Si-H bonds. Thus the number of interface traps generated during the next stress phase will be smaller

compared to the first one. Also  $\Delta V_{th} = \frac{qN_{IT}}{C_{OX}}$ ; where N<sub>IT</sub> is the rate of interface trap generation, C<sub>OX</sub> is

the oxide capacitance, and q is the charge of holes. Due to this  $\Delta V_{th}$  in each and every stress phase will be smaller than that in the previous one, as shown in Figure 6-6.

Figure 6-6.  $\Delta V_{th}$  for second stress phase is smaller compared to that of first

The number of interface traps generated during stress is given by equation (3), and number of interface traps annealed during recovery is given by equation (4).

$$N_{IT}^{A}(t) = N_{IT}(t) \left( \frac{2\xi_{1}t_{e} + \sqrt{\xi_{2}C(t - t_{1})}}{(1 + \delta)t_{OX} + \sqrt{Ct}} \right)$$

.....equation (4)

$t_1$  is the time for which recovery takes place. All other parameters are RD model parameters.

Inserting the values of RD model parameters into equation (4) shows that the term

$$\left(\frac{2\xi_1 t_e + \sqrt{\xi_2 C(t - t_1)}}{(1 + \delta)t_{OX} + \sqrt{Ct}}\right) < 1.$$

Thus we can say that number of interface traps to be generated during the

next stress phase will be lesser compared to the first one, due to not all the H<sub>2</sub> ions form bond with Si during recovery.

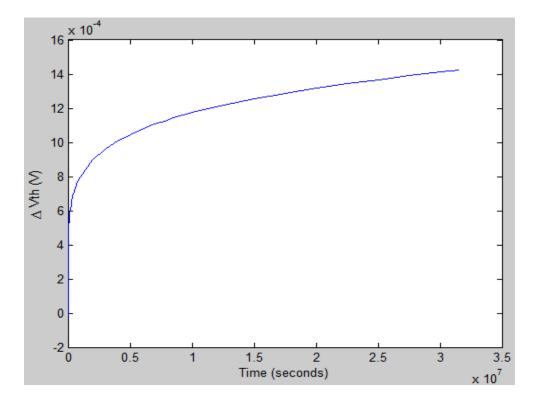

If we see this stress recovery process for a long-run, each stress phase will generate lesser interface traps compared to the previous one, and thus result in lesser  $\Delta V_{th}$  for that cycle compared to all the previous ones. Thus the  $\Delta V_{th}$  degradation for an RD model/process increases at a high rate first and then start becoming stable, or increases at a very small rate. We can say that this trend is very similar to the trend of the logarithmic function. Figure 6-7 shows the  $\Delta V_{th}$  degradation trend for a 1Hz square wave generated from the RD model for a period of 1 year, which similar to the logarithmic function.

Now we carry out data analysis for the curve plotted in Figure 6-7, and show that it is very close to the logarithmic function. There can be numerous functions which can fit a set of data points, but here we need to find one which does so with minimum residual, or error. Residual of an observed value is the difference between the observed value and the estimated function value. Figure 6-8 shows the residuals when any curve is fit for a set of data points.

Figure 6-8. Residuals in curve fitting

When we carry out curve fitting, for a set of data points, using different functions, the best fit function will be the one with minimum residual (or error). The value  $R^2$  quantifies goodness of fit. It is a fraction between 0.0 and 1.0, and has no units. Higher values indicate that the function fits the data points better. Thus if the value of  $R^2$  is as near to 1, the chosen curve fits the data points better. When  $R^2=1.0$ , all points lie exactly on the curve with no scatter.  $R^2$  is computed from the sum of the squares of the residuals, and this is denoted by  $SS_{res}$ , which is in the units of the Y-axis squared. To turn  $R^2$  into a fraction, the result is normalized to the sum of the square of the distances of the points from a horizontal line through the mean of all Y values. This value is called  $SS_{tot}$ . So  $R^2$  is calculated by the

$$R^{2} = 1.0 - \frac{SS_{res}}{SS_{tot}}$$

equation . Thus the curve is best fit when SS<sub>res</sub> is quite smaller than SS<sub>tot</sub>.

We extract data points from the curve in Figure 6-7 and try to perform curve fitting. Figure 6-9 shows how the logarithmic function follows the trend of these RD model generated data points for 1 Hz

square wave for a period of 1 year. Here we achieve a value of  $R^2$ =0.9947, or accuracy of 99.47%. Thus we can say that the logarithmic function is 99.47% close to the RD model trend.

Figure 6-9. Logarithmic function fit has 99.47% accuracy

Table 5 shows the accuracy when curve fitting is carried out with different functions, for the data points obtained from RD model curve in Figure 6-7.

| Functions            | R <sup>2</sup> value |

|----------------------|----------------------|

| Exponential          | 0.604                |

| Linear Polynomial    | 0.6818               |

| Quadratic Polynomial | 0.8058               |

| Cubic Polynomial     | 0.8480               |

| Posynomial            | 0.8556 |

|-----------------------|--------|

| 1st order Logarithmic | 0.8732 |

| 2nd order Logarithmic | 0.9947 |

# 6.3 NBTI degradation Predictor on the Leon 3 FPGA

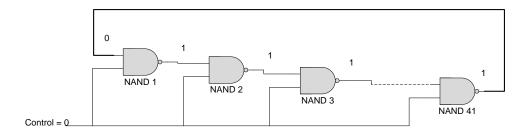

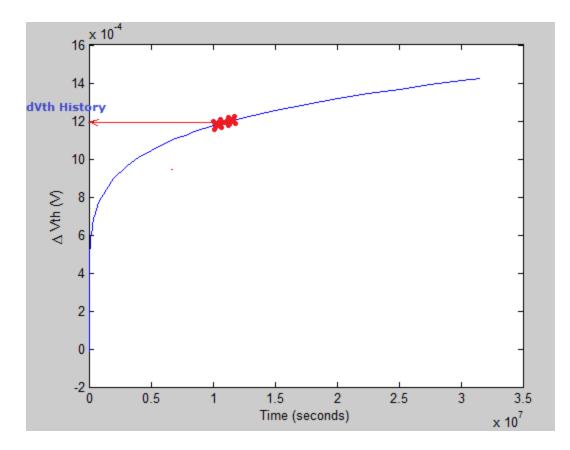

In this section we showed results for the waveform compression and  $\Delta V_{th}$  Estimation/Prediction techniques implemented on the Leon 3 running on Modelsim [25]. But these techniques should be implemented in a real system. We propose to implement a NBTI degradation predictor (NDP) on the Leon3 in a DE2 FPGA [24]. This module would predict the final  $\Delta V_{th}$  degradation value, for the Leon 3 register file, after a specified time period. We also have a 41-stage ring oscillator placed at the four corners of the FPGA to measure the process variation across it.

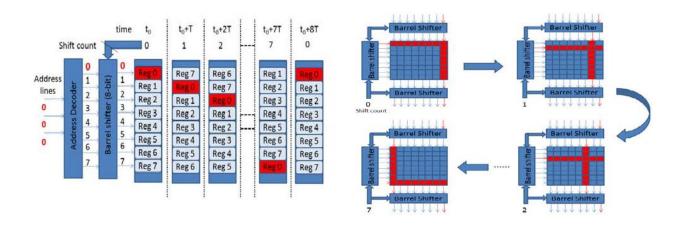

The flow of this predictor is as follows and as in Figure 6-10.

- Run Spec2000 benchmarks on the Leon 3 FPGA

- Perform waveform compression technique on these waveforms and store the statistics

- Retrieve these statistics

- Carry out NBTI degradation estimation using curve fitting

- Predict the final  $\Delta V_{th}$ , after a specified time period, using the curve fitting function

Figure 6-10. Proposed design of NBTI Degradation Predictor on the Leon 3 FPGA

## 6.3.1 Architecture

As mentioned above, we implement the NDP module in hardware to predict the run-time degradation of the register file on the the Leon 3 in a DE2 FPGA, running Spec2000 benchmarks. Figure 6-11 shows the proposed architecture of this module. It consists of 2 main sub-modules, viz. Activity Monitor module and Predictor module. It also consists of the on-chip memory block to store activity statistics and the register file to be monitored. We also plan to measure the actual frequency degradation, of Nstage ring oscillator (n=odd), on the Leon3 in a DE2 FPGA. This will then be compared to the results of the RD model.

## NDP module FPGA FPGA Leon 3 **Activity Monitor** 256 32-bit HDL code **Register File** activity To monitor the activity & **Running WCET** calculate statistics (on the benchmarks fly) FPGA 41-stage RING Give $\Delta V_{th}$ variation OSCILLATOR FPGA across 4 FPGA corners 4 corners **On-chip Memory** To save activity statistics CPU Estimator Predictor FINAL $\Delta V_{th}$ To calculate Function $\Delta V_{th}$

Figure 6-11. Proposed NDP module Architecture

# 6.3.2 Function of each blocks

This section describes the function of each block of the NDP module architecture proposed in 6.3.1.

- **Register-File**: This is the in-built 256 32-bit register file on the Leon 3 in a DE2 FPGA. This register file needs to be monitored through HDL coding to carry out its NBTI degradation prediction.

- **N-stage Ring Oscillator:** This is designed in hardware. The ring-oscillator waveforms will be monitored through HDL coding to finally measure the frequency degradation due to NBTI.

- Activity Monitor: This monitor is the HDL code (Verilog) to monitor the input of all the registers, while running Spec2000 benchmarks, to predict its NBTI wear-out. It monitors and captures the

waveforms of ring oscillator too. It also calculates the statistics, i.e. mean and standard variation (as discussed in section 6.1), of the waveforms and save them in the on-chip memory.

- **On-chip Memory:** It is used to store the statistics calculated by the monitor.

- Estimator: It runs the application (or benchmark) for a specific time (discussed in section 6.3.3), to collect specific number the  $\Delta V_{th}$  data points at regular intervals (how many discussed in section 6.3.3).

- **Predictor:** This block carries out  $\Delta V_{th}$  Estimation/Prediction Technique (discussed in Section 6.2) to obtain the final  $\Delta V_{th}$  functions for different register file bits. These functions are used to predict the future NBTI degradation.

- **Calculate Ring Oscillator frequency:** When the frequency of the ring oscillator is to be measured, the statistics, of the same, are retrieved. This measured frequency from the FPGA is then compared to the same achieved from the RD model.

The question is which particular register file bits will be monitored to predict degradation on the above proposed NDP module. In combinational logic circuits the critical path in a circuit will undergo maximum degradation, and it remains fixed. Here, we monitor the register file inputs to measure NBTI degradation of the PMOSs in each of the SRAM cells. Each SRAM cell degrades depending on the value and the time a value is stored in it. Each of them will undergo different amount of degradation for different applications. So their degradation is application dependent. Thus, it is in the hands of the designer to decide which particular register file bits will be monitored to predict NBTI degradation.

#### **CHAPTER 7**

### DESIGN AND IMPLEMENTATION OF THE NBTI DEGRADATION PRIDICTOR (NDP)

This section explains the design and implementation of the NBTI Degradation Predictor (NDP) proposed in Section 6.3. The hardware design of the Leon3 Register File (RF) activity monitor and the ring oscillators are done in VHDL. We implement these hardware designs on the Leon3 processor in a DE2 FPGA.

The LEON3 processor is a synthesizable VHDL model of a 32-bit processor compliant with the SPARC V8 architecture [30]. The model is highly configurable and particularly suitable for SoC designs. The Leon3 is distributed as integrated parts of the GRLIB IP Library [31]. GRLIB IP is an open source library downloadable from www.gaisler.com.

## 7.1 Design of NDP

Here we discuss the design of the Leon3 RF online activity monitor and the ring oscillator units used to measure the NBTI history and calculate the process variation across the FPGA.

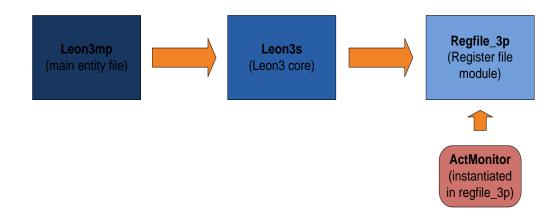

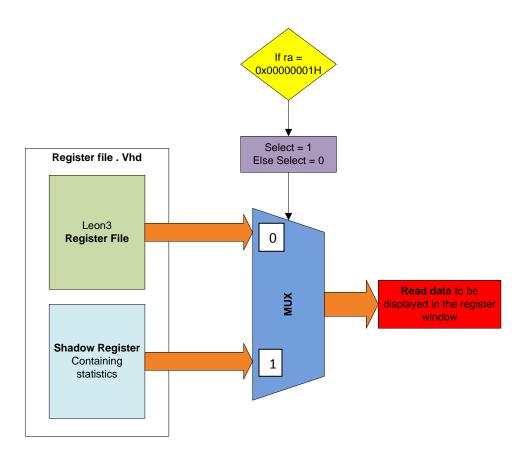

#### 7.1.1 Online Activity Monitor

As discussed in Section 6.3.1, we need to monitor the activity of the register file of the Leon3 on a DE2 FPGA. This is done through an online activity monitor module designed in VHDL. Figure 7-1 shows how we insert the online activity monitor module into the VHDL Leon3 core. The top level entity file is 'leon3mp' and the Leon3 core file is named as '*leon3s*'. The register file '*regfile\_3p*' is instantiated in the core. We insert the activity monitor module called '*actmonitor*', and instantiate it in the '*regfile\_3p*'. Every time the register file cells are written, the input to the cross-coupled inverters in a SRAM cell changes, which plays the major role in their NBTI degradation. Thus by monitoring the activity of the register file SRAM cells, we can estimate/predict its NBTI degradation. Once the activity is known, we

can calculate its statistics, i.e. mean and variance, and store them into the memory, as discussed in earlier sections.

Figure 7-1. Inserting our Activity Monitor in the Leon3 VHDL core

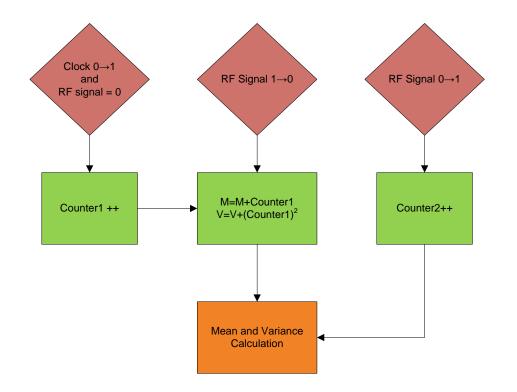

We monitor the activity of the register file using counters. Figure 7-2 shows the design flow of the online activity monitor. To carry out NBTI estimation/prediction, we need to know the time the signal stays at value '0' and the time it stays at value '1'. On an FPGA, using VHDL, we can do this by counting the cycles of the clock, when the signal to be monitored is at value '0' or '1'. In this experiment, we do so by counting the positive edge of the clock when the register file cell activity signal is '0' or '1', using 'counter1'. Say we are counting the amount of time the register file signal stays at '0'. The counter increments at every positive edge of the clock when the RF signal is '0'. When the RF signal is '1' the counter stops and the statistics, i.e. mean and variance, are calculated. There is a second counter, 'counter2', which increments at every positive edge of the RF signal, to calculate the number of it's periods.

Figure 7-2. Leon3 Register File Activity Monitor design flow

The statistics represent the Mean and Standard Deviation of the time the RF signal stays at 0 and 1. They are calculated by the following formulas.

Mean:

$$M = E(X) = \frac{\Sigma X}{n}$$

Standard Deviation:  $SD = \sqrt{E(X^2) - (E(X))^2}$

where X is the number of transitions of the clock when RF signal is 0 or 1, and n is the number of transitions of the RF signal.

Once the statistics are calculated, they are stored into the on-chip memory. When estimation/prediction is carried, out these statistics are retrieved from the same memory to do the same.

#### 7.1.2 $\Delta V_{th}$ Estimation/Prediction

As discussed above, when estimation/prediction is to be carried out, the RF signal statistics stored in the memory need to be retrieved. These statistics is based on the number of clock transitions when the RF signal is '0' or '1', but not the time for which it is at those values. Thus we need to multiply these number of transitions by the period of the FPGA clock, i.e. 0.02us. (50MHz clock of DE2 FPGA).

As discussed in Section 6.3.2, the estimator block collects  $\Delta V_{th}$  data points from equations 1 and 2 (RD model equations) when applied to the random waveforms generated through statistics (waveform compression technique). These random waveforms are generated using the mean and standard variation calculated by the activity monitor module using random normal distribution. The predictor block then does the work of carrying out curve fitting, with the collected  $\Delta V_{th}$  points, to plot an estimate trend of the future degradation and get its function. This function can be used to predict the future  $\Delta V_{th}$  degradation for a given time. As we saw in Section 6.2, this method gives on an average 93% accuracy compared to the tuned RD model, and is 10<sup>2</sup> times faster for Drystone benchmark.

Using the statistics retrieved from the memory, random waveforms are generated using random normal distribution. These waveforms act as inputs in estimating the NBTI  $\Delta V_{th}$  degradation using equations 1 and 2. Here we generate random waveforms for a time of 1 second and collect 20  $\Delta V_{th}$  data points at regular intervals for the same. These data points are used to carry out curve fitting as shown in Section 6.2. Hence, through curve fitting, we will get a function (2<sup>nd</sup> order logarithmic in our case), which can be used to predict the future  $\Delta V_{th}$  degradation.

# 7.1.3 History for NBTI $\Delta V_{th}$ estimation/prediction