## **University of Massachusetts Amherst** ScholarWorks@UMass Amherst

Masters Theses 1911 - February 2014

2011

# Robust Signaling Techniques for Through Silicon Via Bundles

Krishna Chaitanya Chillara University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/theses

Part of the VLSI and Circuits, Embedded and Hardware Systems Commons

Chillara, Krishna Chaitanya, "Robust Signaling Techniques for Through Silicon Via Bundles" (2011). Masters Theses 1911 - February 2014.671.

Retrieved from https://scholarworks.umass.edu/theses/671

This thesis is brought to you for free and open access by ScholarWorks@UMass Amherst. It has been accepted for inclusion in Masters Theses 1911 -February 2014 by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

## ROBUST SIGNALING TECHNIQUES FOR THROUGH SILICON VIA BUNDLES

A Thesis Presented

by

#### KRISHNA C CHILLARA

Submitted to the Graduate School of the

University of Massachusetts Amherst in partial fulfillment

of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

September 2011

Department of Electrical and Computer Engineering

© Copyright by Krishna C Chillara 2011

All Rights Reserved

## ROBUST SIGNALING TECHNIQUES

#### FOR THROUGH SILICON VIA BUNDLES

A Thesis Presented

by

## KRISHNA C CHILLARA

| Approved as to style and content by | y:                                                |

|-------------------------------------|---------------------------------------------------|

| Wayne Burleson, Chair               |                                                   |

| Christopher Salthouse, Member       |                                                   |

| Russell Tessier, Member             |                                                   |

|                                     |                                                   |

|                                     | C.V. Hollot, Department Head                      |

|                                     | Department of Electrical and Computer Engineering |

## **DEDICATION**

To my parents and brother

#### **ACKNOWLEDGEMENTS**

I would like to thank my advisor Professor Wayne Burleson for all his support and guidance throughout this work. His constant guidance and valuable feedback helped me focus on the topics of this research. I thank Prof. Salthouse and Prof. Tessier for serving on my committee and providing valuable suggestions during the course of this work. Special thanks to Jinwook Jang for several valuable discussions we had regarding this work and other topics of common interest. I would like to thank Vinay, Basab and Ibis for their suggestions on several related topics on VLSI. I thank all my lab mates and friends specially Ashwin, Sud, Girish, Tej, Sudhi and Vikram for their support and encouragement. Finally I would like to thank my parents and my brother for their love and support.

#### **ABSTRACT**

## ROBUST SIGNALING TECHNIQUES FOR THROUGH SILICON VIA BUNDLES

## SEPTEMBER 2011 KRISHNA C CHILLARA

B.TECH, VELLORE INSTITUTE OF TECHNOLOGY, INDIA M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Prof. Wayne P. Burleson

3D circuit integration is becoming increasingly important as one of the remaining techniques for staying on Moore's law trajectory. 3D Integrated Circuits (ICs) can be realized using the Through Silicon Via (TSV) approach. In order to extract the full benefits of 3D and for better yield, it has been suggested that the TSVs should be arranged as bundles rather than parallel TSVs. TSVs are required to route the signals through different dies in a multi-tier 3D IC. TSVs are excellent but scarce electrical conductors. Hence, it is important to utilize these resources very efficiently.

In high performance 3D ICs, signaling techniques play a crucial role in determining the overall performance of the system. In this work, 3x3 and 4x4 TSV bundles are considered. Electrical parasitics of TSV bundles are extracted using Ansoft Q3D Extractor. Various techniques for signaling over TSV bundles are analyzed in this work. Performance, energy and robustness are the crucial aspects to be considered for analyzing a signaling technique. For performance analysis, maximum data rate for each of the signaling techniques is obtained and the dominant factors that determine these values are identified. 3D integration is fairly a new field and does not have common

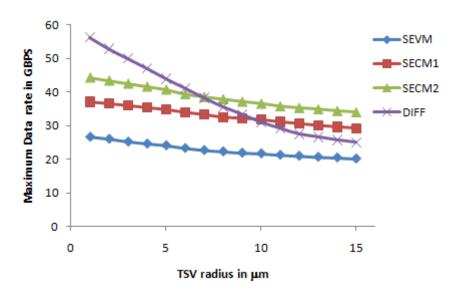

standards. Different research groups (both academic and industry) across the globe have different manufacturing technologies to suit their needs. In this work, we obtain the electrical parasitics of TSV bundles for different TSV radii ranging from 1μm to 15μm. The TSV radius for most of the 3D integration technologies falls within this range. Maximum data rates are determined for different TSV radii ranging from 1μm to 15μm. This study across different TSV radii helps in choosing a better signaling technique for a particular TSV radius depending on the design goals. Energy/bit for each of the signaling techniques is obtained for a common data rate of 10Gbps Pseudo Random Bit Sequence (PRBS) input. For robustness analysis, the impact of process, voltage and temperature variations between driver and receiver circuits is analyzed. Ansoft Q3D extractor, NCSU 45nm PDK and HSPICE simulation tool are used.

From the simulation results, it is observed that a differential technique is beneficial for smaller radii in terms of maximum data rate that can be obtained. For a radius above 7µm, single ended current mode signaling gives a better data rate. Low swing single ended signaling techniques consume less energy but suffer slightly more due to process variations compared to full swing voltage mode signaling. In terms of robustness to supply noise, differential signaling is more robust compared to single ended techniques. An increase in the temperature reduces the data rates of both single ended and differential signaling techniques. Hence, depending on the TSV radius of target technology and process and environment variations, an optimum signaling technique can be chosen.

## TABLE OF CONTENTS

|             |                                                              | Page |

|-------------|--------------------------------------------------------------|------|

| ACKNOWL     | EDGEMENTS                                                    | v    |

| ABSTRACT    |                                                              | vi   |

| LIST OF TA  | ABLES                                                        | X    |

| LIST OF FIG | GURES                                                        | xi   |

|             |                                                              |      |

| CHAPTER     |                                                              |      |

| 1.INTRODU   | JCTION                                                       | 1    |

| 1.1         | Moore's Law and Interconnect Bottleneck                      | 1    |

| 1.2         | Motivation for 3D Integration                                |      |

| 1.3         | Benefits of 3D Integration                                   |      |

| 1.4         | Challenges in 3D Integration                                 |      |

| 1.5         | Problem Statement                                            |      |

| 1.6         | Document Organization                                        | 7    |

| 2.BACKGR    | OUND AND PRIOR WORK                                          | 9    |

| 2.1         | 3D Integration Technologies                                  | 9    |

| 2.2         | Through Silicon Via based 3D ICs                             |      |

| 2.3         | Through Silicon Via parasitic extraction                     |      |

| 2.4         | Delay and power in 2D and 3D interconnects                   |      |

| 2.5         | Signaling, supply noise and reliability in 3D ICs            |      |

|             | 2.5.1 Signaling over TSVs                                    | 22   |

|             | 2.5.2 Supply Noise in 3D ICs                                 |      |

|             | 2.5.3 TSV Fault tolerance using redundancy                   |      |

| 3.THROUG    | H SILICON VIA PARASITIC EXTRACTION                           | 26   |

| 3.1         | TSV parasitic extraction methodology                         | 26   |

| 3.2         | Frequency dependency of TSV parasitics                       |      |

| 3.3         | Skin effect and TSV resistance                               |      |

| 3.4         | Mutual Inductance and Coupling Capacitance in 3x3 TSV Bundle |      |

| 3.5         | Circuit model                                                |      |

| 3.6         | Crosstalk                                                    | 41   |

| 4.SIGNALIN  | G ON THROUGH SILICON VIA BUNDLES                                  | 49           |

|-------------|-------------------------------------------------------------------|--------------|

| 4.1         | Single Ended Techniques                                           | 50           |

|             | 4.4.1 Voltage Mode Signaling                                      | 50           |

|             | 4.4.2 Current Mode Signaling                                      | 53           |

| 4.2         | Differential technique                                            | 56           |

| 4.3         | Energy/bit comparison of signaling techniques                     | 59           |

| 4.4         | Performance of signaling techniques for different TSV radius      |              |

|             | 4.4.1 Variation of resistance, inductance and capacitance with    | - 4          |

|             | TSV radius                                                        | 61           |

|             | 4.4.2 Variation of mutual inductance and coupling capacitance     | <i>-</i> ( ) |

|             | with spacing                                                      |              |

|             | 4.4.3 Performance of signaling techniques for different TSV radii | 65           |

| 5.ROBUSTN   | ESS ANALYSIS                                                      | 71           |

| 5.1         | Process Variations                                                | 71           |

|             | 5.1.1 Threshold Voltage variations                                | 72           |

|             | 5.1.2 Effective channel length variation                          |              |

| 5.2         | Voltage variations                                                | 78           |

| 5.3         | Impact of temperature                                             |              |

| 5.4         | Mechanical impact of temperature on TSV                           |              |

| 5.5         | TSV fault tolerance architectures                                 |              |

| 5.6         | Impact of stuck at faults                                         |              |

| 6.CONCLUS   | ION AND FUTURE WORK                                               | 90           |

| 6.1         | Conclusions                                                       | 90           |

| 6.2         | Future work                                                       |              |

| RIBI IOCD A | DUV                                                               | 03           |

## LIST OF TABLES

| Table | Pag                                                               | ge         |

|-------|-------------------------------------------------------------------|------------|

| 2.1   | 3D Interconnect Technologies based on Interconnect hierarchy [20] | 12         |

| 2.2   | ITRS roadmap for TSV dimensions for interconnects [20]            | 15         |

| 3.1   | Electrical parasitics at DC and 2 GHz frequency                   | 38         |

| 3.2   | Peak-peak voltage using full model and RLC model                  | <b>1</b> 1 |

| 4.1   | Energy/bit for various signaling techniques at 10 GBPS            | 50         |

| 5.1   | Impact of threshold voltage variation                             | 74         |

| 5.2   | Impact of effective channel length variation                      | 76         |

| 5.3   | Impact of mismatch in differential signaling                      | 78         |

| 5.4   | Impact of VDD (IR drop) variation on signaling techniques         | 79         |

| 5.5   | Impact of supply noise on signaling techniques                    | 31         |

| 5.6   | Impact of temperature on signaling techniques                     | 34         |

| 5.7   | Impact of fault TSV                                               | 39         |

## LIST OF FIGURES

| Figure | F                                                                   | Page |

|--------|---------------------------------------------------------------------|------|

| 1.1    | Long interconnects in 2D replaced with shorter 3D interconnects [6] | 3    |

| 1.2    | Heterogeneous 3D Integration[8]                                     | 4    |

| 2.1    | Various 3D Integration Technologies [19]                            | 10   |

| 2.2    | Schematic representing the key process modules in 3D ICs. [20]      | 15   |

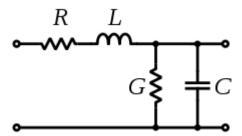

| 2.3    | RLC modeling of interconnect                                        | 16   |

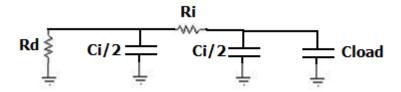

| 2.4    | Equivalent Circuit Model of Through Silicon Via GSG [21]            | 17   |

| 2.5    | 2D interconnect with driver and load                                | 19   |

| 2.6    | Simple model of 3D interconnect with driver and load                | 20   |

| 2.7    | Signaling over 3 parallel TSVs [12]                                 | 22   |

| 2.8    | Shielding technique                                                 | 23   |

| 2.9    | Arranging the TSVs in the form of blocks improves yield [13]        | 25   |

| 2.10   | Fault Recovery Mechanism a) No failure b) TSV_1 is failed [13]      | 25   |

| 3.1    | RLGC parasitic extraction methodology using Q3D                     | 28   |

| 3.2    | Q3D Schematic of 3x3 TSV Bundle                                     | 28   |

| 3.3    | RLGC transmission line model                                        | 30   |

| 3.4  | Linear dependency of R and G with frequency for $\sigma$ =100kS/m | 32 |

|------|-------------------------------------------------------------------|----|

| 3.5  | TSV configuration of a 3x3 bundle                                 | 32 |

| 3.6  | Inverse variation of L with frequency                             | 32 |

| 3.7  | Magnetic field line rings surrounding solid conductor [34]        | 33 |

| 3.8  | Cylindrical TSV with radius r surrounded by dielectric coating    | 34 |

| 3.9  | Skin effect in cylindrical conductor                              | 35 |

| 3.10 | Variation of resistance with frequency                            | 36 |

| 3.11 | 2x1 TSV structure                                                 | 39 |

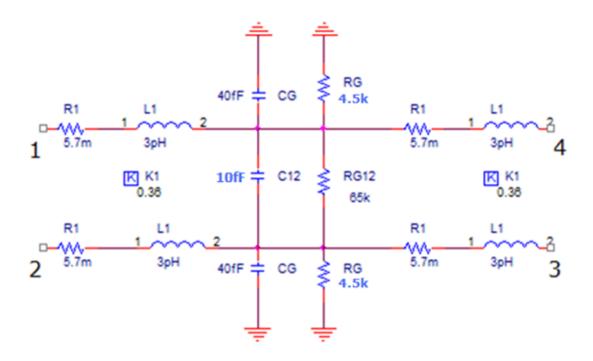

| 3.12 | Equivalent circuit of 2x1 TSV structure                           | 39 |

| 3.13 | Simplified RLC equivalent circuit of 2x1 TSV structure            | 40 |

| 3.14 | Simulation setup for analyzing crosstalk [35]                     | 41 |

| 3.15 | Circuit model for crosstalk analysis [35]                         | 42 |

| 3.16 | Simulation setup for crosstalk estimation in 3x1 (static case)    | 42 |

| 3.17 | Waveforms showing the crosstalk in 3x1 (static case)              | 43 |

| 3.18 | Simulation setup for 3x1 with switching inputs                    | 44 |

| 3.19 | Waveforms showing impact of crosstalk in 3x1 (switching case)     | 44 |

| 3.20 | Simulation structure for cross talk in 3x3 (static)               | 45 |

| 3.21 | Crosstalk in 3x3 structure (static)                      | 46 |

|------|----------------------------------------------------------|----|

| 3.22 | Simulation setup for worst case switching in 3x3         | 47 |

| 3.23 | Crosstalk in 3x3 (switching)                             | 48 |

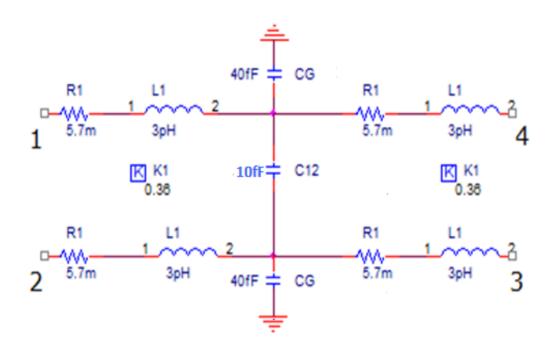

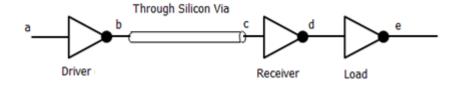

| 4.1  | SEVM signaling simulation setup for one of the TSVs [39] | 52 |

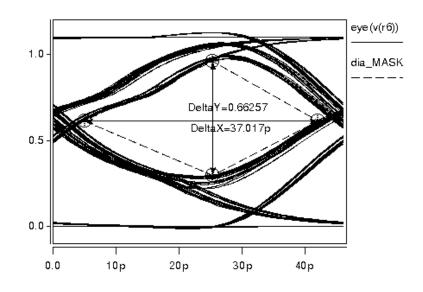

| 4.2  | Eye Diagram at 21.7 GBPS for SEVM signaling[39]          | 52 |

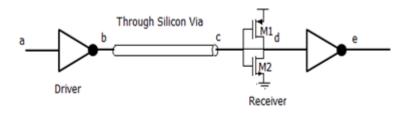

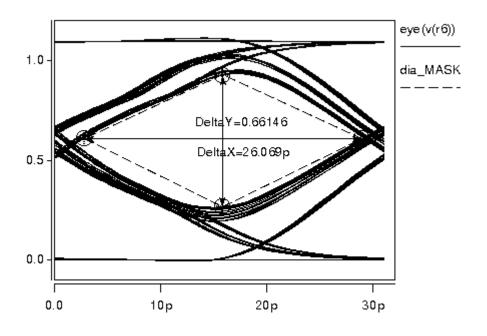

| 4.3  | Simulation setup for SECM1 [39]                          | 53 |

| 4.4  | Eye Diagram at 32.2 GBPS for SECM1 signaling             | 54 |

| 4.5  | Simulation setup for SECM2 signaling [39]                | 55 |

| 4.6  | Eye Diagram at 36.6 GBPS for SECM2 signaling             | 56 |

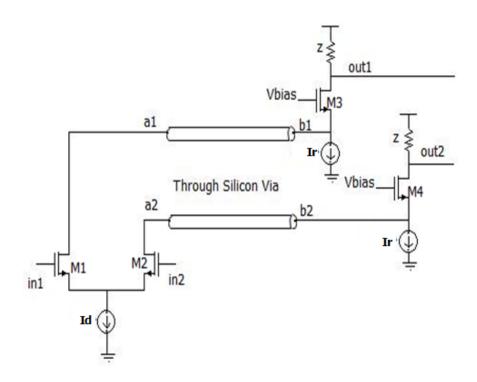

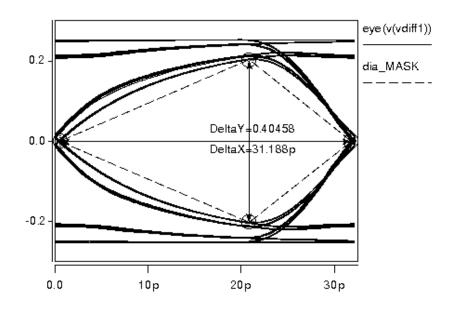

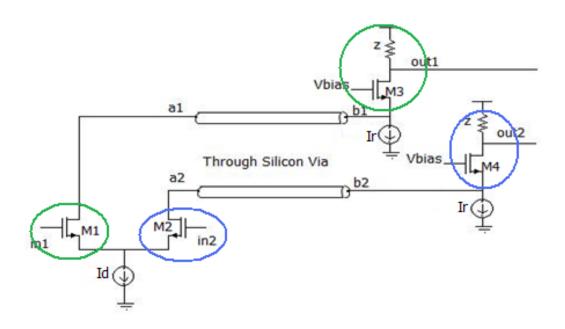

| 4.7  | Schematic for Differential Signaling technique [39]      | 57 |

| 4.8  | Differential output eye diagram at 31 GBPS               | 58 |

| 4.9  | One-bit emphasis circuit [42]                            | 59 |

| 4.10 | A pair of TSVs in a silicon substrate                    | 60 |

| 4.11 | Variation of resistance with TSV radius                  | 61 |

| 4.12 | Variation of TSV inductance with radius                  | 62 |

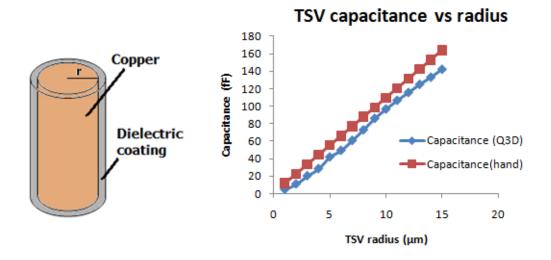

| 4.13 | Single TSV with dielectric coating                       | 63 |

| 4.14 | Coupling capacitance between a pair of TSVs              | 63 |

| 4.15         | Variation of capacitance with TSV radius                                |

|--------------|-------------------------------------------------------------------------|

| 4.16         | Variation of mutual inductance with TSV spacing                         |

| 4.17         | Variation of coupling capacitance with TSV spacing                      |

| 4.18         | Equivalent circuit for TSV delay estimation                             |

| 4.19         | Copper TSV and its capacitance for different TSV radius                 |

| 4.20         | Maximum data rates of signaling techniques for different TSV radii 69   |

| 5.1          | Corner case process variations between driver and receiver circuits 72  |

| 5.2          | Mismatch analysis for differential signaling                            |

| 5.3          | Voltage drop across different tiers in 3D IC [27]                       |

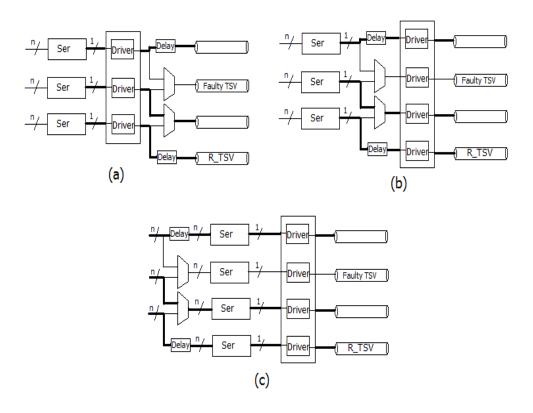

| 5.4          | Redundancy based fault tolerant architectures (a) Final stage MUX based |

| approach (b) | Driver decoupling MUX and TSV approach (c) MUX before Serializer        |

| approach     | 87                                                                      |

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Moore's Law and Interconnect Bottleneck

Any digital system is composed of three main components: memory, data path and control logic. The performance in such systems primarily depends on how well these components can perform the required tasks while communicating with each other. At a lower level the two key factors that determine the overall performance of a digital system are device (transistor) delay and the interconnect delay. One approach to achieve higher performance is by technology scaling. By scaling, the channel length of the device is reduced. In other words, the charge carriers have to travel smaller distances in order to reach the drain terminal from the source terminal. This reduces the amount of time taken to move charge carriers from source to drain, thus resulting in faster circuits. The voltage required to drive the charge carriers after creating the channel is also reduced. This is significant as it reduces the amount of power consumed by the system.

Reduced device and interconnect helps to add more components on a single integrated circuit in compliance with Moore's law [1]. According to Moore's law, the number of transistors that can be added to an integrated circuit doubles every two years. Thus technology scaling has been the driving force behind the semiconductor industry to stay in course with Moore's law. However in Deep Sub Micron (DSM) technologies, scaling of interconnect is not in proportion to that of devices. According to Amdahl's law, overall performance of the system is determined by the slowest unit in the system.

At DSM technology nodes, interconnect delay is higher compared to device delay. Thus, interconnect which is relatively slow compared to device in terms of delay determines the overall performance of an Integrated Circuit. Furthermore, the increased functionality due to scaling has led to the scenario where the overall power is dominated by the interconnects. Hence, there is a need for new methodology to tackle this problem of Interconnect Bottleneck.

#### **1.2** Motivation for 3D Integration

The primary reason for Interconnect bottleneck problem is that the interconnect delay increases in a quadratic manner with an increase in interconnect length [2] [3]. This is due to the linear dependency of both resistance and capacitance of interconnect on its length. Thus RC delay has a quadratic dependency on the wirelength. Techniques like tapered buffers and repeater insertion [4] are proposed to handle this interconnect bottleneck. In these techniques, buffers/repeaters are inserted in such a way that the repeater delay is equal to interconnect delay, thus making the delay a linear function of wirelength. But these repeaters in general are huge inverters consuming both area and power. There is a compromise in terms of power consumed [5] and area occupied with these approaches. One way to handle the interconnect bottleneck is to decrease the length of the interconnects. This was the motivation for the emergence of Three Dimensional Integrated Circuits.

#### 1.3 Benefits of 3D Integration

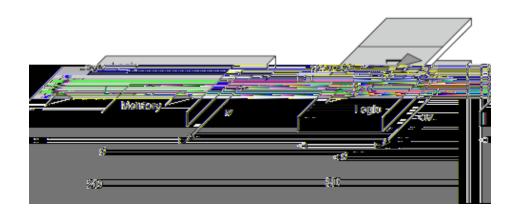

In 3D Integration, different dies can be connected using inter-tier interconnects that directly pass through the substrate. This is called Through Silicon Via (TSV) based 3D integration technology. In 3D integration, the average interconnect length is reduced significantly. Figure 1.1 shows 2D and 3D implementation of a particular design containing both Memory and Logic. In 2D, the logic and memory are placed next to each other and interconnect of length L is required to make a connection. The same design when implemented in 3D, reduces the interconnect length significantly. At system level, it allows the integration of memory with logic, thus allowing larger memory at lower access times, addressing the Memory Bottleneck problem more efficiently.

Figure 1.1 Long interconnects in 2D replaced with shorter 3D interconnects [6]

The inherent advantages of 3D ICs and their ability to go beyond Moore's Law make it more interesting to explore new designs based on 3D integration. Some of the potential benefits of 3D ICs are

#### 1) Higher levels of integration

- 2) Shorter interconnects

- 3) Heterogeneous integration

- 4) High speed operation

- 5) Reduced risk of reverse engineering [7]

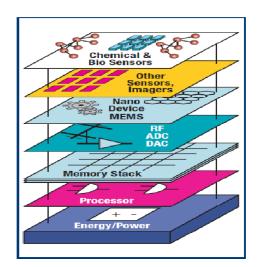

3D integration supports higher levels of integration for a given area. It also allows different designs to be implemented in different technologies. This is particularly useful for System on Chip (SoC) designs. In current 2D SoC designs, we are restricted to fabricate the entire chip in a single technology. Thus, 2D SoC designs require analog, digital and RF blocks to be implemented in a single technology. In 3D integration, different wafers can be stacked using TSVs. Hence it can be used for heterogeneous integration as shown in Figure 1.2.

Figure 1.2 Heterogeneous 3D Integration[8]

#### 1.4 Challenges in 3D Integration

In this section, some of the challenges associated with 3D ICs are discussed. Due to the increasing demand for higher functionality, processors with billions of transistors are in demand. The biggest challenge in such processors is the increasing power density and associated thermal issues. In order to fully utilize the benefits of 3D, it is beneficial to have as many tiers as possible. This increased stacking leads to an increased power density. In 3D ICs, the tier that is farthest from the heat sink will have the highest thermal resistivity and requires greater time to dissipate the heat. The results in [8] show that the temperature increases by 17K for 2 die stack and 33K for a 4 die stack.

Apart from thermal issues, several challenges related to 3D CAD tools remain unaddressed. Due to the addition of another dimension, the complexity in the design and verification increases. It becomes a more complicated problem in case of 3D ICs with heterogeneous integration. Due to this increased complexity, the design flow should include many more hierarchical levels. Apart from this, 3D thermal, signal and power TSVs have to be supported by the CAD tools. This demands the need for 3D tools from physical design to logic verification. Most of the logic and functionality verification tools available for 2D can be utilized for 3D circuits. CAD tools, like 3D CACTI [10] and NCSU3D PDK [11] which can support 3D layout up to 2 layers, are available. But the current version of NCSU 3DPDK cannot extract the RLC parasitics for 3D ICs. Another academic tool from MITLL can only support the 180nm 3D SOI technology. Considering the current 2D processor technology nodes, 180nm is far behind from ITRS roadmap of 28nm technology for 3D ICs.

Post silicon validation and testing for 3D ICs is a big challenge. Techniques that are used for 2D ICs can no longer be effective for 3D ICs. A new approach to handle these 3D ICs is yet to be developed. TSVs in contact with interconnects made of another material (aluminum or copper) are sensitive to temperature. Variations in temperature would lead to the production of a voltage relative to the temperature difference between the two materials. This voltage would affect the signal on the TSV, introducing a significant noise component. Reliability is one of the biggest concerns for 3D ICs. Although TSVs are excellent electrical conductors, a failed TSV can cause a number of known good dies that are stacked together to be discarded. Hence, it is a good idea to consider some fault tolerance scheme. However, this increases additional resources as well as TSV count. These challenges have to be addressed to extract the full benefits of 3D ICs.

#### 1.5 Problem Statement

This thesis is aimed at identifying *Robust signaling techniques for Through Silicon Via bundles*. Most of the earlier work on TSVs has been focused on electrical characterization and modeling. The first work on signaling over TSVs has been carried out by Weerasekera in [12]. But it was restricted to single ended signaling on 3 parallel TSV structures for a particular TSV technology. In order to extract the benefits of 3D, it is important to consider an array of TSVs (also called a TSV bundle), which helps in more efficient usage of die area and yield [13]. Hence, analyzing the signaling schemes over TSV bundles is important.

The following are the contributions of this work.

- We explored various signaling techniques like single ended voltage mode, current mode and differential technique. We obtained the maximum data rates for each of these signaling techniques and identified the factors that determine these numbers.

- Electrical parasitics of a TSV bundle vary with TSV radius. Due to lack of standards for signal TSVs, different research groups across the globe have different manufacturing technologies with different TSV radii. In this work, we considered various TSV radii to understand when a particular signaling technique (single ended or differential) might be beneficial to use.

- Robustness analysis of these signaling schemes is an important aspect. In this work, we analyze the impact of process, voltage and temperature variations on signaling over TSV bundles with focus on variations between the driver and receiver circuits which are residing on different dies.

Thus, in this work we explore signaling over through silicon via bundles, identify the key factors that determine the performance of a particular signaling technique and finally perform robustness analysis to identify the most optimum signaling technique for TSV bundles for a given TSV radius.

#### 1.6 Document Organization

The rest of this document is organized as follows:

- Chapter 2 deals with the necessary background information and related prior work.

- Chapter 3 is dedicated to TSV parasitic extraction and analysis of its electrical parasitics and crosstalk.

- Chapter 4 explores various signaling techniques over TSV bundles and their performance for various TSV radii.

- Chapter 5 contains the robustness analysis.

- Chapter 6 provides the conclusion and suggestions for future work.

#### **CHAPTER 2**

#### BACKGROUND AND PRIOR WORK

This chapter provides the necessary background information on the 3D integration with focus on Through Silicon Via (TSV) based 3D ICs and related prior work on TSV characterization and signaling techniques in such 3D ICs.

#### 2.1 3D Integration Technologies

Apart from its several other benefits, 3D integration allows stacking of dies with different technologies. Several techniques are used for stacking of the chips for 3D integration. Some of them place the individual chips one over the other and connect them across the periphery. These techniques suffer due to the reduced number of I/O connections like in 2D. Such packaging techniques like System in Package (SiP) and Chip Stack Multi-Chip-Module (MCM) do not integrate the chips into a single circuit. True benefits of 3D can be realized using TSV based 3D integration. In TSV based 3D integration, multiple chips can communicate with each other with the help of direct connections in the vertical direction. Such techniques in general are referred to as 3D integrated circuits or simply 3D ICs.

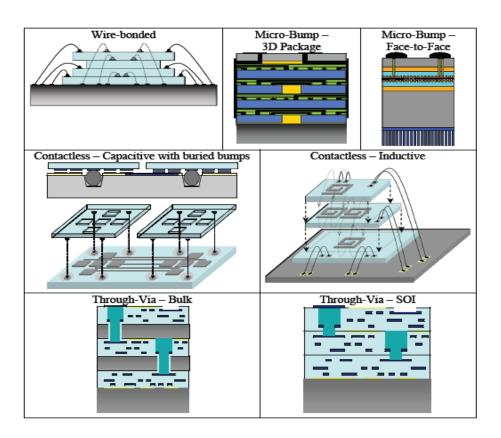

Integration techniques like wire-bonding, micro-bumps, through-vias, and contact less interconnects differ from each other in terms of their density and limitations in their usage. Wire-bonding is the most common approach for general purpose applications. These applications do not include the high performance processors or real time high performance embedded systems. However, it is not a true 3D integration as shown in

Figure 2.1. In this technique, all the connections should go through the chip carrier. The primary advantage of wire-bonding is its reduced complexity and low cost as it simply connects the dies across the periphery. The drawback of this approach is its limited integration density as the communication between the dies is restricted to the periphery, as shown in Figure 2.1. The number of metal layers needed for pads is also more due to the increased mechanical stress, which has the potential to destroy the devices under the pad due to extreme pressure.

Figure 2.1 Various 3D Integration Technologies [19]

Micro-bumps technology uses the solder to make connections on the surface of the die [12]. The mechanical stress in this technique is comparatively lower than that of the wire-bonding approach, thus requiring only one metal layer for pads. The number of layers it can handle is primarily limited by the heat assembled inside the package rather than the assembly process. Face-Face approach provides better performance due to the reduction in the parasitics. The primary disadvantage with face to face approach is its inability to support more than two tiers.

As discussed earlier, 3D circuits can be realized using TSVs. TSVs provide the most promising solution for high performance 3D Integrated Circuits. These TSVs can be assembled in a wafer-wafer approach or die-wafer approach, depending on the application and yield requirements. Generally, the wafer-wafer approach provides higher yield but supports fewer heterogeneous technology integration compared to die-wafer approach. These can be bonded in face-face or face-back manner depending on the application. TSVs with very small dimensions are obtained in Silicon on Insulator (SOI) technology [15] compared to the bulk approach [16]. This is primarily due to low substrate thickness in SOI and hence, for a given aspect ratio, smaller TSV diameters and therefore smaller pitches can be used in 3D SOI technology. The contactless interconnects are achieved using the capacitive and inductive coupling [17] [18] for communication between the layers. This approach is more suitable where there are 3-4 chips that are stacked and communication is required between the chips throughout the stack.

Structured definitions of 3D Interconnect technologies as presented in ITRS [20] are shown in Table 2.1. TSV based 3D integration for high performance applications falls into the category of 3D SICs and 3D ICs as mentioned in Table 2.1, and referred to as 3D ICs throughout the document. Since this work is primarily focused on developing robust

signaling techniques for high performance applications, we will discuss more about TSV based 3D ICs or simply 3D ICs in the next section.

Table 2.1 3D Interconnect Technologies based on Interconnect hierarchy [20]

| Level    | Suggested<br>Name                      | Supply<br>Chain          | Key Characteristics                                                                                                                                                                                                                                                                                    |  |

|----------|----------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Package  | 3D-<br>Packaging<br>(3D-P)             | OSAT<br>Assembly<br>PCB  | <ul> <li>Traditional packaging of interconnect technologies, e.g., wire-bonded die stacks, packageon-package stacks.</li> <li>Also includes die in PCB integration</li> <li>No through-Si-vias (TSVs)</li> </ul>                                                                                       |  |

| Bond-pad | 3D-Wafer-<br>level Package<br>(3D-WLP) | Wafer-level<br>Packaging | <ul> <li>WLP infrastructure, such as redistribution layer (RDL) and bumping.</li> <li>3D interconnects are processed after the IC fabrication, "post IC-passivation" (via last process). Connections on bond-pad level.</li> <li>TSV density requirements follow bond-pad density roadmaps.</li> </ul> |  |

| Global       | 3D-Stacked<br>Integrated<br>Circuit/<br>3D-System-<br>on-Chip<br>(3D-SIC /3D-<br>SOC) | Wafer Fab | <ul> <li>Stacking of large circuit blocks (tiles, IP-blocks, memory –banks), similar to an SOC approach but having circuits physically on different layers.</li> <li>Unbuffered I/O drivers (Low C, little or no ESD protection on TSN<sub>2</sub>)</li> </ul> |  |

|--------------|---------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|              |                                                                                       |           | TSVs).  TSV density requirement significantly higher than 3D-WLP.                                                                                                                                                                                              |  |

| Intermediate | 3D-SIC                                                                                | Wafer Fab | <ul> <li>Stacking of smaller circuit blocks, parts of IP-blocks stacked in vertical dimensions.</li> <li>Mainly wafer-to-wafer stacking.</li> <li>TSV density requirements very high.</li> </ul>                                                               |  |

| Local        | 3D-Integrated<br>Circuit<br>(3D-IC)                                                   | Wafer Fab | <ul> <li>Stacking of transistor layers.</li> <li>Common BEOL interconnect stack on multiple layers of FEOL.</li> <li>Requires 3D connections at the density level of local interconnects.</li> </ul>                                                           |  |

## 2.2 Through Silicon Via based 3D ICs

In Through Silicon Via based 3D ICs, as the name indicates, the vertical interconnect (TSV) will cut through the silicon substrate forming a connection between the two tiers. Generally the TSVs are filled with Cu or W metal and a dielectric coating is applied to prevent any diffusion of the metal into the silicon substrate. Several

approaches can be used to realize this and all the approaches have three common modules [20], as mentioned below.

- 1. Order of Through Silicon Via process

- 2. Wafer thinning, thin wafer handling and backside processing

- 3. The actual 3D-Stacking process.

Depending on the order in which the TSV process occurs with respect to the device fabrication process, the TSV process can be characterized into Via first, Via middle and Via last approach. In Via first approach, TSVs are fabricated before the Front End of Line (FEOL) process. In Via middle approach, TSVs are fabricated after the FEOL but before the Back End of Line (BEOL) process. In Via last approach, the TSV fabrication takes place after the BEOL. 3D ICs can also be differentiated depending on the method of 3D Bonding. Three common approaches are

- 1. Wafer to wafer (W2W) bonding

- 2. Die to Wafer (D2W) bonding

- 3. Die to die (D2D) bonding

Apart from this, secondary classification is made depending on whether it is a Face to face (F2F) bonding approach or Face to back (F2B) approach. Figure 2.2 represents various key process modules in TSV based 3D ICs.

Figure 2.2 Schematic representing the key process modules in 3D ICs. [20]

The performance of 3D ICs depends on the vertical interconnect (TSV) parasitics. Since the electrical characteristics of TSVs are primarily dependent on their physical material, geometry and dimensions, ITRS proposed the roadmap for the minimum TSV dimensions for interconnects as shown in Table 2.2. From Table 2.2, it can be observed that the pitches in general are twice the diameter. The minimum TSV depth can be as low as  $20\,\mu m$ .

Table 2.2 ITRS roadmap for TSV dimensions for interconnects [20]

| Global Level, W2W, D2W or D2D 3D-stacking | 2009-2012  | 2012-2015   |

|-------------------------------------------|------------|-------------|

| Minimum TSV diameter                      | 4-8 μm     | 2-4µm       |

| Minimum TSV pitch                         | 8-16 µm    | 4-8 μm      |

| Minimum TSV depth                         | 20-50 μm   | 20-50 μm    |

| Maximum TSV aspect ratio                  | 5:1 – 10:1 | 10:1 – 20:1 |

| Number of tiers                           | 2-3        | 2-4         |

Having discussed the key features of 3D integration technologies in general and TSV based 3D ICs in particular, it is important to understand the electrical characteristics of TSVs. Resistance, Inductance and Capacitance of the TSV play a crucial role in determining the overall performance of 3D ICs. As this work is focused on signaling techniques over TSV based 3D ICs, a background on TSV modeling and electrical characterization is presented in the following section.

#### 2.3 Through Silicon Via parasitic extraction

The purpose of TSV modeling is to obtain the equivalent circuits that can completely describe the electrical characteristics of the TSV. A simple RLC lumped model of a single interconnect is shown in Figure 2.3. It consists of a series resistance, series inductance and parallel capacitance. Depending on the geometrical dimensions of the interconnect, the values of R, L and C vary significantly.

Figure 2.3 RLC modeling of interconnect.

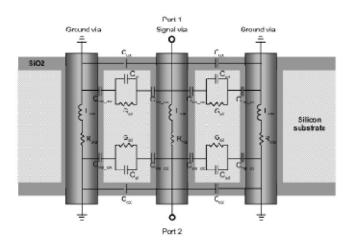

Through Silicon Via modeling should expand the single interconnect modeling of Figure 2.3 by including the impact of silicon substrate, dielectric insulator and coupling effects from surrounding TSVs. A simple electrical equivalent model of 3 parallel TSVs with one of them used as signal TSV and the remaining two connected to ground is

shown in Figure 2.4. Through Silicon Via, as the name suggests, is a via across the silicon substrate. Generally Cu or W is used as the metal filling for the TSV. SiO<sub>2</sub> dielectric can be used as coating over the metal to avoid any DC leakage of metal into the substrate.

Figure 2.4 Equivalent Circuit Model of Through Silicon Via GSG [21]

Several attempts have been made to understand and model the electrical characteristics of Through Silicon Vias. In [22], Friedman et al. have developed the closed form expressions for a 3D via. Closed form expressions for R, L and C developed in [22] are for a single 3D via. Though these expressions cannot be used directly for a group of TSVs, it provides a good model to understand the electrical behavior of Through Silicon Vias.

RLC coupling between two 3D Vias is investigated in [24]. Ansoft Quick 3D extractor [25] is used for RLC parasitic extraction. RLC parasitic extraction is carried out for various configurations by increasing the distance between the two 3D Vias. The results explained that the values of DC coupling capacitance and inductance decrease

with via separation and the AC R, L and C values tend to approach the extracted RLC values of a single 3D via. In [22] and [24], multiple configurations of parallel 3D vias with and without ground plane are considered for the extraction of RLC parasitics. The inclusion of ground plane did not affect the total resistance or inductance but drastically increased the capacitance. The closed form expressions developed are only for individual TSVs and hence cannot be used for obtaining all the parasitics, including coupling for all the surrounding TSVs in case of an array or bundle of TSVs.

Most recent work on developing equivalent lumped element models for n-port TSV models is presented in [23]. In [23], the authors proposed an equivalent lumped model for multi-TSV arrangements. The closed form expressions are developed in terms of physical dimensions and material properties. For checking the accuracy of the model, Q3D extractor is used for extracting the electrical parasitics of various TSV configurations. Each TSV is surrounded by a SiO<sub>2</sub> dielectric coating. The silicon substrate surrounding the TSVs is connected to ground plane.

In [26], electrical characterization of TSVs depending on number of TSV stacks is analyzed. S-parameters for a frequency range of 100MHz to 30GHz are obtained. The s-parameters from 3D full wave simulation are used to evaluate the signal integrity. (2<sup>7</sup>-1) PRBS data streams at 1 Gbps, 2 Gbps, 5 Gbps and 10 Gbps with a 10% rise and fall time are considered. The eye diagrams are obtained by passing the bit stream through a single TSV once and through the stack of 2, 5 and 10 TSVs next, to understand the impact of TSV stacks. It is observed that for a single TSV, capacitance is the dominating factor whereas for a stack of 10 TSVs resistance and capacitance both dominate.

#### 2.4 Delay and power in 2D and 3D interconnects

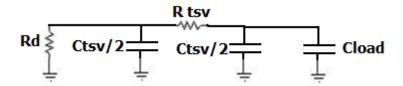

In this section, we will see after what length of 2D interconnect it is beneficial to switch to 3D interconnect both in terms of delay and power. For this study we consider 2D and 3D interconnects with similar driver and load. 2D interconnect model is shown in Figure 2.5. In this we considered a PI-model. PI-model gives Elmore delay equal to distributed RC model delay [27]. In 3D interconnects, capacitance is the dominating factor [28] and it is represented by  $C_{TSV}$  in Figure 2.6.  $R_{TSV}$  is not considered in Figure 2.6 as its resistance is much less compared to driver resistance ( $R_D$ ). The delay equation considering  $R_{TSV}$  and modeling it similar to 2D interconnect PI-model is given by

$$T_{3D} = 0.5R_DC_{TSV} + 0.5(R_D + R_{TSV})C_{TSV} + (R_D + R_{TSV})C_{Load}$$

$R_D$  is few hundreds of ohms and  $R_{TSV}$  is few tens of milli-ohms. Hence we can ignore  $R_{TSV}$  and model the TSV as a capacitive load. The authors in [28] also modeled the TSV as a capacitive load for the delay analysis through TSVs stating that  $R_{TSV}$  has negligible impact on delay.

Figure 2.5 2D interconnect with driver and load

Figure 2.6 Simple model of 3D interconnect with driver and load

Now, we will see the equivalent length of 2D interconnect that gives delay equal to that of a 3D interconnect.

Delay of 2D interconnect is given by

$$T_{2D} = 0.5R_DC_I + 0.5(R_D + R_I)C_I + (R_D + R_I)C_{Load}$$

$R_D$  is th driver resistance,  $C_I$  is interconnect capacitance,  $C_{Load}$  is load capacitance, Considering the unit length capacitance and resistance of interconnect in 45nm technology, we have capacitance per 1mm of length = 250fF and resistance per 1mm of length = 69.84 ohm [29].

Let us say capacitance per 1mm length = a

Resistance per 1mm length = b

Let the length of 2D interconnect be  $l_{2D}$ .

$$T = R_D(al_{2D}) + (al_{2D})(bl_{2D}) + (bl_{2D})C_{Load} + R_DC_{Load}$$

Now we will estimate the delay in case of 3D.

$$T_{3D} = R_D(C_{Load} + C_{TSV})$$

For a TSV radius of  $5\mu m$  and length of  $25\mu m$ , the equivalent length of 2D interconnect for equal delay is calculated to be  $154\mu m$ . If we do not consider the driver resistance for both 2D and 3D interconnects just to compare the 2D interconnect with TSVs, we see that the length of 2D interconnect that gives the delay equal to a TSV (of length 25  $\mu m$  and radius  $5\mu m$ ) is  $0.7\mu m$ . This is due to much lower resistance of TSV compared to 2D interconnect for a given length.

However when driver resistance is considered we observed that for 2D interconnects with length higher than 154 $\mu$ m it is beneficial to move to 3D interconnect (radius 5 $\mu$ m and length 25  $\mu$ m).

Now we will do similar estimation in terms of power. The interconnect power dissipation is given by

$$P = 0.5kfC_tV^2$$

P is the power dissipation

$C_I$  is interconnect capacitance

V is voltage on the interconnect

*k* is the activity factor

f is the frequency of operation

Considering similar activity factor, frequency and voltage on the interconnect we can estimate the length of 2D interconnect that dissipates equal power compared to 3D interconnect. The calculated length of 2D interconnect that has equal power dissipation

through the TSV of radius  $5\mu m$  and length  $25~\mu m$  is  $160\mu m$ . From this study we observed that it is beneficial to use 3D interconnects when length of 2D interconnect exceeds  $154\mu m$  (for delay) and  $160\mu m$  (for power).

# 2.5 Signaling, supply noise and reliability in 3D ICs

## 2.5.1 Signaling over TSVs

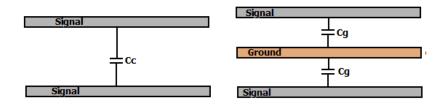

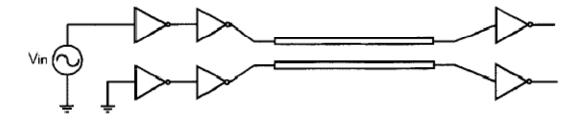

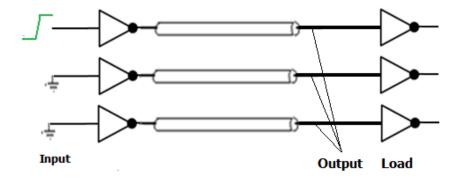

Most of the earlier work has been focused on electrical modeling and characterization of TSVs and very little has been explored on signaling techniques for 3D ICs. TSVs are excellent electrical interconnects but occupy significant area. In [12], the authors considered 3 parallel TSVs to explore signaling over TSVs and crosstalk for a particular TSV technology. Figure 2.7 shows the simulation setup for investigating the effect of crosstalk in 3 parallel TSVs used in [12].

Figure 2.7 Signaling over 3 parallel TSVs [12]

Simple voltage and current mode signaling using inverters as drivers is considered in [12]. For current mode, self-biased inverters are considered at the receiver to provide low impedance. A Pseudo Random Bit Sequence with 10ps rise and fall times and a period of 200ps is applied to 3 parallel TSVs. For the dimensions considered in [12],

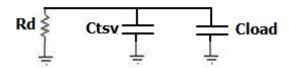

coupling is not negligible and shielding technique is employed to reduce the impact of coupling. In shielding technique, crosstalk between the conductors is reduced by introducing shield conductors between the signal conductors. Figure 2.8 shows how the introduction of a ground conductor turns coupling capacitance into capacitance to ground.

Figure 2.8 Shielding technique

## 2.5.2 Supply Noise in 3D ICs

Power distribution network plays a crucial role in determining the overall performance of the system. In general, supply noise can be categorized into two types:

- 1. Static Noise

- 2. Dynamic Noise

Static Noise is primarily due to the IR drop, as the supply voltage has to pass through the RLC networks associated with the power distribution scheme. The impact of IR drop can be handled by designing a more efficient and balanced power distribution network such as power grids. However, dynamic noise is due to the fluctuations in the supply voltage depending on the activity of the functional blocks. The inductance component of the supply network contributes to the dynamic noise. Maximum supply voltage drop occurs during the first droop. With increased scaling, the voltage levels have

come down significantly. Adding to this, the number of functional blocks on a single chip has increased tremendously, consequently demanding higher currents. Designing an efficient power distribution network in Deep Sub Micron (DSM) technologies has been the biggest challenge.

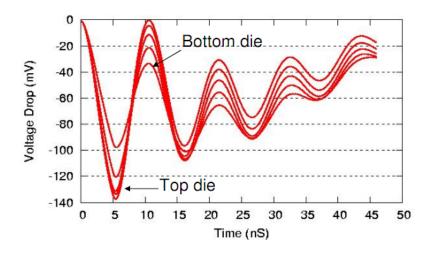

In 3D ICs, by stacking several tiers we are increasing the functionality of the single chip. Also the power distribution network should tackle the additional noise due to the activity in different tiers. 3D stack with k tiers would require k-times higher current compared to a single 2D chip with the same footprint. The supply noise amplitude in stacked 3D ICs is found to be as high as 10% of the supply voltage for a stack of 2 dies. The dynamic noise can increase to up to 240mV (24% of VDD) for a stack of 5 dies [27] [31].

## 2.5.3 TSV Fault tolerance using redundancy

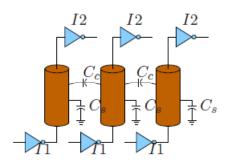

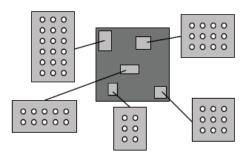

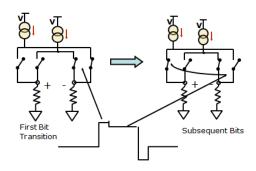

Improving the yield is another important aspect in 3D ICs. It is suggested in [13] that arranging the TSVs in the form of blocks, as shown in Figure 2.9, can provide higher yield compared to sprinkling the TSVs all around. Redundancy based fault tolerance is a simple solution to handle the problem with TSV faults. Each TSV block can contain a TSV chain which includes the fault tolerance architecture. A simple architecture shown in Figure 2.10 can be used as a fault recovery mechanism.

Figure 2.9 Arranging the TSVs in the form of blocks improves yield [13]

Figure 2.10 Fault Recovery Mechanism a) No failure b) TSV\_1 is failed [13]

From Figure 2.10 (b), it can be observed that all TSVs towards the right starting from TSV\_1 are shifted. This provides good performance improvement when compared to shifting only the failed TSV signal all the way to the end. Since it is the slowest signal that determines the overall performance, it is advantageous to shift all the signals by 1 unit as shown in Figure 2.10 (b).

In this chapter necessary background information is provided. TSV modeling and parasitic extraction, signaling techniques for TSVs and various factors that can impact the signaling over Through Silicon Vias like power supply noise are discussed. Through Silicon Via parasitic extraction and their electrical characteristics are covered in Chapter 3.

## **CHAPTER 3**

#### THROUGH SILICON VIA PARASITIC EXTRACTION

As we go into the Deep Sub-Micron (DSM) era, parasitic effects have to be considered. 3D field solvers provide more accurate information on the parasitic values compared to first order analytical expressions. In general, these field solvers require significant computation time and resources. Most of the parasitic effects of the 2D interconnects are well studied and simple analytical models are developed. Since 3D ICs are still in the phase of development, simple electrical models of 3D interconnects are not yet available. This is primarily due to the lack of standardization, which resulted in a wide range of TSV dimensions that can be chosen depending on the application. As mentioned in Chapter 1, there is no proper CAD support for 3D interconnects. Currently NCSU3DPDK is the only available academic PDK for 3D ICs using bulk CMOS technology. It is still in the development phase and currently does not support RLC parasitic extraction and post layout simulation. Hence, 3D field solvers are generally used to obtain the electrical parasitics of TSV.

In this chapter, we first explain the methodology used for the extraction of RLGC parasitics of Through Silicon Via bundle and their frequency dependency. Q3D extractor, a 3D field solver from Ansoft, is used for the parasitic extraction.

## 3.1 TSV parasitic extraction methodology

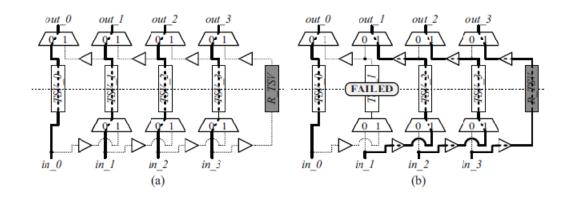

The step-by-step procedure to be followed for the extraction of TSV parasitics using Q3D extractor is shown in Figure 3.1.

Figure 3.1 RLGC parasitic extraction methodology using Q3D

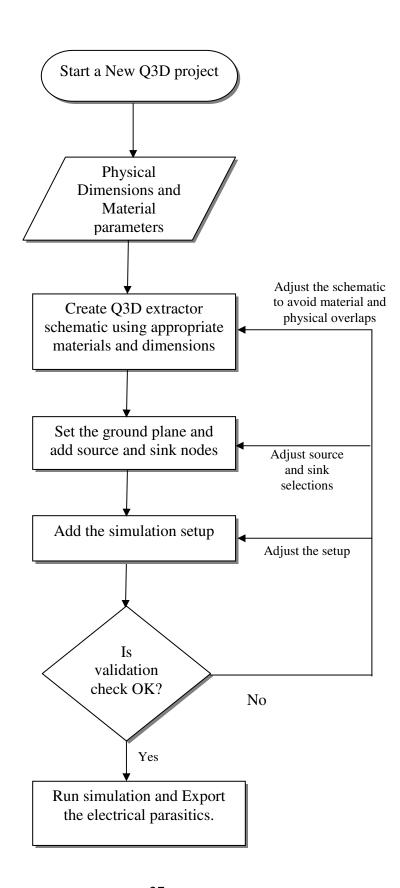

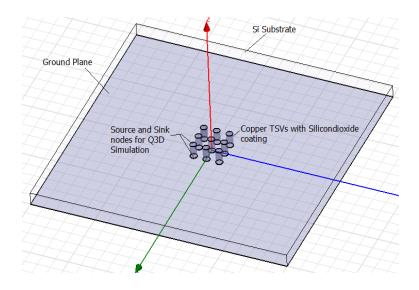

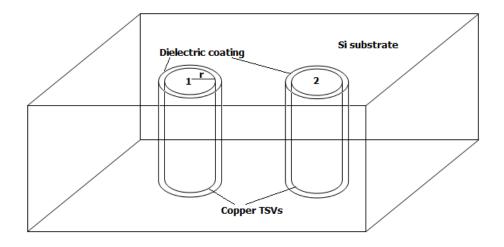

Schematic of 3x3 TSV bundle developed in Q3D extractor is shown in Figure 3.2.

Figure 3.2 Q3D Schematic of 3x3 TSV Bundle

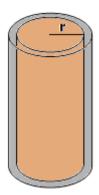

Q3D schematics of Through Silicon Vias with dielectric coating over them are made and embedded in a silicon substrate. Copper is chosen to be the TSV metal fill. Silicon is chosen as the substrate material. Silicon dioxide is used as a dielectric material. The geometrical dimensions of TSV bundles shown in Figure 3.2 are

- 1. TSV diameter =  $10 \mu m$

- 2. TSV pitch =  $20 \mu m$

- 3. TSV height =  $25 \mu m$

- 4. Thickness of dielectric coating over TSV =  $0.2 \mu m$

- 5. Silicon substrate =  $400 \mu m \times 400 \mu m$

Once the schematic is ready, the source and sink nodes along with the ground plane are defined. In the simulation setup, a new frequency setup is created and the frequencies are selected ranging from 100 MHz to 35 GHz. A validation check is performed before running the parasitic extractor. It checks for 3D Model boundaries, excitations, material overlaps and analysis setup. If the validation check fails, check for the errors and modify the appropriate material parameter or geometry. Some of the most common errors are with material overlaps and parametric setup. Once the validation check is complete, the parasitic extractor is executed and the results are obtained in a Touchstone file, which consists of RLGC values for DC and all the frequencies defined in the frequency setup. The Touchstone file can be given as an input for frequency dependent simulations in HSPICE.

## 3.2 Frequency dependency of TSV parasitics

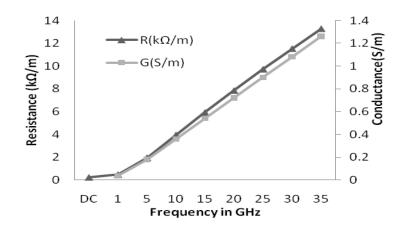

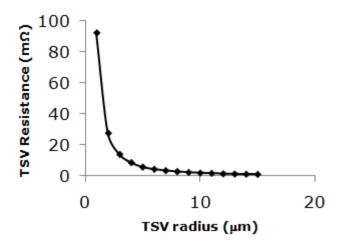

TSV parasitics, particularly Resistance (R), Conductance (G) and Inductance (L) vary with frequency. The variation of resistance and conductance with frequency for a substrate conductivity of 100kS/m and the previously mentioned TSV dimensions are shown in Figure 3.4. It can be observed that the resistance of the TSV and the conductance through the dielectric increase with frequency. The increase of TSV resistance with frequency is due to the skin effect. As the frequency increases, the skin depth decreases thus reducing the overall cross section area for the currents to flow through the conductor (TSV). Since the current flowing through the conductor decreases, the resistance of the conductor increases. In other words, for a given current, the cross section area A decreases, thus increasing the resistance according to

$$R = \frac{\rho l}{A}$$

R – Resistance of the conductor

$\rho$  - Resistivity of the conducting material

*l* - Length of the conductor

A – Area of cross section

The conductance per unit length mentioned is the leakage conductance and not the conductance of the TSV. This is measured in perpendicular direction to the TSV length. Consider a simple RLGC transmission line model as shown in Figure 3.3. As we double the length of the transmission line, the series resistance R of the conductor doubles. However the shunt resistance of the conductor is halved. As we double the length of the line there is more area through which the leakage current can flow, reducing the shunt resistance. In other words, shunt conductance doubles. Hence we can say that shunt resistance or the leakage resistance is nothing but the inverse of shunt conductance 'G'.

Figure 3.3 RLGC transmission line model

$$G = \frac{1}{R_{Leakage}}$$

The dielectric constant of a material is a complex quantity and is represented as

$$\varepsilon_r = \varepsilon_r' - i \varepsilon_r'' [34]$$

$\varepsilon_r$  is the complex dielectric constant

$\varepsilon_r$  representing the real component

$\varepsilon_r$  representing the imaginary component

The angle of the vector with the real axis is called the loss angle  $\delta$ .

$$tan(\delta) = \varepsilon_r^{\prime\prime}/\varepsilon_r^{\prime\prime}$$

$$\varepsilon_r^{"} = \varepsilon_r^{"} \tan(\delta)$$

For the voltage  $V = V_0 \exp(i\omega t)$ , the current through the dielectric is given by

$$I = C \, dV/dt = iC\omega V = i\varepsilon_r \, C_0\omega V = i\varepsilon_r^{'} \, C_0\omega V + \varepsilon_r^{''} \, C_0\omega V$$

In the above equation, the real part represents the loss and the imaginary part represents the capacitive current.

Now,

$$R_{Leakage} = V/Real(I) = V/(\varepsilon_r^{"}C_0\omega V) = 1/(\omega C \tan(\delta))$$

Conductance

$$G = 1/R_{Leakage} = \omega C \tan(\delta)$$

Thus leakage conductance G increases with the frequency.

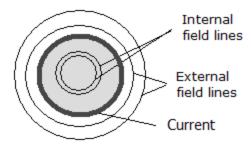

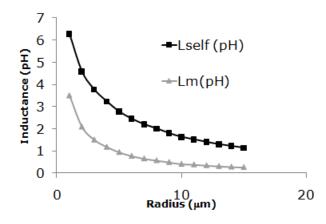

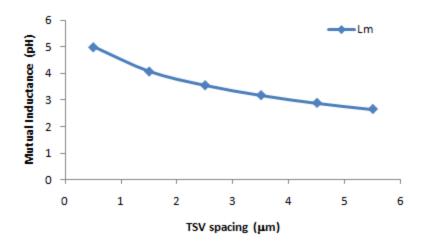

The inductance in a bundle is comprised of self and mutual inductance components. For a 3x3 bundle, mutual inductance between two TSVs varies with spacing.

Considering the arrangement of TSV bundle as shown in Figure 3.5, it can be observed that the TSV-0 is surrounded by a maximum of 8 TSVs. We denote the total mutual inductance by TSV-0 as Lm1. Similarly the total mutual inductance by the TSVs at 1, 3, 6 and 8 is denoted by Lm2 and by the TSVs 2, 4, 5 and 7 is denoted by Lm3. In

Figure 3.6, Ls represents the self inductance and Lm1, Lm2 and Lm3 represent the mutual inductances as discussed above.

Figure 3.4 Linear dependency of R and G with frequency for  $\sigma$ =100kS/m.

Figure 3.5 TSV configuration of a 3x3 bundle

Figure 3.6 Inverse variation of L with frequency

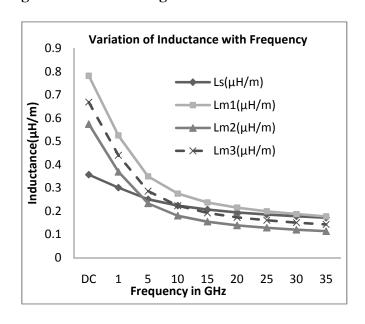

At higher frequencies, the current inside the conductor decreases due to skin effect. Consider a conductor cross-section as shown in Figure 3.7. Total inductance is the sum of internal and external self inductance. As the frequency increases, the current redistributes inside the conductor away from the center thus decreasing the number of internal field rings surrounding the current. This results in the reduction in internal inductance of the conducting rod, thus reducing the total inductance. This is observed in Figure 3.6 where the inductance values decrease with frequency.

Figure 3.7 Magnetic field line rings surrounding solid conductor [34]

#### 3.3 Skin effect and TSV resistance

The resistance of a conductor is evaluated using the formula

$$R = \frac{\rho l}{A}$$

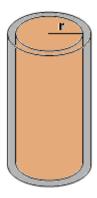

R is the resistance of the conductor,  $\rho$  is the resistivity of the conducting material, l is the length of the conductor and A is the area of cross-section. Now let us consider a cylindrical TSV of radius r as shown in Figure 3.8.

Figure 3.8 Cylindrical TSV with radius r surrounded by dielectric coating

The resistance of cylindrical TSV of length l and radius r as considered in Figure 3.8 is given by

$$R = \frac{\rho l}{\pi r^2}$$

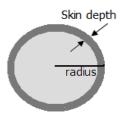

Here the area is taken as the total cross-section area of the cylinder given by  $A = \pi r^2$ . This is true for evaluating DC resistance. However, the current distribution in a conductor is not uniform throughout its cross-section. At higher frequencies the current tends to travel along the outside of the conductor and this phenomenon is known as "Skin effect" i.e. the tendency of the current to flow on the skin (outer surface) of the conductor. As a result of this, the effective area through which the current can flow decreases resulting in increase in the resistance for higher frequencies.

Figure 3.9 Skin effect in cylindrical conductor

The resistance of the interconnect also depends on the skin effect of the substrate depending on the substrate conductivity of silicon [36][37][38]. For substrates with very high conductivity, the skin depth will be low and results in skin effect due to substrate. This results in large variations in current density and current distribution in substrate and leads to variations in interconnect resistance for high frequencies [38]. In substrates with high conductivity, the effective resistance of the interconnect at high frequencies will increase due to both substrate skin effect and the interconnect skin effect. However for substrates with low substrate conductivity, the impact of substrate skin effect is little as the substrate skin depth increases with reduction in substrate conductivity. The skin depth is given by

$$\delta_s = \sqrt{\frac{2\rho}{2\pi f \mu_0 \mu_R}}$$

$\delta_s$  is the skin depth, f is the frequency,  $\rho$  is the resistivity of the material and  $\mu_0$  is the permeability of free space and  $\mu_R$  is the relative permeability of the material.

For substrates with low conductivity, the dominant factor is the conductor skin effect. As discussed earlier, the resistance of a conductor varies with frequency due to skin effect. For hand calculations, simple expression for skin depth is considered for understanding

its impact on resistance. Once the skin depth is calculated, we can obtain the resistance using the formula

$$R = \frac{\rho l}{A}$$

and  $A = \pi r^2 - \pi (r - \delta_s)^2$

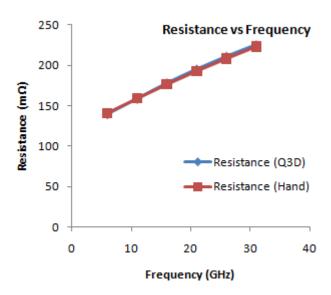

The resistance obtained using hand calculation and those obtained from Q3D are shown in Figure 3.10.

Figure 3.10 Variation of resistance with frequency

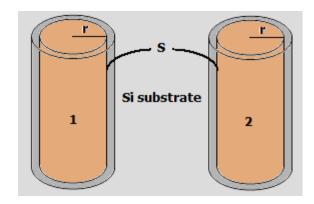

## 3.4 Mutual Inductance and Coupling Capacitance in 3x3 TSV Bundle

In a 3x3 TSV bundle, each TSV will have coupling from all other TSVs. Considering the TSV bundle arrangement shown in Figure 3.5, the total mutual inductance of the center TSV (numbered 0) is

$$Lm1 = L_{01} + L_{02} + L_{03} + L_{04} + L_{05} + L_{06} + L_{07} + L_{08}$$

Due to symmetry,

$$L_{01} = L_{03} = L_{06} = L_{08}$$

$$L_{02} = L_{04} = L_{05} = L_{07}$$

Similarly the total mutual inductance by TSV 1, TSV 3, TSV 6 and TSV 8 is the same and it is equal to

$$Lm2 = L_{12} + L_{13} + L_{14} + L_{15} + L_{16} + L_{17} + L_{18} + L_{10}$$

for TSV 1

Due to symmetry,

$$L_{13} = L_{16}$$

;  $L_{12} = L_{14}$ ;  $L_{15} = L_{17}$

The total mutual inductance by TSV 2, TSV 4, TSV 5 and TSV 7 is the same and is given by

$$Lm3 = L_{20} + L_{21} + L_{23} + L_{24} + L_{25} + L_{26} + L_{27} + L_{28}$$

Due to symmetry,

$$L_{20} = L_{21} = L_{23}$$

$$L_{24} = L_{25}$$

and  $L_{26} = L_{28}$

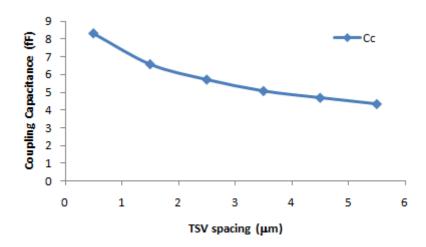

Similar to inductance, the coupling capacitance depends on the location of the TSVs.

The total coupling capacitance of the center TSV is given by

$$Cc1 = C_{01} + C_{02} + C_{03} + C_{04} + C_{05} + C_{06} + C_{07} + C_{08}$$

Due to symmetry, we have

$$C_{01} = C_{03} = C_{06} = C_{08}$$

and  $C_{02} = C_{04} = C_{05} = C_{07}$

Similarly, the total coupling capacitance of each of TSV 1, TSV 3, TSV 6 and TSV 8 is the same and it is equal to

$$Cc2 = C_{12} + C_{13} + C_{14} + C_{15} + C_{16} + C_{17} + C_{18} + C_{10}$$

for TSV 1

Due to symmetry,

$$C_{13} = C_{16}$$

;  $C_{12} = C_{14}$ ;  $C_{15} = C_{17}$

The total coupling capacitance of each of TSV 2, TSV 4, TSV 5 and TSV 7 is the same and is given by

$$Cc3 = C_{20} + C_{21} + C_{23} + C_{24} + C_{25} + C_{26} + C_{27} + C_{28}$$

Due to symmetry,

$$C_{20} = C_{21} = C_{23}$$

$$C_{24} = C_{25}$$

and  $C_{26} = C_{28}$

The extracted values from the field solver at DC and 2GHz frequency are shown in Table 3.1. Self Capacitance and Self Inductance values are denoted under Cs and Ls. As discussed earlier, Lm1, Lm2 and Lm3 represent the mutual inductance and Cc1, Cc2 and Cc3 represent coupling capacitance experienced by different TSVs depending on their location.

Table 3.1 Electrical parasitics at DC and 2 GHz frequency

| Freq. | R (mΩ) | Ls (pH) | Lm1(pH) | Lm2(pH) | Lm3 (pH) | Cs (fF) | Cc1 (fF) | Cc2 (fF) | Cc3 (fF) |

|-------|--------|---------|---------|---------|----------|---------|----------|----------|----------|

| DC    | 4.88   | 7.14    | 15.648  | 11.515  | 13.364   | 116.34  | 0.104    | 0.076    | 0.049    |

| 2GHz  | 16.38  | 5.66    | 7.768   | 5.486   | 6.536    | 116.34  | 0.104    | 0.076    | 0.049    |

From Table 3.1, it can be observed that the coupling capacitance is less compared to self capacitance. This is due to higher spacing between the TSVs and the substrate acting as a shield. Total mutual inductance values are comparable to self inductance values.

## 3.5 Circuit model

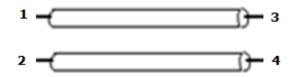

In this section a simplified circuit model is presented. The simulations are carried out to check the accuracy of the simplified circuit model with that of the full circuit model obtained from the Q3D extractor. Consider a simple 2x1 structure (2 pair of TSVs) as shown in Figure 3.11. The TSV radius is  $5\mu m$  and length  $25\mu m$ . Its equivalent circuit is shown in Figure 3.12.

Figure 3.11 2x1 TSV structure

Figure 3.12 Equivalent circuit of 2x1 TSV structure

Simulations are carried out to check the accuracy of the simplified RLC equivalent circuit compared to the full circuit model. The detection of the signal at the receiver circuit depends on the eye opening of the signal at the receiver. Peak to peak voltage of the noise indicates the distortion in the eye opening and hence chosen as a metric. For a 2x1 structure as shown in Figure 3.11, port 1 is given a rising input and the peak to peak voltage at the outputs 3 and 4 are obtained. A similar analysis is carried for 3x1 structure.

Figure 3.13 Simplified RLC equivalent circuit of 2x1 TSV structure

The peak-peak noise voltages using RLC equivalent circuit model and full circuit model are shown in Table 3.2. It can be observed that the results from RLC circuit model are close to full circuit model.

Table 3.2 Peak-peak voltage using full model and RLC model

| Output Node   | $V_{(p-p)}$ full model (V) | $V_{(p-p)}$ RLC model (V) |

|---------------|----------------------------|---------------------------|

| 2x1 aggressor | 0.068                      | 0.067                     |

| 2x1 victim    | 0.061                      | 0.062                     |

| 3x1 aggressor | 0.054                      | 0.057                     |

| 3x1 victim-1  | 0.059                      | 0.060                     |

| 3x1 victim-2  | 0.043                      | 0.047                     |

## 3.6 Crosstalk

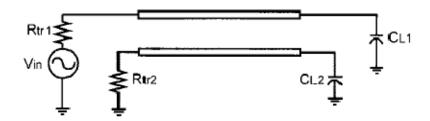

In this section, crosstalk in 3x1 and 3x3 structures is examined. Simulation setup for crosstalk analysis for 2D interconnects is suggested in [35]. The simulation setup for crosstalk analysis suggested in [35] is shown in Figure 3.14. Figure 3.15 shows the equivalent circuit model. The inverter on the driver side is modeled as the resistance Rtr and the inverter on the receiver is modeled as a capacitive load  $C_L$  as shown in Figure 3.15.

Figure 3.14 Simulation setup for analyzing crosstalk [35]

Figure 3.15 Circuit model for crosstalk analysis [35]

In this work, we consider 3x1 and 3x3 structures for crosstalk analysis. For each of these two structures we consider two cases – static case and switching case. By static case we mean that only one of the TSVs will have a switching signal and rest of the TSVs are given a static input. In switching case, we have center TSV switching in opposite direction relative to rest of the TSVs. To understand the crosstalk in interconnects, similar simulation setup as in Figure 3.14 is considered. Simulation setup for 3x1 structure for static case is shown in Figure 3.16. In Figure 3.16, on the input side we have one node with a rising input and the other two nodes are given a "ground" input. The simulation results are shown in Figure 4.

Figure 3.16 Simulation setup for crosstalk estimation in 3x1 (static case)

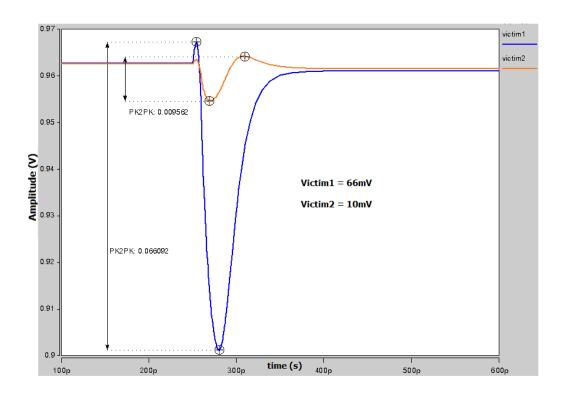

Simulation results are shown in Figure 3.17. From Figure 3.17, it can be observed that the peak to peak voltage of noise induced due to the aggressor on the other TSVs

decreases as we move away from it. This is due to the reduction in coupling between the TSVs. Assuming 3 TSVs arranged as 3x1 (3 parallel TSVs), the coupling between 1 and 2 will be high compared to the coupling between 1 and 3. This is both due to the increase in spacing as well as the shielding provided by the middle TSV.

Figure 3.17 Waveforms showing the crosstalk in 3x1 (static case)

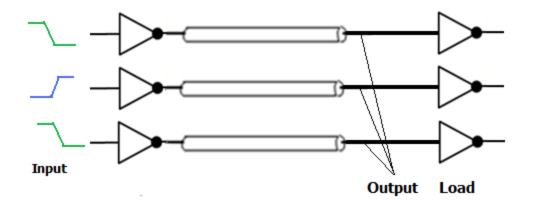

However, when all the TSVs are used for signaling, the worst case switching scenario occurs when the center TSV switches in the opposite direction relative to rest of the TSVs. Now let us consider this scenario shown in Figure 3.18 to analyze the crosstalk in worst case switching.

Figure 3.18 Simulation setup for 3x1 with switching inputs

Figure 3.19 Waveforms showing impact of crosstalk in 3x1 (switching case)

The simulation results for worst case switching in 3x1 structure is shown in Figure 3.19. In switching case all the TSVs have a changing input. However the propagation delay depends on the relative switching between the conductor and its neighboring nodes. For 3x1 switching case, the center TSV will suffer more due to

crosstalk. This is because it has two neighbors switching in the opposite direction resulting in change in voltage of 4VDD. For the edge TSVs, there is only one switching neighbor resulting in 2VDD change in the voltage. From the simulation results it can be observed that the center TSV has higher delay compared to edge TSV.

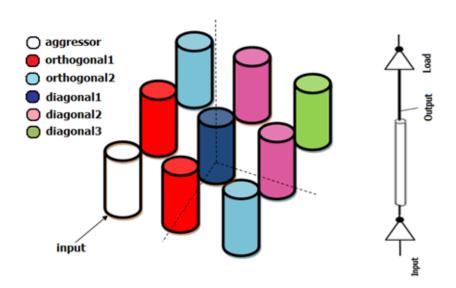

Now we will discuss the crosstalk in 3x3 TSV structure. For static case, we will give a rising input to one of the TSV drivers and the rest of the drivers are "grounded" at the input. Depending on the location of the TSV with respect to aggressor node, the noise due to crosstalk varies. 3x3 TSV structure indicating the aggressor and victim TSV nodes is shown in Figure 3.20. TSVs located orthogonal to the switching TSV are named as orthogonal1 and orthogonal2, orthogonal1 being the TSV immediately orthogonal to the switching TSV and orthogonal2 being the TSV next to orthogonal1. TSVs that are diagonal to switching TSV are named as diagonal1, diagonal2 and diagonal3 as mentioned in Figure 3.20.

Figure 3.20 Simulation structure for cross talk in 3x3 (static)

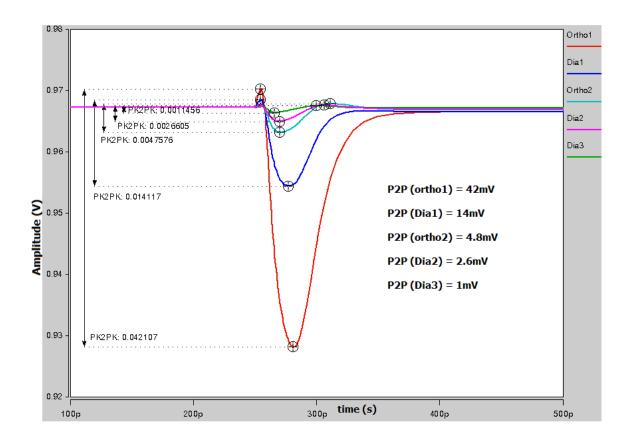

Simulation results are shown in Figure 3.21. In a 3x3 TSV structure, crosstalk noise depends on the location of victim TSV relative to aggressor. The TSVs that are immediately close to aggressor suffer more compared to rest of the TSVs. It can be noticed that the immediate orthogonal TSVs (in red) and immediate diagonal TSV (in dark blue) will have higher crosstalk noise compared to rest of the TSVs. The crosstalk on non immediate neighbors is less due to increased spacing as well as shielding by the immediate neighbors.

Figure 3.21 Crosstalk in 3x3 structure (static)

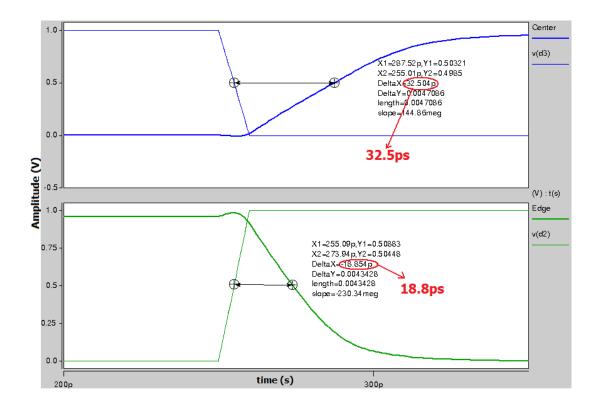

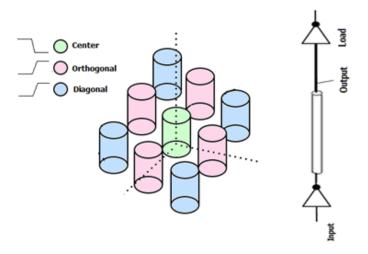

Now we will consider the switching case in 3x3 structure. As discussed earlier, when all the TSVs in a 3x3 bundle are used for signaling, we will have worst case noise when the center TSV switches in the opposite direction relative to rest of the TSVs. Let

us call this the worst case switching scenario and simulation setup is shown in Figure 3.22. The center TSV and rest of the TSVs switch in opposite directions. All the TSVs surrounding the center TSV can be categorized into orthogonal and diagonal TSVs depending on their relative location with respect to the center TSV in the bundle. Simulation results are shown in Figure 3.23.

Figure 3.22 Simulation setup for worst case switching in 3x3

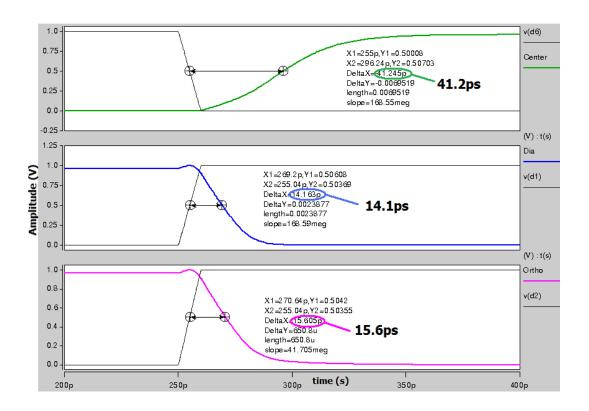

From Figure 3.23 it can be observed that the center TSV has the maximum delay due to crosstalk. The delay through the orthogonal TSV is 14.1ps and the delay through the diagonal TSV is 15.6ps. In this chapter, we dealt with TSV parasitic extraction, circuit model and crosstalk in 3x1 and 3x3 structures. Signaling techniques and their performance for different TSV radii will be discussed in Chapter 4.

Figure 3.23 Crosstalk in 3x3 (switching)

## **CHAPTER 4**

#### SIGNALING ON THROUGH SILICON VIA BUNDLES

Signaling techniques play a crucial role in determining overall performance of a digital system. A typical signalling system consists of a transmitter/driver, channel and a receiver. Depending on the electrical representation of the data, signaling techniques are classified into voltage mode/high impedance mode and current mode/ low impedance mode.

In voltage mode, the signal is represented by the voltage levels, whereas the signal is represented by the currents in current mode. In general, both voltage and current mode primarily depend on the termination at the receiver. If the receiver used is a low impedance termination, then it is more suitable for current mode transmission, since all the current can flow into the receiver as opposed to flowing into ground through a low impedance path. If the receiver is a high impedance node, then voltage mode is suitable since all the voltage can be applied at that node. Based on the number of interconnects used for signal transmission, signaling techniques can be classified into two types.

- a) Single ended signaling technique

- b) Differential signaling technique

In single ended techniques, there is a common reference for all the signals at both transmitter and the receiver. At the receiver side, the signal is compared with this common reference to determine whether the transmitted bit is 0 or 1. In differential signaling technique, each signal requires two interconnects. At the driver side, both signal

and its complement are transmitted. At the receiver side, these two signals are compared to identify the transmitted bit.

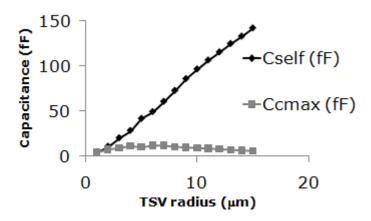

In this chapter we present various signaling techniques for TSV based 3D ICs. Single ended and differential signaling techniques are explored. Maximum data rates and energy/bit for each of the signaling techniques are obtained. All the driver and receiver circuits are designed using 45nm CMOS technology using NCSU PDK. As TSV parasitics vary with its radius, we extracted the parasitics for TSV radii ranging from 1 µm to 15 µm and maximum data rates are determined for each of the signaling techniques determined above.

## 4.1 Single Ended Techniques

# **4.4.1** Voltage Mode Signaling

Voltage Mode signaling is also called high impedance mode signaling due to the high input impedance of the receiver circuit. The driver and receiver circuit in voltage mode signaling can be realized using a simple inverter. Some of the crucial parameters to be considered while designing driver and receiver circuits are

- Rise and Fall times

- Maximum Data rate

- Power consumption

Rise and fall times at the output are important for power and performance issues. For a simple inverter circuit, during the transition from 0 to 1 or 1 to 0, for certain duration both NMOS and PMOS are ON. During this period, there is a direct current path

from VDD to ground which contributes to dynamic leakage power. In general, longer rise and fall times reduce the overall performance. One way to obtain sharp rise and fall times is to increase the drive strength. Hence, it is important to determine the drive strength to increase the data rate. The rise and fall times are determined by the sizing of pull up and pull down networks. For voltage mode signaling with inverters as drivers and receivers, the rise and fall times are determined by the P/N ratio of the inverter and the absolute widths of the transistors. Based on the simulation results, the P/N ratio for equal rise and fall times is found to be 3.5. As the size of the inverter increases, its drive strength increases. However, it also increases the load capacitance due to the driver. After certain point, the reduction in delay due to the increase in drive strength is overcome by the increase in the capacitance. Based on this, simulations are carried out to obtain the absolute widths with performance as primary objective.

The maximum data rate for a particular signaling scheme depends on load capacitance of the driver, interconnect capacitance and the input capacitance of the load. For voltage mode signaling, a unit inverter driving a Fan Out of 4 (FO4) load is considered as the receiver. The parasitics for 3x3 TSV bundle are obtained from Q3D extractor and provided as input touchstone file for HSPICE simulation. Simulations are performed to obtain the maximum datarate that can be achieved using Single Ended Voltage Mode signaling (SEVM). Based on the simulations for minimum delay each TSV of the 3x3 bundle is driven by the 64 x inverter. All the TSVs in a bundle are driven in the same way. The simulation setup for one of the TSVs in 3x3 bundles for SEVM is shown in Figure 4.1.

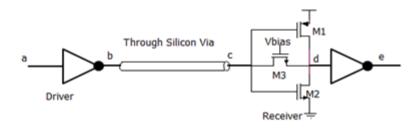

Figure 4.1 SEVM signaling simulation setup for one of the TSVs [39]

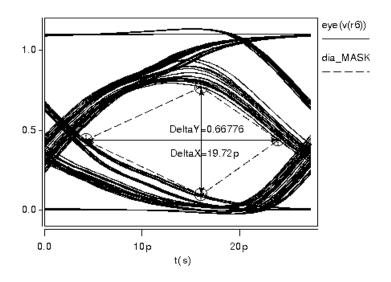

The center TSV will experience the maximum coupling in the bundle. Hence, all the simulation results are taken at the nodes of the center TSV. Simulations are performed in HSPICE with 2<sup>7</sup> – 1 Pseudo Random Bit Sequence (PRBS) as inputs. The eye diagrams are plotted at the output of the 1x receiver, *node'd'* in Figure 4.1. A rise and fall time of 10ps is given at the input. Targeting an eye height of 60% of VDD as considered in [26], the maximum data rate that can be supported by voltage mode signaling for particular TSV radius is determined. For a TSV radius of 10μm, the maximum data rate is found to be 21.7 GBPS. The eye diagram for voltage mode signaling at 21.7 GBPS is shown in Figure 4.2.

Figure 4.2 Eye Diagram at 21.7 GBPS for SEVM signaling[39]

## 4.4.2 Current Mode Signaling