# University of South Carolina Scholar Commons

Theses and Dissertations

2017

# Fault Protection In DC Microgrids Based On Autonomous Operation Of All Components

Qiu Deng University of South Carolina

Follow this and additional works at: http://scholarcommons.sc.edu/etd Part of the <u>Electrical and Computer Engineering Commons</u>

## **Recommended** Citation

Deng, Q.(2017). Fault Protection In DC Microgrids Based On Autonomous Operation Of All Components. (Doctoral dissertation). Retrieved from http://scholarcommons.sc.edu/etd/4091

This Open Access Dissertation is brought to you for free and open access by Scholar Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact SCHOLARC@mailbox.sc.edu.

## FAULT PROTECTION IN DC MICROGRIDS BASED ON AUTONOMOUS OPERATION OF ALL COMPONENTS

by

Qiu Deng

Bachelor of Science Huazhong University of Science and Technology, 2008

Master of Science Huazhong University of Science and Technology, 2011

Submitted in Partial Fulfillment of the Requirements

For the Degree of Doctor of Philosophy in

**Electrical Engineering**

College of Engineering and Computing

University of South Carolina

2017

Accepted by:

Roger A. Dougal, Major Professor

Herbert L. Ginn, Committee Member

Andrea Benigni, Committee Member

Jamil A. Khan, Committee Member

Cheryl L. Addy, Vice Provost and Dean of the Graduate School

© Copyright by Qiu Deng, 2017 All Rights Reserved.

# DEDICATION

To my loving parents, Xin Deng and Xiaoling Dun

&

To all who have supported me through this process

#### ACKNOWLEDGEMENTS

First and foremost, I would like to express my sincere gratitude to my advisor, Dr. Roger Dougal, for his invaluable support and guidance throughout my doctoral study. I am very grateful to him for giving me the opportunity to realize my doctoral degree. His talents and wisdoms have always expanded my vista and broadened my horizon. His always encouragement and support to relate my research work to industrial application have inspired me to explore various knowledge and perspectives. More importantly, I would like to thank him for mentoring me engineering thinking, the philosophy of doing research, and effective communication skills, which will be beneficial for my career.

I would also like to thank the distinguished members of my dissertation committee: Dr. Herbert Ginn, Dr. Andrea Benigni, and Dr. Jamil Khan. All of them has provided invaluable feedback and advises which lead to the successful completion of this dissertation.

I would like to acknowledge the support of the US Office of Naval Research and the Electric Ship Research and Development Consortium (ESRDC) which funded my research and allowed me to demonstrate the values and importance of my work.

Many thanks to the faculties and administrative staff of the Department of Electrical Engineering, especially Valuncha Paterson, Richard Smart and David Metts, for their help and support during my study at USC. I would like to thank Dr. Mohammod Ali and Dr. Yong-June Shin for their support at the early start of my doctoral study.

I would like to acknowledge my fellow graduate students, Cuong Nguyen, Huaxi Zheng, David Coats, Dan Li, Amin Ghaderi, Yihao Zhu, Jingjiang Wang, Issac Nam, Paul Young, Pietro Cairoli, Yuanyuan Fan, Tianlei Zhang, Rostan Rodrigues and Zheqing Zhou, for the always valuable exchange of ideas and suggestions.

My special acknowledgement goes to all my precious friends that I met in Columbia, South Carolina. Especially I would like to thank Jennifer and Rick Byers for their love, support and encouragement throughout all these years. They made my life filled with parents' love even when my family is thousands of miles away. I would like to thank Hunter McKenzie, William Bledsoe and Zhenzhen Yu for their friendship and help. Thanks to all the friends who got me out of the lab every now and then. My life in Columbia cannot be colorful and memorable without them.

Finally, I am especially in debt to my parents, Xin Deng and Xiaoling Dun, for their unconditional love, care and encouragement. Thank you for your support to let me fulfill my dreams without worries.

## Abstract

DC power distribution systems (or so called DC microgrids) are of wide interest for various power applications due to their advantages over traditional AC power distribution systems with respect to power density and power distribution efficiency. On the other hand, short-circuit faults present formidable hazards in these systems. It is difficult to extinguish these arc faults via conventional circuit breakers due to the lack of natural zero-crossing of DC current. Also the DC breakers are usually more bulky and costly. Today, fault protection in these systems – to the extent that it exists – relies on over-current time-out limits in power converters or on special circuit breakers that are tripped via over-current or distance relays and that therefore depend critically on a data network. Morerobust communication-independent, fully-distributed schemes are needed.

In this dissertation, we address the problems for fault protection in DC microgrids, and define an approach Local Information Based Fault Protection (LIFP) for robust protection against short-circuit faults that does not rely on microgrid-wide communications. Builds on work of Pietro Cairoli, we show how each entity connected to the dc bus, including current-limiting power converters and non-load-breaking disconnect switches, can autonomously detect, identify, and appropriately react to the presence of a short-circuit arcing fault based only on its own local observations of voltage and current. Successful implementation of such an approach can eliminate the need for dc breakers or fuses. Such an approach can rapidly detect a fault, shut down power injection to the bus, isolate the

fault, then re-energize and return the bus to service. The entire process can occur in milliseconds and thus can be transparent to load systems that contain small energy buffers.

For MVDC power systems, we extend the coverage of LIFP to arc faults (with arc impedance up to 4  $\Omega$ ) under varying load conditions (1 pu to 2 pu). The effective resistance of an arc can sometimes be large compared to that of the bus cables, and the arc resistance can vary randomly in time with large bandwidth; these characteristics complicate implementation of the LIFP method. Therefore, the characteristics of arc faults in DC systems are investigated, and the time-average resistance of DC arcs was represented via the Paukert equations, with the coefficients fitted to experimental data from DC converter-fed arcs. We describe the system design constraints and how moving average filters and dynamically-coordinated tripping thresholds can overcome these problems, and then we report the effectiveness of applying the method for a reference system over a wide range of system parameters (e.g. cable size and length), operating conditions (e.g. system current), and fault conditions (arc location, arc length).

In order to validate LIFP, the MATLAB-SIMULINK model of a representative multiterminal MVDC system was developed. The effectiveness of the method was evaluated by applying arc faults, one at a time, to many locations. The apparent resistance parameter (V/I ratio) was computed for each controllable entity, for each fault occurrence, and evaluated to determine whether appropriate protection action was taken. Also due to the assumption that the current ramping rate (di/dt) of power converters during any load change is limited to be less than 110A/ms, it is used for differentiating load variations (di/dt < k<sub>limit</sub>) from faults (di/dt > k<sub>limit</sub>). Results demonstrate that there are no cases where a fault was not disconnected from the system and only a few cases where loads lost power when they optimally should not have. For load variation events with a ramping rate up to 50A/ms, LIFP can successfully identify the incident and initiate adjustment of tripping thresholds within 4.5ms.

# TABLE OF CONTENTS

| DEDICATION                                                     |

|----------------------------------------------------------------|

| ACKNOWLEDGEMENTS iv                                            |

| Abstract                                                       |

| LIST OF TABLES xi                                              |

| LIST OF FIGURES                                                |

| LIST OF SYMBOLS                                                |

| LIST OF ABBREVIATIONS xvii                                     |

| CHAPTER 1 INTRODUCTION                                         |

| 1.1 PROTECTION FOR HIGH IMPEDANCE ARC FAULTS                   |

| 1.2 AUTOMATIC CALCULATION OF TRIPPING THRESHOLDS               |

| 1.3 DIFFERENTIATING ARC FAULTS VERSUS NORMAL SYSTEM VARIATIONS |

| 1.4 Noise Tolerance Of Localized Fault Protection              |

| CHAPTER 2 LITERATURE REVIEW AND BACKGROUND                     |

| 2.1 MVDC MICROGRIDS                                            |

| 2.2 FAULT LOCATION METHODS                                     |

| CHAPTER 3 ANALYSIS OF ARC FAULT IN MVDC SYSTEMS                |

| 3.1 Characteristics Of Dc Arc Fault                            |

| 3.2 Arc Branch Model                                           |

| CHAPTER 4 COORDINATION OF PROTECTION SCHEMES IN MVDC SYSTEMS   |

| 4.1 PROTECTION PROCEDURES OF THE FAULT CLEARANCE               |

| 4.2 IMPLEMENTATION OF FAULT PROTECTION CONTROLLERS             |

| 4.3 COORDINATION OF FAULT PROTECTION SCHEMES        | 60 |

|-----------------------------------------------------|----|

| CHAPTER 5 LOCALIZED FAULT PROTECTION FOR ARC FAULTS | 67 |

| 5.1 A BASELINE MVDC SYSTEM                          | 67 |

| 5.2 CURRENT LIMITING TO ARC FAULT VIA CONVERTERS    | 69 |

| 5.3 LOCAL RESPONSE TO ARC FAULT                     |    |

| 5.4 COORDINATION OF SWITCHES                        | 75 |

| 5.5 APPLICABILITY OF THE LIFP METHOD                | 86 |

| CHAPTER 6 COORDINATION OF TRIPPING THRESHOLDS       |    |

| 6.1 DETERMINING THE TRIPPING THRESHOLDS             |    |

| 6.2 EFFECTIVENESS OF AUTO THRESHOLD ADJUSTMENT      |    |

| 6.3 Results                                         |    |

| CHAPTER 7 CONCLUSION AND FUTURE WORK                |    |

| 7.1 Conclusion                                      |    |

| 7.2 Future Work                                     |    |

| References                                          |    |

# LIST OF TABLES

| Table 2.1 Comparison Of Different Fault Location Methods [47]    37                                                             |

|---------------------------------------------------------------------------------------------------------------------------------|

| Table 4.1 Comparison Of LIFP And CFP    61                                                                                      |

| Table 5.1 System Parameters    68                                                                                               |

| Table 5.2 Cable Parameters    68                                                                                                |

| Table 5.3 Apparent Impedance At Switch Terminals                                                                                |

| Table 5.4 Operational Status Of Loads After Operation Of Fault Protection System For         Various Fault Locations         85 |

| Table 5.5 Effectiveness Ratio Of LIFP    86                                                                                     |

| Table 5.6 Tripping Margin Regarding Cable Impedance         89                                                                  |

| Table 6.1 Time Delay For Load Variation Detection Under Various Configurations 101                                              |

# LIST OF FIGURES

| Figure 2.1  | Concept diagram of the MVDC shipboard power system [16] 2                                                                               | 28  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 2.2  | A generic layout of the MVDC shipboard power system [23]2                                                                               | 29  |

| Figure 2.3  | MVDC power system for offshore oil and gas drilling platforms [23]                                                                      | 31  |

| Figure 2.4  | An MVDC shipboard system architecture using SSPD [39]                                                                                   | \$2 |

| Figure 2.5  | A unidirectional interrupting SSPD [39]                                                                                                 | 3   |

| Figure 2.6  | Layout of a fault protection solution in DC Zonal Electrical System [40] 3                                                              | 35  |

| Figure 2.7  | Implementation of active impedance estimation on fault location in a dc microgrid system with SSCBs [4]                                 | 38  |

| Figure 2.8  | Circuit layout of fault location using active impedance estimation                                                                      | 19  |

| Figure 2.9  | Algorithm of differential protection 4                                                                                                  | 0   |

| Figure 2.10 | O Zonal Arrangement of Differential Protection in the MVDC System [22]4                                                                 | 1   |

| Figure 3.1  | Arc fault test through ignition wire [51]4                                                                                              | 5   |

| Figure 3.2  | Arc current and voltage measured during test4                                                                                           | 6   |

| Figure 3.3  | An dc arc branch model 4                                                                                                                | 17  |

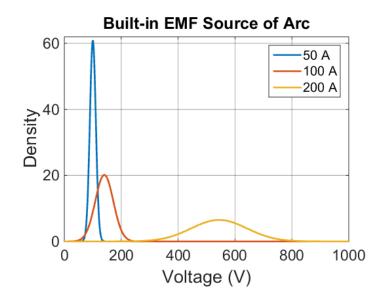

| Figure 3.4  | Density function and normal distribution fitting of the built-in EMF source in the arc model                                            |     |

| Figure 3.5  | Normal distribution fitting of the EMF source of arc at different currents 4                                                            | 9   |

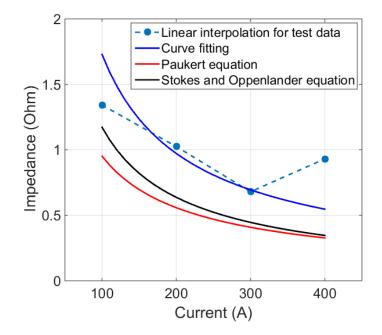

| Figure 3.6  | Comparison of test data with arc models regarding average value of arc impedance for different current level (length of gap at 88.9 mm) | 51  |

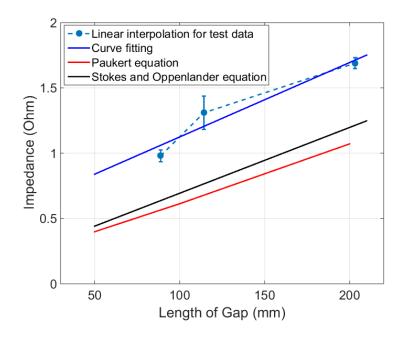

| Figure 3.7  | Comparison of test data with arc models regarding average value of arc impedance for different length of gap (current level at 200 A)   | 52  |

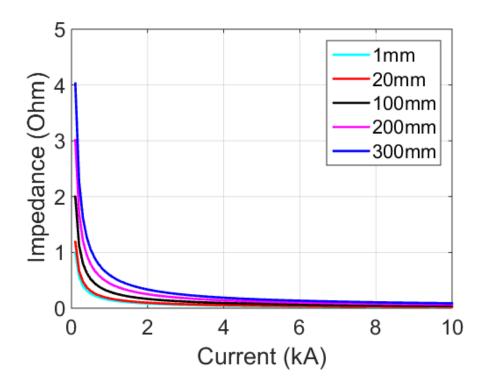

| Figure 3.8  | Arc impedance for different currents and arc length                                                                                     | ;3  |

| Figure 3.9  | Statistical distributed behavior of arc impedance                                                                                       | 55  |

| Figure 4.1  | Conceptual view of the protection procedures for the MVDC system                                                                         | 8 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 4.2  | Implementation of Fault Protection Controllers                                                                                           | 9 |

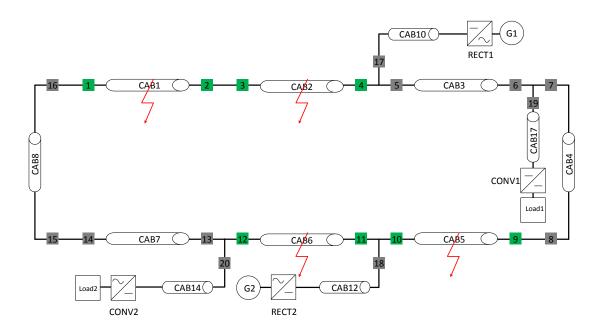

| Figure 4.3  | Shipboard Power System Model for Coordination Test                                                                                       | 2 |

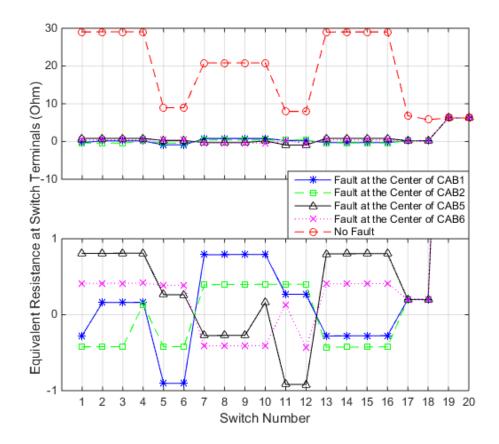

| Figure 4.4  | Comparison of Apparent Resistance at Switch Terminals 1-20 for Fault at the Center of CAB1, CAB2, CAB5, CAB6 and No Fault Condition      |   |

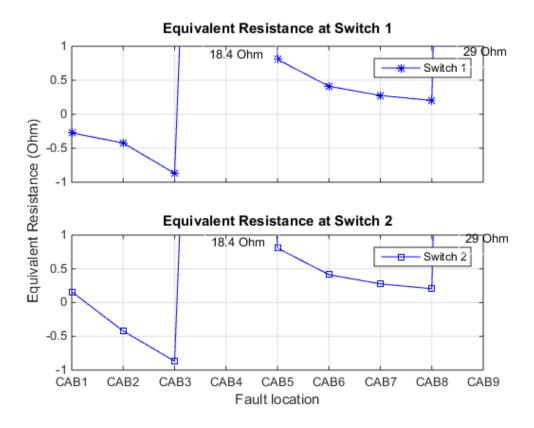

| Figure 4.5  | Apparent resistance at Switch 1 & Switch 2 for Different Fault Locations 6                                                               | 4 |

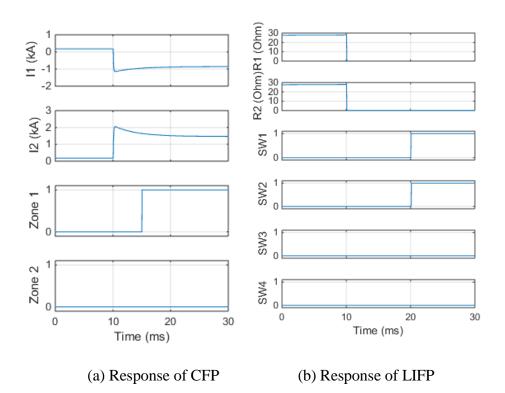

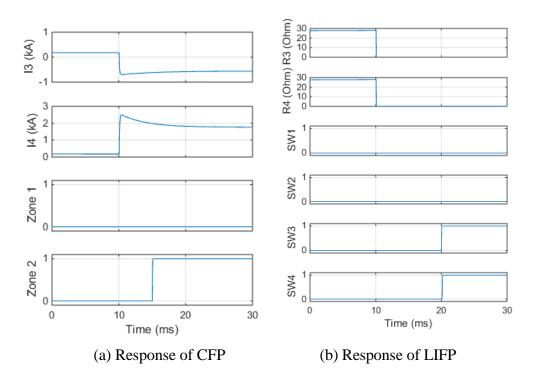

| Figure 4.6  | Responses of CFP&LIFP to Fault at CAB1                                                                                                   | 5 |

| Figure 4.7  | Responses of CFP&LIFP to Fault at CAB2                                                                                                   | 6 |

| Figure 5.1  | A baseline MVDC system                                                                                                                   | 7 |

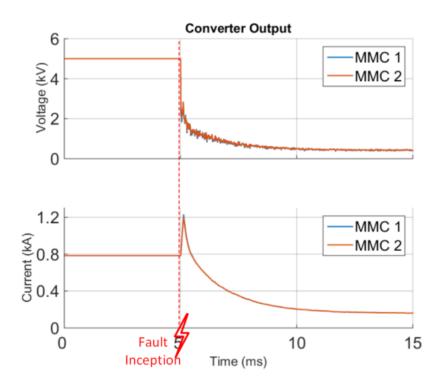

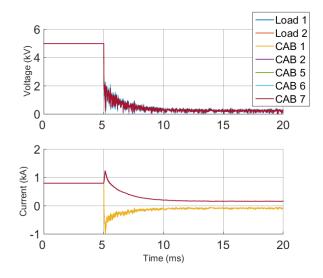

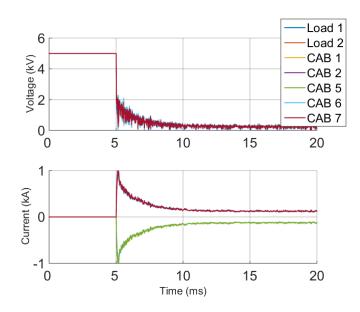

| Figure 5.2  | Voltage and Current at the Output of Power Converters to Arc Fault                                                                       | 0 |

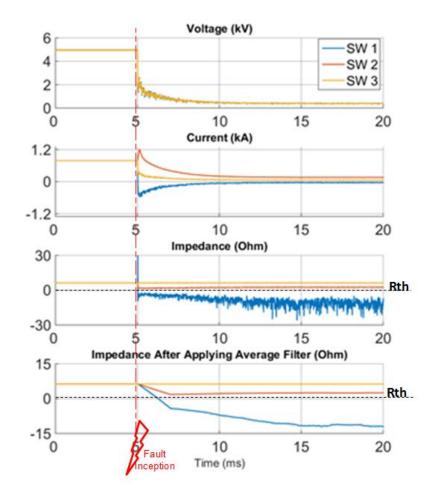

| Figure 5.3  | Arc Fault at Source Branch CAB 1                                                                                                         | 2 |

| Figure 5.4  | Arc Fault at Load 1                                                                                                                      | 3 |

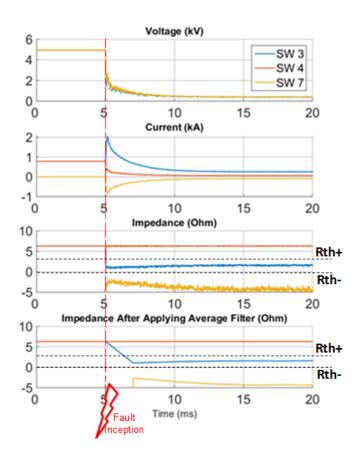

| Figure 5.5  | Arc Fault at Ring Bus CAB 6                                                                                                              | 4 |

| Figure 5.6  | Voltage and Current at the terminals of Switch 3 regarding arc fault at different locations of the system                                |   |

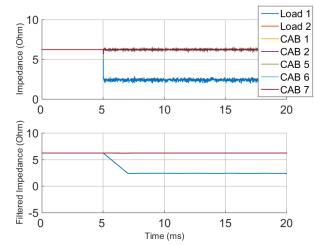

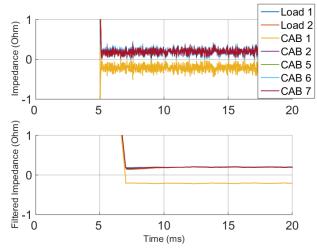

| Figure 5.7  | Apparent impedance at the terminals of Switch 3 regarding arc fault at different locations of the system (arc impedance 1 $\Omega$ )     | 7 |

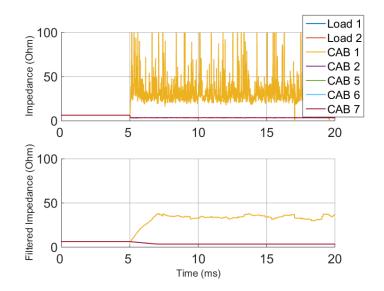

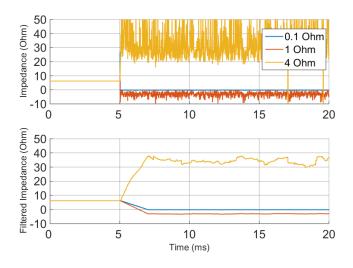

| Figure 5.8  | Apparent impedance at the terminals of Switch 3 regarding arc fault at different locations of the system (arc impedance $0.1 \Omega$ )   | 8 |

| Figure 5.9  | Apparent impedance at the terminals of Switch 3 regarding arc fault at different locations of the system (arc impedance 4 $\Omega$ )     | 8 |

| Figure 5.10 | Apparent impedance at the terminals of Switch 3 regarding different types of arc faults at the branch of Load 1                          |   |

| Figure 5.11 | Voltage and Current at the terminals of Switch 1 regarding arc fault at different locations of the system                                | 9 |

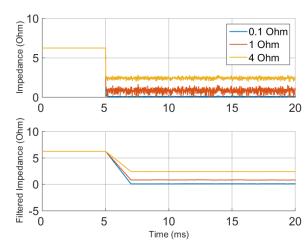

| Figure 5.12 | 2 Apparent impedance at the terminals of Switch 1 regarding arc fault at different locations of the system (arc impedance 1 $\Omega$ )   | 0 |

| Figure 5.13 | 3 Apparent impedance at the terminals of Switch 1 regarding arc fault at different locations of the system (arc impedance $0.1 \Omega$ ) | 0 |

| Figure 5.14 Apparent impedance at the terminals of Switch 1 regarding arc fault at different locations of the system (arc impedance 4 $\Omega$ )                       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.15 Apparent impedance at the terminals of Switch 1 regarding different types of arc faults at the source branch G1                                            |

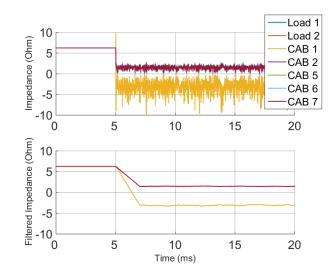

| Figure 5.16 Voltage and Current at the terminals of Switch 7 regarding arc fault at different locations of the system                                                  |

| Figure 5.17 Apparent impedance at the terminals of Switch 7 regarding arc fault at different locations of the system (arc impedance 1 $\Omega$ )                       |

| Figure 5.18 Apparent impedance at the terminals of Switch 7 as a function of arc impedance                                                                             |

| Figure 5.19 Apparent impedance at the terminals of Switch 3 regarding different filter configurations                                                                  |

| Figure 5.20 Noise level (peak to peak) versus filter size                                                                                                              |

| Figure 6.1 Procedures of Auto Adjustment of Tripping Thresholds during a Load Increase Event                                                                           |

| Figure 6.2 Flow chart of the auto adjustment of tripping thresholds                                                                                                    |

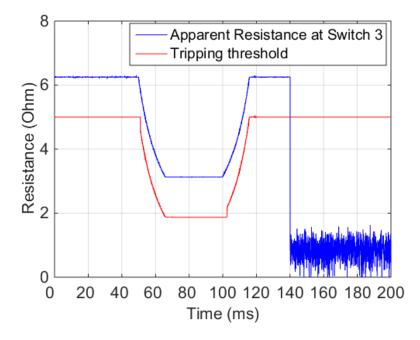

| Figure 6.3 Adjustment of tripping threshold in response to different operating conditions of the system: load increase, load decrease, and short-circuit arc fault 100 |

# LIST OF SYMBOLS

| $V_n$                    | voltage value at the terminal of switch 'n';                      |

|--------------------------|-------------------------------------------------------------------|

| $I_n$                    | current value at the terminal of switch 'n';                      |

| $R_n$                    | apparent resistance at switch 'n' calculated from $V_n / I_n$ ;   |

| $V_r$                    | voltage value at current limiting mode;                           |

| $P_{r+}$                 | heaviest power flow at the direction by default;                  |

| $P_{r}$                  | heaviest power flow at the reverse direction by default;          |

| $R_{th+}$                | positive threshold for fault detection;                           |

| R <sub>th</sub> -        | negative threshold for fault detection;                           |

| $V_{arc}$                | arc voltage;                                                      |

| Iarc                     | arc current;                                                      |

| Rarc                     | arc resistance;                                                   |

| μ                        | mean value;                                                       |

| σ                        | standard deviation;                                               |

| +                        | impedance drops to a lower positive value due to the fault event; |

| -                        | impedance shifts to a negative value due to the fault event;      |

| Ν                        | impedance stays at the same level during the fault event;         |

| Y                        | bus admittance matrix;                                            |

| $V_i$ , $V_j$            | voltage of adjacent nodes;                                        |

| <i>R<sub>CABij</sub></i> | cable resistance between the two nodes i and j;                   |

| <i>p</i> , <i>q</i>      | nodes that are connected to power sources;                        |

XV

$I_{limit_q}$ ,  $I_{limit_p}$  output target of the MMCs during current limiting mode;

- $R_n^{F_x}$  apparent impedance at the terminals of Switch n after fault event happens at location x;

- $V_n^{F_x}$  voltage at either terminal of Switch n after fault event happens at location x;

- $I_n^{F_x}$  current through Switch n after fault event happens at location x;

- $\Delta R$  initial resistance margin;

- $\Delta I$  initial current margin;

# LIST OF ABBREVIATIONS

| DC     | Direct Current                                    |

|--------|---------------------------------------------------|

| AC     | Alternating Current                               |

| LIFP   | Local Information Based Fault Protection          |

| MVDC   |                                                   |

| CFP    | Centralized Fault Protection                      |

| LFC    | Local Fault Controller                            |

| CFC    | Central Fault Controller                          |

| ESRDCE | Electric Ship Research and Development Consortium |

| MW     | Megawatts                                         |

| HVDC   | High Voltage Direct Current                       |

| UHVDC  | Ultra-High Voltage Direct Current                 |

| LVDC   | Low Voltage Direct Current                        |

| SES    | Shipboard Electrical System                       |

| SiC    | Silicon Carbide                                   |

| SSPD   | Solid State Protective Device                     |

| PDM    | Power Distribution Module                         |

| VSC    | Voltage Source Converter                          |

| SSCB   | Solid State Circuit Breaker                       |

| CFM    | Centralized Fault Management                      |

| VSM    |                                                   |

| CSM    | Current Source Mode                               |

## CHAPTER 1

## INTRODUCTION

This Chapter aims to describe and discuss the challenges in this research, whereas all of the background material with most references has been put in Chapter 2.

The goal of this research is to develop a "breakerless" method of protecting DC microgrids against short-circuit arc faults based on shut-down and reconfigure. This method is expected to detect and locate a wide range of faults, including low impedance (<0.02pu) bolted faults as well as high impedance (>0.08pu) arc faults, only via local information without wide area communication. This research is important as interest in dc microgrids is rapidly increasing, especially for applications such as data centers, smart houses, power collection in wind or solar farms, or integrated power and propulsion systems for ships, electric vehicles or offshore oil and gas drilling platforms [1]-[9]. Due to the absence of natural zero-crossings for dc current, it is difficult to clear short circuits in dc systems with traditional mechanical circuit breakers, even if electrically-tripped. This difficulty has led us to investigate a different approach which relies on coordinated control of power converters and non-load-breaking disconnect switches, so that the fault can be cleared by completely de-energizing the entire affected portion of the system, reconfiguring (i.e. isolating the faulty section) via disconnect switches while de-energized, and finally re-energizing the entire system [60]-[62].

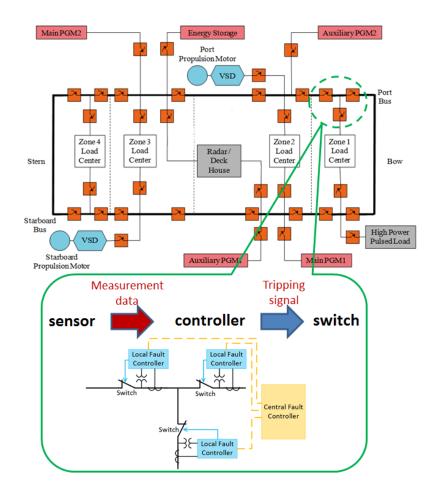

The objective for the fault protection algorithm is to ensure that the closest switch/switches (either two closest switches at both ends of the cable on a ring bus, or one closest switch at one end of the cable at the branch circuit) are assigned to isolate the faulted segment while the remaining parts of the system stay fully functional. It is obvious that this fault protection scheme needs to be integrated with fault localization approaches in order to guarantee selectivity just like all the other fault protection schemes. There are always tradeoff decisions to be made when designing the fault protection scheme for a Medium Voltage DC (MVDC) system. The adoption of differential protection, so called Centralized Fault Protection (CFP) [22], can be a viable solution for achieving fast and accurate protection for short-circuit faults. But it can also put the whole system at great risk in the event of failure in the wide area communication system. In contrast, the Local Information Based Fault Protection (LIFP), which has adopted the concept of "distance protection" that is common in ac systems, chooses a different strategy by relying only on local observations of voltage and current. Apparently this method brings huge benefits because a system that does not rely on communications is not susceptible to failure based on failure of the communications. Also the distributed decision making capability (decision can be made directly at local fault controllers (LFC) instead of through central fault controllers (CFC)) provides additional protection to the system in dealing with undesirable operating conditions.

When it comes to multi-terminal microgrids, "communication dependent" fault protection schemes are widely used because there are not yet any known methods for avoiding dependence on communication especially considering the difficulty of coordinating tripping settings. Very few studies have been carried out to develop impedance based communication-independent fault protection methods in such systems until the rapid advancing of dc microgrids applications in recent years. One of the driving forces is led by the Electric Ship Research and Development Consortium (ESRDC), which is of special interest to develop a communication-independent fault protection scheme for the next generation of "all-electric" naval ship [15]-[16].

The major challenges with the LIFP method are often associated with its communication-independent feature. On one hand, it requires more efforts to coordinate tripping settings at each LFC to guarantee reliability and selectivity for fault protection. Also, it may be difficult for a device "here" to determine that a fault has occurred "there" (far away), and that it should shut down in order to clear the fault. In order to overcome these challenges, a novel algorithm needs to be developed and integrated with the LIFP method. This algorithm should be able to differentiate whether the system is experiencing normal load variations or a short circuit fault by evaluating the changing rate of the local measurements. Also it should be able to automatically determine and adjust the tripping settings for each switch with the presence of severe system noise. This approach is expected to largely increase the applicability of LIFP to the MVDC shipboard power systems, and has great potential to facilitate the application of LIFP in other dc microgrids.

Therefore, this work aims to address and solve challenges that are summarized as follows:

• Limited fault coverage (only response to low impedance fault (<0.02pu) with constant value) of existing communication-independent fault location technique.

• Difficulty of existing fault identification technique for differentiating normal load variations from short circuit faults.

20

• Coordination of tripping settings for all switches in the system still needs human intervention and is time consuming.

#### **1.1 PROTECTION FOR HIGH IMPEDANCE ARC FAULTS**

One of the most common challenges for impedance-based fault protection method is protecting against high impedance short circuit faults. It is difficult to locate a fault when the fault impedance is nearly the same as the system cable impedance – which can be very small in a high power dc system. Thus, it will be interesting to investigate how the fault impedance can affect the effectiveness of the LIFP method, and how the tradeoff decision can be made between the coverage range of the LIFP for fault and the effectiveness of the LIFP in application. On one hand, it is important to define the range of fault impedance that the existing fault protection scheme can cover without losing its reliability and selectivity for a given system configuration. On the other hand, it is valuable to test the response of the fault protection scheme for different system configurations (such as cable resistance), so as to provide possible optimization for the system level design.

Also it should be noticed that most of the previous studies assumed that faults could be modeled as pure resistances. However for applications like the shipboard systems, arc faults have very high probability to occur in the short circuit events. The current of arc can vary randomly in a wide range, and the impedance can be unpredictable due to its nonlinear and time varying behavior. Hence, it is worthwhile to analyze the characteristic of arc impedance for various fault conditions (current level, operating mode, arc length and etc.) in order to establish a practical arc model [51]-[55]. Furthermore, it is of great importance to validate the LIFP method in correspondence with these high impedance arc

faults, so as to find out whether LIFP still works as it should, or under what condition this method will work.

### **1.2 AUTOMATIC CALCULATION OF TRIPPING THRESHOLDS**

It has been illustrated in previous studies [48] that both the power converters and the dc disconnect switches need to be aware of the fault events under current fault protection scheme. However the difference is, the power converters only need to know if there is a fault in the system, because all of them will eventually operate to de-energize the whole system through the fault clearing sequence, whereas the switches need to estimate the fault location, because only the corresponding switches should open to isolate the faulted segment while the others should remain closed. The power converters adopt overcurrent protection. The current through the converters are measured and compared to the tripping thresholds to determine whether the converters should go into current limiting mode. Similar ideas are applied to the switches which adopt impedance protection. The impedance tripping thresholds defines the tripping zone and non-tripping zone of each switch, and further determines the operation status of each switch during fault scenarios. Therefore, it is of great importance to optimize the settings of tripping thresholds, otherwise the switches may operate incorrectly under certain circumstances.

The setting of tripping thresholds can vary switch by switch, and is strongly affected by the topology and the parameters of the system. Former study assumes the MVDC system is always operating with the same system configuration, so as fixed tripping thresholds are assigned for switches based on simple estimation. However for a practical MVDC systems, each generation unit or zonal load can either be connected to or disconnected from the whole system or experience significant shifting of power demand regarding

22

various operating conditions (take the shipboard system for example, the pulse load can be active at certain conditions, and the propulsion load demand can vary dramatically). Even the system topology can change by changing switch settings. Therefore, it is necessary to develop an algorithm that can automatically calculate the tripping thresholds for all the switches during the interval between each system reconfiguration.

#### 1.3 DIFFERENTIATING ARC FAULTS VERSUS NORMAL SYSTEM VARIATIONS

The existing LIFP method evaluates current at converter terminals and apparent resistance at switch terminals to determine the status of the system: whether in fault condition or normal operating condition. And this method assumes that tripping thresholds for switches remain fixed between each system reconfiguration. However the power demand of system loads will be time varying, and these events may look similar to arc faults in terms of current or apparent resistance. This characteristic complicates implementation of the LIFP method. For example, assume that the rated value of some load is 4  $\Omega$  and that the apparent resistance of this load can drop to 0.8  $\Omega$  under certain load ramping up conditions. Comparatively, if an arc fault with 1  $\Omega$  resistance occurs near the load, the apparent resistance of the arc plus load will also be equal to 0.8  $\Omega$ . Therefore, it is difficult to tell a fault event apart from normal system variation events by only referring to the apparent resistance value.

It will have merit if some extra information can be extracted from the apparent resistance for fault identification purpose. According to the IEEE standard 1709, a connected load cannot draw more power from the dc bus than is allowed by the load di/dt rating. Hence the current derivative is of special interest for further investigation. It is expected to be an effective indicator to differentiate whether the system is experiencing a fault or just a load variation. It would be a very interesting challenge to develop a local information based algorithm which automatically adjusts the tripping thresholds under various load variation scenarios without compromising the reliability and accuracy of arc fault detection.

### 1.4 NOISE TOLERANCE OF LOCALIZED FAULT PROTECTION

There can be considerable amount of noise on the dc bus even when the system is operating at steady state, such as that caused by the operation of switching power converters or that caused by short-circuit arc faults. While these noises may be insignificant in terms of power distribution, but can cause big problems for the LIFP method, as explained next.

One major concern is false triggering when noise causes a parameter to exceed the detection threshold. The tripping signal can be generated by the local controller once the apparent resistance is calculated and monitored through measurement falls into the preset tripping zone. However, it can be possible that the peak values of the apparent resistance go beyond the threshold while the average value of the apparent resistance remains below the threshold. Thus, in order to increase the noise tolerance and guarantee the reliability of the LIFP scheme, it is important to overcome this mistripping challenge by analyzing how the noise will affect the protection scheme, and further propose a noise-compatible solution.

Another major concern regards the undesirable influence noise may impose on the current derivative based fault identification method. The current derivative can vary dramatically even when the system is in normal operating condition due to the unpredictable feature of system noise. If low pass filter is adopted to reduce bandwidth,

24

considerable time delay will be introduced to the whole fault clearing process. Thus, it is of great importance to propose a noise-immune solution for this current derivative based algorithm.

## **CHAPTER 2**

## LITERATURE REVIEW AND BACKGROUND

Interest in MW-scale microgrids is rapidly increasing. Microgrids are electrical distribution systems containing loads and distributed energy resources that can be operated either connected to the main power network or islanded [1]. It is a promising technology that fits in with the Smart Grid concept. Compared to traditional large-scale power systems, microgrids bring more flexibility and efficiency to power generation and power distribution, so as such they are being widely adopted in both industrial and residential applications.

According to a tracker report from Navigant Research, more than 480 microgrid projects are proposed, planned, under construction, or operating worldwide, representing nearly 3800 magawatts (MW) of capacity [2]. Microgrids are beginning to move into the mainstream, and have caught the attention of many research groups in industry and academe. Recent literatures show interest in microgrid technologies such as system dynamic and fault protection, intelligent management and control, renewable generation, power quality, power flow, load forecasting, and system integration.

## 2.1 MVDC MICROGRIDS

The benefit of dc over ac in microgrids generally lies in three facts: First, the rapid advance of power electronic techniques make transformer free power systems applicable at the distribution level. Second, dc systems require fewer stages of power conversion for various ac and dc loads connected to the common bus [5] [6]. Third, ac current only flows through the outer surface of cable due to the skin effect, whereas dc current can flow through the entire cable. Thus dc systems can deliver times more power than ac systems for power cables of the same size [4].

However, when it comes to fault protection, ac microgrids still have a clear advantage over dc microgirds. The existing IEEE/IEC standards for fault protection within ac systems can be easily applied to an ac microgrid. But the same rule doesn't apply for dc microgrids, because the standards on the protection of dc systems currently do not exist [4]. Additionally, ac circuit breakers are very common and well developed equipment in ac systems (from medium voltage level to high voltage level) for fault isolating purpose, whereas the application of such circuit breakers in dc systems is largely constrained to voltage ratings under 1-10 kV, because there are no natural zero crossings of the dc current [7]-[10]. There are dc circuit breakers available as products in industry by manufacturers like ABB and EATON, for voltage rating up to 1 kV. But still they are costly and bulky in size [11]-[13].

DC power systems can be categorized by means of voltage rating: at transmission level, high voltage dc (HVDC) is rated above 65 kV, while ultra-high voltage dc (UHVDC) is typically rated above 800 kV; at distribution level, medium voltage dc (MVDC) is rated from 1500 V to 22 kV, while low voltage dc (LVDC) is rated below 1500 V [3]. Although there have been significant research on HVDC transmission systems, the dc distribution (MVDC & LVDC) systems are becoming more and more popular especially in recent years [4].

#### 2.1.1 MVDC SHIPBOARD POWER SYSTEM.

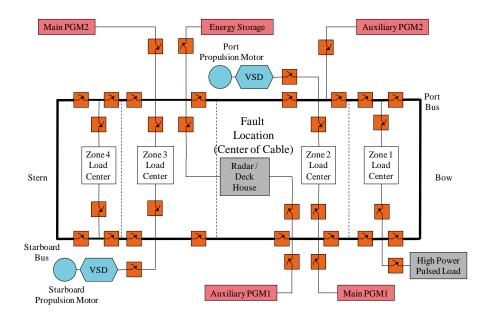

MVDC power systems are of wide interest for the next generation of "all-electric" naval ships because MVDC appears to be the only technology that will be able to meet the stringent demands on power and energy density [14][15]. One general topology of an MVDC shipboard power system is displayed in Figure 2.1 [16][17].

Figure 2.1 Concept diagram of the MVDC shipboard power system [16]

This system is an implementation of a generic multi-terminal dc Shipboard Electrical System (SES) derived from [18]-[20]. It has several ac generators feeding the dc ring bus through rectifier converters. The dc ring bus is rated at 5 kV, the two main generators are rated at 47 MVA each, and the two auxiliaries are rated at 5 MVA each. The voltage-controlled rectifiers are rated at 5 MVA each, and they convert the 4.16 kV, three-phase ac voltage to 5 kV dc [21]. These rectifiers are assumed to have a built-in fault protection mode that will limit current or shut off completely when a fault is detected. In this MVDC

system, sectionalizers (dc disconnect switches) are placed at each end of each cable section on the ring bus, and at the connecting end of the cables on branches connected to the ring bus, so that a faulted section can be isolated from the rest of the system. Loads within zones are supplied through dc-dc converters [22].

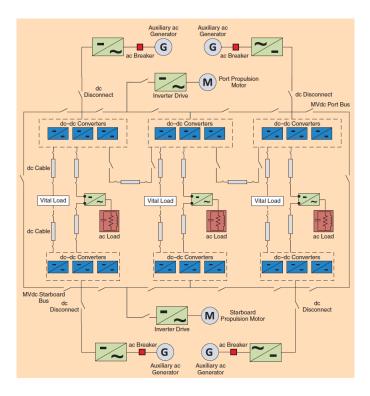

The Office of Naval Research and the University of Pittsburgh also proposed a generic MVDC-based electric ship architecture shown in Figure 2.2 [23]. It applies similar concept of integrated power system (IPS) as in [16] which enables all the energy generated by the ac generators to be converted to dc power at the MVDC ring bus, and further delivered to various dc and ac loads in the ship system through dc/dc and dc/ac converters. There are also dc disconnects at both the ring bus and the load branches for fault protection purpose.

Figure 2.2 A generic layout of the MVDC shipboard power system [23]

#### 2.1.2 OTHER DC MICROGRIDS

The dc microgrids are not only of interest in dc zonal systems for ships, but also attract great attention in other industrial applications such as offshore oil and gas drilling platforms, remote area mine site, renewable energy systems, and data centers [7][24][25]. There are three main reasons for the popularity of MVDC/LVDC microgrids in these applications: First, for certain industrial operations in remote areas (such as offshore oil and gas drilling, and remote area mining), it is hard or even impossible to obtain electric power from the national grid through power transmission. As a result, using the power generated and distributed locally seems to be the only viable solution. Second, it has been well recognized worldwide that using renewable energy such as solar power can achieve long-term environmental and economic benefits. The dc microgrids provide a flexible platform for conveniently integrating the maximum possible renewable energy sources which predominantly generate dc into these localized power systems [26]. Third, comparing to ac microgrids, the dc microgrids have improved power quality, increased conversion efficiency and simpler power electronic interfaces.

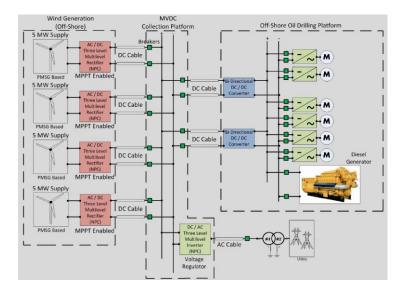

Reference [23][27][28] introduced a MVDC power system for offshore oil and gas drilling platforms. The system architecture is shown in Figure 2.3. Up to 20MW power is generated locally by off-shore wind farms to serve the offshore drilling platform through the MVDC system. It can be noticed that breakers are placed at each branch for fault protection. However, there is no breaker at the MVDC collection platform, so if short circuit fault occurs at the dc bus, the whole collection platform will need to be disconnected, and the drilling platform can only use its secondary dc bus which fed by its local diesel generator.

Figure 2.3 MVDC power system for offshore oil and gas drilling platforms [23]

Reference [32] indicates Mitsubishi Electric is planning to build a development and demonstration facility for MVDC distribution at its power distribution system center. Also, companies and institutes like Intel, HP, Emerson Network Power, The Green Grid, Lawrence Berkeley National Laboratory and Universal Electric are in favor of 400 V dc systems for their data centers [33]-[37]. A study conducted by these companies concluded that energy savings of approximately 7 to 8 percent could be achieved over high efficiency, best practices 480-280 Vac – with a 15 percent electrical facility capital cost savings, as well as a 33 percent space savings and 200 percent reliability improvement [34].

#### 2.1.3 PROTECTION STRATEGIES FOR DC MICROGRIDS

Reference [29][30] investigated the protection and control strategies for an MVDC microgrid within a remote area mine site. A communication based differential protection scheme is adopted as primary protection, whereas the overcurrent protection scheme is set

as backup. Reference [31] introduced a multi-terminal MVDC distribution system with renewable energy sources. The fault current is extinguished by dc circuit breakers, and then the faulty part is isolated by dc switches. However, this protection scheme needs communication between over current relays for fault location and coordination.

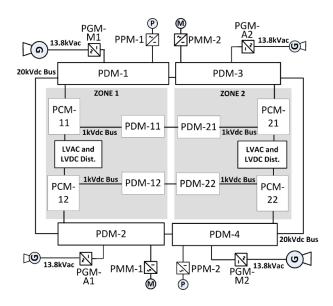

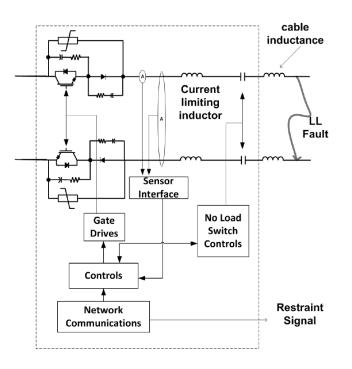

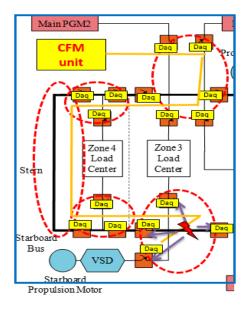

As the advance of wide bandgap power semiconductor technology such as the enabling of Silicon Carbide (SiC) with voltage rating from 1.2kV to 10kV in power electronics [38], the solid state protective devices (SSPDs) are presently being considered for fault mitigation in "Breaker-Based" future shipboard power system shown in Figure 2.4. These SSPDs are deployed at the Power Distribution Modules (PDMs) both at the main dc ring bus and LVDC distribution bus. There are communications among these SSPDs for the coordination of fault protection. The location of the fault is ascertained by capturing fault current snapshots at every fault isolation point and then communicating this information up to a higher level in order to determine which no-load switch to open [39]. Apparently, this approach is still communication-dependent comparing to LIFP.

Figure 2.4 An MVDC shipboard system architecture using SSPD [39]

Figure 2.5 illustrates the layout of a unidirectional interrupting SSPD at the system shown in Figure 2.5. Compared to direct interruption of fault current (along with arc extinguishing) via conventional mechanical breakers, these SSPDs use power electronics to drive fault current to zero so that the fault can be galvanically isolated from the rest of the system by no-load mechanical switches. When a fault occurs at the MVDC side, the energy stored in the output capacitors of the VSC will discharge into the fault and induce large fault current going through the SSPD. The rate of rise in this fault current (di/dt) is limited by the current limiting inductor as shown in Figure 2.5, but once the fault current goes beyond the tripping level in the SSPD, all of the SiC MOSFETs in the SSPD will be informed to open. The device current will be diverted into the parallel RC snubber, which limits the rate of rise in voltage (dv/di), and damped through the resistance [39].

Figure 2.5 A unidirectional interrupting SSPD [39].

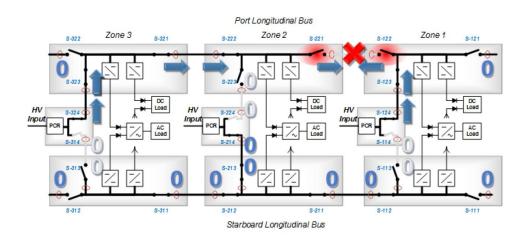

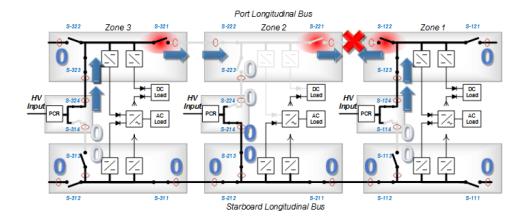

Currently, a DC Zonal Electrical System (DCZEDS) topology [40] as shown in Figure 2.6 has also been taken into consideration by the US Navy for the next generation allelectric ships. Similar to the architectures mentioned in Figure 2.1 and Figure 2.4, this system layout enables the sharing of energy resources via phase controlled rectifiers (PCRs) among different loads, such as electric propulsion, pumps, lighting and pulsed loads, so increases the overall system survivability. It can be noticed that every load can be feed bi-directionally and independently. The PCRs are followed by large output capacitors for harmonics filtering, so as these VSCs can bring in very high discharge current when short-circuit fault occurs. Again the electromechanical no load switches placed at various locations are for system segmentizing but not current interrupting purpose. When fault occurs on one of the longitudinal buses, PCRs that connected to the faulted bus (either the port longitudinal bus or the starboard longitudinal bus) will bring down the fault current to zero only after the filter capacitor at the output of PCR discharges, while the loads can still be fed through the other bus.

(a) Fault interruption with communications.

(b) Fault interruption without communications

Figure 2.6 Layout of a fault protection solution in DC Zonal Electrical System [40]

The fault identification and isolation process in this system is fulfilled via LAN communications between bus switch assemblies and PCRs. The current is measured at the current sensor in each assembly and constantly compared to a predetermined threshold (10kA) ten times of the rated current (1kA). If the value exceeds this threshold, the assembly detects the fault event and then sends out this information to all connected PCRs and switch assemblies via communications. Eventually each assembly gathers information from adjacent assemblies to determine a course of action by following two criterions:

*a*. If the summation of current going into/out of an assembly is not equal to zero, it means internal fault occurs inside this assembly, so as all switches within this assembly will be open to isolate the fault from the remained system.

*b*. If the current flowing out of a port of an assembly doesn't equal to the current flowing into the adjacent port of an adjacent assembly as shown in Figure 2.6(a), it means

fault occurs between the two, so as both assemblies open the switch at corresponding ports [40].

Though this fault protection scheme requires LAN communications among the assemblies, it doesn't rely on any centralized controllers for fault identification. However, if the communication is interrupted, only criterion a can be used for fault identification. Whereas for criterion b, all assemblies that detect the high fault current will assume the fault is just beyond the outgoing switch and consequently open the outgoing switch as shown in Figure 2.6(b). This will result in the isolation of a larger portion of the system compared to the case with communication.

#### 2.2 FAULT LOCATION METHODS

#### 2.2.1 CLASSIFICATION OF FAULT LOCATION METHODS

The concept of fault protection generally includes two parts: fault detection and fault location. The objective for fault detection is to determine the existence of a fault, whereas the localization of fault typically requires more effort in the accuracy of data measurement and data processing to determine the location of a fault.

Various kinds of conventional fault location methods have already been developed for large scale ac power grids over decades, such as methods that rely on phasor measurement unit (PMU) or phasor information [41][42], methods based on monitoring system reactance from one terminal of a line [43][44], and methods that use traveling wave generated from fault as an index for fault location, so as compare the difference in time of arrival at two or more locations of a bus to determine the fault location [45][46]. However these methods are typically applied for large scale systems with many miles long distance, and they may face difficulties when it comes to dc microgrids with low cable impedance due to short distance [4]. Fortunately, some techniques used in the ac systems can still be applied directly to the MVDC systems. Different fault location methodologies are summarized in Table I [47], and they can be categorized as either communicationdependent method or communication-independent method.

|                                       | Differential protection                   | Directional protection                                                                             | Impedance<br>protection                                                            | Overcurrent<br>protection                               | Current<br>derivative<br>protection                                                                     |

|---------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Algorithm                             | Current<br>summation<br>equal to zero     | Reverse of<br>current direction<br>after fault                                                     | Apparent<br>impedance<br>drop into the<br>tripping zone<br>after fault             | Current go<br>beyond<br>threshold after<br>fault        | Current<br>derivative go<br>beyond<br>threshold after<br>fault                                          |

| Wide area communication               | Dependent                                 | Dependent                                                                                          | Independent                                                                        | Independent                                             | Independent                                                                                             |

| Measurement                           | Global, low resolution                    | Global, high resolution                                                                            | Local,<br>medium/high<br>resolution                                                | Local,<br>medium/high<br>resolution                     | Local,<br>medium/high<br>resolution                                                                     |

| Sensitivity                           | Highly depends<br>on<br>communication     | Sensitive to<br>dynamic<br>interactions at<br>transients;<br>Highly depends<br>on<br>communication | Sensitive to<br>fault<br>impedance;<br>Sensitive to<br>fault close to<br>next zone | Sensitive to<br>distorted fault<br>current<br>waveforms | Sensitive to<br>system noise                                                                            |

| Issues in<br>practical<br>application | Limited by<br>communication<br>capability | Limited by<br>communication<br>capability                                                          | Coordination<br>of tripping<br>thresholds for<br>different<br>switches             | Selection of<br>proper tripping<br>thresholds           | Selection of<br>proper tripping<br>thresholds;<br>Time delay<br>introduced by<br>the low pass<br>filter |

Table 2.1 Comparison Of Different Fault Location Methods [47]

The communication-dependent methods rely on the exchange of information at different locations of the system via wide area communication: 1) Differential protection – The summation of current going into a given protection zone is compared to zero (or a given small value) to determine if fault happens within the protection zone. 2) Directional

protection – The direction of current flowing through the given relay will change when fault occurs at given protection zone. This protection method is often combined with other protection methods such as overcurrent protection in application.

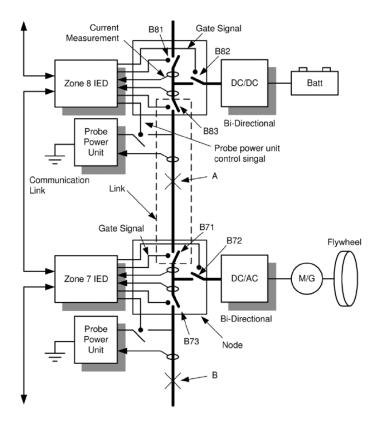

Other fault location techniques are often used in combination with differential protection [4]. Take a dc microgrid system shown in Figure 2.7 for example, Solid State Circuit Breakers (SSCBs) are adopted for interruption of fault current and isolation of faulted branch. These SSCBs are grouped to set zones for differential protection. After the faulted segment has been identified via differential protection and separated by the SSCBs, the probe power unit will be connected to test the fault status before reclosing the SSCBs [4].

Figure 2.7 Implementation of active impedance estimation on fault location in a dc microgrid system with SSCBs [4]

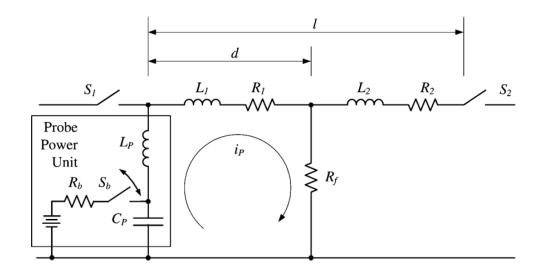

Figure 2.8 shows the circuit diagram of this fault location technique via active impedance estimation. The probe power unit consists of its own power source (battery), probe capacitor, probe inductor and connection switch. Once the probe voltage is applied to the faulted bus, the probe current will be induced as a system response to this second-order RLC circuit. With the knowledge of the parameters of the probe circuit, the distance to the fault location d can be readily calculated from the probe current frequency, and the fault resistance can be obtained via the envelope waveform of the probe current [4]. However, this method assumes that the fault persists even at the low probe voltage.

Figure 2.8 Circuit layout of fault location using active impedance estimation

Comparatively, the communication-independent methods only rely on information obtained locally: 1) Impedance protection – The apparent impedance, which is calculated through voltage and current measurements at switch terminals, is compared to tripping thresholds to determine if fault happens within the protection zone. 2) Overcurrent

protection – The current going through the switch is compared to tripping threshold to determine if fault occurs within the protection zone. This protection method often requires step-type coordination to guarantee the selectivity. 3) Current derivative protection – The current derivative is compared to tripping thresholds to determine if fault happens within the protection zone.

#### 2.2.2 DIFFERENTIAL PROTECTION

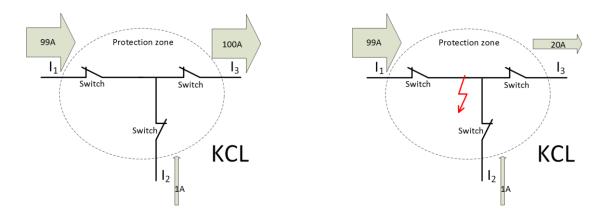

The operating mechanism for differential protection is illustrated in Figure 2.9, as the summation of current going into a given protection zone should be equal to (or very close to) the summation of current going out of a given protection zone when no fault occurs within this protection zone.

(a) No fault in the protection zone

(b) Fault occurs within the protection zone

#### Figure 2.9 Algorithm of differential protection

For the MVDC system shown in Figure 2.10, the whole system is partitioned into a number of protection zones for the purposes of fault localization and isolation. The remote sensors are distributed at the switches, where they measure current and send the digitized

current data to their corresponding controller. When a fault happens, the differential schemes will tell if the fault is inside or outside of its zone [22].

Figure 2.10 Zonal Arrangement of Differential Protection in the MVDC System [22]

## 2.2.3 IMPEDANCE PROTECTION

In the impedance protection scenario, dc switches autonomously decide to open or not based on their local interpretation of time-to-trip curves as functions of apparent circuit resistance. In the terrestrial power community this method is also called "distance protection". Only the actual distances in a dc microgrid may be very short. Each dc switch needs to look at its own current and voltage status and simultaneously make the same decision – whether the fault is very near to itself, or is it beyond its range of influence. The process can be divided into two distinct steps [48]:

1. Terminal resistance calculation – voltage sensors and current sensors are installed at the terminal of each dc switch to obtain voltage and current values. These real-

time data are transmitted through local wiring to the controller, that has also been placed locally with the switch, to calculate real-time apparent resistance at the output terminal for each sampling cycle using (2.1),

$$R_n(t) = \frac{V_n(t)}{I_n(t)}$$

(2.1)

Where;

$V_n$  is the voltage value at the terminal of switch 'n';

$I_n$  is the current value at the terminal of switch 'n';

$R_n$  is the apparent resistance at switch 'n' calculated from  $V_n / I_n$ .

2. Threshold resistance calculation – the real-time apparent resistance value R<sub>n</sub> is then compared with pre-defined thresholds in the local controller. If the controller recognizes an apparent resistance beyond pre-defined thresholds, the local switch will get an enabling signal from the local controller, so that it knows to open after the system is de-energized (refer to time period t4 shown in Figure 4.1). Notice here we are using two thresholds instead of a single threshold. This is because for a multi-terminal closed-loop ring bus MVDC system, characteristics of the fault such as location, type and impedance value, may not only affect the value but also the direction of current flow, which will result in a negative value for corresponding apparent resistance at the terminal. Therefore, the positive threshold for fault detection has to be smaller than the apparent resistance corresponding to the heaviest power flow from the pre-defined positive direction, yet the negative threshold has to be larger than the apparent resistance

corresponding to the heaviest power flow from the pre-defined negative direction, as shown in (2.2),

$$R_{th+} < \frac{V_r^2}{P_{r+}}; R_{th-} > \frac{V_r^2}{P_{r-}}$$

(2.2)

Where;

V<sub>r</sub> is the voltage value at current limiting mode;

$P_{r+}$  is the heaviest power flow at the direction by default;

$P_{r-}\xspace$  is the heaviest power flow at the reverse direction by default;

$R_{th+}$  is the positive threshold for fault detection;

$R_{th\mathchar`-}$  is the negative threshold for fault detection.

It is obvious that dc switches in different zones/locations have different priorities for opening. Each dc switch open only when its terminal apparent resistance falls into its own tripping thresholds. Hence these threshold values need to be properly chosen in order to guarantee the robustness and selectivity of this distance protection scheme [49].

# CHAPTER 3

# ANALYSIS OF ARC FAULT IN MVDC SYSTEMS

In order to evaluate our fault protection method, the characteristic of arc fault in MVDC systems should be studied. It is necessary to find out an arc model which can represent realistic arc effects that might hinder operation of the arc fault detector, so as the coverage and performance of LIFP regarding such fault scenarios can be identified.

As a most common fault in the MVDC system, short circuit fault can be triggered through a minor conductor (such as copper wire, steel screw, and pencil graphite) across the bus and the ground, a small animal bridging the conductors, condensation of water on an insulator or even impingement damage. It can rapidly develop into a lasting arc due to the absence of natural zero-crossing in the direct current. Apparently, this arc fault has different characteristics compared to bolted fault [48].

## 3.1 CHARACTERISTICS OF DC ARC FAULT

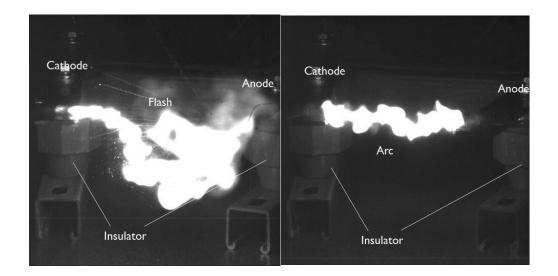

Various arc tests were performed by staff and researchers at CAPS on a fault testbed shown in Figure 3.1 [51]. These test data and test configurations are shared with us for research purpose. The cathode and the anode were connected across the dc source through metal rails, and supported by insulators off the ground. An ignition wire with 0.35 mm diameter was connected bridging the 88.9 mm (3.5 inch) gap between the electrodes. When MVDC was applied to the electrodes, current builds up in the wire and there is flash over the ignition gap as shown in Figure 3.1 (a). The evaporated metal materials from both

the wire and the surface of electrodes resulted in plasma jets, and eventually developed into a continually burning metal-vapor arc displayed in Figure 3.1 (b).

(a) Flash along the ignition wire (b) Arc across the electrode gap

Figure 3.1 Arc fault test through ignition wire [51]

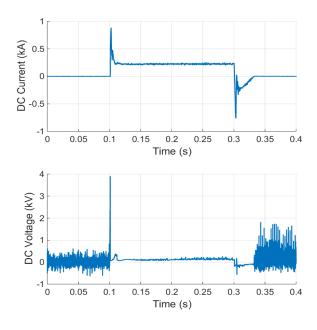

Due to the fact that the converters can run at different mode (voltage source mode (VSM) versus current source mode (CSM)) before and after fault occurs, it will be helpful to know how the characteristic of arc may vary regarding these two different modes. Figure 3.2 (a) shows an example of the arc voltage and arc current measured under VSM. The dc voltage across the electrodes was stepped from 0 to 6 kV at 0.1 s and then stepped back down to 0 kV after an additional 0.2 s. It is obvious that arc was formed rapidly once the testbed is energized, and lasted until the system is de-energized. The arc current varies from 200 A to 240 A, and the arc voltage varies around 100 V. Comparatively, Figure 3.2 (b) shows the measurements under CSM. The current was stepped from 0 to 200 A, and ramped down to 0 at 4 kA/s (limited by the power converter hardware settings) after 0.2 s.

It can be seen that the arc behaves differently as there is much less current overshoot at the initial phase of arc for the CSM than the VSM. This is one important reason why CSM is chosen over VSM when it comes to fault current limiting.

(a) Voltage source mode

(b) Current source mode

Figure 3.2 Arc current and voltage measured during test.

#### 3.2 ARC BRANCH MODEL

The next step is to develop an arc model based on the test data taken by staff and researchers at CAPS [51]. Considering the highly randomness of arc behavior along with large measurement noise, a model of dc arc is in need for evaluating the effectiveness of the impedance-based LIFP method. This model should reveal how the arc impedance is related to factors such as arc current and arc length, so that the range of fault impedance, which is the key in this study, can be found regarding a wide variety in fault conditions.

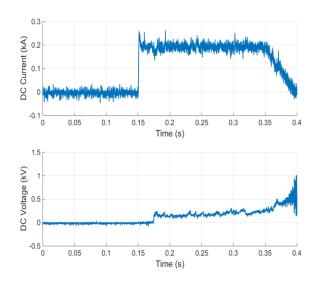

Figure 3.3 shows a dc arc branch model derived from a hyperbolic approximation of the voltage and current trajectory of arc fault in dc microgrids [52]. This model consists of a resistance r in series with an EMF source  $V_0$ . The arc voltage can be represented as:

$$V_{arc} = v_0 + r * i = V + \Delta v + (R + \Delta r) * i$$

(3.1)

Where V and R represent the mean value,  $\Delta v$  and  $\Delta r$  represent the randomness in each component as:

$$\mathbf{v}_0 = \mathbf{V} + \Delta \mathbf{v} \tag{3.2}$$

$$\mathbf{r} = \mathbf{R} + \Delta \mathbf{r} \tag{3.3}$$

Figure 3.3 An dc arc branch model

The dynamic resistance in the arc model can be obtained through:

$$dv_{arc}/di = r = R + \Delta r \tag{3.4}$$

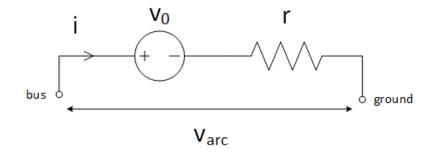

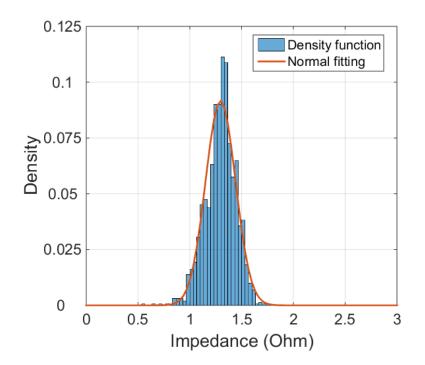

Thus, the built-in EMF source can be calculated via (3.1). For the arc test Figure 3.4 shows the probability density function and normal distribution fitting for 3600 sets of data regarding the built-in EMF source of arc calculated via (3.1)-(3.4) using a 1 kHz low pass filter. The two plots show good agreement in pattern. The mean value  $\mu$  given by the normal (Gaussian) distribution fitting equals to 100.5 V.

Figure 3.4 Density function and normal distribution fitting of the built-in EMF source in the arc model

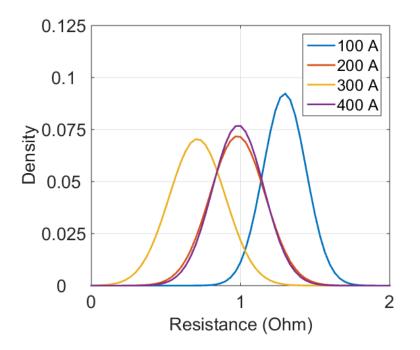

Similar tests with larger (3.5 inch) gap between electrodes have been carried out to explore the distribution function of the built-in EMF source of the arc. Figure 3.5 compares the normal distribution fitting of the built-in EMF source at different currents (50 A, 100 A, 200 A). Apparently, the mean value  $\mu$  of the built-in EMF source increases

with the arc current as also shown in Figure 3.5, while the standard deviation  $\sigma$  is in an inverse correlation with the arc current.

Figure 3.5 Normal distribution fitting of the EMF source of arc at different currents

Previous researchers have proposed various kinds of dc arc models, which were derived based on large amount of repetitive data through experiments, such as the Nottingham equation, the Stokes and Oppenlander equation, and the Paukert equations [53][54]. In Nottingham's study, the arc voltage for fixed arc length of 10 mm with copper electrodes is defined as a combination of a constant voltage drop and an exponential term related to the arc current [55]:

$$V_{\rm arc} = 27.5 + 44 \cdot I_{\rm arc}^{-0.67} \tag{3.5}$$

Stokes and Oppenlander also investigated the V-I characteristics of dc arc regarding different gap length (5 mm~500 mm) over a wide range of arc current (1 A~10 kA) through hugh amount of arc tests, including horizontal arc in open air with copper

electrodes and vertical arc in open air with aluminum electrodes. The arc voltage is found to decrease as the current level increase before a transition level, and increase after the transition level (10 A~100 A) which is related to the gap length. Their arc model removes the constant voltage drop, and defines that the arc voltage (so as the impedance) varies linearly with the length of gap L when the current is above transition level [53]:

$$V_{\rm arc} = (20 + 0.534 \cdot L) \cdot I_{\rm arc}^{0.12}$$

(3.6)

$$R_{arc} = (20 + 0.534 \cdot L) \cdot I_{arc}^{-0.88}$$

(3.7)

Similarly the Paukert equations provides very straightforward formulation of arc voltage and arc impedance in terms of arc current (ranged from 100 A to 100 kA):

$$V_{\rm arc} = a \cdot I_{\rm arc}^{\ b} \tag{3.8}$$

$$R_{arc} = a \cdot I_{arc}^{b-1}$$

(3.9)

Where a and b are both determined by the length of electrode gaps (ranged from 1 mm to 200 mm) [53]. A comparison of these three models shows that the arc impedance decreases nonlinearly with the increase of the arc current. However the arc impedance is highly unpredictable, and the three models show large discrepancy when current is less than 1 kA [55].

Figure 3.6 compares the test data with the Paukert equation and the Stokes and Oppenlander equation regarding the average value of arc impedance for different arc current when the length of gap is 88.9 mm (3.5 inch). It can be found from the test data that the arc impedance drops as the arc current increases from 100A to 300A. This can be explained as higher current level of arc will generate more heat, which can bring in more metal materials that evaporated from the electrodes to form a more conductive arcing

channel. However, as current level approaches to 400A, the arc impedance turns to increase, which may be caused by other factors such as the turbulence of air under higher temperature. Curve fitting of the test data shows a similar pattern compared to the other two models, though they are different in magnitude. Hence the steady-state arc impedance over the span that the arc current is from 100 A to 400 A:

$$R_{arc} = 79 \cdot I_{arc}^{-0.83}$$

(3.10)

Figure 3.6 Comparison of test data with arc models regarding average value of arc impedance for different current level (length of gap at 88.9 mm)

The relationship between arc impedance and length of gap has been revealed in Figure 3.7, which is also based on data acquired through the experiments. There were two trials for each test point. The average value of arc impedance was calculated through the voltage and current measurements over a certain period of time (50ms) when the arc fault was relatively stable across the gap. It can be seen from Figure 3.7 that the average value of arc

impedance increases as the length of gap increases from 3.5 inches to 8 inches. This result can be explained as the increase of length of gap will result in the increase of arc length, and eventually cause the increase of arc voltage (as long as the source voltage is larger than the arc voltage). Calculations through the Paukert equation and the Stokes and Oppenlander equation show similar pattern that the arc impedance increases linearly with the length of gap. Thus an arc model with similar form of (3.7) is chosen based on the result in (3.10):

$$R_{arc} = (c + d \cdot L) \cdot I_{arc}^{-0.83}$$

(3.11)

The factors of equations (3.11) for the arc model can be obtained through curve fitting as show in Figure 3.7, so as the steady-state arc impedance over the span that the arc length is from 88.9 mm to 203.2 mm (3.5 inch to 8 inch):

$$R_{arc} = (44.9948 + 0.4634 \cdot L) \cdot I_{arc}^{-0.83}$$

(3.12)

Figure 3.7 Comparison of test data with arc models regarding average value of arc impedance for different length of gap (current level at 200 A)

Apparently, these factors have different values compared to those formulated in (3.7). It can result from the highly dependency of arc impedance on various factors other than the length of gap and arc current, such as ambient temperature, electrode material, electrode configurations and etc. This finding further supports the fact that the arc characteristic can vary dramatically under different circumstances. Thus the problem in a circuit protection system is that a very broad range of all possible short-circuit arcs need to be correctly identified. Figure 3.8 lists the arc impedance for arc length from 1 mm to 300 mm and currents from 100 A to 10 kA based on the proposed model (3.12). The arc impedance is found can vary from  $0.1 \Omega$  to  $4 \Omega$ .

Figure 3.8 Arc impedance for different currents and arc length

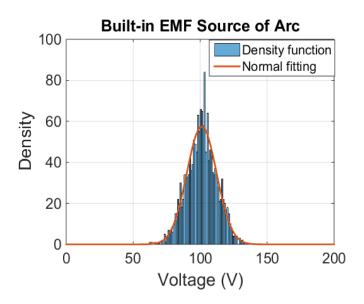

Due to the highly randomness of arc impedance in time even when the arc is relatively stable, the distribution pattern of arc impedance in time is investigated to help form a more detailed arc model. Figure 3.9 (a) shows the probability density function and normal distribution fitting for 1600 sets of arc impedance data calculated through voltage and current measurements. The probability density of the normal distribution is described as:

$$f(\mathbf{x}|\mu,\sigma^{2} = \frac{1}{\sqrt{2\sigma^{2}\pi}}e^{-\frac{(\mathbf{x}-\mu)^{2}}{2\sigma^{2}}})$$

(3.13)

Where  $\mu$  is the mean value, and  $\sigma$  is the standard deviation. Again it is an arc across 88.9 mm (3.5 inch) gap with current reference at 100A. A low pass filter was used for reducing measurement noise so the bandwidth is limited at 1 kHz. These two plots show good agreement in distribution pattern. Moreover, Figure 3.9 (b) compares normal distribution fittings of arc impedance regarding different arc current. Apparently  $\mu$  falls into the range from 0.1  $\Omega$  to 4  $\Omega$  as discussed, while  $\sigma$ , which indicates the noise level of the arc impedance, is within the range from 0.15 to 0.19.

(a) Density function and normal distribution fitting of arc impedance

(b) Normal distribution fitting of arc impedance regarding different current Figure 3.9 Statistical distributed behavior of arc impedance

It should be noticed that the characteristic of arc fault varies case by case in the dc systems. The behavior of the arc can still be affected by a combination of electrical, magnetic, thermal, dimensional and material factors other than current and arc length, so as it is difficult for an arc model to represent universal arc faults that may happen in the dc system. However, this analysis gives a general idea of how the dc arc may behave in such fault events. Also the upper and lower limits of likely arc impedance properties are obtained, so as the functionality of LIFP can be evaluated out to these limits. The normal distribution model (3.13) for the arc impedance is adopted for the following study to include the impact from arc noise.

# CHAPTER 4

### COORDINATION OF PROTECTION SCHEMES IN MVDC SYSTEMS

Conventional ac systems generally rely on mechanical breakers to interrupt fault current and eventually isolate the faulted section from the whole system. However when it comes to dc systems, especially MVDC system, this strategy may encounter with big problems, because it is rather difficult to extinguish dc arc across the contacts of breakers/switches as there is no natural zero-crossing for dc current. Some electronic circuit breakers, such as Z-source solid state circuit breakers, have been proposed in literatures as alternatives [56]-[58] because they don't arc and therefore are not susceptible to faults of arcing contacts. But they can have drawbacks in terms of conduction loss and voltage oscillations.

Another solution is to design an MVDC system which operates without breakers [59]. Instead, the fault current can be brought down to zero via power converters. Thus this protection scheme relies on coordinated control of power converters and non-fault-breaking mechanical disconnect switches to effect the fault clearance process— fault detection and localization, complete de-energizing of the system, isolation of faulted branch and re-energizing of the system [60]-[63]. On top of this fault protection scheme, the fault localization can be accomplished via various fault location methods categorized in Section 2.2. One proposed solution for an MVDC shipboard system is to combine a communication-dependent method with a communication-independent method: The

CFP method depends on communication between distributed sensors and a central decision-making authority to achieve fastest primary protection. It is backed up by a local response function LIFP that takes over in case of failure in the primary method.

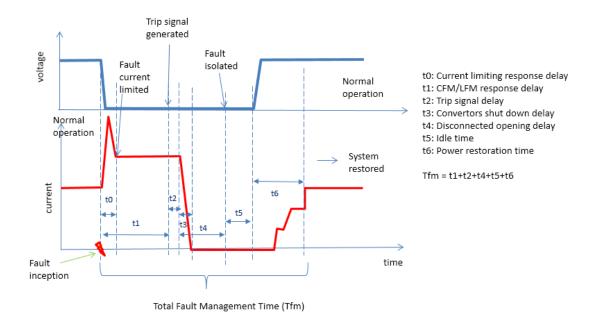

## 4.1 PROTECTION PROCEDURES OF THE FAULT CLEARANCE

Due to the breakerless feature of the MVDC system, the fault clearance sequence is defined as follows [48]:

a. Fault detection and localization – When a fault happens, all power converters that feed the ring bus will be forced into current-limiting mode by their built-in overcurrent protection scheme. Then both CFP and LIFP will work independently to detect and locate the fault.

b. Completely de-energizing of the system – After the fault location is identified, the system will be completely de-energized.

c. Isolation of faulted branch – Corresponding disconnect switches will be actuated to open once the initial discharge current from all the capacitance in the MVDC system decays to zero thus isolating the faulted section.

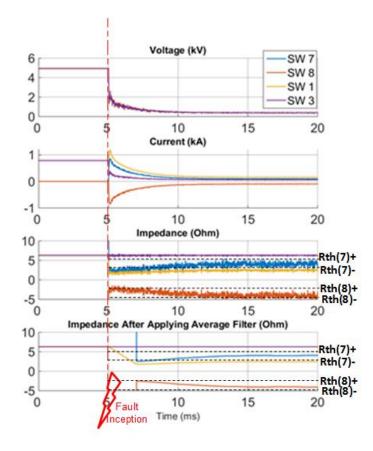

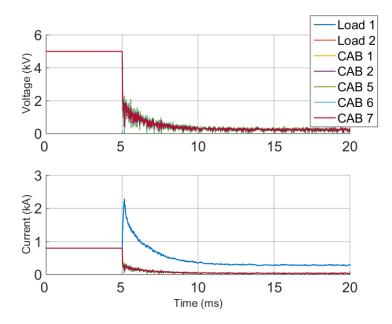

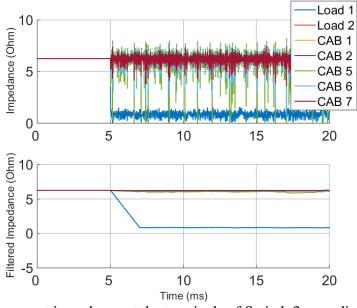

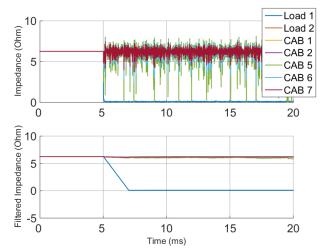

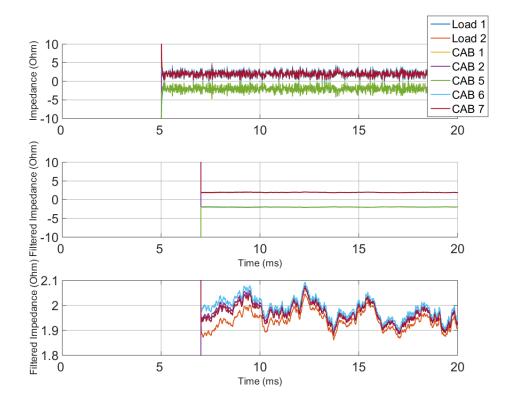

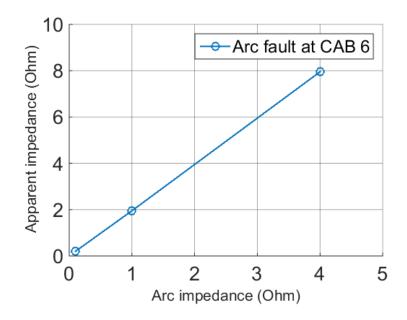

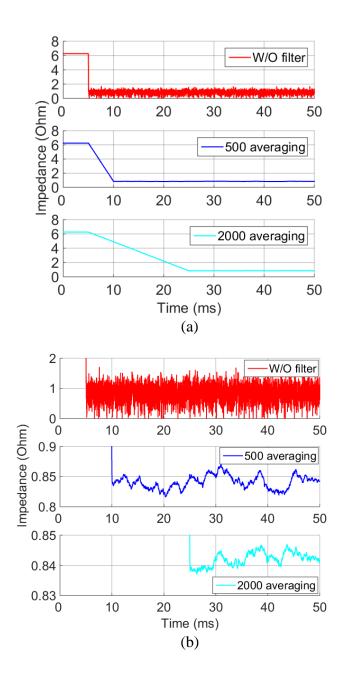

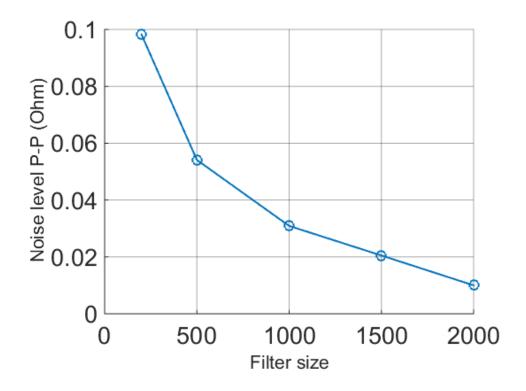

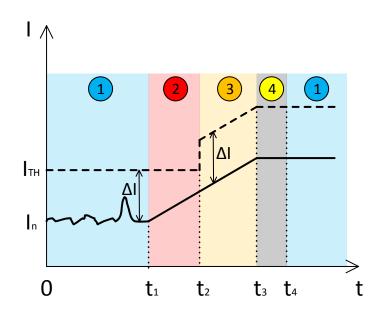

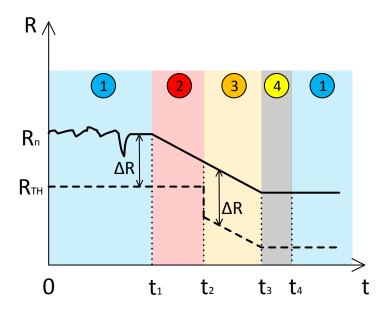

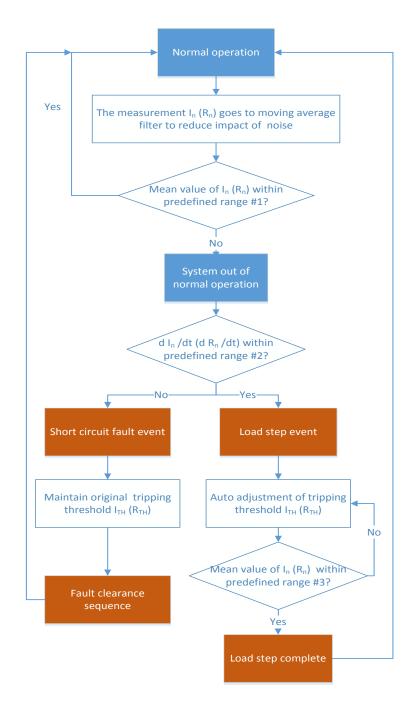

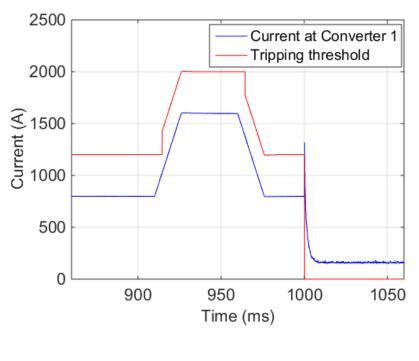

d. Re-energizing the system – After the fault is isolated by proper operation of switches, the converters re-energize the system.