# HIGH FREQUENCY CONTINUOUS TIME FILTERS IN DIGITAL CMOS PROCESSES

by Shanthi Pavan Yannis Tsividis

Kluwer Academic Publishers Boston/Dordrecht/London

#### HIGH FREQUENCY CONTINUOUS TIME FILTERS IN DIGITAL CMOS PROCESSES

#### HIGH FREQUENCY CONTINUOUS TIME FILTERS IN DIGITAL CMOS PROCESSES

#### **Shanthi Pavan**

Texas Instruments, Incorporated

**Yannis Tsividis**

Columbia University

KLUWER ACADEMIC PUBLISHERS

New York / Boston / Dordrecht / London / Moscow

eBook ISBN: 0-306-47014-4 Print ISBN: 0-792-37773-7

©2002 Kluwer Academic Publishers New York, Boston, Dordrecht, London, Moscow

Print ©2000 Kluwer Academic Publishers Massachusetts

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Kluwer Online at: http://kluweronline.com

and Kluwer's eBookstore at: http://ebooks.kluweronline.com

#### **Contents**

| Lis | t of      | Figures                                                     | ix       |

|-----|-----------|-------------------------------------------------------------|----------|

| Lis | st of     | Tables                                                      | xix      |

| Pr  | eface     |                                                             | xxi      |

| 1.  | INT       | RODUCTION                                                   | 1        |

|     | 1.        | MOTIVATION                                                  | 1        |

| 2.  | МО        | S CAPACITOR MODELING                                        | 5        |

|     | 1.        | INTRODUCTION                                                | 5        |

|     | 2.        | DISTORTION GENERATION IN NONLINEAR CAPACITORS               | 6        |

|     | 3.        | GATE CAPACITOR STRUCTURES IN CMOS TECHNOLOGY                | 8        |

|     | 4.        | MODELING OF ACCUMULATION MOS CAPACITORS FOR ANALOG          | 40       |

|     | 5.        | DESIGN SIMULATION RESULTS AND MODEL VALIDATION              | 10<br>13 |

|     | 5.<br>6.  | MODEL IMPLEMENTATION                                        | 15       |

|     | 0.<br>7.  | THE POLYSILICON GATE DEPLETION EFFECT                       | 19       |

|     | 7.<br>8.  | MEASUREMENT RESULTS AND DISCUSSION                          | 22       |

|     | o.<br>9.  | HIGH FREQUENCY CHARACTERISTICS                              | 23       |

|     | 3.<br>10. |                                                             | 28       |

|     |           | SUMMARY                                                     | 31       |

|     |           | GOWINATO                                                    |          |

| 3.  | ΑF        | REVIEW OF INTEGRATOR ARCHITECTURES                          | 33       |

|     | 1.        | INTRODUCTION                                                | 33       |

|     | 2.        | NON-IDEALITIES IN INTEGRATORS                               | 33       |

|     | 3.        | MOSFET-C FILTERS                                            | 37       |

|     | 4.        | Gm-C FILTERS                                                | 42       |

|     | 5.        | Gm-OTA-C FILTERS                                            | 46       |

|     | 6.        | A STUDY OF CMOS TRANSCONDUCTORS                             | 48       |

|     | 7.        | PROBLEMS OF PROGRAMMABLE FILTER DESIGN                      | 56       |

|     | 8.        | APPROACHES TO THE DESIGN OF WIDELY PROGRAMMABLE INTEGRATORS | 60       |

#### vi HIGH FREQUENCY CONTINUOUS TIME FILTERS

|    | 9.                                            | CONCLUSIONS                                                                                                                                                                                                                                                                       | 69                                                 |

|----|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 4. | TIM<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7. | E SCALING IN ELECTRICAL NETWORKS INTRODUCTION TIME SCALING: DEFINITION THE LINEAR CASE NOISE PROPERTIES OF SCALED NETWORKS EXTENSION OF SCALING TO THE NONLINEAR CASE DISTORTION IN WEAKLY NONLINEAR SCALED FILTERS IMPLEMENTATION OF SCALED INTEGRATORS IN CMOS VLSI CONCLUSIONS | 71<br>71<br>72<br>72<br>75<br>79<br>86<br>90<br>93 |

| 5. | 1.<br>2.<br>3.<br>4.<br>5.                    | FILTER DESIGN                                                                                                                                                                                                                                                                     | 95<br>95<br>98<br>103<br>109<br>116<br>120         |

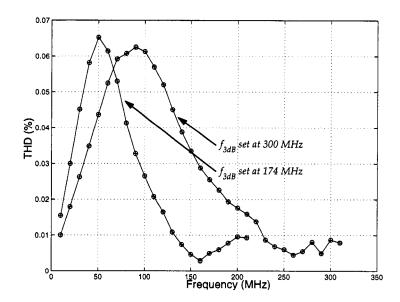

| 6. | 1.                                            | TER TESTING AND MEASUREMENT RESULTS INTRODUCTION FREQUENCY RESPONSE FILTER OUTPUT NOISE DISTORTION TEMPERATURE MEASUREMENTS SUMMARY                                                                                                                                               | 133<br>133<br>136<br>138<br>143<br>143<br>145      |

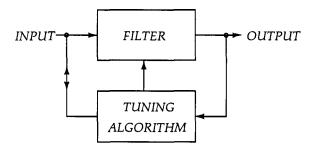

| 7. | 1,<br>2.                                      | RTHER APPLICATIONS OF SCALING INTRODUCTION NAUTA'S CMOS VHF FILTER TECHNIQUE IMPROVED FILTER TECHNIQUE A MODIFIED Gm-OTA-C TECHNIQUE SUMMARY AND CONCLUSIONS                                                                                                                      | 149<br>149<br>149<br>152<br>157<br>160             |

| 8. | TUN<br>1.<br>2.<br>3.<br>4.<br>5.             | IING IN CONTINUOUS-TIME FILTERS INTRODUCTION THE VOLTAGE CONTROLLED FILTER TECHNIQUE THE VOLTAGE CONTROLLED OSCILLATOR TECHNIQUE AN ANALYTICAL SOLUTION TO A CLASS OF OSCILLATORS APPLICATIONS OF THE FILTER COMPARATOR OSCILLATOR TO FILTER TUNING CONCLUSION                    | 165<br>165<br>167<br>170<br>172<br>182<br>188      |

| Contents                                                                       | vii |

|--------------------------------------------------------------------------------|-----|

| Appendices                                                                     |     |

| A-AN EXPLICIT EXPRESSION FOR Ψ <sub>S</sub> IN A MOS<br>ACCUMULATION CAPACITOR | 199 |

| B-CALCULATION OF THE BIAS VOLTAGE AT WHICH $\frac{dC_{GB}}{dV_{GB}}=0$         | 201 |

| C-SUMMARY OF THE PROPERTIES OF A DISTRIBUTED RC LINE                           | 205 |

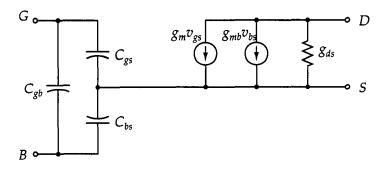

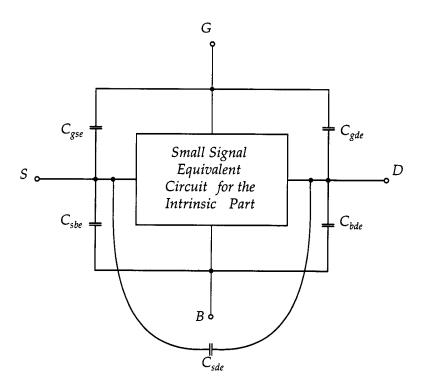

| D-SMALL SIGNAL MOS TRANSISTOR MODELS                                           | 207 |

| 1. OPERATION IN STRONG INVERSION AND SATURATION                                | 207 |

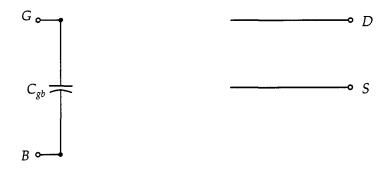

| 2. MODEL WHEN THE DEVICE IS OFF                                                | 209 |

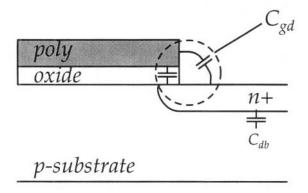

| 3. EXTRINSIC PARASITICS                                                        | 209 |

| E-CALCULATION OF THE STEADY STATE WAVEFORM OF THE FILTER COMPARATOR OSCILLATOR | 211 |

| Index                                                                          |     |

|                                                                                | 213 |

#### **List of Figures**

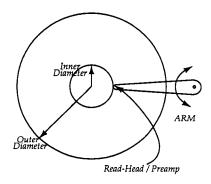

| 1.1  | A hard disc platter.                                                                                                                                                                                                           | 2  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

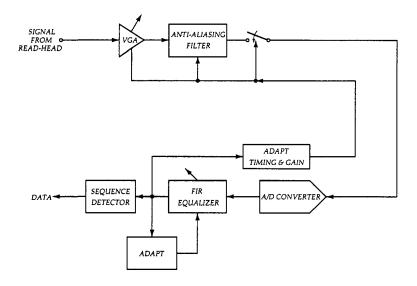

| 1.2  | The simplified block diagram of a read-channel chip.                                                                                                                                                                           | 2  |

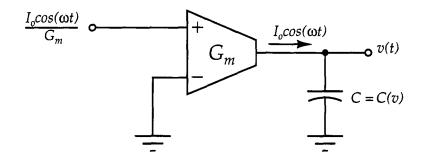

| 2.1  | Gm-C integrator with a non-linear capacitor.                                                                                                                                                                                   | 6  |

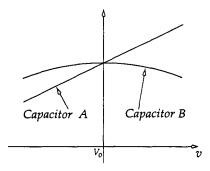

| 2.2  | Capacitor A generates a much smaller third harmonic than Capacitor B.                                                                                                                                                          | 8  |

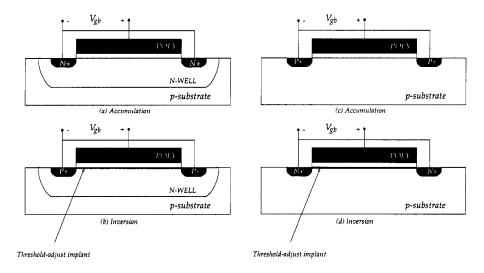

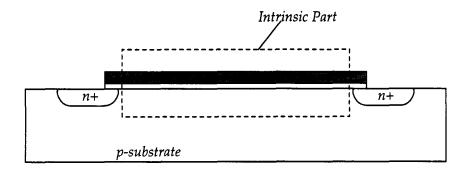

| 2.3  | Gate capacitor structures in an <i>n</i> -well CMOS technology.                                                                                                                                                                | 9  |

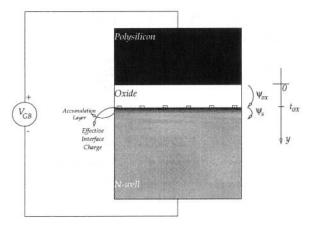

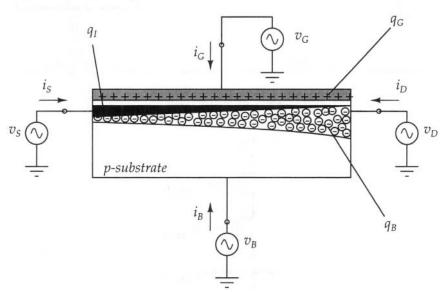

| 2.4  | Cross section of an MOS capacitor.                                                                                                                                                                                             | 11 |

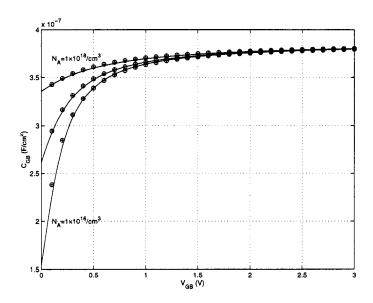

| 2.5  | Comparison of numerical simulation and proposed models for different values of substrate doping concentration (– numerical, $\oplus$ proposed). $C'_{ox} = 3.84 \text{ fF}/\mu\text{m}^2$ , $V_{FB} = 0$ , $T=300 \text{ K}$ . | 14 |

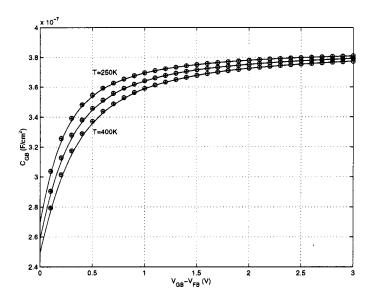

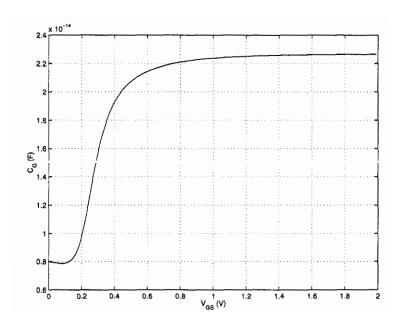

| 2.6  | Variation of capacitance with temperature(- numerical, $\oplus$ proposed). $C'_{ox} = 3.84 \text{ fF}/\mu\text{m}^2$ , $V_{FB} = 0$ , $N_D = 10^{17} \text{ cm}^{-3}$ .                                                        | 14 |

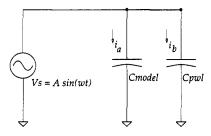

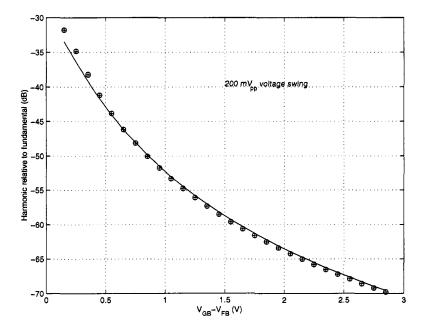

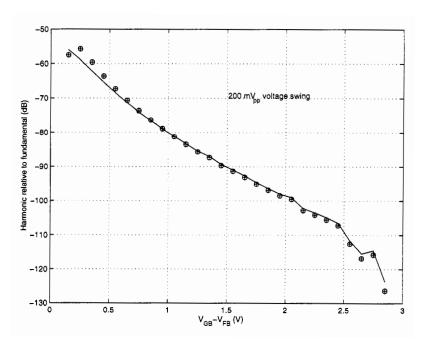

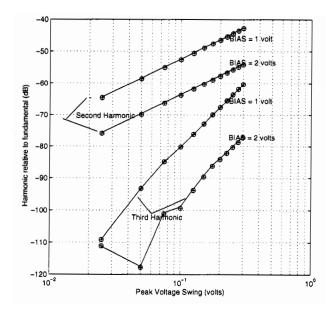

| 2.7  | Circuit to compare both piecewise linear and explicit models.                                                                                                                                                                  | 16 |

| 2.8  | Second harmonic relative to fundamental(− P-WL, ⊕ proposed).                                                                                                                                                                   | 16 |

| 2.9  | Third harmonic relative to fundamental(− PWL, ⊕ proposed).                                                                                                                                                                     | 17 |

| 2.10 | Harmonics relative to fundamental for different values of bias voltage( $-$ PWL, $\oplus$ proposed).                                                                                                                           | 17 |

|      |                                                                                                                                                                                                                                |    |

#### x HIGH FREQUENCY CONTINUOUS TIME FILTERS

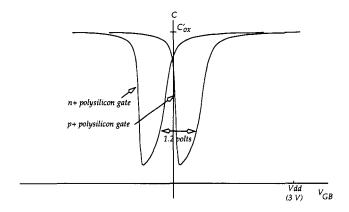

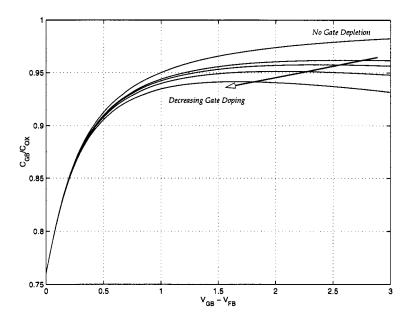

| 2.11 | Qualitative C-V curves of a MOS capacitor with                     |    |

|------|--------------------------------------------------------------------|----|

|      | n+ and $p+$ polysilicon gates. Since an $n-$ type                  |    |

|      | substrate is assumed, accumulation is to the                       |    |

|      | right of the minimum on each curve.                                | 18 |

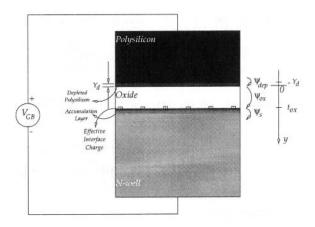

| 2.12 | MOS capacitor cross section.                                       | 19 |

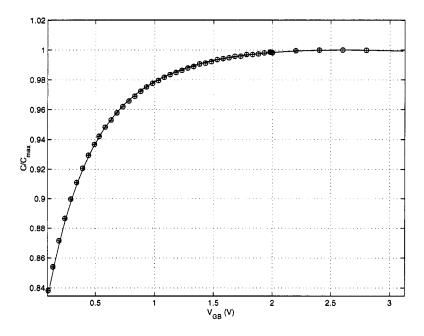

| 2.13 | Comparison of complete model with measure-                         |    |

|      | ments. $t_{ox} = 85 \text{ Å}(-\text{model}, \oplus \text{data}).$ | 23 |

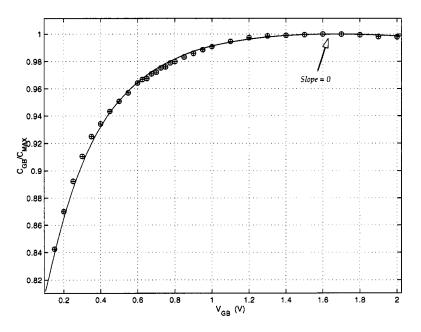

| 2.14 | Comparison of complete model with measure-                         |    |

|      | ments. $t_{ox} = 45 \text{ Å}(-\text{model}, \oplus \text{data}).$ | 24 |

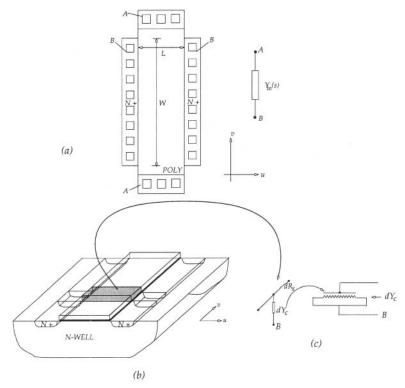

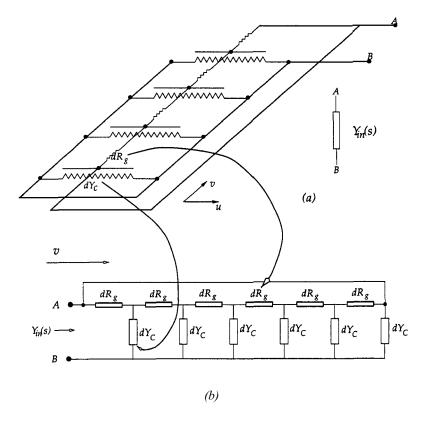

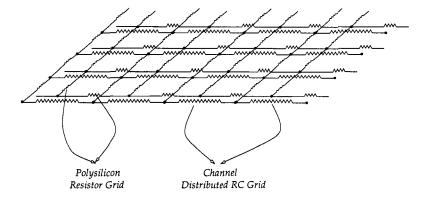

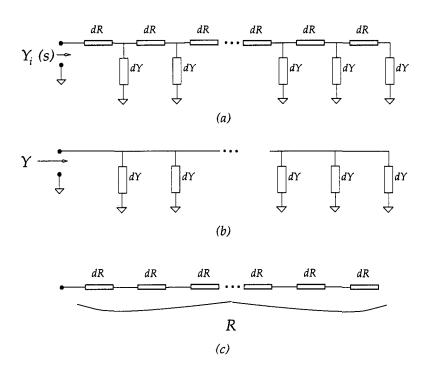

| 2.15 | Structure of the MOS capacitor and derivation                      |    |

|      | of a two dimensional $\overline{URY}$ equivalent circuit.          | 25 |

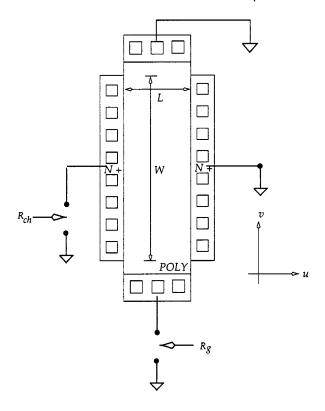

| 2.16 | Distributed Model for the MOS capacitor.                           | 26 |

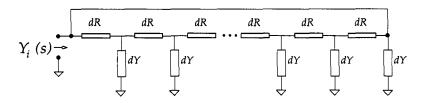

| 2.17 | Definitions of $R_{ch}$ and $R_{g}$ .                              | 27 |

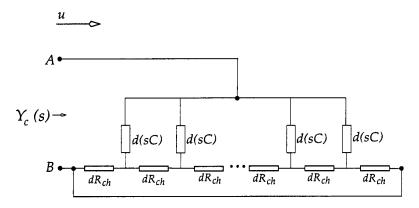

| 2.18 | Distributed network to calculate $Y_c(s)$ .                        | 27 |

| 2.19 | Part of a grid to simulate 2-D effects in SPICE.                   | 29 |

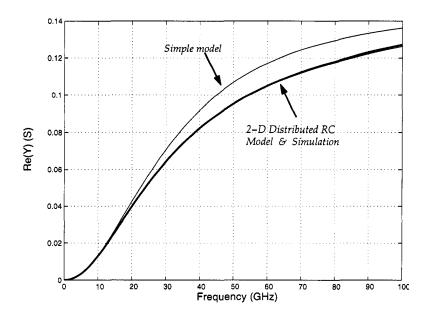

| 2.20 | Re(Y) computed using various models.                               | 29 |

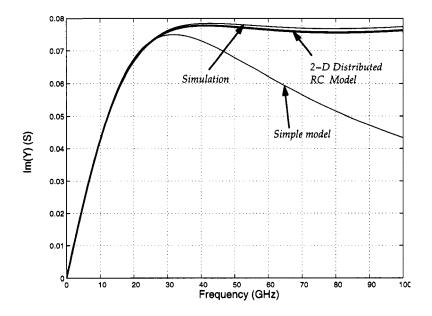

| 2.21 | Im(Y) computed using various models.                               | 30 |

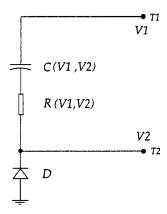

| 2.22 | Complete model for the poly-n-well MOS accu-                       |    |

|      | mulation capacitor.                                                | 30 |

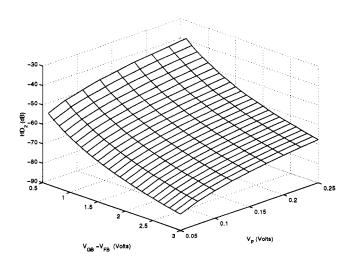

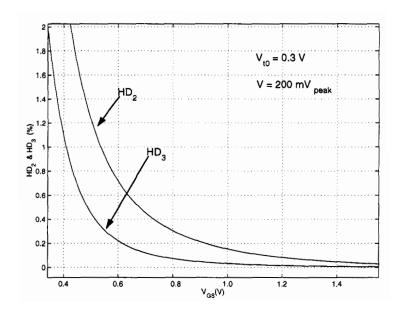

| 2.23 | $HD_2$ as a function of bias voltage and signal level.             | 32 |

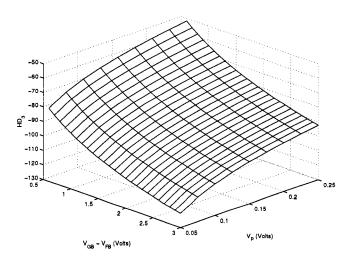

| 2.24 | $HD_3$ as a function of bias voltage and signal level.             | 32 |

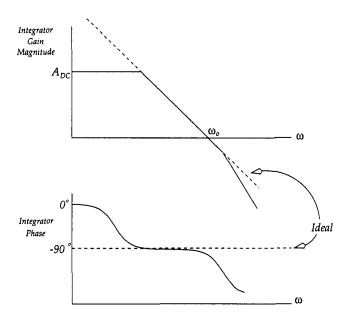

| 3.1  | Magnitude and phase responses of an integrator                     | 34 |

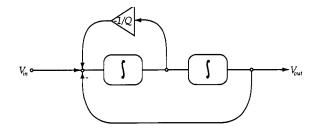

| 3.2  | Pole forming section of a biquad                                   | 35 |

| 3.3  | Pole forming section of a biquad with non-ideal                    |    |

|      | integrators                                                        | 35 |

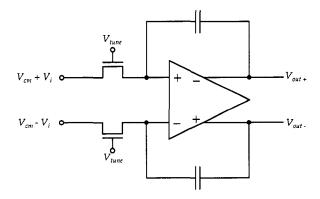

| 3.4  | A MOSFET-C integrator                                              | 37 |

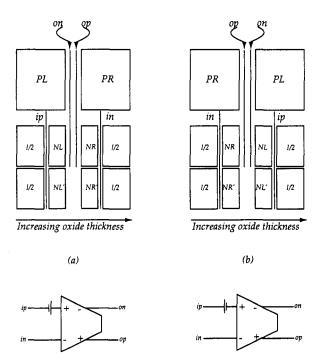

| 3.5  | Conceptual schematics of MOSFET-C integrators                      |    |

|      | with accumulation capacitors.                                      | 39 |

| 3.6  | A MOSFET-C integrator using accumulation ca-                       |    |

|      | pacitors.                                                          | 40 |

| 3.7  | An alternate MOSFET-C integrator using accu-                       |    |

|      | mulation capacitors.                                               | 41 |

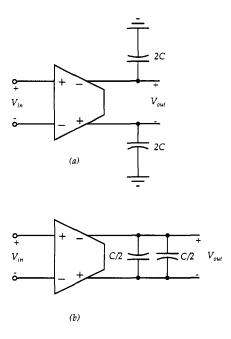

| 3.8  | Two versions of the Gm-C integrator.                               | 43 |

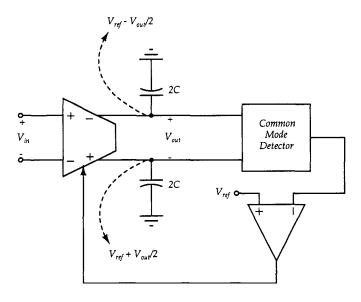

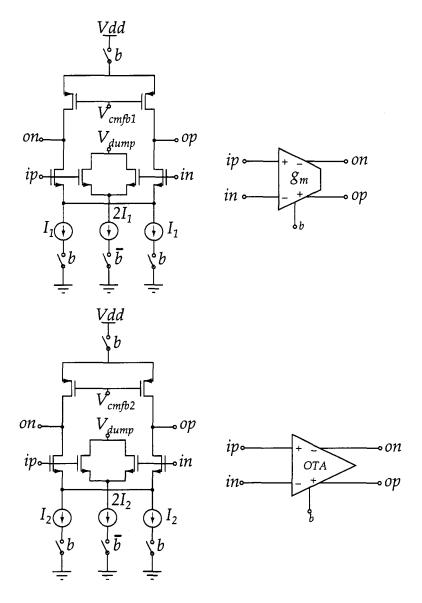

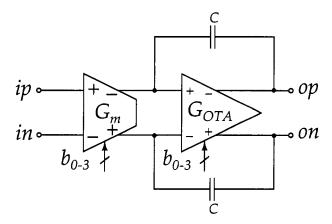

| 3.9  | The Gm-C integrator with the common-mode                           |    |

|      | setting loop explicitly shown.                                     | 44 |

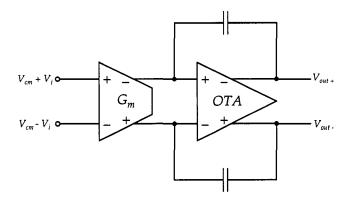

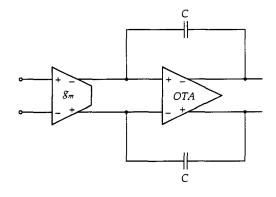

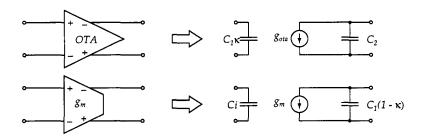

| 3.10 | A conceptual schematic of a Gm-OTA-C integra-                      |    |

|      | tor.                                                               | 46 |

|      | List of Figures                                                                                                                                                                                                                                                                                           | хi |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

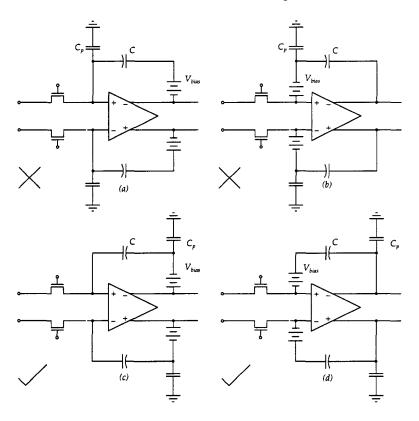

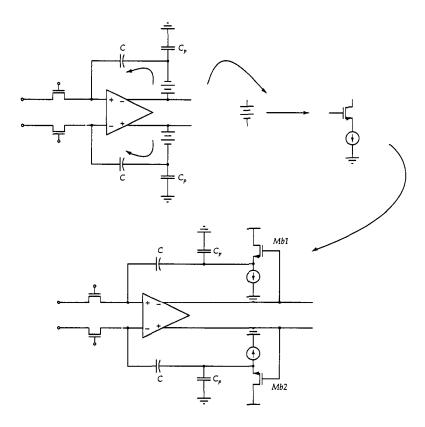

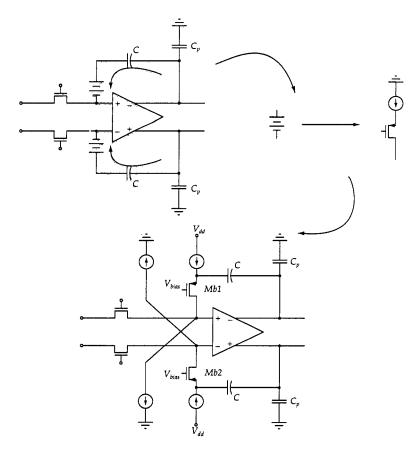

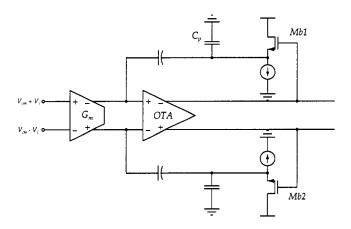

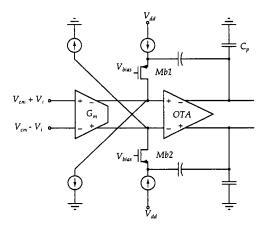

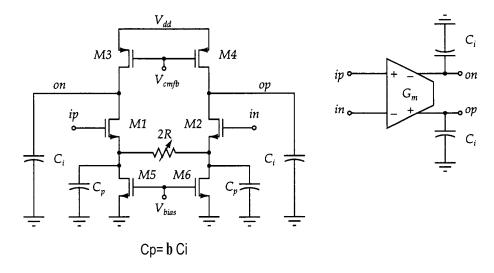

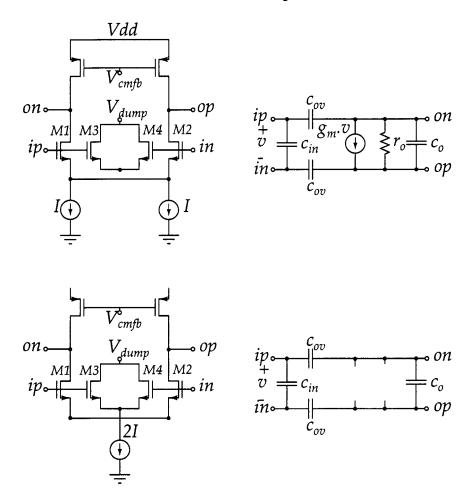

| 3.11 | Schematic of a Gm-OTA-C integrator with accumulation capacitors.                                                                                                                                                                                                                                          | 47 |

| 3.12 | Alternative schematic of a Gm-OTA-C integrator with accumulation capacitors.                                                                                                                                                                                                                              | 48 |

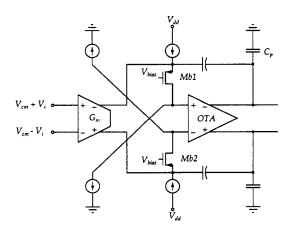

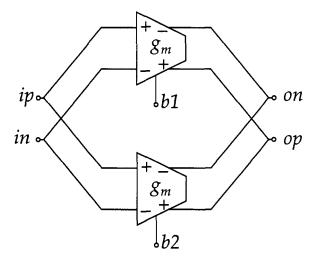

| 3.13 | Another Gm-OTA-C integrator with accumula-                                                                                                                                                                                                                                                                |    |

|      | tion capacitors.                                                                                                                                                                                                                                                                                          | 48 |

| 3.14 | A degenerated differential pair.                                                                                                                                                                                                                                                                          | 49 |

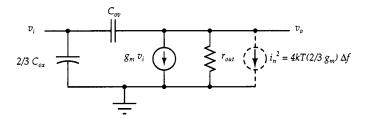

| 3.15 | A degenerated differential pair with parasitic                                                                                                                                                                                                                                                            |    |

|      | effects and excess noise sources.                                                                                                                                                                                                                                                                         | 50 |

| 3.16 | The transconductor of Krummenacher and Joehl.                                                                                                                                                                                                                                                             | 52 |

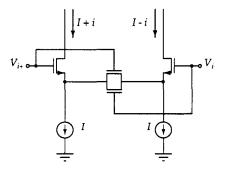

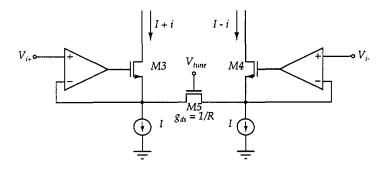

| 3.17 | Transconductors based on opamps.                                                                                                                                                                                                                                                                          | 52 |

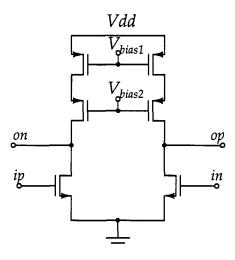

| 3.18 | Conceptual schematic.                                                                                                                                                                                                                                                                                     | 53 |

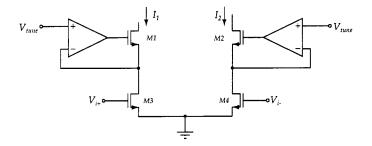

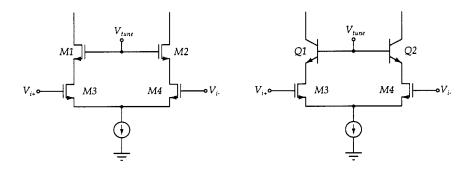

| 3.19 | Realizations in CMOS and BiCMOS.                                                                                                                                                                                                                                                                          | 53 |

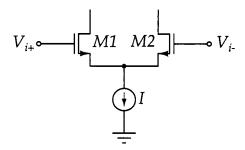

| 3.20 | The differential pair.                                                                                                                                                                                                                                                                                    | 54 |

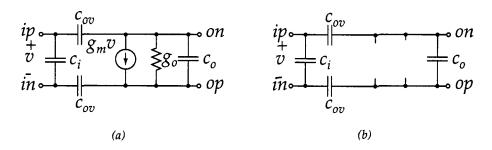

| 3.21 | Small signal single ended equivalent circuit of a differential pair.                                                                                                                                                                                                                                      | 55 |

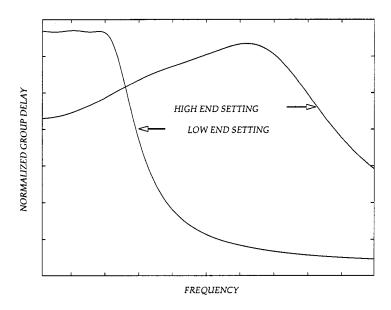

| 3.22 | Aberrations in filter response at high bandwidth                                                                                                                                                                                                                                                          |    |

|      | settings due to variations in phase error.                                                                                                                                                                                                                                                                | 59 |

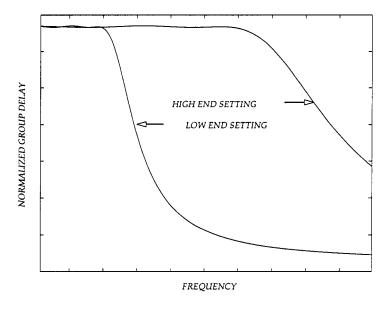

| 3.23 | Response of a programmable filter, where the                                                                                                                                                                                                                                                              |    |

|      | integrators have a constant phase error, indepen-                                                                                                                                                                                                                                                         |    |

|      | dent of their unity gain frequencies.                                                                                                                                                                                                                                                                     | 59 |

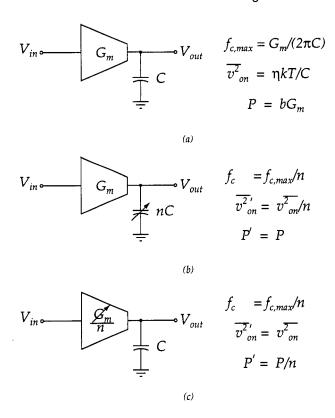

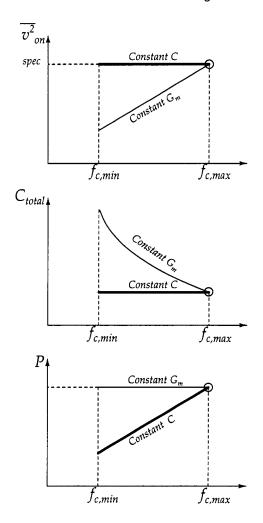

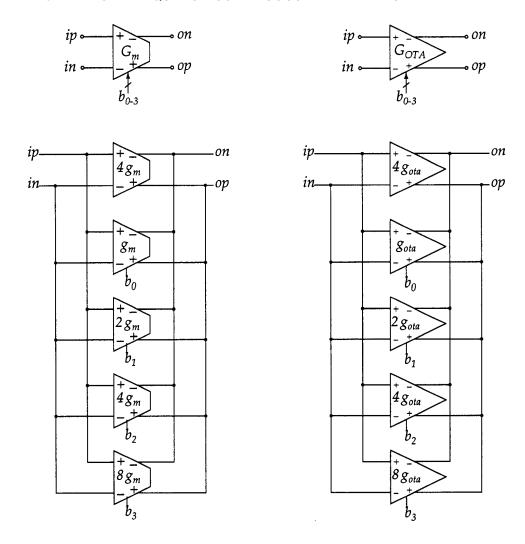

| 3.24 | (a) A Gm-C integrator designed to achieve the maximum cutoff frequency in a programmable range; (b) Lowering the cutoff frequency of (a) by increasing the capacitance ("constant $G_m$ " approach); (c) Lowering the cutoff frequency of (a) by decreasing the transconductance ("constant C" approach.) | 61 |

| 2 25 |                                                                                                                                                                                                                                                                                                           | 01 |

| 3.25 | Variation of mean squared noise, total capacitance and power dissipation versus cutoff frequency for programmable integrators using the "constant $G_m$ " approach (thin line) and the "constant $C$ " approach (thick line). The circle indicates a design optimized for the maximum                     |    |

| 2.26 | $f_c$ setting.                                                                                                                                                                                                                                                                                            | 63 |

| 3.26 | A conventional Gm-C integrator.                                                                                                                                                                                                                                                                           | 64 |

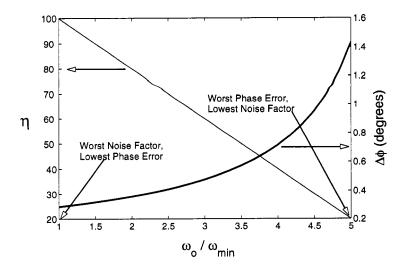

| 3.27 | $\eta$ and $\Delta \phi$ as a function of $w_0$ .                                                                                                                                                                                                                                                         | 65 |

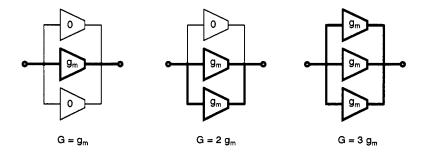

| 3.28 | A programmable transconductor using multiple                 |    |

|------|--------------------------------------------------------------|----|

|      | switchable unit transconductors.                             | 66 |

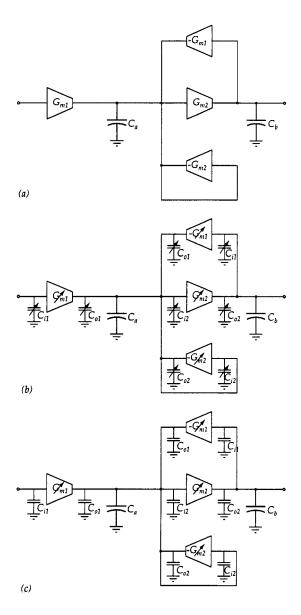

| 3.29 | (a) A second order Gm-C filter; (b) The filter in            |    |

|      | (a), made programmable by varying transcon-                  |    |

|      | ductances; the parasitic input and output capac-             |    |

|      | itances also vary, as indicated by arrows; (c) The           |    |

|      | filter in (a), assuming all parasitics remain fixed          |    |

|      | while transconductances are varied.                          | 68 |

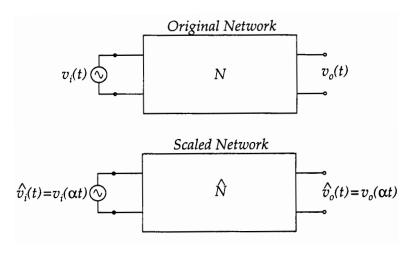

| 4.1  | Definition of time scaling.                                  | 72 |

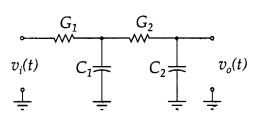

| 4.2  | An example network.                                          | 74 |

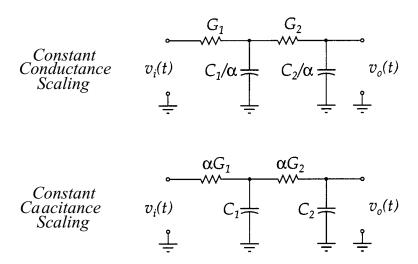

| 4.3  | Illustration of constant-conductance and constant-           |    |

|      | capacitance scaling for the network of Figure 4.2.           | 75 |

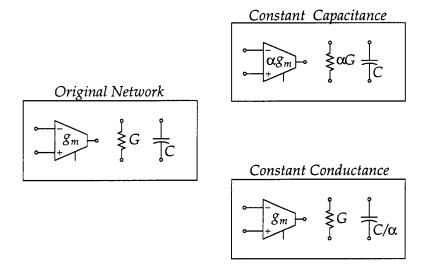

| 4.4  | Illustration of constant-conductance and constant-           |    |

|      | capacitance scaling for a general (trans)conductance-        |    |

|      | capacitance network.                                         | 75 |

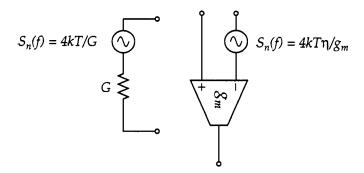

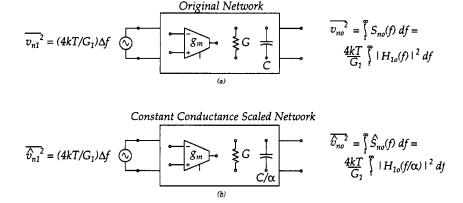

| 4.5  | Noise model for the conductances and transconductors.        | 76 |

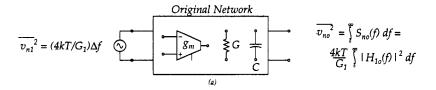

| 4.6  | Noise properties of constant-conductance scaled              |    |

|      | networks.                                                    | 76 |

| 4.7  | Noise properties of constant-capacitance scaled              |    |

|      | networks.                                                    | 78 |

| 4.8  | Model for nonlinear (trans)conductors and capacitors.        | 80 |

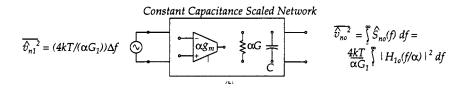

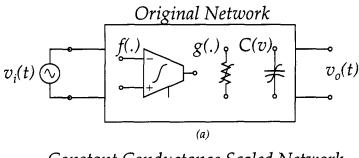

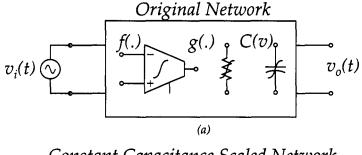

| 4.9  | Constant-conductance scaling in nonlinear networks.          | 81 |

| 4.10 | Constant-capacitance scaling in nonlinear networks.          | 84 |

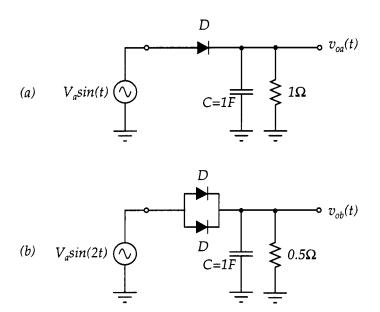

| 4.11 | A network example to illustrate scaling - (a)                |    |

|      | Original network, (b) network constant-C scaled              |    |

|      | by $\alpha = 2$ .                                            | 85 |

| 4.12 | Top: Output waveform $v_{oa}(t)$ , Middle: Output            |    |

|      | waveform $v_{ob}(t)$ , Bottom: $v_{oa}(t)$ and $v_{ob}(t/2)$ |    |

|      | overlaid on the same plot.                                   | 86 |

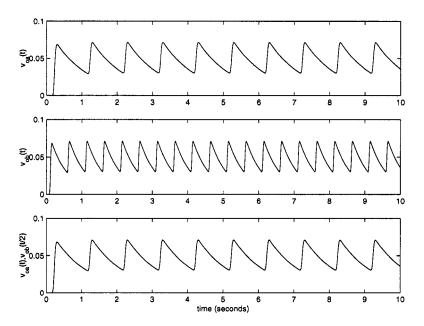

| 4.13 | Distortion in weakly nonlinear filters.                      | 87 |

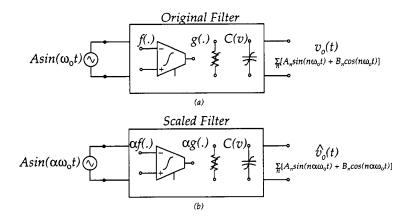

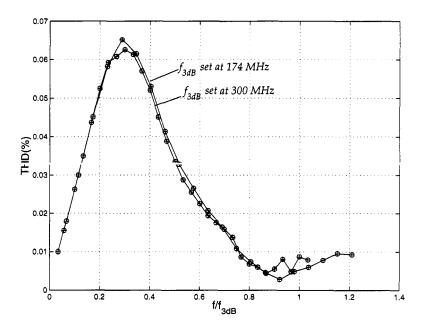

| 4.14 | Distortion simulations of a scaled Butterworth               |    |

|      | filter.                                                      | 88 |

| 4.15 | Distortion simulations of a scaled Butterworth               |    |

|      | filter, plotted with the x-axis normalized to                |    |

|      | bandwidth.                                                   | 89 |

| 4.16 | A constant-conductance scaled integrator.                    | 91 |

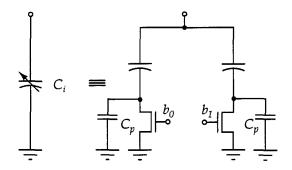

| 4.17 | A digitally tuned variable capacitor.                        | 91 |

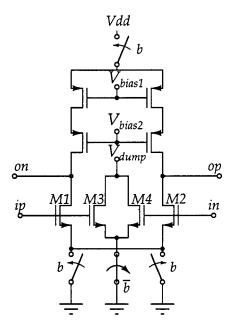

| 4.18 | A unit transconductance element.                             | 92 |

| 4.19 | The small-signal equivalent circuit of the transconductor of Figure 4.18 under differential excitation, for the cases (a) $b = 1$ and (b) $b = 0$ |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | (where $b$ denotes the state of the corresponding                                                                                                 |     |

|      | switches in Figure 4.18).                                                                                                                         | 93  |

| 4.20 | Parallel connection of two unit transconductors.                                                                                                  | 94  |

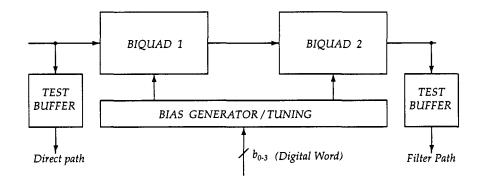

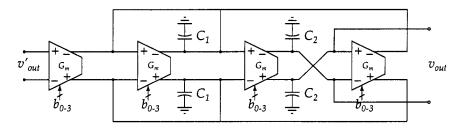

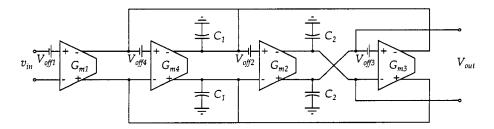

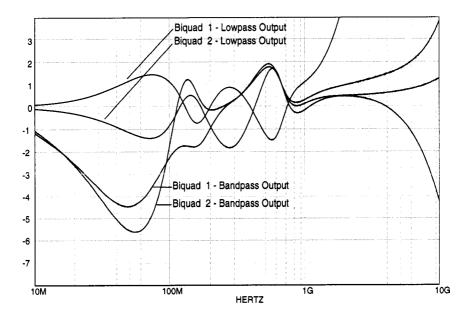

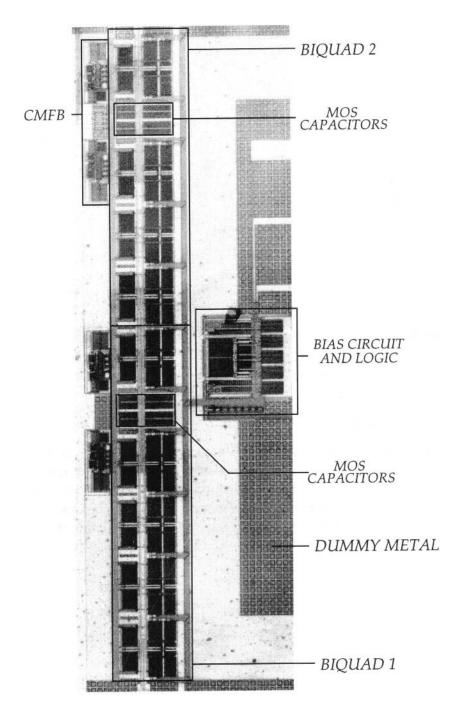

| 5.1  | Block diagram of the test chip.                                                                                                                   | 96  |

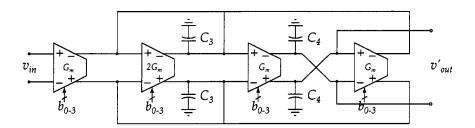

| 5.2  | Biquad 1 used in the realization of the fourth                                                                                                    |     |

|      | order Butterworth filter prototype.                                                                                                               | 97  |

| 5.3  | Biquad 2 used in the realization of the fourth                                                                                                    |     |

|      | order Butterworth filter prototype.                                                                                                               | 97  |

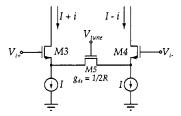

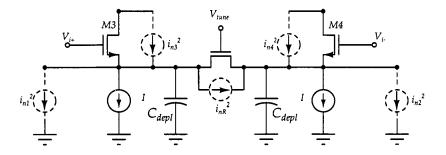

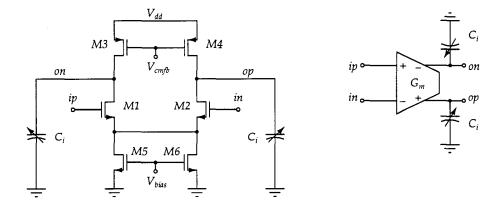

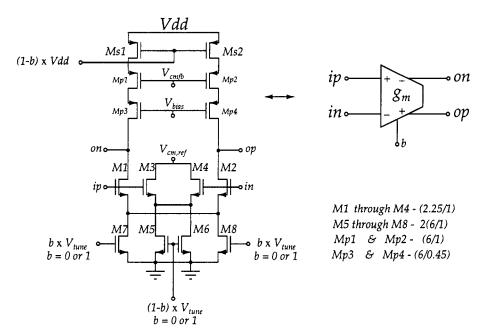

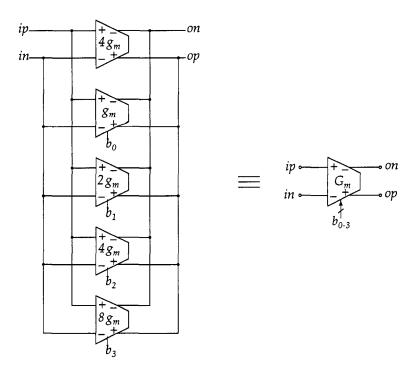

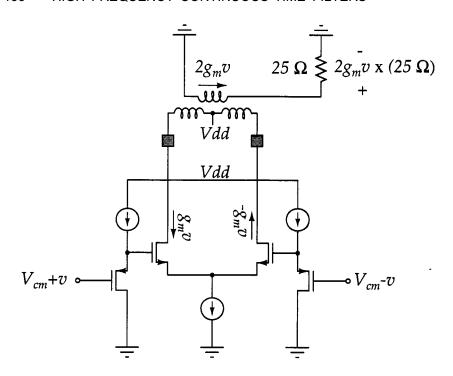

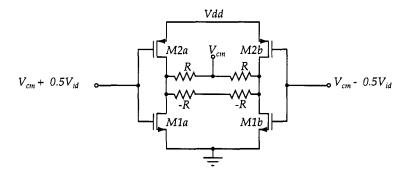

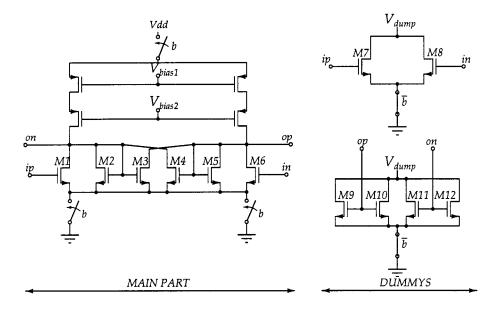

| 5.4  | Unit transconductor cell.                                                                                                                         | 97  |

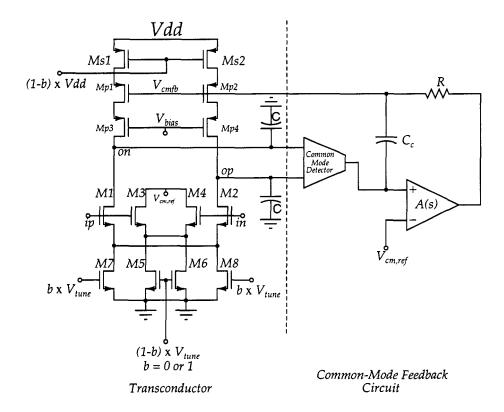

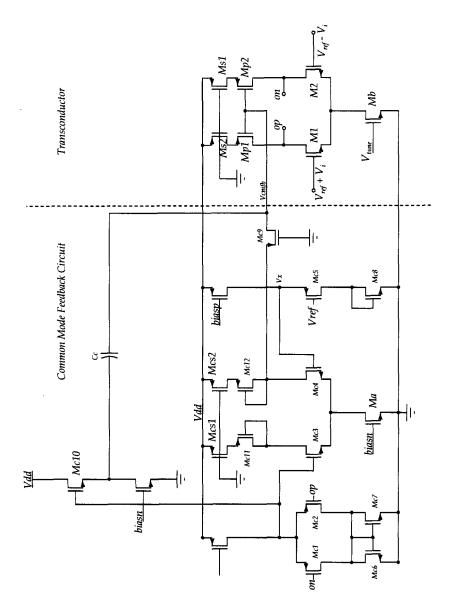

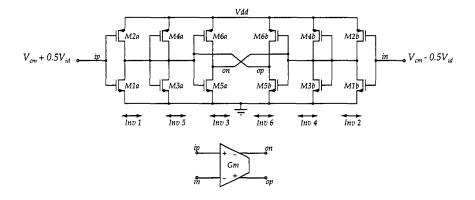

| 5.5  | Complete transconductor.                                                                                                                          | 99  |

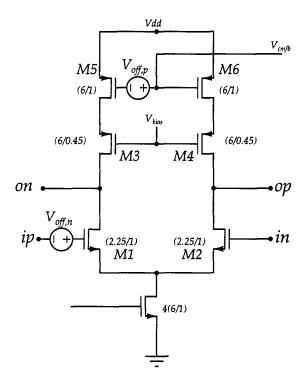

| 5.6  | Offsets in a unit transconductance cell.                                                                                                          | 102 |

| 5.7  | Block diagram of the common-mode feedback circuit.                                                                                                | 103 |

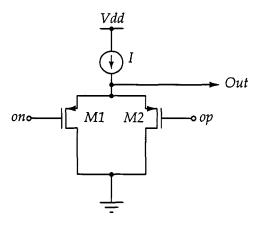

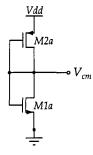

| 5.8  | A differential pair as a common-mode detector.                                                                                                    | 104 |

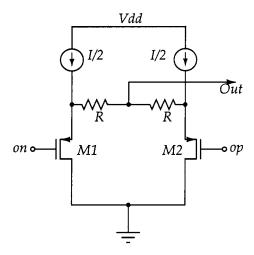

| 5.9  | A degenerated differential pair as a common-                                                                                                      |     |

|      | mode detector.                                                                                                                                    | 105 |

| 5.10 | Preliminary design of the CMFB loop.                                                                                                              | 106 |

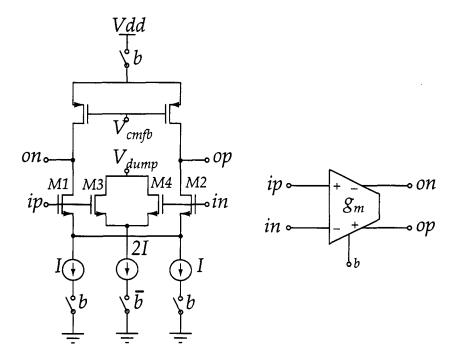

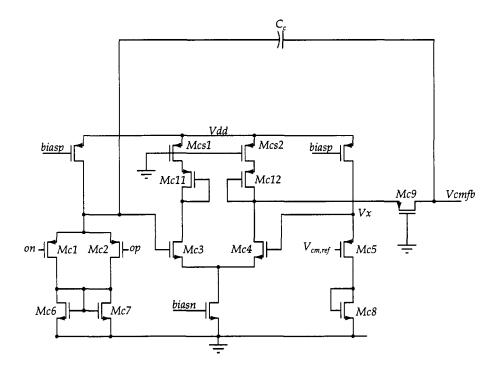

| 5.11 | Final CMFB loop.                                                                                                                                  | 107 |

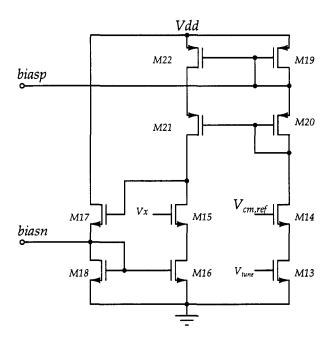

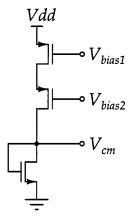

| 5.12 | Schematic of the bias generation circuit for the CMFB loops.                                                                                      | 108 |

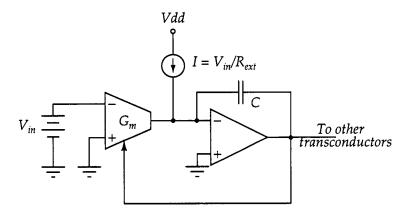

| 5.13 | Conceptual schematic of a conventional resistor-                                                                                                  |     |

|      | servo loop.                                                                                                                                       | 110 |

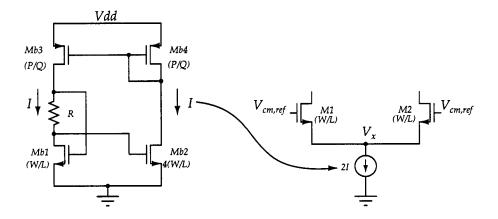

| 5.14 | Basic fixed transconductance bias circuit.                                                                                                        | 110 |

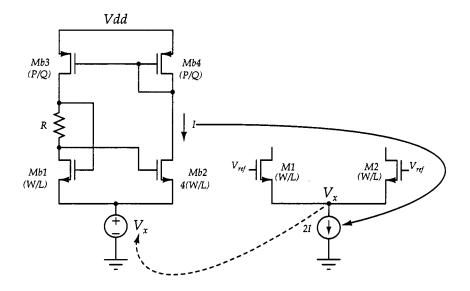

| 5.15 | Deriving an improved fixed transconductance bias circuit.                                                                                         | 112 |

| 5.16 | Scheme with reduced sensitivity to the output                                                                                                     |     |

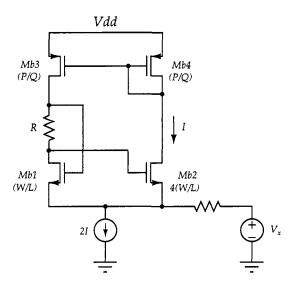

|      | resistance of $V_x$ in Figure 5.15.                                                                                                               | 113 |

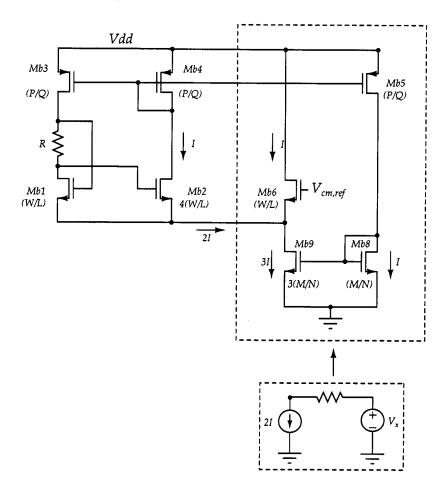

| 5.17 | Circuit implementation of the scheme of Figure 5.16.                                                                                              | 114 |

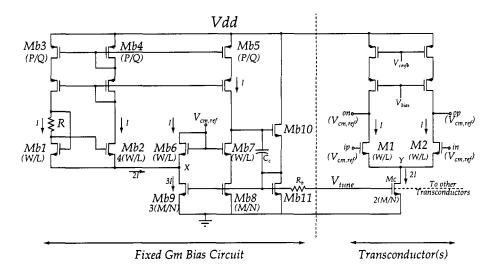

| 5.18 | Complete "fixed transconductance bias" circuit,                                                                                                   |     |

|      | shown along with a transconductor used in the filter.                                                                                             | 115 |

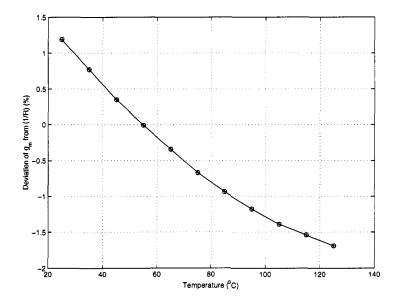

| 5.19 | Percent $g_m$ variation of the differential pair with                                                                                             |     |

|      | temperature.                                                                                                                                      | 115 |

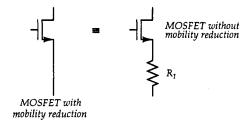

| 5.20 | Equivalent representation of mobility reduction.                                                                                                  | 116 |

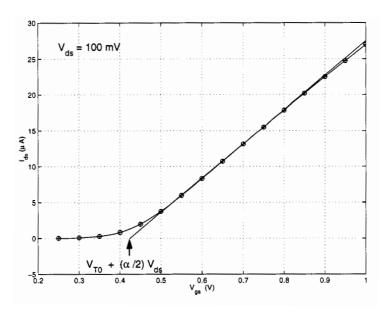

| 5.21 | $I_D$ as a function of $V_{GS}$ .                                                                                                                 | 117 |

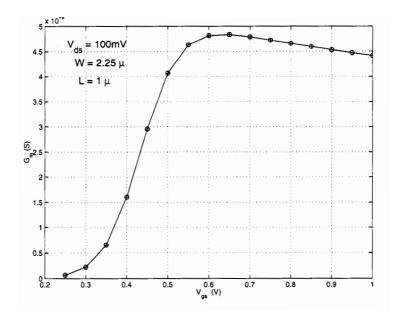

| 5.22 | $g_m$ as a function of $V_{GS}$ .                                                                                                                 | 117 |

#### HIGH FREQUENCY CONTINUOUS TIME FILTERS

xiv

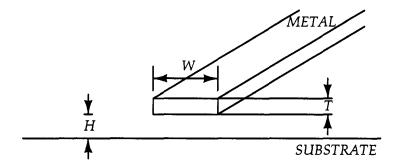

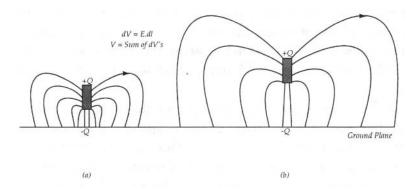

| Cross section of an interconnect line.               | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Comparing the capacitance of a thin interconnect     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| line for two different heights over a ground plane.  | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

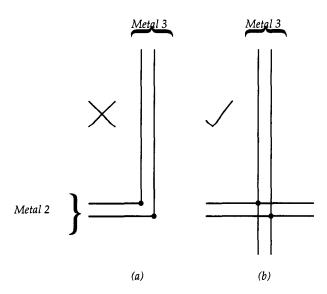

| An inherently balanced interconnect technique.       | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

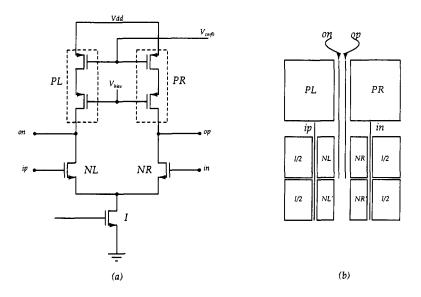

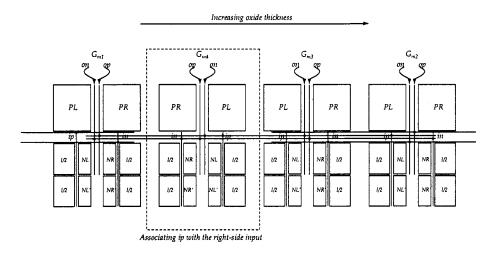

| Schematic and layout of the transconductor used      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| in the filter.                                       | 121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Two transconductor layout representations, and       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| their equivalent circuits in the presence of an      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| oxide gradient.                                      | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Schematic of a biquadratic section.                  | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Layout of a biquadratic section tolerant to small    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| oxide gradients.                                     | 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

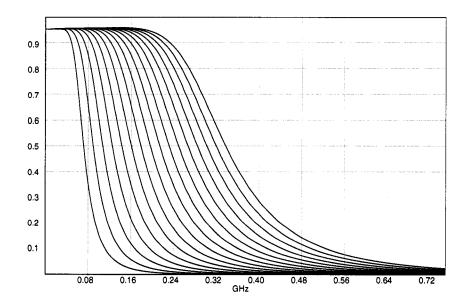

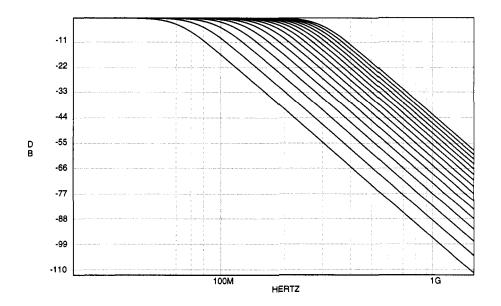

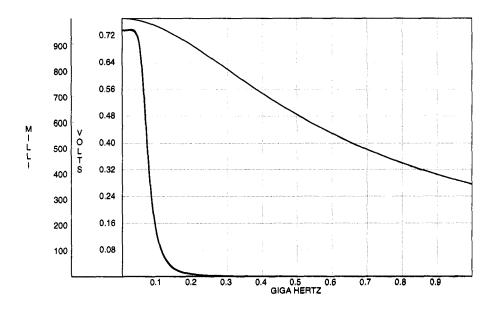

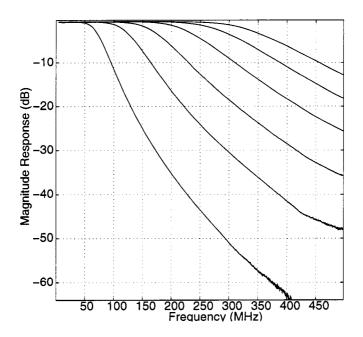

| Frequency response as a function of program-         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ming word – linear scale.                            | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

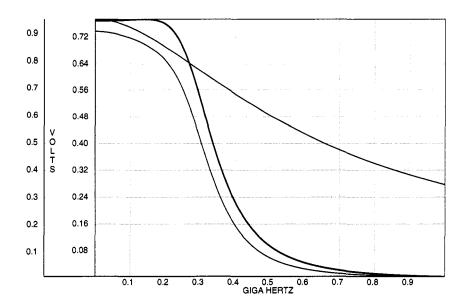

| Frequency response as a function of program-         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ming word – logarithmic scale.                       | 126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

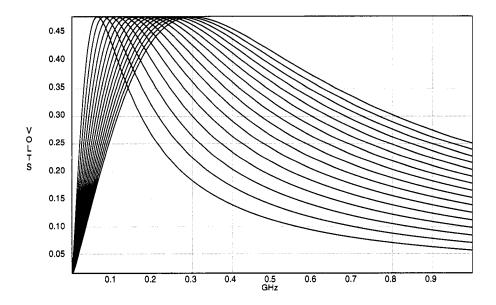

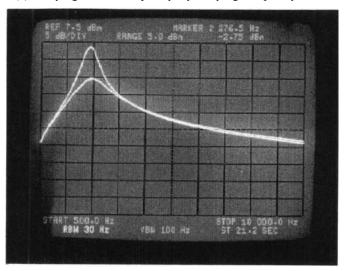

| Bandpass output of Biquad 1 as a function of         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| programming word.                                    | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

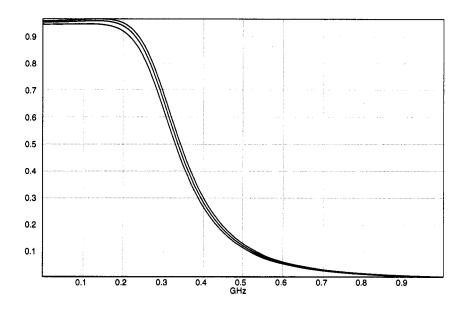

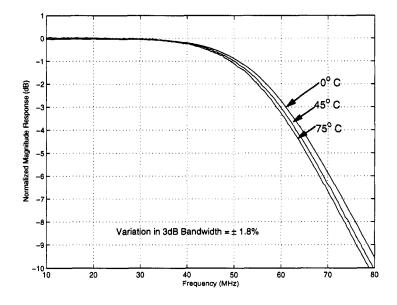

| Filter response for temperature values of            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 25, 65 and 125 °C.                                   | 128                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Balance in the filter layout.                        | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

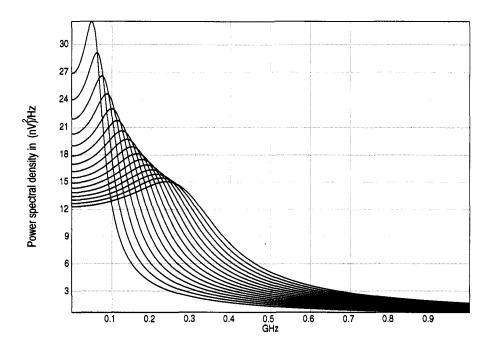

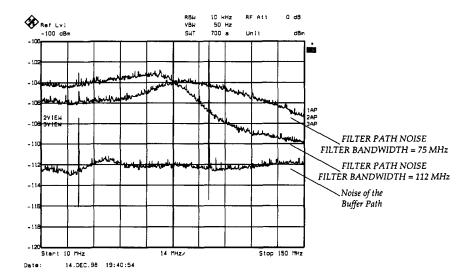

| Output noise power spectral density plots as the     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| frequency control word is stepped from 0000          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| thru 1111.                                           | 130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

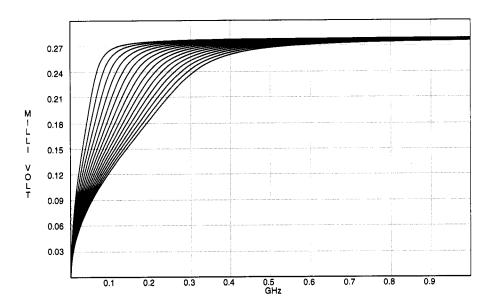

| Integrated output noise as the frequency control     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| word is stepped from 0000 thru 1111.                 | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

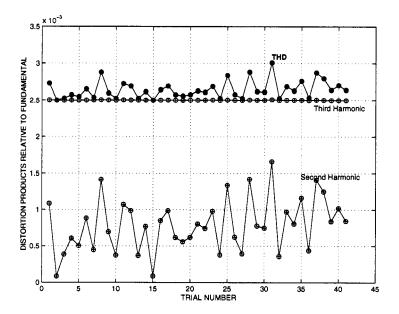

| Results of Monte Carlo simulations of the filter     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| with random offsets. The largest THD is 0.3%.        | 132                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

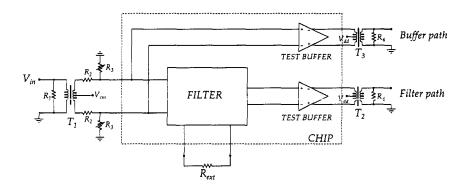

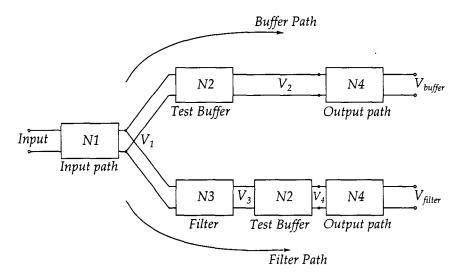

| Simplified schematic of test setup.                  | 133                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

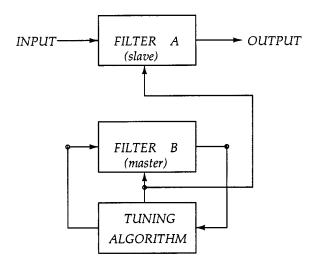

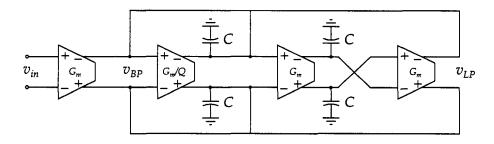

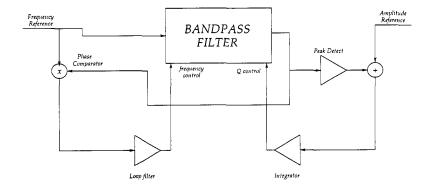

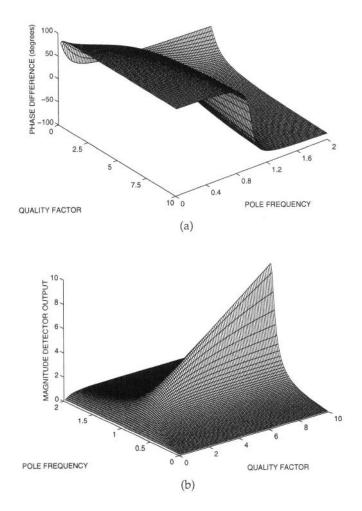

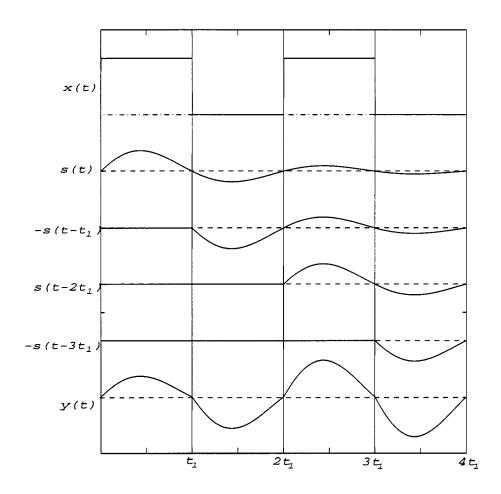

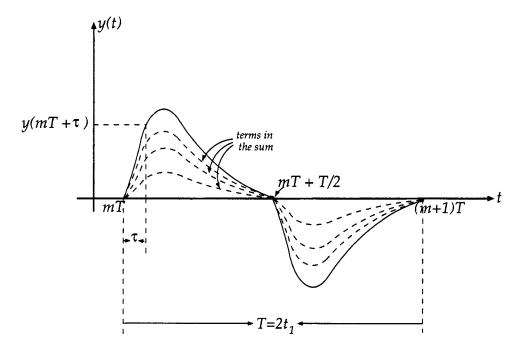

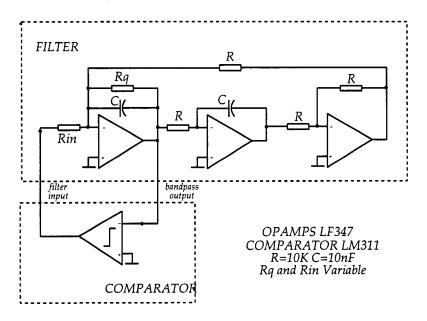

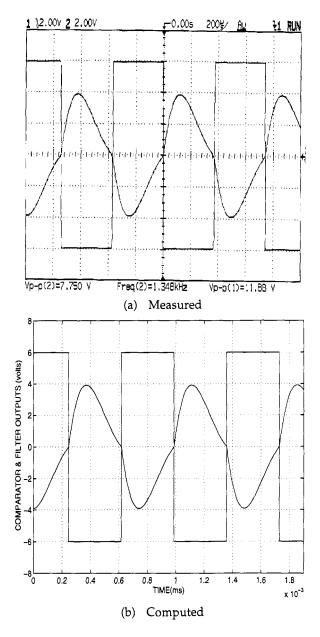

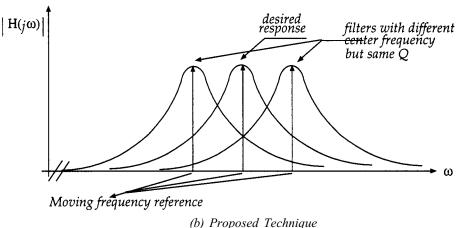

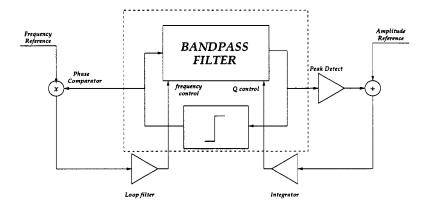

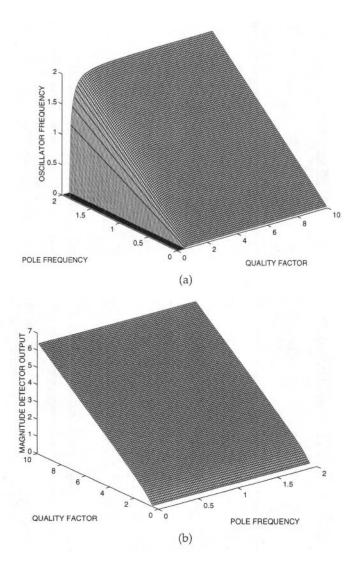

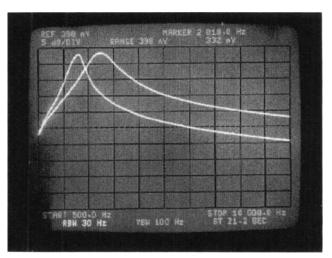

| Twoport representation of the test setup.            | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |