Fei Yuan

# CMOS Active Inductors and Transformers

Principle, Implementation, and Applications

# CMOS Active Inductors and Transformers

Principle, Implementation, and Applications

# Fei Yuan

# CMOS Active Inductors and Transformers

Principle, Implementation, and Applications

Fei Yuan

Department of Electrical and Computer Engineering

Ryerson University

Toronto, Ontario, Canada

ISBN 978-0-387-76477-1 e-ISBN 978-0-387-76479-5

Library of Congress Control Number: 2008925091

#### © 2008 Springer Science+Business Media, LLC

All rights reserved. This work may not be translated or copied in whole or in part without the written permission of the publisher (Springer Science+Business Media, LLC, 233 Spring Street, New York, NY 10013, USA), except for brief excerpts in connection with reviews or scholarly analysis. Use in connection with any form of information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now know or hereafter developed is forbidden. The use in this publication of trade names, trademarks, service marks and similar terms, even if they are not identified as such, is not to be taken as an expression of opinion as to whether or not they are subject to proprietary rights.

Printed on acid-free paper.

9 8 7 6 5 4 3 2 1

springer.com

| This book is dedicated to<br>Jing |

|-----------------------------------|

|                                   |

|                                   |

|                                   |

|                                   |

#### **Preface**

CMOS spiral inductors have found a broad range of applications in high-speed analog signal processing and data communications. These applications include bandwidth enhancement, delay reduction, impedance matching, frequency selection, distributed amplifiers, RF phase shifters, low-noise amplifiers, and voltage-controlled oscillators, to name a few. The effectiveness of these inductors, however, is affected by a number of limitations intrinsic to the spiral layout of the inductors. These limitations include a low quality factor, a low self-resonant frequency, a small and non-tunable inductance, and the need for a prohibitively large silicon area. The use of CMOS spiral transformers in RF applications such as low-noise amplifiers, power amplifiers, and LC oscillators has emerged recently. These transformers are constructed by coupling two spiral inductors via a magnetic link. They offer the advantages of a reduced silicon consumption and increased inductances. The limitations of spiral inductors, however, are inherited by spiral transformers.

Inductors and transformers synthesized using active devices, known as active inductors and transformers, offer a number of unique advantages over their spiral counterparts including virtually no chip area requirement, large and tunable inductances with large inductance tuning ranges, large and tunable quality factors, high self-resonant frequencies, and full compatibility with digital oriented CMOS technologies. Active inductors and transformers have found increasing applications in high-speed analog signal processing and data communications where spiral inductors and transformers are usually employed. As compared with spiral inductors and transformers, the applications of CMOS active inductors and transformers are affected by a number of limitations intrinsic to synthesized devices. These limitations include a small dynamic range, poor noise performance, a high level of power consumption, and a high sensitivity to supply voltage fluctuation and process variation.

This book provides a comprehensive treatment of the principle, topologies, and characteristics of CMOS active inductors and transformers, and an in-depth

examination of their emerging applications in high-speed analog signal processing and data communications. The materials presented in the book are based on the work of many researchers who contributed to the theory and design of CMOS active inductors and transformers. In recognition of their contributions, the active inductors and transformers presented in this text are named in the names of the researchers. For active inductors and transformers developed by more than two researchers, although due to the space constraint, only the name of the first author of the work is used to name the active inductors and transformers, the contributions of all other authors are equally recognized. This is reflected by the presentation of the full authorship of the work in the *References* of the book. The same approach is followed in the presentation of CMOS active inductor/transformer bandpass filters, oscillators, and other sub-systems.

This book consists of two parts: Part I - Principle and Implementation of CMOS Active Inductors and Transformers, and Part II -Applications of CMOS Active Inductors and Transformers.

Part I of the book deals with the topologies, characteristics and implementation of CMOS active inductors and transformers. This part consists of three chapters.

Chapter 1 starts with a brief investigation into why inductive characteristics are critically needed in high-speed applications. This is demonstrated with the applications of inductors and transformers in LC oscillators, impedance matching networks, RF phase shifters, RF power dividers, frequency selection networks, in particular, RF bandpass filters, and low-noise amplifiers. A detailed examination of the design constraints of monolithic inductors and transformers is followed. The advantages and design challenges of CMOS active inductors and transformers are examined in detail.

Chapter 2 presents the principles of the synthesis of inductors using gyrator-C networks. Both lossless and lossy single-ended and fully differential gyrator-C active inductors are studied. The important figure-of-merits that quantify the performance of active inductors including frequency operation range, inductance tunability, quality factor, noise, linearity, stability, supply voltage sensitivity, parameter sensitivity, signal sensitivity, and power consumption are examined in detailed. The details of the CMOS implementation and analysis of single-ended and fully differential active inductors are presented. The circuit implementation and characteristics of published CMOS active inductors are examined in detail.

Chapter 3 focuses on the principles of the synthesis of CMOS active transformers. Both lossless and lossy gyrator-C active transformers are studied. The characterization of active transformers including stability, frequency operation range, the tunability of self and mutual inductances, turn ratios, coupling

*PREFACE* ix

factors, voltage and current transfer characteristics, impedance transformation, noise, quality factors, linearity, supply voltage sensitivity, parameter sensitivity, and power consumption is examined in detail. The CMOS implementation of several published CMOS active transformers is presented and their characteristics are analyzed.

Part II of the book focuses upon the emerging applications of CMOS active inductors and transformers in high-speed analog signal processing and data communications. This part consists of four chapters.

Chapter 4 investigates the implementation and characteristics of RF bandpass filters using CMOS active inductors. The chapter starts with a detailed investigation of the characterization of bandpass filters. Bandwidth, 1-dB compression points, third-order intercept points, noise figure, noise bandwidth, spurious-free-dynamic range, frequency selectivity, and passband center frequency tuning are examined. It is followed by a detailed examination of the configurations of RF bandpass filters with active inductors. Wu bandpass filters, Thanachayanont bandpass filters, Xiao-Schaumann bandpass filters, Thanachayanont-Payne bandpass filter, and Weng-Kuo bandpass filters are studied and their performance is compared.

Chapter 5 looks into the realization of the building blocks of high-speed transceivers using CMOS active inductors and transformers. The use of CMOS active inductors in low-noise amplifiers, optical front-ends, RF phase shifters, RF modulators, RF power dividers, and Gb/s serial-link transceivers is examined in detail.

Chapter 6 starts with a brief review of the fundamentals of electrical oscillators. Both ring and LC oscillators are investigated. The use of CMOS active inductors in improving the performance of ring oscillators is investigated. The presentation continues with a close examination of the use of CMOS active inductors in LC oscillators. A special attention is given to the comparison of the phase noise of these oscillators. LC oscillators and LC quadrature oscillators using CMOS active transformers are also studied.

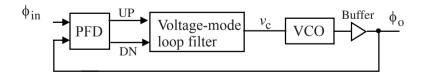

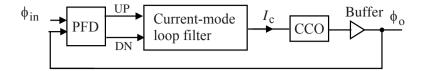

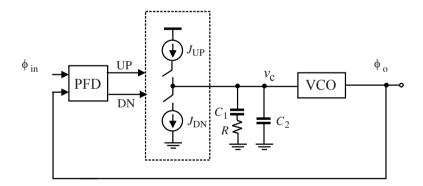

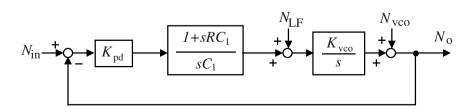

Chapter 7 presents the theory of current-mode phase-locked loops (PLLs) and examines the intrinsic differences between voltage-mode and current-mode PLLs. The chapter starts with an in-depth study of the configurations and characteristics of voltage-mode PLLs. Both type I and type II voltage-mode PLLs are studied. It then moves on to investigate current-mode PLLs with CMOS active inductors and transformers. The loop dynamics of these PLLs are investigated in detailed. Three design examples are utilized to demonstrate the performance of current-mode PLLs with active inductors and active transformers.

The materials of the book are presented with an emphasis on both the evolution of each class of circuits and a close comparison of their advantages and limitations. The examples given in the book were implemented in TSMC-

$0.18\mu m$  1.8V and UMC- $0.13\mu m$  1.2V CMOS technologies, and analyzed using SpectreRF from Cadence Design Systems with BSIM3v3RF device models that account for both the parasitics and high-order effects of MOS devices at high frequencies. Readers are assumed to be familiar with the fundamentals of electrical networks, microelectronic devices and circuits, signals and systems, and basic RF circuits.

This book is the first text that provides a comprehensive treatment of the principle, implementation, and applications of CMOS active inductors and transformers. It is a valuable resource for senior undergraduate / graduate students and an important reference for IC design engineers.

Although an immense amount of effort has been made in preparation of the manuscript, flaws and errors will still exist due to erring human nature. Suggestions and corrections will be gratefully appreciated by the author.

Fei Yuan

December 31, 2007

# Acknowledgments

I would like to take this opportunity to express my sincere gratitude to the Natural Science and Engineering Research Council of Canada, Ryerson University, and CMC Microsystems Inc., Kingston, Ontario, Canada, for their financial and technical supports to our research on integrated circuits and systems. The support from the Department of Electrical and Computer Engineering of Ryerson University where I introduced and taught graduate courses EE8501 (CMOS analog integrated circuits), EE8502 (VLSI systems), and EE8503 (VLSI circuits for data communications) is gratefully acknowledged. I am also grateful to Ryerson University for awarding me the Ryerson Research Chair with both a much needed research grant and a reduced teaching load in 2005-2007 during which much of the research work on active inductors and transformers was carried out. The sabbatical leave from September 2007 to August 2008 provided me with the critically needed time and freedom to complete the manuscript of the monograph.

Special thanks go to my current graduate students Adrian Tang and Dominic DiClemente, and my former graduate students Jean Jiang (Intel Corp., Folsom, CA.), Alec Li (Micron Technologies, Bois, Idaho), and Tao Wang (McMaster University, Hamilton, Canada) for fruitful and productive discussion in our weekly research meetings where many of the original ideas on CMOS active inductors, CMOS active transformers, and their applications in wireless communications and high-speed data communications emerged. Mr. Jason Naughton, our System Administrator, deserves a special thank-you for his prompt response to our random calls on computer/CAD-tool related issues and for keeping CAD tools up-to-date and running all the time.

The editorial staff of Springer, especially Mr. Alex Greene, the Editorial Director of Engineering, have been warmly supportive from the submission of the initial proposal of the book to the completion of the manuscript. Ms. Jennifer Mirski, the Editorial Assistant of Engineering at Springer, deserves a special thank-you for her warm and professional assistance in arranging the

review of the submitted manuscript, the design of the lovely cover of the book, and the coordination of the publishing of the book.

Finally and most importantly, this book could not have been possible without the support of my family. I am indebted to my wife Jing for her love, patient, and understanding throughout the project. I also want to thank our daughter and son, Michelle and Jonathan, for the joy that they have brought to our life, and for their forbearance of my bad temper due to the stress of writing.

# **Contents**

| De  | edicat | ion       |                                                         | V      |

|-----|--------|-----------|---------------------------------------------------------|--------|

| Pro | eface  |           |                                                         | vii    |

| Ac  | knov   | vledgme   | ents                                                    | xi     |

| _   |        |           |                                                         |        |

| Pa  | rt I   | Principle | e and Implementation of CMOS Active Inductors & Transfo | ormers |

| 1.  | INT    | RODU      | CTION                                                   | 3      |

|     | 1.1    | Induct    | tive Characteristics in High-Speed Applications         | 3      |

|     |        | 1.1.1     | LC Oscillators                                          | 4      |

|     |        | 1.1.2     | Bandwidth Improvement                                   | 4      |

|     |        | 1.1.3     | Impedance Matching                                      | 7      |

|     |        | 1.1.4     | Phase Shifting                                          | 9      |

|     |        | 1.1.5     | Frequency Selection                                     | 10     |

|     |        | 1.1.6     | C                                                       | 10     |

|     |        | 1.1.7     | Power Dividers                                          | 11     |

|     | 1.2    | Spiral    | Inductors and Transformers                              | 11     |

|     |        | 1.2.1     | Planar Spiral Inductors                                 | 12     |

|     |        | 1.2.2     | Stacked Spiral Inductors                                | 12     |

|     |        | 1.2.3     | Spiral Transformers                                     | 13     |

|     |        | 1.2.4     | Characteristics of Spiral Inductors and Transformers    | 14     |

|     | 1.3    | Active    | e Inductors and Transformers                            | 17     |

|     | 1.4    | Chapte    | er Summary                                              | 20     |

| 2.  | CM     | OS AC     | TIVE INDUCTORS                                          | 21     |

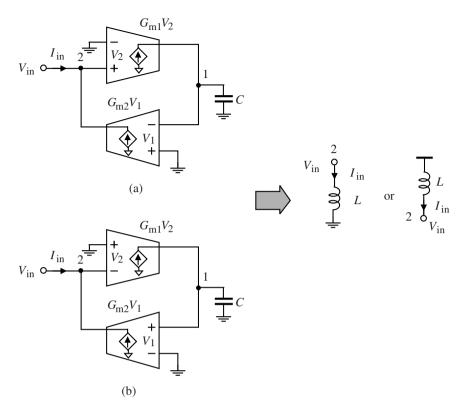

|     | 2.1    | Princi    | ples of Gyrator-C Active Inductors                      | 21     |

|     |        | 2.1.1     | Lossless Single-Ended Gyrator-C Active Inductors        | 21     |

|     | 2.1.2  | Lossless Floating Gyrator-C Active Inductors         | 22 |

|-----|--------|------------------------------------------------------|----|

|     | 2.1.3  | Lossy Single-Ended Gyrator-C Active Inductors        | 25 |

|     | 2.1.4  | Lossy Floating Gyrator-C Active Inductors            | 28 |

| 2.2 | Charac | eterization of Active Inductors                      | 29 |

|     | 2.2.1  | Frequency Range                                      | 29 |

|     | 2.2.2  | Inductance Tunability                                | 30 |

|     | 2.2.3  | Quality Factor                                       | 35 |

|     | 2.2.4  | Noise                                                | 44 |

|     | 2.2.5  | Linearity                                            | 50 |

|     | 2.2.6  | Stability                                            | 51 |

|     | 2.2.7  | Supply Voltage Sensitivity                           | 52 |

|     | 2.2.8  | Parameter Sensitivity                                | 53 |

|     | 2.2.9  | Signal Sensitivity                                   | 55 |

|     | 2.2.10 | Power Consumption                                    | 55 |

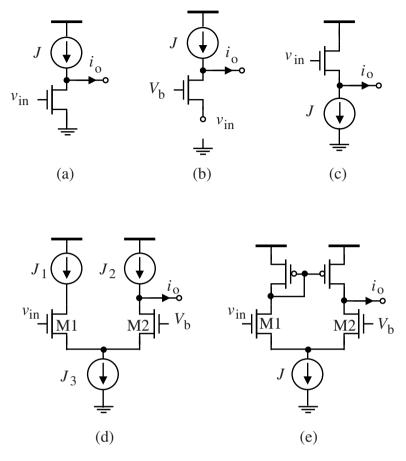

| 2.3 | Implen | nentation of Single-Ended Active Inductors           | 55 |

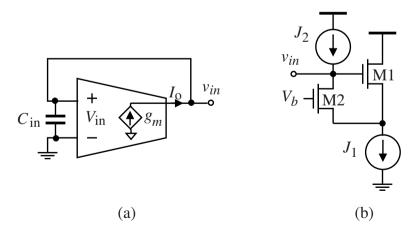

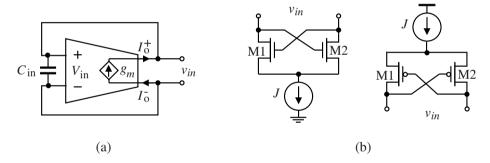

|     | 2.3.1  | Basic Gyrator-C Active Inductors                     | 56 |

|     | 2.3.2  | Wu Current-Reuse Active Inductors                    | 60 |

|     | 2.3.3  | Lin-Payne Active Inductors                           | 62 |

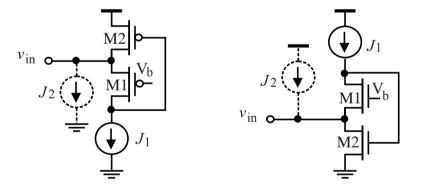

|     | 2.3.4  | Ngow-Thanachayanont Active Inductors                 | 62 |

|     | 2.3.5  | Hara Active Inductors                                | 62 |

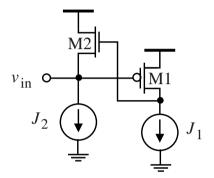

|     | 2.3.6  | Wu Folded Active Inductors                           | 65 |

|     | 2.3.7  | Karsilayan-Schaumann Active Inductors                | 68 |

|     | 2.3.8  | Yodprasit-Ngarmnil Active Inductors                  | 72 |

|     | 2.3.9  | Uyanik-Tarim Active Inductor                         | 74 |

|     | 2.3.10 | Carreto-Castro Active Inductors                      | 75 |

|     | 2.3.11 | Thanachayanont-Payne Cascode Active Inductors        | 77 |

|     | 2.3.12 | Weng-Kuo Cascode Active Inductors                    | 82 |

|     | 2.3.13 | Manetakis Regulated Cascode Active Inductors         | 82 |

|     | 2.3.14 | Hsiao Feedback Resistance Cascode Active Inductors   | 84 |

|     | 2.3.15 | Abdalla Feedback Resistance Active Inductors         | 85 |

|     | 2.3.16 | Nair Active Inductors                                | 86 |

|     | 2.3.17 | Active Inductors with Low Supply-Voltage Sensitivity | 87 |

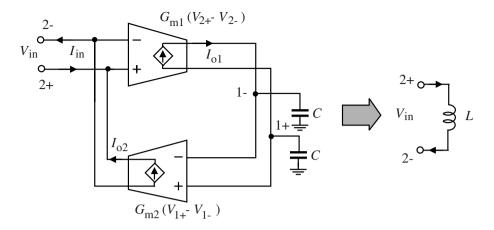

| 2.4 | Implen | nentation of Differential Active Inductors           | 89 |

|     | 2.4.1  | Lu Floating Active Inductors                         | 89 |

|     | 2.4.2  | Grözing Floating Active Inductors                    | 89 |

|     | 2.4.3  | Thanachayanont Floating Active Inductors             | 90 |

|     | 2.4.4  | Mahmoudi-Salama Floating Active Inductors            | 91 |

|     | 2.4.5  | Feedback Resistance Floating Active Inductors        | 93 |

Contents XV

|     | 2.5   | Class A                               | AB Active Inductors                                 | 95  |  |  |

|-----|-------|---------------------------------------|-----------------------------------------------------|-----|--|--|

|     | 2.6   | Chapte                                | er Summary                                          | 98  |  |  |

| 3.  | CM    | OS ACT                                | TIVE TRANSFORMERS                                   | 101 |  |  |

|     | 3.1   | oles of Gyrator-C Active Transformers | 101                                                 |     |  |  |

|     |       | 3.1.1                                 | Lossless Single-Ended Gyrator-C Active Transformers | 102 |  |  |

|     |       | 3.1.2                                 | Lossless Floating Gyrator-C Active Transformers     | 106 |  |  |

|     |       | 3.1.3                                 | Lossy Single-Ended Gyrator-C Active Transformers    | 107 |  |  |

|     |       | 3.1.4                                 | Active Transformers With Multiple Windings          | 112 |  |  |

|     | 3.2   | Charac                                | eterization of Active Transformers                  | 116 |  |  |

|     |       | 3.2.1                                 | Stability                                           | 117 |  |  |

|     |       | 3.2.2                                 | Frequency Range                                     | 117 |  |  |

|     |       | 3.2.3                                 | Tunability of Self and Mutual Inductances           | 119 |  |  |

|     |       | 3.2.4                                 | Turn ratios                                         | 119 |  |  |

|     |       | 3.2.5                                 | Coupling Factors                                    | 120 |  |  |

|     |       | 3.2.6                                 | Voltage Transfer Characteristics                    | 120 |  |  |

|     |       | 3.2.7                                 | Current Transfer Characteristics                    | 122 |  |  |

|     |       | 3.2.8                                 | Impedance Transformation                            | 123 |  |  |

|     |       | 3.2.9                                 | Noise                                               | 125 |  |  |

|     |       | 3.2.10                                | Quality Factors                                     | 127 |  |  |

|     |       | 3.2.11                                | Linearity                                           | 129 |  |  |

|     |       | 3.2.12                                | Supply Voltage Sensitivity                          | 129 |  |  |

|     |       | 3.2.13                                | Parameter Sensitivity                               | 130 |  |  |

|     |       | 3.2.14                                | Power Consumption                                   | 131 |  |  |

|     | 3.3   | Implementation of Active Transformers |                                                     |     |  |  |

|     |       | 3.3.1                                 | Basic Active Transformers                           | 132 |  |  |

|     |       | 3.3.2                                 | Tang Active Transformers                            | 135 |  |  |

|     |       | 3.3.3                                 | Active Transformers With Low $V_{DD}$ Sensitivity   | 137 |  |  |

|     |       | 3.3.4                                 | Tang Class AB Active Transformers                   | 143 |  |  |

|     | 3.4   | Chapte                                | er summary                                          | 145 |  |  |

| Par | rt II | Applica                               | ations of CMOS Active Inductors and Transformers    |     |  |  |

| 4.  |       |                                       | ASS FILTERS WITH ACTIVE INDUCTORS                   | 149 |  |  |

| •   | 4.1   |                                       | eterization of Bandpass Filters                     | 150 |  |  |

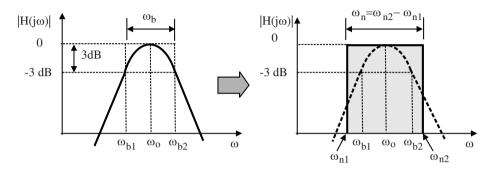

|     | т. 1  | 4.1.1                                 | Bandwidth                                           | 150 |  |  |

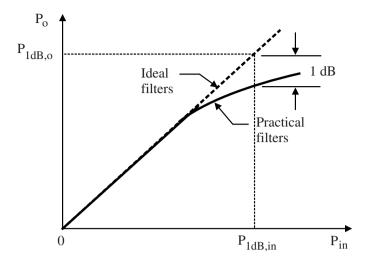

|     |       | 4.1.2                                 | 1-dB Compression Points                             | 152 |  |  |

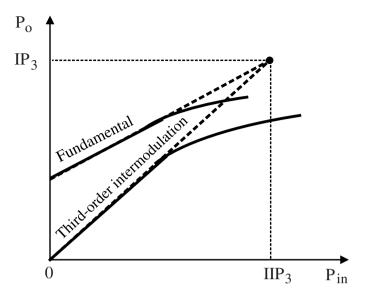

|     |       | 4.1.3                                 | Third-Order Intercept Points                        | 152 |  |  |

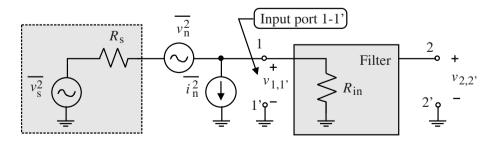

|     |       | 4.1.4                                 | Noise Figures                                       | 153 |  |  |

|     |       |                                       |                                                     |     |  |  |

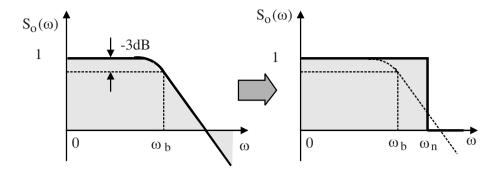

|    |     | 4.1.5  | Noise Bandwidth                                    | 156 |  |

|----|-----|--------|----------------------------------------------------|-----|--|

|    |     | 4.1.6  | Spurious-Free-Dynamic-Range                        | 158 |  |

|    |     | 4.1.7  | Frequency Selectivity and Frequency Tuning         | 158 |  |

|    | 4.2 | Config | guration of Bandpass Filters with Active Inductors | 159 |  |

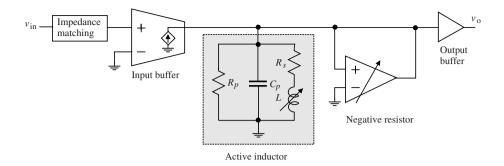

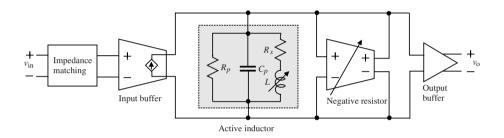

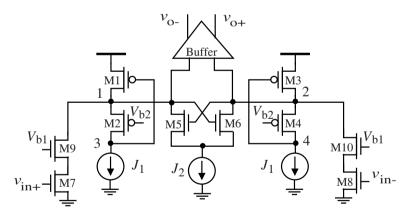

|    | 4.3 | CMOS   | S Active Inductor Bandpass Filters                 | 160 |  |

|    |     | 4.3.1  | Wu Bandpass Filters                                | 160 |  |

|    |     | 4.3.2  | Thanachayanont Bandpass Filters                    | 162 |  |

|    |     | 4.3.3  | Xiao-Schaumann Bandpass Filters                    | 163 |  |

|    |     | 4.3.4  | Thanachayanont-Payne Bandpass Filters              | 163 |  |

|    |     | 4.3.5  | Weng-Kuo Bandpass Filters                          | 165 |  |

|    |     | 4.3.6  | High-Order Active Inductor Bandpass Filters        | 165 |  |

|    | 4.4 | Chapt  | er Summary                                         | 167 |  |

| 5. |     |        | CIVERS WITH ACTIVE INDUCTORS &                     |     |  |

|    | TRA | ANSFO  | RMERS                                              | 169 |  |

|    | 5.1 | Low-N  | Noise Amplifiers                                   | 169 |  |

|    | 5.2 | Optica | al Front-Ends                                      | 171 |  |

|    |     | 5.2.1  | Säckinger-Fischer Limiting Amplifiers              | 172 |  |

|    |     | 5.2.2  | Chen-Lu Limiting Amplifiers                        | 173 |  |

|    |     | 5.2.3  | Wu Limiting Amplifiers                             | 174 |  |

|    | 5.3 | Phase  | Shifters                                           | 175 |  |

|    |     | 5.3.1  | Lu-Liao Active Inductor Phase Shifter              | 177 |  |

|    |     | 5.3.2  | Abdalla Active Inductor Phase Shifter              | 178 |  |

|    | 5.4 | Transo | ceivers for Wire-line Communications               | 178 |  |

|    |     | 5.4.1  | Current-Mode Class A Transmitters                  | 179 |  |

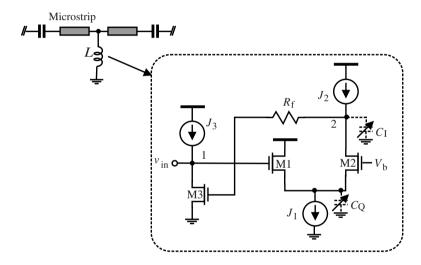

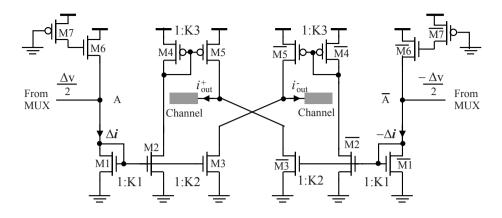

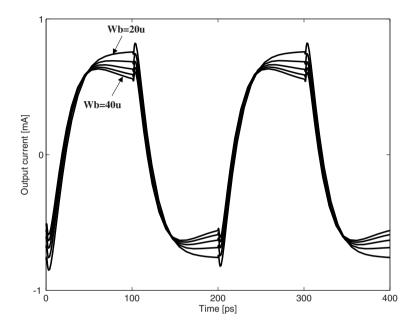

|    |     | 5.4.2  | Current-Mode Class AB Transmitters                 | 181 |  |

|    |     | 5.4.3  | Pre-Emphasis and Post-Equalization                 | 183 |  |

|    | 5.5 | Phase  | Modulators                                         | 185 |  |

|    | 5.6 | Chapt  | er summary                                         | 187 |  |

| 6. |     |        |                                                    |     |  |

|    | TRA | ANSFO  | RMERS                                              | 191 |  |

|    | 6.1 | Introd | uction                                             | 191 |  |

|    |     | 6.1.1  | LC Oscillators                                     | 192 |  |

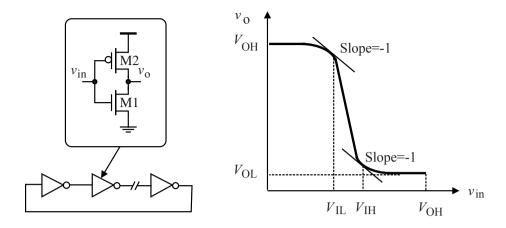

|    |     | 6.1.2  | Ring Oscillators                                   | 193 |  |

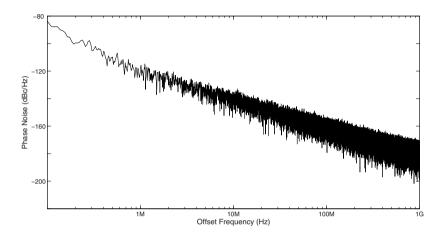

|    |     | 6.1.3  | Phase Noise of Oscillators                         | 195 |  |

|    | 6.2 | Ring ( | Oscillators With Active Inductors                  | 199 |  |

|    |     | 6.2.1  | Source-Coupled Ring VCOs                           | 200 |  |

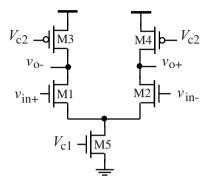

|    |     | 6.2.2  | Cross-Coupled Ring VCOs                            | 202 |  |

| Contents | 3/3/11 |

|----------|--------|

| Contents | XV11   |

|     |       | 6.2.3  | Park-Kim Ring VCOs                                     | 205 |

|-----|-------|--------|--------------------------------------------------------|-----|

|     | 6.3   | LC Os  | cillators With Active Inductors                        | 211 |

|     |       | 6.3.1  | LC VCOs with Wu Current-Reuse Active Inductors         | 214 |

|     |       | 6.3.2  | LC VCOs with Lin-Payne Active Inductors                | 215 |

|     |       | 6.3.3  | LC VCOs with Grözing Active Inductors                  | 215 |

|     |       | 6.3.4  | LC VCOs with Karsilayan-Schaunann Active Inductors 216 |     |

|     |       | 6.3.5  | LC VCOs with Lu Active Inductors                       | 218 |

|     | 6.4   | LC VC  | COs With Active Transformers                           | 219 |

|     | 6.5   | Quadr  | ature LC VCOs With Active Inductors                    | 222 |

|     | 6.6   | Quadr  | ature LC VCOs with Active Transformers                 | 224 |

|     | 6.7   | Perfor | mance Comparison of Active LC VCOs                     | 227 |

|     | 6.8   | Chapte | er summary                                             | 228 |

| 7.  | CUF   | RRENT  | -MODE PHASE-LOCKED LOOPS WITH ACTIVE                   |     |

|     | IND   | UCTO   | RS & TRANSFORMERS                                      | 231 |

|     | 7.1   | Funda  | mentals of PLLs                                        | 232 |

|     |       | 7.1.1  | Classifications                                        | 232 |

|     |       | 7.1.2  | Loop Dynamics of Voltage-Mode PLLs                     | 233 |

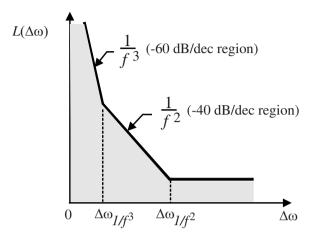

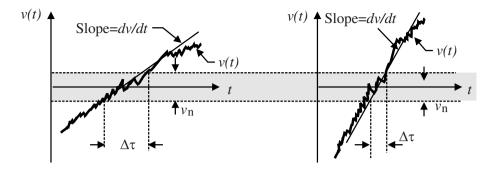

|     |       | 7.1.3  | Phase Noise of Voltage-Mode PLLs                       | 238 |

|     |       | 7.1.4  | Simulation of Phase Noise of PLLs                      | 240 |

|     | 7.2   |        | nt-Mode PLLs with Active Inductors                     | 241 |

|     |       | 7.2.1  | Current-Mode Loop Filter with Active Inductors         | 241 |

|     |       | 7.2.2  | Loop Dynamics of Type I Current-Mode PLLs              | 244 |

|     |       | 7.2.3  | Loop Dynamics of Type II Current-Mode PLLs             | 247 |

|     |       | 7.2.4  | Phase Noise of Current-Mode PLLs                       | 251 |

|     |       | 7.2.5  | Design Examples                                        | 253 |

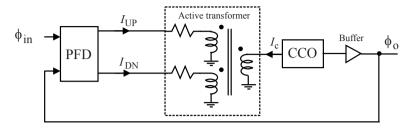

|     | 7.3   | Currer | nt-Mode PLLs with Active Transformers                  | 260 |

|     |       | 7.3.1  | Current-Mode Loop Filters with Active Transformers     | 261 |

|     |       | 7.3.2  | Loop Dynamics of Current-Mode PLLs                     | 264 |

|     |       | 7.3.3  | Phase Noise of Current-Mode PLLs                       | 268 |

|     |       | 7.3.4  | Design Example                                         | 269 |

|     | 7.4   | Chapte | er Summary                                             | 271 |

| Re  | feren | ces    |                                                        | 275 |

| Inc | lex   |        |                                                        | 287 |

# Chapter 1

#### INTRODUCTION

CMOS spiral inductors and transformers have found a broad range of applications in high-speed analog signal processing including impedance matching and gain-boosting in wireless transceivers, bandwidth improvement in broadband data communications over wire and optical channels, oscillators and modulators, RF bandpass filters, RF phase shifters, RF power dividers, and coupling of high-frequency signals, to name a few. Traditionally, passive inductors and transformers are off-chip discrete components. The need for off-chip communications with these passive components severely limits the bandwidth, reduces the reliability, and increases the cost of systems. Since early 1990s, a significant effort has been made to fabricate inductors and transformers on a silicon substrate such that an entire wireless transceiver can be integrated on a single substrate monolithically. In the mean time, the need for a large silicon area to fabricate spiral inductors and transformers has also sparked a great interest in and an intensive research on the synthesis of inductors and transformers using active devices, aiming at minimizing the silicon consumption subsequently the fabrication cost and improving the performance.

This chapter looks into the characteristics of spiral and active inductors and transformers, both their advantages and limitations, and the impact of these characteristics on the applications of these devices. Section 1.1 demonstrates the critical need for an inductive characteristic in high-speed applications. The characteristics of spiral inductors and transformers are examined in Section 1.2. In Section 1.3, we investigate the pros and cons of active inductors and transformers. The chapter is summarized in Section 1.4.

# 1.1 Inductive Characteristics in High-Speed Applications

Inductive characteristics are critically needed in high-speed applications to improve the performance of the systems, such as improving bandwidth and

boosting gain, and to perform specific tasks, such as impedance matching and frequency selection. These applications include LC tank oscillators, bandwidth enhancement in broadband communications, impedance matching in narrowband communications, phase shifting for RF antennas and radars, RF power dividers, frequency selection, in particular, RF bandpass filters, RF power amplifiers, and gain boosting of RF low-noise amplifiers.

#### 1.1.1 LC Oscillators

One of the key applications of inductors and transformers in wireless communications is the construction of LC oscillators. As compared with ring oscillators, LC oscillators with spiral inductors or transformers offer the key advantage of a low level of phase noise. They are widely used in wireless communication systems where a stringent constraint on the phase noise of oscillators exists. Frequency tuning of LC oscillators with spiral inductors or transformers is typically done by varying the capacitance of the LC tanks as the inductance tuning of spiral inductors or transformers in a monolithic integration is rather difficult. These variable capacitors are usually realized using MOS varactors and offer a relatively small capacitance tuning range, subsequently a small frequency tuning range of the oscillators. Because the need for the frequency tuning range in narrow-band wireless applications is much relaxed as compared with that for clock and data recovery in broadband data communications over wire lines or optical channels, the capacitance-based frequency tuning usually provides an adequate frequency tuning range. Table 1.1 compiles some of the recently published work on LC oscillators with either spiral inductors or spiral transformers.

# 1.1.2 Bandwidth Improvement

Bandwidth is of a critical concern in broadband communications, such as optical front-ends and data communications over wire links. The bandwidth of a circuit is set by the time constant of the critical node, i.e. the node that has the largest time constant, of the circuit. Three approaches, namely *inductive peaking*, *current-mode signaling*, and *distributed amplification*, are widely used to improve the bandwidth of circuits.

■ *Inductive peaking* - The idea is to place an inductor at the node where a large nodal capacitance exists such that the first-order RC network associated with the node is replaced with a second-order RLC network. Because a RLC network has three different modes of operation, namely over damped, critically damped, and under damped. The bandwidth in these three cases differs with under-damped RLC systems exhibit the largest bandwidth. Both shunt peaking [11, 12] and series peaking [13], have been used, as shown

| Reference                      | Tech.                 | $f_o$       | Tuning | Phase       | Power |

|--------------------------------|-----------------------|-------------|--------|-------------|-------|

|                                |                       | [GHz]       | range  | [dBc/Hz]    | [mW]  |

| Straayer et al. [1] (2002)     | $0.35 \mu \mathrm{m}$ | 1.7         | 6.3%   | -138@0.6MHz | 35*   |

| Baek et al.[2] (2003)          | $0.18 \mu \mathrm{m}$ | 8.08-7.83   | 3%     | -108@1MHz   | 24*   |

| Wang et al. [3] (2003)         | $0.18 \mu \mathrm{m}$ | 5.75-5.95   | 3.4%   | -105@5MHz   | 18*   |

| Gierkink et al.[4] (2003)      | $0.25 \mu \mathrm{m}$ | 4.57-5.21   | 13%    | -124@1MHz   | 21.9* |

| Choi et al.[5] (2004)          | $0.25 \mu \mathrm{m}$ | 1.5         | _      | -100@1MHz   | 28.8* |

| Dehghani & Atarodi [6] (2004)  | $0.25 \mu \mathrm{m}$ | 5.8         | 4.4%   | -134.6@3MHz | 5.8   |

| Kim et al.[7] (2004)           | $0.25 \mu \mathrm{m}$ | 2.27        | _      | -137@1MHz   | 30*   |

| Chang & Kim [8] (2005)         | $0.18 \mu \mathrm{m}$ | 5.5-6.7     | 20%    | -115@1MHz   | 5.76  |

| Oh & Lee [9] (2005)            | $0.18 \mu \mathrm{m}$ | 11          | 2.73%  | -109.4@1MHz | 6.84  |

| Soltanian & Kinget [10] (2006) | $0.25 \mu \mathrm{m}$ | 1.755-2.123 | 19%    | -120@0.6MHz | 2.25  |

Table 1.1. Performance comparison of CMOS spiral inductor / transformer LC VCOs.

- 1. Legends: TVCO Transformer VCO; QVCO Quadrature VCO.

- 2. VCO proposed by Choi et al. is a source-injection quadrature VCO.

- 3. VCO proposed by Chang and Kim is a cascode-coupling quadrature VCO.

- 4. VCO proposed by Gierkink et al. is a super-harmonic coupled VCO.

- 5. VCO proposed by Oh and Lee is a back-gate transformer feedback VCO.

- 6. VCO proposed by Soltanian and Kinget is a tail-current shaped VCO.

- 7. \* Total power consumption including buffers. Otherwise, the power consumption of oscillator core only.

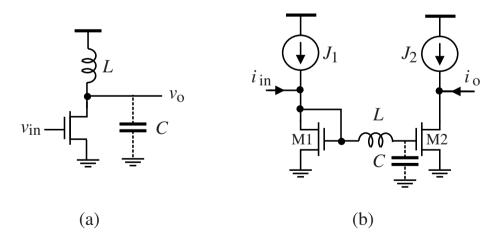

in Fig.1.1. It was demonstrated in [11, 12] that inductive shunt peaking can improve the bandwidth of a common-source amplifier by as much as 70%.

Figure 1.1. Inductive peaking. (a) Shunt peaking - The peaking inductor L is in parallel with the dominant capacitor C. (b) Series peaking - The peaking inductor L is in series with the dominant capacitor C.

• Current-mode signaling - A circuit is classified as current-mode if the information carriers of the circuit are the branch currents of the circuit. A key distinction between current-mode and voltage-mode circuits is that the nodal impedance of current-mode circuits is low whereas that of voltagemode circuits is high. This distinct characteristic forms the foundation on which current-mode circuits are designed. Since the information processed by a current-mode circuit is represented by the branch currents rather than nodal voltages of the circuit, the swing of the nodal voltages of the circuit can be made small without sacrificing the fidelity of the signal. Currentmode circuits offer an improved bandwidth due to the following reasons : (i) Low nodal impedances - the low nodal impedances of current-mode circuits lower the nodal time constants of the circuits. (ii) Low voltage swing - the small swing of the nodal voltages of current-mode circuits reduces the amount of the time required to charge and discharge the nodes of the circuits [14]. It should be emphasized that the speed improvement using currentmode signaling is often moderate as lowering the nodal impedance of a nodal is often echoed with an increase in the capacitance of the node at the same time. Because each node is essentially a first-order RC network whose time constant is given by  $\tau_n = R_n C_n$ , where  $R_n$  and  $C_n$  denote the resistance and capacitance of the node, respectively, the net reduction in the nodal time constant is rather moderate.

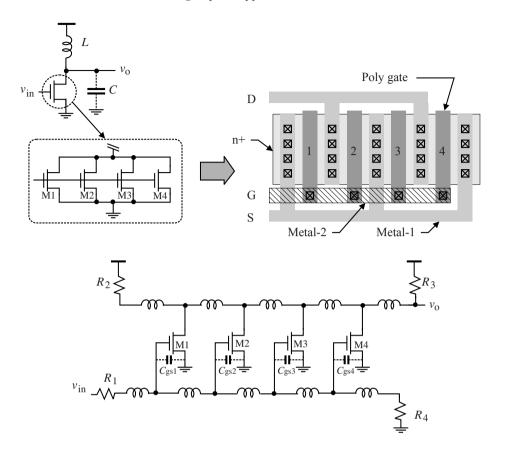

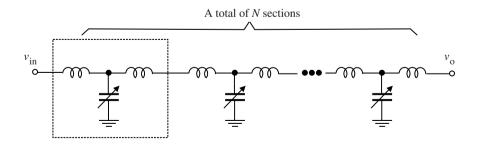

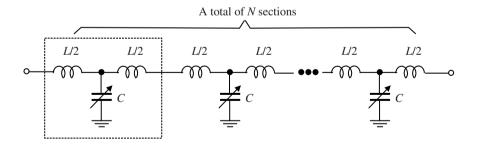

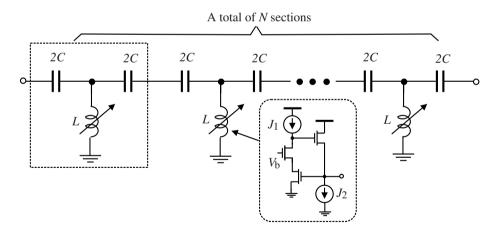

■ Distributed amplification - As pointed out earlier that the bandwidth or speed of a circuit is set by the time constant of the critical node of the circuit. An effective way to minimize the effect of the large shunt capacitance of the critical node is to break the large shunt capacitor into several smaller shunt capacitors and separate them with inductors such that the large shunt capacitor is replaced with a distributed LC network or a transmission line [15, 16]. Shown in Fig.1.2 is a common-source amplifier where an shuntpeaking inductor is employed at the drain of the transistor to offset the effect of the large output capacitance C arising from the large width of the transistor. Inductive shunt-peaking, though effective, can not deliver the needed bandwidth in this case. Notice that a transistor is typically laid out in a multi-finger fashion. This is equivalent to connecting N smaller transistors whose width is only 1/N of that of the original transistor in parallel, as shown in the figure, where N is the number of the fingers of the transistor. Inductors can then be employed to separate these small transistors and form two transmission lines, one at the drain and the other at the source. Resistors  $R_{1-4}$  are for the purpose of impedance matching.

Figure 1.2. Distributed amplifiers.

# 1.1.3 Impedance Matching

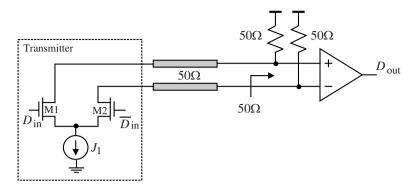

Impedance matching is required between channels and high-speed circuits to minimize signal reflection at their interfaces. Resistors are usually used to provide a matching impedance in broadband communication systems as impedance matching is required over a broad frequency spectrum, as shown in Fig.1.3 where a shunt resistor termination at the far end of the channels is employed. Active termination where transistors are used as termination devices has also been used recently to take the advantage of the tunability of the termination resistance [14]. Frequency-dependent elements, such as capacitors and inductors, can not be used for impedance matching in broadband communication systems simply due to their frequency-dependent characteristics.

Most wireless communication systems operate in a narrow-band mode. A matching impedance in this case is only required over a very narrow frequency

Figure 1.3. Impedance matching in high-speed current-mode serial links.

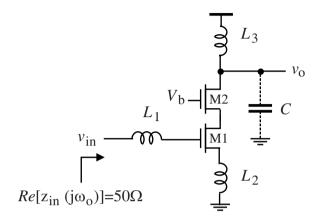

range. Although resistors can be used for these applications, the high level of the thermal noise of resistors disqualifies themselves from being used in wireless communications where a stringent constraint on the noise performance of the systems exists. Instead, noiseless elements such as capacitors and spiral inductors are widely used in narrow-band impedance matching because these frequency-dependent noiseless elements can provide the desired impedance in a narrow frequency band and at the same time keep the noise at the minimum [17, 18]. Shown in Fig.1.4 is a widely used termination scheme for narrow-band low-noise amplifiers. Neglecting  $C_{gd}$  and other parasitic capacitances, it is elementary to show that the input impedance of the LNA is given by

$$z_{in} = \left[ j\omega(L_1 + L_2) + \frac{1}{j\omega C_{gs1}} \right] + \frac{g_{m1}L_2}{C_{gs1}}, \tag{1.1}$$

where  $C_{gs1}$  and  $g_{m1}$  are the gate-source capacitance and transconductance of  $M_1$ , respectively. It is seen from (1.1) that the first term on the right hand side of (1.1) is reactive while the second term is resistive. The reactive term can be made zero by imposing

$$\omega(L_1 + L_2) - \frac{1}{\omega C_{qs1}} = 0. \tag{1.2}$$

The input impedance of the LNA in this case becomes purely resistive and is given by

$$z_{in} = \frac{g_{m1}L_2}{C_{qs1}}. (1.3)$$

The need for two inductors  $L_1$  and  $L_2$  with  $L_1$  at the gate and  $L_2$  at the source is justified as the followings: Once the dimension of  $M_1$  is chosen,  $g_{m1}$  and

$C_{gs1}$  are determined. The desired input impedance of the LNA in this case can be obtained by adjusting  $L_2$ . Once  $L_2$  is chosen, the value of  $L_1$  can be tuned to ensure the total cancellation of the reactive part of the input impedance.

Figure 1.4. Impedance matching in narrow-band low-noise amplifiers.

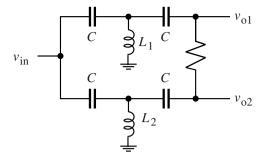

# 1.1.4 Phase Shifting

A phase shifter is a uni-directional serial network inserted in a signal path so that the phase of the signal at the output of the signal path can be adjusted in a controlled manner [19, 20]. A well-designed phase shifter should possess the characteristics of a low insertion loss, a high return loss, and a large phase shift range. The common configuration of RF phase shifters is shown in Fig.1.5. The floating inductors are typically implemented using high-impedance metal lines. The tuning of the amount of the phase shift is carried out by varying the capacitance of the shunt varactors.

Figure 1.5. RF phase shifters with floating inductors and shunt varactors.

# 1.1.5 Frequency Selection

Bandpass filters with a high passband center frequency are used extensively in narrow-band wireless communications for RF band selection. These filters are traditionally implemented using lumped LC and surface acoustic wave (SAW) filters with SAW filters the most widely used. SAW filters, however, are not compatible with CMOS technologies. The recent effort on integrating RF bandpass filters on a silicon substrate is accelerated with the emergence of CMOS spiral inductors and transformers. A single-chip realization of RF transceivers with on-chip RF bandpass filters offers a number of critical advantages including a reduced assembly cost, increased system reliability, and improved performance. To compensate for the high insertion loss of spiral inductors at high frequencies, active negative resistors have been used to boost the quality factor of the spiral inductors. Table 1.2 tabulates some recently reported RF bandpass filters with spiral inductors and active Q-enhancement.

| Reference                     | Year | Tech.                 | $f_o$    | Tuning range |

|-------------------------------|------|-----------------------|----------|--------------|

| Kuhn et al. [21]              | 1997 | $2\mu\mathrm{m}$      | 0.2 GHz  | 4.5%         |

| Duncan et al. [22]            | 1997 | $0.8 \mu \mathrm{m}$  | 0.75 GHz | 2.3%         |

| Soorapanth-Wong [23]          | 2002 | $0.25 \mu \mathrm{m}$ | 2.14 GHz | 1.4%         |

| Dulger et al. [24]            | 2003 | $0.35 \mu \mathrm{m}$ | 2.1 GHz  | 13%          |

| Kuhn <i>et al</i> . [25]      | 2003 | -                     | 0.9 GHz  | 2.2%         |

| Bantas-Koutsoyannopoulos [26] | 2004 | $0.35\mu\mathrm{m}$   | 1 GHz    | 11%          |

$0.18 \mu m$

2.368 GHz

1.3%

2006

Table 1.2. Bandpass filter with Q-enhanced spiral inductors.

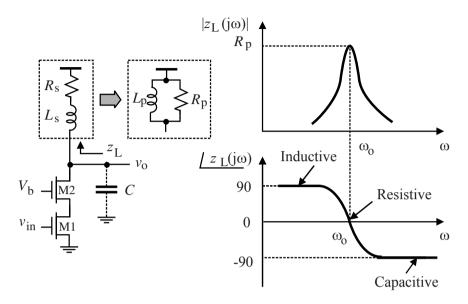

# 1.1.6 Gain Boosting

Kulyk-Haslett [27]

Traditional gain-boosting techniques such as cascodes and regulated cascodes lose their potency at high frequencies due to the increased gate-source and gate-drain couplings via the gate-source and gate-drain capacitors of MOS-FETs. A technique that is widely used in boosting the voltage gain of narrowband low-noise amplifiers (LNAs) is to use a LC tank as the load of the LNAs, utilizing the infinite impedance of ideal LC tanks at their self-resonant frequency. When a LC tank is used as the load of a common-source amplifier whose voltage gain is approximated by  $A_v \approx -g_m z_L$ , where  $g_m$  is the transconductance of the MOSFET and  $z_L$  is the load impedance, as shown in Fig.1.6, the large impedance of the LC tank at its self-resonant frequency  $\omega_b = \frac{1}{\sqrt{L_p C}}$

will significantly boost the gain of the amplifier at  $\omega_o$ . The resonant frequency of the tank is set to be the same as the frequency of the input of the LNA. Note that voltage gain of the amplifier at frequencies other than  $\omega_o$  is low.

Figure 1.6. Gain boosting of low noise amplifiers using LC tank load.

#### 1.1.7 Power Dividers

RF power dividers are traditionally realized using transmission lines. Lumped passive implementation of power dividers has also been used to reduce the size of the power dividers, however, at the cost of a high insertion loss and a limited bandwidth. Fig.1.7 shows the equivalent circuit of lumped Wilkinson power divider. The use of CMOS active inductors to replace passive spiral inductors of RF power dividers was proposed by Lu and Wu in [28] to take the advantages of the high quality factor, low silicon consumption, and high self-resonant frequency of CMOS active inductors.

# 1.2 Spiral Inductors and Transformers

Monolithic on-chip inductors and transformers are also known as spiral inductors and transformers due to the way in which these inductors and transformers are laid out. Both planar and stacked spiral inductors and transformers have been developed and the detailed characterization and modeling of these inductors and transformers are available. Modern CAD tools for IC design are equipped with spiral inductors as standard elements in their component libraries.

Figure 1.7. Equivalent circuit of lumped Wilkinson power divider.

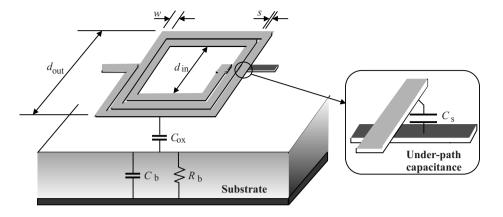

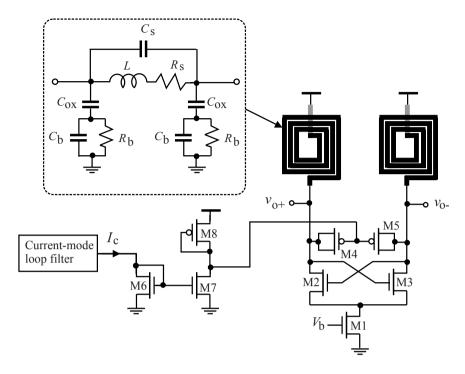

#### 1.2.1 Planar Spiral Inductors

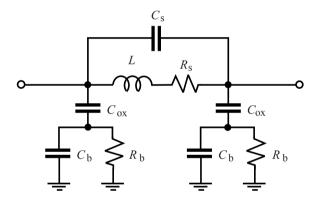

Fig.1.8 is a sketch of square-shaped planar spiral inductors. The lumped equivalent circuit of spiral inductors is given in Fig.1.9, where L is the inductance of the spiral inductor,  $R_s$  represents the series resistance of the spiral caused by the skin-effect induced resistance in the spiral and the resistance induced by the eddy current in the substrate [29],  $C_{\rm s}$  accounts for the capacitance due to the overlap of the spiral and the center-tap underpasses,  $C_{ox}$  denotes the capacitance between the spiral and the substrate,  $C_b$  and  $R_b$  quantify the capacitance and resistance of the substrate, respectively. Although modern CMOS technologies are equipped with multiple metal layers, typically only the top metal layer is used to construct planar spiral inductors and transformers such that the unwanted parasitic capacitance between the spiral and the substrate is minimized. As pointed out in [29], the substrate loss accounts for 10-30% reduction of the quality factor of the spiral inductors in low GHz ranges, mainly due to the penetration of the electric field generated by the spiral into the substrate. A main drawback of planar spiral inductors is their low inductance.

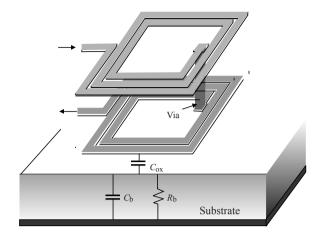

# 1.2.2 Stacked Spiral Inductors

The inductance of spiral inductors can be increased significantly using stacked configurations, as shown in Fig.1.10, however, at the price of an increased spiral-substrate capacitance because the lower metal layers are also used in the construction of the inductors [30]. The total inductance of a stacked inductor with two spiral layers is given by

$$L_{total} = L_1 + L_2 + 2M, (1.4)$$

where  $L_1$  and  $L_2$  are the self-inductances of spirals 1 and 2, respectively, and M is the mutual inductance between the two spirals. Note the direction of the routing of the spirals in differential metal layers must be carefully

Figure 1.8. Square-shaped planar spiral inductors. w is the width of the spiral and s is the spacing between the turns of the spiral.

Figure 1.9. Lumped circuit model of planar spiral inductors.

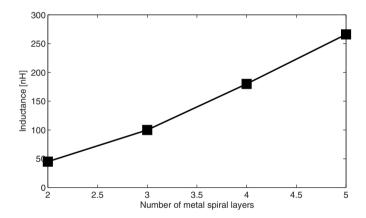

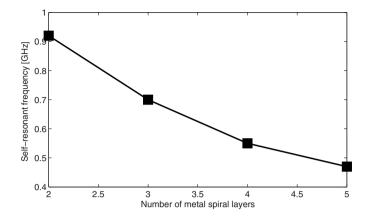

chosen such that the total inductance increases. Figs.1.11 and 1.12 show the dependence of the measured inductance and self-resonant frequency of stacked inductors on the number of spiral layers [30]. It is seen that the inductance of stacked spiral inductors increases approximately linearly with the increase in the number of the spiral layers of the inductors. The self-resonant frequency of stacked inductors decreases with the increase in the number of spiral layers in a nonlinear fashion.

# 1.2.3 Spiral Transformers

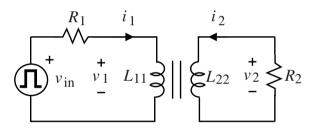

To increase the inductance without significantly increasing silicon consumption, stacked spiral transformers and bilifar spiral transformers emerged. Transformers are essentially two spiral inductors coupled via a magnetic link.

Figure 1.10. Square-shaped stacked spiral inductors.

Figure 1.11. Dependence of the inductance of stacked spiral inductors on the number of spiral layers.

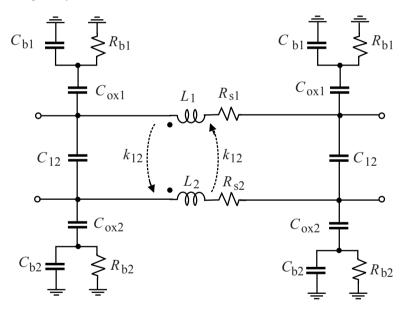

Fig.1.13 shows the lumped circuit model of bifilar spiral transformers [31], where  $C_{12}$  is the mutual capacitance between the primary and secondary windings, and  $k_{12}$ ,  $k_{21}$  are the coupling coefficients. All other parameters are the same as those in Fig.1.9.

# 1.2.4 Characteristics of Spiral Inductors and Transformers

Spiral inductors and transformers offer the key advantages of superior linearity and a low level of noise. The performance and applications of spiral inductors and transformers are affected by a number of drawbacks that are intrinsic to the physical geometry of these passive devices and CMOS tech-

Figure 1.12. Dependence of the self-resonant frequency of stacked spiral inductors on the number of spiral layers.

Figure 1.13. Lumped circuit model of spiral transformer.

nologies in which spiral inductors and transformers are implemented. These drawbacks include:

■ Low quality factor - The quality factor of spiral inductors and transformers is limited by the ohmic loss of the spiral at high frequencies. Two sources that contribute to the ohmic loss of the spiral inductors and transformers exist: the skin-effect induced resistance of the spiral and the resistance

induced by the eddy currents in the substrate. The former is proportional to the square-root of the frequency of the signal flowing in the spiral whereas the latter is proportional to the square of the frequency of the signal flowing in the spiral. Because the resistance of the substrate in the lateral direction is much larger as compared with that in the vertical direction [32], the eddy currents in the literal direction in the substrate are small. The substrate eddy-current induced resistance of the spiral is often negligible as compared with the resistance caused by the skin-effect [23]. The quality factor of spiral inductors in standard CMOS is typically below 20, as is evident in Table 1.3 where the parameters of some recently reported CMOS spiral inductors are tabulated.

- Low self-resonant frequency The self-resonance of a spiral inductor is the resonance of the LC tank formed by the series inductance of the spiral inductor and the shunt capacitance between the spiral of the inductor and the substrate, as well as its underpass capacitance. The low self-resonant frequency of spiral inductors is mainly due to the large spiral-substrate capacitance, arising from the large metal area occupied by the spiral. The typical self-resonant frequency of spiral inductors is in the low GHz range, as is evident in Table 1.3.

- Low and fixed inductance As pointed out earlier that the inductance of a planar spiral inductor is low and fixed once the number of the turns of the spiral is set. The only way to increase the inductance of the spiral inductor is to either increase the number of the turns of the spiral or use a stacked configuration where spirals on multiple metal layers are connected using vias. The former is at the expense of a large silicon area while the latter increases the spiral-substrate capacitance.

- Large silicon area Due to the low inductance of spiral inductors, especially planar spiral inductors, and the fact that the inductance of these inductors is directly proportional to the number of the turns of the spiral of the inductors, the silicon area required for routing the spiral of the inductors is large. As an example, it was shown in [11] that a square-shaped spiral inductor of an inductance 8 nH will require 6 turns with  $d_{out} = 400 \mu m$ . The actual silicon consumption of the inductor is larger than  $400 \times 400 \mu m^2$  when design rules on the minimum spacings are followed. Moreover, the design rules of most IC foundries prohibit the placement of either active or passive devices in the region between the spiral of the inductors and the substrate, making spiral inductors the most silicon-consuming components.

| Structure | Inductance [nH] | $d_{out}$ [ $\mu$ m] | Turns | $Q(\omega_o)$ | $f_o$ [GHz] | Year | Ref. |

|-----------|-----------------|----------------------|-------|---------------|-------------|------|------|

| Square    | 3.5             | 330                  | 4     | 11            | 3.9         | 1996 | [21] |

| Square    | <6              | _                    | 7     | <6            | 1           | 1996 | [33] |

| Square    | 15.2            | 310                  | 8     | <4            | 1.5         | 1998 | [34] |

| Square    | 8               | 400                  | 6     | _             | _           | 1999 | [11] |

| Octagon   | 6               | 320                  | 4     | 11            | 1.4         | 2003 | [35] |

| Octagon   | 4.3             | 200                  | 3     | 5             | 4           | 2003 | [36] |

Table 1.3. Key parameters of some CMOS spiral inductors.

#### 1.3 Active Inductors and Transformers

CMOS active inductors are active networks that consist mainly of MOS transistors. Resistors are sometimes used as feedback elements to improve the performance of active inductors. Under certain dc biasing conditions and signal-swing constraints, these networks exhibit an inductive characteristic in a specific frequency range. As compared with their spiral counterparts, CMOS active inductors offer the following attractive advantages:

- Low silicon consumption Because only MOS transistors are usually required in the realization of CMOS active inductors and the inductance of these active inductors is inversely proportional to the transconductances of the transistors, the silicon consumption of CMOS active inductors is negligible as compared with that of their spiral counterparts.

- Large and tunable self-resonant frequency CMOS active inductors with a large self-resonant frequency are highly desirable. For example, the pass-band center frequency of an active inductor RF bandpass filter is typically set to the self-resonant frequency of the active inductor of the filter. The larger the self-resonant frequency of the active inductor, the higher the passband center frequency of the filter. In applications where CMOS active inductors are used for low-pass filters, these filters are operated at frequencies below their self-resonant frequency of active inductors. A large self-resonant frequency of active inductors will have an inductive characteristic over a large frequency range. As to be seen in Chapter 2 that the self-resonant frequency of a CMOS active inductor is the maximum frequency of the transconductors constituting the active inductor. When the basic configurations of transconductors, such as common-source

and common-gate transconductors, are used, this frequency approaches  $f_T$  of the devices.

- Large and tunable inductance As to be seen in Chapter 2, the inductance of CMOS active inductors is inversely proportional to the transconductances of the transistors synthesizing the inductors. The smaller the width of the transistors, the larger the inductance. Also the inductance can be tuned conveniently by varying the dc biasing condition of the transistors synthesizing the inductor with a large inductance tuning range. The coarse tuning of the inductance of active inductors is typically attained in this way. The fine tuning of the inductance of active inductors can also be achieved by varying the load capacitance of the transconductors of the active inductors using MOS varactors.

- Large and tunable quality factor The quality factor of CMOS active inductors is set by the ohmic loss of the inductors, arising mainly from the finite output resistance of the transconductors of the inductors. The quality factor of CMOS active inductors can be increased by increasing this output resistance. A number of methods are available to boost the output resistance, such as cascodes, regulated cascodes, and negative resistor compensation. In each of these approaches, the degree of compensation can be varied. For example, in the cascode approach, the output resistance of a cascode-configured transconductor can be adjusted by varying the biasing voltage of the cascoding transistor. In the regulated cascode approach, the output resistance of the regulated-cascode configured transconductor can be changed by varying the voltage gain of its auxiliary voltage amplifier. In the negative resistor compensation approach, the resistance of the compensating negative resistor can be adjusted by varying the biasing current of the negative resistor. A detailed presentation of these approaches will be given in Chapter 2.

- Compatibility with digital CMOS technologies Spiral inductors are not available in low-cost digital-oriented CMOS processes. They are available only in more expensive mixed-mode CMOS technologies. CMOS active inductors, however, can be realized using standard digital CMOS processes.

CMOS active inductors and transformers have found increasing applications in areas where an inductive characteristic is required. These applications include LC and ring oscillators, RF bandpass filters, RF phase shifters, limiting amplifiers for optical communications, low-noise amplifiers for wireless communications, RF power dividers, ultra wideband low-noise amplifiers, and transceivers for high-speed data links over wire lines. Table 1.4 summarizes some of the recently published work where CMOS active inductors and transformers were employed.

| Year | Tech.                                                                                                                | Applications                                                                                                                                                                                                                                                                                                                                                                            | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2000 | $0.8 \mu \mathrm{m}$                                                                                                 | IF Bandpass                                                                                                                                                                                                                                                                                                                                                                             | 100 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2000 | $0.8 \mu \mathrm{m}$                                                                                                 | LC VCO                                                                                                                                                                                                                                                                                                                                                                                  | 0.45-1.2 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2000 | $0.35 \mu \mathrm{m}$                                                                                                | LC VCO                                                                                                                                                                                                                                                                                                                                                                                  | 1.1-2.1 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2000 | $0.25 \mu \mathrm{m}$                                                                                                | Limiting amp.                                                                                                                                                                                                                                                                                                                                                                           | 3 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2001 | $0.35 \mu \mathrm{m}$                                                                                                | LC VCO                                                                                                                                                                                                                                                                                                                                                                                  | 0.1-0.9 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2001 | $0.30 \mu \mathrm{m}$                                                                                                | LC VCO                                                                                                                                                                                                                                                                                                                                                                                  | 0.4-4 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2001 | $0.35 \mu \mathrm{m}$                                                                                                | RF bandpass                                                                                                                                                                                                                                                                                                                                                                             | 0.4-1.1 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2002 | $0.35 \mu \mathrm{m}$                                                                                                | RF bandpass                                                                                                                                                                                                                                                                                                                                                                             | 2.4-2.6 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2002 | $0.18 \mu \mathrm{m}$                                                                                                | RF lowpass                                                                                                                                                                                                                                                                                                                                                                              | 4.57 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2004 | $0.18 \mu \mathrm{m}$                                                                                                | RF bandpass                                                                                                                                                                                                                                                                                                                                                                             | 3.5-5.7 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2005 | $0.18 \mu \mathrm{m}$                                                                                                | RF power divider                                                                                                                                                                                                                                                                                                                                                                        | 4.5 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2005 | $0.18 \mu \mathrm{m}$                                                                                                | RF bandpass                                                                                                                                                                                                                                                                                                                                                                             | 3.45-3.6 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2005 | $0.25 \mu \mathrm{m}$                                                                                                | RF bandpass                                                                                                                                                                                                                                                                                                                                                                             | 2.05-2.45 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2005 | $0.35 \mu \mathrm{m}$                                                                                                | Limiting amp.                                                                                                                                                                                                                                                                                                                                                                           | 2.3 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

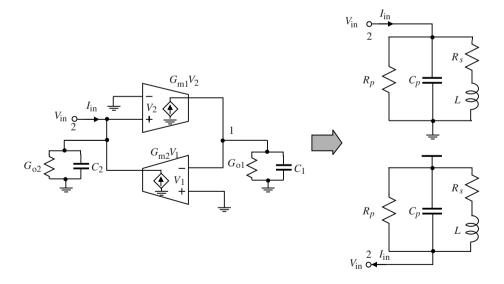

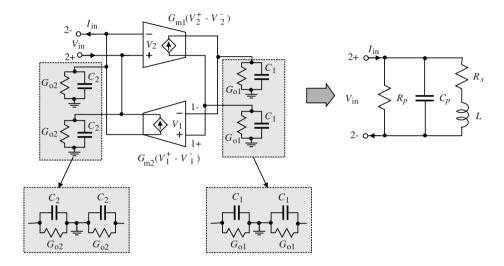

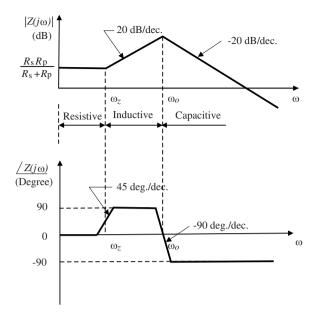

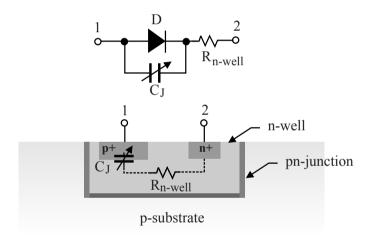

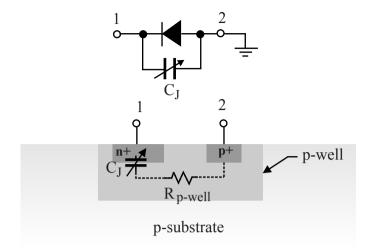

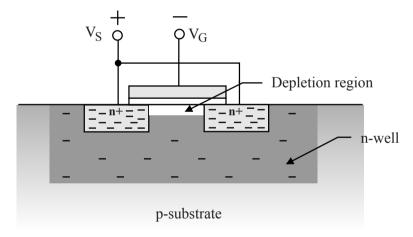

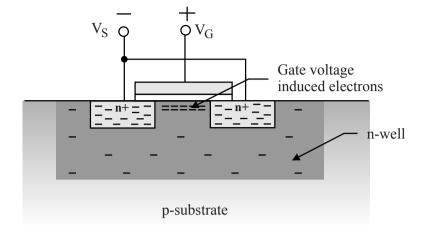

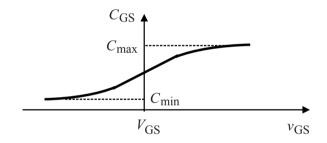

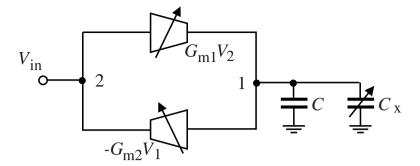

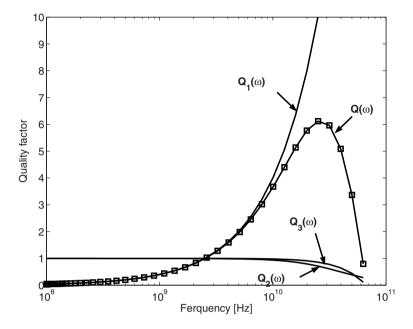

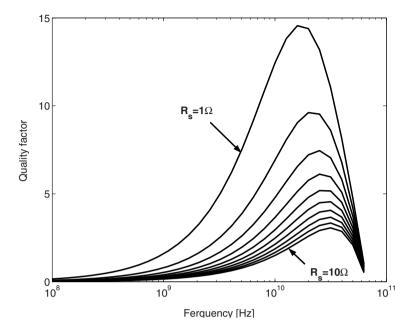

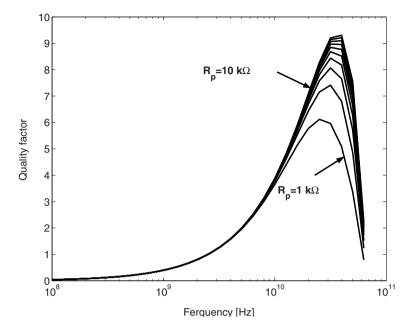

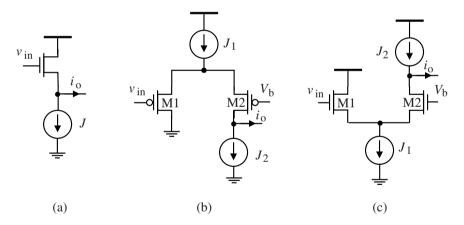

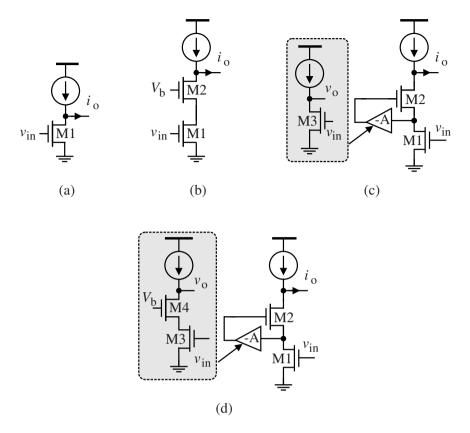

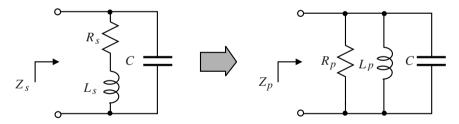

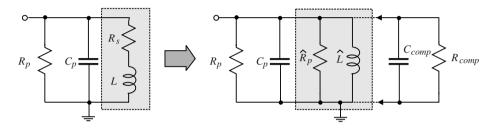

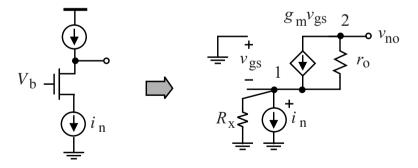

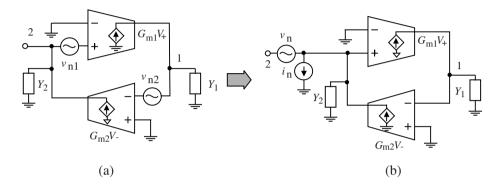

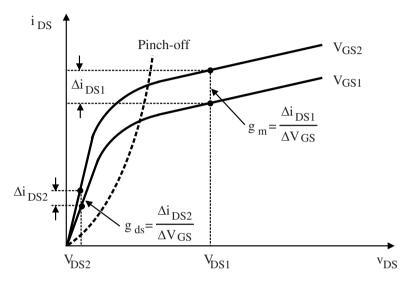

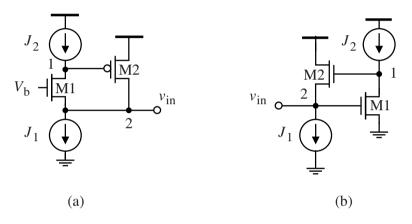

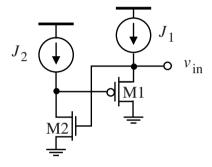

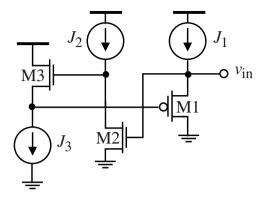

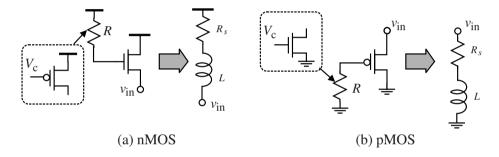

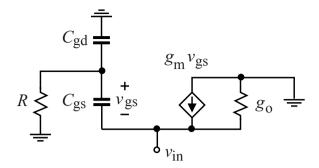

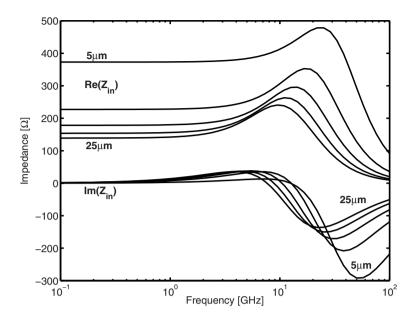

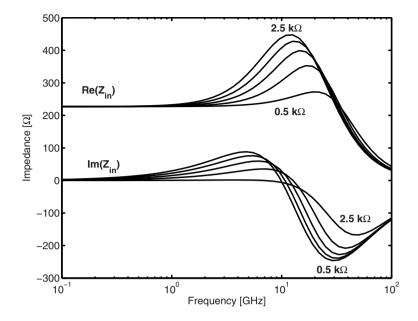

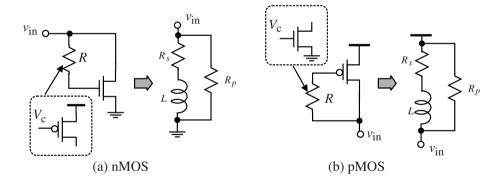

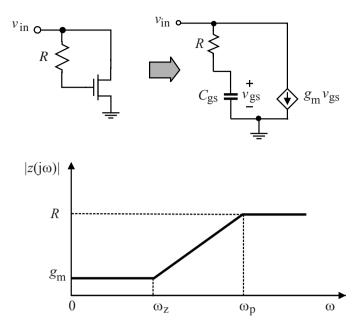

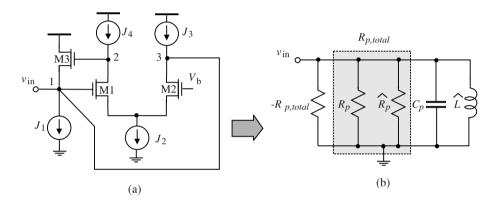

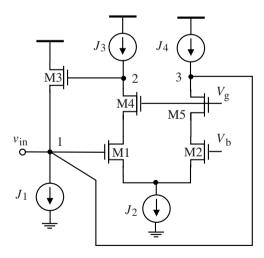

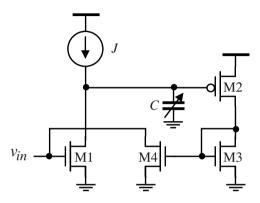

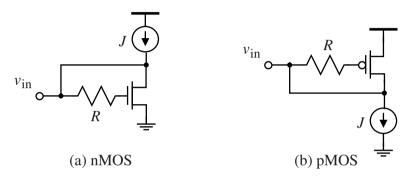

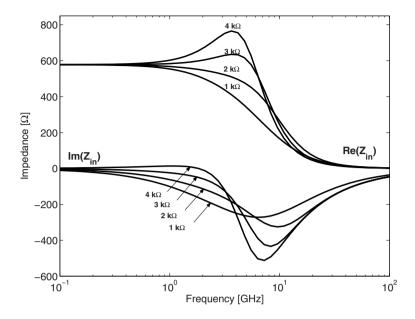

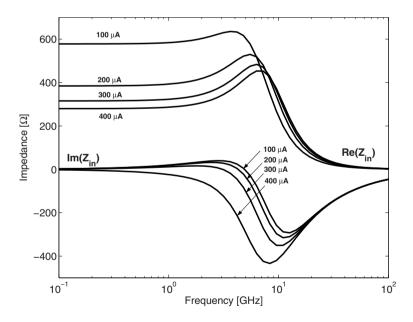

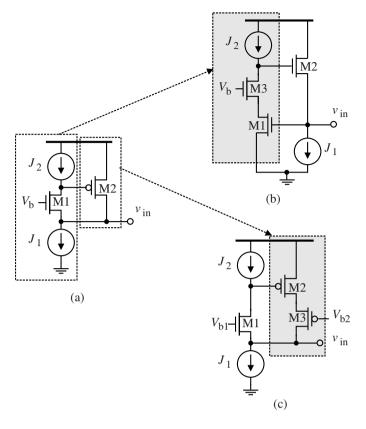

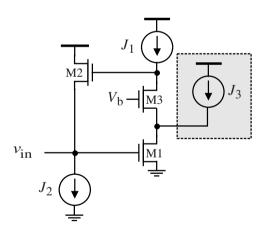

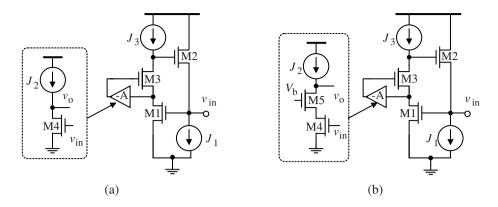

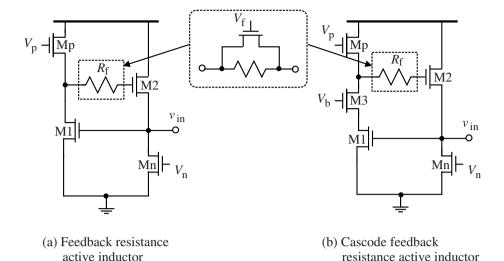

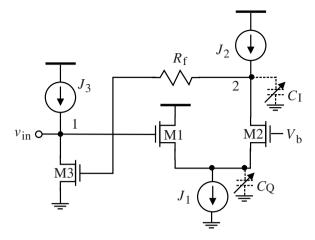

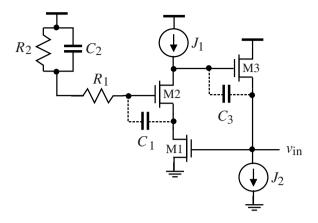

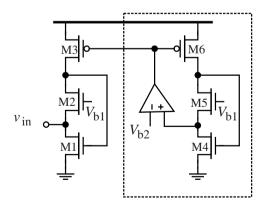

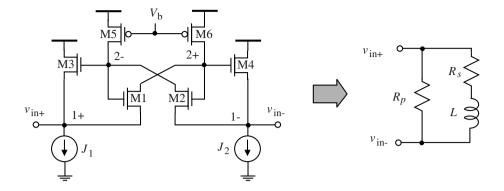

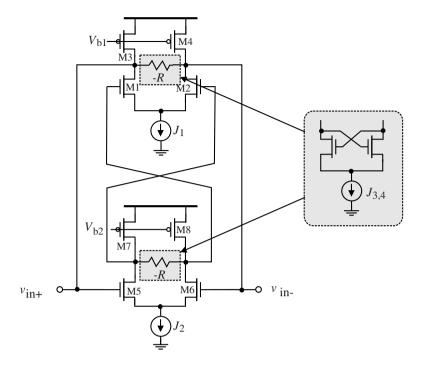

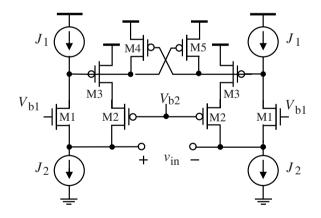

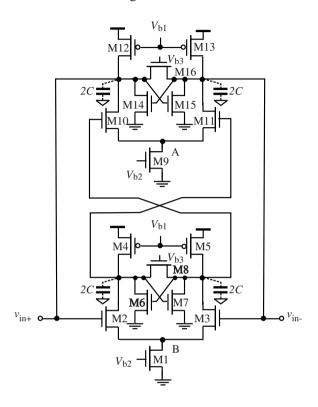

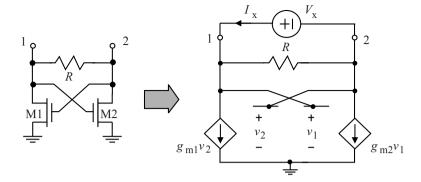

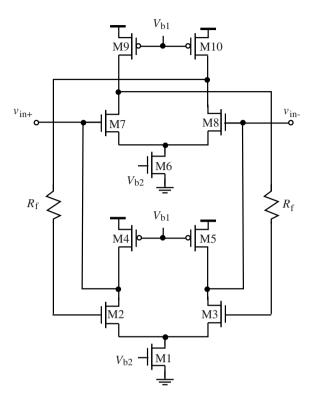

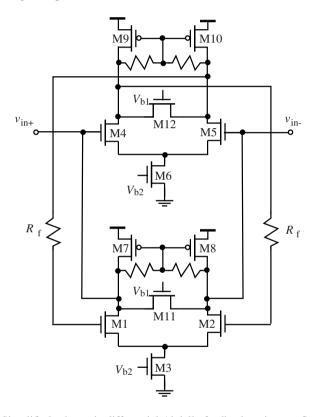

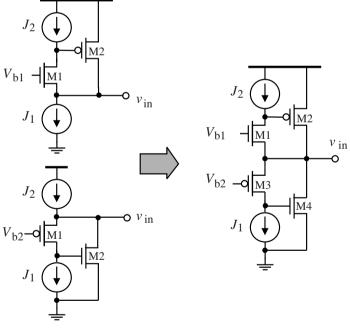

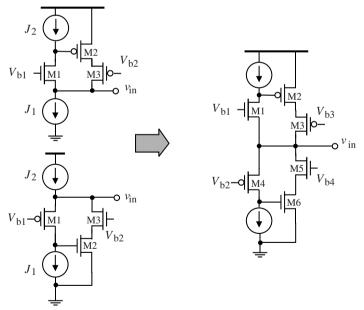

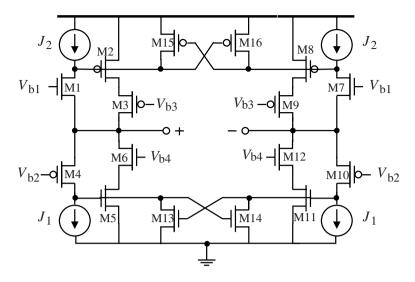

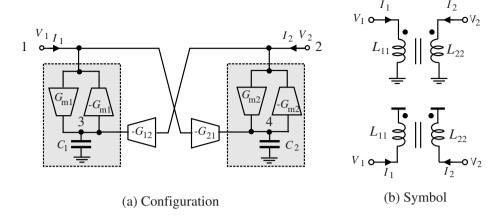

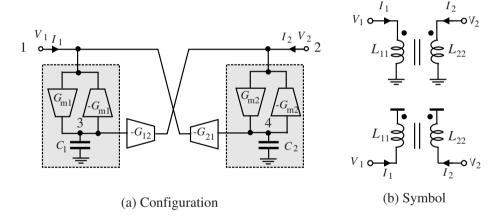

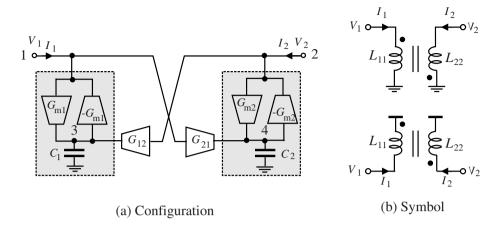

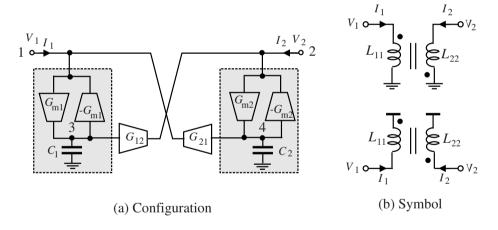

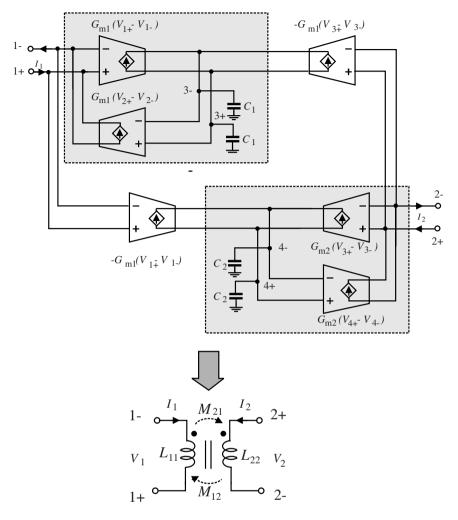

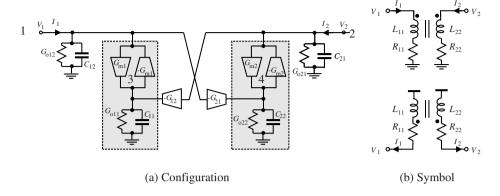

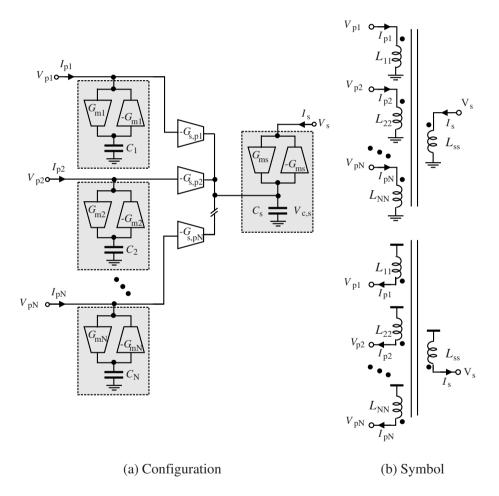

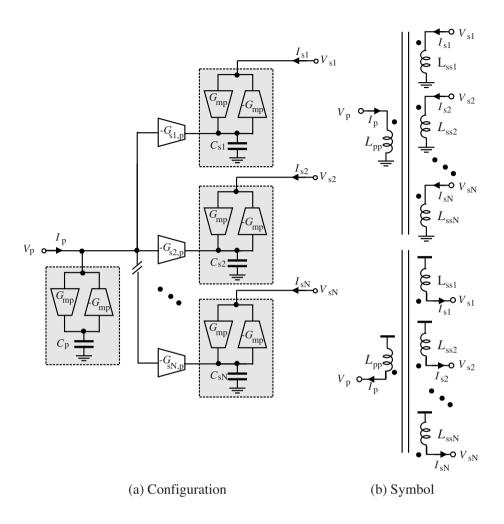

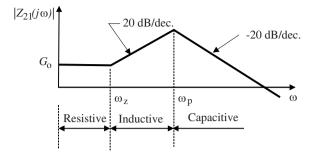

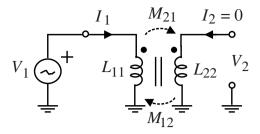

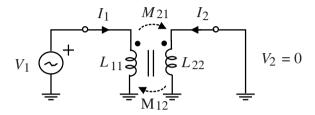

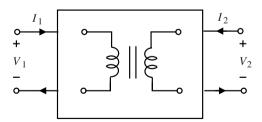

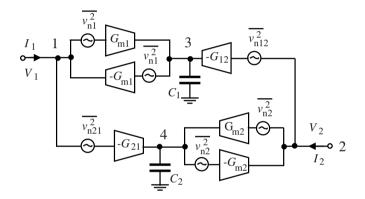

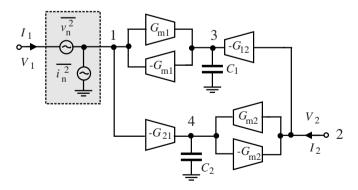

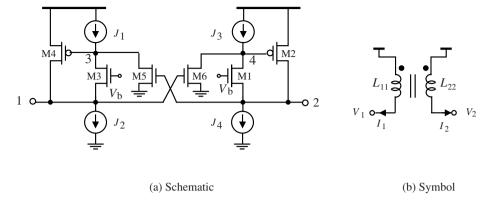

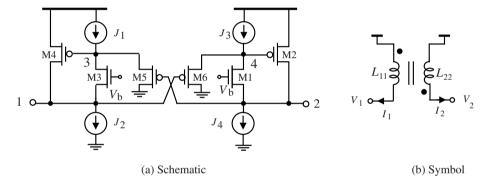

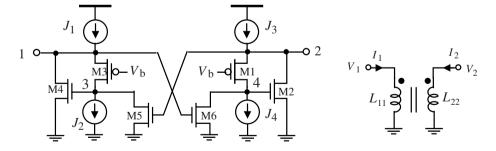

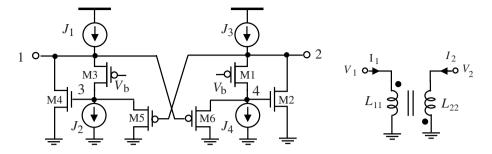

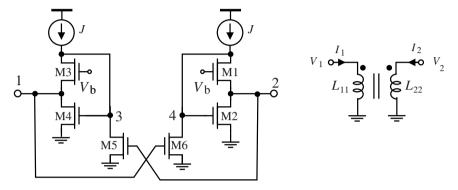

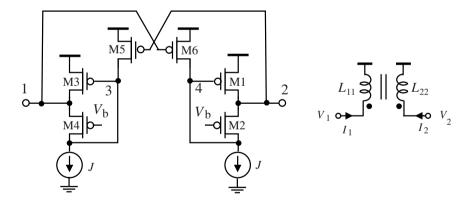

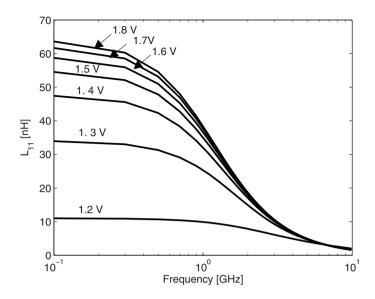

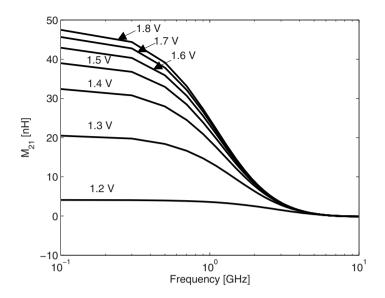

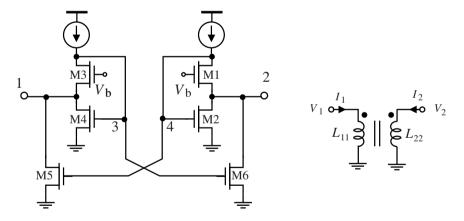

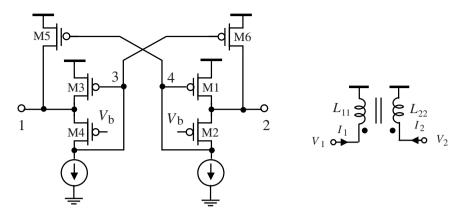

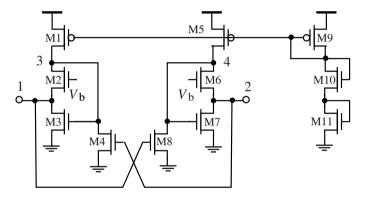

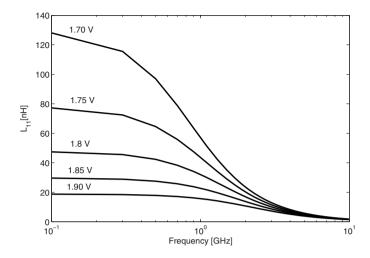

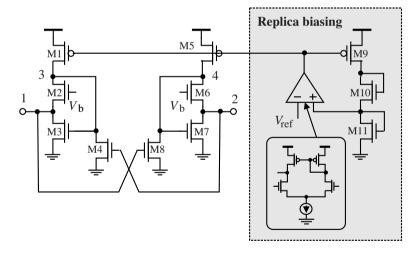

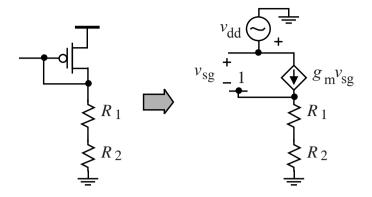

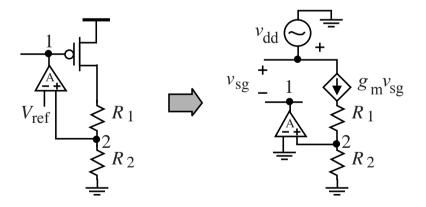

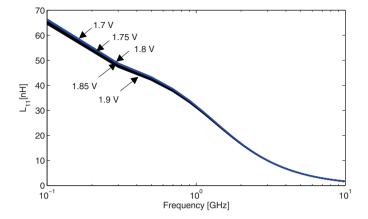

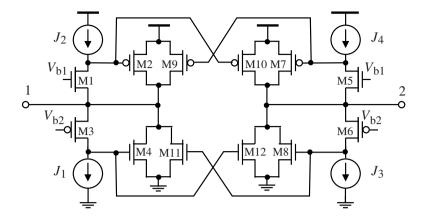

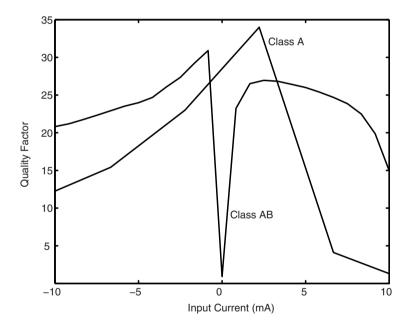

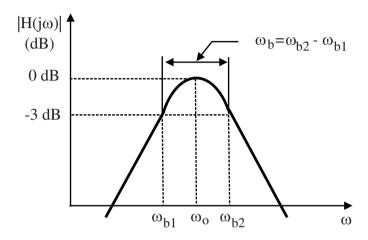

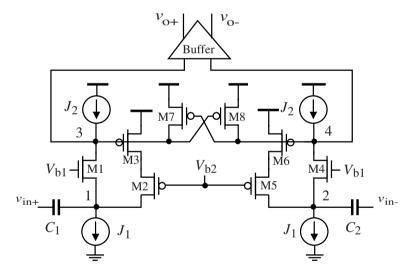

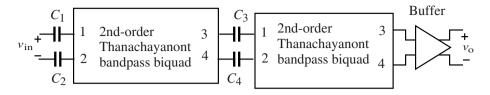

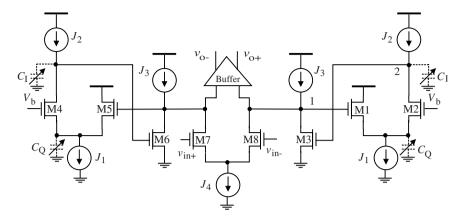

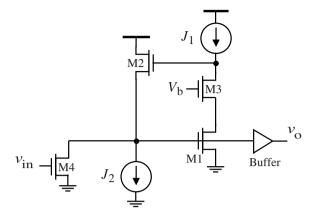

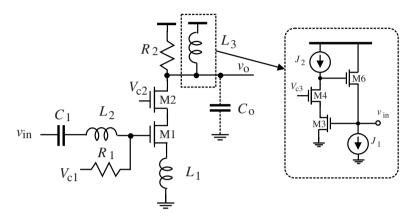

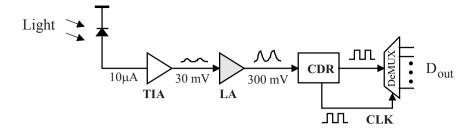

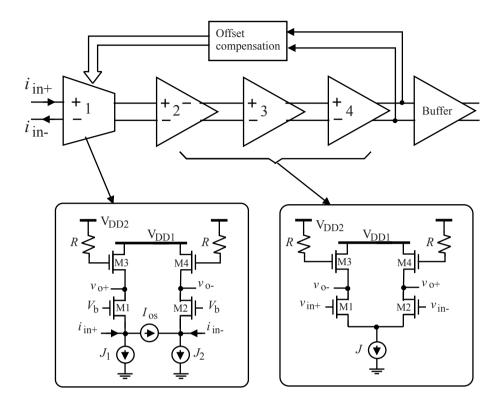

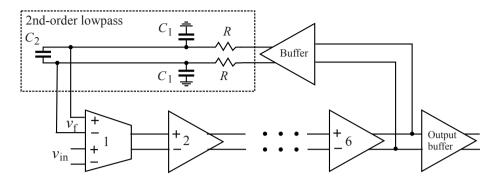

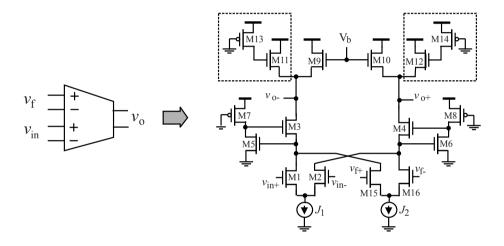

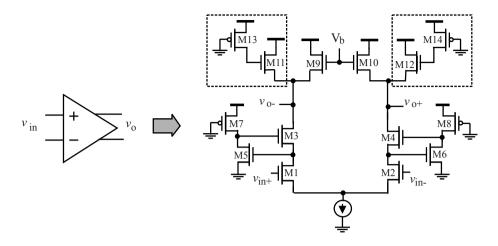

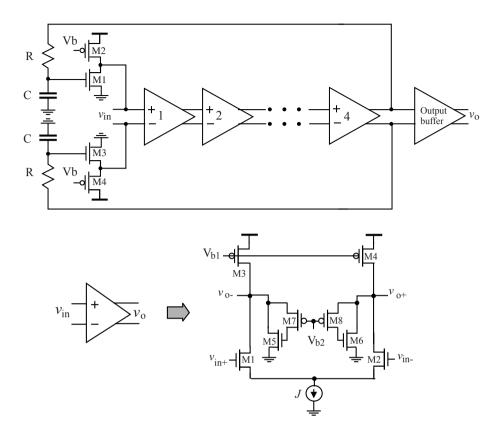

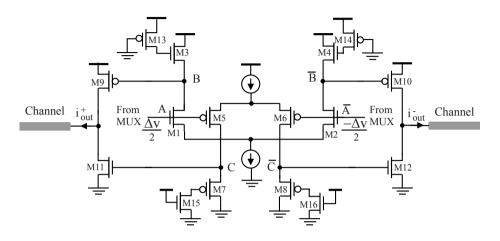

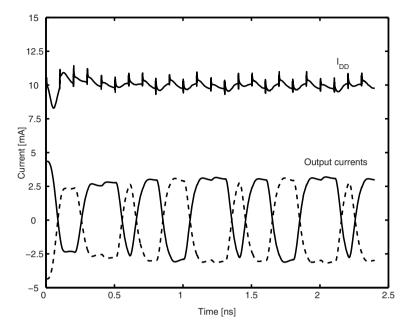

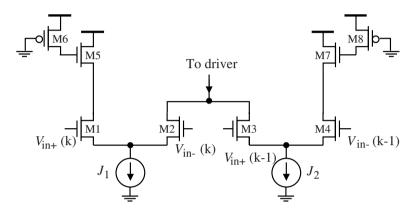

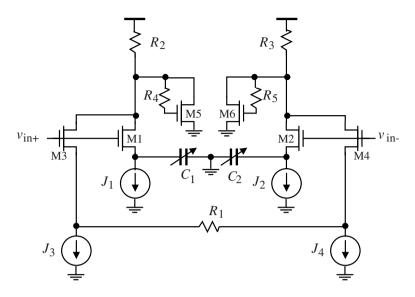

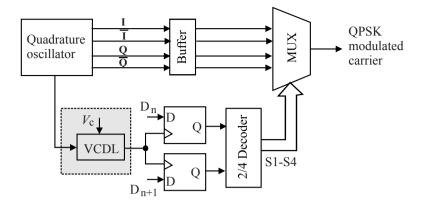

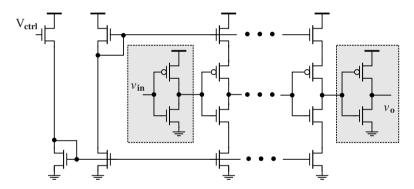

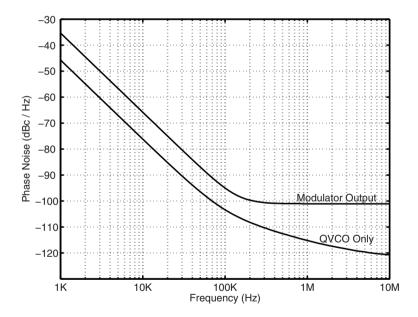

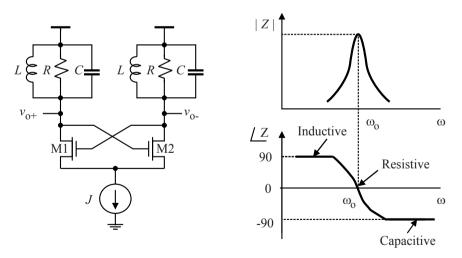

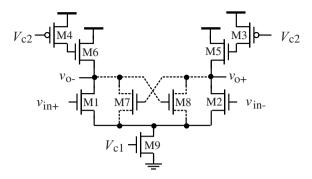

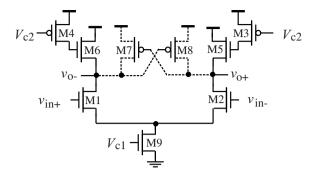

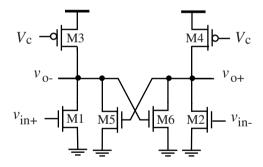

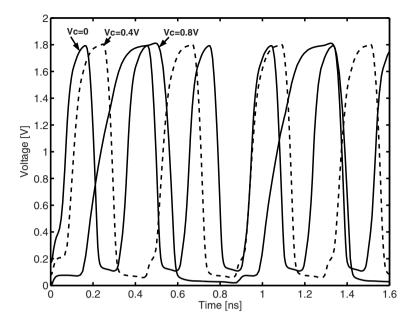

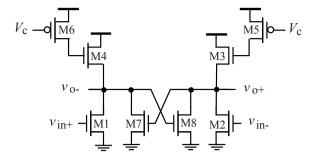

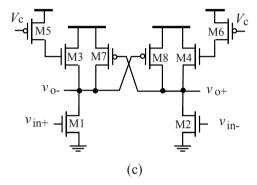

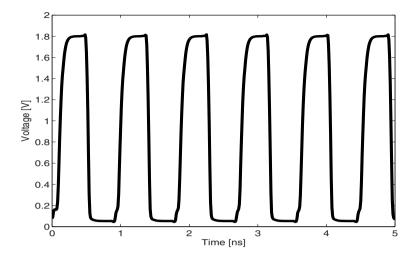

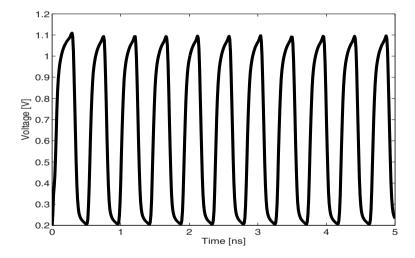

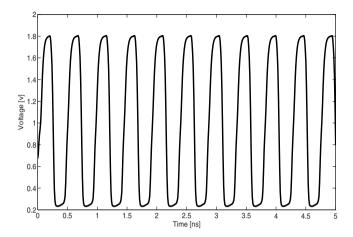

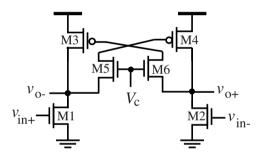

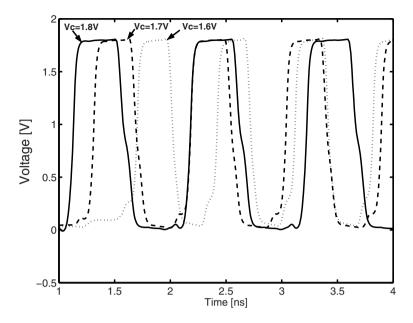

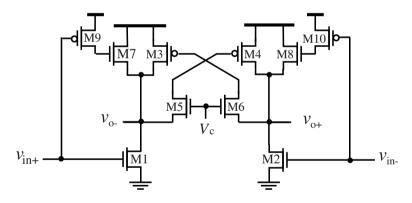

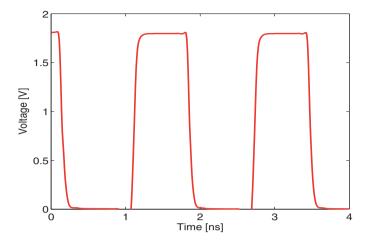

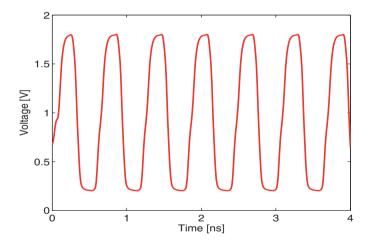

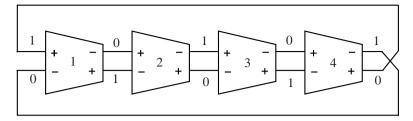

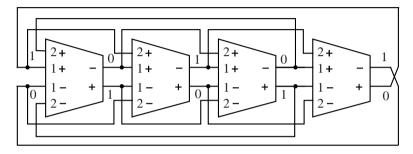

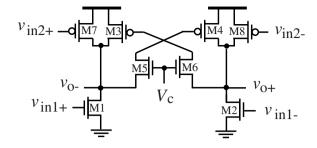

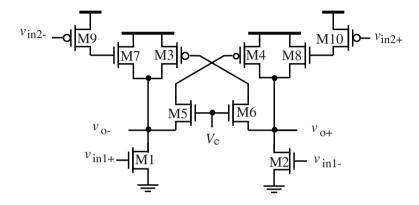

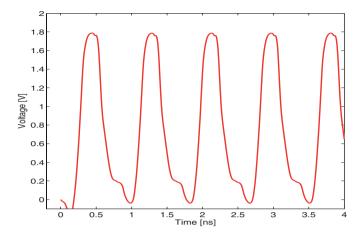

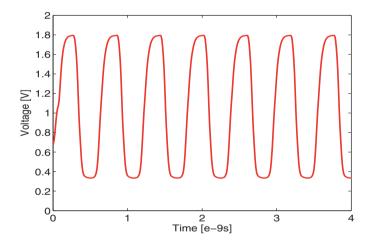

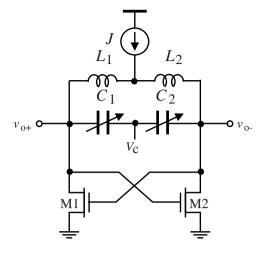

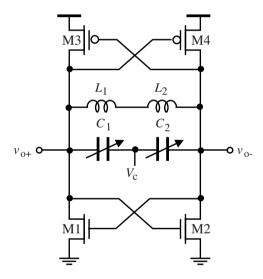

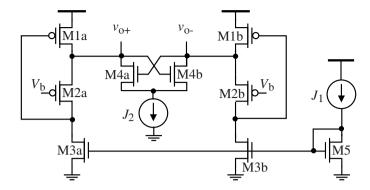

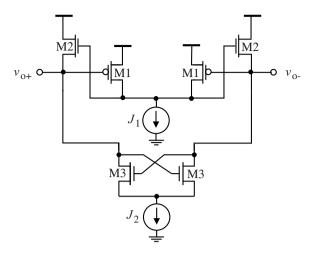

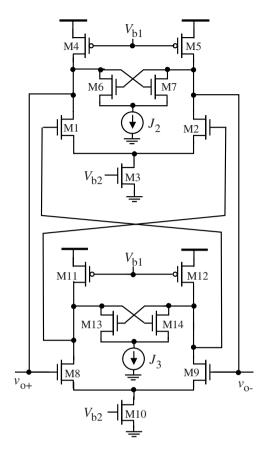

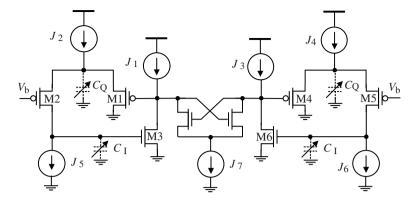

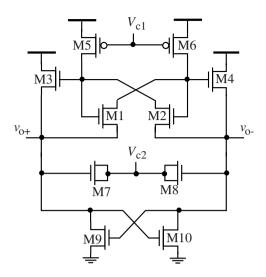

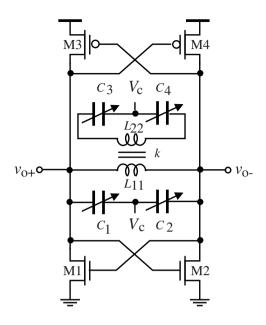

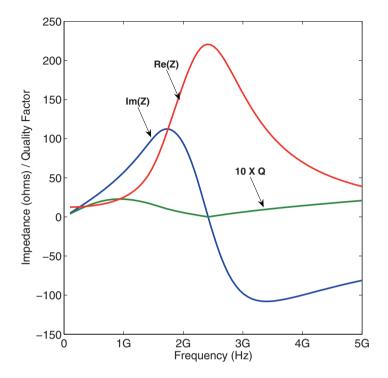

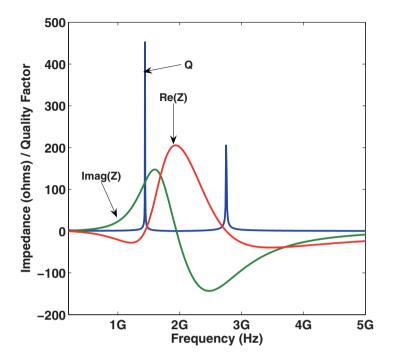

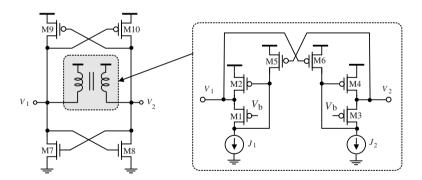

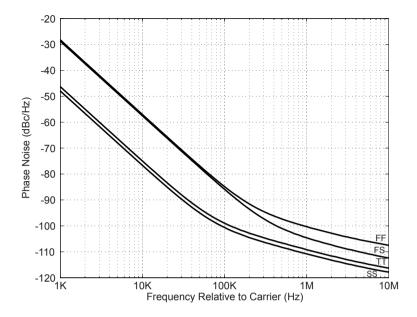

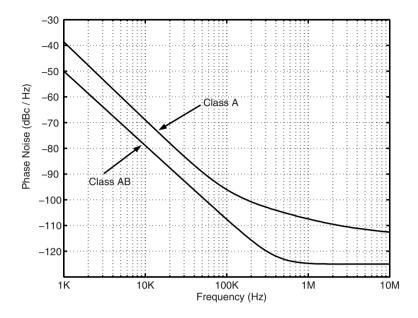

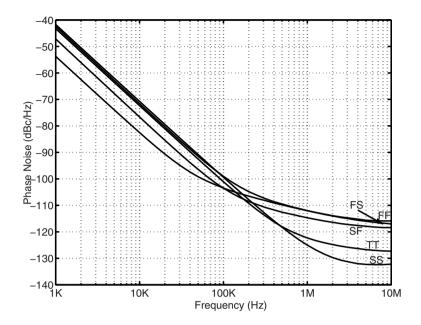

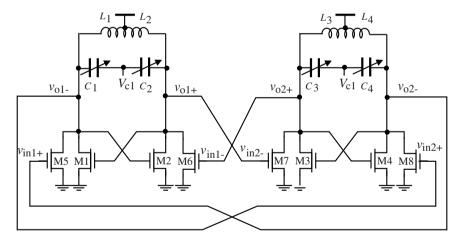

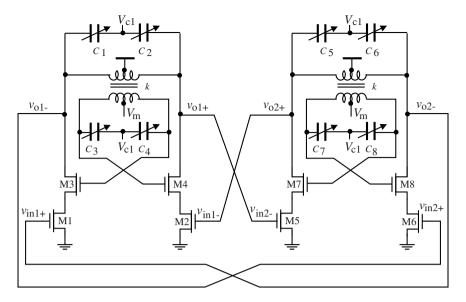

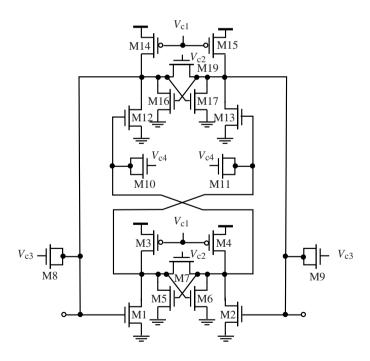

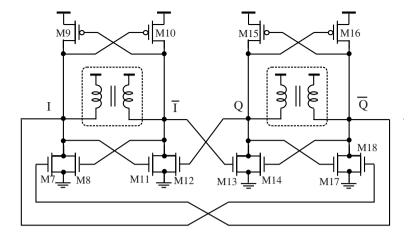

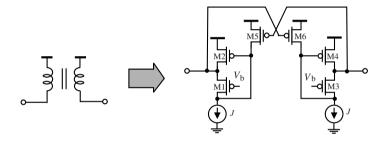

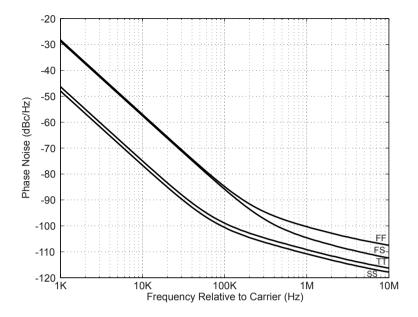

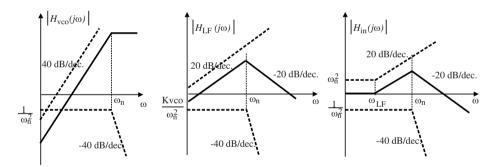

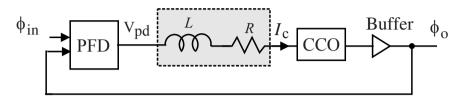

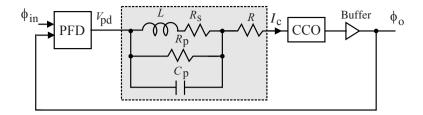

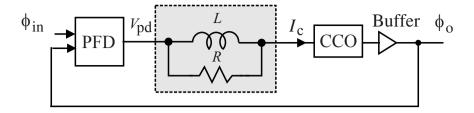

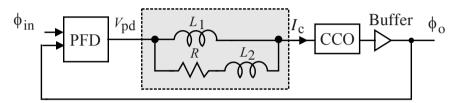

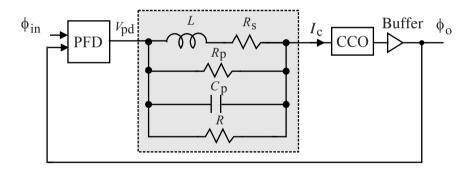

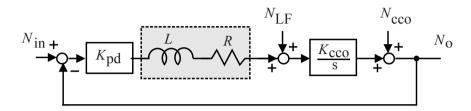

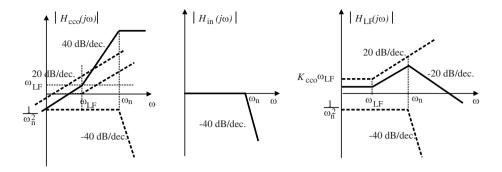

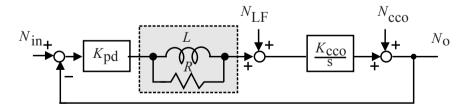

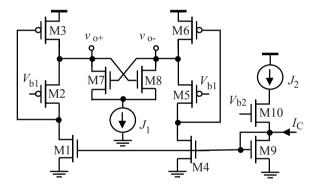

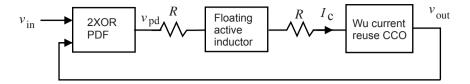

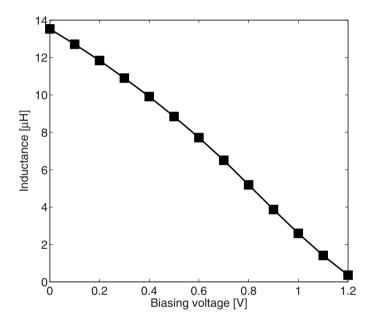

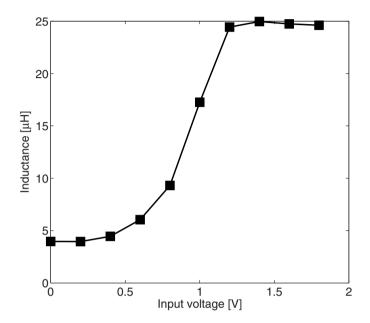

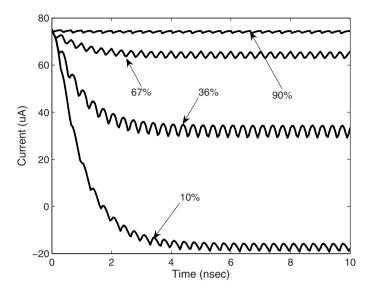

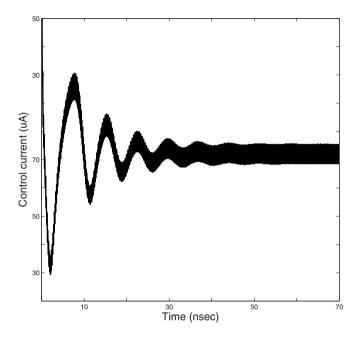

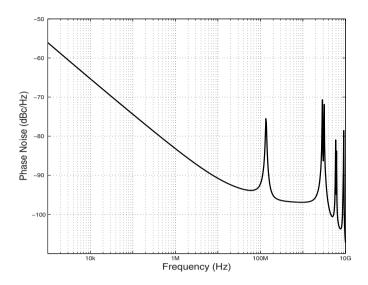

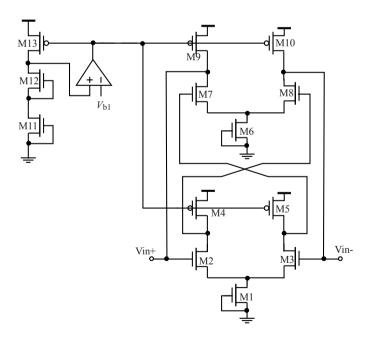

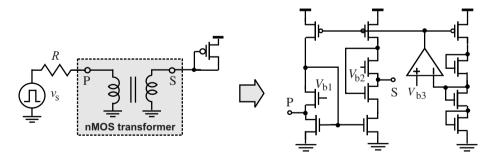

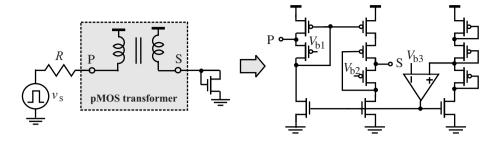

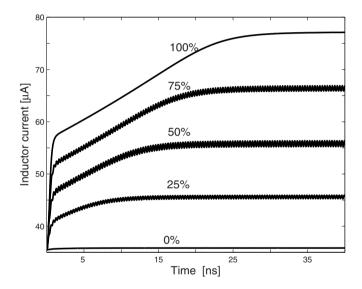

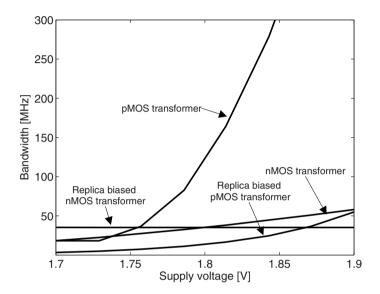

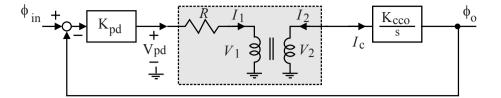

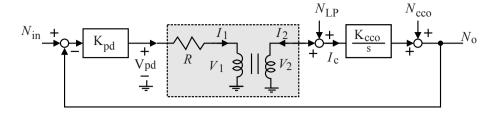

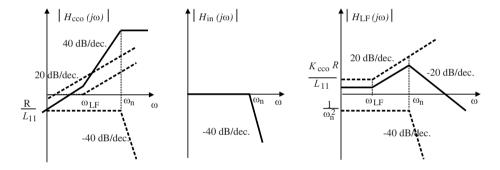

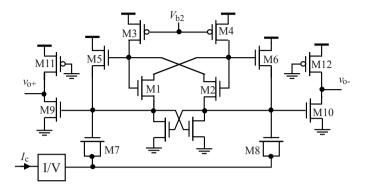

| 2005 | $0.18 \mu \mathrm{m}$                                                                                                | RF Phase shifter                                                                                                                                                                                                                                                                                                                                                                        | 360 degrees                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |