Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller II: Digital and Analog Hardware Interfacing

# Synthesis Lectures on Digital Circuits and Systems

#### **Editor**

Mitchell A. Thornton, Southern Methodist University

## Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller II: Digital and Analog Hardware Interfacing

Douglas H. Summerville 2009

#### Designing Asynchronous Circuits using NULL Convention Logic (NCL)

Scott C. Smith, JiaDi 2009

## Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller I: Assembly Language Programming

Douglas H.Summerville 2009

#### Developing Embedded Software using DaVinci & OMAP Technology

B.I. (Raj) Pawate

#### Mismatch and Noise in Modern IC Processes

Andrew Marshall 2009

### Asynchronous Sequential Machine Design and Analysis: A Comprehensive Development of the Design and Analysis of Clock-Independent State Machines and Systems

Richard F. Tinder 2009

#### An Introduction to Logic Circuit Testing

Parag K. Lala 2008

#### **Pragmatic Power**

William J. Eccles 2008

#### Multiple Valued Logic: Concepts and Representations

D. Michael Miller, Mitchell A. Thornton

#### Finite State Machine Datapath Design, Optimization, and Implementation

Justin Davis, Robert Reese 2007

#### Atmel AVR Microcontroller Primer: Programming and Interfacing

Steven F. Barrett, Daniel J. Pack 2007

#### **Pragmatic Logic**

William J. Eccles 2007

#### **PSpice for Filters and Transmission Lines**

Paul Tobin 2007

#### **PSpice for Digital Signal Processing**

Paul Tobin 2007

#### **PSpice for Analog Communications Engineering**

Paul Tobin 2007

#### **PSpice for Digital Communications Engineering**

Paul Tobin 2007

#### **PSpice for Circuit Theory and Electronic Devices**

Paul Tobin 2007

#### Pragmatic Circuits: DC and Time Domain

William J. Eccles 2006

#### Pragmatic Circuits: Frequency Domain

William J. Eccles 2006

#### Pragmatic Circuits: Signals and Filters

William J. Eccles 2006

# **High-Speed Digital System Design** Justin Davis

2006

# **Introduction to Logic Synthesis using Verilog HDL** Robert B.Reese, Mitchell A.Thornton

2006

#### Microcontrollers Fundamentals for Engineers and Scientists

Steven F. Barrett, Daniel J. Pack 2006

Copyright © 2009 by Morgan & Claypool

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopy, recording, or any other except for brief quotations in printed reviews, without the prior permission of the publisher.

$Embedded\ Systems\ Interfacing\ for\ Engineers\ using\ the\ Freescale\ HCS08\ Microcontroller\ II:$

Digital and Analog Interfacing

Douglas H. Summerville

www.morganclaypool.com

ISBN: 9781608450084 paperback ISBN: 9781608450091 ebook

DOI 10.2200/S00199ED1V01Y200906DCS022

A Publication in the Morgan & Claypool Publishers series SYNTHESIS LECTURES ON DIGITAL CIRCUITS AND SYSTEMS

Lecture #22

Series Editor: Mitchell A. Thornton, Southern Methodist University

Series ISSN

Synthesis Lectures on Digital Circuits and Systems

Print 1932-3166 Electronic 1932-3174

# Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller II: Digital and Analog Hardware Interfacing

Douglas H. Summerville State University of New York at Binghamton

SYNTHESIS LECTURES ON DIGITAL CIRCUITS AND SYSTEMS #22

#### **ABSTRACT**

The vast majority of computers in use today are encapsulated within other systems. In contrast to general-purpose computers that run an endless selection of software, these embedded computers are often programmed for a very specific, low-level and often mundane purpose. Low-end microcontrollers, costing as little as one dollar, are often employed by engineers in designs that utilize only a small fraction of the processing capability of the device because it is either more cost-effective than selecting an application-specific part or because programmability offers custom functionality not otherwise available. *Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller* is a two-part book intended to provide an introduction to hardware and software interfacing for engineers. Building from a comprehensive introduction of fundamental computing concepts, the book suitable for a first course in computer organization for electrical or computer engineering students with a minimal background in digital logic and programming. In addition, this book can be valuable as a reference for engineers new to the Freescale HCS08 family of microcontrollers. The HCS08 processor architecture used in the book is relatively simple to learn, powerful enough to apply towards a wide-range of interfacing tasks, and accommodates breadboard prototyping in a laboratory using freely available and low-cost tools.

In Part II: Digital and Analog Hardware Interfacing, hardware and software interfacing concepts are introduced. The emphasis of this work is on good hardware and software engineering design principles. Device drivers are developed illustrating the use of general-purpose and special-purpose digital I/O interfaces, analog interfaces, serial interfaces and real-time I/O processing. The hardware side of each interface is described and electrical specifications and related issues are considered. The first part of the book provides the programming skills necessary to implement the software in this part.

#### **KEYWORDS**

microcontrollers, embedded computers, computer engineering, digital systems, Freescale HCS08, device drivers, hardware/software interfacing

# Contents

|   | Ackr  | nowledgm  | nentsxiii                                        |

|---|-------|-----------|--------------------------------------------------|

| 1 | Intro | duction t | o the MC9S08QG4/8 Hardware                       |

|   | 1.1   | Input/C   | Output Basics                                    |

|   |       | 1.1.1     | Pin Diagrams 1                                   |

|   |       | 1.1.2     | Memory-Mapped I/O 2                              |

|   |       | 1.1.3     | I/O Synchronization 4                            |

|   |       | 1.1.4     | Device Drivers 5                                 |

|   | 1.2   | A MC      | 9S08QG4/8 Skeleton Program                       |

|   |       | 1.2.1     | System Configuration Registers 6                 |

|   |       | 1.2.2     | Computer Operating Properly (COP) Watchdog 7     |

|   |       | 1.2.3     | Interrupt Vector Table 8                         |

|   |       | 1.2.4     | HCS08 Modes of Operation 9                       |

|   |       | 1.2.5     | Program Skeleton for the MC9S08QG4/8 10          |

|   | 1.3   | Genera    | 1-Purpose Digital I/O                            |

|   |       | 1.3.1     | General Purpose I/O on the MC9S08QG4/8 14        |

|   |       | 1.3.2     | Electrical Specifications 17                     |

|   |       | 1.3.3     | Switch Input Interface 21                        |

|   |       | 1.3.4     | Switch Bounce 24                                 |

|   |       | 1.3.5     | LED Indicators 26                                |

|   |       | 1.3.6     | Emulation of Open-Drain and Tri-State Outputs 32 |

|   | 1.4   | Interru   | pt Synchronization                               |

|   |       | 1.4.1     | HCS08 CPU Interrupt Processing 34                |

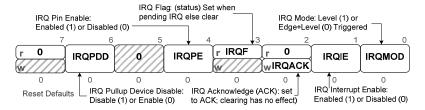

|   |       | 1.4.2     | IRQ Interrupt Pin 35                             |

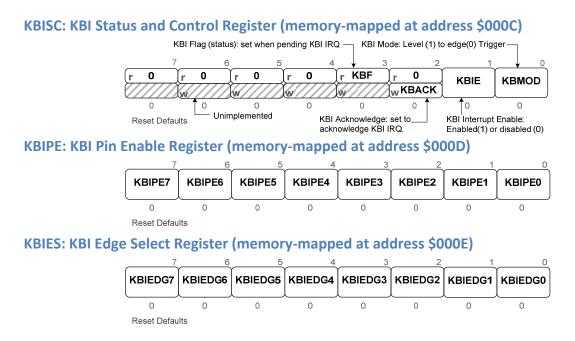

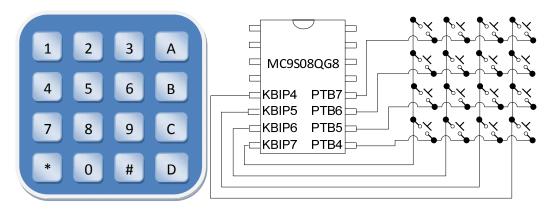

|   |       | 1.4.3     | Keyboard Interrupt 38                            |

|   | 1.5   | Chapte    | r Problems                                       |

#### x CONTENTS

| 2 | Anal  | g Input4                                                                 | 17             |

|---|-------|--------------------------------------------------------------------------|----------------|

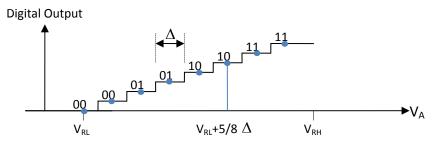

|   | 2.1   | Analog to Digital Conversion                                             | <del>1</del> 7 |

|   |       | 2.1.1 ADC Basics 47                                                      |                |

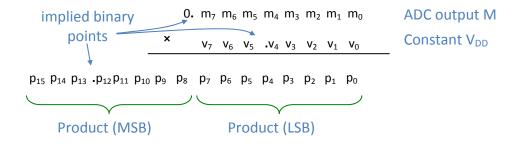

|   |       | 2.1.2 Converting ADC Output to Fixed-Point 48                            |                |

|   | 2.2   | ADC on the MC9S08QG4/85                                                  | 50             |

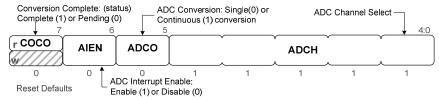

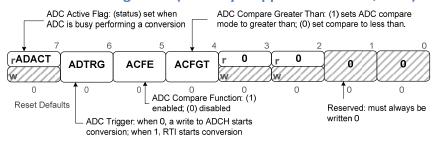

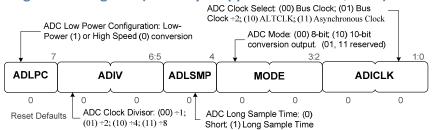

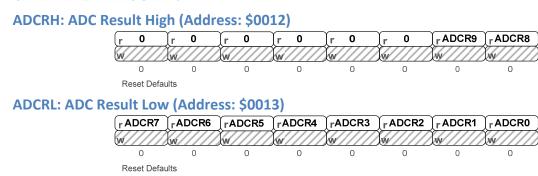

|   |       | 2.2.1 MC9S08QG4/8 ADC I/O Interface Registers 51                         |                |

|   | 2.3   | Driver Examples for the MC9S08QG4/8 ADC                                  | 54             |

|   |       | 2.3.1 Basic 8-Bit Single-Pin Polled I/O Driver 56                        |                |

|   |       | 2.3.2 Basic 10-Bit Single Conversion with Software Selectable Pin 58     |                |

|   |       | 2.3.3 Interrupt-Based 8-Bit Driver 58                                    |                |

|   |       | 2.3.4 Multiple ADC Pin Scanning using Interrupt-Based Driver 61          |                |

|   |       | 2.3.5 8-Bit Polled Driver with Compare Function 63                       |                |

|   |       | 2.3.6 8-Bit Interrupt-Based Driver with Compare Function 64              |                |

|   |       | 2.3.7 8-Bit Interrupt-Based Driver with Hysteresis 65                    |                |

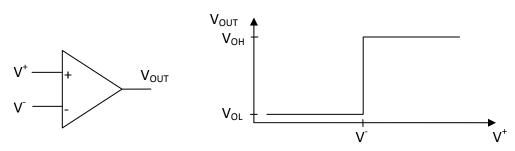

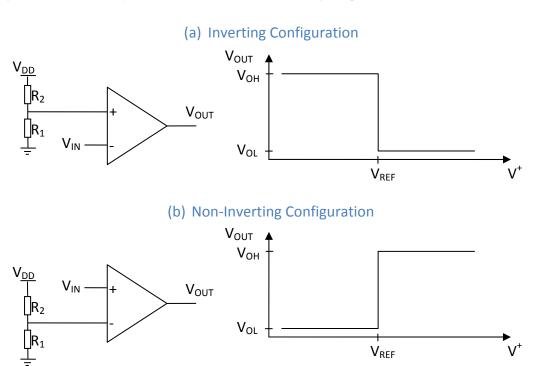

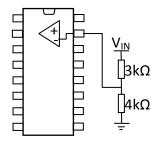

|   | 2.4   | Analog Comparator                                                        | 66             |

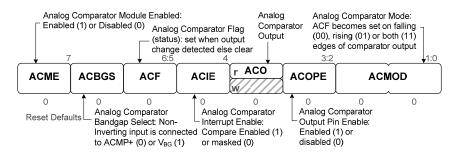

|   | 2.5   | Analog Comparator on the MC9S08QG4/8                                     | 70             |

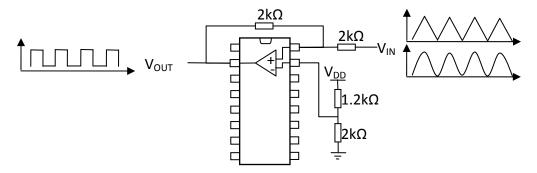

|   | 2.6   | Analog Comparator Driver Examples                                        | 71             |

|   |       | 2.6.1 DC Voltage Monitoring 71                                           |                |

|   |       | 2.6.2 Analog Signal to Digital Waveform Generation 72                    |                |

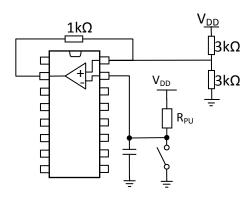

|   |       | 2.6.3 Hardware Switch Debouncing Using the Analog Comparator 73          |                |

|   | 2.7   | Chapter Problems                                                         | 75             |

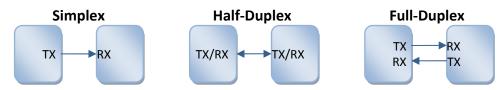

| 3 | Seria | Communication                                                            | 77             |

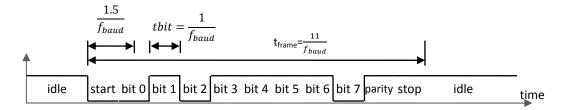

|   | 3.1   | Serial Communication Interface                                           | 77             |

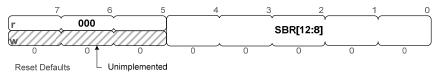

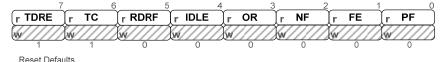

|   |       | 3.1.1 MC9S08QG8 SCI 79                                                   |                |

|   |       | 3.1.2 SCI Driver Examples 84                                             |                |

|   |       | 3.1.3 Polled-I/O Full-Duplex SCI Driver 85                               |                |

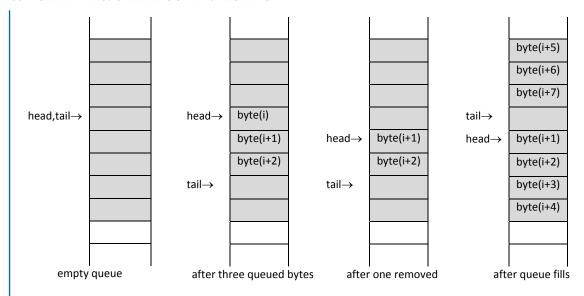

|   |       | 3.1.4 Interrupt-Based Ring-Buffered SCI Simplex (Receive-Only) Driver 87 |                |

|   |       | 3.1.5 Interrupt-Based Ring-Buffered SCI Simplex (Transmit) Driver 91     |                |

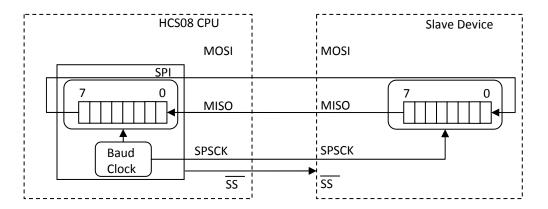

|   | 3.2   | Serial Peripheral Interface (SPI)                                        | €              |

|   |       | 3.2.1 MC9S08GQ8 SPI 95                                                   |                |

|   |       | 3.2.2 MC9S08QG8 SPI Driver Examples 98                                   |

|---|-------|--------------------------------------------------------------------------|

|   |       | 3.2.3 Full-Duplex 8-bit Polled-I/O SPI Driver 99                         |

|   |       | 3.2.4 Simplex 16-bit Polled-I/O SPI Driver 99                            |

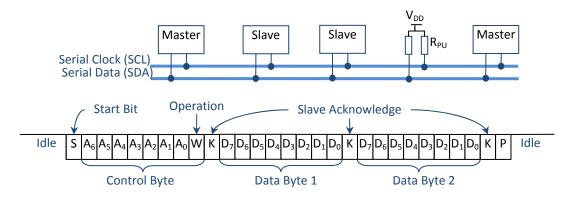

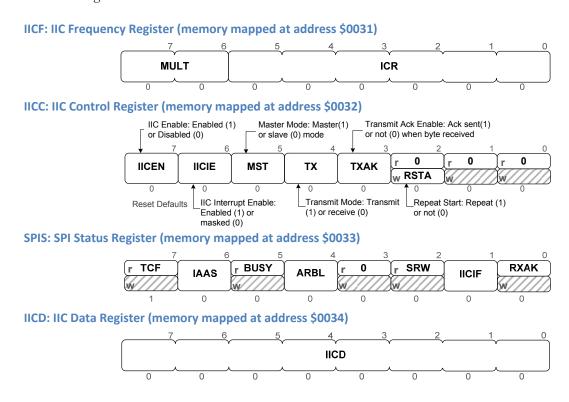

|   | 3.3   | Inter-Integrated Circuit (IIC)                                           |

|   |       | 3.3.1 MC9S08QG8 IIC 102                                                  |

|   | 3.4   | IIC Driver Examples                                                      |

|   |       | 3.4.1 Generic IIC Driver for Devices with Simple Read/Write Behavior 106 |

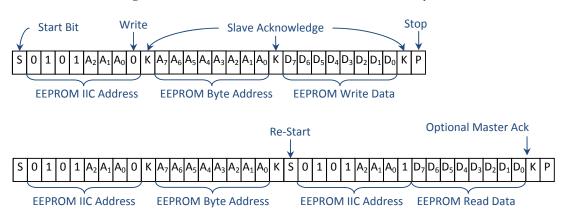

|   |       | 3.4.2 Driver for an Atmel AT24C02B EEPROM Interfaced via the IIC Bus 108 |

|   | 3.5   | Chapter Problems                                                         |

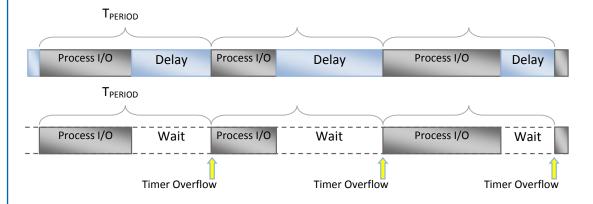

| 4 | Real- | Time I/O Processing                                                      |

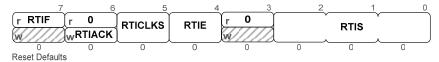

|   | 4.1   | Real-Time Interrupt                                                      |

|   | 4.2   | MC9S08QG4/8 Real-Time Interrupt Module                                   |

|   |       | 4.2.1 Periodic System Wakeup using the Real Time Interrupt 114           |

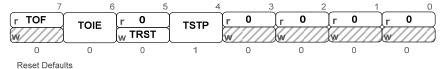

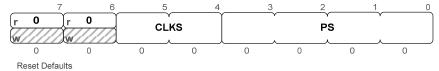

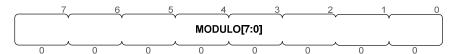

|   | 4.3   | Modulo Timer Module (MTIM)                                               |

|   |       | 4.3.1 Generating Delays with the MTIM 117                                |

|   |       | 4.3.2 Non-blocking Software Delays using the MTIM 118                    |

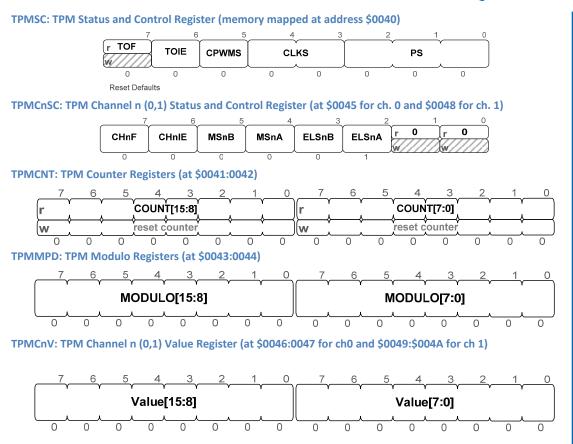

|   | 4.4   | Pulse Width Modulation                                                   |

|   | 4.5   | MC9S08QG4/8 TPM                                                          |

|   |       | 4.5.1 TPM Variable Duty Cycle Driver 122                                 |

|   | 4.6   | Chapter Problems                                                         |

|   | Biogr | aphy                                                                     |

# Acknowledgments

Most of all, I thank Erika, Nicholas, Daniel and Stephanie for their support, encouragement and for tolerating all the weekends and evenings that I spent working on this book instead of being with them. This book is dedicated to you. I also thank all the students who debugged the early versions of this book and whose curiosity, questions and comments helped to shape the presentation of this material.

Douglas H. Summerville August 2009

# Introduction to the MC9S08QG4/8 Hardware

A computer is a device capable of processing data under control of a program. Input and output provide the means by which the computer can receive, exchange, or transmit such data. Without input/output (I/O), even the most powerful computer is all but useless. While general-purpose computers can be used to run a wide range of applications, embedded computers are primarily about I/O processing.

Embedded Systems Interfacing for Engineers using the Freescale HCS08 Microcontroller is a two-part book intended to provide an introduction to hardware and software interfacing concepts. In Part I: Assembly Language Programming, the programmer's model of the HSC08 family of processors is introduced, intended to prepare the engineer with the programming skills necessary to write device drivers and perform basic input/output processing in this part. The emphasis of Part II: Digital and Analog Hardware Interfacing is on hardware and software design concepts necessary to integrate hardware components into the embedded microcomputer system.

#### 1.1 INPUT/OUTPUT BASICS

I/O refers collectively to the hardware and software methods used by a computer to interact with its environment. A computer's I/O unit is a collection of hardware interfaces used by the central processing unit (CPU) to interact with peripheral devices and other computers. An *interface* (or *port*) is a well-defined specification for communication between two devices, including the mechanical, electronic and data format standards. Generally, devices connected to these interfaces interact with people or other systems, or simply sense or control the environment.

#### 1.1.1 PIN DIAGRAMS

The MC9S08QG family of microcontrollers from Freescale Semiconductor feature an easy to learn 8-bit architecture, up to 8 KiB of Flash ROM, up to 512B of RAM, and a rich set of peripherals including an analog to digital convertor, three serial communications interfaces (IIC, SCI and SPI), an analog comparator and pulse width modulator. In addition, these low-cost devices come in a variety of packages, including dual-inline packages that facilitate breadboard prototyping. In addition, low-cost development kits and free development software are available.

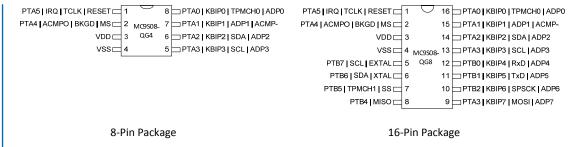

Pin diagrams of the MC9S08QG4 in an 8-pin DIP package and MC9S08QG8 in a 16-pin DIP package are shown in Figure 1.1. These devices come in a variety of other 8 and 16 pin packages. Pins 1 through 4 are identical on both packages; pins 5 through 8 on the MC9S08QG4 are equivalent

Figure 1.1: Device package pin assignments for the MC9S08QG4/8 microcontrollers.

to pins 13 through 16 on the MC9S08QG8.  $V_{DD}$  and  $V_{SS}$  (pins 3 and 4) are the power supply pins (power and ground, respectively). The manufacturer recommends that two separate capacitors be placed across the power pins. A  $10-\mu F$  tantalum capacitor is recommended to provide bulk charge storage and a  $0.1-\mu F$  ceramic bypass capacitor is recommended to suppress high-frequency noise; the latter should be placed as close to the power-supply pins as possible.

All pins other than power supply pins have multiple I/O functions assigned to them. Multiplexing pins in this way is a common technique used with microcontrollers to provide flexibility in assigning functions to pins and minimize unused pins. The system designer can select the functions needed in a particular system and configure the pins accordingly. When multiple I/O functions are enabled on a pin an assigned priority determines which interface uses that pin. For example, if the analog to digital convertor function is enabled on pin 13 (ADC3), that function is given priority over the GPIO interface on that pin (PTA3). This multiplexing approach maximizes the number of peripherals that can be included within a given package size. Since unused interfaces may not result in unused pins, it can also maximize pin utilization.

#### 1.1.2 MEMORY-MAPPED I/O

I/O interfaces can be input only, output only or bidirectional (input and output). Generally, an I/O interface includes of a set of registers through which the CPU can read or write data. These I/O registers can be classified into one of three types: data, control and status. A *data register* is used for exchanging data with the interface, a *control register* is for configuring or controlling the operation of the interface, and a *status register* indicates information about the state or condition of the interface. An I/O interface can include any number and combination of these registers, from a simple I/O interface consisting of a single data register to a complex I/O interface with several data, control and status registers. Some registers are subdivided into individual bits that serve as status, control or data bits individually.

To communicate with the I/O interface, the CPU must have the ability to read and write I/O interface registers. Just as with memory, each of these I/O registers is assigned a unique identifier through which it is addressed by the CPU. These I/O addresses form an address space that can

either be part of the CPU's memory address space or be separate from it. When memory and I/O share the same address space, the CPU is said to use *memory-mapped I/O*; otherwise, it is said to use *separate I/O*. Since memory-mapped I/O interface registers are mapped into the CPU's memory address space, these registers are manipulated by software in the same way as memory bytes, using existing CPU instructions and addressing modes. This allows much flexibility when working with I/O registers, but reduces the amount of the address space that can be mapped to RAM or ROM. With separate I/O, special additional CPU instructions or addressing modes are needed to access I/O registers due to the separation of the two address spaces. The HCS08 CPU uses memory-mapped I/O.

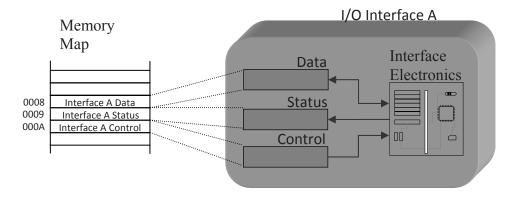

An example of a fictional memory-mapped I/O interface is shown in Figure 1.2. As shown,

Figure 1.2: Illustration of a memory-mapped I/O interface.

the data register has been mapped into the CPU address space at address  $0008_{16}$ , the status register at  $0009_{16}$  and the data register at  $000A_{16}$ . The CPU can read the contents of the data register with a load from address  $0008_{16}$ , for example, or configure a property of the interface by manipulating bits at address  $000A_{16}$ .

Although memory-mapped I/O registers are accessed as though they were memory bytes, they generally do not behave like RAM or ROM. One reason is that the data in an interface register can be changed outside of program control, making its contents volatile (successive loads from the register can return different values). Another reason is that not all I/O registers have both read and write capability. For example, a data register in an input interface might be read-only by software and a store to the associated memory address would have no effect on the contents of the register.

Figure 1.3 shows the memory maps of the MC9S08QG8 and MC9S08QG4 microcontrollers. For both devices, some I/O port registers are mapped in the direct page (addresses \$0000-\$005F) and some are mapped in the high page (\$1800-\$184F). Direct page registers tend to be registers associated with I/O ports that are accessed more frequently by software, while high page registers tend to be registers that are for system configuration and likely to be accessed only once after a

| \$0000<br>\$005F | Memory-Mapped I/O Registers | \$0000<br>\$005F | Memory-Mapped I/O Registers |

|------------------|-----------------------------|------------------|-----------------------------|

| \$0060<br>\$025F | RAM (512B)                  | \$0060<br>\$015F | RAM (256B)                  |

|                  | unmapped                    |                  | unmapped                    |

| \$1800           | Memory-Mapped               | \$1800           | Memory-Mapped               |

| \$184F           | I/O Registers               | \$184F           | I/O Registers               |

|                  | unmapped                    |                  | unmapped                    |

| \$E000<br>\$FFFF | Flash (8KiB)                | \$F000<br>\$FFFF | Flash (4KiB)                |

|                  | MC9S08QG8                   | •                | MC9S08QG4                   |

Figure 1.3: Memory maps of the MC9S08QG8 and MC9S08QG4 microcontrollers.

system reset. Since there are only 256 direct page locations, mapping infrequently used I/O registers to the extended page allows more RAM to be mapped to the direct page.

#### 1.1.3 I/O SYNCHRONIZATION

During program execution, software accesses I/O ports to exchange data with the peripheral devices connected to them. The times at which software accesses the ports will rarely correspond to the times when the I/O device connected to the port is ready to accept or provide data. For example, consider a keypad connected to a microcomputer system via an input port. When a program is ready to accept user input, it reads the port associated with the keypad to determine which key is pressed. If this read does not occur in the interval during which the user is pressing the key, the key press will not be detected. In general, a mechanism is needed to coordinate software accesses to I/O ports with the timing characteristics of the device connected to the port. This coordination is called I/O synchronization. In general, there are three forms of I/O synchronization: polling, real-time synchronization and interrupts.

Polling is the simplest of the three types of I/O synchronization. When performing polled I/O, software repeatedly checks (polls) the status of the device connected to the port to determine if the input or output operation can be performed. Thus, a fundamental requirement for using polled-I/O is the ability to query the state of the device. If a device contains a status register, this status register holds information on the state of the interface or the device; this state is often used for polling. In addition, it is sometimes possible to poll a data register for a particular value that indicates the state of the device. For example, it is possible to determine the state of a push-button switch connected to a general-purpose I/O pin by reading the logic value reflected in the data register associated with the port.

The primary advantage of polling is its simplicity. The main disadvantage of polling is that the CPU is idle while polling; that is, it cannot execute other useful instructions unless they can be included within the polling loop.

Delay synchronization uses software delays to match program timing to I/O timing. This form of synchronization is useful if I/O operations have predictable timing characteristics. For example, suppose a peripheral device can accept data at a maximum rate of 1 byte per millisecond. Since the CPU can write data to the port at a much higher rate that this, synchronization can be achieved by inserting a 1 millisecond delay between subsequent writes to the port. In some cases, the CPU requests data from an I/O device and the device requires a finite amount of time to process the request. An example is an analog to digital convertor, which requires several clock cycles to compute a digital approximation of the analog voltage. In these cases, a fixed delay can be inserted between the request and the load of data from the device, allowing sufficient time for the I/O operation to complete. Delay synchronization is useful when there is no status to poll and when I/O operations have predictable timing characteristics.

Delay synchronization is slightly more complex than polling because of the need to generate accurate software delays, typically using timed software loops. If polling is possible, it is generally easier and more efficient to do. In addition, because the CPU is idle while executing software delay loops, delay synchronization is no more efficient than polling.

Interrupt Synchronization uses the CPU hardware interrupt mechanism to interrupt running programs when an I/O event has occurred. This synchronization mechanism is generally the most efficient since the CPU is interrupted only when I/O processing needs to occur. Hardware support, in the form of integration with the CPU interrupt mechanism, is required as is the need to create an interrupt service routine, which is a special subroutine used to process the I/O. Interrupt synchronization is covered in more detail in Section 1.4.

#### 1.1.4 **DEVICE DRIVERS**

The CPU interacts with I/O interfaces through interface registers, which provide for low-level control of the interface and access to data. When designing programs that access I/O, the embedded systems programmer is more concerned with high-level operations; the low-level interface details are of little concern. For example, the programmer is concerned with what key is being pressed on a keypad and not necessarily with how the keypad is interfaced or what steps are required to obtain the key value from the I/O interface. Having to perform low-level access to I/O interfaces overly complicates the work the programmer must do to access and control the peripheral on the interface. By writing a set of subroutines to manipulate the I/O interface and peripheral, the programmer can subsequently access the peripheral at a higher level of abstraction, without managing the underlying details of how the interface actually works. This set of subroutines is called a device driver.

Device drivers have all of the benefits of modular program development associated with subroutines in general, including code reuse and ease of program maintenance. The device driver provides high-level abstraction that speeds program development because it separates the require-

ments of the application from the specifics of the hardware. This abstraction also allows the same program to work with different types of interfaces and peripherals, as long as the drivers for each interface/peripheral combination provide the same functional abstraction to the program. This abstraction also allows a device of one type to look like another type to software (for example, connect a digital camera to your PC and it looks like a removable hard drive). This is how modern operating systems seamlessly integrate the hardware of different manufacturers and allow different types of devices to be manipulated in similar ways.

Device driver subroutines that use polled I/O can be either *blocking* or *non-blocking*. A blocking subroutine does not return back to the calling program until the I/O operation performed by the subroutine is complete. In a non-blocking subroutine, the subroutine returns an error code if the I/O operation cannot complete, allowing software to continue if possible.

#### 1.2 A MC9S08QG4/8 SKELETON PROGRAM

In addition to device drivers to access I/O and software to manipulate data, a complete program for an embedded microcontroller must include some start-up code to configure the microcontroller after reset as well as perform basic system management required to keep the microcontroller running. Unlike a general-purpose computer, an embedded microcomputer does not always have an operating system that performs these startup and system management functions. The minimal set of such functions necessary to start up and keep a basic MC9S08QG4/8 system running are described in this section. These include configuring system registers, managing the watchdog timer, creating a simple interrupt service routine and programming the interrupt vector table.

#### 1.2.1 SYSTEM CONFIGURATION REGISTERS

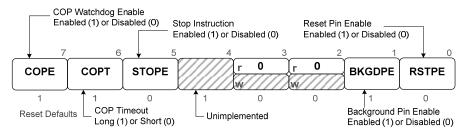

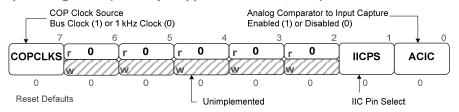

The MC9S08QG4/8 contains two system options registers, SOPT1 and SOPT2, shown in Figure 1.4. These high page registers are write-once registers, meaning that subsequent writes to them have no effect. This prevents erroneous software from altering critical system configuration parameters, which could cause the system to become unstable. This also means that any MC9S08QG4/8 software should always write to these registers once after reset, even if the default values are being used, to prevent such errors from occurring. The default values of the registers after reset are shown below each register in the figure. Because these are I/O registers and not memory, the values returned by a load do not necessarily reflect those last written. When the read and write behavior of a register is different, the read behavior is shown on the top half of each bit and the write behavior on the bottom. For example, software will always read zero for bits 2 through 6 of SOPT2, independent of the values written to these bits.

The configuration bits COPE, COPT, and COPCLKS control the configuration of the computer operating properly (COP) watchdog, which is described in detail in Section 1.2.2. STOPE enables or disables STOP mode. STOP mode is a low power mode that the microcontroller enters upon execution of a STOP instruction. When disabled, execution of a STOP instruction will instead cause an illegal opcode reset.

#### SOPT1: Systems Option Register 1 (memory-mapped at address \$1802)

#### SOPT2: Systems Option Register 2 (memory-mapped at address \$1803)

Figure 1.4: System options registers.

BKGDPE is the background debug pin enable bit. Background debug mode allows software tools to analyze microcontroller operation during software development. Using background debug mode, memory and register contents can be inspected and modified and the CPU can be controlled to implement single-stepping and other debug functions. A single wire debug connection on PTA4 (pin 2) is used by development tools to access and control the microcontroller. When the system in under development, BKGDPE needs to be enabled (BKGDPE=1) for such debugging. When the system is ready for production, if pin 2 is to be used as a general-purpose I/O pin in the final system, the BKGDPE must be disabled.

Reset pin enable (RSTPE) enables the active-low reset function on microcontroller pin 1. When enabled, an active low pulse on pin 1 forces a CPU reset. When RSTPE is disabled, pin 1 can be used as an I/O pin.

IICPS is the pin select configuration bit for the inter-integrated circuit (IIC) module. When the IIC module is enabled, it can be configured to use either pins 6 and 7 or pins 13 and 14 (IIC uses two pins called SDA and SCL). When the IIC module is not being used, the value of IICPS is irrelevant. When set, ACIC (Analog Comparator to Input Capture) enable connects the output of analog comparator module to the input of the timer/pulse-width modulator.

#### COMPUTER OPERATING PROPERLY (COP) WATCHDOG 1.2.2

The computer operating properly (COP) watchdog is a circuit intended to reset the CPU in the event of a software error. The COP watchdog consists of a free-running counter that is configured

to count at a certain rate. If the counter reaches its terminal value, then a system reset is forced. In order to avoid a watchdog reset, software must reset the COP counter periodically.

The COP watchdog is configured via the system options registers, SOPT1 and SOPT2, as described in Section 1.2.1. The COPE (COP Enable) bit of SOPT1 selects whether the COP is enabled or disabled. When disabled, a COP watchdog reset never occurs. When enabled, the COPCLKS bit (bit 7 of SOPT2) selects the clock source to the COP counter controlling the counting rate. This rate can be configured to be the bus clock frequency (COPCLKS=1), which is 4 MHz by default out of reset, or a separate 1 kHz internal clock (COPCLKS=0). The COPT (COP Timeout) bit in SOPT1 selects a short or long timeout period. When the 1 kHz clock is selected as the COP clock source, a short timeout is defined as 32 periods of the clock (32 ms) and a long timeout is defined as 256 clock periods (256 ms). When the bus clock is selected as the COP clock source, a short timeout is defined as 2<sup>13</sup> periods (8.192 ms at 4 MHz) and a long timeout 2<sup>18</sup> periods (0.262 s at 4 MHz). The timeout period is selected depending on system design requirements.

Resetting the COP counter consists of writing any value to the SRS register, which is memory mapped to location \$1800. Embedded software is often structured to have a main loop that repeats forever. In such applications, the reset of the COP counter can be placed somewhere in this main loop such that the counter will be reset once per iteration. As long as the execution time through the loop is shorter than the COP timeout period, this approach will prevent a COP reset unless there is a software error such as an infinite loop. If the code in the main loop includes blocking I/O operations, care should be taken to prevent the COP reset if the blocking time exceeds the COP timeout period. This is usually accomplished by resetting the COP counter in the I/O polling or delay loop.

#### 1.2.3 INTERRUPT VECTOR TABLE

Resetting the microcontroller is a way of initializing it to a known operating state. Upon reset, I/O registers default to their reset states (usually disabled) and the I bit in the CCR is set to block maskable interrupts, allowing the programmer to configure the system to a safe state before interrupts can occur. An interrupt is an asynchronous event that can occur at almost any time while the microcontroller is running. When either a reset or interrupt occurs, the CPU needs an address in memory (a vector) at which it should start executing. In the case of a reset, the vector is the address of the start of the system code; in the case of an interrupt, the vector is the address of the start of the interrupt service routine that will deal with the request.

The CPU maintains a table of reset and interrupt vectors that must be correctly initialized at the time the microcontroller is programmed. Table 1.1 lists each vector location and its associated interrupt or reset source. Each vector requires two bytes of storage to hold an address. Note that the addresses in the table are not contiguous; for example, there are no vectors located from \$FFD2 to \$FFD5. These locations of the vector table are reserved for future use.

| <b>Table 1.1:</b> Interrupt/Reset Vector Locations of the |                                                |  |  |  |  |

|-----------------------------------------------------------|------------------------------------------------|--|--|--|--|

|                                                           | MC9S08QG4/8.                                   |  |  |  |  |

| Vector Address                                            | Interrupt/Reset Source                         |  |  |  |  |

| \$FFD0:FFD1                                               | Real Time Interrupt (RTI)                      |  |  |  |  |

| \$FFD6:FFD7                                               | Analog Comparator (ACMP)                       |  |  |  |  |

| \$FFD8:FFD9                                               | Analog to Digital Converter (ADC)              |  |  |  |  |

| \$FFDA:FFDB                                               | Keyboard Interrupt (KBI)                       |  |  |  |  |

| \$FFDC:FFDD                                               | Inter-Integrated Circuit (IIC)                 |  |  |  |  |

| \$FFDE:FFDF                                               | Serial Communications Interface (SCI) Transmit |  |  |  |  |

| \$FFE0:FFE1                                               | Serial Communications Interface (SCI) Receive  |  |  |  |  |

| \$FFE2:FFE3                                               | Serial Communications Interface (SCI) Error    |  |  |  |  |

| \$FFE4:FFE5                                               | Serial Peripheral Interface (SPI)              |  |  |  |  |

| \$FFE6:FFE7                                               | Modulo Timer (MTIM) Overflow                   |  |  |  |  |

| \$FFF0:FFF1                                               | Timer/Pulse Width Modulator (TPM) Overflow     |  |  |  |  |

| \$FFF2:FFF3                                               | Timer/Pulse Width Modulator (TPM) Channel 1    |  |  |  |  |

| \$FFF4:FFF5                                               | Timer/Pulse Width Modulator (TPM) Channel 0    |  |  |  |  |

| \$FFF8:FFF9                                               | Low Voltage Detect Reset                       |  |  |  |  |

| \$FFFA:FFFB                                               | Interrupt Request Pin (IRQ) Reset              |  |  |  |  |

| \$FFFC:FFFD                                               | Software Interrupt (SWI)                       |  |  |  |  |

| \$FFFE:FFFF                                               | CPU Reset                                      |  |  |  |  |

#### **HCS08 MODES OF OPERATION** 1.2.4

The HCS08 CPU has 4 primary modes of operation: run, wait, stop and active background. The run mode is the primary mode of operation in which the CPU sequences instructions and peripherals operate normally. Run mode is entered upon power-on reset when the BKGD pin is high. In run mode, instruction sequencing begins at the address in the reset vector. Active background mode is a debugging mode that is useful when developing and testing new software. In this mode, the CPU is in a suspended state and debugging commands are accepted over the BKGD pin. These debugging commands allow for inspection and modification of registers or memory locations and for single stepping instructions. Active background mode can be entered in several ways, including the CPU BKGD instruction and holding the BKGD pin low during power-on reset.

Wait mode is entered upon execution of the WAIT instruction. In this mode, the CPU ceases instruction sequencing and is not clocked, lowering power consumption. In wait mode, peripherals operate normally and any interrupt request automatically wakes-up the CPU and places it back into run mode. Since an interrupt is required to wake the CPU, the CPU always resumes instruction sequencing with the interrupt service routine corresponding to the source of the interrupt that woke the CPU. After the service routine completes, instruction sequencing resumes after the WAIT instruction that put the CPU in wait mode. The WAIT instruction always clears the I mask in the

CCR to ensure that interrupts are enabled. At least one interrupt source must be enabled to wake the CPU or it will wait indefinitely.

There are three levels of stop mode provided in the CPU. In all levels, the CPU and most peripheral devices are shut down to minimize power consumption. Stop mode is entered by executing the STOP instruction and the stop level is determined by system configuration register settings. Stop level 1 provides maximum power savings and requires a power-on reset to restart the system. Stop level 2 is an intermediate level that maintains the state of RAM and I/O pins. A real-time interrupt can restart the system from stop level 2. Stop level 3 (the default level) maintains the same system state as stop level two in addition to the CPU register contents.

#### 1.2.5 PROGRAM SKELETON FOR THE MC9S08QG4/8

Code Listing 1.1 is a complete *program skeleton* for the MC9S08QG4/8. A program skeleton is a template that outlines program structure and contains code that is common to all programs. Lines 4 through 6 define the memory locations within the memory map. On all members of the microcontroller family, the start of RAM is at address \$0060. This is defined using an equate pseudo-op on line 4. The RAM size and start of flash ROM, however, differ for various microcontroller family members and the equates for RAMSIZE and FLASHSTART on lines 5 and 6 must be programmed accordingly. Lines 7 through 13 contain equate pseudo-ops that define the memory-map locations of individual I/O registers described previously.

Lines 17 through 24 contain system configuration constants that are use by the initialization code to configure the microcontroller. Constant CLOCKFREQ is a 2-bit value used to establish the operating frequency of the microcontroller clock (bus clock). These two bits are written to the ICSSC2 register in the system initialization code. COPSET is used to select the desired COP setting; a value of 0 disables the COP, while values of 2 and 3 enable it and select a short or long timeout period, respectively. STOPEN, when set to 1, enables the STOP instruction, which allows programs to direct the CPU to enter stop mode. BKGDPEN, when set, enables the BKGD function on pin 2; this must be enabled during system development when debugging, but disabled if other functions on pin 2 are to be used (PTA4 or analog comparator output ACMPO). RSTPEN is used to enable the active low reset function on pin 1; this must be cleared if the reset function is to be disabled or if the IRQ or PTA5 functions are needed on this pin. The constant SOPT1VAL combines the COPSET, STOPEN, BKGDPEN and RSTPEN constants to form the value that needs to be written to system options register 1. Similarly, SOPT2VAL is the value that is written to system options register 2.

Line 28 contains the ORG pseudo-op for RAM. All variable definitions intended for RAM should follow this ORG. Line 33 contains a similar pseudo-op defining the location of flash memory. The first instructions following this ORG on line 33 are system initialization instructions that should not be changed without careful consideration. Lines 34 through 37 program the write-once system options registers.

The onboard clock generator is not very accurate and can be off by a considerable extent. Software can tweak the clock frequency by writing a trim value to the ICSTRIM system configuration

```

;------

; Memory Map Definitions

$0060

RAMSTART equ

RAMSIZE equ 256 ; this is 256 on QG4, 512 on QG8

FLASHSTART equ $f000 ; this is $F000 on QG4, $E000 on QG8

WATCHDOG equ $1800 ; location of watchdog's food dish

VECTOR TBL equ $ffd0 ; start of interrupt vector table

SOPT1 equ

$1802 ; system options registers

10 SOPT2

equ

$1803

11 ICSTRIM equ $003A ; clock trim register

12 ICSSC2 equ $0039 ; clock status and control register

13 ICSTRIMVAL equ $FFAF ; factory programmed clock trim value

14 ;-----

15 ; System Configuration OPtions

16 :-----

77 CLOCKFREQ equ 0 ; 0 - 8MHz; 1 - 4MHz; 2 - 2MHz; 3 - 1MHz

18 COPSET equ 3 ; 0- disable COP, 2- enable with short timeout

19 ; 3- enable with long timeout

20 STOPEN equ 1 ; 0- disable stop instruction, 1- enable

21 BKGDPEN equ 1 ; 0- disable BKGD function, 1- enable

22 RSTPEN equ 0 ; 0- disable RST pin, 1- enable

23 COPSENCE (6 | STOPENCE 4 | PROPERIOR 1 | PROPERIOR 2 | PROPER

23 SOPT1VAL equ (COPSET<<6| STOPEN<< 4 | BKGDPEN<<1 | RSTPEN )

24 SOPT2VAL equ $00 ;COP clk is 1kHz, IICPS and ACIC at defaults

26 ; Variable data section: ORGed to start of RAM

27 ;-----

orq

RAMSTART

29 ExampleVar: ds.b 1

31 ; Code Section: ORGed to start of flash

32 ;-----

org FLASHSTART

lda #SOPT1VAL

34 MAIN:

; configure system options

sta SOPT1

lda #SOPT2VAL

sta SOPT2

;load factory programmed trim value

lda ICSTRIMVAL

;write to clock trim register

sta ICSTRIM

mov #(CLOCKFREQ<<6),ICSSC2 ;set internal clock frequently

ldhx #(RAMSTART+RAMSIZE) ;initialize the stack pointer</pre>

#(CLOCKFREQ<<6), ICSSC2 ; set internal clock frequency

42

txs

```

Code Listing 1.1: Skeleton Program for the MC9S08GQ4/8 (*Continues*).

```

43 MAININIT: nop

; program initialization

cli

; enable interrupts after system init

45 MAINLOOP: nop

; main loop body

47 FEEDTHEDOG: sta WATCHDOG

; reset the watchdog

bra MAINLOOP

49 ;-----

50 ; Constant Section: Not ORGed, follows code section in flash

52 NULL

dc.b 0

;-----

; Dummy ISR to catch spurious interrupts

;-----

56 DUMMY ISR: bra DUMMY ISR ; stay here to force COP reset

;-----

58;

Interrupt Vector Table

org VECTOR TBL

dc.w DUMMY ISR ; $FFD0:FFD1 RTI

ds.w 2

; $FFD2:FFD5 ***Reserved***

dc.w DUMMY ISR ; $FFD6:FFD7 ACMP

dc.w DUMMY ISR ; $FFD8:FFD9 ADC Conversion

dc.w DUMMY ISR ; $FFDA:FFDB KBI Interrupt

dc.w DUMMY_ISR ; $FFDC:FFDD IIC

dc.w DUMMY_ISR; $FFDE:FFDF SCI Transmit

dc.w DUMMY_ISR; $FFE0:FFE1 SCI Receive

dc.w DUMMY_ISR; $FFE2:FFE3 SCI Error

dc.w DUMMY_ISR; $FFE4:FFE5 SPI

dc.w DUMMY_ISR; $FFE6:FFE7 MTIM Overflow

ds.w 4

; $FFE8:FFEF ***Reserved***

dc.w DUMMY ISR ; $FFF0:FFF1 TPM Overflow

dc.w DUMMY ISR; $FFF2:FFF3 TPM Channel 1

dc.w DUMMY_ISR; $FFF4:FFF5 TPM Channel 0

ds.w 1 ; $FFF6:FFF7 ***Reserved***

dc.w DUMMY ISR ; $FFF8:FFF9 Low Voltage Detect

dc.w DUMMY_ISR ; $FFFA:FFFB IRQ

dc.w DUMMY_ISR; $FFFC:FFFD SWI

dc.w MAIN

; $FFFE:FFFF Reset

```

Code Listing 1.1: (Continued) Skeleton Program for the MC9S08GQ4/8.

register. Freescale has defined flash memory location \$FFAF as the predefined location of the trim value necessary to trim the clock to 4 MHz out of reset. Each microcontroller has a trim value stored in memory at the factory, and many development tools compute and reprogram this value each time flash is programmed. Lines 38 and 39 use this value to trim the system clock. Subsequently, the MOV instruction on line 40 sets the clock divisor bits in the system clock status and control register to define the desired bus clock frequency.

Lines 41 and 42 initialize the stack pointer to point to the last byte in RAM. The NOP instruction on line 43 is a placeholder for the main initialization code needed to set up the microcontroller peripherals and global variables for a specific application. This usually involves calling driver initialization routines to initialize peripherals and setting global variables to their initial values. Line 44 enables interrupts by clearing the I mask bit in the CCR. This must be done after driver initialization to ensure that no interrupts are triggered until peripherals are properly configured.

The NOP on line 45 is another placeholder. It should be replaced with the body of the main program loop that is repeated for as long as the microcontroller is running. Once per iteration of this main loop, on line 47, the COP watchdog counter is reset. If the execution time of the main loop could exceed the configured watchdog timeout period, the watchdog may need to be at other locations within the main loop body. Following this is the branch back to the beginning of the main program loop that causes the loop to repeat forever.

Program constants, drivers and subroutines follow immediately after the main program loop and do not require an ORG pseudo-op. A default interrupt service routine, DUMMY\_ISR, is provided to initialize interrupt vectors that are not in use. This helps to catch spurious interrupts caused by misconfiguration of a peripheral. The BRA DUMMY\_ISR instruction keeps the CPU at the ISR until the COP resets the processor, allowing the system to safely recover from the error. Good programming will ensure that this never happens.

Line 60 begins the definition of the interrupt vector table. All interrupt vectors not assigned to a specific service routine are initialized with a DC. W pseudo-op that points the vector to DUMMY\_ISR. The CPU reset vector, at \$FFFE: \$FFFF, represents the address of the first instruction executed after a CPU reset. This is programmed to point to label MAIN, which corresponds to the line of the first instruction of the program.

#### 1.3 GENERAL-PURPOSE DIGITAL I/O

General purpose digital I/O, the simplest form of I/O in an embedded system, allows software to directly control the logic levels on microcontroller pins. In addition to introducing general purpose digital I/O concepts, this section describes the electrical characteristics of the MC9S08QG microprocessor family.

A general-purpose input port uses microcontroller pins as digital inputs. A load from a data register associated with the input port will return the logic values on the pins. A general-purpose output port uses the pins as digital outputs, controlled via a store to the data register associated

with interface. A general-purpose input/output port uses the pins as either digital inputs or outputs, configurable through a control register called a *data direction register*.

#### 1.3.1 GENERAL PURPOSE I/O ON THE MC9S08QG4/8

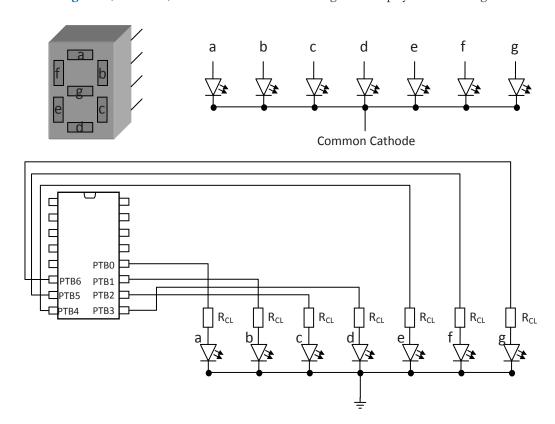

MC9S08QG4/8 pins labeled PTBi and PTAi correspond to pins that can be used as general-purpose I/O (GPIO) pins. These are organized into two ports: Port A and Port B. Port A is associated with 6 pins, labeled PTAO-PTA5, and port B is associated with 8 pins, PTBO-PTB7. The signals for port B are not available on an 8-bit package. Each of these GPIO pins can be independently configured as input or output, except input only PTA5 and output only PTA4.

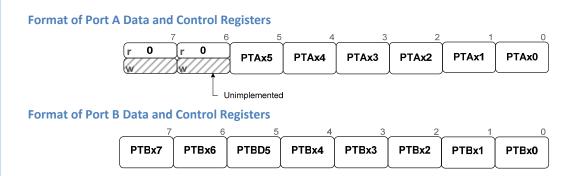

Figure 1.5 illustrates the format of the Port A and Port B data and control registers. Pin PTBx

Figure 1.5: General purpose I/O port register formats.

can be individually configured as input or output via bit x in the I/O configuration register called the Port B Data Direction Register (PTBDD), which is memory-mapped to address \$0003. When PTBDD bit x is a '1', the pin is an output driven by the logic value in bit x of the Port B Data Register (PTBD), which is memory-mapped to \$0002. When PTBDD bit x is 0, pin PTBx is configured as an input. A read from bit x of PTBD returns the current logic value on the input pin. Table 1.2 summarizes the configuration options for port B as well as the value returned on a read from the port B data register. Note that a read from the port B data direction register always returns the current pin direction. The Port A operation is similar. Port A data (PTAD) is memory mapped to \$0000, while its direction

| <b>Table 1.2:</b> Summary of configuration settings for PTB.         |   |                     |                                  |  |  |  |

|----------------------------------------------------------------------|---|---------------------|----------------------------------|--|--|--|

| PTBDDx PTBDx Pin Configuration Read from Port B Data Register (PTBD) |   |                     |                                  |  |  |  |

| 0                                                                    | - | Input               | Returns logic value on input pin |  |  |  |

| 1                                                                    | 0 | Output driving low  | Returns 0                        |  |  |  |

| 1                                                                    | 1 | Output driving high | Returns 1                        |  |  |  |

register (PTADD) is mapped to \$0001. Note that pin PTA4 is an output-only pin and pin PTA5 is an input only pin, and there is no pin PTA6 or PTA7.

Table 1.3 summarizes the configuration registers associate with GPIO ports A and B. Note

| Table 1.3: Summary of GPIO port data and configuration registers. |         |                  |                                                                                                                                           |  |

|-------------------------------------------------------------------|---------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| Register                                                          | Address | Reset Default    | Description                                                                                                                               |  |

| Port A Data (PTAD)                                                | \$0000  | \$00             | Port A I/O data register.                                                                                                                 |  |

| Port A Data Direction<br>(PTADD)                                  | \$0001  | \$00 (input)     | Port A I/O direction control. PTA4 is always output (clearing PTADD4 has no effect); PTA5 is always input (setting PTADD5 has no effect). |  |

| Port A Pull-up Enable (PTAPE)                                     | \$1840  | \$00 (disabled)  | Port A pull-up resistor enable. PTAPEx=1 enables pull-up resistor on pin PTAx.                                                            |  |

| Port A Slew Rate Control (PTASE)                                  | \$1841  | \$3F (enabled)   | Port A slew rate control; PTASEx=1 enables slew rate limiting on pin PTAx.                                                                |  |

| Port A Drive Strength (PTADS)                                     | \$1842  | \$00 (low drive) | High drive strength control; high drive strength enabled on pin PTAx when PTADSx=1.                                                       |  |

| Port B Data (PTBD)                                                | \$0002  | \$00             | Port B I/O data register.                                                                                                                 |  |

| Port B Data Direction (PTBDD)                                     | \$0003  | \$00 (input)     | Port B I/O direction control.                                                                                                             |  |

| Port B Pull-up Enable<br>(PTBPE)                                  | \$1844  | \$00 (disabled)  | Port B pull-up resistor enable. PTBPEx=1 enables pull-up resistor on pin PTBx.                                                            |  |

| Port B Slew Rate Control (PTBSE)                                  | \$1845  | \$FF (enabled)   | Port B slew rate control; PTBSEx=1 enables slew rate limiting on pin PTBx.                                                                |  |

| Port B Drive Strength (PTBDS)                                     | \$1846  | \$00 (low drive) | High drive strength control; high drive strength enabled on pin PTBx when PTBDSx=1.                                                       |  |

that when a pin is configured as input, a write to port data register has no effect on the pin, but the value written is stored in the data register and will become the value driving the pin if its direction is changed from input to output. This allows the logic value on the pin to be correctly configured before the pin is enabled as an output, preventing glitches.

An internal pull-up resistor for each GPIO pin can be selectively enabled in an I/O control register called a Pull-Up Enable register. This internal pull-up eliminates the need to include an external resistor on the pin when one is required. Pull-ups are automatically disabled, regardless of the pull-up register setting, when the pin is configured as output.

The GPIO ports on the MC9S08QG4/8 microprocessors also have configuration registers that control drive strength and slew rate. Slew rate defines how quickly an output can change logic levels. Because fast switching outputs can cause higher electromagnetic interference (EMI), enabling slew rate control on a pin reduces how quickly it can switch, thereby reducing EMI. Drive strength control defines how much current the pin can source or sink. Under low drive strength, an output pin can source or sink a current of up to approximately 5-10 mA; when high drive strength is enabled, the maximum current increases to approximately 15-20 mA.

**Example 1.1.** Write the instructions necessary to configure all 8 pins of Port B as input pins, with internal pull-up registers enabled.

**Solution:** Since the entire port is being used, configuration data can be directly written to the data direction register and pull-up enable register. Since PTBPE is an extended address, MOV cannot be used.

```

Answer:

1 PTBD

equ

$02

;port B data register

equ $03

;port B direction control register

PTBDD

3 PTBPE

equ

$1844

;port B pull-up control register

4

INITSW:

lda #$FF

; enable pull-ups on all Port B pins

5

sta PTBPE

6

mov #$00,PTBDD

; configure all port B pins as input pins

```

**Example 1.2.** Write the instruction(s) necessary to configure pin PTA1 as an output pin with low drive strength and slew rate control on.

**Solution:** Since a single pin is being configured, it is required to modify only one bit of each control registers. BCLR and BSET are useful for registers in the direct page; general masking must be used for high page registers. To make PTA1 an output pin, its bit in PTADD must be set. PTASE1=1 to turn on slew rate control, and PTADS1=0 for low drive strength.

```

Answer:

$0000

1

PTAD

equ

;port B data register

2

PTADD

$0001

; PTB direction control register

equ

3

PTAPE

$1840

;PTB pull-up control register

equ

;port A slew control enable

4

PTASE

equ

$1841

5

PTADS

equ

$1842

;port A drive strength control

6

7

INITSW:

bclr 1,PTAD

;write initial 1 to Port A data register

8

lda

PTADS

9

and #%11111101

10

sta

PTADS

;PTA1 drive strength low

11

PTASE

lda

12

#%0000010

ora

13

sta

PTASE

;slew rate control on for PTA1

bset 1,PTADD

; configure PTA1 as output

14

```

Example 1.3. Write the instructions necessary to configure pins PTB3, PTB2, PTB1, and PTB0 as input pins with pull-ups enabled, without changing the configuration of the other PTB pins. Solution: Since the entire Port is not being configured, data cannot be directly written to the data direction register or pull-up enable register. Thus, masking operations should be used.

Solution: Since the entire Port is not being configured, data cannot be directly written to the data direction register or pull-up enable register. Thus, masking operations should be used.

```

Answer:

PTBD

equ

$0002

;port B data register

1

2

PTBDD

equ $0003

;PTB direction control register

3

PTBPE

equ

$1844

;PTB pull-up control register

4

ONE_MASK

equ

%00001111

;ONE mask of pins being configured

5

ZERO_MASK

equ

%11110000

; ZERO mask of pins being configured

6

7

INITSW:

lda

PTBPE

;load current PTBPUE configuration

8

ora #ONE_MASK ;set bits 3-0 (enable pull-ups)

9

sta PTBPE ; write back modified configuration

10

lda PTBDD

;load current DDR configuration

11

and #ZERO_MASK ; clear bits 3-0 (configure as inputs)

sta PTBDD

;write back modified DDR configuration

12

```

#### **ELECTRICAL SPECIFICATIONS** 1.3.2

The electrical specifications, found in the MC9S08QG8/MC9S08QG4 Data Sheet, define the electrical, timing and temperature conditions under which the device can be safely operated. When integrating hardware into the microcontroller-based system, these specifications must be considered to ensure proper operation of the device. The device specifications include Absolute Maximum Ratings that define the limits to which the device can be exposed without causing permanent damage to it. The Functional Operating Range defines the valid voltage, current, timing and temperature ranges under which the device will function correctly. The functional operating range is always within the absolute maximum ratings. While it is possible to subject the device to conditions outside the functional range, but within the absolute maximum ratings, the device is not guaranteed to operate properly.

Table 1.4 lists the absolute maximum ratings for the MC9S08QG4/8, obtained from the device data sheet. All voltages are relative to the supply voltage ground, VSS, which is 0V or ground by definition. The supply voltage  $V_{\rm DD}$  must not be allowed to exceed  $+3.8{\rm V}$  or  $-0.3{\rm V}\,{\rm V}_{\rm SS}$ . The Digital Input Voltage characteristic, VIN, defines the allowable voltage range on all pins (other than  $V_{\rm DD}$  and  $V_{\rm SS}$ ). The voltage on any pin must not exceed  $V_{\rm DD} + 0.3 \rm V$  or drop lower than  $V_{\rm SS} - 0.3 \rm V$ . This is especially important to consider when interfacing external analog circuits connected to these pins and in mixed-voltage digital systems. If the voltage on a data pin should exceed VIN, current will flow into (or out of) the pin and can damage the device; an appropriate current limiting circuit

| Table 1.4: Absolute maximum ratings for the MC9S08QG4/8. |                  |                 |      |  |  |

|----------------------------------------------------------|------------------|-----------------|------|--|--|

| Rating                                                   | Symbol           | Value           | Unit |  |  |

| Supply voltage                                           | $V_{DD}$         | -0.3 to +3.8    | V    |  |  |

| Maximum current into VDD                                 | $I_{DD}$         | 120             | mA   |  |  |

| Digital input voltage                                    | V <sub>IN</sub>  | -0.3 to VDD+0.3 | V    |  |  |

| Instantaneous maximum current per port pin               | I <sub>D</sub>   | ± 25            | mA   |  |  |

| Storage temperature range                                | T <sub>STG</sub> | –55 to 150      | °C   |  |  |

must be used to prevent this. The maximum power supply current is 120mA (parameter  $I_{\rm DD}$ ); this includes all current being sourced by microcontroller pins in addition to that used to operate the CPU and peripherals. The instantaneous maximum current,  $I_{\rm D}$ , for data pins is  $\pm$  25 mA.

Table 1.5 lists selected electrical characteristics in the functional operating range for the MC9S08QG4/8 devices. The functional operating range for the MC9S08QG4/8 specifies that

| Table 1.5: Selected electrical characteristics for the MC9S08QG4/8. |                        |                      |                    |      |  |  |

|---------------------------------------------------------------------|------------------------|----------------------|--------------------|------|--|--|

| Parameter                                                           | Symbol                 | Minimum Value        | Maximum Value      | Unit |  |  |

| Supply Voltage                                                      | <b>V</b> <sub>DD</sub> | 1.8                  | 3.6                | V    |  |  |

| Input High Voltage                                                  | $V_{IH}$               | .7×V <sub>DD</sub>   | -                  | V    |  |  |

| Input Low Voltage                                                   | V <sub>IL</sub>        | -                    | .3×V <sub>DD</sub> | V    |  |  |

| Digital Input Hysteresis                                            | $\mathbf{V}_{HYS}$     | $0.06 \times V_{DD}$ | -                  | V    |  |  |

| Input Leakage Current (per pin)                                     | I <sub>IN</sub>        | -                    | 1.0                | μΑ   |  |  |

| Internal Pull-up Resistance                                         | $R_{PU}$               | 17.5                 | 52.5               | kΩ   |  |  |

| Output High Voltage                                                 | V <sub>OH</sub>        | Depends on           | OH (see text)      | V    |  |  |

| Output High Current (sum, all pins)                                 | I <sub>OHT</sub>       | -                    | 60                 | mΑ   |  |  |

| Output Low Voltage                                                  | V <sub>OL</sub>        | Depends on           | IOH (see text)     | V    |  |  |

| DC Injection Current (per pin)                                      | I <sub>IC</sub>        | -0.2                 | 0.2                | mA   |  |  |

| DC Injection Current (all pins)                                     | I <sub>IC</sub>        | -5                   | 5                  | mA   |  |  |

V<sub>DD</sub> can be in the range from 1.8V to 3.6V. Many of the electrical specifications for the device depend on the supply voltage, temperature, and other operating conditions, often in a nonlinear way. The values listed in Table 1.5 are typical values for moderate operating conditions. If more precise values are required, the engineer needs to consult the device datasheet or perform laboratory measurements.

For digital input pins, the values of interest include the input high and low voltages,  $V_{\rm IH}$  and  $V_{\rm IL}$ , input leakage current  $I_{\rm IN}$ , input hysteresis  $V_{\rm HYS}$ , and the internal pull-up resistance  $R_{\rm PU}$ . The values listed are typical and may be different at the extremes of the functional operating range.  $V_{\rm IH}$  represents the range of voltages on an input pin that are interpreted as logic high. This range is defined by .7 $V_{\rm DD}$  on the low end and is limited by the maximum operating value for the device

$(V_{\rm DD}+0.3 \rm V)$  on the high end. Likewise, the range of voltages that will be interpreted as logic low inputs is bounded by  $V_{\rm SS}$  (0V) on the low end and  $.35 V_{\rm DD}$  on the high end. The input leakage current is the current that flows into and input pin. Though small, this current must be taken into account if large pull-up or pull-down resistors are used on inputs as it will cause a measurable voltage drop across the resistor. Usually, the maximum input leakage is the parameter of interest. Input hysteresis defines the minimum change in input voltage necessary to toggle the input logic level. For slowly changing inputs, a large hysteresis is desirable to prevent rapid input switching due to noise. Finally, each internal pull-up resistor has a value between 17.5 kOhm and 52.5 kOhm; the actual value depends on the value of the supply voltage; graphs of  $R_{\rm PU}$  versus  $V_{\rm DD}$  are provided in the data sheet.

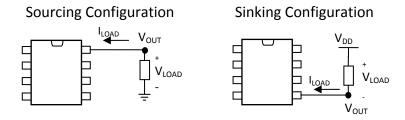

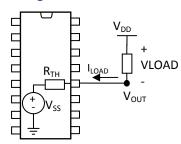

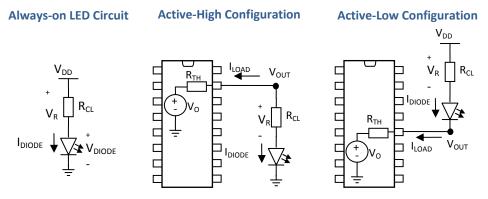

A load on an output pin can be configured in a *sourcing configuration* or *sinking configuration*, as shown in Figure 1.6. In the figure,  $V_{LOAD}$  is the voltage drop across the load,  $V_{OUT}$  is the output

Figure 1.6: Illustration of sourcing and sinking output load configurations.

voltage at the pin (relative to ground) and  $I_{LOAD}$  is the load current, which by convention is defined as going into the pin.

For output pins, the parameters of interest are the output high and low voltages and the output current. The parameters  $V_{OH}$  and  $V_{OL}$  specify the voltage at the output pin when logic high and low values are output, respectively. In the sourcing configuration, the load is connected across the output pin and ground and  $V_{LOAD} = V_{OUT}$ . When the pin outputs a logic 1,  $V_{LOAD} = V_{OH}$  and  $I_{LOAD}$  is negative (current flows out of the pin), thus the pin is said to be sourcing current. Because the pin is acting as a non-ideal voltage source, the actual value of  $V_{OH}$  depends on the output current  $I_{LOAD}$ . In the sourcing configuration, when the pin outputs a logic low,  $V_{LOAD} = V_{OUT} = 0V$  and  $I_{LOAD} = 0$  mA.

In the sinking configuration, the load is connected across the output pin and  $V_{\rm DD}$  and  $V_{\rm LOAD} = V_{\rm DD} - V_{\rm OUT}$ . When the pin outputs a logic 1,  $V_{\rm OUT} = V_{\rm DD}$  and both  $V_{\rm LOAD}$  and  $I_{\rm LOAD}$  are zero. When the pin outputs a logic 0,  $V_{\rm LOAD} = V_{\rm DD} - V_{\rm OL}$  and  $I_{\rm LOAD}$  is positive (current flows into the pin), thus the pin is said to be sinking current.  $V_{\rm OL}$  depends on the amount of current the pin is sinking.

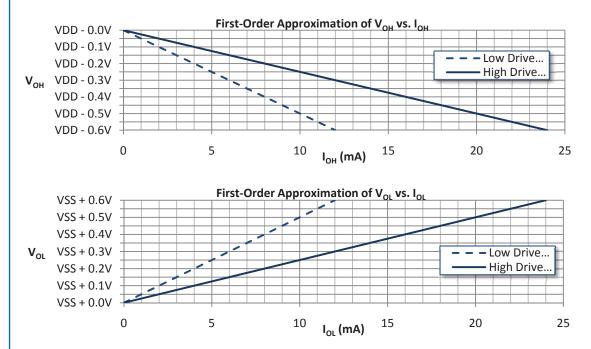

$V_{\mathrm{OH}}$  and  $V_{\mathrm{OL}}$  both depend on  $I_{\mathrm{LOAD}}$ ,  $V_{\mathrm{DD}}$ , device operating temperature and the drive strength configuration of the output pin. For the sinking configuration,  $V_{\mathrm{OL}}$  increases from  $V_{\mathrm{SS}}$  as  $I_{\mathrm{LOAD}}$  increases; for the sourcing configuration,  $V_{\mathrm{OH}}$  decreases (from  $V_{\mathrm{DD}}$ ) as  $I_{\mathrm{LOAD}}$  increases. The

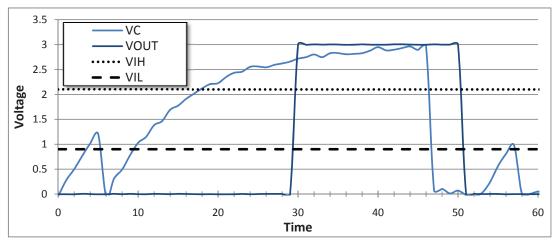

data sheet provides graphs of the relationship for  $V_{\rm DD}=3.0 {\rm V}$ , but these can only be used as a starting point for approximation since actual values depend on many factors. A first-order approximation based on these graphs is shown in Figure 1.7. These approximations were made for  $V_{\rm DD}=3.0 {\rm V}$  at

Figure 1.7: V<sub>OH</sub> versus I<sub>OH</sub> and V<sub>OL</sub> versus I<sub>OL</sub> curves for low and high drive strengths.

room temperature. The output high voltage characteristic shows the difference in voltage  $V_{\rm OH}$  from its ideal value  $V_{\rm DD}$  for the sourcing configuration, while the output low voltage characteristic shows the value of  $V_{\rm OL}$  for the sinking configuration. Thus, both plots characterize the deviation from the ideal output voltage level. Clearly, as the load current increases in both configurations, the output voltage deviates increasingly from its ideal.

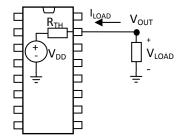

A model of this relationship is an ideal voltage source with a series resistor. The resulting Thevenin equivalent models of the output pin in sourcing and sinking configurations are shown Figure 1.8.  $R_{TH}$  is the Thevenin series resistance, which can be obtained from the slope of the V-I curves above. From the figure,  $R_{TH}$  is approximately 50 Ohms for low drive strength and 25 Ohms for high drive strength. For either configuration,  $V_{LOAD} = V_{DD} - I_{LOAD} \times R_{TH}$ .

Note that there is a maximum combined  $I_{OH}$  parameter,  $|I_{OHT}|$ , of 60 mA and a maximum total  $I_{OL}$ ,  $|I_{OLT}|$ , of 60 mA. This means that the sum of the load currents sourced for all output high pins must not exceed 60 mA. Similarly, the sum of all sinking load currents must not exceed 60 mA. The single pin limit is 25 mA, defined in the absolute maximum ratings.

#### **Sourcing Pin Model**

#### **Sinking Pin Model**

Figure 1.8: Thevenin equivalent circuit models for VOL and VOH.

The following are additional guidelines to consider when using the general-purpose I/O ports:

- Unused GPIO pins should never be left floating (that is, have no external circuit driving the pin to V<sub>DD</sub> or V<sub>SS</sub>). A floating input pin has an indeterminate voltage level that can cause excess internal current consumption. Unused GPIO pins should be configured as inputs with internal pull-ups enabled, or configured as output pins driving either a '1' or '0'.

- If external pull-down resisters are used, internal pull-up resisters must be disabled; otherwise, a voltage divider is formed and the input voltage may not represent a valid input high or input low.

- If glitches are a consideration for the circuit connected to an output pin, write the initial logic value desired to the data register before configuring the data direction register as output.

#### 1.3.3 SWITCH INPUT INTERFACE

One of the simplest input sources is the mechanical switch input. A two-terminal mechanical switch is fashioned from two conductors that can be in one of two states: closed (in contact) or open (not in contact). While there are many types of switches available incorporating a variety of physical mechanisms to actuate the switch (temperature, motion, etc.), their integration into a microcomputer-based system is generally the same. Thus, while the focus of this section is on the integration of human-actuated switches, the same principles apply to other switch types.

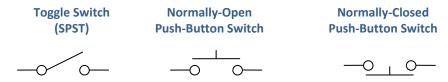

Two types of simple mechanical switches are toggle switches and momentary switches. A toggle switch is set to the open or closed position and remains in that position until changed. A momentary switch has a normal state (open or closed) which is the state of the switch when there is no mechanical action; the switch is in the opposite state as long as the mechanical action lasts. The schematic symbols for common switches are shown in Figure 1.9. A human-actuated momentary switch is call a push-button switch.

Figure 1.9: Schematic symbols for common mechanical switches.

Figure 1.10: Switch input interface circuit configurations.

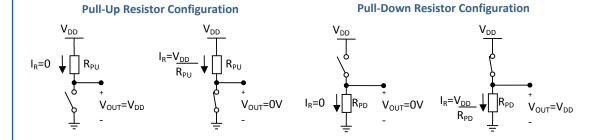

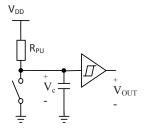

A switch by itself cannot provide a digital input source for general-purpose input. Instead, the switch must be included in a circuit that can convert the open and closed states of the switch into high and low logic levels. This is accomplished using a pull-up or pull-down resistor in series with the switch, as shown in Figure 1.10. When the switch is open in the pull-up resistor circuit, there is almost no current through the resistor (recall that there is the small leakage current,  $I_{IL}$ , drawn by the microcontroller input pin). Therefore, there is almost no voltage drop across the resistor and  $V_{OUT} \approx V_{DD}$ , resulting in a high logic output. When the switch is closed,  $V_{OUT}$  has a direct path to ground ( $V_{OUT} = 0V$ ), resulting in a low-logic output; the purpose of the pull-up resistor in this case is to limit the current to  $I = V_{DD}/R_{PU}$ . The pull-down configuration works in a similar way, except that the logic levels are reversed. Generally, it is desirable to have as high a resistance for  $R_{PU}$  or  $R_{PD}$  as possible to limit wasted power when the switch is closed. The main limiting factor to using high resistance values is microcontroller input pin leakage current, which can cause a voltage drop across the resistor when the switch is open. This voltage drop must be limited to be well within the valid range for  $V_{IH}$  or  $V_{IL}$ , depending on the situation. This is addressed in the chapter problems.

When a momentary switch is used, the interface circuit is an active-high configuration if the logic level on the microcontroller pin is high when the switch is actuated. An active low configuration is one in which a logic low is on the microcontroller input pin when the switch is actuated. If the pull-up resistor switch configuration is used, then the internal pull-up resistor can be used instead of the external resistor; the resulting circuit functions in the same manner but eliminates one external circuit component. On the other hand, if the pull-down configuration is used, the pull-up resistor

must be disabled or a voltage divider will be formed, resulting in an intermediate voltage input when the switch is open, which can lead to erroneous circuit operation.

The software side of the interface is implemented with a device driver. The device driver can implement different functionality depending on the needs of the software that will use the switch input. In addition, the device driver can perform some processing of the input before it is returned to the requesting programs. This is illustrated in Code Listing 1.2. Lines 1-4 contain pseudo-ops used to define the memory-mapped I/O port locations as well as the pin number the interface is for, which minimizes code changes if the need to change the port or input pin used arises. These EQU pseudoops also make the code easier to read and understand and allow the code to be easily ported to other HCS08-based microcomputers, which might map the port registers to different addresses. INITSW is the driver initialization subroutine, which must be called from within the driver initialization section of the main program. INITSW uses masking operations to configure the pin as an input with internal pull-ups enabled. The OR-mask for the pin is formed by the assembler expression #(1<<SWPIN), which results in a mask with a single 1 in bit position SWPIN. This expression is computed by the assembler and does not result in additional instructions being generated.

```

PTBD equ $02 ;port B data register

pTBDD equ $03 ;PTB direction control register

pTBPE equ $1844 ;PTB pull-up control register

SWPIN equ 3 ;defines the pin that switch is on

;-----

6 INITSW: psha

; callee save

bclr SWPIN, PTBDD ; only change setting for this pin

lda PTBPE ;enable internal pull-up resistor

ora \#(1 \le SWPIN); using an OR mask

sta PTBPE ;write back modified PTBPE value

;callee restore