Bert Serneels Michiel Steyaert

A CS P

Analog Circuits And Signal Processing

# Design of High Voltage xDSL Line Drivers in Standard CMOS

# DESIGN OF HIGH VOLTAGE XDSL LINE DRIVERS IN STANDARD CMOS

# ANALOG CIRCUITS AND SIGNAL PROCESSING SERIES

## Consulting Editor: Mohammed Ismail. Ohio State University

#### Titles in Series:

#### ULTRA LOW POWER CAPACITIVE SENSOR INTERFACES

Bracke, W., Puers, R. (et al.)

ISBN: 978-1-4020-6231-5

#### BROADBAND OPTO-ELECTRICAL RECEIVERS IN STANDARD CMOS

Hermans, C., Steyaert, M.

ISBN: 978-1-4020-6221-6

# CMOS MULTICHANNEL SINGLE-CHIP RECEIVERS FOR MULTI-GIGABIT OPTICAL DATA COMMUNICATIONS

Muller, P., Leblebici, Y.

ISBN: 978-1-4020-5911-7

#### SWITCHED-CAPACITOR TECHNIQUES FOR HIGH-ACCURACY FILTER AND ADC...

Quinn, P.J., Roermund, A.H.M.v.

ISBN: 978-14020-6257-5

#### LOW-FREQUENCY NOISE IN ADVANCED MOS DEVICES

von Haartman, M., Östling, M.

ISBN: 978-1-4020-5909-4

# CMOS SINGLE CHIP FAST FREQUENCY HOPPING SYNTHESIZERS FOR WIRELESS MULTI-GIGAHERTZ APPLICATIONS

Bourdi, Taoufik, Kale, Izzet

ISBN: 978-1-4020-5927-8

#### ANALOG CIRCUIT DESIGN TECHNIQUES AT 0.5V

Chatterjee, S., Kinget, P., Tsividis, Y., Pun, K.P.

ISBN-10: 0-387-69953-8

# IQ CALIBRATION TECHNIQUES FOR CMOS RADIO TRANCEIVERS

Chen, Sao-Jie, Hsieh, Yong-Hsiang

ISBN-10: 1-4020-5082-8

## FULL-CHIP NANOMETER ROUTING TECHNIQUES

Ho, Tsung-Yi, Chang, Yao-Wen, Chen, Sao-Jie

ISBN: 978-1-4020-6194-3

# THE GM//ID DESIGN METHODOLOGY FOR CMOS ANALOG LOW POWER

#### INTEGRATED CIRCUITS

Jespers, Paul G.A.

ISBN-10: 0-387-47100-6

# PRECISION TEMPERATURE SENSORS IN CMOS TECHNOLOGY

Pertijs, Michiel A.P., Huijsing, Johan H.

ISBN-10: 1-4020-5257-X

#### CMOS CURRENT-MODE CIRCUITS FOR DATA COMMUNICATIONS

Yuan, Fei

ISBN: 0-387-29758-8

# RF POWER AMPLIFIERS FOR MOBILE COMMUNICATIONS

Reynaert, Patrick, Steyaert, Michiel

ISBN: 1-4020-5116-6

ISBN: 1-4020-4638-3

# ADVANCED DESIGN TECHNIQUES FOR RF POWER AMPLIFIERS Rudiakova, A.N., Krizhanovski, V.

CMOS CASCADE SIGMA-DELTA MODULATORS FOR SENSORS AND TELECOM del Río, R., Medeiro, F., Pérez-Verdú, B., de la Rosa, J.M., Rodríguez-Vázquez, A.

ISBN: 1-4020-4775-4

# SIGMA DELTA A/D CONVERSION FOR SIGNAL CONDITIONING

Philips, K., van Roermund, A.H.M.

Vol. 874, ISBN: 1-4020-4679-0

#### CALIBRATION TECHNIQUES IN NYOUIST A/D CONVERTERS

van der Ploeg, H., Nauta, B.

Vol. 873, ISBN: 1-4020-4634-0

# ADAPTIVE TECHNIQUES FOR MIXED SIGNAL SYSTEM ON CHIP

Fayed, A., Ismail, M.

Vol. 872, ISBN: 0-387-32154-3

# WIDE-BANDWIDTH HIGH-DYNAMIC RANGE D/A CONVERTERS

Doris, Konstantinos, van Roermund, Arthur, Leenaerts, Domine

Vol. 871, ISBN: 0-387-30415-0

# METHODOLOGY FOR THE DIGITAL CALIBRATION OF ANALOG CIRCUITS AND SYSTEMS: WITH CASE STUDIES

Pastre, Marc, Kayal, Maher

Vol. 870, ISBN: 1-4020-4252-3

# HIGH-SPEED PHOTODIODES IN STANDARD CMOS TECHNOLOGY

Radovanovic, Sasa, Annema, Anne-Johan, Nauta, Bram

Vol. 869, ISBN: 0-387-28591-1

# Design of High Voltage xDSL Line Drivers in Standard CMOS

By

# **BERT SERNEELS**

KU Leuven, Belgium

and

# **MICHIEL STEYAERT**

KU Leuven, Belgium

| A C.I.P. Catalogue record for this book is available from the Library of Congress.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| ISBN 978-1-4020-6789-1 (HB)<br>ISBN 978-1-4020-6790-7 (e-book)                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| ISBN 976-1-4020-0790-7 (C-000K)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Published by Springer,<br>P.O. Box 17, 3300 AA Dordrecht, The Netherlands.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| www.springer.com                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Printed on acid-free paper                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| All Rights Reserved © 2008 Springer Science + Business Media B.V.  No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. |  |  |  |  |

# **Preface**

TODAY, the worldwide DSL market penetration has surpassed all other forms of broadband access technologies. However, still less than 5% of the world's phone lines are connected to DSL networks. At over 173 million DSL subscribers, as of September 2006, the majority of the world remains thus "unconnected". The opportunity of DSL is to reuse the billions of available twisted pairs of the classical plain old telephone service (POTS) to offer a triple play of high-speed Internet, voice over IP (VOIP) and multichannel television to your home.

The Discrete MultiTone (DMT) modulation was developed to provide bitrates close to the Shannon limit for the lossy transmission medium. In this modulation technique, the used bandwidth is divided into several carriers, spaced at 4.3125 kHz. Each carrier is modulated by a quadrature amplitude modulation. A large disadvantage of this technique is the high Crest Factor (CF) of the signals in the time domain, requiring linear amplifiers for a broad range of input signal amplitudes. This results in line drivers with very low efficiencies.

It is known that the Self-Oscillating Power Amplifier (SOPA) is a highly efficient line driver for xDSL applications. However, in the nano-electronic era, the line driver remains more than ever the major bottleneck for lowering the cost and power of the xDSL modem. The low supply voltages coming from nanometer technologies increase the current density in the line driver for a constant output power. This results in a low efficiency and reliability problems.

To solve these low voltage issues, high voltage design techniques are discussed in this book using the principle of stacking standard nanometer devices. Two realisations are analysed to demonstrate the feasibility of this principle. A first high voltage driver is implemented in a standard 2.5 V 0.25  $\mu m$  CMOS technology. Although the supply voltage of the high voltage driver is set at three times the nominal supply voltage, none of the transistors in the circuit is stressed by applying too large voltages, resulting in reliable operation and guaranteed minimum lifetime of operation described by the foundry.

### VI Preface

An output swing of 6.46 V at a frequency of 10 MHz is measured over a 50  $\Omega$  load. With the second high voltage driver, the boundaries of the stacking principle are even further explored. The chip is implemented in a standard 1.2 V 130 nm CMOS technology. With five stacked transistors and a supply voltage of 5.5 V an output swing of 4.2 V at a frequency of 40 MHz is measured over a 4  $\Omega$  load with an efficiency of 79%.

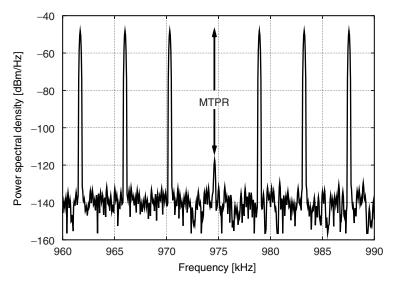

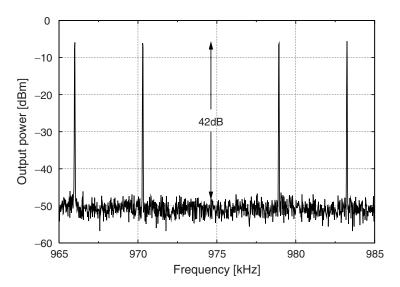

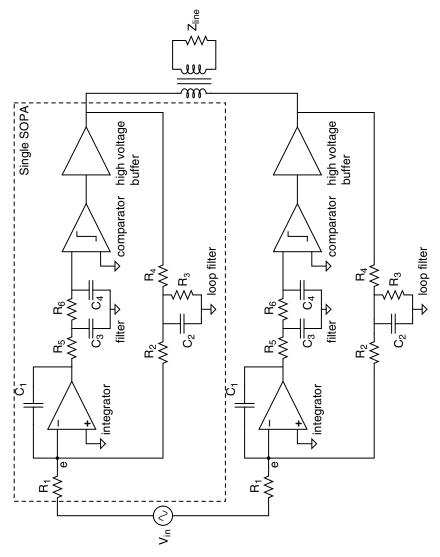

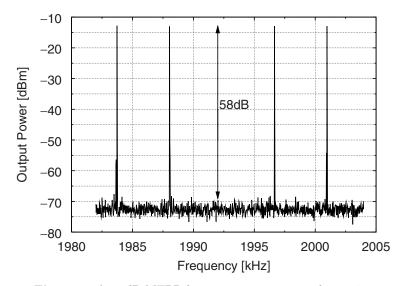

To prove the usefulness of this stacking principle, a high voltage driver is integrated in the SOPA architecture, which leads to a fully integrated high voltage line driver. Again, two test chips were developed in a standard 1.2 V 130 nm CMOS technology to materialize this concept. The first, zeroth order, SOPA complies with the aDSL-Lite specification with its 1.1 MHz bandwidth and 42 dB Missing Tone Power Ratio (MTPR). The efficiency is 40%. The second, first order, SOPA faces the two challenges of line drivers in wireline communications: increasing the signal's bandwidth while maintaining a high efficiency. The circuit complies with the aDSL2+ specifications. A MTPR of 58 dB is reached for a DMT signal with a CF of 15 dB. The efficiency for driving a 100 mW aDSL2+ signal is 42%.

Heverlee August 2007 Bert Serneels Michiel Steyaert

# List of Abbreviations and Symbols

# Abbreviations

ADC Analog-to-Digital Converter

aDSL Asymmetric Digital Subscriber Loop

AFE Analog Front-End

AM Amplitude Modulation

AMI Alternate-Mark Inversion

AWG American Wire Gauge

BER Bit-Error Rate

CAD Computer Aided Design

CF Crest Factor

CMOS Complementary Metal-Oxide-Semiconductor

CO Central Office

CPE Customer Premises Equipment DAC Digital-to-Analog Converter

DC Direct Current

DFE Digital Front-End

DIDF Dual Input Describing Function

DMT Discrete MultiTone modulation

DSL Digital Subscriber Line

DSP Digital Signal Processing

ESD Electrostatic Discharge

FEXT Far-End Crosstalk

FFT Fast Fourier Transform

G-Lite less performing ADSL-Lite

GBW Gain Bandwidth

HCD Hot Carrier Degradation

$\mathrm{HD}_2$  Second-order Harmonic Distortion Term  $\mathrm{HD}_3$  Third-order Harmonic Distortion Term  $\mathrm{HDSL}$  High-speed Digital Subscriber Line

HDTV High Definition Television

# VIII List of Abbreviations and Symbols

HPF High-Pass Filtering IC Integrated Circuits

${

m IM}_2$  Second-order Intermodulation Distortion Product  ${

m IM}_3$  Third-order Intermodulation Distortion Product

IP<sub>3</sub> Third-order Intercept Point

ISDN Integrated Service Digital Network

ISP Internet Service Provider

ITU-T International Telecommunications Union -

Telecommunications standardization sector of ITU

ITRS International Technology Roadmap for Semiconductors

LD Line Driver

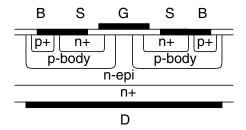

LDDMOS Laterally Double Diffused MOS

LDMOS Laterally Diffused MOS

LPF Low-Pass Filtering

MIM Metal-Insulator-Metal

MOSFET MOS Field Effect Transistor

MTPR Missing Tone Power Ratio

NEBS Network Exploitation Board Specifications

NEXT Near-End Crosstalk

NOS Non-Overlapping Switching Optical Network Unit ONU OSR Over Switching Ratio Peak-to-Average-Ratio PAR. **PCB** Printed Circuit Board PON Passive Optical Network POTS Plain Old Telephone Service Power Spectral Density PSD

PSTN Public Switched Telephone Network

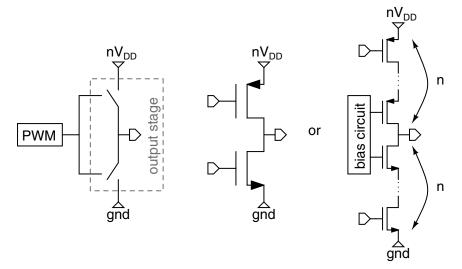

PWM Pulse Width Modulation

QAM Quadrature Amplitude Modulation

RF Radio-Frequency rms root mean square

Rx Receive

SHDSL Symmetric HDSL

SFDR Spurious Free Dynamic Range SLIC Subscriber Line Interface Circuit SINAD Signal-to-Noise and Distortion Ratio

SNR Signal-to-Noise Ratio SOI Silicon On Insulator

SOPA Self-Oscillating Power Amplifier

TDDB Time-Dependent Dielectric Breakdown

THD Total Harmonic Distortion

TSIDF Two Sinusoid Describing Function

Tx Transmit

VDMOS Vertical integrated Diffused MOS

vDSL Very high-speed Digital Subscriber Loop

VGA Variable Gain Amplifier

VLSI Very Large-Scale Integration

VOIP Voice-over IP

xDSL Digital Subscriber Loop

# **Symbols**

$_2F_1(a,b;c;z)$  The 2-1 hyper-geometric function in the variable z

with factors (a, b) and (c) [-]

$\alpha$  Coupling factor between two coupled SOPAs [-]  $\alpha(\omega)$  Gain term of the complex propagation constant [-]

A Limit cycle amplitude [V]

$(a)_n$  The Pochhammer symbol, a notation for

$\Gamma(x+n)/\Gamma(x)$  [-]

$\beta(\omega)$  Phase term of the complex propagation constant [-]

$C_{gate}$  Gate capacitance of a MOSFET [F]

$C_{int}$  Integrator capacitance [F]  $C_{in}$  Input capacitance [F]

$C_j$  Junction capacitance of a diode [F]  $C_{ox}$  Oxide capacitance of a MOSFET [F]

$C_{well}$  Well-capacitance [F] d Cable length [km] dx Unit length [-] e Euler's number 2.72 [-]

$f_{fil}$  Cut-off frequency of a loop filter [Hz]  $f_{int}$  Unit-gain frequency of an integrator [Hz]

$f_{lc}$  Limit cycle frequency [Hz]

$\gamma(\omega)$  Complex propagation constant [-]  $g_m$  Transconductance of a MOSFET [S]

$I \qquad \qquad \sqrt{-1} \, [-]$

$I_q$  Quiescent current [A]  $I_{DS}$  Drain-source current [A]

$I_{rms}$  Rms current [A]

$\mathcal{I}m(z)$  The imaginary part of the complex number z [-]  $J_n(x)$  Besselfunction of the first kind and order n [-] k Boltzmann constant  $1.3807 \cdot 10^{-23}$  [J/K]

$k_R$  Material-dependent factor for calculating the skin-effect [-]

Length of a MOS transistor [µm]

L(s) Transfer function of a linear loop filter [-]

$L_{min}$  Minimal gate length of a specified CMOS technology [µm]

$\eta$  Total power efficiency of a power amplifier [-] or [%]

N Number of tones in a DMT signal [-]

y $Z_0$

| 1                 | List of Abbreviations and Symbols                          |

|-------------------|------------------------------------------------------------|

| n                 | Voltage multiplication factor [-]                          |

|                   | Number of stacked transistors [-]                          |

| $N_A(A)$          | The single input describing function of a non-linearity    |

|                   | with one sinusoidal input with amplitude A [-]             |

| $N_B(A$           | (B) The dual input describing function for a non-linearity |

|                   | with two sinusoidal inputs with amplitudes A and B,        |

|                   | describing the gain of the signal with amplitude B [-]     |

| $O(\phi)$         | The Landau symbol also called big-O, which denotes that    |

|                   | there exists a positive value A so that if $f = O(\phi)$ , |

|                   | $ f  < A\phi$ [-]                                          |

| $P_{out}$         | Output power [W] or [dBm]                                  |

| $R_L$             | Load resistance $[\Omega]$                                 |

| $R_S$             | Switch resistance $[\Omega]$                               |

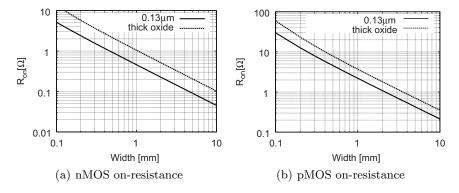

| $R_{on}$          | On-resistance of a MOSFET $[\Omega]$                       |

| $\mathcal{R}e(z)$ | The real part of the complex number z [-]                  |

| $\sigma_n^2$      | Noise energy [dBm]                                         |

| s                 | Laplace variable = $I2\pi f$ [1/s]                         |

| $\Gamma(x)$       | Gamma function [-]                                         |

| $t_{d0}$          | Delay time of a unit inverter [s]                          |

| μ                 | Mobility $[cm^2/Vs]$                                       |

| $V_{BD}$          | Junction breakdown voltage [V]                             |

| $V_T$             | MOS threshold voltage [V]                                  |

| $V_{DD}$          | Nominal supply voltage [V]                                 |

| $V_{DS}$          | Drain-source voltage [V]                                   |

| $V_{GB}$          | Gate-bulk voltage [V]                                      |

| $V_{GD}$          | Gate-drain voltage [V]                                     |

| $V_{GS}$          | Gate-source voltage [V]                                    |

| $\omega$          | Pulsation [rad/s]                                          |

| W                 | Width of a MOS transistor [μm]                             |

| x                 | Scaling factor of an inverter chain [-]                    |

|                   | m c : []                                                   |

Transformer ratio [-] Characteristic line impedance  $[\Omega]$

# Contents

| $\mathbf{Pr}$ | eface |        |                                             | V   |

|---------------|-------|--------|---------------------------------------------|-----|

| Lis           | st of | Abbre  | viations and Symbols                        | VII |

| 1             | Inti  | roduct | ion                                         | 1   |

|               | 1.1   | Motiv  | ration of the Work                          | 3   |

|               |       | 1.1.1  | xDSL Technologies: The Market Opportunities | 4   |

|               |       | 1.1.2  | xDSL Technologies: The Gap                  | 4   |

|               |       | 1.1.3  | Power or High Voltage in Nanometer CMOS?    | 5   |

|               | 1.2   | Organ  | nisation of the Book                        | 7   |

| 2             | Dig   | ital S | ubscriber Line: Signals, Specifications     |     |

|               | and   |        | er Solutions                                | 11  |

|               | 2.1   | DSL i  | in a Nutshell                               | 12  |

|               |       | 2.1.1  | History                                     |     |

|               |       | 2.1.2  | How it Works                                | 13  |

|               |       | 2.1.3  | Continuing Developments in DSL              | 14  |

|               | 2.2   | The C  | Channel                                     | 16  |

|               |       | 2.2.1  | Cable Technology                            | 16  |

|               |       | 2.2.2  | Twisted Pair Cable Modeling                 | 17  |

|               |       | 2.2.3  | Cable Impairments                           | 20  |

|               | 2.3   | Modu   | lation Techniques                           | 21  |

|               |       | 2.3.1  | The Shannon Limit                           | 21  |

|               |       | 2.3.2  | DMT Modulation                              | 21  |

|               |       | 2.3.3  | DMT Specifications                          | 24  |

|               | 2.4   | Soluti | ions for xDSL Line Drivers                  | 26  |

|               |       | 2.4.1  | Line Driver Requirements                    | 26  |

|               |       | 2.4.2  | Class AB                                    | 27  |

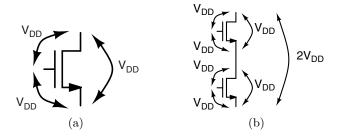

|               |       | 2.4.3  | Class G/H                                   | 29  |

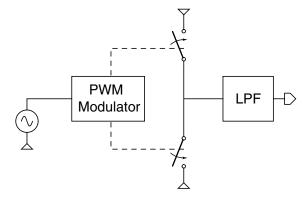

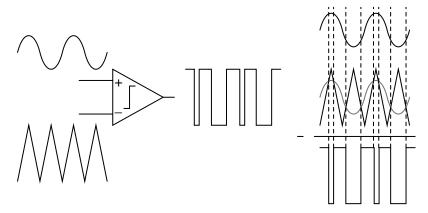

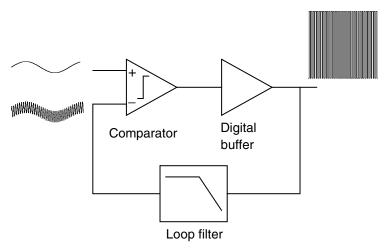

|               |       | 2.4.4  | Class D                                     |     |

|               |       | 2.4.5  | Class K and Other Combined Structures       | 33  |

|               | 2.5   | Concl  | usions                                      | 34  |

| 3 | $Th\epsilon$ | e SOPA xDSL Line Driver                                         | 37  |

|---|--------------|-----------------------------------------------------------------|-----|

|   | 3.1          | The Describing Function Analysis Method                         | 37  |

|   |              | 3.1.1 Nonlinear Systems                                         | 37  |

|   |              | 3.1.2 The Describing Function Viewpoint                         | 38  |

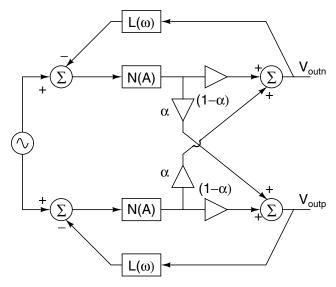

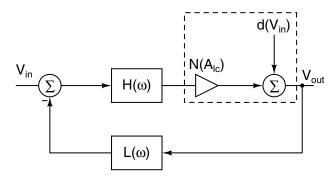

|   | 3.2          | Behavior Model of the SOPA                                      | 40  |

|   |              | 3.2.1 Reference Model                                           | 40  |

|   |              | 3.2.2 Limit Cycle Oscillation                                   | 42  |

|   |              | 3.2.3 The Coupled System                                        | 43  |

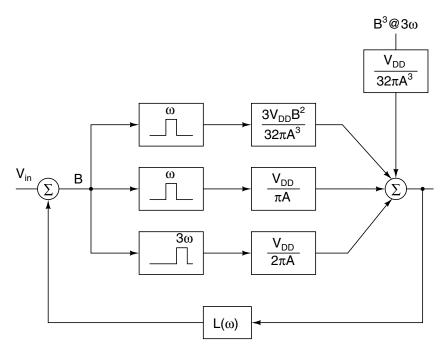

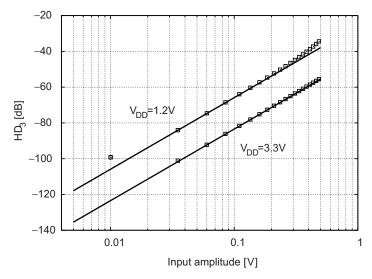

|   |              | 3.2.4 The Forced System                                         | 46  |

|   |              | 3.2.5 Higher Order SOPA Amplifiers                              |     |

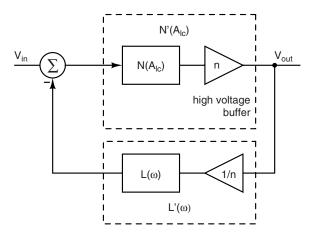

|   | 3.3          | High Voltage SOPA Amplifiers                                    |     |

|   | 3.4          | Conclusions                                                     | 59  |

| 4 | Hig          | h Voltage Design Considerations                                 | 61  |

|   | 4.1          | CMOS Scaling                                                    |     |

|   |              | 4.1.1 Introduction: Moore's Law                                 |     |

|   |              | 4.1.2 CMOS Scaling Laws                                         |     |

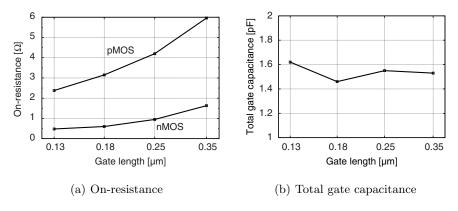

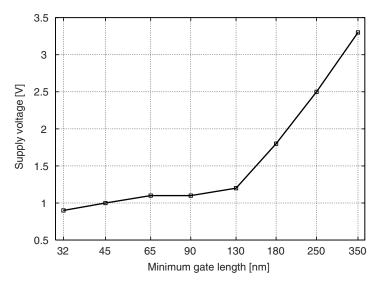

|   |              | 4.1.3 Influence of CMOS Scaling on Switching Amplifiers         | 64  |

|   |              | 4.1.4 Influence of CMOS Scaling on SOPA Design                  | 67  |

|   |              | 4.1.5 Reliability Issues                                        |     |

|   |              | 4.1.6 Customized Silicon Technologies                           | 75  |

|   | 4.2          | Stacking Devices: The High Voltage CMOS Solution                |     |

|   |              | 4.2.1 Introduction                                              |     |

|   |              | 4.2.2 Power Dissipation                                         |     |

|   | 4.3          | Conclusions                                                     | 90  |

| 5 | Hig          | h Voltage Implementations in Standard CMOS                      | 91  |

|   | 5.1          | A 7.5 V Output Driver in a 2.5 V 0.25 $\mu m$ CMOS Technology . |     |

|   |              | 5.1.1 Introduction                                              |     |

|   |              | 5.1.2 Building Block Design                                     |     |

|   |              | 5.1.3 Layout Aspects                                            |     |

|   |              | 5.1.4 Power Dissipation                                         |     |

|   |              | 5.1.5 Measurements                                              |     |

|   |              | 5.1.6 Discussion of the Results                                 |     |

|   | 5.2          | A 5.5 V Output Driver in a 1.2 V 130 nm CMOS Technology .       |     |

|   |              | 5.2.1 Introduction                                              |     |

|   |              | 5.2.2 Building Block Design                                     |     |

|   |              | 5.2.3 Layout Aspects                                            |     |

|   |              | 5.2.4 Power Dissipation                                         |     |

|   |              | 5.2.5 Measurements                                              |     |

|   |              | 5.2.6 Discussion of the Results                                 |     |

|   | 5.3          | Conclusions                                                     | 148 |

|     |       |         |                                | Contents | XIII |

|-----|-------|---------|--------------------------------|----------|------|

| 6   | Hig   | h Volt  | tage Line Driver Realisations  |          | 149  |

|     | 6.1   |         | oth-Order SOPA in 130 nm CMOS  |          |      |

|     |       | 6.1.1   | Introduction                   |          | 149  |

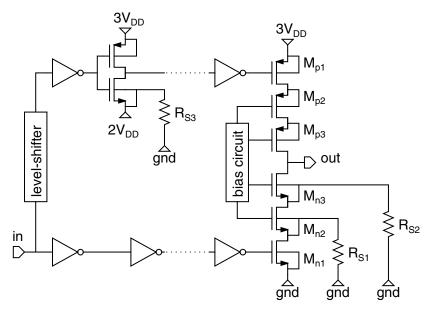

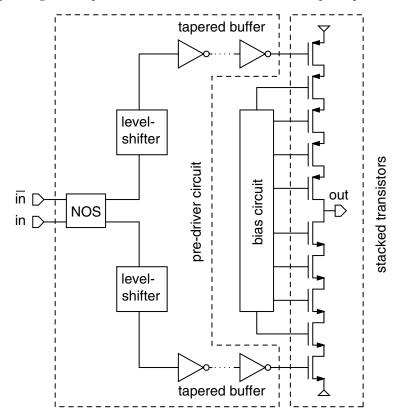

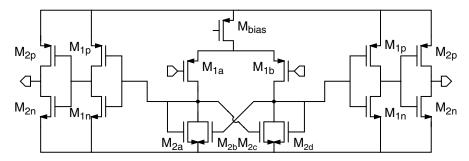

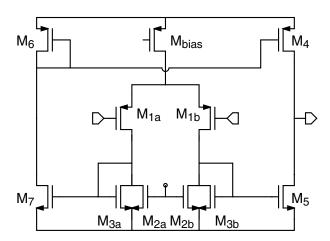

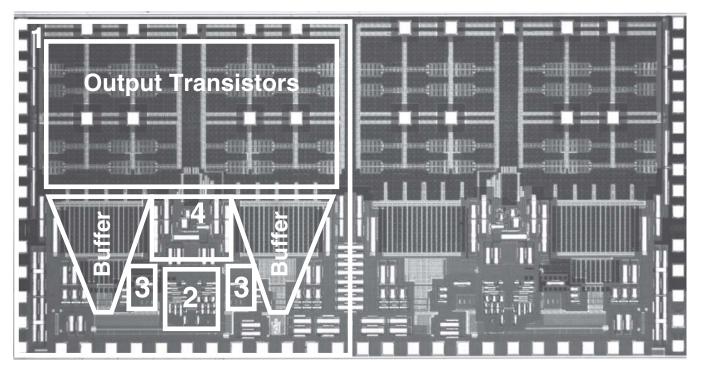

|     |       | 6.1.2   | Building Block Design          |          | 151  |

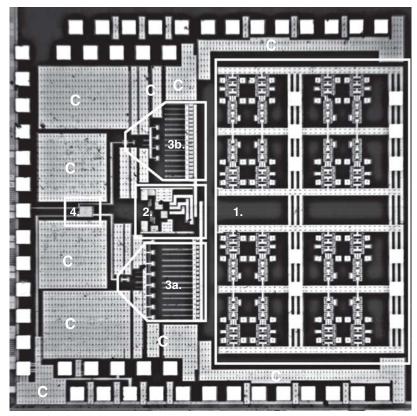

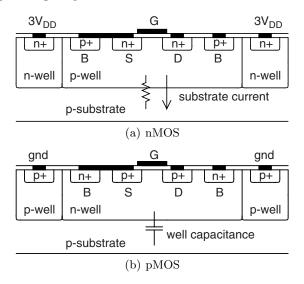

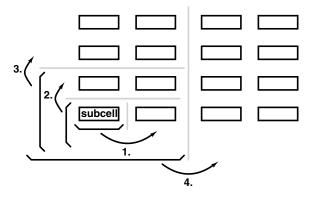

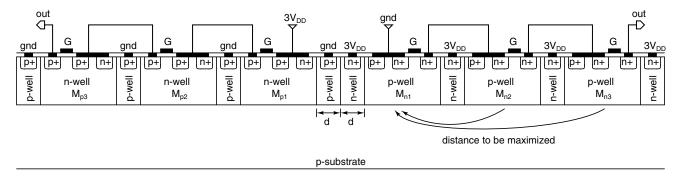

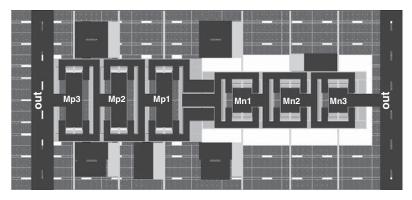

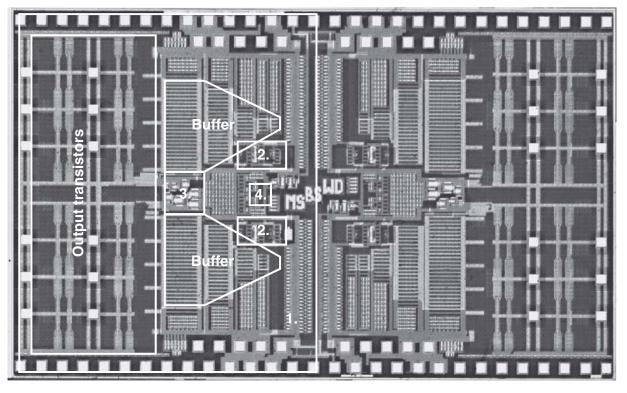

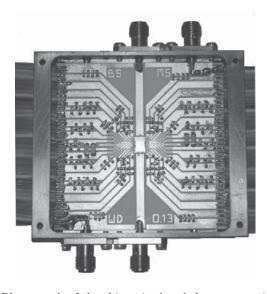

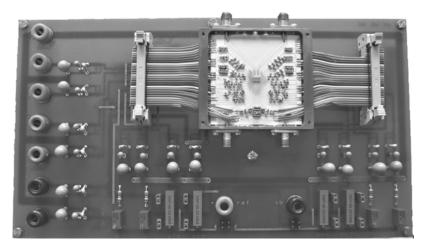

|     |       | 6.1.3   | Layout Aspects                 |          |      |

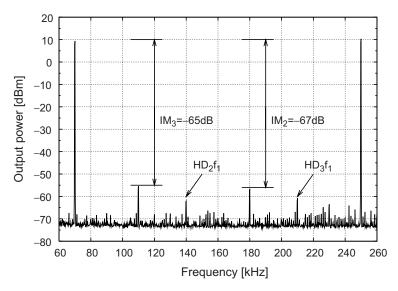

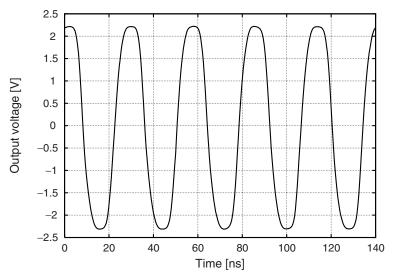

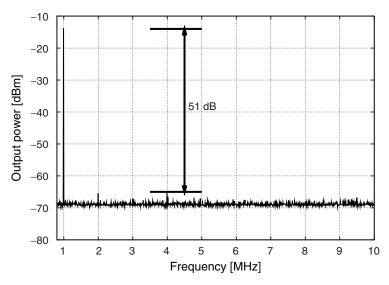

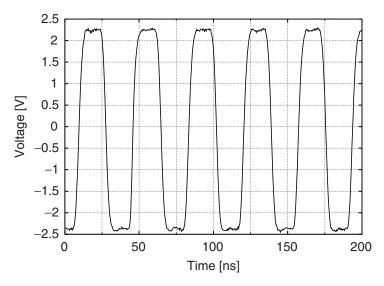

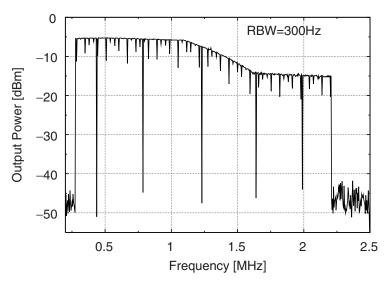

|     |       | 6.1.4   | Measurements                   |          |      |

|     |       | 6.1.5   | Discussion of the Results      |          | 159  |

|     | 6.2   | A Firs  | st-Order SOPA in 130 nm CMOS   |          | 160  |

|     |       | 6.2.1   | Introduction                   |          | 160  |

|     |       | 6.2.2   | Building Block Design          |          |      |

|     |       | 6.2.3   | Layout Aspects                 |          |      |

|     |       | 6.2.4   | Measurements                   |          |      |

|     |       | 6.2.5   | Discussion of the Results      |          |      |

|     | 6.3   | Concl   | usions                         |          | 172  |

| 7   | Coı   | nclusio | ons                            |          | 175  |

|     | 7.1   | Main    | Contributions and Achievements |          | 175  |

| Re  | feren | ices    |                                |          | 179  |

| Inc | dex . |         |                                |          | 183  |

# Introduction

In 1874, while Alexander Graham Bell (who considered himself to be a teacher of the deaf, more than the inventor of the telephone) was working on the harmonic telegraph, the telephone and hearing aids for the deaf, he built a device called phonoautograph. The device was made with Frankensteinian ingenuity out of a dead man's ear (It is not recorded just where the ear came from, volunteered or otherwise.). Speaking into the device caused the ear to operate ... like an ear. The ear's membrane vibrated according to the intensity of the voice, more for louder voices or sounds, less for quieter sounds or whispers. This in turn caused a lever attached to the ear to "write" a wave pattern on smoked glass; bigger waves for louder sounds and smaller for quieter sounds. This inspired Bell. He thought that, by using a membrane to convert sounds of varying intensity into electrical current of varying intensity (instead of just the working of the lever) and then reversing the process on the other end with another membrane, he could replicate speech over long distances. It took him two years to put this idea into practice, but it became the founding principle of telephony.

Once the variable current is generated, it has to have some way to travel to the receiving end, where it is converted back to sounds. From the beginning, copper wire has been the carrier of choice. But, how many wires are needed? The first phones did just use one wire, carrying both the transmitter's and receiver's current and grounding each end in the earth to complete the circuit. However, this created a lot of static interference, since everyone was using the earth to ground their phones. This was fixed when Bell invented a two-wire circuit in 1881. It meant that a phone conversation would require two wires creating a complete circuit, where grounding in the earth was not needed. The two-wire circuit is considered as the start of the billions of twisted pairs for the Plain Old Telephone Service (POTS) that are laying in the ground at this moment.

The history of data-transmission began thus with Alexander Graham Bell, a pioneer who developed the idea that data could be transmitted through copper wire. Of course, he had no idea of the scope of his findings or where they would actually lead to. However, the principles had been established.

In the course of history, many people improved the telephone. The invention of the microphone by David Hughes, with further improvements by Thomas Edison who introduced the carbon granule transmitter, made the telephone into an instrument that was much more sensitive than Bell's Aluminium alloy diaphragm. By the early 1960s, low-cost transistors and associated circuit components made the introduction of touch-tone into home telephones possible. Extensive human factors tests determined the position of the buttons to limit errors and increase dialing speed even further.

Also in the 1960s, the telephone system gradually began converting its internal connections to a packet-based, digital switching system, whereas the earlier phone systems were purely analog causing great inefficiency. It was very prone to breakdown and noise and did not lend itself well to long distance connections. Today, most voice switching in the world is digital with the exclusion of the final connection from the local Central Office (CO) to the Customer Premises Equipment (CPE). This final connection is an analog POTS line, also called *The Last Mile*.

From the 1950s on, people started experimenting sending digital data over the copper wires. However, while the theoretical capacity of copper to transmit data was long known, mathematician Claude Shannon presented in 1948 its theory of channel-information capacity, the practical use of telephone wires for high-speed data was first demonstrated in the late 1980s. Joseph Lechleider demonstrated, through mathematical analysis, the feasibility of sending broadband. The first efforts, to make use of this capacity, created Integrated Service Digital Network (ISDN). The ISDN vision was very ambitious: to construct a global network for data communications and telephony.

In 1986 the early concept definition of High-speed Digital Subscriber Line (HDSL) started. Digital Subscriber Line (DSL) technology was originally implemented as part of the ISDN specifications. Under the impulse of Joseph Lechleider, asymmetry, between up- and downstream data-rates, was introduced in the DSL spectrum, representing the *a* in aDSL. He understood that many users would benefit from the higher data rates possible in one direction.

In the early years of DSL, the economic benefit was not present. However, the .com boom of the mid-1990s created a viable market for DSL. Nowadays, multiple standards for DSL are emerging, grouped under the term xDSL. The reason is the ever-increasing demand for more bandwidth. Latest developed standards, such as aDSL2+ and vDSL2, have the opportunity to offer a triple play of high-speed Internet, Voice-over IP (VOIP) and High Definition Television (HDTV). As such, DSL can preserve its market position between cable and Passive Optical Network (PON) in the field of last mile access solutions.

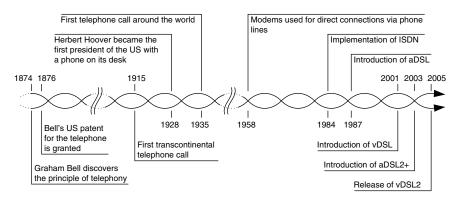

Figure 1.1 shows a timeline with some interesting aspects of wireline communications from the invention of the telephone to the latest DSL standards.

Fig. 1.1. Timeline of telephone wireline communications

# 1.1 Motivation of the Work

Today, the worldwide DSL market penetration has surpassed all other forms of broadband last mile access technologies combined. The resulting xDSL standards and the prospects of the vDSL2 system have proven the expectations for millions of broadband users. The implementations of these techniques had, however, a big drawback from a power consumption point of view, certainly at the CO side. Its line drivers, the final building block between the modem and the telephone line, consume an enormous amount of power.

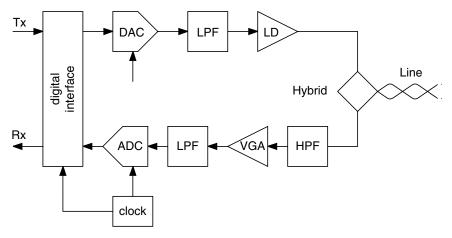

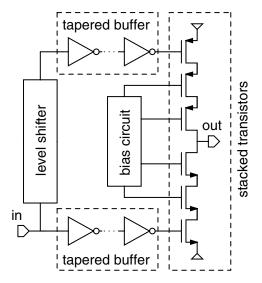

A typical CO modem architecture for xDSL is shown in Figure 1.2 [Sto06]. Coding and modulation is done in the digital interface by digital signal processing. The analog part of the Transmit (Tx) channel contains a Digital-to-Analog Converter (DAC), Low-Pass Filtering (LPF) and a Line Driver (LD). The function of the hybrid is to separate the strong transmitted signals from the weak received signals and thus prevent saturation of the Receive (Rx) path. In the Rx channel High-Pass Filtering (HPF) is used to reduce the out-of-band signals such as the echo from the transmit signal. A Variable Gain Amplifier (VGA) is used in order to ensure that the Rx signal optimally fits into the input of the Analog-to-Digital Converter (ADC). This converter is preceded by an anti-alias filter. With the advent of the nano-electronic era, the line driver remains more than ever the bottleneck for lowering cost and power of the Analog Front-End (AFE).

The presented research activities are aimed at improving this building block, to design aDSL/aDSL2+ compliant line drivers with a high voltage output buffer in a low voltage mainstream Complementary Metal-Oxide-Semiconductor (CMOS) technology and at the same time, maximize its efficiency. In this chapter the importance of this work will be motivated and an overview of the contents of this book is given to guide the reader through this work.

Fig. 1.2. Simplified block diagram of an AFE CO modem for xDSL applications

# 1.1.1 xDSL Technologies: The Market Opportunities

DSL's subscriber base went up to more than 173 million, while global broadband subscribers reached more than 263 million in the 12 months to 30 September 2006. Each week, 1.25 million people signed up to broadband according to the latest statistics prepared for the international DSL Forum by industry analyst Point Topic. Two-thirds of new subscribers are choosing DSL technology, that delivers broadband over telephone lines. [source: www.dslforum.org]

DSL is by far the most popular broadband access technology in the world at 65.6% market share, rising to 82% in the European Union, the world's largest broadband region. Of the remaining broadband access technologies, cable and fiber-to-the-home deliver respectively 23% and 10% of the world's broadband subscribers. Less than 1% of broadband is delivered by satellite, accounting for less than one million subscribers. However, there are still large opportunities for DSL since less than 5% of the phone lines are connected to DSL networks. The majority of the world remains thus "unconnected". DSL reuses the billions of available twisted pairs of the classical POTS. Today vDSL2 with a bandwidth of 30 MHz can offer 100 Mbit symmetrical data rate and enables real triple play. In this point of view, DSL is complying to the need-for-speed on the web for the millions of broadband users.

# 1.1.2 xDSL Technologies: The Gap

The reuse of the billions of copper wires in the ground for last mile access is a good choice from a market point of view. However, the implementation of those xDSL systems has brought engineers and analog designers a lot of worries. The transmission line characteristics of the twisted pair telephone wires are far from good at higher frequencies. Therefore, specialized modulation techniques

Lines per 500 cm<sup>2</sup> 24 48 72 96 120 Class AB 740 mW Class G 400 mW NOT NEBS COMPLIANT  $\Delta \Sigma$  Class D 200 mW SOPA 100 mW NEBS COMPLIANT

Table 1.1. Overview of the most important driver architectures in relation to the maximum number of lines per  $500 \text{ cm}^2$  board

are necessary to reach high bandwidths in Asymmetric Digital Subscriber Loop (aDSL). aDSL signals have a noise-like look with several voltage peaks. This large Crest Factor (CF), meaning the ratio between the maximum voltage and the root mean square (rms) signal voltage, render traditional class AB power amplifiers to be low efficient line drivers.

The importance of high efficiency can be easily observed by taking a look at the Network Exploitation Board Specifications (NEBS) norms. The NEBS prescribe the maximal amount of power that can be dissipated on a 500 cm<sup>2</sup> modem board. If the efficiency of the line drivers is taken into account, the power dissipation will fix the maximum number of lines that can be served by a single board. The result of these calculations is depicted in Table 1.1 [Sev02]. The cost per served line thus increases with decreasing efficiencies of the line drivers. The modem-board density is, nowadays, not only limited by the number and size of the components, but also by thermal limitations.

If a complete modem-board is split in an AFE, Digital Front-End (DFE) and a line driver, one can say that, when scaling the technology to a next node, the power dissipation for the DFE and AFE decreases with roughly 50% and 30% respectively. However, the power savings in the line driver is only a few percent. Today, the line driver represents about 80% of the total power dissipation per served line. The goal is to design highly efficient line drivers such that the cost per line can be lowered. Table 1.1 shows also that traditional architectures do not suffice. Therefore, the presented research activities are based on a relatively novel, highly efficient architecture for xDSL line drivers: the Self-Oscillating Power Amplifier (SOPA) [Pie04].

# 1.1.3 Power or High Voltage in Nanometer CMOS?

An important research topic of this work is high voltage design in mainstream nanometer CMOS for designing analog power building blocks. The nanometer technologies provide an answer to the increasing integration density of Very Large Scale Integration (VLSI) circuits and the low power requirements of complex signaling processing applications. For mass-production, the integration of the power amplifier within the digital part of the system could lead to a lower production cost and smaller products [Rey05].

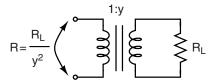

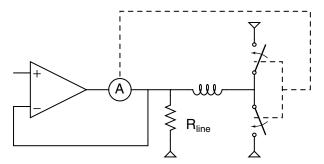

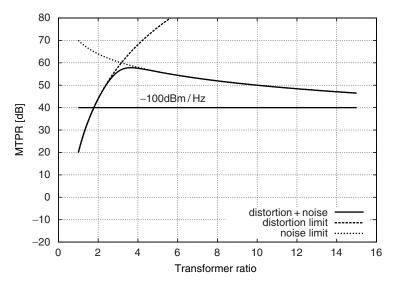

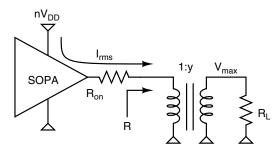

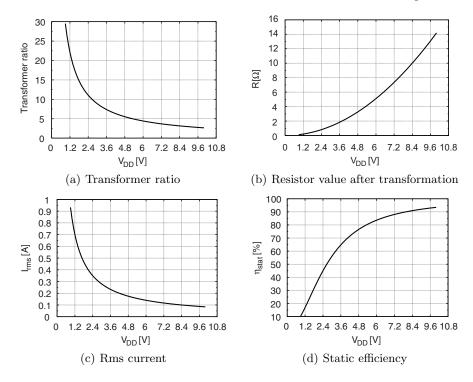

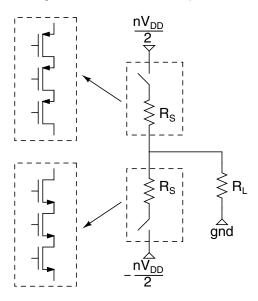

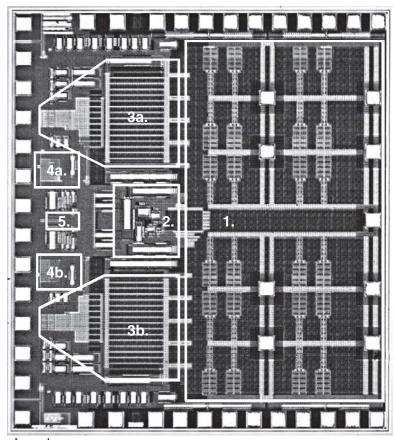

A major issue when integrating power amplifiers in CMOS technologies is the fact that for nanometer technologies, the supply voltage drops to nearly 1 V or even below 1 V. This is done to limit the electric field across the transistor's channel, such that the foundry reliability targets are met. However, the output power is coupled with the square of the maximum voltage swing by  $P = V^2/R_L$ , and the output swing is of course limited by the supply voltage. Another problem is that the load impedance  $R_L$  is fixed by physical constraints, which are very difficult to change. For instance, the characteristic impedance of free space, also called the  $Z_0$  of free space, is an expression of the relationship between the electric-field and magnetic-field intensities. The  $Z_0$  of free space is, like the characteristic impedance in general, expressed in ohms. It is considered as a physical constant and its exact value is  $120\pi \Omega$ . Therefore, the load impedance needs to be converted or transformed into a lower value for achieving a constant output power. This is typically done by an impedance matching network, resulting in extra power losses. On the one hand, these are losses in the impedance network itself. On the other hand, these are losses due to the large current densities in the amplifier driving a low ohmic resistance. After all, when driving high currents, small parasitic resistors can lower the overall efficiency drastically. Moreover, reliability becomes an issue, since electro-migration effects can occur at these current densities. For an xDSL system, the impedance transformation is performed by the line transformer, which is depicted in Figure 1.3.

New power amplifier architectures, such as the SOPA, addresses these issues up to some point, but when entering in the nano-electronic era more has to be done. A 1 V supply is too low for designing an xDSL CO modem. The transformer ratio of the impedance matching network becomes too large such that it becomes impossible to meet the noise specifications of an xDSL system. Moreover, the received signal in the modem will be attenuated with this ratio, resulting in Signal-to-Noise Ratio (SNR) specifications for the building blocks in the Rx path (Figure 1.2) that appeals to one's imagination. The low voltage issues can be elevated by going to higher voltages. This can be done in three ways:

Fig. 1.3. Schematic of the line transformer as an impedance matching network

- 1. By using a separate high voltage output stage comprised of power transistors. This is a very costly solution, since this requires extra *costly* components on the line card.

- 2. By using a technology that is able to deal with higher voltages, like DMOS or BiCMOS technologies. These technologies can be integrated in a low cost CMOS process at, of course, a higher cost. After all, this integration requires extra process steps and mask sets. When scaling towards nanometer lengths, the price of these mask sets is increasing exponentially.

- 3. By using drain source engineering and circuit techniques in a standard CMOS technology. This technique ensures that the devices never encounter a voltage as high as the breakdown voltage over their gate capacitance, while the output swing is higher than this value.

These solutions are ordered from an easy implementation to a very difficult one, but also from a high cost to a low cost implementation. It is only the third and last solution that results in a fully integrated, low cost modem for xDSL applications. Therefore, an important part of the research in this book is dedicated to high voltage circuit design in a mainstream, low voltage nanometer CMOS technology.

These high voltage techniques can also be used for other (low power) applications when using (sub) 1 V CMOS technologies. After all, such low supply voltages put serious restrictions on the design of analog circuits, such as limited gain and SNR.

# 1.2 Organisation of the Book

The presented work aims for a high efficiency, high voltage line driver in a mainstream nanometer CMOS technology. It is a contribution to a fully integrated low cost, high efficiency AFE for xDSL CO modems.

Chapter 2 starts with an investigation of the required specifications for an xDSL line driver. Since these requirements are a direct consequence of the used channel, a short overview of the channel properties is given. From that, it will become clear why Discrete MultiTone modulation (DMT) is used as the modulation technique. The DMT signals pose severe requirements on the line drivers. A brief overview of the most important reported architectures is given. The conclusion of this overview is that a self-oscillating switching structure is necessary for a high efficient xDSL line driver.

The high voltage techniques developed in this work are applied on the output stage of the SOPA architecture for it is the most efficient line driver for xDSL applications. Therefore, a summary of the behavioral model of the SOPA is given in Chapter 3. The SOPA is characterized by the limit cycle oscillation. Techniques to calculate its amplitude and frequency are discussed. The limit cycle oscillation will act as a natural dither in the non-linear system. Formulas are derived to calculate the possible distortion and Missing Tone

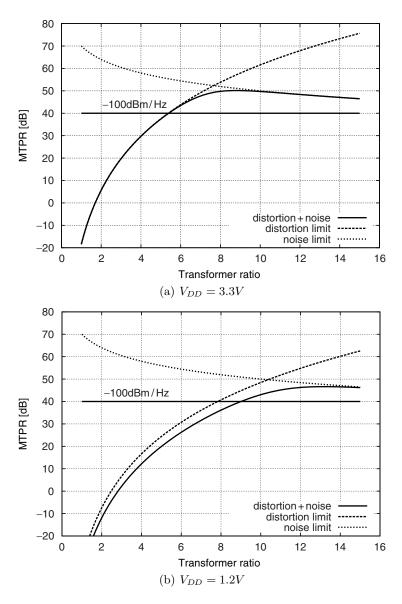

Power Ratio (MTPR) levels. The limitations of the SOPA system, due to the low supply voltages of nanometer technologies, will be explained by means of the behavioral model and the improvements of inserting a high voltage output stage in the self-oscillation structure will be discussed.

Chapter 4 elaborates further on the SOPA architecture in a low voltage technology. The chapter is divided into two major parts. In the first part, the effects of CMOS scaling on the SOPA line driver are further investigated. It will be shown that the efficiency and reliability of the driver will seriously degrade due to the low supply voltages coming from nanometer CMOS technologies.

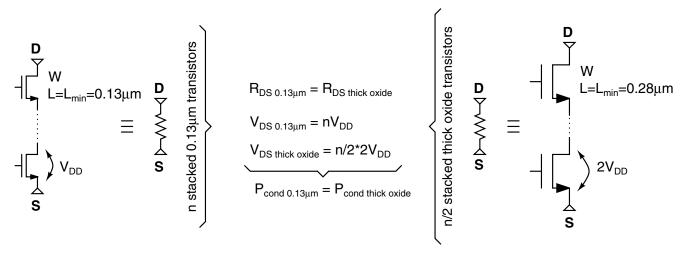

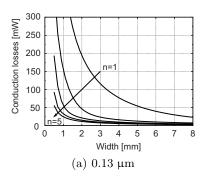

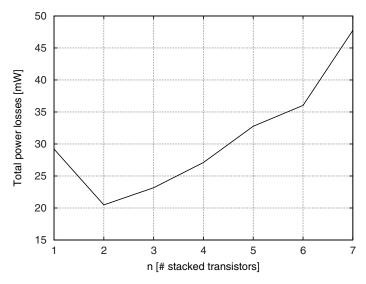

In the second part of Chapter 4, the principle of stacking mainstream CMOS transistors, as a solution for designing high voltage circuits, is described. Through high level calculations of the power losses, a comparison is made between a high voltage solution in a mainstream low voltage technology and a technology from a previous generation with a high nominal supply voltage. It will be shown that the stacking of standard low voltage transistors is more advantageous in terms of power dissipation and integration prospects.

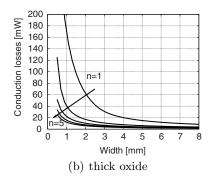

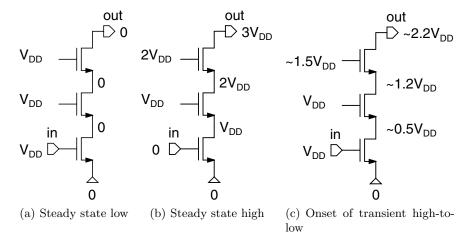

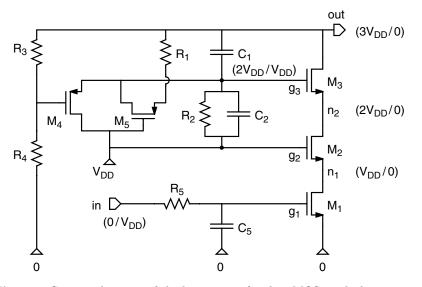

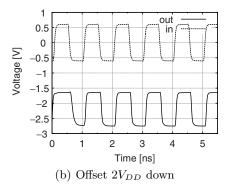

Chapter 5 provides a materialization for the principle of stacking devices for designing high voltage circuits. Two different implementations are presented. The most important design issues are given and the obtained measurement results are described and compared with the present state of the art. The first design is a 7.5 V output buffer in a 2.5 V 0.25  $\mu m$  CMOS technology. Using three stacked transistors, an output swing of 6.46 V is measured in a 50  $\Omega$  load. With the second design, the boundaries of the stacking principle are further explored. An output stage comprised of five stacked transistors resulted in a 5.5 V buffer realized in a 1.2 V 130 nm standard CMOS technology. An output swing of 4.2 V at a frequency of 40 MHz is measured in a 4  $\Omega$  load. The efficiency of this buffer is 79%.

While Chapter 5 gives a materialization of the principle of stacking standard CMOS devices for designing high voltage circuits, Chapter 6 goes one step further. In this chapter, two implementations of the SOPA line driver with a high voltage output buffer in a mainstream 1.2 V 130 nm CMOS technology are presented. The realized prototypes are compared with the present state of the art and they serve as a proof that the stacking principle can be used, even in high-end applications. The first design is a zeroth order SOPA line driver. Measurements point out its compliance with the aDSL-G.Lite specifications and this for a measured efficiency of 40%. With the second design, the goal was set more ambitiously. A first-order SOPA is chosen to comply with the aDSL2+ specifications. A MTPR of 58 dB is measured for a DMT signal with a CF of 15 dB. The total power dissipation for an average output power of 100 mW is 237 mW, resulting in an efficiency of 42%. The presented chips serve as a proof that the superior efficiency of the SOPA line driver can be maintained in nanometer CMOS, thanks to the inclusion of a high voltage output buffer based on the stacking principle.

Chapter 7 concludes with the major contributions and achievements of this research work.

# **URLs**

- http://www.telcomhistory.org/vm/sciencePhonesWork.shtml

- http://www.thehistoryof.net/history-of-dsl.html

- http://www.ralphb.net/ISDN/history.html

- http://isdn.totalaccess.net/history.html

- http://www.fullnet.net/news/0106.html

# Digital Subscriber Line: Signals, Specifications and Driver Solutions

NLIKE competing technologies, DSL eliminates the need for extensive and expensive infrastructure upgrades – improvements that are hard to measure in terms of time or money. Where original telephone company strategies centered on the time consuming and costly task of fiber installation, demand for multimegabit services has forced them to evaluate approaches that leverage the existing infrastructure and provide a quicker time to market. That is one of the DSL technology's chief advantages: the ability to transform the nearly 700 million phone lines installed worldwide into multimegabit data pipes capable of speeding digital voice and data to homes and businesses. [Par00].

The first section of this chapter gives an introduction to the DSL technology. Wading through an alphabet soup of acronyms, the history and working principle of a DSL-system will be discussed. This knowledge is mandatory for understanding the various inherited constraints to design an AFE for a Digital Subscriber Loop (xDSL) system.

DSL uses the twisted pair telephone cable to bridge the last mile. This is, however, a very poor channel for high data-rate communication. In the second section an overview of the channel properties is given. With a lumped parameter model of the twisted pair cable, the huge losses of this channel at high frequencies and large loop lengths will be shown. Moreover, cable impairments like bridged taps, cross talk and radio frequent interference will further limit the throughput through the channel. Therefore, specialized modulation techniques will be necessary to allow for the high data-rates of xDSL.

By applying DMT modulation in xDSL-systems, bit-rates close to the Shannon limit can be achieved. DMT splits the channel into several carriers and by loading every carrier with a bit-rate that is proportional to the measured SNR in that frequency bin, the full capacity is usable. Moreover, DMT is easy to implement in an all-digital domain, especially with the increasing processing power and modern Digital Signal Processing (DSP) techniques in nanometer CMOS. In this section, the basics of DMT-modulation and its specifications for an xDSL-system will be explained.

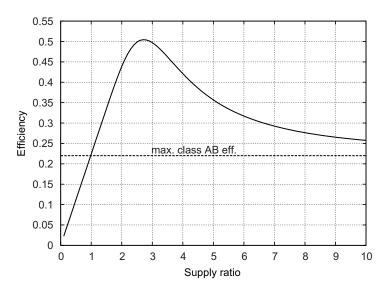

In the last section, traditional solutions for constructing an xDSL line driver are discussed. The large CF of DMT-signals limits the design of high efficiency line drivers. The widely used class AB line driver provides a very linear solution for driving xDSL-signals, but it suffers from an extremely high power dissipation. An improvement to this class AB line driver results in the class G and class H line drivers. By using multiple supplies for a class AB topology, higher efficiencies can be reached. However, for further decreasing the power consumption, switching type line drivers have to be used. This leads to the SOPA line driver, which will form the basis of this research work.

# 2.1 DSL in a Nutshell

# 2.1.1 History

Running data and voice traffic over copper wires is nothing new, but during the 1990s new technology has been applied that has made copper into gold. Within the existing copper wire network, that is used for telephony, lies the promise of the need for speed.

The start of DSL is given in the early 1980s. Equipment vendors were working aggressively to develop Basic Rate ISDN, which would provide up to two 64 kb/s B-channels, plus a 16 kb/s D-channel used for signaling and packet data. The information payload, plus other overhead associated with implementation, resulted in 160 kb/s in total transmitted information. A key requirement of ISDN was that it had to reach customers over the existing copper wire loops, equating to 18 kft. However, an Alternate-Mark Inversion (AMI) encoding implementation of Basic Rate ISDN would require use of the lower 160 kHz, which resulted in too much signal attenuation and would fall short of the required 18 kft loop reach.

By 1988, advancements in signal processing and line coding doubled the effectiveness of legacy AMI code by sending two bits of information with each cycle of an analog waveform or baud. The line code was called 2 Binary, 1 Quaternary (2B1Q). A 2B1Q implementation of Basic Rate ISDN uses frequencies ranging from 0 to approximately 80 kHZ, which has less attenuation and results in the desired 18 kft loop reach.

In the early 1990s, some vendors encouraged the use of 2B1Q at higher speeds as an alternate way to provide T1 and E1 services, without repeaters. The technique consisted of splitting the 1.544 Mb/s service into two pairs (four wires), which each ran at 784 kb/s. This technique was referred to as HDSL. The result was a HDSL-based service, specifying loops of up to 12 kft. [Par00].

Further improvement of HDSL has resulted in a single pair HDSL, which is known under the generic name Symmetric HDSL (SHDSL). In a second generation (HDSL2), more improved modulation schemes were used. The spectra

<sup>&</sup>lt;sup>1</sup> 18 kft corresponds with approximately 5.5 km.

of HDSL mostly remained symmetric, which is favourable for normal data traffic, but is unusable for more recreative applications.

A possible entertainment application was video-on-demand, due to the development of new compression standards for video like MPEG. Video-ondemand needs a high downstream bit-rate (from CO to CPE), but requires a very limited upstream (from CPE to CO). This resulted in aDSL, making use of the power of asymmetry. However, video-on-demand never fulfilled its prospects. However, through the course of these video-on-demand trials, the industry has come to recognize that many data applications were actually asymmetric in nature. The best example of this is Internet access. Typically, Internet users send a small stream of data to a distant server requesting the download of a particular data, graphic, audio or video file. In response, the server begins sending the file at the data-rate that can be supported across the network to the distant workstation. This transaction is extremely asymmetric in nature. During this same time, the Internet evolved into a whole new phenomenon with unheard of growth rates of new Internet service subscribers. The biggest complaints across all users was that it took too long to download files at dial modem or even ISDN data-rates. Hence, a new service and a new technology have soon been married, and aDSL was re-focused to support Internet access. [Par00].

# 2.1.2 How it Works

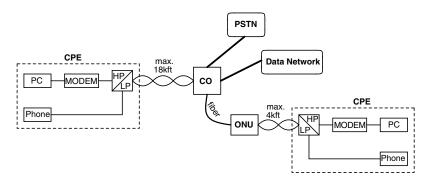

The deployment topology of a generic aDSL network is depicted in Figure 2.1. The aDSL technology was aimed at the non-professional user, so a new subscriber should be able to use aDSL out-of-the-box and without modifications on its existing communication network, i.e. the POTS system. The local loop conveys simultaneously the following signals through one pair of wires [Pie04]:

- Downstream bit-rates of up to 8 Mb/s

- Upstream bit-rates of up to 1 Mb/s

- POTS, i.e. analog voice signals

Fig. 2.1. Topology of an aDSL/vDSL network

This is done by the use of frequency division multiplexing without overlap. Voice, arriving from the Public Switched Telephone Network (PSTN) and data, arriving from the data network or Internet Service Provider (ISP) are brought together in the CO and transfered over the telephone line to the CPE. The splitting function for separating the POTS with the aDSL-signals is performed by a splitter consisting of mere low- and high pass filters. For an aDSL system, the loop length between the CO and the CPE is typically limited to 18 kft to ensure a minimal downstream rate of 1.5 Mb/s. To reach the maximum downstream rate of 8 Mb/s the loop must be shorter than 9 kft.

At the high data-rates of a Very high-speed Digital Subscriber Loop (vDSL) system, the loops must be so short that optical fiber will be used until the last few thousand feet (or the last mile), which is also shown in Figure 2.1. vDSL will be primarily used for loops fed from an Optical Network Unit (ONU), which is typically located less than 3 kft from the customer. Few vDSL loops will be served directly from a CO. Optical fiber connects the ONU to the CO. The maximum loop length of a vDSL system reaches 4,000 ft to deliver a data rate of 13 Mb/s. Maximum downstream rates of 55 Mb/s are possible over lines up to 1,000 ft. At this high data-rates, a combination of fiber cables, feeding neighborhood ONUs (fiber-to-the-curb), and last-leg-premises connections by existing copper through a vDSL system provides an attractive alternative for the costly fiber-to-the-home system solution.

# 2.1.3 Continuing Developments in DSL

The onslaught of new vendors is sure to bring continued variations in DSL technology. Even as mass deployments of aDSL and SHDSL reach the market, new variants are being developed and marketed to fulfill the needs of certain segments of the DSL market [Par00]. The ultimate goal is to increase data-rate and reach for offering a triple play of high speed Internet, VOIP and HDTV.

The main improvements over the original aDSL standard, leading to aDSL2, can be summarized as follows. The speed and reach increases in aDSL2 are largely owed to improved performance on long lines in the presence of interference. aDSL2 can deliver a maximum of 12 Mb/s while extending the reach of the original aDSL by 900 ft.

The new aDSL2 Recommendation also realigns the voice channels and offers providers the ability to combine multiple aDSL2 lines for faster bandwidth to certain customers. In addition, aDSL2 systems can enter an "all digital" mode where voice channels are reassigned to data. This is especially important for business lines that may not need voice services over the aDSL2 line.

The aDSL2+ standard builds further on the aDSL2 standard, increasing the bandwidth by extending the usable frequencies on the line. While both technologies use the same frequencies for telephone calls and uploading data, the download channel is extended from a maximum of 1.1 MHz for aDSL2 to 2.2 MHz for aDSL2+. This increases the maximum downstream rate to 24 Mb/s.

vDSL is the latest member of the xDSL family, which was already mentioned in the previous section. vDSL offers a maximum downstream rate of  $55 \,\mathrm{Mb/s}$  over very short distances. vDSL was originally named vaDSL, but the a, for asymmetric, was dropped because vDSL can support both symmetric as asymmetric transport. These connections can be very fast because the physical distances are kept very short, allowing for maximum throughput. As fiber-optic networks continue to move closer to communities around the world, vDSL will become increasingly important as a way to bridge the last mile.

With the aDSL2+ en vDSL standards, the downstream rates are fit to deliver high-speed Internet and video-on-demand, but multiple HDTV channels are still not in reach. The newly standardized vDSL2 (second generation vDSL) enables very high transmission rates up to symmetrical 100 Mb/s (both up- and downstream) on loops of about 300 ft by using a bandwidth of 30 MHz. vDSL2 is able to support multi-channel HDTV using the existing ubiquitous copper telephone line infrastructure. That capability combined with the capacity for multimode implementations enabling interoperability with existing aDSL equipment, means that vDSL2 will integrate readily into legacy and next generation telecommunication networks.

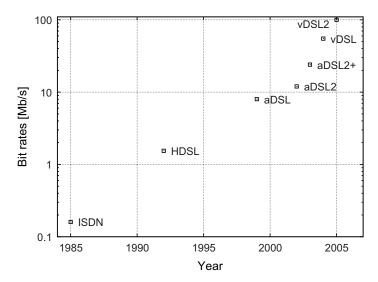

Figure 2.2 shows an overview of the maximum downstream bit-rates versus the year of ratification for various xDSL standards. One can clearly notice the increase in bit-rate following the customer needs. The way these bit-rates are achieved will be more elaborated in the following sections. However, while reading the techniques involved with xDSL, one should always keep in mind

Fig. 2.2. Maximum downstream bit-rate versus year of ratification for various xDSL standards

the legacy of POTS. One of the big advantages of xDSL is its compatibility with POTS, nevertheless it costs flexibility and increased building block specifications.

# 2.2 The Channel

# 2.2.1 Cable Technology

As was already mentioned in the introduction of Chapter 1, early telephone systems did use only one wire. The loop was closed by ground. Since the earth acts as a gigantic magnet, the grounded loop picked up various magnetic signals. In 1881 a solution was found by Graham Bell with its invention of the two-wire telephone circuit.

By the use of two wires, the lines became more "quiet", but it only last for a short time. As business bloomed and more people subscribed to the telephone system, the lines again produced unexpected noises. This was due to crosstalk between parallel telephone lines by inductive coupling of the wires. This problem became more prominent in large cities. Due to the advent of the skyscraper, more wires were needed to be put into the ground. Crosstalk seemed to be inevitable. But is was also Bell again who came up with a solution to this problem in 1881: he invented the twisted pair. By twisting the wires, the disturbing signal becomes common mode to the wires and is, in that way, heavily suppressed. Although the twisting schemes evolved, present telephone wires are still built on the same principle [Pie04].

The twisting improves the egress and ingress properties of the wire: it reduces the electromagnetic radiation as well as the pick up of unwanted signals if submerged in an electric field. Wire pairs are combined in cables of different sizes ranging from a couple to a few hundreds of pairs. The cable structure can vary considerably. In Europe, the pairs are often combined in quads that consists of two pairs twisted around each other. These quads constitute binders of some tens of pairs. Finally, several binders are grouped in a single cable [Cor99].

Another cabling issue is the choice of material. Copper seemed to be the best choice from an electrical point of view but it was too soft and too weak. The strength issue was solved by using hard-drawing copper wires. The major problem however is, as always, cost. Therefore, thin copper wires were preferred to save copper. But, thin wires have a higher resistance than thick wires, which in turn means more attenuation. Thus the distance over which a signal can travel is reduced. Therefore, telephone companies have designed their cable plant using the thinnest gauge wire that could support the required services.

In the USA, wire thickness is represented by the denominator composed of the fraction of an inch in wire size, assuming a numerator of 1. Therefore, a wire that is 1/24 inch in diameter is referred to as 24 American Wire

Gauge (AWG). Wire gauges of 24, and more often 26, are present in most North American cable plants. The design rules used by nearly all telephone companies provided for a change in wire gauge with a thinner gauge used near the entrance of a CO to minimize physical space requirements and changing to thicker gauges over long loops to maximize loop reach.

In most markets outside of North America, wire gauges are referred to by their diameter in millimeters. For example, 0.4 mm, which is comparable to 26 gauge, and 0.5 mm, which is comparable with 24 gauge, are the most common; although in many developing countries, heavy gauges of 0.6 mm to 0.9 mm can be found in newly urbanized areas. This variation in wire gauge adds to the challenge of determining a particular DSL system's performance over a particular loop. [Par00].

# 2.2.2 Twisted Pair Cable Modeling

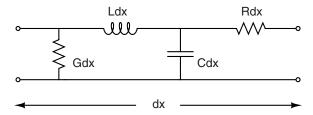

A twisted pair cable is modeled as a transmission line and can be described using four primary parameters: R, G, L and C [Joh97]. These four parameters are shown in Figure 2.3, where, in terms of "per unit length", R is the internal resistance, G is the conductance, E is the inductance and E is the capacitance. Due to the skin-effect for ac-signals, the internal resistance is actually a complex impedance and can be modeled by

$$R(\omega) = k_R(1+j)\sqrt{\omega} \ \Omega/km \tag{2.1}$$

where  $k_R$  is a constant determined by the diameter and the material of the wires. Note that  $R(\omega)$  is proportional to the square root of the frequency. Parameters L and C are relatively constant at higher frequencies (larger than 100 kHz) and  $G \cong 0$  in modern cables.<sup>2</sup> Typical values for these parameters are  $k_R = 0.2$ , L = 0.6mH/km and  $C = 0.05\mu F/km$  for a 24AWG cable at frequencies higher than 100 kHz.

Fig. 2.3. A lumped parameter model for a short section of twisted pair cable

$<sup>^2</sup>$  The conductance does not equal zero in cables with a poor quality, which leads to a term proportional to f in the transfer function.

# Characteristic Impedance

The characteristic impedance of a transmission line can be shown to equal

$$Z_0 = \sqrt{\frac{R + j\omega L}{G + j\omega C}} \tag{2.2}$$

Substituting G = 0 and using the approximation  $\sqrt{1+x} \cong 1+x/2$  for  $x \ll 1$ , equation (2.2) becomes

$$Z_0 \cong \sqrt{\frac{L}{C}} + \frac{k_R(1-j)}{2\sqrt{\omega LC}} \tag{2.3}$$

Thus, for high frequencies  $Z_0 = \sqrt{L/C}$ . In other words, since L and C are relatively constant, the characteristic impedance of the line is more or less a constant at higher frequencies. Using the typical values above,  $Z_0$  equals 110  $\Omega$  for frequencies larger than 100 kHz. At lower frequencies, the characteristic impedance has an extra term, which is inverse proportional to  $\sqrt{f}$ .

# Transfer Function

The transfer function of a twisted pair cable can be modeled by

$$H(d,\omega) = e^{-d\gamma(\omega)} = e^{-d\alpha(\omega)} \cdot e^{-jd\beta(\omega)}$$

(2.4)

where  $\gamma(\omega) = \alpha(\omega) + j\beta(\omega)$  and is given by

$$\gamma(\omega) = \sqrt{(R + j\omega L)(G + j\omega C)}$$

(2.5)

$\alpha$  and  $\beta$  are the attenuation and phase constants respectively and d is the cable length. Setting G=0 and substituting equation (2.1) into equation (2.5), one becomes

$$\gamma(\omega) = j\omega\sqrt{LC}\sqrt{1 + \frac{k_R(1-j)}{L\sqrt{\omega}}}$$

(2.6)

Now using the approximation  $\sqrt{1+x} \cong 1+x/2$  for  $x \ll 1$  and making use of  $\gamma(\omega) = \alpha(\omega) + j\beta(\omega)$ , the following results are obtained:

$$\alpha(\omega) = \frac{k_R}{2} \sqrt{\frac{\omega C}{L}} \tag{2.7}$$

$$\beta(\omega) = \omega \sqrt{LC} + \frac{k_R}{2} \sqrt{\frac{\omega C}{L}}$$

(2.8)

Combining equations (2.4) and (2.7), one can see that for a given length d, the cable's transfer function gain (in dB) is given by

$$H_{dB}(d,f) = 20 \log_{10} |H(d,f)|$$

$$= -4.343d \cdot k_R \sqrt{\frac{2\pi fC}{L}}$$

(2.9)

Thus, the gain in dB is inverse proportional to the square root of f.

In terms of the cable's transfer function phase, combining equations (2.4) and (2.8) one can see that most of the phase is linear, which is a result of delay through the length of the cable, while a nonlinear component is proportional to the square root of the frequency.

Finally, using the typical primary constants above for the 24AWG cable, one can find the gain for a typical twisted pair cable to be approximately

$$H_{dB}(d,f) \approx -0.02d\sqrt{f} \tag{2.10}$$

where d is in km and f is in Hz. Note that equation (2.10) is only useful in estimating the loss in a typical cable as it depends on the primary constants of the cable, which in turn depend on the physical construction such as wire gauge, twist lengths, insulation types and thickness.

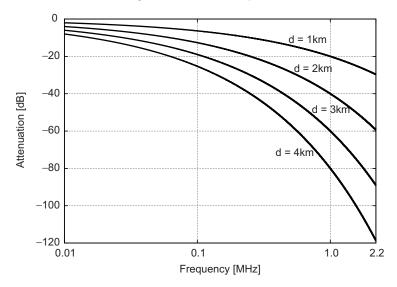

A graphical representation of equation (2.10) is depicted in Figure 2.4. The figure shows the line attenuation in the aDSL2+ frequency spectrum for different loop lengths. It can be seen that, e.g., for a loop length of 3 km the attenuation of the signal is -60 dB at a frequency of 1.0 MHz. This results in a division of the received signal by a factor of 1,000 compared to the transmit signal. From this calculation, the importance of a small transformer ratio becomes once again clear. After all, the transformer ratio leads to a further attenuation of the received signal, which requires extremely low noise specifications of the building blocks in the Rx path.

Fig. 2.4. Line attenuation in the aDSL2+ frequency spectrum for different loop lengths

# 2.2.3 Cable Impairments

The transmission channel capacity depends highly on the twisted pair characteristics, as described in the previous section, but it also suffers from a number of impairments [Cor99].

- Load coils have been used in the early days of telephony to boost and flatten the frequency response of the line at the upper edge of the voice band. As these coils give an unacceptable attenuation at higher frequencies they should be removed, if still present, to allow for DSL services.

- The frequency-dependent attenuation and dispersion leads to pulse distortion and inter-symbol interference. In multi-carrier systems, like DSL, also inter-carrier interference occurs.

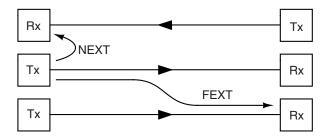

- Between different wires in the same cable, there exists capacitive and inductive coupling. The coupling increases as the wires are closer together. It causes unwanted cross talk between the pairs. The cross talk between wire pairs in the same binder or adjacent binder groups is a main noise source contribution. Two types of cross talk can be distinguished, as depicted in Figure 2.5. Near-End Crosstalk (NEXT) occurs at the receiver that is collocated with the disturbing source, while Far-End Crosstalk (FEXT) occurs at a remote receiver. FEXT is attenuated by propagation through the loop, while NEXT is not. Therefore, NEXT dominates FEXT by far for echo canceled systems.

- Some subscriber loops have open-circuited wire pairs tapped onto the main wire pair, called bridge taps. This is mostly due to a subscriber that is disconnected or still has to be connected to the service. The existence of bridged taps in the loop differs from country to country and depends upon the cabling rules in the past. Their presence causes reflections and affects the frequency response of the cabling leading to pulse distortion and inter-symbol interference.

- A loop can also be built up of wires with different diameters, leading to reflections and distortion as well.

- As a result of the cable unbalance, Radio-Frequency (RF) signals can be picked up during propagation over the wire and interfere with the transmitted data at the receiving side. The balance of the cable decreases

Fig. 2.5. Illustration of NEXT and FEXT

as the frequency goes up. The aerial drop-wires, the vertical cables in high-rise buildings and the in-house wires are the most vulnerable for RF ingress. This ingress can come from a variety of sources such as Amplitude Modulation (AM), radio amateur communication and public safety and distress bands.

# 2.3 Modulation Techniques

# 2.3.1 The Shannon Limit

In a communication system, achieving a high bit-rate with a very low probability of bit-error at the same time, is wanted. These parameters can be improved if the transmission power is increased and/or the bandwidth is increased and/or the system's complexity is increased. Of course, a minimum of power, bandwidth and complexity is desirable. But, in fact, the communication system itself puts a limit on these parameters [Alc].

One of these limits is described by the Shannon–Hartley capacity theorem, which provides a theoretical limit for the capacity of a channel that is limited by white Gaussian noise. This limit can be regarded as the maximal achievable bit-rate through a channel. It is given by

Capacity

$$[b/s] = BW \log_2(1 + SNR)$$

(2.11)

BW [Hz] stands for the channel's bandwidth and SNR [dB] is the signal-to-noise ratio in the channel. For a band-limited and frequency depended transfer function, the capacity limit becomes

Capacity [b/s] =

$$\int_{f_{min}}^{f_{max}} \log_2(1 + SNR) df \qquad (2.12)$$

For long loops, it is shown that a DMT based aDSL system approaches the Shannon limit. For short distances, the departure from the Shannon limit increases. But, by using available techniques, such forward error correction, the gap with the Shannon limit can be closed. However, the cost will increase exponentially.

# 2.3.2 DMT Modulation

DMT is a form of multicarrier modulation. DMT splits the bandwidth into several discrete channels. In the initialization phase of the modem, the SNR is measured for every channel. Every channel is then modulated by an m-bit Quadrature Amplitude Modulation (QAM)-signal. The constellation size is determined by the measured SNR in accordance with Shannon's theorem (2.11). The use of DMT modulation for xDSL systems has several benefits [Reu96]:

- DMT achieves near optimum use of the line capacity because it can adaptively allocate information and transmit power across the available bandwidth.

- Bit-rates can be adjusted in small increments of a few tens of kilobits per second, enabling DMT hardware to be programmed to support a wide range of data rates in both directions with the possibility of changing these rates "on the fly".

- Power spectral density can be adjusted very flexibly. Forbidden bands (e.g. amateur radio band) can thus be avoided simply by imposing a suitable frequency mask.

- DMT is good at coping with interference from multiple radio frequency sources.

- DMT is the more cost-effective option on complex lines with numerous bridged taps.

- The multi-carrier modulation and demodulation is easy to implement in an all-digital domain by exploiting Fast Fourier Transform (FFT) methods.

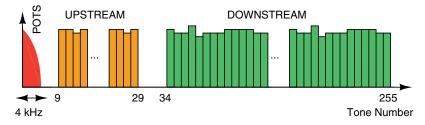

Figure 2.6 shows an illustration of the frequency spectrum used for an aDSL system. The DMT modulation consists in this case of 20 carriers constructing the upstream band and 221 carriers constructing the downstream band.

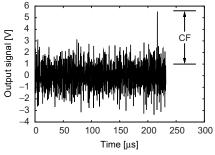

The time domain representation of a DMT-modulated aDSL signal is shown in Figure 2.7(a). Since in the frequency domain the spectrum is flat, the signal in the time domain will have a noise-like nature. An important property of a DMT signal can be clearly seen in this figure. For an aDSL system using a DMT implementation, there is a maximum of 255 discrete subcarriers all transmitting at the same time. Each subcarrier is at a different frequency and phase. When the phases of several carriers align in constructive interference, a voltage spike occurs in the signal. A measure for this voltage spike is the Crest Factor (CF) of the signal. It is defined as the maximum voltage over the rms voltage:

$$CF = \frac{V_{max}}{V_{rms}} \tag{2.13}$$

Sometimes, the Peak-to-Average-Ratio (PAR) is used as a measure for the voltage spike. It is defined as peak power over the rms power of the signal.

Fig. 2.6. Spectrum of a DMT-modulated aDSL signal

- (a) Time domain representation

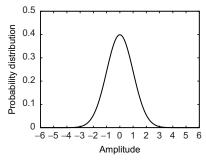

- (b) Associated probability distribution

Fig. 2.7. Time domain representation of a DMT-modulated signal and its associated probability distribution

The downstream time-domain aDSL signal can be represented by [Pie04]

$$x(t) = \sum_{n=34}^{255} a_n s(t - nT) \cos(2\pi n f_i) + \sum_{n=34}^{255} b_n s(t - nT) \sin(2\pi n f_i)$$

(2.14)

In this equation,  $a_n$  and  $b_n$  represent the constellation point of the m-bit QAM modulation. Note that the constellation size m is on itself function of the carrier number n. s(t) is an envelope function used to normalize the average energy per channel. The carrier spacing  $f_i$  is set to 4.3125 kHz for the aDSL system. An aDSL symbol has thus a length of  $1/f_i$ . During this time the constellation points stay fixed.

A DMT-modulated aDSL signal is thus the sum of N independent QAM symbols, each being carried over a distinct carrier frequency. In equation (2.14) N equals 255-34. For large numbers of N ( $N \ge 10$ ), the amplitude distribution  $f_A$  of the DMT-signal can be accurately modeled as a Gaussian random process [Mes93]:

$$f_A = \frac{1}{\sigma\sqrt{2\pi}} \exp\left(-\frac{A^2}{2\sigma^2}\right) \tag{2.15}$$

with  $\sigma$  representing the rms-voltage of the signal. This is graphically represented in 2.7(b). It can be seen from Figure 2.7 and equation (2.15) that large amplitude spikes arise very rarely because of statistical averaging. Therefore, it is advantageous to accept some clipping in the DMT signal to make a trade-off between the resulting SNR loss against a gain in lowering the quantization noise of the used ADC and DAC and their power consumption. However, allowing too much clipping results in a steep decrease of the Bit-Error Rate (BER).

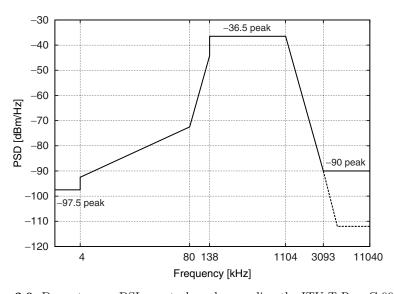

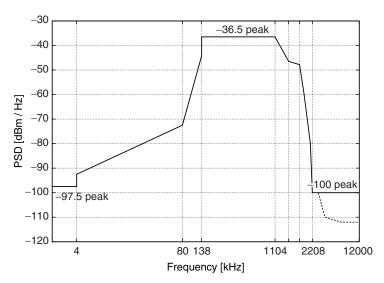

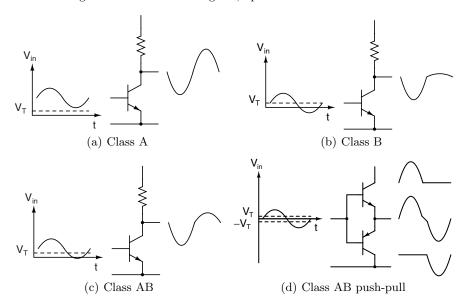

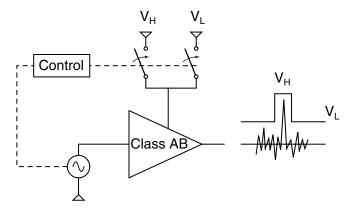

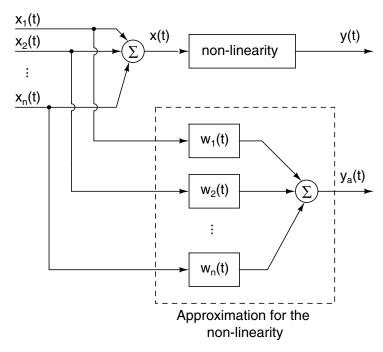

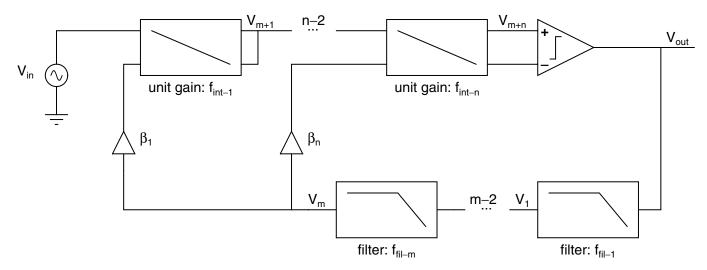

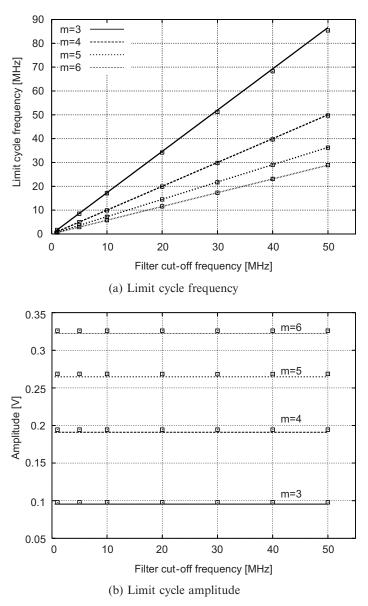

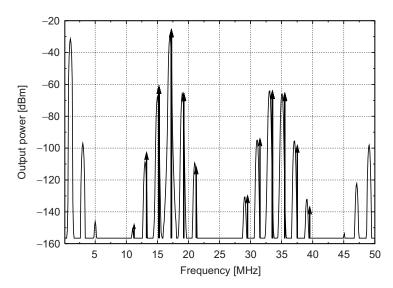

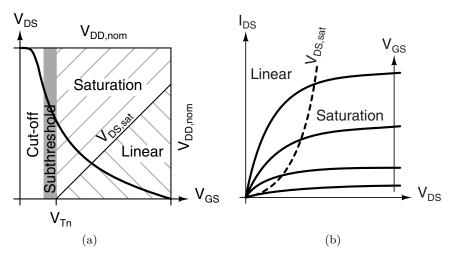

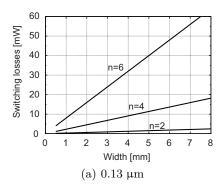

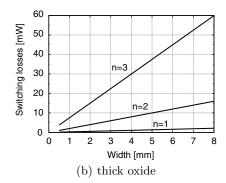

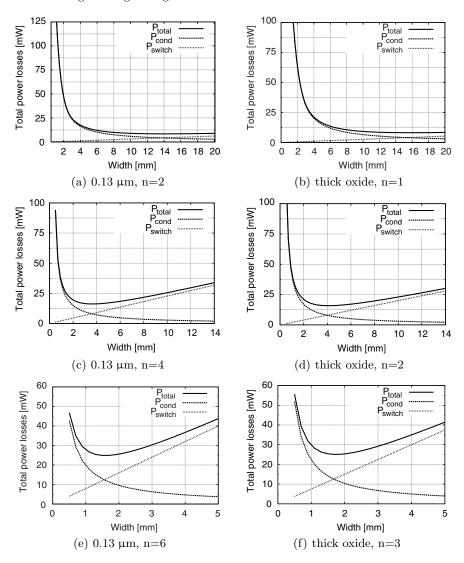

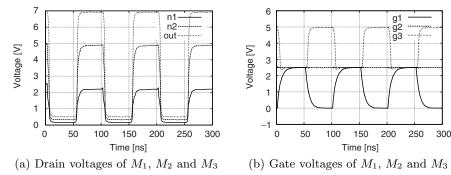

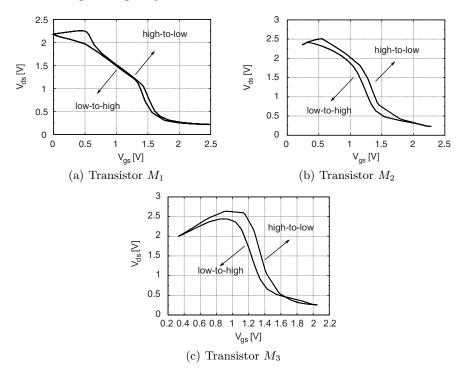

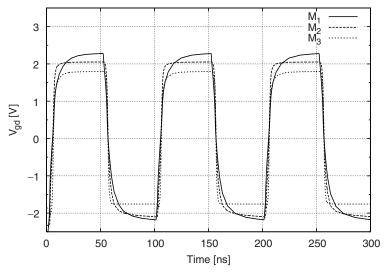

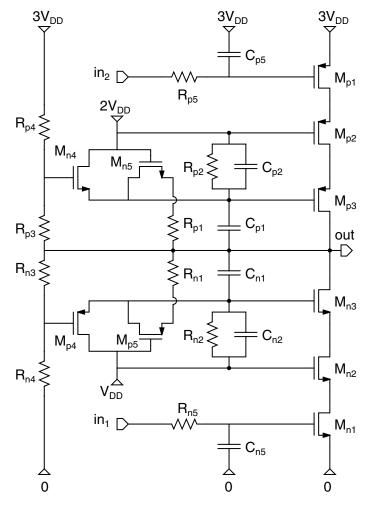

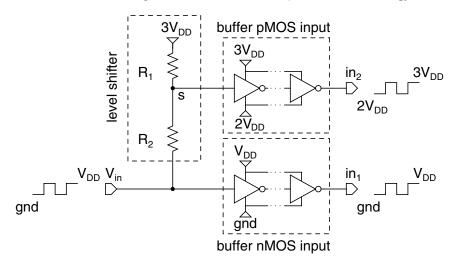

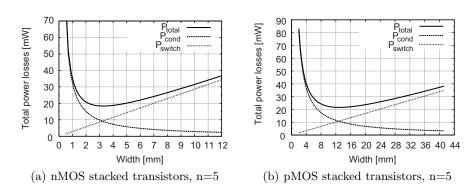

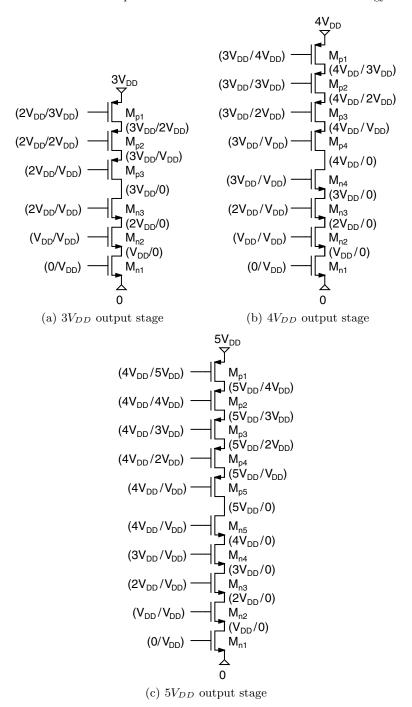

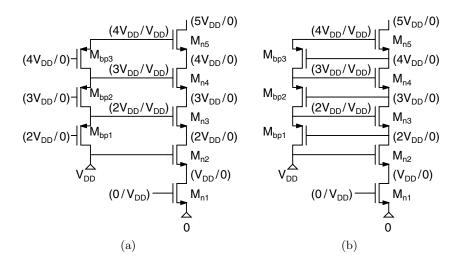

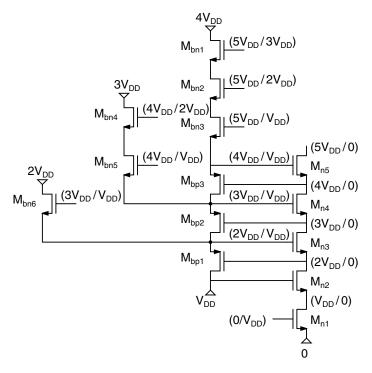

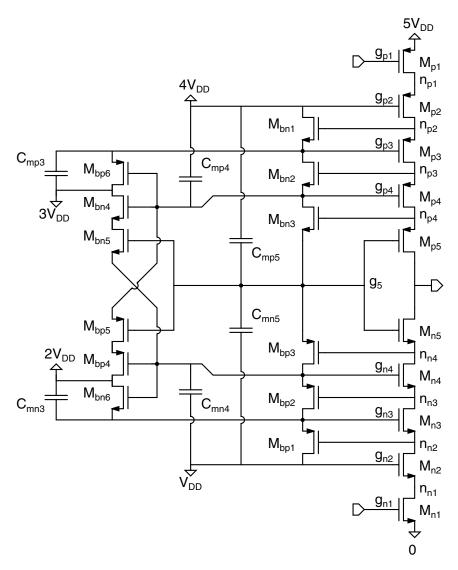

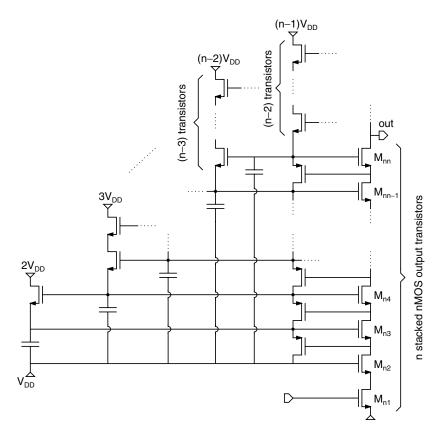

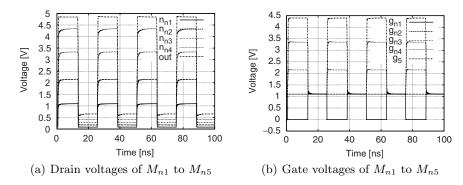

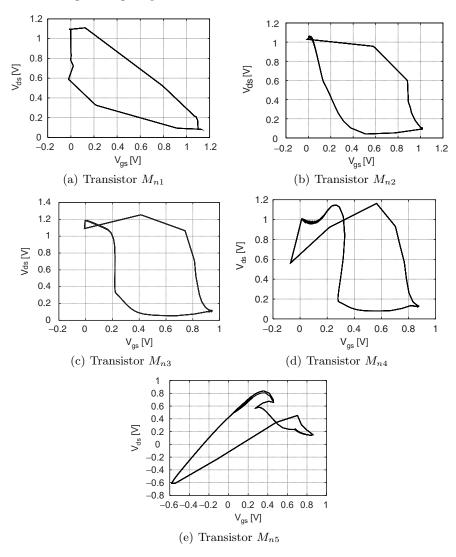

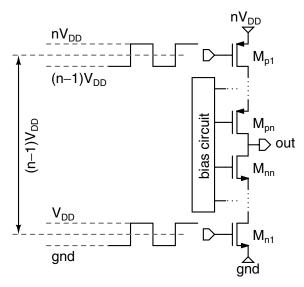

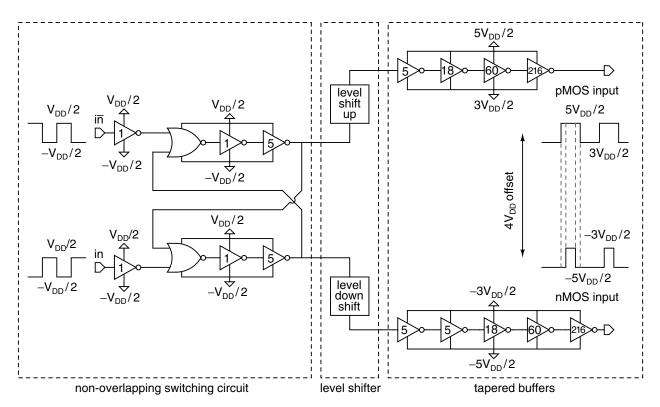

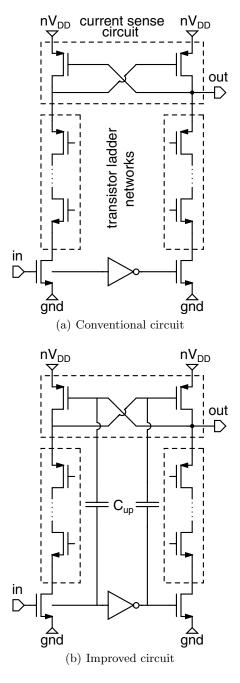

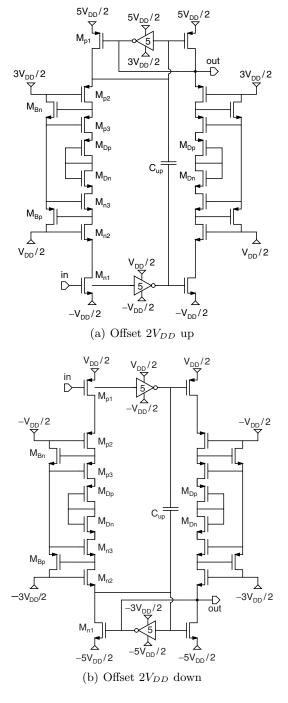

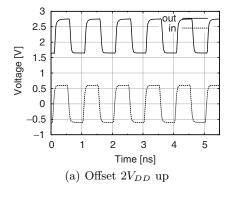

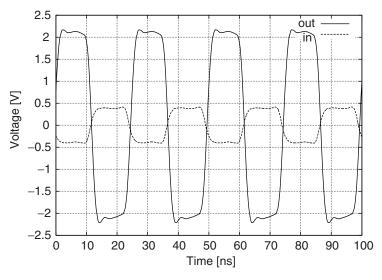

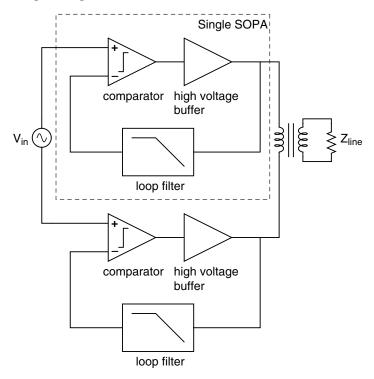

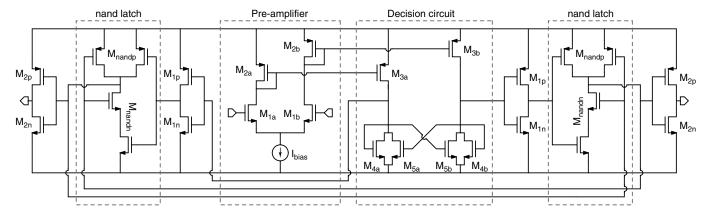

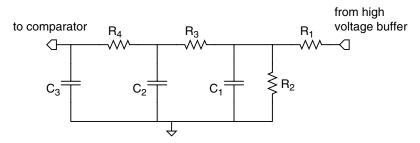

To satisfy the system requirement of voltage clipping occurring with a probability of less than  $1 \cdot 10^{-7}$ , the circuitry must pass the peak voltages corresponding to this probability. To do this, the system must accommodate a