### **University of South Florida** Scholar Commons

Graduate Theses and Dissertations

Graduate School

June 2017

# Speed, Power Efficiency, and Noise Improvements for Switched Capacitor Voltage Converters

Orhun Aras Uzun University of South Florida, oau255@gmail.com

Follow this and additional works at: http://scholarcommons.usf.edu/etd

Part of the Electrical and Computer Engineering Commons

#### Scholar Commons Citation

Uzun, Orhun Aras, "Speed, Power Efficiency, and Noise Improvements for Switched Capacitor Voltage Converters" (2017). Graduate Theses and Dissertations.

http://scholarcommons.usf.edu/etd/6970

This Dissertation is brought to you for free and open access by the Graduate School at Scholar Commons. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact scholarcommons@usf.edu.

Speed, Power Efficiency, and Noise Improvements for Switched Capacitor Voltage Converters

by

#### Orhun Aras Uzun

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy Department of Electrical Engineering College of Engineering University of South Florida

Major Professor: Selçuk Köse, Ph.D. Lingling Fan, Ph.D. İsmail Uysal, Ph.D. Hao Zheng, Ph.D. Mücahit Kozak, Ph.D.

> Date of Approval: May 24, 2017

Keywords: DC-DC power conversion, switched capacitor circuits, reconfigurable architectures, transient response, integrated circuits

Copyright © 2017, Orhun Aras Uzun

#### ACKNOWLEDGMENTS

Firstly, I would like to thank my advisor Selcuk Kose for his help and support in this work and especially for his extraordinary patience. I would also like to offer my gratitude to my committee members, Lingling Fan, Ismail Uysal, Hao Zheng and Mucahit Kozak.

The chip fabrication in Canada would not have been possible without the help of Dr. Li Chen and his group. I would like to offer special thanks to my friends Rui Liu, Yuanqing Li, Xing Zhao, Mo Chen and Yi Ren not only for their help with the design but also for making my time in Canada very delightful.

For their help at USF, I would like to thank to my friends, Ismail Uluturk, Emre Seyyal, Majdi Ababneh, Bahadir Celebi, Ali Gorcin, Alphan Sahin, Fatih Demir, Ertugrul Guvenkaya, Esad Ankarali, Murat Karabacak, Berker Pekoz, Merve Kacar, Anas Tom, Weize Yu and Longfei Wang. I also would like to offer special thanks to Meg Floyd, Ben Floyd and all my friends from Turkey who have supported me throughout this process.

I would like to offer my gratitude for my previous advisors Devrim Aksin and Turker Kuyel, without their guidance I would not have been able to develop my understanding in electronics.

Finally I would like to thank my family for their unconditional support.

# TABLE OF CONTENTS

| LIST OF TABLES       |                                                                                      | iv                                      |

|----------------------|--------------------------------------------------------------------------------------|-----------------------------------------|

| LIST OF FIGURES      |                                                                                      | v                                       |

| ABSTRACT             |                                                                                      | ix                                      |

| CHAPTER 1: INT       | RODUCTION                                                                            | 1                                       |

| 1.1 On-Chi           | p Voltage Converters                                                                 | 3                                       |

| 1.1.1                | LDO Regulators                                                                       | 4                                       |

| 1.1.2                | Buck Converters                                                                      | 5                                       |

| 1.1.3                | Switched Capacitor Voltage Converters                                                | 6                                       |

| 1.2 Objecti          | ves                                                                                  | 7                                       |

| 1.3 Organiz          | zation                                                                               | 7                                       |

| ТО                   | VERAGING ON-CHIP SC VOLTAGE REGULATORS IMPROVE HARDWARE SECURITY, TRANSIENT RESPONSE | 0                                       |

|                      | D POWER SUPPLY INTEGRITY                                                             | 9                                       |

| 2.1 Introdu          |                                                                                      | 9                                       |

|                      | ound and Motivation                                                                  | 11                                      |

|                      | ter-Gating                                                                           | 14                                      |

| 2.3.1                | i i                                                                                  | 15                                      |

|                      | 2.3.1.1 Switch Driving Loss                                                          | 16                                      |

|                      | 2.3.1.2 Switch Buffer Loss                                                           | 17<br>17                                |

|                      | 2.3.1.3 Parasitic Capacitance Losses 2.3.1.4 Control and Reference Losses            | 18                                      |

| 2.3.2                |                                                                                      | 10                                      |

| 2.3.2                | Power Efficiency of SC Converters with Different Flying Ca-<br>pacitor Values        | 18                                      |

| 2.3.3                | •                                                                                    | 20                                      |

| ۵.5.5                | 2.3.3.1 On - Off Transition Time of Individual Regulators                            | 21                                      |

|                      | 2.3.3.2 Area Overhead                                                                | 21                                      |

|                      | 2.3.3.3 Power Overhead                                                               | 21                                      |

|                      | 2.3.3.4 Output Noise                                                                 | 21                                      |

| 2.4 Circuit          | Level Design of Converter-Gating                                                     | 21                                      |

| 2.4 Circuit<br>2.4.1 |                                                                                      | $\begin{array}{c} 21 \\ 22 \end{array}$ |

| 2.4.1 $2.4.2$        |                                                                                      | 24                                      |

| 2.4.2                |                                                                                      | 24                                      |

|                      | Converter-Gating as a Side-Channel Attack Countermeasure                             | 25                                      |

| 2.5     | Functional Verification of Converter-Gating                         | 26 |

|---------|---------------------------------------------------------------------|----|

|         | 2.5.1 Power Efficiency                                              | 27 |

|         | 2.5.2 Configurable 2:1 to 1:1 SC Voltage Converter                  | 28 |

|         | 2.5.3 Voltage Maps of the Power Grid                                | 28 |

|         | 2.5.4 Output Voltage Ripple                                         | 30 |

|         | 2.5.5 Input Current Scrambling with Pseudo-Random Converter-Gating  | 32 |

| 2.6     | Conclusions                                                         | 34 |

| CHAPTER | 3: TRANSIENT RESPONSE ANALYSIS OF RECONFIGURABLE                    |    |

|         | AND RESPONSE ENHANCED CONVERTERS AND TECHNIQUES                     |    |

|         | TO IMPROVE RESPONSE TIME                                            | 35 |

| 3.1     | Introduction                                                        | 35 |

| 3.2     | Analysis of Dynamic Behavior in SC Voltage Converters               | 39 |

|         | 3.2.1 Analysis of the Ideal Voltage Conversion Ratio                | 40 |

|         | 3.2.1.1 Direct Analysis                                             | 40 |

|         | 3.2.1.2 Systematic Analysis                                         | 42 |

|         | 3.2.2 Charge Transfer in a 1/1 Converter                            | 45 |

|         | 3.2.3 Charge Transfer in an m to n Converter                        | 50 |

| 3.3     | Transient Response Time Implications on Reconfigurable or Response- |    |

|         | Enhanced Converters                                                 | 54 |

|         | 3.3.1 In Reconfigurable Converters                                  | 56 |

|         | 3.3.2 In Response-Enhanced Converters                               | 61 |

|         | 3.3.2.1 Enhancing the Response with Interrupt States                | 62 |

|         | 3.3.2.2 Enhancing Response with Conversion Ratio Manipulation       | 64 |

| 3.4     | Addressing the Transient Response Issues                            | 64 |

| 3.5     | Conclusion                                                          | 70 |

| CHAPTER | 4: IMPLEMENTATION OF AN SC CONVERTER WITH A FAST                    |    |

|         | CONTROL LOOP USING HYBRID CONTROL METHOD IN                         |    |

|         | 28NM FDSOI TECHNOLOGY                                               | 71 |

| 4.1     | Introduction                                                        | 71 |

| 4.2     | Architecture of the Implemented Design                              | 72 |

|         | 4.2.1 Hybrid Control Method                                         | 73 |

|         | 4.2.2 Adaptive Gain Selection                                       | 74 |

| 4.3     | Implementation of Sub Circuits                                      | 75 |

|         | 4.3.1 Switched Capacitor Core                                       | 75 |

|         | 4.3.2 Comparators                                                   | 78 |

|         | 4.3.3 Oscillator                                                    | 81 |

|         | 4.3.4 Control Logic                                                 | 82 |

|         | 4.3.5 Top Level                                                     | 83 |

| 4.4     | Testing and Expected Results                                        | 85 |

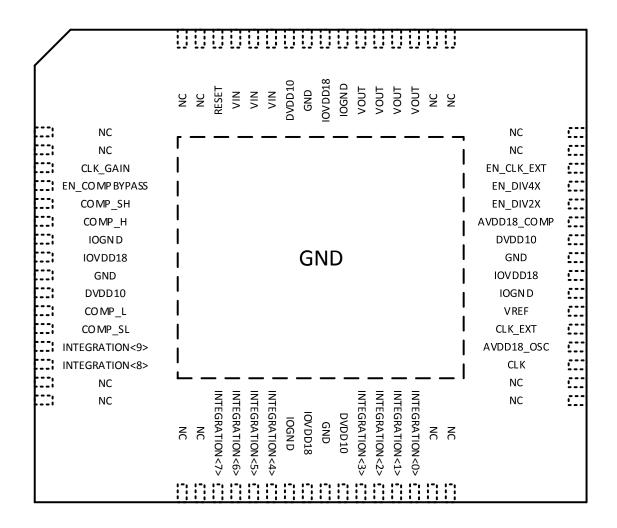

| 2.1     | 4.4.1 Options, Pins and Configuration                               | 87 |

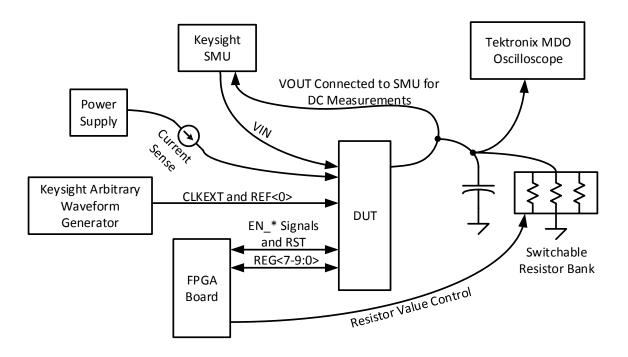

|         | 4.4.2 Test Scenarios                                                | 90 |

|         | 4.4.2.1 Checks                                                      | 91 |

|         | 4.4.2.2 Efficiency and DC Performance                               | 92 |

|         | 4.4.2.3 Transient Response                                          | 93 |

| 93       |

|----------|

| 94       |

| 94       |

| 95       |

| 97       |

| 99       |

| 105      |

| 106      |

| 113      |

| End Page |

|          |

# LIST OF TABLES

| Table 3.1 | Comparison of Charge Transfer in Different Configurations | 53 |

|-----------|-----------------------------------------------------------|----|

| Table 4.1 | Pins and Descriptions                                     | 88 |

# LIST OF FIGURES

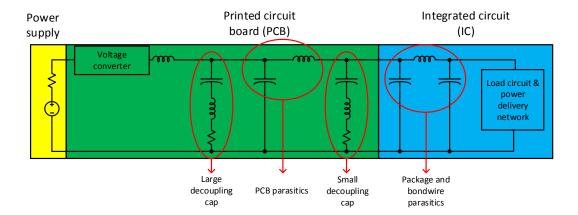

| Figure 1.1  | Off-chip voltage conversion and regulation offer highly efficient and flexible solution but the parasitics in between the voltage converter and the load circuit may cause problems for systems with stringent requirements. | 2  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

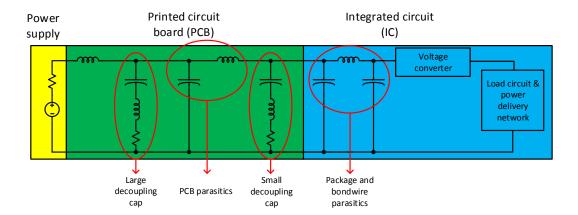

| Figure 1.2  | On-chip voltage conversion and regulation is more challenging as the energy storage elements such as inductors and capacitors are harder to implement on-chip but on-chip system bypasses all the parasitics.                | 3  |

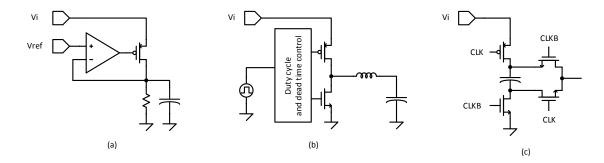

| Figure 1.3  | Comparison of commonly used on-chip voltage converters a) low dropout regulator b) buck converter c) switched capacitor converter.                                                                                           | 4  |

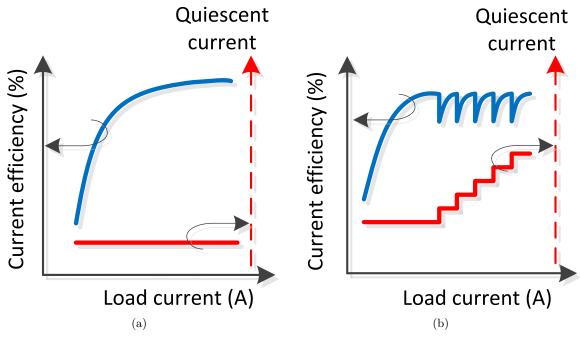

| Figure 2.1  | Current efficiency of different LDO regulators.                                                                                                                                                                              | 11 |

| Figure 2.2  | Power efficiency of different SC converters.                                                                                                                                                                                 | 13 |

| Figure 2.3  | Power efficiency of buck converters.                                                                                                                                                                                         | 15 |

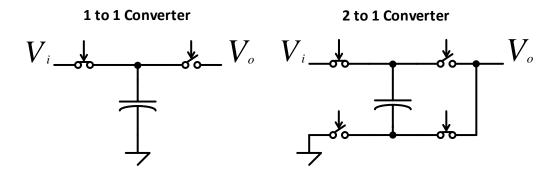

| Figure 2.4  | Two different topologies for SC voltage converters where the MOSFET switches are controlled with non-overlapping $Clock$ and complimentary $ClockB$ signals.                                                                 | 15 |

| Figure 2.5  | Power conversion efficiency of various SC voltage converter with different flying capacitor values.                                                                                                                          | 19 |

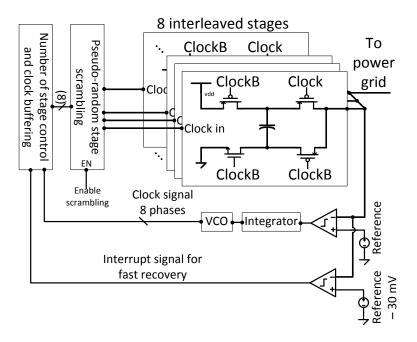

| Figure 2.6  | Top level schematic of the proposed converter-gating system.                                                                                                                                                                 | 22 |

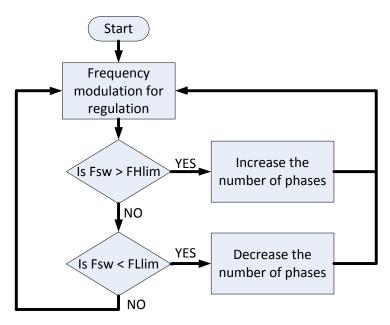

| Figure 2.7  | Proposed converter-gating algorithm that enables workload aware activity management of distributed SC voltage converters.                                                                                                    | 23 |

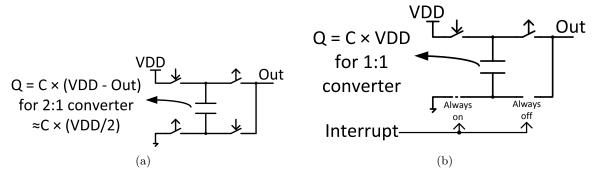

| Figure 2.8  | Amount of charge transferred to the output note in a single cycle for a) a conventional 2:1 SC voltage converter and b) a 2:1 converter that is configured as a 1:1 converter by controlling the illustrated switches.       | 24 |

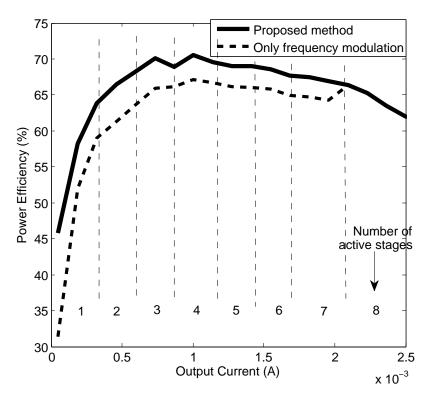

| Figure 2.9  | Power conversion efficiency of an eight stage interleaved SC voltage converter with and without applying the proposed converter-gating technique.                                                                            | 27 |

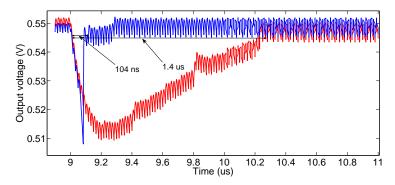

| Figure 2.10 | Transient response of a 2:1 SC converter when the load current increases from 1 mA to 3 mA.                                                                                                                                  | 28 |

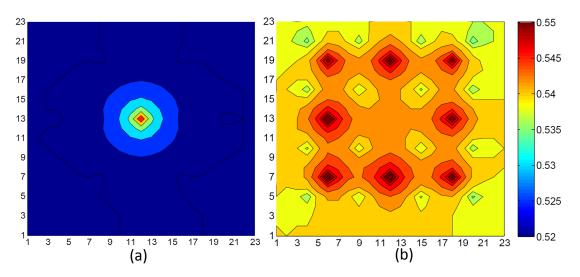

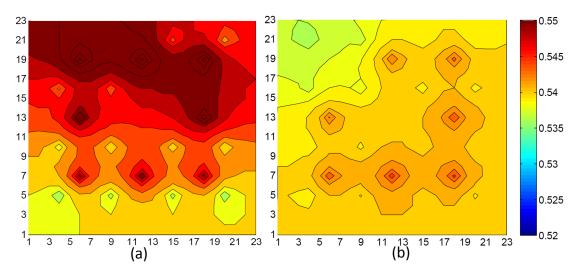

| Figure 2.11 | Voltage map of the power grid when the load circuits are uniformly distributed.                                                                                                                                                                                                                                                                                                                                                                                 | 29 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.12 | Voltage map of the power grid when the load circuits located at the upper-left corner of the power grid enters idle state and all of the eight stages of an SC converter are distributed uniformly.                                                                                                                                                                                                                                                             | 29 |

| Figure 2.13 | Output voltage ripple of a four phase interleaved SC voltage converter with different number of active stages.                                                                                                                                                                                                                                                                                                                                                  | 30 |

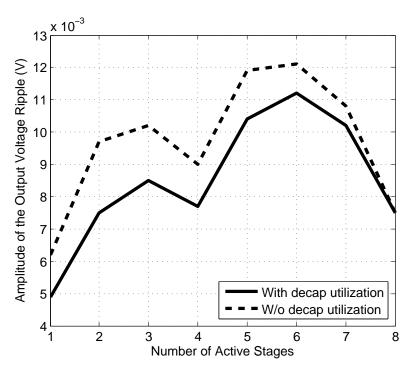

| Figure 2.14 | Amplitude of the output voltage when the inactive converter stages are utilized as decoupling capacitor (solid line) and without decoupling capacitor utilization (dashed line).                                                                                                                                                                                                                                                                                | 31 |

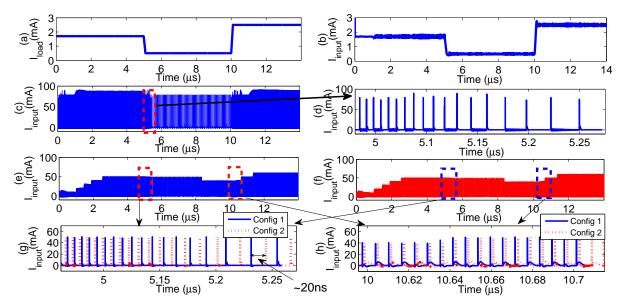

| Figure 2.15 | Load current profile and corresponding input current profile for various voltage regulation schemes.                                                                                                                                                                                                                                                                                                                                                            | 32 |

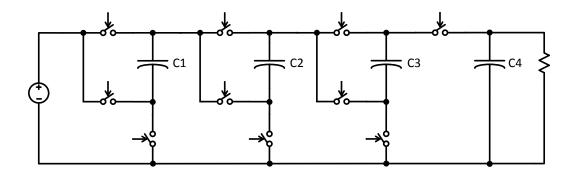

| Figure 3.1  | Comparison of $1/1$ and $1/2$ SC converters with abstract switches.                                                                                                                                                                                                                                                                                                                                                                                             | 36 |

| Figure 3.2  | Conventional methods to implement control loops for SC DC-DC converters.                                                                                                                                                                                                                                                                                                                                                                                        | 38 |

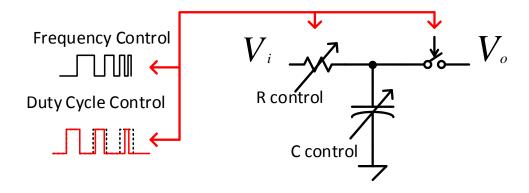

| Figure 3.3  | Some of the converter parameters that are used in regulation.                                                                                                                                                                                                                                                                                                                                                                                                   | 38 |

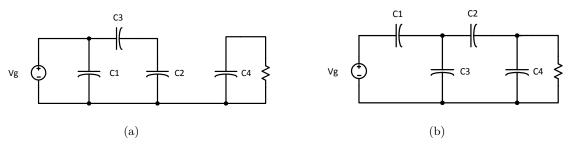

| Figure 3.4  | Simplified $5/1$ up converter                                                                                                                                                                                                                                                                                                                                                                                                                                   | 42 |

| Figure 3.5  | 2 phases of a $5/1$ up converter                                                                                                                                                                                                                                                                                                                                                                                                                                | 43 |

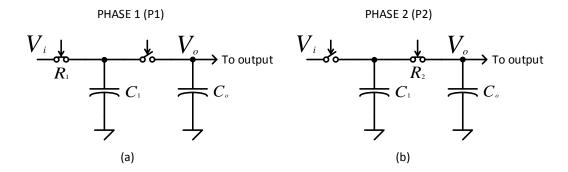

| Figure 3.6  | Two phases of operation for a $1/1$ SC converter; (a) phase 1 (charging phase) and (b) phase 2 (discharging phase).                                                                                                                                                                                                                                                                                                                                             | 46 |

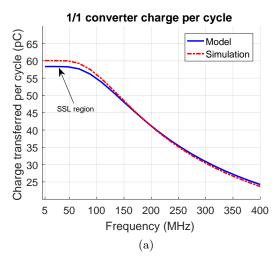

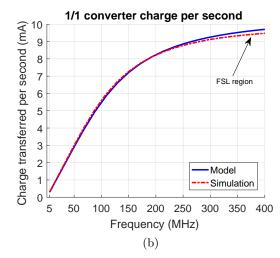

| Figure 3.7  | Charge transfer comparison in a $1/1$ SC converter over 5-400 MHz frequency range between the model and the simulation; (a) per cycle charge transfer (b) per second charge transfer                                                                                                                                                                                                                                                                            | 48 |

| Figure 3.8  | Per second charge transfer comparison in a $1/1$ SC converter over 0 to 1 V output voltage range between the model and the simulation.                                                                                                                                                                                                                                                                                                                          | 50 |

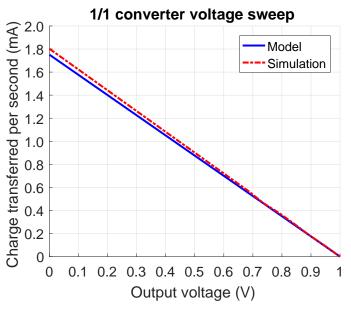

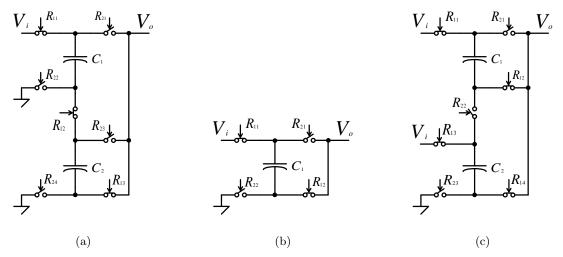

| Figure 3.9  | Different SC converter topologies with abstract switches that can be implemented in a reconfigurable converter; a) $1/3$ converter, b) $1/2$ converter, and c) $2/3$ converter.                                                                                                                                                                                                                                                                                 | 51 |

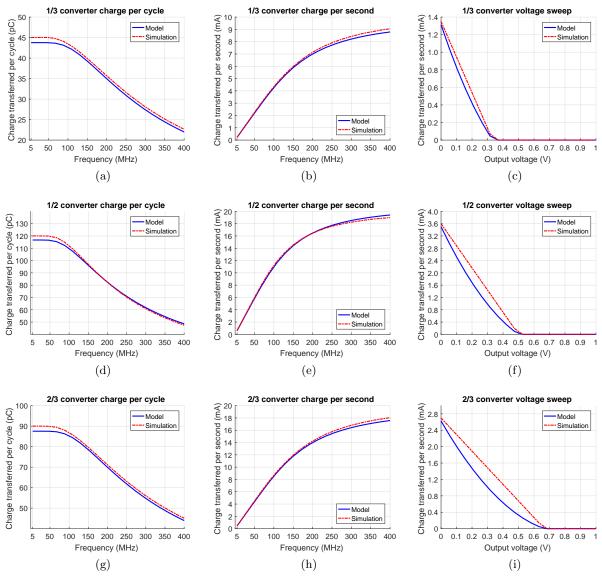

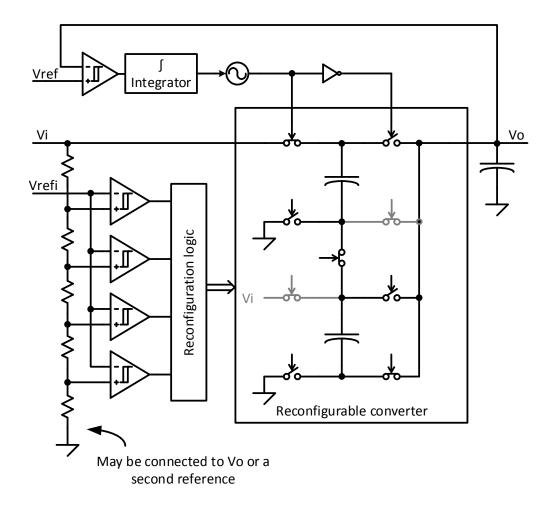

| Figure 3.10 | Comparison of charge transfer between the generalized model and the simulation in converters with different conversion ratios; (a), (d), (g) per cycle transfer for $1/3$ , $1/2$ , and $2/3$ converters over 5-400 MHz frequency range, (b), (e), (h) per second transfer for $1/3$ , $1/2$ , and $2/3$ converters over 5-400 MHz frequency range, (c), (f), (i) per second transfer for $1/3$ , $1/2$ , and $2/3$ converters over 0-1 V output voltage range. | 55 |

| Figure 3.11 | A reconfigurable SC converter with a conventional control loop and reconfiguration logic.                                                                                                                                                                                                                                                                                                                                                                       | 57 |

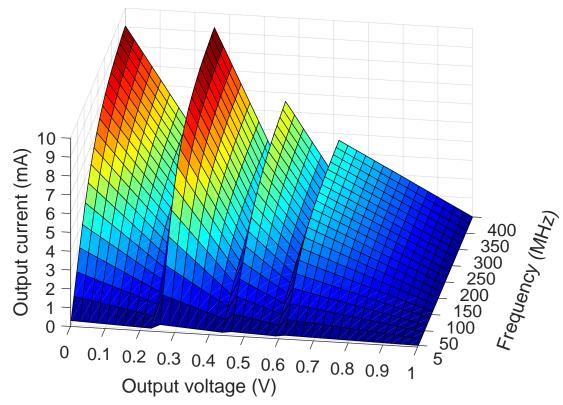

| Figure 3.12 | Output current (charge transfer per second) of a reconfigurable SC converter that is reconfigured to maintain high efficiency over 0 to 1 V output voltage range.                                          | 58 |

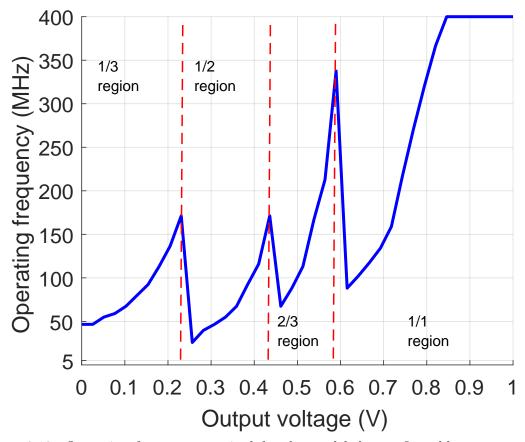

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.13 | Operating frequency required for the modeled reconfigurable converter over 0-1 V output voltage to maintain 2 mA output current.                                                                           | 60 |

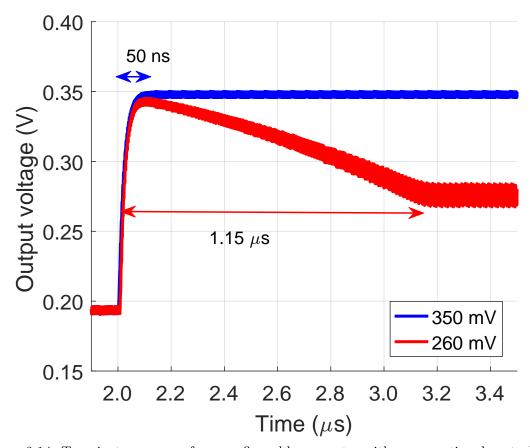

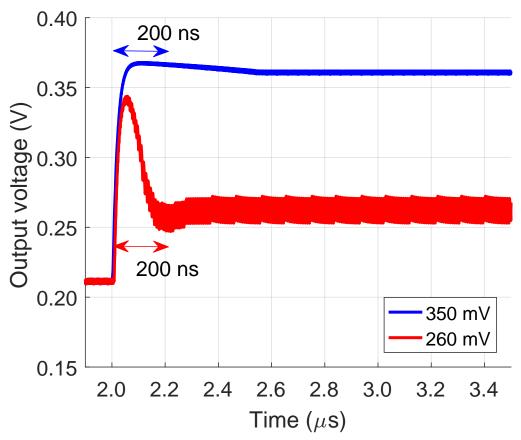

| Figure 3.14 | Transient response of a reconfigurable converter with a conventional control loop given in Fig. 3.11 to a voltage reference step from 210 mV to 350 mV and a voltage reference step from 210 mV to 260 mV. | 61 |

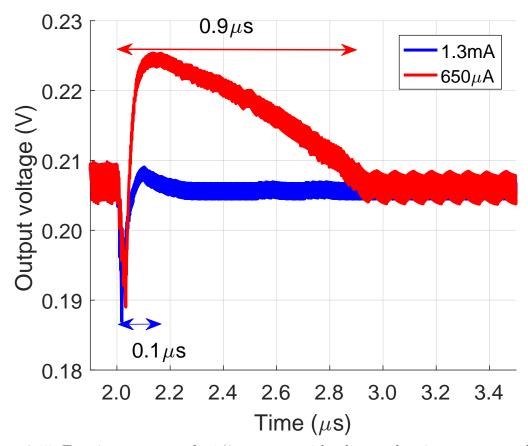

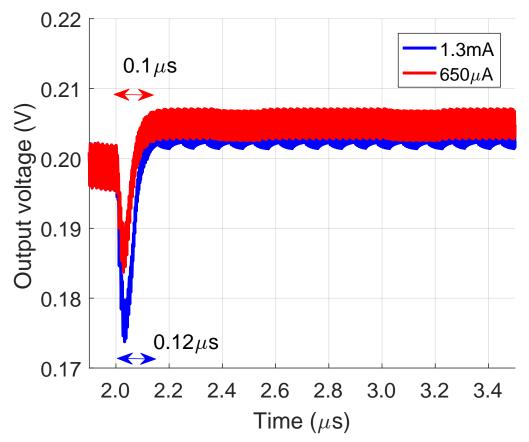

| Figure 3.15 | Transient response of a $1/3$ converter with a loop and an interrupt state that sets the control parameter to the maximum value when the output voltage drops more than $30 \text{ mV}$ .                  | 65 |

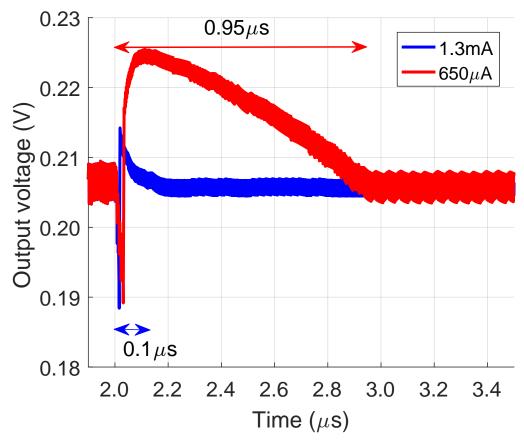

| Figure 3.16 | Transient response of a $1/3$ converter while adaptively reconfiguring to a $1/2$ converter to speed up the recovery when the voltage drop is sensed.                                                      | 65 |

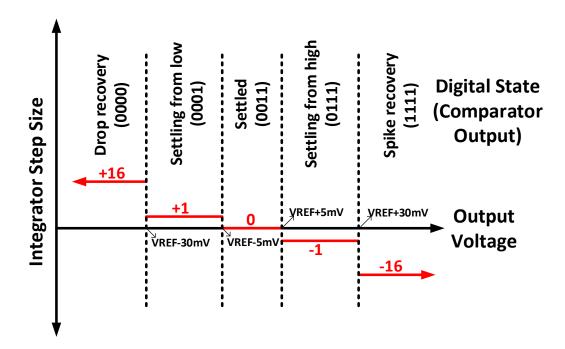

| Figure 3.17 | Proposed gain modification scheme to prevent overshoots or undershoots.                                                                                                                                    | 66 |

| Figure 3.18 | Implementation of the proposed method by using 4 comparators.                                                                                                                                              | 67 |

| Figure 3.19 | Transient response of the proposed control method to a voltage reference change from 210 mV to 350 mV and from 210 mV to 260 mV.                                                                           | 68 |

| Figure 3.20 | Transient response of a $1/3$ converter with the proposed control method.                                                                                                                                  | 69 |

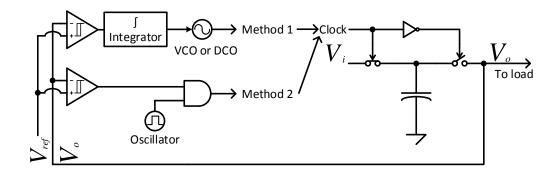

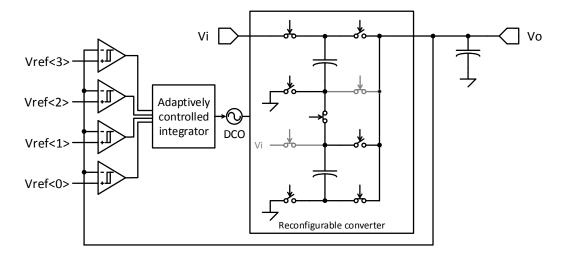

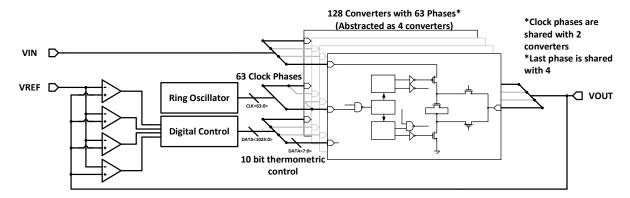

| Figure 4.1  | Simplified block diagram of the implemented design.                                                                                                                                                        | 73 |

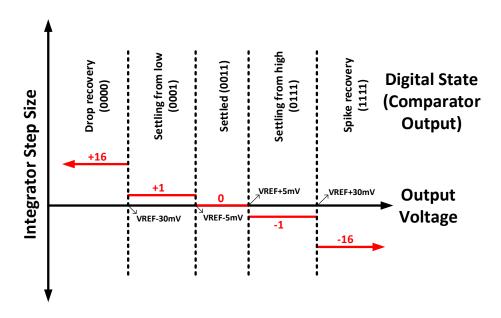

| Figure 4.2  | Gain or the step size of the integrator is modified according to the difference between the output voltage and the reference voltage to help fast recovery.                                                | 75 |

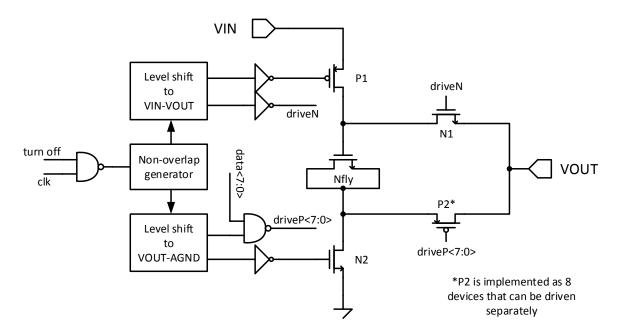

| Figure 4.3  | Switched capacitor core includes a divided switch which has parts that can be driven separately to allow charge control to the output.                                                                     | 77 |

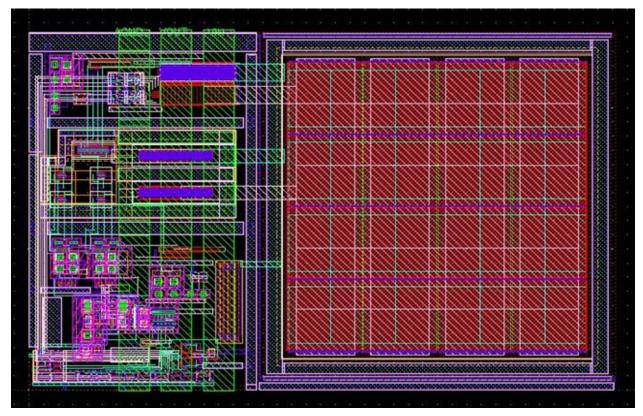

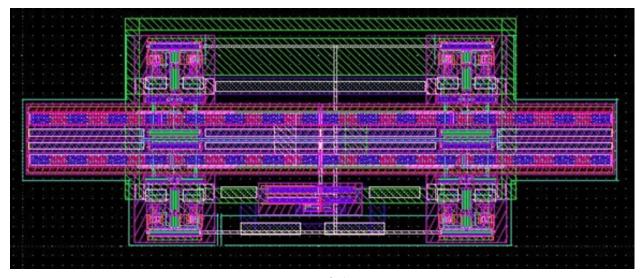

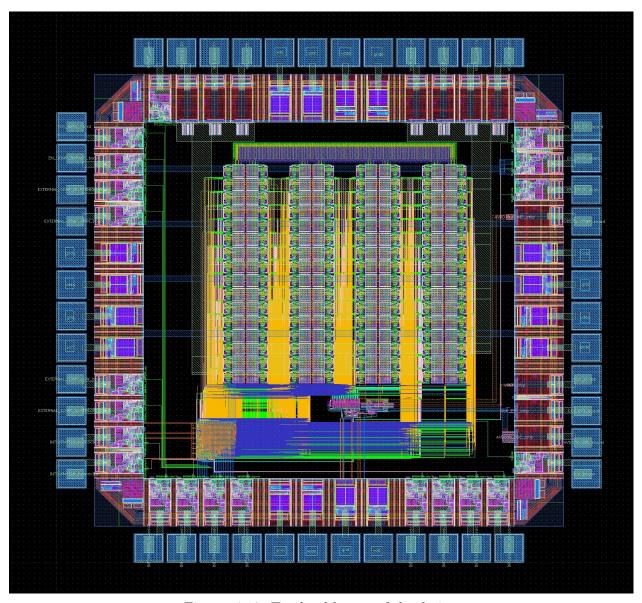

| Figure 4.4  | Layout of the switched capacitor core circuit                                                                                                                                                              | 78 |

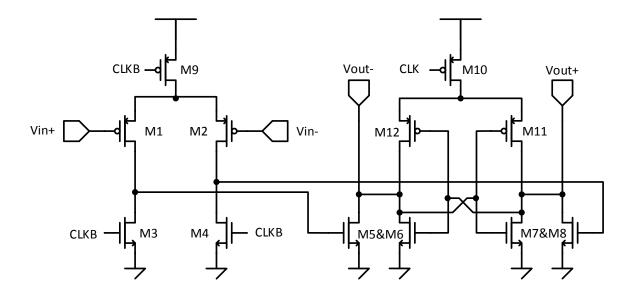

| Figure 4.5  | A dynamic comparator is used in this design to reduce DC current.                                                                                                                                          | 80 |

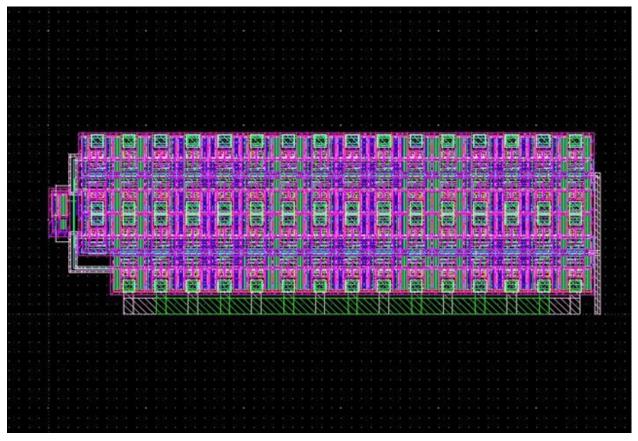

| Figure 4.6  | Layout of the 4 comparators                                                                                                                                                                                | 80 |

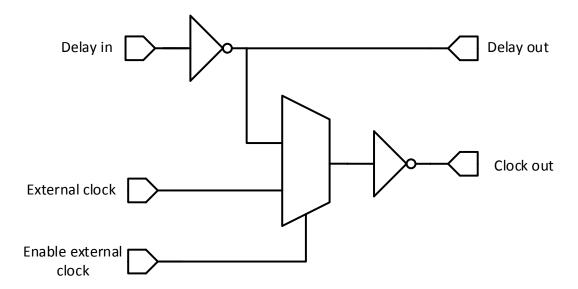

| Figure 4.7  | The delay cell of the oscillator has buffers to maintain uniform phase distribution.                                                                                                                       | 81 |

| Figure 4.8  | Layout of the ring oscillator                                                                                                                                                                              | 83 |

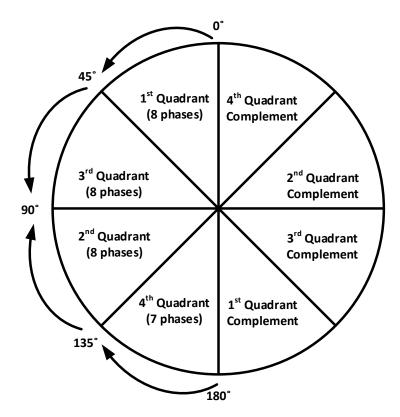

| Figure 4.9  | Sequence used to turn SC cores on/off is chosen to minimize the output voltage ripple by distributing the clock phases as evenly as possible.                                                              | 84 |

| Figure 4.10 | Top level layout of the design                                                          | 86 |

|-------------|-----------------------------------------------------------------------------------------|----|

| Figure 4.11 | Package and pin configuration of the design                                             | 87 |

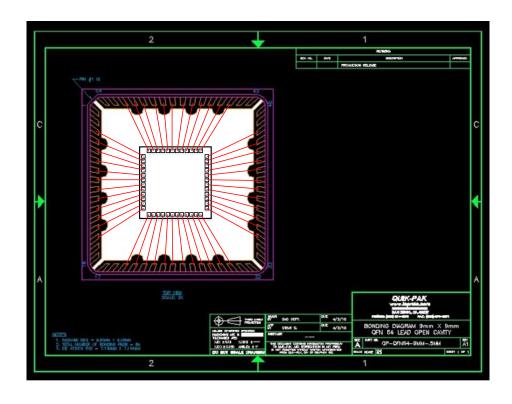

| Figure 4.12 | Bondwire diagram                                                                        | 88 |

| Figure 4.13 | Test setup includes several different configurations for DC and transient measurements. | 91 |

#### ABSTRACT

Switched-capacitor (SC) DC-DC converters provide a viable solution for on-chip DC-DC conversion as all the components required are available in most processes. However, power efficiency, power density characteristics of SC converters are adversely affected by the integration, and characteristics such as response time and noise can be further improved with an on-chip converter. An analysis on speed, power efficiency, and noise performance of SC converters is presented and verified using simulations. Based on the analysis two techniques, converter-gating and adaptive gain control, are developed. Converter-gating uses a combination of smaller stages and reconfiguration during transient load steps to improve the power efficiency and transient response speed. The stages of the converter are also distributed across the die to reduce the voltage drop and noise on power supply. Adaptive gain control improves transient response through manipulation of the gain of the integrator in the control loop. This technique focuses on improving the response time during converter reconfiguration and offers a general solution to transient response improvement instead of focusing on the worst case scenario which is usually the largest transient load step. The techniques developed are then implemented in ST 28nm FDSOI process and test methodologies are discussed.

#### CHAPTER 1:

#### INTRODUCTION

As the demand for high performance electronics in industrial, military and consumer markets is growing, wide variety of solutions are designed and developed. These solutions, regardless of the requirements they fulfill, always need a power management and delivery system as they all rely on a power supply that behaves within specific limitations. For example, a data conversion circuit used in high precision data conversion may require a power supply that has very low voltage ripple around a constant voltage, or a microprocessor may require a power supply that can change its output voltage for dynamic voltage scaling (DVS). So, invariably all the electronic solutions require a power management and delivery system to a certain degree even if it is something as simple as a carefully designed metal lines or as complex as a DVS system. This requirement makes the research in power management and delivery very valuable as the power section of a circuit usually determines the maximum achievable performance.

With the scaling of integrated circuits, however, the power delivery is becoming the bottleneck for performance [1, 2]. Because the integrated circuit operating voltages scale down with the

advancements in processing technology while the battery and external power source voltages remain

relatively constant. This fact, combined with the increased power consumption of the integrated

circuits put stringent requirements on power management and delivery systems since now a higher

conversion ratio is needed and a higher amount of current needs to be delivered. The two aspects of

the power delivery problem therefore is addressed using two approaches, i) by implementing high efficiency, high conversion ratio DC-DC converters to reduce the losses during voltage conversion and

to reduce the current requirement, ii) by employing methods such as DVS at the load side to reduce

the total power needed by the load circuit and by optimizing the on-chip power delivery. These

Figure 1.1: Off-chip voltage conversion and regulation offer highly efficient and flexible solution but the parasitics in between the voltage converter and the load circuit may cause problems for systems with stringent requirements.

two approaches can be implemented together using a single DC-DC converter that has configurable output voltage level for DVS and a high conversion ratio.

Conventionally DC-DC conversion and the power management and delivery is implemented outside the load circuit using discrete elements or dedicated integrated circuits as shown in Fig. 1.1. In the system shown, the voltage converter is implemented as a separate element on the printed circuit board (PCB) and once the voltage is converted to a usable voltage for the load and regulated it is given to the load circuit which is an integrated circuit. Although this system offers a very easily scalable and high efficiency solution, the PCB and IC package parasitics may limit the performance. For example, often two decoupling capacitors with different values are placed on the PCB to act as a reservoir and respond to the load transients quickly. However, even if the decoupling capacitors can be placed next to the IC, the package parasitics still limit the fastest response and if the parasitics between the voltage converter and the decoupling is large enough, voltage converter may not be able to replenish the charge lost from the capacitors fast enough to maintain a constant voltage, introducing higher noise and drop on the power supply. Moreover, the power reduction features such as DVS rely heavily on being able to change the voltage levels of the power supply in short amount of time. With an external voltage converter, the amount of time required to change the power supply voltage is limited by the PCB parasitics and the decoupling capacitors.

Figure 1.2: On-chip voltage conversion and regulation is more challenging as the energy storage elements such as inductors and capacitors are harder to implement on-chip but on-chip system bypasses all the parasitics.

The shortcomings of an external power delivery and management system can be overcome by integrating the voltage converter and power delivery system into the IC. Such a system is shown in Fig. 1.2. With on-chip voltage converters and power delivery, all the parasitics of the PCB can be bypassed and the load power supply voltage can be regulated within a loop that is much closer to the load. Having lower parasitics on the power delivery path can help with simplifying PCB design requirements, while the on-chip voltage regulation loop can help achieving very fast voltage level shifting. Moreover, an on-chip voltage conversion scheme greatly reduces the PCB footprint which is important in mobile applications where the physical size is very limited.

As a result, the on-chip voltage conversion is becoming common for power delivery and management solutions. There are different architectures that can be used to implement on-chip voltage converters, so the merits of the on-chip voltage converters and comparison of commonly used architectures will be discussed next.

#### 1.1 On-Chip Voltage Converters

To enable complete on-chip power conversion and delivery, it is necessary to reduce the total occupied area of these devices while still maintaining high power efficiency. The total area occupied by the voltage converter is important as it is directly related to the total manufacturing cost of

Figure 1.3: Comparison of commonly used on-chip voltage converters a) low dropout regulator b) buck converter c) switched capacitor converter.

the die, it is also important to keep the load as close to the voltage converter as possible. On-chip components usually have lower efficiency since the processes are usually optimized for the operation of the transistors and not for the passive devices such as capacitors and inductors. As it will be explained later, these two objectives are often conflict, therefore the performance of on-chip voltage converters is usually determined by their power density (W/mm<sup>2</sup>) and power efficiency (%)

In modern devices, on-chip voltage converters are usually implemented using three dominant topologies. These topologies are low dropout regulators (LDO), buck converters (inductance-based), switched capacitor converters (capacitance-based). There are also hybrid configurations available but these are out of the scope of this work [3]. The advantages and disadvantages of these converters are summarized in the next sections.

#### 1.1.1 LDO Regulators

LDOs offer simplest and most widely used solution to the power delivery problem. An LDO includes a power transistor controlled by a feedback loop to stabilize its output voltage. This type of regulators provide, fast response as the feedback loop is usually only limited by the stable bandwidth of the error amplifier. The power to the output flows through the power transistor, and its power density is usually limited by the current density of transistors available in a given technology which is usually high enough to surpass the density of the other two topologies. Also because the output is usually controlled in a continuous time loop, these type of converters have clean output signals which does not include ripples and is limited by the noise performance of the

device. However this type of regulators suffer from large power efficiency drop as the difference between output and the input voltage gets higher. The reason behind this is the fact that the same current that is going to the output has to flow through the adjustable resistor which is the power transistor. This means that for every unit current that is delivered to the output at the voltage  $V_o$  has to come from the voltage supply  $V_i$ . Therefore the efficiency of the LDOs are ultimately limited by  $V_o/V_i$  ratio. Because of their efficiency limitation, LDOs reduce the benefits of using DVS, and are not suitable for high conversion ratios. LDOs however can be used to generate cleaner outputs from a noisy power supply, and are suitable for on-chip distribution because of their high power density [4–7].

#### 1.1.2 Buck Converters

Buck converters are inductance based converters. In buck converters the current and direction of the current on an inductance is adjusted to create a specific output voltage. The conventional method of controlling the current flow through the inductance is using two power transistors, one connected to supply voltage and the other connected to ground. The switching activity in this configuration causes a varying current to go through the inductance, which in turn creates the output voltage. The switching activity causes output to have a certain amount of ripple voltage, causing spurs in the spectrum of the output voltage. Usually this type of converters are implemented in a duty cycle based control loop. Duty cycle determines the time spent during power transistor connected to the supply or the one that is connected to the ground. Controlling the duty cycle with enough resolution allows this type of converters to generate a wide range of output voltages. From efficiency perspective, the buck converter is efficient for the higher conversion ratios, as the power is not wasted on a resistor. Instead it is stored on the inductance and converted to another voltage. In an ideal buck converter, for every unit of current delivered to the load at half of the supply voltage requires only half unit of current as the inductance is used in the operation. However power efficiency of these converters are affected by the losses in the circuit and therefore is not 100 % except in ideal case. These losses include, parasitic losses of the inductance, switching losses and switch driving losses. State of the art buck converters are able to deliver high output power at high efficiencies. Buck converters are suitable for DVS systems as output voltage range is large, and this type of converters provide high power density if not as high as LDOs. However the implementation of high quality inductances on-chip remains to be a problem even in modern technologies, inductors occupy a large area with large overhead (*i.e.* active area underneath is usually left unused) and are not very scalable meaning implementing many small inductors is not as area efficient as implementing a large inductor.

#### 1.1.3 Switched Capacitor Voltage Converters

Switched capacitor voltage converters use capacitors in different configurations to deliver power to output. Usually this type of converters have a charging phase when the capacitors are charged to a pre-determined voltage level, and a discharging phase during which the charge stored on the capacitors are delivered to the output. Frequency of operation as well as the duty cycle can be and is being used in controlling the output voltage levels. However since capacitors charge to a certain voltage in a certain configuration, these converters usually have a single ideal conversion ratio at which they generate ideally 100 % efficiency. The output voltage can be changed using frequency and duty cycle but the efficiency for a single converter is ultimately limited by  $V_o/(n \times V_i)$  where n is the conversion ratio for a specific configuration [8]. To overcome dependency of efficiency on topology, converters with multiple ratios are being used in literature. The power efficiency of these converters are again reduced by the losses which are parasitics of capacitors, switching losses and switch driving losses. State of the art SC converters are as efficient as inductive converters with comparable power densities [9]. This type of converters are suitable for DVS systems, and provide a medium range power density and benefit from the high quality and dense capacitors provided by the technology kit.

As summarized above three types of converters are main candidates for on-chip voltage conversion. In this work SC converters are chosen for following reasons, i) SC converters do not require implementation of elements that are not in baseline CMOS technology (advantage over buck converters) therefore easier to integrate on chip, ii) SC converters provide higher efficiencies

compared to LDOs and in par with the buck converters, iii) SC converters are optimum for low-medium output power with high efficiency and the power output is highly scalable.

#### 1.2 Objectives

To enable on-chip voltage conversion using SC converters certain performance metrics of SC converters must be improved. First, power efficiencies comparable with external DC-DC converters have to be achieved at high power densities, because any degradation in power efficiency translates as increased power consumption which may hinder the benefits of using an on-chip voltage converter. Second, the advantages of on-chip converters must be exploited to improve the power supply integrity. Third, the transient response of the SC converters under different configurations or conditions must be improved for fast DVS applications and to reduce the power supply noise during load transients. Fourth, the developed methods should be proven using simulations and silicon implementation.

#### 1.3 Organization

This work is organized as follows. In Chapter 2 the power efficiency is analyzed for SC converters and based on the analysis the converter-gating technique is introduced. This technique uses a combination of smaller SC converters to maintain high efficiency at lower output currents. Several other aspects of SC converters are also improved through using properties of the proposed method in Chapter 2.

In Chapter 3 the charge transfer in reconfigurable converters and converters with response enhancements is analyzed. Based on this analysis the implications of reconfiguration on transient response is discussed. The transient response of these converters are improved through using a new method which adaptively changes the gain of the integrator in the control loop.

In Chapter 4 the design procedure and the implementation details of a test chip in 28nm FDSOI technology is discussed. Each subcircuit is explained, test methodologies and future improvements are presented.

In Chapter 5 conclusions are drawn from the results and possible future work options are presented.

#### CHAPTER 2:

#

#### 2.1 Introduction

The continuous advancements in the semiconductor industry and transistors with smaller than 20 nm feature size have enabled the integration of multi-billion transistors on a single die [10, 11]<sup>1</sup>. With the failure of Dennard's scaling [12], however, only a fraction of the transistors on a die can operate at full voltage/frequency in order not to exceed the thermal design power (TDP) [13, 14]. A large proportion of the circuit blocks is either inactive (dark silicon) or in a reduced-power state (dim silicon) at any given time to satisfy the power and thermal constraints [15, 16]. Despite the significant amount of research and growing necessity for a holistic power optimization technique, existing efforts to minimize power dissipation are typically not coherent, as highlighted in the report for the NSF Workshop on Cross-layer Power Optimization and Management (CPOM'12) [17]. The existing research efforts are disjointed into two pieces: i) the dynamic and static power loss at the load circuits is minimized or ii) the power loss during power-conversion is minimized.

Circuits typically enter reduced power states when the workload is light to save power and reduce the cost of cooling. On-chip voltage regulators, however, operate indifferently under varying workload conditions and generally provide optimum efficiency for a certain output power. Since dynamically changing the design parameters of a voltage regulator under different workloads

<sup>&</sup>lt;sup>1</sup>This chapter was published in IEEE Journal on Emerging and Selected Topics in Circuits and Systems, vol. 4, no. 2, pp. 169-179, June 2014 "Converter-Gating: A Power Efficient and Secure On-Chip Power Delivery System" and in 2014 IEEE Computer Society Annual Symposium on VLSI, Tampa, FL, 2014, pp. 13-18 "Regulator-Gating Methodology with Distributed Switched Capacitor Voltage Converters". Permissions are included in Appendix B.

is difficult, existing power management techniques suffer from increased voltage conversion losses during idle states when the current demand is low [1, 18, 19].

Another growing concern is the security of the information that is processed or stored within ICs. Several techniques are used by attackers to obtain the secret information or functionality and a widely used non-invasive technique is the side channel power attacks. In these attacks, the correlation between the stored information (or functionality) and power consumption of the IC is exploited. Various input combinations are typically applied to the IC by an attacker. The correlation among the power consumption profiles for different input patterns is statistically analyzed to solve the secret key or learn the secret functionality [20]. Most of the side channel attacks can be mitigated if the internal power consumption is masked from the attacker by either: i) injecting excess current at certain times to obtain a quite constant power consumption profile [21] or ii) scrambling the on-chip power consumption to disrupt the correlation between the logic operations and power consumption profile [22]. These widely used techniques significantly degrade the overall efficiency of the power delivery system [23, 24]. In this chapter, specialized power management techniques are presented as a countermeasure to side channel power attacks without degrading the power efficiency of the system.

Below are the primary contributions presented in this chapter:

- A workload aware, secure converter-gating technique is proposed in this chapter. Individual stages within an interleaved switched capacitor (SC) voltage converter are turned on and off based on the load current demand.

- A configurable SC voltage converter circuit is proposed that provides  $\sim 10 \times$  faster transient response as compared to the conventional SC converters.

- The amplitude of the output voltage ripple is reduced by utilizing the flying capacitors within deactivated converter stages as decoupling capacitors is proposed.

- An efficient countermeasure for side channel power attacks is proposed. The correlation between the internal logic operations and the overall chip power consumption is significantly disrupted with the proposed randomized converter-gating.

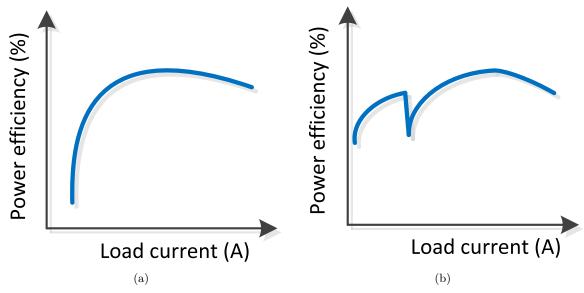

Figure 2.1: Current efficiency of different LDO regulators. a) Current efficiency of an LDO regulator increases monotonically with the load current when the quiescent current is constant. b) Adaptively controlling the quiescent current based upon the load current can improve the current efficiency.

The related background and motivation for the proposed voltage regulator management technique is provided in the next section.

The proposed converter-gating technique is explained in Section 2.3. The circuit level design details are offered in Section 2.4. The proposed converter-gating technique is validated with extensive simulations in Section 2.5. The chapter is concluded in Section 2.6.

#### 2.2 Background and Motivation

More than 32% of the overall power is dissipated during high-to-low voltage conversion before even reaching the load circuits in modern mobile platforms [25]. The primary reason for this huge power loss is that power delivery networks are designed to satisfy the stringent noise requirements under the worst-case loading conditions, which is typically the full utilization of the overall chip computing and memory resources when the current demand is the highest. The current or power efficiency of low-dropout (LDO) regulators, SC converters, and buck converters are illustrated in

Figs. 2.1, 2.2, and 2.3, respectively. The current efficiency of an LDO regulator depends on the quiescent current consumption. Although the efficiency of an LDO regulator can be improved by adaptively changing the quiescent current, current efficiency is significantly degraded at light load currents, as shown in Fig. 2.1b [5, 26]. The power conversion efficiency of a conventional SC converter increases with the output current and reduces significantly at light loads, as illustrated in Fig. 2.2a. Although advanced techniques are used to improve the power conversion efficiency at light load currents, as illustrated in Fig. 2.2b [27], the power conversion efficiency is typically degraded while providing light output current. The power conversion efficiency of a buck converter is also degraded significantly while delivering light load current, as shown in Fig. 2.3. All the on-chip voltage regulator topologies suffer from degraded power efficiencies while providing light output current. When the load circuit is in idle or sleeping mode, the voltage converter is driven into this low power conversion efficiency region, reducing the overall power conversion efficiency of power delivery system. Although significant power savings are achieved at the load circuits during reduced power states, these saving can be easily boosted if the power delivery system adaptively configures itself based on the workload under a wide range of load currents.

Another performance limiting factor in power delivery is the parasitic impedance of the power grid network between the voltage converter and load circuits. When the voltage regulator is implemented off-chip, the parasitic impedance of the off-chip interconnection networks and power/ground pins degrade the power suply integrity by increasing the response time, and IR and Ldi/dt voltage drops. Many techniques, such as a flipped voltage (super source) follower [26] and adaptive bias current [28], have been proposed to enable on-chip implementation of LDO regulators. Even though LDO regulators provide fast response time, the power conversion efficiency of linear regulators is limited to  $\frac{V_o}{V_{in}}$  where  $V_{in}$  and  $V_o$  are, respectively, the input and output voltages [29]. To obtain higher power conversion efficiency for a wide range of conversion ratios, the SC converters can be used, which are the main foci in this chapter. With the continuous technology scaling, high density on-chip capacitors can be realized on-chip. SC converters with high density on-chip capacitors can achieve 4.6 W/mm<sup>2</sup> power density, with ~86% efficiency [30].

Figure 2.2: Power efficiency of different SC converters. a) The power efficiency of an SC converter is not necessarily monotonic but the maximum efficiency is typically obtained while delivering a certain output current. b) Different techniques can be used to improve the efficiency at light load currents.

Distributed voltage regulation has recently gained attention as this technique can provide fast transient response and low noise [31–36]. Parallel integration of LDO regulators can breed challenges such as device mismatch, offset voltages among parallel regulators, overall system stability, and balanced current sharing, however, distributed voltage regulation can provide sub-nanosecond load regulation to attain high performance under increased temporal and spatial workload variations in modern ICs. Bulzacchelli et al. achieved 500 ps transient response time with a system of eight distributed LDO regulators [33]. Alternatively, individual stages of an interleaved SC converter can be distributed throughout the power grid without the aforementioned challenges. In interleaved converters, each interleaved converter stage operates at a different phase of a clock signal to minimize the output voltage ripple [37, 38]. Interleaved converters reduces the filter size, provides higher power efficiency [39], and by distributing the interleaved stages, the power supply noise can be minimized.

On-chip voltage regulators can also be used as a countermeasure to side channel power attacks by preventing attackers to obtain the actual power consumption information [40–43]. A

constant overall power consumption profile can be obtained by inserting a certain amount of excess current in addition to the actual load current. The sum of the excess current and actual current consumed by the active circuit blocks is kept constant by scaling the excess current inversely proportional to the actual current [21]. The primary disadvantage of this technique is the huge power loss to maintain constant power consumption, especially when the load current demand is low. Another technique is to randomize the current provided to the chip from outside and disrupt the correlation between the overall power consumption and load current consumption. A power profile scrambling technique is proposed in [22] to change the amplitude and frequency of the input current spikes. All of these mitigation techniques increase the overall power consumption and therefore degrade the overall system performance.

An important motivation for this work is the observation of a strong impact of the type of the voltage regulator on the power consumption profile. LDO regulators are typically employed as on-chip voltage regulators. A primary problem of utilizing on-chip LDO regulators for secure applications is the direct relationship between the input and output current of an LDO. Due to this intrinsic characteristic, LDO regulators typically leak the maximum possible power consumption information to the attacker if no advanced techniques are employed to mask the power consumption.

Alternatively, in this work, a new switching regulator architecture is used to reduce the dependence of the input current on load current. When switching regulators are utilized, the input current is no longer linearly dependent on the load current. The correlation between the input current and load current is further reduced by reconfiguring the number of active phases within a switched capacitor converter with the proposed technique. Details of the proposed approach that ensures secure on-chip power delivery are explained in Section 2.4.4.

#### 2.3 Converter-Gating

The details of the proposed converter-gating technique are explained in this section. The working principle of conventional SC converters and their power loss mechanisms are explained in Section 2.3.1. A case study that motivates the proposed work is explained in Section 2.3.2. The

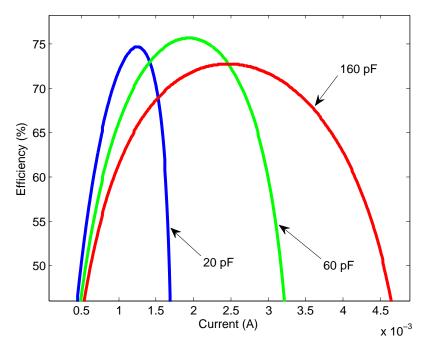

Figure 2.3: Power efficiency of buck converters. The efficiency graph exhibits a non-monotonic behavior and the maximum power efficiency is obtained at a certain output current.

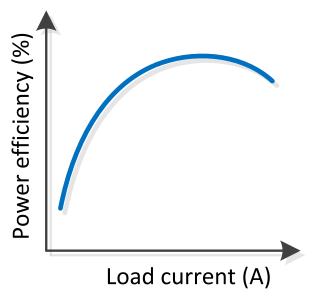

Figure 2.4: Two different topologies for SC voltage converters where the MOSFET switches are controlled with non-overlapping *Clock* and complimentary *ClockB* signals. a) 1:1 converter with two switches and a flying capacitor. b) 2:1 converter with four switches and a flying capacitor.

proposed control mechanism that adaptively turns on and off individual SC converter stages is discussed in Section 2.3.3.

#### 2.3.1 Efficiency Analysis of Switched Capacitor Voltage Converters

A conventional SC voltage regulator is composed of multiple switches, a capacitor network, and related feedback circuits. A clock signal is used to control the switches through which the capacitors are charged to a certain voltage level based on the converter topology and pulse width of clock

period. Another group of switches, controlled by a complementary non-overlapping clock signal, connects the capacitor to the output node to deliver the stored charge. The charge transfer ratio, thus the ideal voltage conversion ratio, is determined by the SC converter topology. To generate a wide range of output voltages, converters with configurable topologies are used [44]. Various output voltage levels can be generated by controlling the amount of charge stored in the flying capacitor network with pulse width modulation, frequency modulation, or capacitance modulation.

A simple SC voltage converter that uses minimum number of switches and capacitors is the 1:1 converter, as shown in Fig. 2.4a. The complete operation of this SC converter is performed in two phases, phase 1 (PH1) and phase 2 (PH2). During PH1, the flying capacitor is charged to  $V_{in}$  and during PH2 this capacitor is discharged to the output load, providing 1:1 voltage conversion. Another topology, a 2:1 SC voltage converter that has four switches and a flying capacitor is shown in Fig. 2.4b. In this configuration, the flying capacitor is charged to  $V_{in} - V_{in}$ , forcing the output to settle at  $V_{in}/2$ . An ideal 2:1 SC converter can provide 100% efficiency when the output voltage is  $V_{in}/2$  at no load condition. When a finite amount of current is provided to the output load, the output voltage reduces below the desired  $V_{in}$ , reducing the power efficiency of the converter. The power efficiency of an SC converter is therefore fundamentally limited to  $V_{in}/2$  where i is the voltage conversion ratio. A detailed analysis of the fundamental power efficiency limitations of SC voltage converters is provided in [45, 46]. This topology related power efficiency limitation has motivated the researchers to design configurable SC converters that can support multiple topologies with a single design to provide high power efficiency over a wide input and output voltage range.

Other than the topology related fundamental power efficiency limitation, parasitic losses of SC converters reduce the power efficiency of the converter. These power loss mechanisms include: i) switch driving loss, ii) switch buffer loss, iii) parasitic losses, and iv) control and reference losses.

#### 2.3.1.1 Switch Driving Loss

The switches within an SC converter are implemented with MOS transistors. A finite amount of power is dissipated when the switches turn on and off. The power dissipated during the switching

activity is,

$$P_{SW} = C_{sw} V_{DD}^2 f_{sw}, (2.1)$$

where the  $C_{sw}$  is the total gate capacitance of the switches,  $V_{DD}$  is the supply voltage, and  $f_{sw}$  is the switching frequency of the converter. The power dissipated during the switching activity increases with frequency and switch size. Since SC converters with a smaller flying capacitor require smaller switches, the switch driving loss is lower for smaller SC converters.

#### 2.3.1.2 Switch Buffer Loss

When the flying capacitor and switches are large, a series of tapered buffers are used to drive each individual switch. The switch buffer loss is the power consumed by these tapered buffers. Buffer loss becomes important when the switch sizes increase and therefore must be included in the efficiency analysis. The total power dissipated within the tapered buffers is [47],

$$P_{Buff} = \sum_{i=1}^{i=N} C_{Desired} F^{i-1} V_{DD}^2 f_{sw}, \tag{2.2}$$

where the N is the optimum number of stages,  $C_{Desired}$  is the desired load of the VCO, and F is the optimum fanout of each stage. The power dissipated within the tapered buffers exhibits a similar behavior with the switching power loss and increases with the switching frequency and flying capacitor size.

#### 2.3.1.3 Parasitic Capacitance Losses

A significant amount of power is wasted to charge and discharge the parasitic capacitance of the flying capacitor and switches. The main contributor of the power loss is the bottom plate capacitance of the flying capacitor. For example, in a 2:1 SC converter, the bottom plate of the flying capacitor is charged to  $V_o$  during charging phase and is discharged to ground during the charge transfer phase. In other words, a relatively large parasitic capacitor is charged and discharged at every cycle, significantly reducing the overall power conversion efficiency. Since the highest possible power is dissipated when the parasitic capacitance is charging and discharging between the output

voltage and ground, the related power loss is,

$$P_{Par} = C_{BottomPlate} V_o^2 f_{sw}, (2.3)$$

where  $C_{BottomPlate}$  is the total bottom plate capacitance and  $V_o$  is the output voltage of the converter. The power loss due to the parasitic capacitance scales with the size of flying capacitance and switching frequency.

#### 2.3.1.4 Control and Reference Losses

Another loss mechanism is the power dissipated within the related control and reference circuits. Finite amount of power is consumed to: i) generate the reference voltage, ii) compare the output voltage with reference to provide feedback, and iii) generate the feedback signal. The control and reference circuit related power losses  $P_{Control}$  can be considered constant over a wide current range with little or no dependence to output voltage or output current.

The overall power efficiency of a conventional SC voltage converter is,

$$\eta_{SC} = \frac{P_{out}}{P_{out} + P_{SW} + P_{Buff} + P_{Control} + P_{Par}},\tag{2.4}$$

where  $P_{out}$  is the output power of the converter. (2.4) is used in the rest of the work to analytically determine the efficiency of the proposed system. A more comprehensive power efficiency analysis can be found in [48].

#### 2.3.2 Power Efficiency of SC Converters with Different Flying Capacitor Values

A decision flow similar to [48] has been used to determine the optimum switching frequency that provides a certain output voltage of a 2:1 SC converter. First, the required output impedance to generate a certain output voltage under a given output current load is determined. The optimum switching frequency to obtain the required output impedance at a particular output current and power efficiency is then obtained using (2.4).

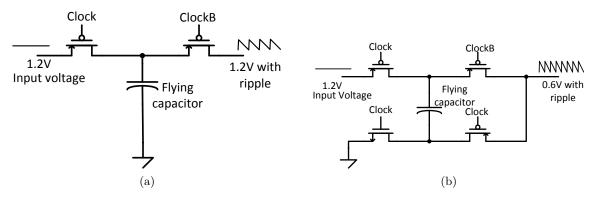

Figure 2.5: Power conversion efficiency of various SC voltage converter with different flying capacitor values. A smaller converter provides maximum power efficiency when the load current is lower whereas a larger converter can provide better efficiency under higher output current.

The power efficiency of differently sized 2:1 SC voltage converters with flying capacitors of 20 pF, 60 pF, and 160 pF when the load current ranges between 0.1 mA and 5 mA is illustrated in Fig. 2.5. Note that the switches and tapered buffers are scaled based on the size of the flying capacitor. A tapering factor of  $\sim 2.5 \times$  is used in the analysis. A quite important result observed from Fig. 2.5 is that SC converters with different flying capacitor values provide the maximum possible power efficiency under different load currents. An SC converter with a smaller flying capacitor provides a high power efficiency when the load current is low because the tapered drivers and buffers used in the configuration are smaller. Alternatively, an SC converter with a larger flying capacitor can provide higher power efficiency under a larger load current. A flat power efficiency curve can therefore be achieved if the size of the SC converter is adaptively modified based on the workload.

#### 2.3.3 Converter-Gating and Distribution

Interleaved SC converters typically utilize frequency modulation, capacitance modulation, or pulse width modulation to provide a constant output voltage under transient load currents [27, 44, 45]. However, these control techniques do not guarantee high power efficiency when the load current is low. At low load currents, the power efficiency is significantly degraded since the power dissipated in the control circuitry and parasitic impedances becomes significantly higher as compared to the load current.

Based on the observations that smaller SC converters are more efficient at lower load currents whereas larger SC converters are more power efficient at higher load currents, a new converter-gating technique is proposed in this paper. Since most of the SC converters are interleaved, each interleaved stage is turned on and off to provide a specific type of capacitance modulation as a coarse control technique. Frequency modulation is used as a fine control technique to regulate the output voltage between capacitance steps. This proposed approach increases the power conversion efficiency by forcing each stage to operate at the highest achievable power efficiency. The proposed voltage converter control technique therefore achieves a higher power efficiency as compared to the existing techniques which typically employ either capacitance or frequency modulation. To deactivate an individual converter stage, certain switches within an SC converter stage are turned off, isolating the input and connecting the flying capacitor to the output node. The implementation cost of the proposed converter is negligible as the components of the proposed converter-gating technique are already implemented in a conventional interleaved SC converter. The only additional circuit is a simple decoder that turns the stages on and off.

The interleaved stages of the converter are distributed throughout the power grid to act as local voltage converters. Distributing individual converter stages reduces the parasitic impedance between the converter and load circuits and therefore reduces the IR and Ldi/dt voltage drop. Additionally, the response time of the converter to transient load changes is improved due to the reduced power grid parasitic impedance between the converter and the load.

The primary overheads of the proposed converter-gating technique, assuming that the system already has on-chip voltage regulation, are summarized below.

#### 2.3.3.1 On - Off Transition Time of Individual Regulators

As individual interleaved stages of the regulator turn on and off depending on the output current, the activation and deactivation time of these stages must be sufficiently short to not disrupt the operation of the circuit. A control technique is proposed in Section 2.4 that permits a 2:1 SC converter to behave as a 1:1 SC converter for a short time to reduce the activation time of an individual stage. This technique improves the charge transfer ratio for a couple of cycles to transfer the required charge to the output node faster.

#### 2.3.3.2 Area Overhead

Assuming that the circuit already has control circuitry for power/clock gating, and on-chip sensors and performance counters, the area overhead of the converter-gating will be the additional control circuitry and one decoder to control the activity of the individual converter stages.

#### 2.3.3.3 Power Overhead

The modified control circuitry and decoders slightly increase the power consumption which is significantly lower than the power savings with the proposed technique.

#### 2.3.3.4 Output Noise

The output voltage ripple is increased due to the asymmetrical behavior caused by changing number of interleaved stages, which is given in Fig. 2.13. To minimize the output noise, the inactive stages are utilized as decoupling capacitors by connecting the flying capacitor to the output node, as explained in Section 2.5-C.

The primary strength of the proposed technique is that the power conversion efficiency is increased over 5% with slight modifications to the existing on-chip voltage regulation system.

#### 2.4 Circuit Level Design of Converter-Gating

The proposed method is designed using IBM 130 nm technology kit. The proposed convertergating methodology is explained in Section 2.4.1. The impact of distributing individual interleaved

Figure 2.6: Top level schematic of the proposed converter-gating system.

stages on the power noise is discussed in Section 2.4.2. The proposed configurable 2:1 to 1:1 SC converter is presented in Section 2.4.3. The exploitation of the proposed converter-gating technique as a countermeasure against side channel power attacks is explained in Section 2.4.4.

#### 2.4.1 Converter-Gating Control Methodology

The complete converter-gating control structure is shown in Fig 2.6. MOS capacitors are used as flying capacitors within the 2:1 SC converter. The converter uses two comparators to create feedback signals for the control loop. One comparator compares the output voltage with the reference voltage and the comparator output is integrated to create the control voltage for the voltage controlled oscillator (VCO), which is realized as a current limited inverter chain. The second comparator detects transient load changes that would result in more than 30 mV voltage drop. In this case an interrupt is triggered and its operation is explained in Section 2.4.3. The control logic determines the optimum number of active stages and provides the required control signals to the interleaved SC voltage converter through a pseudo-random scrambling circuit. The scrambling circuit uses a pseudo-random number generator and scrambles the activation pattern of

Figure 2.7: Proposed converter-gating algorithm that enables workload aware activity management of distributed SC voltage converters.

the individual stages. When certain converter stages are deactivated, each remaining active stage is effectively forced to operate at its maximum efficiency. Deactivated stages are connected to the output node and act as a decoupling capacitor to reduce the output voltage ripple. The algorithm used to determine the number of active converters is given in Fig. 2.7. When the switching frequency or the input voltage of the VCO exceeds a predetermined limit FHlim (60 MHz) for more than 5 cycles, an additional converter stage is activated. Alternatively, when the switching frequency becomes lower than a certain limit FLlim (30 MHz) for more than 5 cycles, a converter stage is deactivated. To prevent stages from turning on and off randomly when the control signal is at limit values, a hysteresis loop with 10 MHz width is implemented. The frequency limits are selected as 60 MHz and 30 MHz to optimize the power density and efficiency according to [48]. In the proposed control, the activity of individual converter stages is utilized as a coarse control technique whereas the switching frequency is used as a fine control technique. For example, if the load current demand increases when certain number of stages are active, the operating frequency increases to provide the required load current. If the frequency exceeds the upper frequency limit FHlim (60 MHz), another individual stage turns on, which in turn reduces the switching frequency. The 30 MHz and 60 MHz

Figure 2.8: Amount of charge transferred to the output note in a single cycle for a) a conventional 2:1 SC voltage converter and b) a 2:1 converter that is configured as a 1:1 converter by controlling the illustrated switches. 1:1 configuration provides two times more charge to the output node in a given cycle, improving the response time.

limits imply that each converter stage delivers an output current between  $\sim 80$  uA and  $\sim 350$  uA. When converter stages are forced to deliver more than  $\sim 350$  uA or less than  $\sim 80$  uA, frequency exceeds 60 MHz or goes below 30 MHz, turning on or off another stage and keeping the frequency in 30 MHz - 60 MHz range.

#### 2.4.2 Distribution of the Interleaved Stages

Each interleaved stage of the SC converter is uniformly distributed throughout the power grid to minimize the power noise and enable point-of-load voltage regulation. The physical location of the active SC stages is important to reduce the power noise. Based on the information provided by local voltage and current sensors, performance counters and temperature sensors, a specific voltage regulator can be turned on or off using the proposed algorithm. The implication of distributing individual interleaved stages on the power noise is analyzed with extensive simulations in Section 2.5.3.

#### 2.4.3 Configurable SC Voltage Converter

A new control technique is proposed to adaptively configure the conversion ratio of an SC voltage converter for a couple of clock cycles to speed up the activation and deactivation of individual stages. To achieve a fast recovery during either activation (deactivation) of individual

stages or transient voltage drop (bounce), it is necessary to transfer a higher (lower) amount of charge to the output node for a finite amount of time. Introducing interrupts and fast loops has been used in [27, 49]. However, a convenient and simple technique to achieve fast response time is configuring a 2:1 converter as a 1:1 converter during the load transients. During the normal operation of a 2:1 converter, the flying capacitor is charged to as high as  $V_{in} - V_o$ . Alternatively, if a 1:1 configuration is used, the total charge can be increased by  $C_{flying} \times V_o$ . By configuring a 2:1 converter as a 1:1 converter, the total amount of charge transferred to the output node in each cycle is increased nearly by a factor of two, significantly reducing the response time. One of the advantages of this configuration technique is that most of the existing voltage converters can be adaptively configured as a 1:1 SC converter, reducing the implementation cost of the proposed approach to only a decoder in digital domain and a comparator to generate interrupt signals. The working principle of the proposed method is explained in Fig. 2.8. During the transients, when the interrupt signal is given, the switch connected to ground remains on, and the switch connected between the bottom plate of the flying capacitance and the output remains off, effectively configuring the 2:1 converter as a 1:1 converter, increasing the amount of charge transfer to the output node per unit time. Using this approach may generate output voltages higher than the desired voltage. which in turn may cause instability. Therefore the drop voltage (30 mV) must be selected carefully to prevent the 1:1 converter from generating higher voltages than the desired output voltage even under worst case conditions.

#### 2.4.4 Converter-Gating as a Side-Channel Attack Countermeasure

The relationship between the input current and load current profiles is linear for LDO regulators, as shown in Fig 2.15b. Alternatively, switching converters have an input current that consists of current spikes whose amplitude, frequency, and width depends on the control signal generated by the feedback loop. Due to this complicated relationship between input and output current profiles of an on-chip switching converter, a decipher requires more time and effort to understand the functionality or the stored secret key. The relation between the input and output currents becomes even more complicated when the proposed converter-gating approach is used. The

frequency and amplitude are no longer linearly correlated with the load current since the frequency and amplitude of the spikes adaptively vary during the operation as the number of active stages change. Although the input current and power waveforms are more sophisticated to analyze even with a conventional SC voltage converter, the overall power consumption can be further convoluted by randomizing the activation pattern of the individual stages.

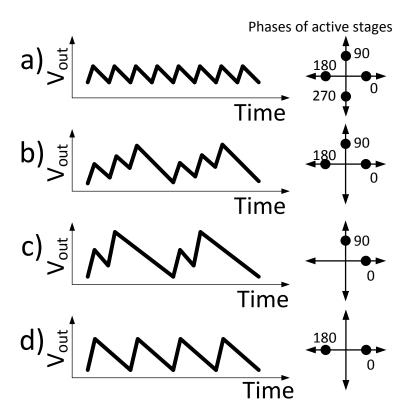

A randomized converter-gating technique is proposed in this section to minimize the correlation between the input and load current profiles. The activation pattern of the individual stages within the proposed SC converter system is determined with a linear feedback shift register (LFSR) based 10-bit pseudo random number generator. As a result, a random delay is inserted to the input current waveform and the amplitude of the spikes randomly varies with the activation pattern. For example, when five interleaved stages are active, the phases of these active stages can be configured as  $(0^{\circ}, 45^{\circ}, 90^{\circ}, 135^{\circ})$  and  $(0^{\circ}, 90^{\circ}, 180^{\circ}, 225^{\circ})$ , and  $(0^{\circ}, 90^{\circ})$  ( $(0^{\circ}, 90^{\circ})$ ) ( $(0^{\circ}, 90^{\circ})$

# 2.5 Functional Verification of Converter-Gating

An eight stage 2:1 SC voltage converter is designed with 130 nm IBM CMOS technology. The top level schematic of the complete design is illustrated in Fig. 2.6. Each individual converter stage has a 20 pF flying capacitor (implemented using MOS capacitors) to allow a total output current between 200 uA and 2.5 mA. Although a conventional 2:1 SC voltage converter is used, the controller of the switches is designed to permit this 2:1 converter configurable as a 1:1 converter, as shown in Fig. 2.8.