# **University of South Florida** Scholar Commons

Graduate Theses and Dissertations

Graduate School

November 2017

# Compact and Wideband MMIC Phase Shifters Using Tunable Active Inductor Loaded All-Pass Networks

David M. Zaiden University of South Florida, dzaiden@mail.usf.edu

Follow this and additional works at: https://scholarcommons.usf.edu/etd

Part of the Electrical and Computer Engineering Commons

# Scholar Commons Citation

Zaiden, David M., "Compact and Wideband MMIC Phase Shifters Using Tunable Active Inductor Loaded All-Pass Networks" (2017). Graduate Theses and Dissertations.

https://scholarcommons.usf.edu/etd/7454

This Dissertation is brought to you for free and open access by the Graduate School at Scholar Commons. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact scholarcommons@usf.edu.

# Compact and Wideband MMIC Phase Shifters Using Tunable Active Inductor Loaded All-Pass Networks

by

David M. Zaiden

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Department of Electrical Engineering

College of Engineering

University of South Florida

Co-Major Professor: Gokhan Mumcu, Ph.D. Co-Major Professor: Thomas Weller, Ph.D. Jian Wang, Ph.D. Srinivas Katkoori, Ph.D. John Grandfield, M.S.E.E.

> Date of Approval: October 18, 2017

Keywords: GaAs, MMIC, Active Balun, S-band, L-band, Tunable Inductor

Copyright © 2017, David M. Zaiden

#### **Dedication**

To my family and friends especially my wife Jesusita and my boys, Antonio, Adiel, Athan and Alzan. I couldn't have done this without your love, support and understanding. Baba did this for you guys!

To my brother for laying down the footprints that I could follow and my Mom for refusing to give up on me.

To my "Comprade" Catarino for always being there for me especially during those difficult times. Thanks for all the advice and encouragement.

To my guardian angel "Brecka" for keeping a close watch over me like you always did when you were here. Love always!

To Mama Lina, Papa Tono, Tia Awi, Tia Blankie and Bito, seems like just yesterday you were here with me. Time goes by so fast and only the best memories of you remain. You made my childhood one that I would never trade for anything else. Love and miss you.

Dabito

## Acknowledgments

I would like to sincerely thank Professor Thomas Weller and Associate Professor GokhanMumcu for their invaluable advice and guidance. It is truly my honor to have them as myadvisors. Their support and guidance has allowed me to transform a dream into reality. I would also like to acknowledge my examination committee Associate Professors Jing Wang and Srinivas Katkoori and John Grandfield from Charles Start Draper Labs

I would also like to thank the Charles Stark Draper Laboratory and in particular, JohnGrandfield and Amy Duwel, for the Doctoral Fellowship that made this all possible.

There are so many more people like me, with the desire to go to school and get an education and hopefully have a positive impact on this world. With people like the ones mentioned above it becomes a lot easier to turn those dreams into reality. Thanks!

# **Table of Contents**

| List of Tables                                      | iii  |

|-----------------------------------------------------|------|

| List of Figures                                     | iv   |

| Abstract                                            | viii |

| Chapter 1: Introduction                             | 1    |

| 1.1 Overview                                        | 1    |

| 1.2 Brief Review of Previous Work                   | 5    |

| 1.3 Motivation and Organization of the Dissertation | 7    |

| 1.4 Technology Overview                             | 10   |

| 1.5 References                                      | 10   |

| Chapter 2: Phase Shifter Fundamentals               | 14   |

| 2.1 Introduction                                    | 14   |

| 2.2 Types of Phase Shifters                         | 16   |

| 2.2.1 Switched Line Phase Shifter                   | 17   |

| 2.2.2 Reflection Type Phase Shifter                 | 18   |

| 2.2.3 Loaded Line Phase Shifter                     | 18   |

| 2.2.4 High/Low Pass and All Pass Phase Shifter      | 19   |

| 2.2.5 Vector Modulators                             | 20   |

| 2.2.6 Periodically Loaded Transmission Line         | 22   |

| 2.2.7 Integrated Switches                           | 23   |

| 2.3 Phase Shifter Requirements                      | 25   |

| 2.3.1 Phase Shift Error                             | 25   |

| 2.3.2 Amplitude Imbalance                           | 26   |

| 2.3.3 Insertion Loss                                | 26   |

| 2.3.4 Return Loss                                   | 27   |

| 2.3.5 Number of Bits                                | 27   |

| 2.3.6 Operating Frequency Band and Device Size      | 28   |

| 2.4 Summary                                         | 28   |

| 2.5 References                                      | 29   |

| Chapter 3: All-Pass Phase Shifter Design            | 30   |

| 3.1 Introduction                                    | 30   |

| 3.2 All-Pass Filter Design Theory                   | 31   |

| 3.3 All-Pass Phase Shifter Design                   | 33   |

| 3.4 Fabrication and Measurement                     | 46   |

| 3.5 Summary                                         | 51   |

| 3.6 References                                      | 52   |

| Chapter 4: Active Inductor Design           | 53       |

|---------------------------------------------|----------|

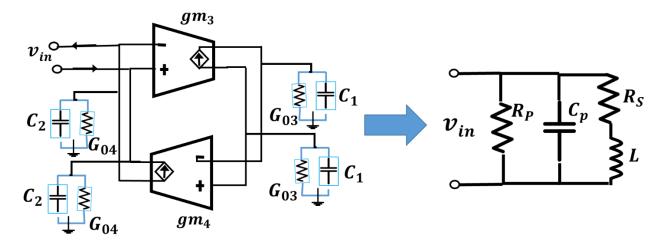

| 4.1 Gyrator Based Active Inductor           | 53       |

| 4.2 Frequency Response of Active Inductors  | 55       |

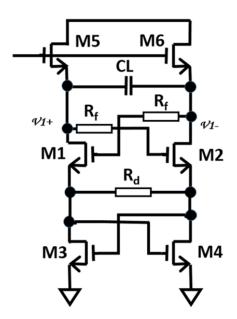

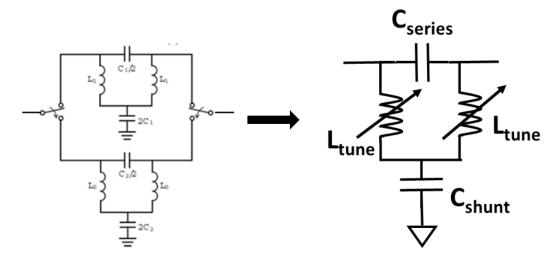

| 4.3 Differential Active Inductors           | 58       |

| 4.4 Circuit Implementation                  | 61       |

| 4.5 Post-Layout Simulation Results          | 63       |

| 4.6 Summary                                 | 65       |

| 4.7 References                              | 66       |

| Chapter 5: Modified All-Pass Phase Shifter  | 67       |

| 5.1 System Level Design                     | 67       |

| 5.2 Active Balun Based 180° Phase Shifter   | 68       |

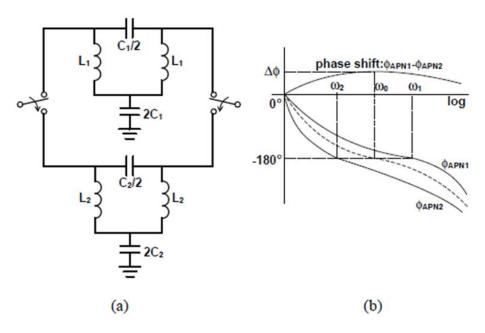

| 5.3 Active Inductor Loaded All-Pass Network | 73       |

| 5.4 Output VGA/Buffer                       | 78       |

| 5.5 Experimental Verification               | 84       |

| 5.6 References                              | 90       |

| Chapter 6: Conclusion and Future Work       | 91       |

| 6.1 Summary and Conclusion                  | 91       |

| 6.2 Future Work                             | 92       |

| Appendix A: Design Tutorial                 | 96       |

| A.1 Passive All-Pass Filter Design          | 96       |

| A.2 Active Inductor Design                  | 98       |

| A.3 Active All-Pass Phase Shifter Design    | 101      |

| A.4 Active Balun Design                     | 102      |

| A.5 VGA/Buffer Design                       | 103      |

| A.6 References                              | 104      |

| About the Author                            | End Page |

# **List of Tables**

| Table 3.1 | Calculated LC Values (C in pF, L in nH)                                                                     | 38  |

|-----------|-------------------------------------------------------------------------------------------------------------|-----|

| Table 5.1 | Effect of Varying Transconductance and Feedback Resistance on<br>Performance of the Tunable Active Inductor | 76  |

| Table 5.2 | Transistor Sizes of the Optimized Tunable Active Inductor                                                   | 77  |

| Table 5.3 | Performance Comparison                                                                                      | 90  |

| Table A1  | Effects of Varying Transconductance and Feedback Resistance on Performance of Tunable Active Inductor       | 101 |

# **List of Figures**

| Figure 1-1  | Array antenna systems: (a) mechanically steered, rotating reflector array and (b) electrically steered, fixed phased-array | 1  |

|-------------|----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1-2  | Beamforming in cellular wireless communication network                                                                     | 3  |

| Figure 1-3  | Phased-array applications in civilian sectors                                                                              | 4  |

| Figure 2-1  | Block diagram of a phase shifter                                                                                           | 14 |

| Figure 2-2  | Switch-line phase shifter                                                                                                  | 17 |

| Figure 2-3  | Reflection type phase shifter (a) hybrid, (b) circulator                                                                   | 18 |

| Figure 2-4  | Loaded-line phase shifter                                                                                                  | 19 |

| Figure 2-5  | Phase shifter with switching elements                                                                                      | 20 |

| Figure 2-6  | High pass/low-pass network                                                                                                 | 20 |

| Figure 2-7  | Vector modulator phase shifter                                                                                             | 21 |

| Figure 2-8  | Periodically loaded line phase shifter                                                                                     | 22 |

| Figure 2-9  | Equivalent circuit of a FET operating as a switch                                                                          | 23 |

| Figure 2-10 | SPDT switch using series FETs                                                                                              | 24 |

| Figure 2-11 | SPDT switch using series-shunt FETs                                                                                        | 25 |

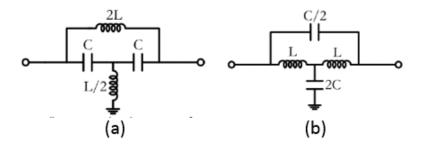

| Figure 3-1  | All pass filter in series L (a) and series C (b) configuration                                                             | 31 |

| Figure 3-2  | Single section all pass phase shifter                                                                                      | 32 |

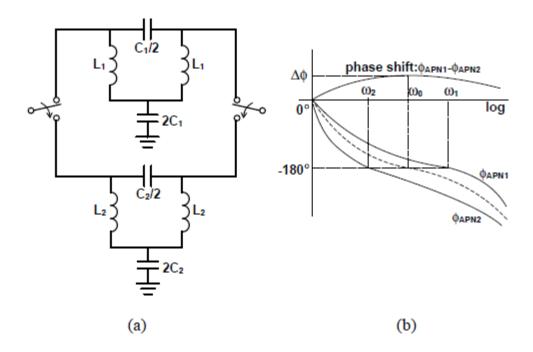

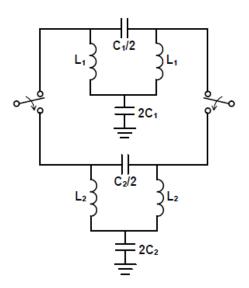

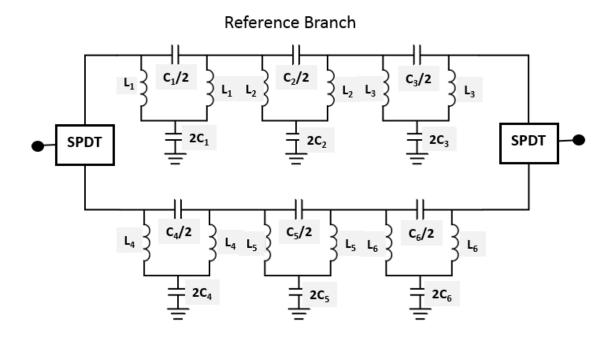

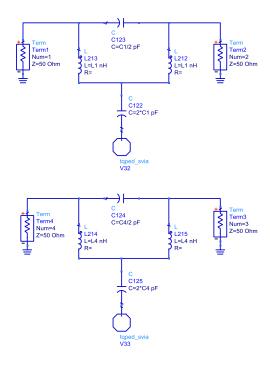

| Figure 3-3  | Topology of a single stage all-pass phase shifter                                                                          | 34 |

| Figure 3-4  | Topology of a single bit                                                                                                   | 35 |

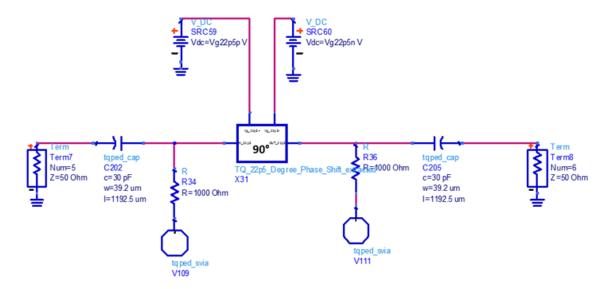

| Figure 3-5  | Simulation setup for 90° phase shifter                                                                                     | 36 |

| Figure 3-6  | Single section 90° phase shifter at 1.9 GHz                                                                                | 36 |

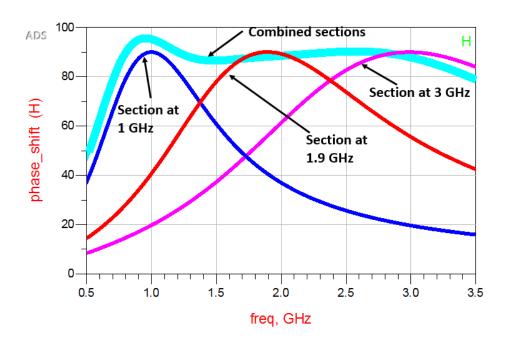

| Simulation results of 90° phase shifter                                                                   | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

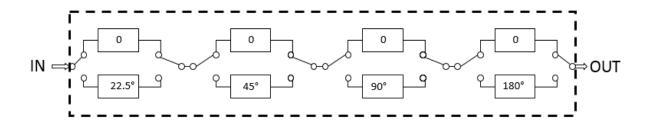

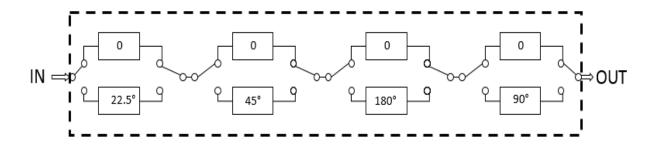

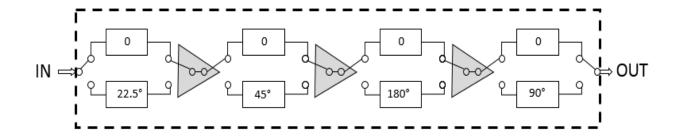

| Block diagram of 4-bit phase shifter                                                                      | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Optimal bit ordering                                                                                      | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Schematic of 22.5 <sup>0</sup> phase shifter                                                              | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

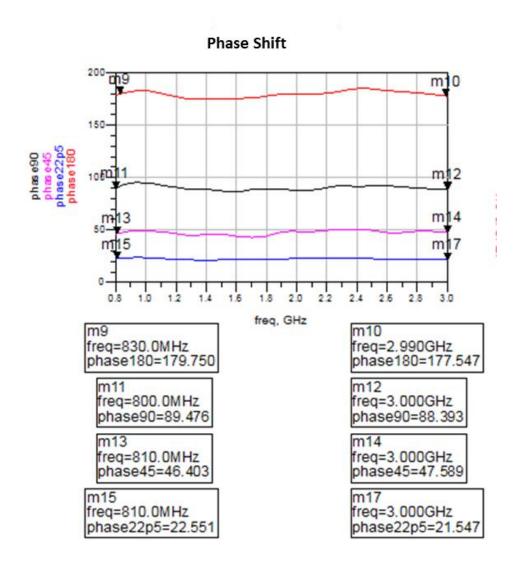

| Simulated phase shift of 4 bit system                                                                     | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

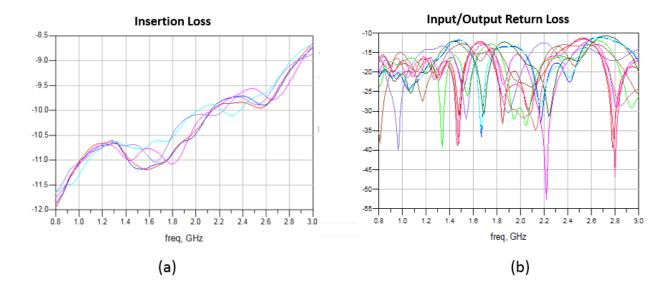

| Simulated insertion loss (a) and input/output return loss (b)                                             | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Concept of 4 bit phase shifter with amplifiers                                                            | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

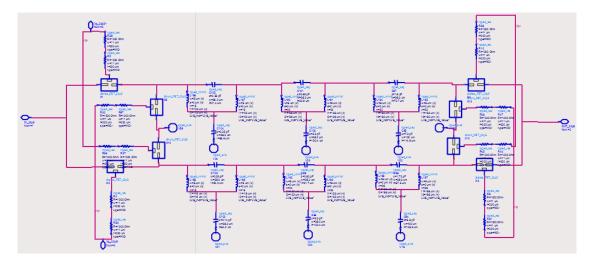

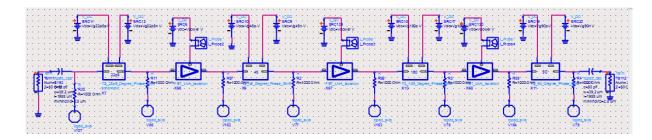

| Schematic of 4 bit phase shifter with amplifiers                                                          | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

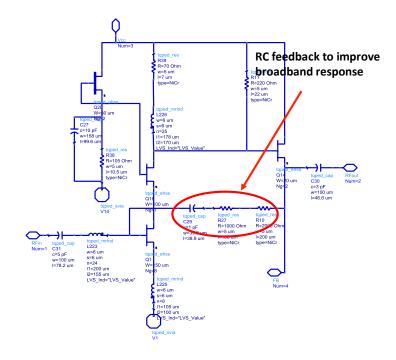

| Wideband LNA Design                                                                                       | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

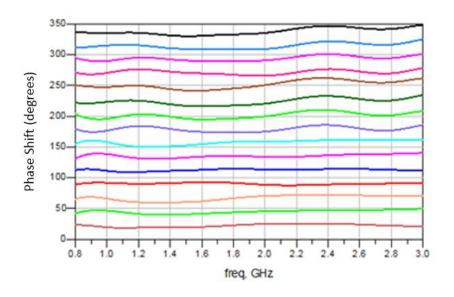

| System level simulation of phase shift (degrees)                                                          | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

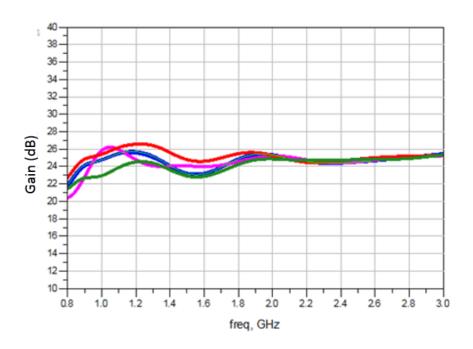

| System level gain (dB)                                                                                    | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

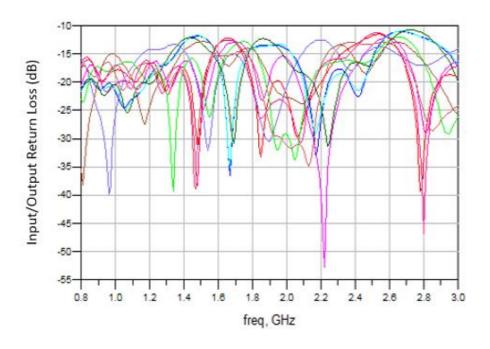

| Simulation results of input/output return loss                                                            | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

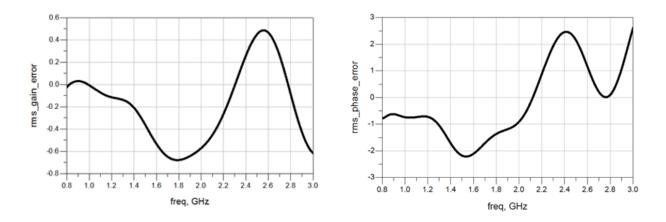

| RMS gain and RMS phase error                                                                              | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

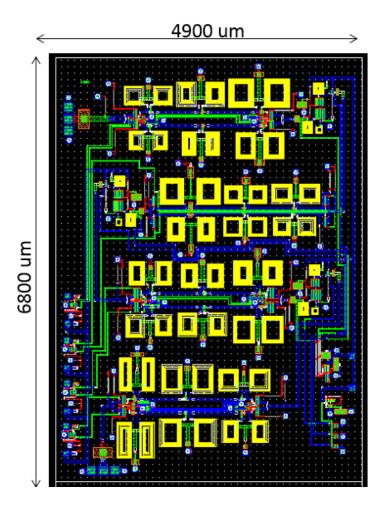

| Complete chip layout                                                                                      | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

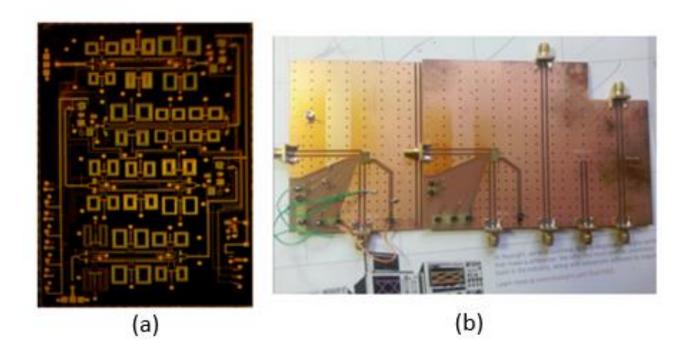

| Fabricated chip and test board                                                                            | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

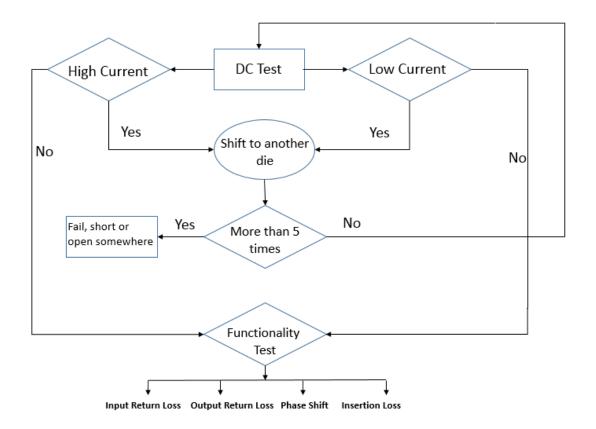

| Flowchart for initial testing                                                                             | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

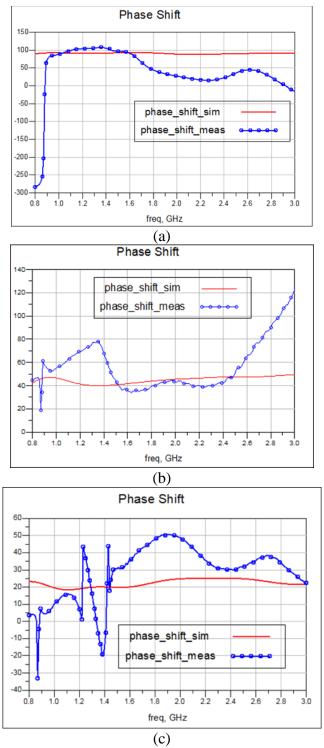

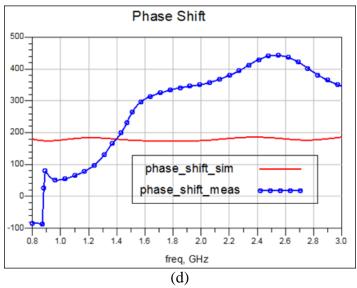

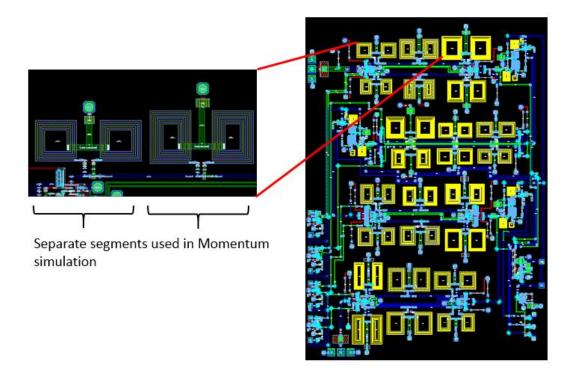

| Simulated vs. measured phase shift (a) $90^{\circ}$ (b) $45^{\circ}$ (c) $22.5^{\circ}$ (d) $180^{\circ}$ | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

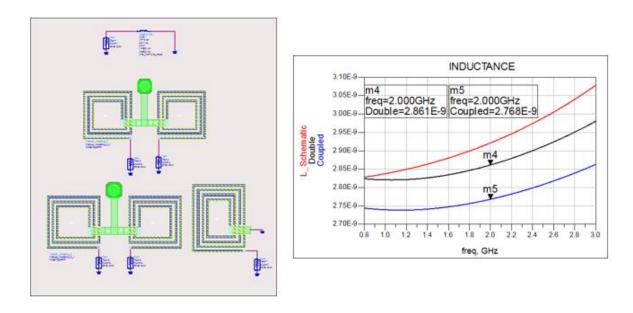

| Segment of layout used for case study on mutual inductance                                                | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Inductor mutual inductance                                                                                | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

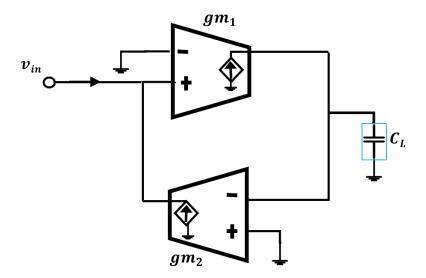

| Lossless single-ended gyrator-c active inductor                                                           | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Lossy floating gyrator-c active inductor and equivalent RLC circuit                                       | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

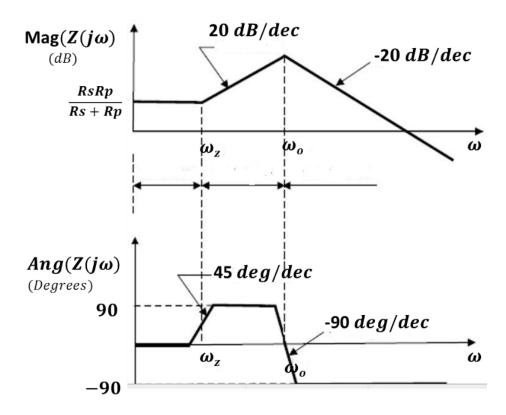

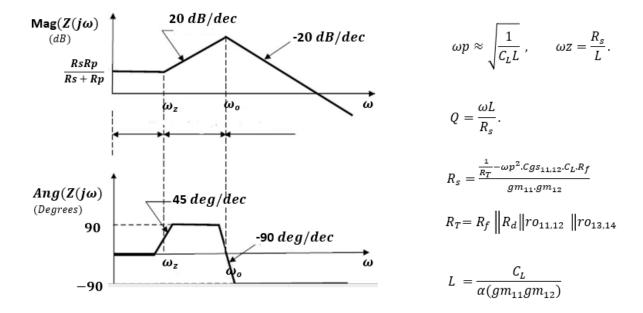

| Bode plot of lossy gyrator-c active inductor                                                              | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

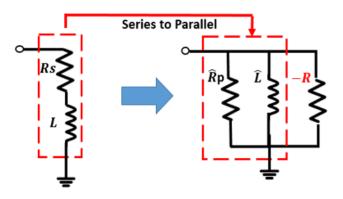

| RL parallel to RL series branch transformation                                                            | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                           | Block diagram of 4-bit phase shifter  Optimal bit ordering  Schematic of 22.5° phase shifter  Simulated phase shift of 4 bit system  Simulated insertion loss (a) and input/output return loss (b)  Concept of 4 bit phase shifter with amplifiers  Schematic of 4 bit phase shifter with amplifiers  Wideband LNA Design  System level simulation of phase shift (degrees)  System level gain (dB)  Simulation results of input/output return loss  RMS gain and RMS phase error  Complete chip layout  Fabricated chip and test board  Flowchart for initial testing  Simulated vs. measured phase shift (a) 90° (b) 45° (c) 22.5° (d) 180°  Segment of layout used for case study on mutual inductance  Inductor mutual inductance  Lossless single-ended gyrator-c active inductor  Lossy floating gyrator-c active inductor  Bode plot of lossy gyrator-c active inductor |

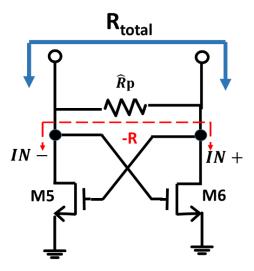

| Figure 4-5  | Negative resistance cross-coupled transistors                                 | 57 |

|-------------|-------------------------------------------------------------------------------|----|

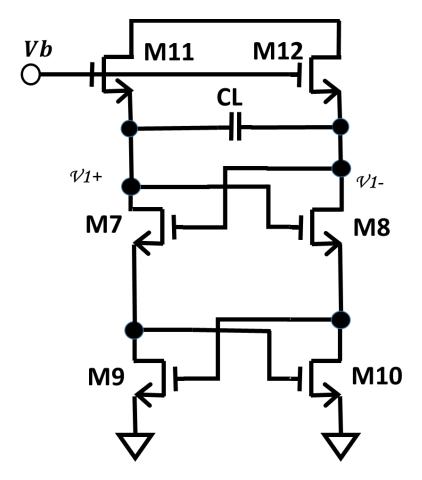

| Figure 4-6  | DAI based on cross-coupled transistors                                        | 58 |

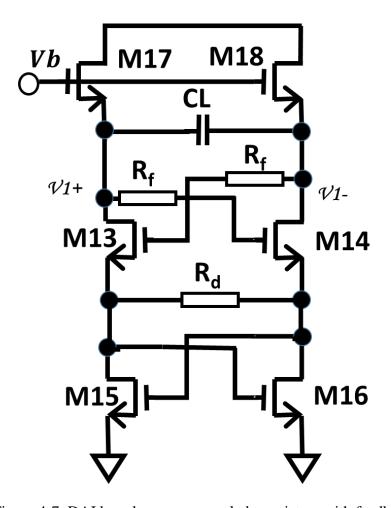

| Figure 4-7  | DAI based on cross-coupled transistors with feedback                          | 60 |

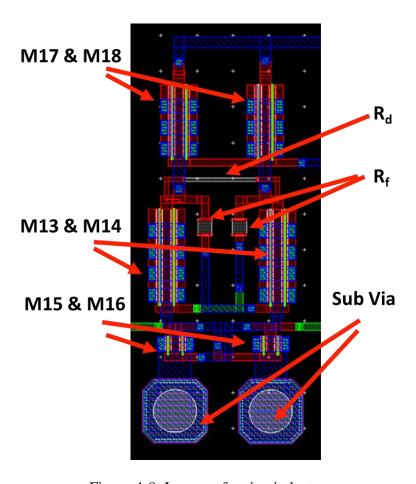

| Figure 4-8  | Layout of active inductor                                                     | 62 |

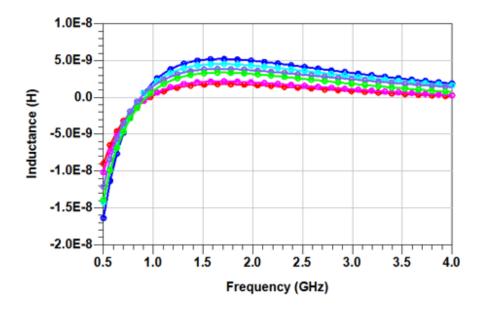

| Figure 4-9  | DAI inductance tuning range                                                   | 64 |

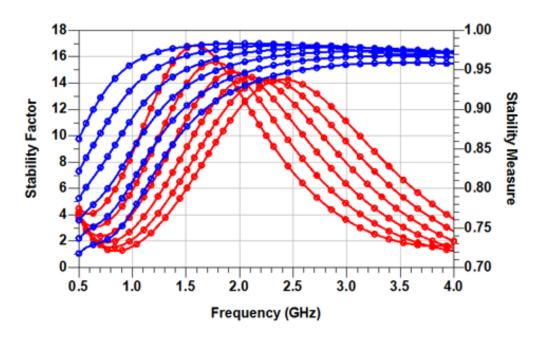

| Figure 4-10 | DAI stability simulation results                                              | 64 |

| Figure 4-11 | DAI quality factor for inductance tuning range                                | 65 |

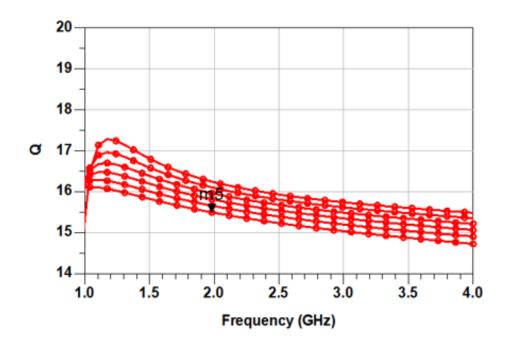

| Figure 4-12 | Input third order intercept point                                             | 65 |

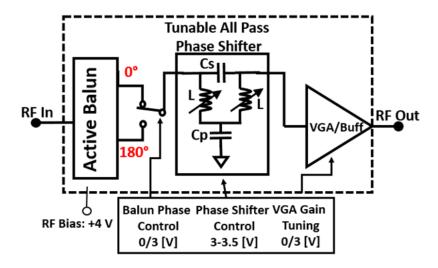

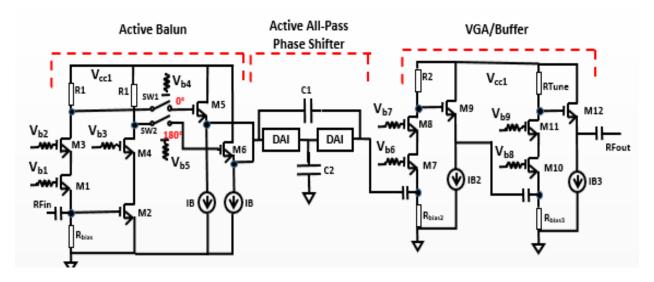

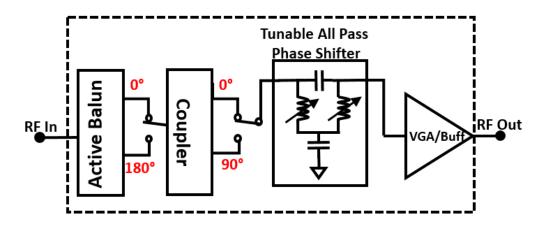

| Figure 5-1  | Functional block diagram                                                      | 68 |

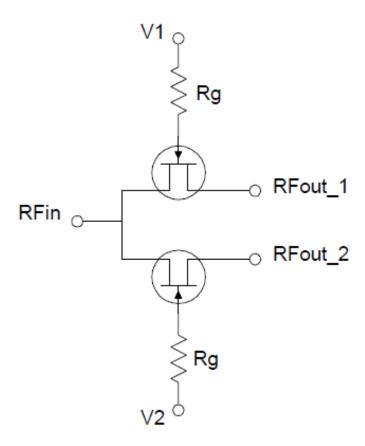

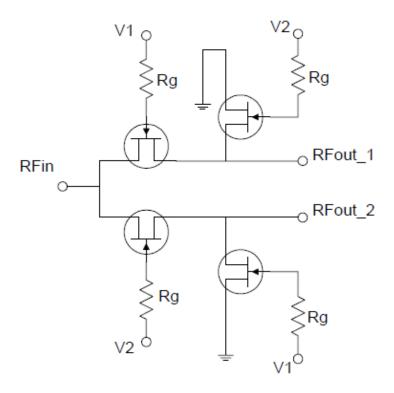

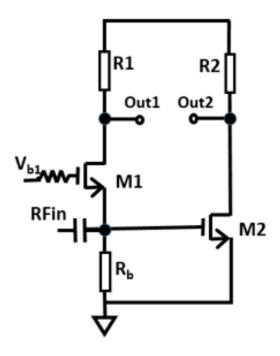

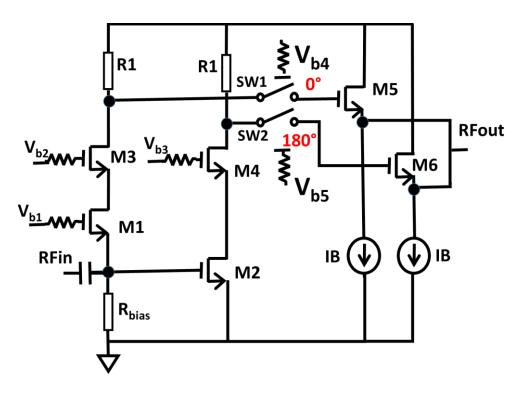

| Figure 5-2  | Common-gate common-source active balun                                        | 69 |

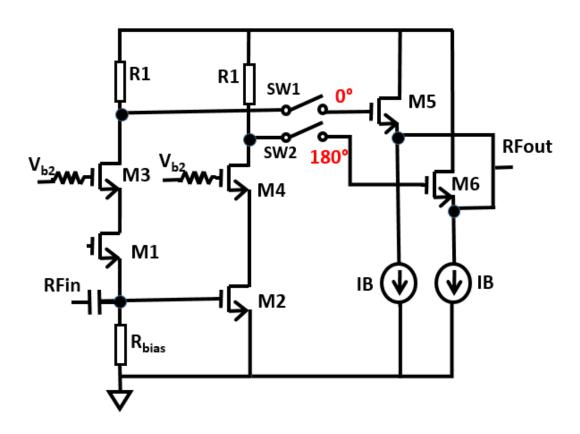

| Figure 5-3  | Active balun with switches                                                    | 71 |

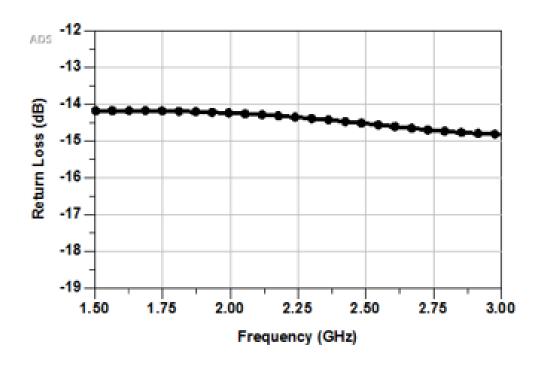

| Figure 5-4  | Return loss of active balun                                                   | 72 |

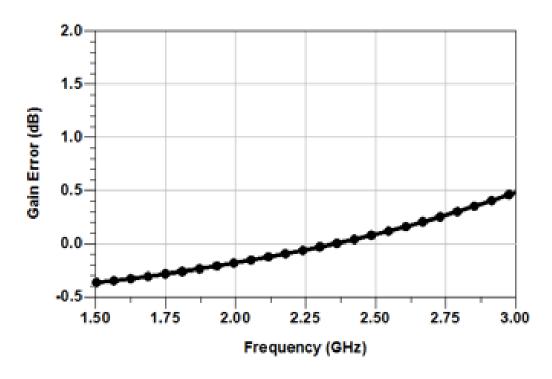

| Figure 5-5  | Gain error of active balun                                                    | 72 |

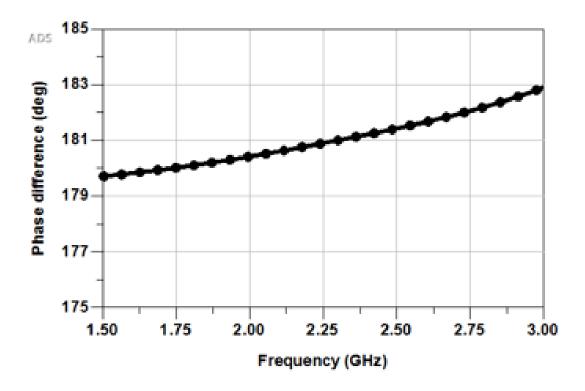

| Figure 5-6  | Phase difference of active balun                                              | 73 |

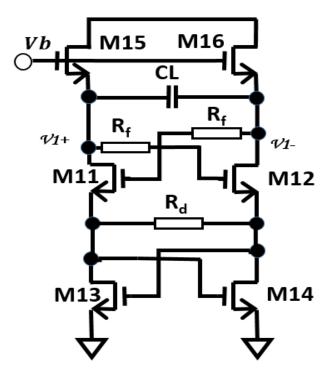

| Figure 5-7  | Differential active inductor (DAI)                                            | 74 |

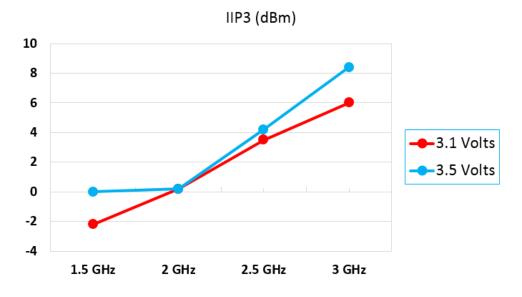

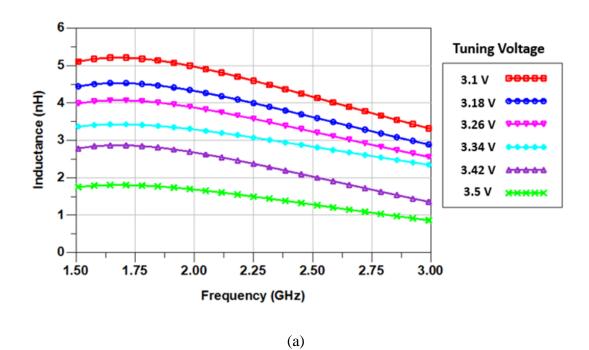

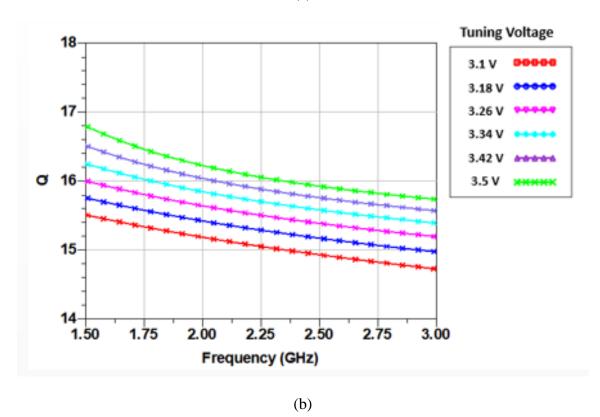

| Figure 5-8  | Inductance tuning range (a) and quality factor variation (b) of DAI           | 79 |

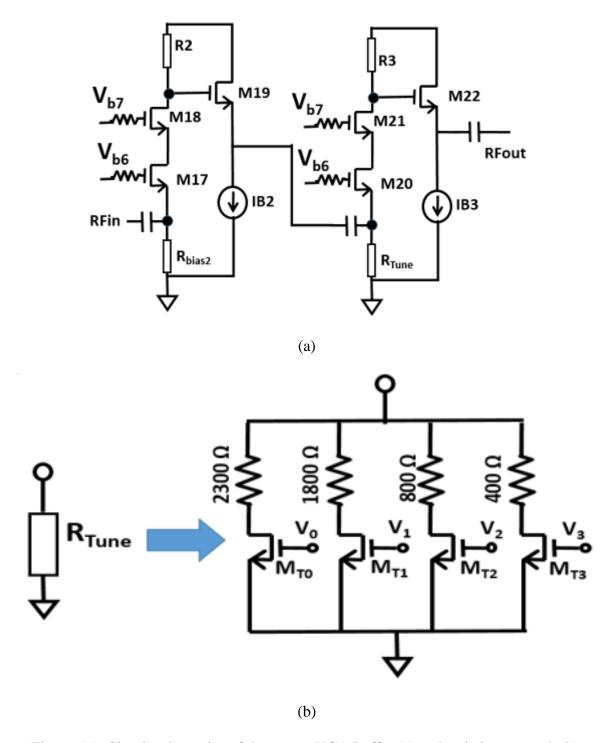

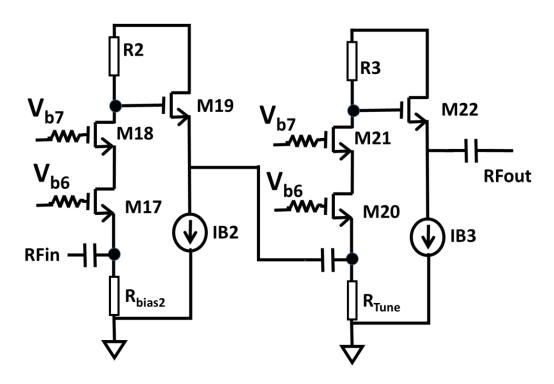

| Figure 5-9  | Circuit schematics of the output VGA/buffer (a) and resistive network (b)     | 80 |

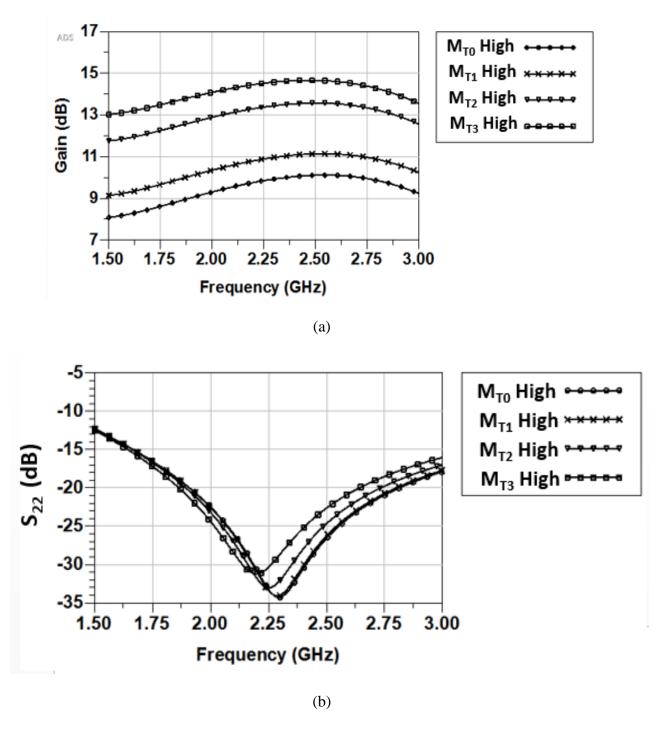

| Figure 5-10 | Simulated gain (a) and S <sub>22</sub> (b) of the designed VGA/buffer circuit | 82 |

| Figure 5-11 | Expanded circuit schematic of the phase shifter                               | 83 |

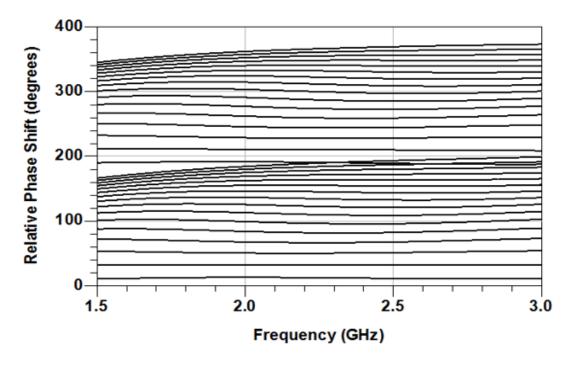

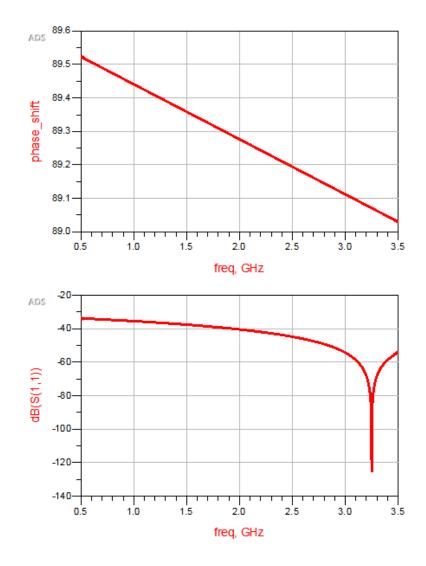

| Figure 5-12 | Simulated phase shift performance from the designed layout                    | 83 |

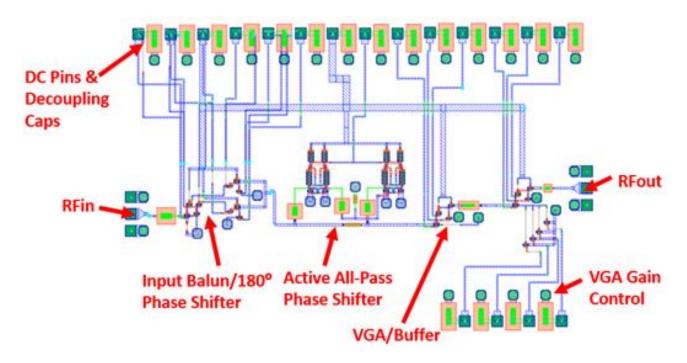

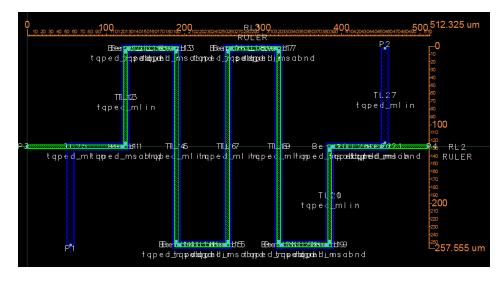

| Figure 5-13 | Layout of the complete phase shifter                                          | 84 |

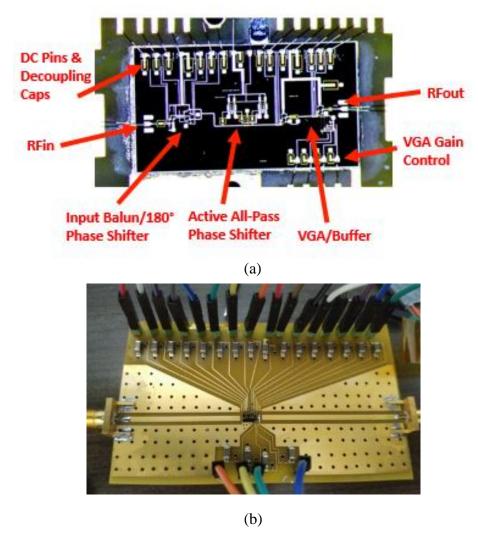

| Figure 5-14 | Fabricated phase shifter: (a) microphotograph; (b) test board                 | 85 |

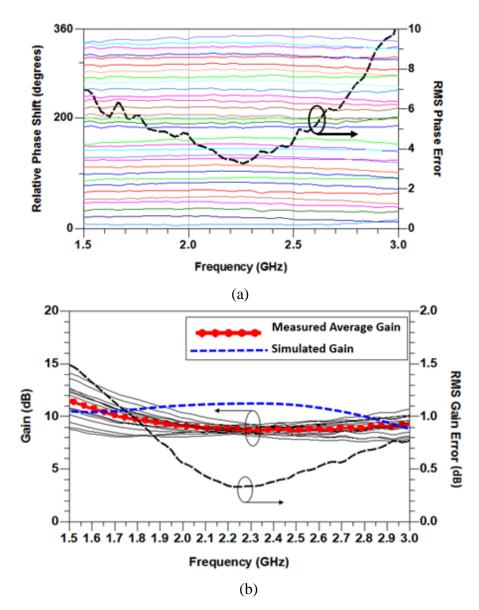

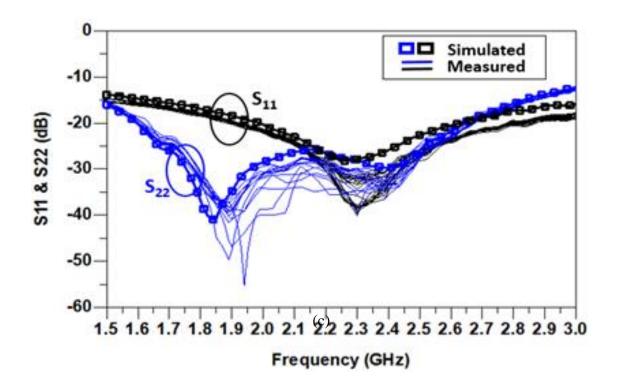

| Figure 5-15 | Measured performance of the fabricated phase shifter: (a) Phase response      |    |

|             | and RMS phase error; (b) Gain and RMS gain error; (c) $S_{11}$ and $S_{22}$ . | 86  |

|-------------|-------------------------------------------------------------------------------|-----|

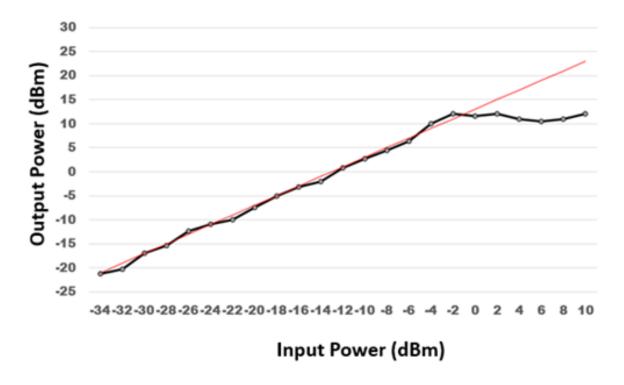

| Figure 5-16 | Measured P1dB performance at 3 GHz for high gain setting                      | 89  |

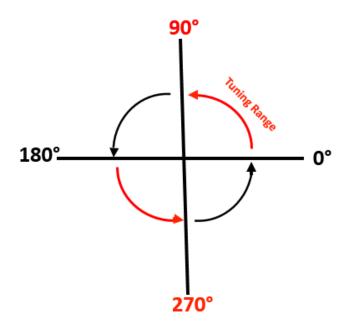

| Figure 6-1  | Tuning range of active all-pass filter with digital 90° phase shifter         | 93  |

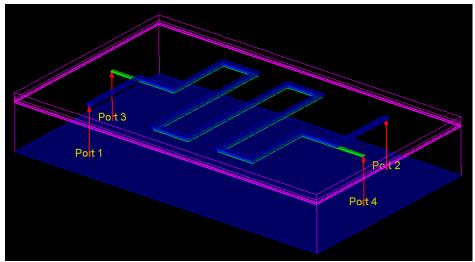

| Figure 6-2  | Broadside 90° coupler and 3D view                                             | 94  |

| Figure 6-3  | Simulated performance of broadside coupler                                    | 95  |

| Figure 6-4  | System level view with broadside coupler                                      | 95  |

| Figure A-1  | Switched all-pass phase shifter                                               | 96  |

| Figure A-2  | MathCAD worksheet                                                             | 97  |

| Figure A-3  | Tunable active inductor                                                       | 98  |

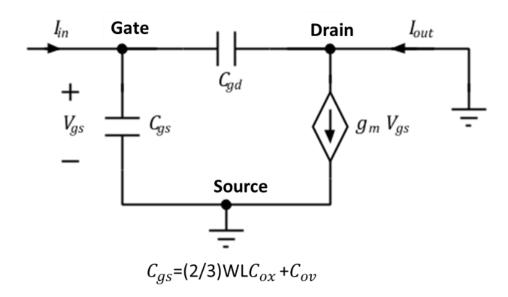

| Figure A-4  | Basic transistor model                                                        | 100 |

| Figure A-5  | Frequency response of active inductor                                         | 101 |

| Figure A-6  | Replacing all-pass switch network with tunable version                        | 102 |

| Figure A-7  | Active balun                                                                  | 103 |

| Figure A-8  | VGA/Buffer schematic                                                          | 104 |

#### **Abstract**

This dissertation addresses the design of monolithically integrated phase shifters at S- and Lfrequency bands using a commercially available GaAs process from Triquint. The focus of the design is to operate over a wide bandwidth with full 360° phase shift capability, 50  $\Omega$  input/output impedance match and low RMS phase and gain errors. The first version of the design is based on passive all-pass phase shifters integrated with wideband amplifiers to compensate for insertion loss. This design uses a 4-bit system to achieve the required phase shift and each bit consists of 3 sections of all-pass filters designed at separate frequencies within the 0.8 – 3 GHz band. Simulation results show a complete 360° phase shift with RMS gain error of less than 0.6 dB and RMS phase error of less than 2.5°. The system is also shown to achieve good input and output impedance matching characteristics. However, the fabricated prototype fails to perform with full functionality due to the excessive number of passive inductors in the design and the resulting mutual coupling. The mutual coupling issue could be solved by spacing out the layout to allow more separation among the inductors. Unfortunately, in the S- and L-bands, this is not an option for this research work as the fabricated design already uses the maximum allowed chip size as determined by the foundry. In addition, larger chip sizes considerably increase the cost in practical applications. To address the challenging needs of small size, wide bandwidth and low frequency applicability, the second design introduced in this dissertation proposes a novel phase shifter implementation that utilizes tunable active differential inductors within all-pass networks. The inductor tuning is used to achieve phase shifts up to 180°. A switchable active balanced to unbalanced transition circuit (balun) is included in front of the all-pass network to complement its phase shift capability by

another 180°. In addition, the all-pass network is followed by a variable gain amplifier (VGA) to correct for gain variations among the phase shifting states and act as an output buffer. Although active inductors have been previously used in the design of various components, to the best of our knowledge, this is the first time that they have been used in an all-pass phase shifter. The approach is demonstrated with an on-chip design and implementation exhibiting wideband performance for S and L band applications by utilizing the 0.5 µm TriQuint pHEMT GaAs MMIC process. Specifically, the presented phase shifter exhibits 1 × 3.95 mm² die area and operates within the 1.5 GHz to 3 GHz band (i.e. 2:1 bandwidth) with 10 dB gain, less than 1.5 dB RMS gain error and less than 9° RMS phase error. Comparison with the state-of-the-art MMIC phase shifters operating in S and L bands demonstrates that the presented phase shifter exhibits a remarkable bandwidth performance from a very compact footprint with low power consumption. Consequently, it presents an important alternative for implementation of wideband phase shifters where all-passive implementations will consume expensive die real estate.

# **Chapter 1:**

## Introduction

#### 1.1 Overview

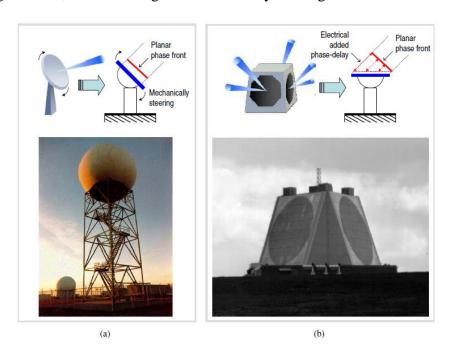

A phased array is a group of antennas which act as a single antenna unit and allow the transmission or reception of an electronic signal in a specific direction (Beam-steering) by adjusting its effective radiation pattern while suppressing signals from undesired directions. The shape of the radiated pattern (Beam- Forming) can also be achieved by changing the signal amplitude in each antenna [1.1]. Combining the signals coherently also improves the signal to beam steering methods, the first being the mechanically rotating reflectors shown in Figure 1(a)

Figure 1-1. Array antenna systems: (a) mechanically steered, rotating reflector array and (b) electrically steered, fixed phased-array

noise ratio (SNR) of the system compared to a single antenna element. There exist two main beam steering methods, the first being the mechanically rotating reflectors shown in Figure 1(a) [1.2, 1.3] where the reflective surface is moved to change the angle of the beam and the second being the electronically beam steering phased array where beam steering is achieved by changing the phase of the signal on each antenna in the array as shown in Figure 1(b) [1.2, 1.3].

Phased array systems provide several advantages over mechanical radars since phased arrays can transmit multiple beams simultaneously while place a null in the direction of undesired signals such as jammers. These array systems can be one, two or three dimensional, and have a planar or conformal surface. In the case of a passive phased array (does not include any active devices providing gain to the system), the individual antenna elements consist of a T/R module which is a cascade of a phase-shifter and an attenuator where each element is individually adjusted to steer the beam. For the best performance of the phase array it is necessary to improve system noise figure as well as transmitter output power which can be achieved by using an active T/R module which has both a low noise and high power amplifier located inside it and can be used to compensate the losses of the feed network.

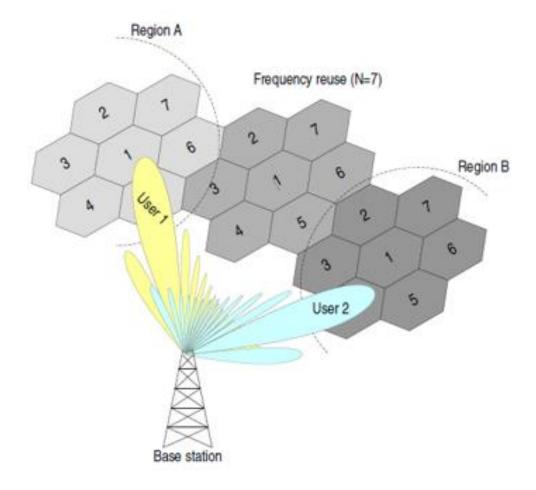

In the past, phased array systems were mainly used for military and government applications such as Search and Detection, Target Tracking, Missile Guidance, Air Mapping Systems and Ground and Battle field Surveillance [1.4]. Recently, phased array systems are being introduced for mobile cellular communications, automotive radar, Wi-Fi/Wimax networks as well as navigation and air traffic control [1.5, 1.6]. Figure 1-2 shows an example of implementation of phased array systems in mobile cellular networks which allows for an increase number of users to share the same available network [1.6]. It works by focusing energy in the desired direction thus minimizing energy toward other directions and satisfying transmit power requirements.

Figure 1-2. Beamforming in cellular wireless communication network

Some examples for civilian use of phased array systems is shown in Figure 1-3 [1.6]. Significant improvement in lead time for severe weather is made possible by rapid scan capabilities of phased arrays decrease warning times associated with extreme weather events. Phased-arrays also make it possible to more quickly accomplish aircraft surveillance tasks leading to more efficient air traffic controls. Phased-arrays systems can also be used to diagnose air quality at a level needed to track airborne biological, radiological, chemical and nuclear contaminants in the atmosphere.

Figure 1-3. Phased-array applications in civilian sectors

Early phased array systems were developed exclusively using off the shelf components with a hybrid-design concept that includes printed circuit board components such as microstrip traces and strip lines as well as passive components combined with microwave integrated circuits resulting in not only high cost but also resulted in large bulky systems that consumed a lot of power [1.7]. Recently, commercial applications have become more feasible from a cost standpoint due to the maturity of technology of integrated circuits. This makes it possible to integrate the entire RF T/R chain into a single monolithic microwave integrated circuit or module thereby reducing the cost as well as size weight and power (SWaP) of the phased array system [1.8]. Leveraging the maturity of integrated circuits, low cost, highly reliable phase array systems can now be designed and implemented for both military as well as commercial applications.

In the design of phased array systems, the phase shifter is the most essential element and is also the most difficult to design, especially when integrated on a single chip. Considering chip integration, the phase shifter represents a considerable portion of the overall system cost [1.3] and while the demand for phased array systems has been dominated by military applications that can absorb this cost, many commercial applications have recently emerged as discussed previously. In the case of on-chip integration, small circuits are favorable concerning costs and depending on the frequency of operation, different design techniques for the phase shifter should be considered. At lower Rf frequencies such as S- and L- band applications, some passive phase shifters require large inductors which consume a lot of chip real estate requiring alternative design approach. Some of the performance constraints and requirements for robust phase shifter design are 360° phase shift, adequate bandwidth, small size, low power consumption, low RMS phase and gain error, adequate linearity and unconditional stability. To meet these specifications at different frequencies, both active (provides gain to system) and passive phase shifters have been designed including reflective type phase shifter, tuned transmission lines, vector modulator type and switch filter. These types of phase shifters and more are briefly discussed in the next section.

#### 1.2 Brief Review of Previous Work

Using coupled transmission-line elements, B.M. Schiffman [1.9], in the 1950's demonstrated the concept of broadband microwave phase shifters by designing a matched differential phase shifter. Several improvements based on the Schiffman method were subsequently reported during the years [1.10] – [1.18]. The Schiffman method consists of the use of parallel coupled transmission lines with one being the reference path and the other providing the required phase shift, determined by the length of the transmission line. In [1.10], improvements to the Schiffman original approach was obtained by using new forms of multi-section coupled lines. The

requirement of very narrow gaps between the lines provided to be troublesome using printed circuit board (PCB) technology. Reference [1.11] used a multi-section Schiffman phase shifter to achieve more than 90% bandwidth with very small phase ripple and good return loss. Again here, PCB fabrication technology limited the applicability of the design since it also required very narrow gaps as well as high impedance lines. The approach in [1.15] used a Schiffman phase shifter together with a network of switches implemented as transmission lines, to achieve broadband performance for 90° and 180° phase shifters at 3 GHz. A similar approach was used in [1.16] where a broadband 180° phase shifter was designed. This design used a different approach for the design of the switching network and included the use of coupled lines and parallel open and short circuit stubs. Measured performance showed a return loss of 14 dB with maximum phase deviation of 5° from 1.5 to 4.5 GHz. In [1.18] the use of open circuit and short circuit multi-section stubs presented a new approach to the design of a 45° phase shifter. The proposed design was much smaller in size with better bandwidth performance than its predecessors. Despite this smaller size, the use of passive components makes in impractical for chip integrations as the size would be excessively large.

The design of switched line, reflection type, loaded line and high-pass low-pass phase shifters using PIN diodes as switches was reported in [1.20]. In [1.21], improved bandwidth and larger phase shifts of these types of phase shifters was reported. Here, both constant phase shift as well as constant time delay performance was improved by eliminating resonance effects which negatively affect both amplitude and phase response. A reflection type 180° phase shifter was proposed in [1-24] that used both series and parallel LC circuits as well as a 3 dB Lange coupler. The design was implemented as a MMIC with a 180° phase shift from 0.5 to 30 GHz. The work reported in [1.25] used lumped element all-pass filters to design a C-band 5 bit MMIC. In [1.26],

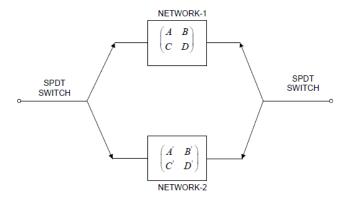

a series cascade of all-pass filters is used to develop a full 360° MMIC phase shifter by implementing thin film BST varactors, resulting in a low cost compact phase shifter. The authors in [1.28] presented a unique method of designing broadband phase shifters using networks of unbalanced all-pass filters in combination with single-pole double-throw switches (SPDT). Cascading two or more of these networks provided phase shifts with single- and multi- octave bandwidth. All-pass networks are suitable for RF applications at lower frequency bands since the transition frequency of the all-pass network can be at a higher frequency of operation. This in turn, results in smaller passive components especially for inductors which for MMIC applications translated into small chip area. The initial design in this dissertation is based on this design technique while the second part uses the initial design criteria to establish a baseline for the final active phase shifter design. More details on the design of passive all-pass phase shifter is presented in Chapter 3.

Various analog techniques using vector summation have recently been reported [1.29] – [1.35]. This technique achieves the desired phase shift by varying the amplitude of I/Q signals using variable gain amplifiers or attenuators. This approach lends itself quite suitable to integrated circuit applications because of its limited use of bulky passive components. At lower RF frequencies such as S- and L- band the necessary requirement for the generation of I/Q signals results in bulky R-C based lumped passive quadrature networks using either RC-CR or R-C polyphase filters which also have very limited bandwidth [1.29].

## 1.3 Motivation and Organization of the Dissertation

Studies and research on phase shifters generally focus on achieving high phase shift resolution with minimal phase error as well as low gain variation between the different phase states in as

wide a bandwidth as possible all while being as small as possible to minimize cost (chip real estate).

The purpose of this research is to improve on the design of broadband all pass phase shifters in the L- and S- frequency range and implement this in integrated circuit form in an effort to decrease the size of the phase shifters while providing minimal phase and amplitude errors for phase shifts from 0° to 360°. All design will be implemented in a 0.5 µm GaAs pHEMT process with both enhancement and depletion mode transistors. The challenge here is to realize a phase shifter capable of providing 360° phase shift with good performance metrics while occupying a small chip size which can be a problem at the lower S- and L- band frequencies. Using techniques implemented in both board level and integrated circuit designs two design approaches are introduced. The first consists of the design of passive all-pass phase shifters and wideband amplifiers implemented in a 4-bit system with each bit consisting of 3 separate sections of all-pass filters to achieve a full 360° phase shift. The second design technique uses a different approach to the first. Here, an active tunable inductor together with a broadband active balun and variable gain amplifier is designed to achieve a similar function to the passive all-pass network of the first design resulting in a very compact and tunable phase shifter capable of achieving 360° phase shift with good input and output match and low RMS gain and phase error and occupying ¼ chip size of first design.

The main achievements of this work include:

A 1.5 GHz to 3 GHz wideband active balun/180° phase shifter with switchable outputs and stable input match. It has a gain error of less than 0.3 dB and phase error of less than 2° across the entire frequency range. Design implemented in 0.5 μm GaAs process.

- Wideband 1.5 GHz to 3 GHz two stage variable gain amplifier/buffer using switchable resistor network for gain variation from 10 dB to 15 dB at mid-band with stable output match. Design also implemented in 0.5 µm GaAs process.

- Novel all-pass phase shifter using active tunable inductor to achieve tunable phase shift up to 180° with a single stage at s- and L- band and occupying ¼ chip size of a similar phase shifter using passive components to achieve similar functions. Design was also implemented in 0.5 µm GaAs process.

- A complete S- and L- band phase shifter capable of achieving full 360° phase shift using components listed above with a chip size 0f 2.7 x 4.5 mm<sup>2</sup> including all bias lines and bondpads. Measured results show a gain of 10 dB, RMS phase error < 9, RMS gain error < 1.5, power consumption of 78 mW, P1dB of 12 dBm at mid-band and fractional bandwidth of 67%.

- All designs described about use techniques that can easily be implemented in cheaper silicon process.

The dissertation consists of 6 chapters. Chapter 2 covers phase shifter fundamentals that include a basic explanation of phase shifter, phase shifter architectures and performance requirements. Having discussed the different phase shifter architectures, the passive all-pass architecture was selected as the best choice for the current application because of its inherent match to  $50~\Omega$  and wideband performance. Chapter 3 then goes into more details about broad-band all-pass phase shifter design, discussing the all-pass filter design theory and its implementation in the design of phase shifters. It then details the design of a broadband all-pass passive phase shifter implemented in  $0.5~\mu m$  GaAs process. However, the fabricated prototype fails to perform with full functionality due to the excessive number of passive inductors in the design and the resulting mutual coupling.

The mutual coupling issue could be solved by spacing out the layout to allow more separation among the inductors. Unfortunately, in the S- and L-bands, this is not an option for this research work as the fabricated design already uses the maximum allowed chip size as determined by the foundry. Chapter 4 details a different approach to the problem and goes into details on the design of active inductors using gyrator networks. Detailed design techniques are presented into the design of a floating active inductor. Chapter 5 implements the active inductor designed in the previous chapter into an active all-pass phase shifter using the same knowledge presented in chapter 3 for the design of broadband phase shifters. The conclusions and recommendations are then discussed in Chapter 6.

## 1.4 Technology Overview

The technology utilized for the circuits developed in this work was provided by Triquint (Qorvo). The TQPED GaAs process is a 150mm, 0.5 µm, pHEMT process with both depletion and enhancement mode pHEMTs. This process is targeted for high efficiency and linearity in power amplifier, high linearity and low loss in RF switch, low noise in low-noise amplifier applications.

The standard TQPED process offers a D-Mode pHEMT with a –0.8 V pinch off and an E-Mode pHEMT with a Vp of +350 mV. The three metal interconnecting layers are encapsulated in a high performance dielectric that allows wiring flexibility, optimized die size and plastic packaging simplicity. Precision NiCr resistors and high value MIM capacitors are included allowing higher levels of integration, while maintaining smaller, cost effective die sizes.

#### 1.5 References

- [1.1] H. L. Van Trees, Optimum Array Processing. Part IV of Detection, Estimations, and Modulation Theory. Wiley New York, NY, 200

- [1.2] V. F. Fusco, "Mechanical Beam Scanning Reflectarray," IEEE Trans. Antennas and Propagation, vol. 11, no. 53, pp. 3842–3844, Nov. 2005.

- [1.3] Federal Research and Development Needs and Priorities for Phased Array Radar (FCMR25-2006). Report from Office of the Federal Coordinator for Meteorological Services and Supporting Research (OFCM), 2006.

- [1.4] D. Parker and D. C. Zimmermann, "Phased arrays-part II: implementations, applications, and future trends," IEEE Trans. Microw. Theory Techn., vol. 50, pp. 688-698, 2002.

- [1.5] A. Hottinen, M. Kuusela, K. Hugl, J. Zhang, and B. Raghothaman, "Industrial embrace of smart antennas and MIMO," IEEE Wireless communications, vol. 13, no. 4, pp. 8–16, Aug. 2006.

- [1.6] A. Alexiou and M. Haardt, "Smart antenna technologies for future wireless systems: trendsand challenges," IEEE communications Magazine, vol. 42, no. 9, pp. 90–97, Sep. 2004.

- [1.7] A. J. Fenn, D. H. Temme, W. P. Delaney, and W. E. Courtney, "The Development of Phased-Array Radar Technology," Lincoln Laboratory Journal, vol. 12, no. 2, pp. 321–339, 2002

- [1.8] FCM-R25-2006, "Federal research and development needs and priorities for phased array radar", available online at: http://www.ofcm.gov/r25-mpar/fcm-r25.Html

- [1.9] B. Schiffman, "A New Class of Broadband Microwave 90-degree Phase Shifter," IRE Trans. Microw. Theory Tech., vol. MTT-6, no. 4, pp. 232-237, Apr. 1958.

- [1.10] B. Schiek and J. Kohler, "A Method for Broad-Band Matching of Microstrip Differential Phase Shifters," IEEE Trans. Microw. Theory Tech., vol. MTT-25, no.8, pp. 666-671, Aug. 1977.

- [1.11] J. L. P. Quirarte and J. P. Starski, "Synthesis of Schiffman Phase Shifters," IEEE Trans. Microw. Theory Tech., vol. 39, no. 11, pp. 1885-1889, Nov. 1991.

- [1.12] J. Quirarte and J. Starski, "Novel Schiffman Phase Shifters," IEEE Trans. Microw. Theory Tech., vol. 41, no. 1, pp. 9-14, Jan. 1993.

- [1.13] W. J. Brown and J. P. Starski, "A Broad-Band Differential Phase Shifter of Novel Design," in IEEE MTT-S Int. Microw. Symp. Dig., vol. 3, pp. 1319-1322, 1999.

- [1.14] V. P. Meschanov, I. V. Metelnikova, V. D. Tupkin, G. G. Chumaevskaya, "A New Structure of Microwave Ultrawide-Band Differential Phase Shifter," IEEE Transactions on Microwave Theory and Techniques, vol. 42, no. 5, May 1994.

- [1.15] S. Y. Eom, S. I. Jeon, J. S. Chae, and J. G. Yook, "Broadband 180° Bit Phase Shifter Using a New Switched Network," in IEEE MTT-S Int. Microw. Symp. Dig., vol. 1, pp. 39-42, June 2003.

- [1.16] Soon-Young Eom, "Broadband 180° Bit Phase Shifter Using  $\Box\Box$  / 2 Coupled Line and Parallel  $\Box\Box$  /8 Stubs," IEEE Microwave and Wireless Components Letters, vol. 14, no. 5, May 2004.

- [1.17] Y. Guo, Z. Zhang, and L. Ong, "Improved Wideband Schiffman Phase Shifter," IEEE Trans. Microw. Theory Tech., vol. 54, no. 3, pp. 1196-1200, Mar. 2006.

- [1.18] S. Y. Zheng, S. H. Yeung, W. S. Chan, K. F. Man and S. H. Leung, "Improved Broadband Dumb-Bell-Shaped Phase Shifter Using Multi Section Stubs," Electronics Letters, vol. 44, no. 7, pp. 478-480, Mar. 2008.

- [1.19] Amin M. Abbosh, "Ultra-Wideband Phase Shifters," IEEE Trans. Microw. Theory Tech., vol. 55, no. 9, pp. 1935-1941, Sep. 2007.

- [1.20] Garver R., V., "Broad-Band Diode Phase Shifters," IEEE Transactions on Microwave Theory and Techniques, vol. MTT-20, no. 5, pp. 314-323, May 1972.

- [1.21] Guy D. Lynes, "Ultra Broadband Phase Shifters," Microwave Symposium Digest, G-MTT International, vol. 73, pp. 104-106, Jun 1973.

- [1.22] E. Menzel, B. Shiek, A. Gronefeld, "Broadband Phase Shifters Using RC-Allpass-Networks and Active Balun Circuits," European Microwave Conference, pp. 397-402 Oct. 1988.

- [1.23] K. Hajek, J. Sedlacek and B. Sviezeny, "New Circuits for Realization of the 1st and 2nd Order All-Pass LC Filters with a Better Technological Feasibility," 2002 IEEE, vol. 3, pp. 523-526.

- [1.24] K. Miyaguchi, M. Hieda, K. Nakahara, H. Kurusu, M. Nii, M. Kasahara, T. Takagi, "An Ultra Broad Band Reflection Type 180° Phase Shifter with Series and Parallel LC Circuits," 2001 IEEE MTT-S Int. Micr. Symp. Dig, vol. 1, pp. 237-240.

- [1.25] K. Miyaguchi, M. Hieda, M. Hangai, T. Nishino, N. Yunoue, Y. Sasaki and M. Miyazaki, "An Ultra Compact C-Band 5 bit MMIC Phase Shifter Based on All-Pass Network," in Proceedings of the 1st European Microwave Integrated Circuits Conference, pp. 277-280, September 2006, Manchester UK.

- [1.26] L.-Y. V. Chen, R. Forse, A. H. Cardona, T. C. Watson, R. York, "Compact Analog Phase Shifters using Thin-Film (Ba,Sr) Varactors," Microwave Symp. 2007, IEEE MTT-S, pp. 667-670, June 2007.

- [1.27] D. Kholodnyak, E. Serebryakova, I. Vendik, O. Vendik, "Broadband Digital Phase Shifter Based on Switchable Right- and Left-Handed Transmission Line Sections," IEEE Microwave and Wireless Components Letters, Vol. 16, No. 5, pp. 258-260, May 2006.

- [1.28] D. Adler and R. Popovich, "Broadband Switched-Bit Phase Shifter Using All-Pass Networks," 1991 IEEE MTT-S Int. Microwave Symp. Dig., vol. 1, pp. 265- 268, July 1991.

- [1.29] K.-J. Koh and G. M. Rebeiz, "0.13-µm CMOS phase shifters for X-, Ku-and K-band phased arrays," IEEE J. Solid-State Circuits, vol. 42, no. 11, pp. 2535–2546, Nov. 2007

- [1.30] Y. Zheng and C. E. Saavedra, "Full 360° vector-sum phase-shifter for microwave system applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 4, pp. 752–758, Apr. 2010.

- [1.31] A. Asoodeh and M. Atarodi, "A full 360° vector-sum phase shifter with very low RMS phase error over a wide bandwidth," IEEE Trans. Microw. Theory Techn., vol. 60, no. 6, pp. 1626–1634, Jun. 2012.

- [1.32] S. P. Sah, X. Yu, and D. Heo, "Design and analysis of a wideband 15–35-GHz quadrature phase shifter with inductive loading," IEEE Trans. Microw. Theory Techn., vol. 61, no. 8, pp. 3024–3033, Aug. 2013

- [1.33] H. Zijie and K. Mouthaan, "A 0.5–6 GHz 360° vector-sum phase shifter in 0.13-μm CMOS," in IEEE MTT-S Int. Microw. Symp. Dig., Jun. 2014, pp. 1–3

- [1.34] Y. Kim, S. Kim, I. Lee, M. Urteaga, and S. Jeon, "A 220–320-GHz vector-sum phase shifter using single Gilbert-cell structure with lossy output matching," IEEE Trans. Microw. Theory Techn., vol. 63, no. 1, pp. 256–265, Jan. 2015.

- [1.35] C. Quan, S. Heo, M. Urteaga, and M. Kim, "A 275 GHz active vector sum phase shifter," IEEE Microw. Wireless Compon. Lett., vol. 25, no. 2, pp. 127–129, Feb. 2015.

# Chapter 2:

## **Phase Shifter Fundamentals**

## 2.1 Introduction

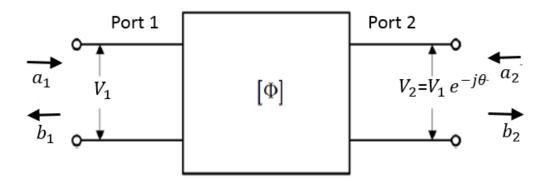

Phase shifters, in a simple way, can be described as a two-port device that changes the phase of the input signal with minimal amount of attenuation. In reality, phase shifters will have some amount of attenuation associated with the phase shift. This will depend on the type of phase shifter used, being either active or passive. Figure 1 shows a general two port network functioning as a phase shifter [2.1]. The output signal at port 2 is a combination of the input signal  $V_1$  with the additional phase shift denoted by  $e^{-j\theta}$  with the phase shift being  $\theta$ . In this ideal case, the signal does not experience any gain attenuation.

Figure 2-1. Block diagram of a phase shifter

The scattering matrix for the ideal two port phase shifter is given by:

$$\begin{pmatrix} b_1 \\ b_2 \end{pmatrix} = \begin{pmatrix} 0 & e^{-j\theta} \\ e^{-j\theta} & 0 \end{pmatrix} . \begin{pmatrix} a_1 \\ a_2 \end{pmatrix}$$

(2.1)

The insertion phase of the signal is the phase of  $S_{21}$  and the phase shift always has to be referenced to an initial state or it is meaningless and the phase shift of the signal will always be in comparison to the reference state. The phase shift ranges from  $0^0$  to  $360^0$  for complete rotation.

In practical applications insertion loss (or gain) will be experienced by the signal. The loss in dB is again derived from the scattering parameters as:

$$IL(dB) = 20\log_{10}|S_{21}| \tag{2.2}$$

In the design of phase shifters, phase performance is generally related to the insertion loss and used as a figure of merit when describing the performance. Insertion loss can be overcome with additional amplification in applications such as military radar where both phase and gain error are very important but comes at the cost of increased power consumption. In other systems such as automotive radar, a trade-off with power consumption can be made. In general, some of the most critical parameters of phase shifters are 360° phase shifting capability, insertion loss, amplitude variation, third-order intercept point (IP3), return loss, linearity of control function, power consumption and chip size for IC applications. Insertion loss is largely driven by the number of stages necessary to achieve a certain bandwidth as well as the topology used. Amplitude variation relates to phase shift and is the variation in insertion loss for different phase shift values. IP3 is a measure of linearity for the phase shifter while return loss shows how good of a match the input/output of the phase shifter is, typically in reference to  $50\Omega$ . Return loss plays a less important role for phase shifters implemented on chip as part of a system where its input/output are not directly interfacing with the 50  $\Omega$  outside world. Linearity of control function is the relationship between the control voltage and the corresponding phase shift values. Ideally this would be a linear relationship for passive phase shifters but is usually non-linear for active devices as transistor change states from cutoff to saturation.

#### 2.2 Types of Phase Shifters

Phase shifter may be analog or digital depending on the type of control that sets the different phase states. These can be either electric or mechanical control, based on the tuning mechanism used. Electronic phase shifters use electronic components to control the phase response. These include voltages and currents and have a much faster response than mechanical methods [2.1]. Mechanical phase shifters on the other hand are generally constructed using transmission lines structures in combination with some means of manual tuning to achieve the desired phase shift response.

Electronic phase shifters can be put into two major categories based on how they are controlled. Digital phase shifters are only able to achieve discreet phase shift values that depend on the resolution or number of bits and are controlled by set voltages. The idea behind digital phase shifters is to switch the signal between some reference path and some desired phase shift path with the phase shift being the difference. These require only digital voltages to control the switching paths which are usually done using electronic switches such as transistors or diodes. There are several ways of creating a phase shift bit using this approach. Continuous phase shifters vary the phase in a continuous manner and are capable of achieving any desired phase shift value within the tuning range with the appropriate applied tuning voltage. Continuous phase shifters are very popular especially for on-chip applications and are capable of achieving 360° phase shift. The control voltages for these types of phase shifters are usually implemented using multibit DAC for greater accuracy and ease of calibration. The discussion from this point onward will only include electronic phase shifters, both digital and continuous.

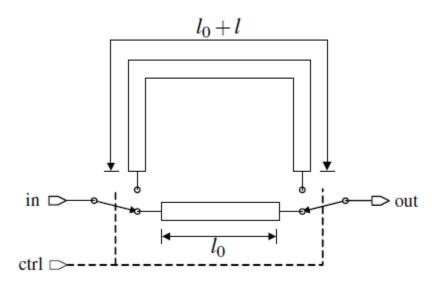

#### 2.2.1 Switched Line Phase Shifter

The Switch Line Phase Shifter uses different line lengths as alternate the signal paths controlled by switches as shown in Figure 2 [2.2]. The difference in time delay between the two paths accounts for the phase shift where the time delay (in seconds) for a given line of length  $L_0$  is  $\tau_D = \frac{2\pi L_0}{v_p}$ . The phase shift (in degrees) can be derived from the line length difference between the reference and modified lines. Given a difference in length  $\Delta L$ , the time delay becomes  $\Delta \tau_D = \frac{2\pi \Delta L}{v_p}$  where  $v_p$  is the phase velocity.

Figure 2-2. Switch-line phase shifter

One of the major advantages of switched line phase shifters is that the phase shift is wideband which avoids or minimizes bean squinting in wideband arrays. For low GHz applications, this architecture is quite bulky and suffers from variations in attenuation between the two paths because of the varying line lengths. Loss can become significant and therefore not ideal for applications that require SWaP (size, weight and power) performance.

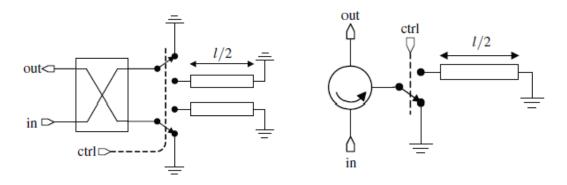

# 2.2.2 Reflection Type Phase Shifter

Reflection type phase shifter use the directional properties of a 3-dB hybrid coupler (Fig 2-3a) or of a circulator (Figure 2-3b) [2.3]. In the 3dB 90° hybrid coupler the power incident at the excitation port gets divided evenly to thru port and coupled port with 90° phase difference. Based on the state of the switch, the two parts are either reflected back and recombine at the output port or travel on the l/2 transmission line and are reflected back having travelled an additional l/2 length before being recombined. Since the total traveled length is l, the time delay that the signal is subject to is provided by  $\tau_D = \frac{2\pi L_0}{v_p}$ . Either PIN diode or FET switching may be used for digital phase shift operation. A reflection type phase shifter with a very compact termination circuit is reported in [2.4].

Figure 2-3. Reflection type phase shifter (a) hybrid, (b) circulator

#### 2.2.3 Loaded Line Phase Shifter

In loaded line phase shifters, instead of using varying line lengths to achieve the phase shift as in the previous two techniques, phase difference is created by changing the propagation characteristics of the transmission line by switching between shunt susceptance or series reactance as it is seen in Figures 2-4.a and 2-4.b [2.1]. This is done by manipulating the characteristics of the transmission line which are composed of a quarter wavelength transmission line with both ends terminated by either an inductive or capacitive load. The drawback with the use of quarter

wavelength lines is that it limits the useful bandwidth of this design. As the phase shift values increase, quality of the input match degrades so it is not applicable for requirements that call for large phase shifts or large bandwidth.

Figure 2-4. Loaded-line phase shifter

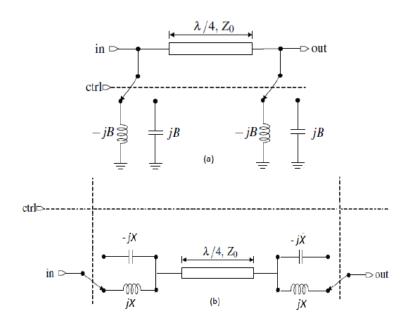

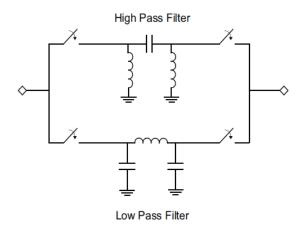

#### 2.2.4 High/Low Pass and All Pass Phase Shifter

A high pass passive network in parallel with low pass network (HPF-LPF) (Fig. 2-6)[2.4] as well as two parallel all pass filter networks (APF) (Fig 2-7) [2.5] can be used to design phase shifters which are based on filter networks and are popular switching phase shifter topologies with similar operation principles. This type of phase shifter uses circuits which only require "digital" control voltages used to control SPDT switches to switch between two paths, these being the high pass path and the low pass path or between all pass filters path as shown in Figure 2-5. One path becomes the reference path and the other the phase shift path. The desired phase shift is the phase difference between the reference and phase path. High pass filters provide a phase advance, while the opposite can be said for the low pass filter, giving a phase delay. Both HPF-LPF and APF

topologies exhibit good return loss characteristic which allows for easy tuning over the desired phase shift performance. Overall insertion loss and chip size increase with increasing phase shift resolution as these require more networks in cascade. This architecture has been implemented on chip because of its small size and flat phase response at high frequencies (> 5 GHz) but become bulky at lower frequencies which require higher values of inductors in implementing the filters.

Figure 2-5. Phase shifter with switching elements

Figure 2-6. High pass/low-pass network

## 2.2.5 Vector Modulators

All the phase shifters described previously can be classified as digital since these only provide discrete phase states. Continuous phase shifters may be attractive for on-chip applications that

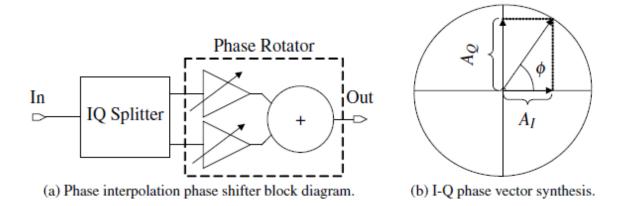

require a full 360° phase shift with high resolution. The control voltages for these types of phase shifters are usually implemented using multibit DAC for greater accuracy and ease of calibration. Vector Modulators (Fig. 2-7a) form a continuous type of phase shifter capable of achieving 360<sup>0</sup> phase shift [2.6] – [2.7]. Also called a phase interpolation phase shifter, it functions by splitting the input signal into two equal amplitude signals that are ideally 90° apart in phase. The two signals are then amplified by two variable gain amplifiers (VGAs) and then summed, forming the output signal. The phase shift is determined by the gain of the two VGAs which are independent of each other. Using this approach, phase between 0° and 360° can be achieved. The weighted summation of the I and Q components used to form the resultant phase shift is shown in Figure 2-7b. This type of architecture is quite common for integrated circuit implementation because of it's extensive use of active components. One major drawback of this approach is the exceptional accuracy and complexity required of the amplitude control components to minimize the RMS phase errors which in turn requires complex control circuitry to ensure precision of the phase shift. Apart from this, operation at lower RF frequencies results in bulky passive I/Q splitters that may not be able to be integrated on chip.

Figure 2-7. Vector modulator phase shifter

# 2.2.6 Periodically Loaded Transmission Line

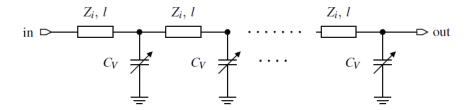

Figure 2-8. Periodically loaded line phase shifter

Tunable transmission lines can be used as phase shifters. The lumped element equivalent circuit of the periodically loaded line phase shifter is depicted in figure 2-8 [2.8] and is composed of series transmission lines and shunt varactors. Tuning the varactors causes the characteristics of the transmission line can also be varied. If a unit cell of the artificial transmission line is assumed to have characteristic impedance Zi with a corresponding phase velocity vi and length l, then the equivalent inductance and capacitance of each section is given as:

$$L_t = \frac{lZ_i}{v_i} \tag{2.3}$$

$$C_t = \frac{l}{Z_i v_i} \tag{2.4}$$

By varying the capacitance of the line using the varactors, the characteristics of the artificial line change and the phase shift becomes a function of the varying capacitance as:

$$\Delta \emptyset = 2\pi f \frac{i}{v_p} \left( \sqrt{1+x} - \sqrt{1+xy} \right) \tag{2.5}$$

$$x = \frac{C_{v\_max}}{C_t}$$

$$y = \frac{C_{v\_min}}{C_{v\_max}}$$

The lumped element equivalent circuit implementation is preferred as it is smaller than the transmission line and this can be implemented as low-pass or high-pass structures using lumped inductors and varactors. Cascading several sections can increase the phase resolution at the cost of higher insertion loss but can achieve 360° phase shift.

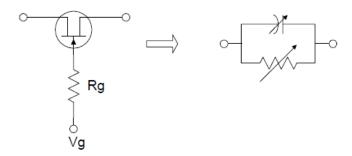

#### 2.2.7 Integrated Switches

The use of switches in the realization of phase shifters such as those described previously in sections 2.2.1-2.2.4 becomes very important for phase shifter performance in particular that associated with insertion loss. Most switches used in these examples rely on FET technology to achieve the switching function. By means of gate voltage, the channel conductivity of the FET can be controlled while consuming no DC power. Varying the channel resistance R<sub>DS</sub> the FET as a switch, can either be turned OFF or ON. In other words, the channel resistance behaves as a voltage variable resistor. Figure 2-9 below shows the equivalent circuit of a FET used as a switch. Typical performance metrics of a switch are it ON resistance and OFF capacitance which are determined by the process used and the size of the FET. These have a direct impact on the undesired insertion loss in ON state and high frequency isolation in the OFF state.