# Singapore Management University Institutional Knowledge at Singapore Management University

Dissertations and Theses Collection (Open Access)

Dissertations and Theses

1-2014

# Virtualization-based System Hardening against Untrusted Kernels

Yueqiang CHENG

Singapore Management University, yqcheng.2008@phdis.smu.edu.sg

Follow this and additional works at: http://ink.library.smu.edu.sg/etd\_coll

Part of the <u>Databases and Information Systems Commons</u>, <u>Information Security Commons</u>, and the <u>Systems Architecture Commons</u>

#### Citation

CHENG, Yueqiang. Virtualization-based System Hardening against Untrusted Kernels. (2014). 1-179. Dissertations and Theses Collection (Open Access).

Available at: http://ink.library.smu.edu.sg/etd\_coll/105

This PhD Dissertation is brought to you for free and open access by the Dissertations and Theses at Institutional Knowledge at Singapore Management University. It has been accepted for inclusion in Dissertations and Theses Collection (Open Access) by an authorized administrator of Institutional Knowledge at Singapore Management University. For more information, please email libIR@smu.edu.sg.

# Virtualization-Based System Hardening Against Untrusted Kernels

YUEQIANG CHENG

SINGAPORE MANAGEMENT UNIVERSITY 2013

# Virtualization-Based System Hardening Against Untrusted Kernels

# by **Yueqiang Cheng**

Submitted to School of Information Systems in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in Information Systems

#### **Dissertation Committee:**

Robert DENG Huijie (Supervisor / Chair) Professor of Information Systems Singapore Management University

Xuhua DING (Co-supervisor) Associate Professor of Information Systems Singapore Management University

Debin GAO Assistant Professor of Information Systems Singapore Management University

Yongdong WU Senior Scientist of Infocomm Security Department Institute for Infocomm Research

Singapore Management University 2013

Copyright (2013) Yueqiang Cheng

## Virtualization-Based System Hardening Against Untrusted Kernels

#### Yueqiang Cheng

#### **Abstract**

Applications are integral to our daily lives to help us processing sensitive I/O data, such as individual passwords and camera streams, and private application data, such as financial information and medical reports. However, applications and sensitive data all surfer from the attacks from kernel rootkits in the traditional architecture, where the commodity OS that is supposed to be the secure foothold of the system is routinely compromised due to the large code base and the broad attack surface. Fortunately, the virtualization technology has significantly reshaped the landscape of the modern computer system, and provides a variety of new opportunities for us to protect application and sensitive data.

In this dissertation, we first design and implement a lightweight and reliable hypervisor *Guardian* as the system secure foothold, which leverages virtualization technology and a secure boot and shutdown mechanism to protect itself in its whole life cycle. Guardian is the first bare-metal hypervisor with integrity and availability guarantees. Moreover, we extend Guardian to be a framework of secure foothold, which consists of summarized common security primitives for facilitating our proposed systems and other security services. Based on the reliable secure foothold (Guardian), we propose *AppShield*, which protects critical applications through putting them into isolated execution environments (IEEs). In an IEE, AppShield is able to reliably and efficiently protect data secrecy and integrity of a critical application, as well as the execution integrity, against kernel rootkit attacks. Moreover, it is able to defend against newly identified threats, which are evidence that protecting applications against the malicious OS is more difficult than previously realized.

The inputs and outputs of protected application are not protected by AppShield such that they could be tampered by kernel rootkits. To fix this gap, we propose

a trusted path (TP) scheme, named as *Driverguard*, to protect I/O flows between hardware input/output devices and protected applications. DriverGuard is the first generic approach that protects all kinds of I/O flows with a combination of cryptographic and virtualization techniques. The combination of IEE and TP could protect almost all applications and sensitive data. But for certain user data, we could do it better. In this dissertation, we purpose a dedicated system *KGuard* to protect user passwords in the increasingly popular online services without needing any IEE and trusted path. In particular, KGuard does not trust any software components in the guest kernel and user space (without IEE requirement), and also not leverage any special hardware to assist the protection.

We implement the prototypes of all the above systems, and evaluate their performance overheads. The experiment results show that the performance costs on CPU computation and device I/O are insignificant.

# **Table of Contents**

| 1 | Intr | oduction | n                               | 1  |

|---|------|----------|---------------------------------|----|

|   | 1.1  | Proble   | m Overview                      | 1  |

|   | 1.2  | Resear   | ch Objectives                   | 3  |

|   |      | 1.2.1    | Reliable Secure Foothold        | 3  |

|   |      | 1.2.2    | Application Protection          | 4  |

|   |      | 1.2.3    | I/O Data Protection             | 5  |

|   | 1.3  | Threat   | Model                           | 6  |

|   | 1.4  | Metric   | s                               | 8  |

|   | 1.5  | Termin   | nology                          | 8  |

|   | 1.6  | Dissert  | tation Overview                 | 9  |

|   |      | 1.6.1    | Dissertation Organization       | 11 |

| 2 | Rela | ited Wo  | rk                              | 13 |

|   | 2.1  | Applic   | ation Protection                | 13 |

|   |      | 2.1.1    | Self-contained Code Protection  | 13 |

|   |      | 2.1.2    | Whole Application Protection    | 14 |

|   | 2.2  | I/O Da   | ta Protection                   | 16 |

|   |      | 2.2.1    | Virtualization-based Protection | 16 |

|   |      | 2.2.2    | Hardware-based Protection       | 17 |

|   |      | 2.2.3    | OS-based Protection             | 18 |

|   | 2.3  | Hyperv   | visor Security                  | 18 |

|   | 2.4  | Root o   | f Trust                         | 20 |

|   |       | 2.4.1    | Software-based Root of Trust                 | 20 |

|---|-------|----------|----------------------------------------------|----|

|   |       | 2.4.2    | Hardware-based Root of Trust                 | 20 |

| 3 | Relia | able Sec | cure Foothold                                | 22 |

|   | 3.1   | Proble   | m Definition                                 | 23 |

|   |       | 3.1.1    | Threat Model                                 | 23 |

|   | 3.2   | Design   | of Guardian                                  | 24 |

|   |       | 3.2.1    | Establishing Guardian as a Security Foothold | 24 |

|   |       | 3.2.2    | Secure User-Hypervisor Interface             | 31 |

|   | 3.3   | Implen   | mentation                                    | 32 |

|   |       | 3.3.1    | System Benchmark                             | 33 |

|   | 3.4   | Summa    | ary                                          | 35 |

| 4 | App   | lication | Protection                                   | 36 |

|   | 4.1   | Synops   | sis                                          | 37 |

|   |       | 4.1.1    | Threat Model                                 | 37 |

|   |       | 4.1.2    | Desired Properties                           | 38 |

|   |       | 4.1.3    | AppShield Overview                           | 38 |

|   | 4.2   | Dynan    | nic Address Space Isolation                  | 40 |

|   |       | 4.2.1    | Address Space Isolation                      | 40 |

|   |       | 4.2.2    | Dynamic Isolation                            | 41 |

|   | 4.3   | Secure   | Context Switch                               | 47 |

|   |       | 4.3.1    | Transit Module                               | 47 |

|   |       | 4.3.2    | Event Capture                                | 49 |

|   |       | 4.3.3    | Context and Address Space Switch             | 50 |

|   |       | 4.3.4    | Special Considerations                       | 51 |

|   | 4.4   | System   | n Call Adaption                              | 52 |

|   |       | 4.4.1    | System Call Emulation                        | 54 |

|   |       | 4.4.2    | Ptrace                                       | 55 |

|   | 4.5   | Implen   | mentation and Evaluation                     | 55 |

|   |     | 4.5.1    | Micro Benchmark                        | 56 |

|---|-----|----------|----------------------------------------|----|

|   |     | 4.5.2    | Macro Benchmark                        | 57 |

|   | 4.6 | Discus   | ssions                                 | 60 |

|   | 4.7 | Summ     | ary                                    | 61 |

| 5 | Gen | eric Pro | otection On I/O Flows                  | 62 |

|   | 5.1 | Proble   | m Definition                           | 63 |

|   |     | 5.1.1    | Our Goals                              | 63 |

|   |     | 5.1.2    | Threat Model and Assumptions           | 64 |

|   |     | 5.1.3    | Attacks                                | 65 |

|   |     | 5.1.4    | Security Requirements                  | 66 |

|   |     | 5.1.5    | Challenges                             | 67 |

|   | 5.2 | Design   | n Rationale                            | 67 |

|   | 5.3 | Design   | Overview                               | 69 |

|   |     | 5.3.1    | Protection Mechanism                   | 69 |

|   |     | 5.3.2    | Access Control Over Critical Regions   | 71 |

|   |     | 5.3.3    | Cryptographic Components               | 72 |

|   |     | 5.3.4    | PCB Execution Escorting                | 72 |

|   | 5.4 | Privile  | ged Code Block                         | 73 |

|   |     | 5.4.1    | Identifying PCB                        | 74 |

|   |     | 5.4.2    | PCB Format                             | 74 |

|   | 5.5 | Design   | n Details                              | 75 |

|   |     | 5.5.1    | Driver Context Initialization          | 75 |

|   |     | 5.5.2    | Checkpoint Deployment                  | 77 |

|   |     | 5.5.3    | PCB Execution Escorting                | 80 |

|   |     | 5.5.4    | Data Region Access Control             | 82 |

|   |     | 5.5.5    | Device Control Protection              | 83 |

|   |     | 5.5.6    | Device Configuration Space Restriction | 84 |

|   |     | 557      | User-Space Device Driver Support       | 85 |

|   | 5.6  | Discus   | ssions                           |

|---|------|----------|----------------------------------|

|   |      | 5.6.1    | Automatically Identifying PCB 85 |

|   |      | 5.6.2    | Full I/O Path Protection         |

|   | 5.7  | Evalua   | ation                            |

|   |      | 5.7.1    | Security Analysis                |

|   |      | 5.7.2    | Security Evaluation              |

|   |      | 5.7.3    | Usage of PCB                     |

|   |      | 5.7.4    | Performance Evaluation           |

|   | 5.8  | Summ     | ary                              |

| 6 | Dedi | icated F | Protection on User Passwords 102 |

|   | 6.1  | Overvi   | iew                              |

|   |      | 6.1.1    | Design Criteria                  |

|   |      | 6.1.2    | Design Rationale                 |

|   |      | 6.1.3    | Architecture                     |

|   | 6.2  | Design   | n Details                        |

|   |      | 6.2.1    | User-Hypervisor Interaction      |

|   |      | 6.2.2    | Keystroke Interception           |

|   |      | 6.2.3    | Handling SSL Session             |

|   |      | 6.2.4    | Security Analysis                |

|   | 6.3  | Impler   | mentation                        |

|   |      | 6.3.1    | KGuard in Hypervisor             |

|   |      | 6.3.2    | Browser Extension and Plugin     |

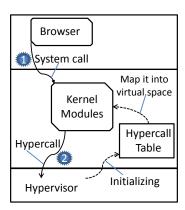

|   |      | 6.3.3    | Hypercall Support In HVM         |

|   | 6.4  | Perfor   | mance Evaluation                 |

|   |      | 6.4.1    | Overhead for Password Input      |

|   |      | 6.4.2    | Overhead for Password Submission |

|   | 6.5  | Discus   | ssions                           |

|   |      | 6.5.1    | Hypervisor Security              |

|   |      | 6.5.2   | Trusted Certificate Updates                           | 126 |

|---|------|---------|-------------------------------------------------------|-----|

|   |      | 6.5.3   | Sensitive Keyboard Input Protection                   | 126 |

|   | 6.6  | Summa   | ary                                                   | 127 |

| 7 | Fran | nework  | For Security Services                                 | 128 |

|   | 7.1  | Archite | ecture                                                | 128 |

|   |      | 7.1.1   | Security Primitive                                    | 129 |

|   |      | 7.1.2   | Event Log                                             | 130 |

|   | 7.2  | Securit | y Utilities                                           | 131 |

|   |      | 7.2.1   | Device Monitoring                                     | 131 |

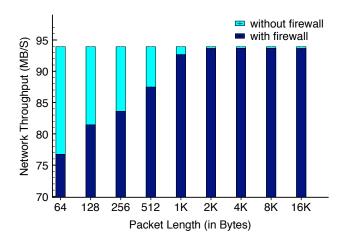

|   |      | 7.2.2   | Hyper-firewall                                        | 132 |

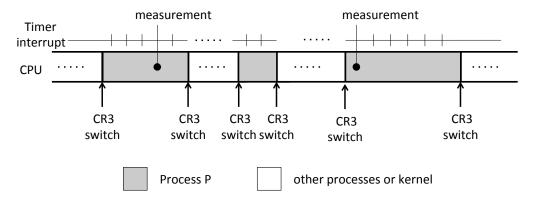

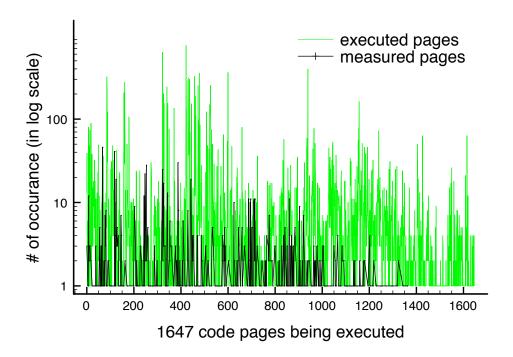

|   |      | 7.2.3   | Software Runtime Attestation                          | 136 |

|   |      | 7.2.4   | User Presence Attestation For Password Authentication | 141 |

| 8 | Cone | clusion | and Future Work                                       | 143 |

|   | 8.1  | Look in | nto the Future                                        | 144 |

# **List of Figures**

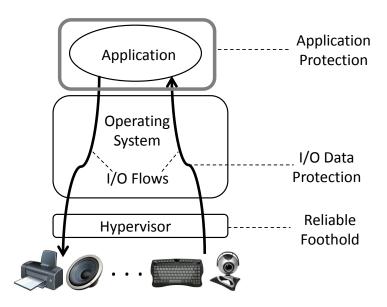

| 1.1 | Research Objectives. In this dissertation, we focus on the applica- |    |

|-----|---------------------------------------------------------------------|----|

|     | tion protection and I/O data protection based on a reliable secure  |    |

|     | foothold                                                            | 4  |

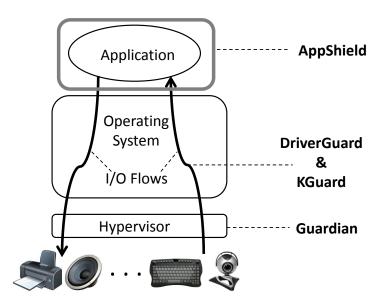

| 1.2 | AppShield protects an application through an isolated execution en- |    |

|     | vironments built upon Guardian (the reliable secure foothold). The  |    |

|     | I/O flows between the protected application and hardware I/O de-    |    |

|     | vices are protected by DriverGuard through trusted paths. For user  |    |

|     | passwords, they are specifically protected by KGuard                | 10 |

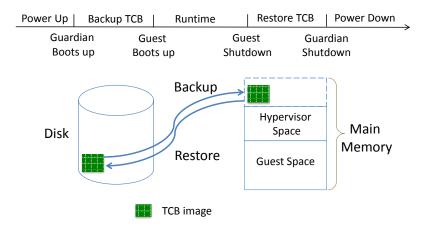

| 3.1 | Protection of the TCB (from power up to power down). The TCB        |    |

|     | consists of the Guardian image and the bootloader core. The pro-    |    |

|     | tected memory for the TCB image is reserved by Guardian and in-     |    |

|     | accessible for the guest OS                                         | 26 |

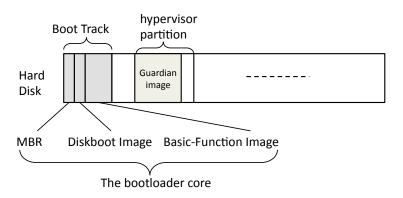

| 3.2 | An illustration of the disk layout                                  | 26 |

| 3.3 | The sequence of secure bootup                                       | 27 |

| 3.4 | ACPI sleep states                                                   | 29 |

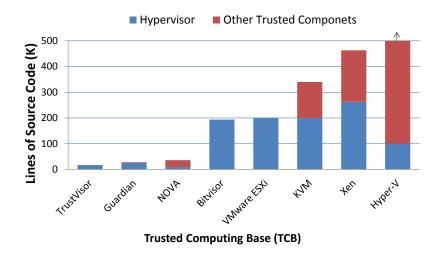

| 3.5 | TCB size. Larger TCB implies more bugs                              | 33 |

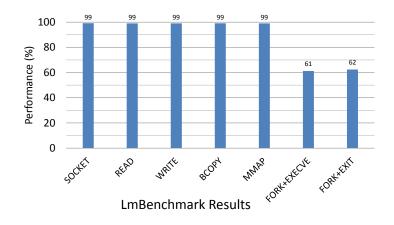

| 3.6 | The LmBench results on OS operations                                | 33 |

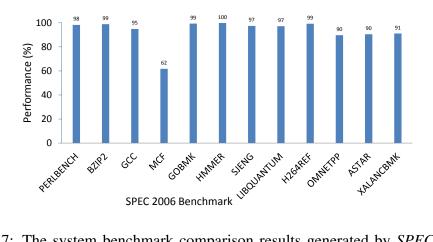

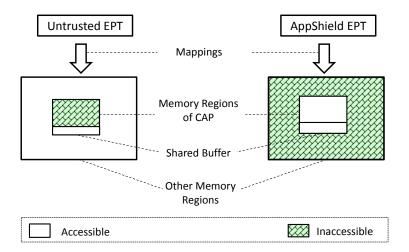

| 3.7 | The system benchmark comparison results generated by SPEC CPU       |    |

|     | 2006                                                                | 34 |

| 3.8 | The I/O-bound benchmark results                                     | 34 |

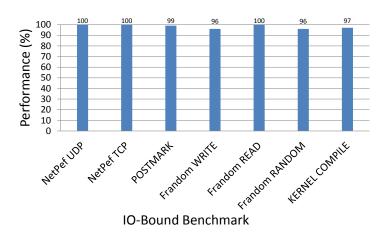

| 4.1         | The architecture of AppShield. The data flows (dotted lines) be-      |    |

|-------------|-----------------------------------------------------------------------|----|

|             | tween the protected Critical APplication (CAP) always go through      |    |

|             | the shared buffer and mediated by the shim code. The control flows    |    |

|             | (solid lines) between CAP and the OS are mediated by the Transit      |    |

|             | Module (TraMod). The execution of transit module are protected        |    |

|             | by the hypervisor                                                     | 39 |

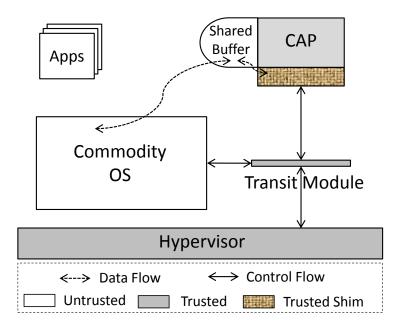

| 4.2         | Address Space Isolation. With the trusted AppShield EPT, only the     |    |

|             | memory regions of CAP and the shared buffer are accessible, while     |    |

|             | with the original EPT, the memory regions except the shared buffer    |    |

|             | are inaccessible.                                                     | 41 |

| 4.3         | Threats for address space isolation                                   | 42 |

| 4.4         | Control flow between the CAP and the guest kernel                     | 47 |

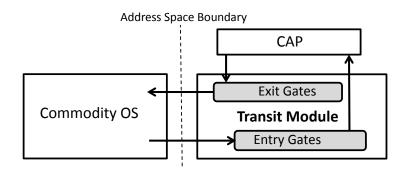

| 4.5         | The format of transit module                                          | 48 |

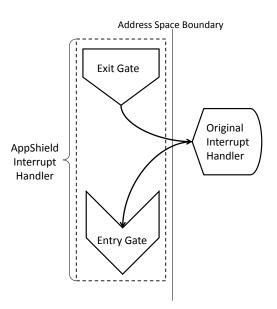

| 4.6         | The AppShield interrupt handler                                       | 48 |

| 4.7         | Performance Overhead Localization. When the context switches to       |    |

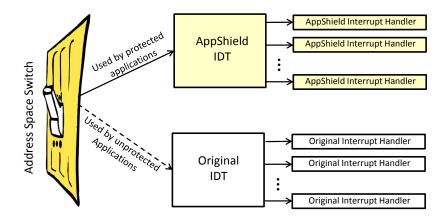

|             | CAP, the normal IDT is uninstalled and the secure IDT is installed    | 49 |

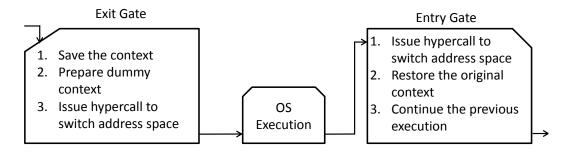

| 4.8         | A typical address space switch always starts with an exit gate and    |    |

|             | ends with an entry gate. The commodity OS handles the events that     |    |

|             | trigger the address space switch                                      | 51 |

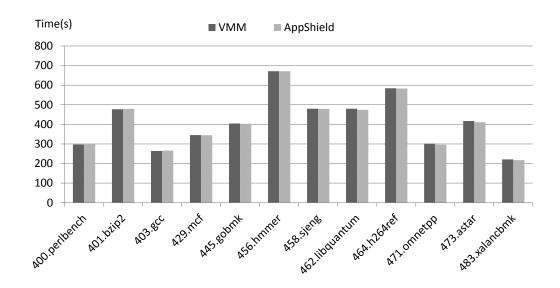

| 4.9         | SPECint 2006 Result. AppShield introduces insignificant slow-         |    |

|             | down comparing with virtualization                                    | 58 |

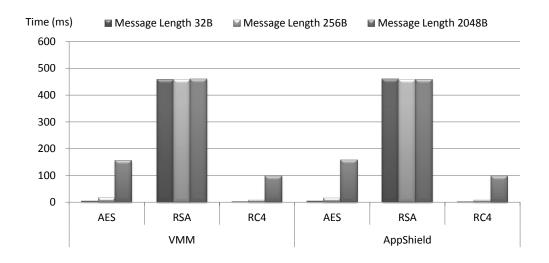

| 4.10        | The effects of AppShield protection on computation                    | 58 |

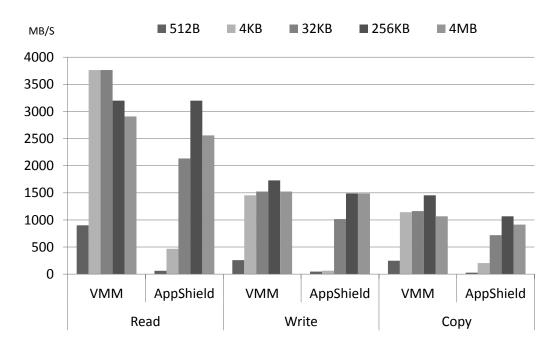

| 4.11        | The disk I/O Benchmark.                                               | 59 |

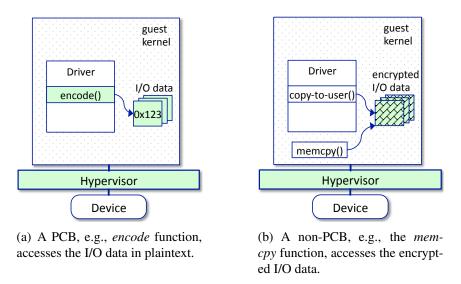

| 5.1         | The concept of privileged code block (PCB)                            | 70 |

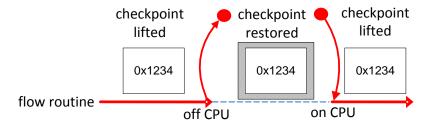

| 5.2         | An illustration of runtime protection, where $0x1234$ is an exemplary | 70 |

| J. <u>L</u> |                                                                       | 72 |

|             | memory address with a PTE checkpoint                                  | 12 |

| 5.3 | The two types of PCB format. (a) A PCB ending with encryption.          |

|-----|-------------------------------------------------------------------------|

|     | Thus, the hypervisor does not need to enforce access control on the     |

|     | data; (b) A PCB ending with protection requirement. Therefore, the      |

|     | hypervisor must enforce access control on the data to restrict the      |

|     | access                                                                  |

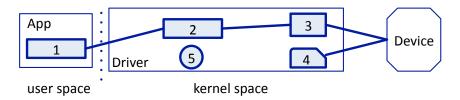

| 5.4 | An illustration of five types of regions with same numbering in the     |

|     | description                                                             |

| 5.5 | Algorithm for PCB admission                                             |

| 5.6 | Interrupt handler for escorting. When there is an interrupt interrupt-  |

|     | ing the execution of the execution of a PCB, the interrupt handler      |

|     | restores the protection on the escorted data, and saves the context of  |

|     | current escorting PCB                                                   |

| 5.7 | Exception handler for escorting. When a previous interrupted PCB        |

|     | resumes, the exception handler restores the PCB execution context 82    |

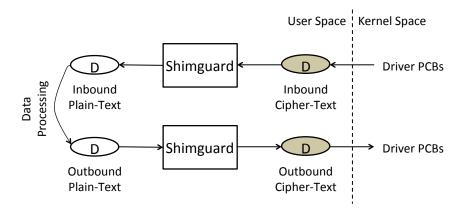

| 5.8 | The shimguard helps Overshadow and DriverGuard to protect the           |

|     | whole life cycle of the I/O data. Note that the I/O data denoted as     |

|     | D in the shaded regions are encrypted either by driver PCBs or by       |

|     | shimguard                                                               |

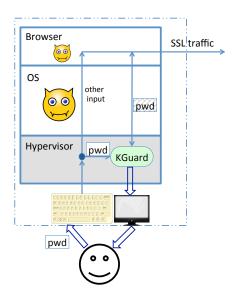

| 6.1 | The Architecture of The Password Protection System                      |

| 6.2 | The hypercall mechanism in a HVM domain                                 |

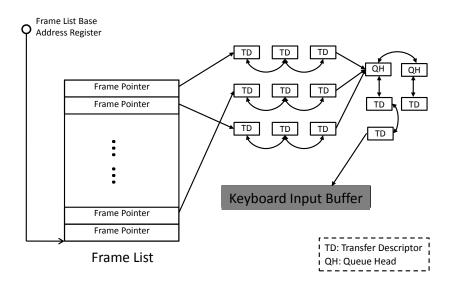

| 6.3 | Data structures used by the USB-keyboard. The (grey) input buffer       |

|     | indicates that it is set inaccessible. Other (white) parts of the whole |

|     | data structure are set read-only                                        |

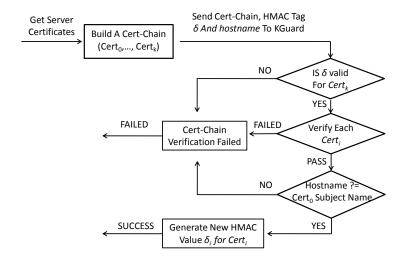

| 6.4 | The certificate chain verification                                      |

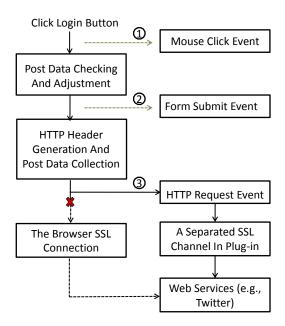

| 6.5 | Three events generated during authentication. The third one is in-      |

|     | tercepted by the extension                                              |

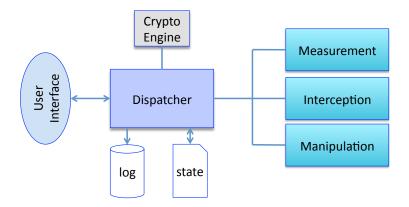

| 7.1 | The architecture of Guardian                                            |

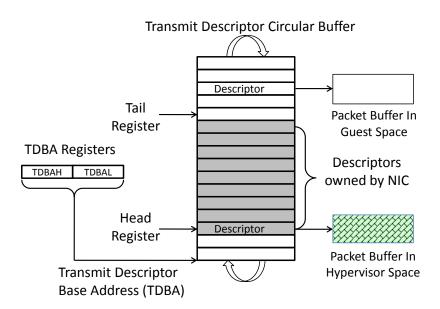

| 72  | The transmit descriptor circular queue used by the NIC 133              |

| 7.3 | The benchmark results with and without hyper-firewall 135            |

|-----|----------------------------------------------------------------------|

| 7.4 | An illustration of probabilistic measurement in software runtime at- |

|     | testation                                                            |

| 7.5 | The benchmark results with and without hyper-firewall 140            |

# **List of Tables**

| 4.1 | The time cost of the parameter marshalling in a system call. Our     |     |

|-----|----------------------------------------------------------------------|-----|

|     | scheme is relatively efficient because we give up the costly crypto- |     |

|     | graphic operations and reduce the switch times                       | 53  |

| 4.2 | The configurations of the experiment machine                         | 55  |

| 4.3 | Supported system calls                                               | 56  |

| 4.4 | The micro-benchmark results for address space switch                 | 57  |

| 4.5 | The benchmark results of Apache                                      | 60  |

| 5.1 | The number of PCBs and the average size for each driver used in      |     |

|     | our experiments. The drivers labeled with stars are those within the |     |

|     | kernel's I/O subsystem. The PCB size includes the hypercalls and     |     |

|     | the calls to the encryption and decryption functions                 | 96  |

| 5.2 | Cost of DriverGuard components                                       | 97  |

| 5.3 | Time cost induced on the guest domain data access                    | 97  |

| 5.4 | overhead of a protected keyboard I/O                                 | 98  |

| 5.5 | The performance of a USB camera                                      | 99  |

| 5.6 | The turnaround time of fingerprint collection                        | 99  |

| 5.7 | The turnaround time of file printing                                 | 100 |

| 5.8 | overhead of the protected sound-card opening                         | 100 |

| 5.9 | Graphic card performance evaluation with x11pref                     | 101 |

| 6.1 | The performance overhead for password input protection in KGuard.    | 124 |

| 6.2 | The performance overhead of each component for password sub-        |     |

|-----|---------------------------------------------------------------------|-----|

|     | mission                                                             | 124 |

| 6.3 | The overall performance measurement in the login procedure          | 125 |

| 7.1 | The runtime cost of each operation in the software runtime attesta- |     |

|     | tion service                                                        | 140 |

# **Acknowledgments**

I am grateful to my advisors, Robert H. Deng and Xuhua Ding, for guiding me in my research, helping me to develop strong research stills, and encouraging me to become a better person overall. I am also very grateful to the other members of my thesis committee, Debin Gao and Yongdong Wu, for their advice and guidance throughout the dissertation process. Their invaluable comments, guidance and encouragement dramatically helped me clarify my thesis, refine my approach and broaden my vision of security research. Seeing their work and accomplishments inspired me to become a more rigorous researcher. I greatly appreciate the guidance and assistance of my mentors Virgil Gligor and Adrian Perrig at Carnegie Mellon University. I would also like to thank all my co-authors and collaborators: Zongwei Zhou and Miao Yu, Qijia Wang, Zhi Zhang, Li Deng, for their indispensable collaboration help.

Finally, I dedicate this dissertation to my wife, Caiyu Lu, for her continuous love and support, and my son, Haoran Cheng, for the ultimate joy and happiness he brings to me.

# Chapter 1

# Introduction

#### 1.1 Problem Overview

Commodity operating systems are ubiquitous in home, commercial, government, and military settings. The OSes are supposed to be the secure footholds of systems since they manage the entire resources, so compromising an OS compromises every program and all security services upon it. In fact, unfortunately, the OSes are routinely compromised due to the large code base, the broad attack surface and the buggy loaded modules (drivers). Specifically, modern OSes usually have large code base. According to the statistics from kernel developers [103], the Linux kernel version 3.5 contains 39096 files with 15.6M SLOC, and its next version (i.e., version 3.6) adds 637 files with around 300,000 SLOC in less than 3 months (i.e., 71 days). For such large code base, it is impossible for current formal verification techniques to formally remove all bugs [39]. The broad attack surface is also a threat for OS security. The statistical results show that the Linux kernel version 3.6 has up to 337 system calls besides many implicit interfaces (e.g., /proc and /sysvirtual file systems) for applications to communicate with the OS. The dynamically loaded modules and drivers are usually buggy (not fully tested) and they inevitably increase the complexity of the OS and the number of attack interfaces. All these factors cause the OS is not a good candidate of secure foothold of a system.

Once a part of the monolithic commodity OS is compromised, the whole OS is compromised and consequently all applications are compromised. Applications are used in our daily life to process sensitive information, from sensitive I/O data, such as individual passwords, biometric finger prints and camera streams, to private application data, such as online banking information, medical reports and email content. When the OS (secure foothold) is compromised, all data within application address space are freely accessed by the adversary, and all security protections that are built upon the OS to intentionally protect the application data are consequently broken. Thus, a new application protection scheme that should be able to protect the whole applications address space against the potentially compromised OS is desired.

Another main threat from the compromised OS is the secrecy of the I/O data, which are transmitted between the hardware input/output devices and user applications via the compromised OS. The I/O data usually contains sensitive information, such as the data rendered from applications, e.g., sound data and printer data, or generated for applications, e.g., keyboard passwords and fingerprints. In such I/O data, all network traffics and disk files could be well protected through encryption, such as the SSL technique can protect network I/O data. However, for the raw I/O data, such as keyboard inputs, camera streams and fingerprints cannot be protected through encryption techniques, because they are structured data. The encryption may break constrains or change the meaning of certain fields, and consequently cause unpredictable errors. For example, a camera stream consists of header and data sections that are encoded by the camera device. If we simply encrypt the whole stream, the header information will be lost or wrongly translated, which will lead to video errors and even crash the camera driver or the corresponding user application. In addition, the commodity hardware devices are not encryption-capable. Thus, the generated data or the received data should be in plain text, such as the keyboard scan code and the document content receiving by the printer. Once kernel rootkits know the locations of the buffers caching the plain text, they can reveal and tamper with the data by directly accessing them.

To address the above problems, we need to answer a series of critical research questions: which component/layer of the system could be the secure foothold? What security mechanisms can be applied to it to make it reliable while still compatible with existing OS and applications? How to protect the whole application against untrusted OS while still keeping it usable, e.g., allowing it to exchange data with outside and use the memory as a fashion in the normal setting? How to efficiently protect the secrecy of the I/O data transmitting between hardware input/output devices and applications via the potentially compromised OS? Is the encryption-capable device necessary? Can we do it better if we only focus on the protection on one specific I/O data? Furthermore, Based on the secure foothold, what secure primitives it can provide, and what security services can be built, besides the application protection and the I/O data protection?

## 1.2 Research Objectives

In this dissertation, we aim to answer the above questions. Moreover, we aim to design and implement several secure virtualization systems to demonstrate and evaluate our solutions on today's hardware and software architecture.

#### 1.2.1 Reliable Secure Foothold

The hypervisor is a promising secure foothold candidate. As a small piece of software between the OS and the hardware, the hypervisor has the unique advantages, in terms of the balance between security and versatility. However, to be a reliable secure foothold, the hypervisor should meet two critical requirements. Firstly, it should be secure against attacks from rootkits which can subvert the operating system. Secondly, it should be always *available* throughout the life cycle even when the OS is corrupted. By virtue of the virtualization, a hypervisor is widely deemed as software which can resist attacks from an untrusted guest OS. However, *no* hypervisor can simultaneously satisfy all the above requirements, especially for the

Figure 1.1: Research Objectives. In this dissertation, we focus on the application protection and I/O data protection based on a reliable secure foothold.

availability requirement. It is challenging to achieve the reliability property, because 1) the kernel rootkits can directly modify or even delete the TCB (including the hypervisor) images from the disk to make them unavailable. If the hypervisor chooses to do runtime checking through intercepting disk I/O, it will lead to numerous context switches, reducing the performance of the disk I/O as well as the CPU utilization; and 2) the rebooting and shutdown mechanism of commodity systems are complex. The hypervisor should efficiently and completely handle all of them to ensure the availability before the system really rebooting/shutdown.

In this dissertation, we aim to build a reliable and lightweight secure foothold with integrity and availability guarantees. Moreover, we aim to extend our secure foothold to be a framework, which consists of common security primitives that are potentially needed by our proposed systems and many other security systems. In this way, people can quickly adopt it to support new security services with no or minimum customizations.

### 1.2.2 Application Protection

The application protection is challenging due to the complex memory management and the intensive data exchange between the protected applications with

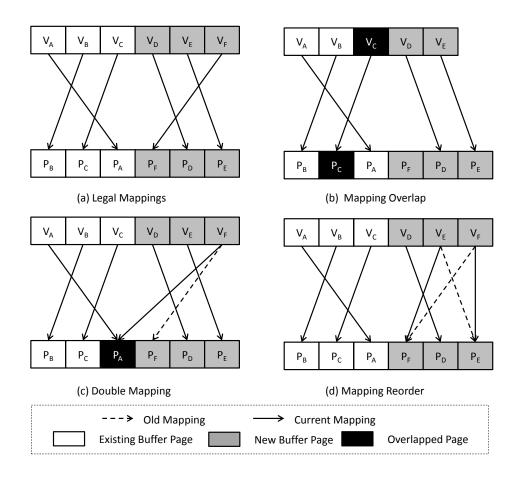

outside (e.g., the OS). The approaches like Flicker [57], TrustVisor [56] and Fides [89] simplify the problem setting by assuming that the protected code is self-contained with pre-defined inputs and outputs (e.g., inputs are the initial parameters and outputs are the final returns); and that the protected execution does not involve dynamic memory allocation or deallocation. Some other systems [57, 56, 89, 13, 17, 106, 92, 16, 90] aim to protect the whole application in the real settings. However, they have various drawbacks, such as high performance overhead, large Trusted Computing Base (TCB), hardware modifications, or with a restriction imposed on the protected code. Moreover, several newly identified threats in Chapter 4 are evidence that protecting applications from malicious OS is more challenging than previously realized. For example, the malicious OS may swap two address translation mappings to break the data integrity without directly accessing the data pages (i.e., mapping reorder attack). It may also illicitly return an allocated memory region with its virtual addresses occupied by the application stack (i.e., Iago attack [15]). By doing so, the application may happen to modify the control data (e.g., return address) in the stack, and thereby compromise the execution of the victim application.

Thus, in this dissertation, we aim to propose a system to protect an application with small TCB and low performance loss, as well as no modifications on system hardware. Moreover, the new scheme should be able to defend against newly identified attacks.

#### 1.2.3 I/O Data Protection

Application protection can only protect the data within application address space. For the I/O data out of the protected application (transmitting in the kernel space) are not protected. Thus, a I/O data protected scheme is desired. In fact, protecting I/O data is to build trusted paths, which are secure channels that assure the secrecy and/or authenticity of data transfers between a hardware devices and an isolated execution environment. Without a trusted path, an adversary could illicitly

obtain sensitive user inputs and the outputs of an application. Traditional trusted paths are built upon commodity OS, which is not a reliable secure foothold. Thus, some researchers propose new trusted path schemes to defend against untrusted OS. However, they all have several drawbacks, such as needing encryption-capable devices [59, 97], and incompatible with legacy applications [109].

Thus, in this dissertation, we aim to propose a generic, secure (against untrusted OS) and practical (without needing special hardware and compatible with legacy applications) trusted path scheme for protecting I/O flows on the commodity platforms. It is challenging since it needs to handle *all* kinds of device I/O, and has *no* extra assistance from special hardware.

#### **Password Protection**

The combination of IEE and TP could protect almost all applications and sensitive data. But for certain user data, we could do it better, even in terms of security. In this dissertation, we aim to propose a dedicated system to protect user passwords in the increasingly popular online services. To make the new system secure and practical, it should satisfy several requirements. Firstly, the new system should not need any trusted information from isolated/trusted components in the guest space. Secondly, it should not need special hardware to build trusted path. Thirdly, the new system should be compatible with existing OS and all applications, especially for legacy web browsers. Fourthly, the new system should be user-friendly, meaning the interaction interface for web authentication should keep the same. Last but not the least, the performance overhead and the latency in the whole process of the web authentication should be insignificant. In this dissertation, we aim to let the new proposed system support all these five requirements.

### 1.3 Threat Model

We assume the end-users themselves are security conscious, meaning that they are aware of the potential dangers/attacks that arise from adversaries. The securityconscious users are willing to enable some protection mechanisms and are wary of authentication of the availability of the protection, e.g., the user will verify if he/she gets a secret feedback (a secret message or a flashing signal) when the corresponding protection mechanism is enabled.

We assume that a remote adversary completely controls the guest operating systems, meaning that the remote adversary is able to launch arbitrary code or applications to access any system resources, such as I/O ports, Memory-Mapped I/O (MMIO) and main memory. Specifically, the adversary may 1) get the data stored in the device memory or I/O ports by manipulating the configuration space of the target or other devices, 2) intercept the I/O flows that goes through the kernel space via device drivers, and 3) read user sensitive data from the user space by directly accessing a particular memory region or following the links in some data structures. The purposes of the adversary are to break the system foothold (the hypervisor), and/or get the secrecy of the I/O data.

We assume that the adversary can not compromise the hardware devices whose behaviors always exactly follow their specifications. We also assume the system firmware is trusted. In fact, the modern BIOS has a built-in hardware lock mechanism [91] to set itself as read-only so that the OS cannot tamper with it. Furthermore, the modern BIOS only accepts signed updates [45, 97]. Due to the complexity of the x86 platform (e.g., optional ROM), this assumption may not always true. Nonetheless, it is still possible to validate the system firmware by the proposed attestation approach [52] or by a trusted system integrator.

The hypervisor is trusted. The load-time integrity of the hypervisor is achieved through secure boot mechanism [96], and the runtime security is guaranteed by the virtualization technology. Specifically, the hypervisor isolates its memory region by configuring Extended/Nested Page Table (EPT/NPT) and IOMMU to stop software and DMA access driven by hardware. The hypervisor is not as secure as the TPM chip since several attacks have been discovered to compromise some versions of hypervisors [94, 27, 49, 69]. However, the security of the hypervisor can be verified

by those schemes [99, 98, 5, 69].

#### 1.4 Metrics

We identify several key metrics to evaluate the security, efficiency and practicality of a protection mechanism.

- Size of Code Base (e.g., SLOC). The size of the TCB should be as small as possible. The smaller TCB will export less attack surface which may be used by adversaries to compromise the system, and its security may be proven through the rigorous formal verification mechanism [39].

- Performance Overhead. The security protection system should only introduce reasonable performance overhead for the protected target (e.g., an application) and other components in that system. The poor performance may dramatically reduce the value of the protection system.

- Compatibility. The compatibility issue should be considered during the design of a protection system. It is better to be transparent to either the legacy applications or the operating systems if it is not simultaneously compatible with both of them.

- Practicality. The whole protection mechanism should be user-friendly for normal end-users who do not possess or lack security domain knowledge.

Furthermore, the mechanism should be able to be widely deployed without requiring special hardware (e.g., encryption-capable keyboard).

## 1.5 Terminology

This section establishes the terminology that is used throughout this dissertation.

Secure Foothold. A secure foothold is a piece of code with highest privilege

in a system. The secure foothold is trusted and always behaves as expected.

It can bolster various security systems by growing the trust chains.

- Isolated Execution Environment (IEE). The execution environment is defined by code S executing on a specific platform. The isolated execution environment protects the execution of S from any other code.

- Trusted Path (TP). A Trusted Path (TP) is a secure channel that assures the secrecy and/or authenticity of data transfers between a hardware devices and an isolated execution environment. Without a trusted path, an adversary could illicitly obtain sensitive user inputs and the outputs of an application.

- Trusted Computing Base (TCB). The trusted computing base of a computer system is the set of all hardware, firmware, and software components that are critical to its security. Once they are compromised by the adversary, the security properties will be broken.

- **Virtualization.** Virtualization is a technology that creates, manages, introspects and destroys guest domains (virtual machines). The software that implements virtualization is usually called *virtual machine monitor (VMM)* or *hypervisor*.

### 1.6 Dissertation Overview

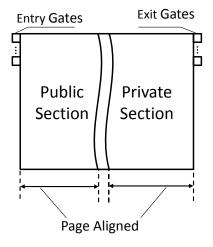

In this dissertation, we leverage virtualization technology to harden systems [19, 18, 20, 21]. Specifically, we build a lightweight and reliable hypervisor (Guardian) as a system secure foothold, which is able to boost computer security and provide reliable assistance for the end user to cope with various threats. Guardian as the system secure foothold has two prominent features. The first is a secure bootup and shutdown mechanism, which enhances the existing hardware-based secure bootup by offering integrity and availability protection of the TCB images and critical information. Another feature is a user-hypervisor interface which allows the end-user to issue commands to and receive responses from Guardian at runtime. The interface is secure in the sense that the channel between the end-user and the hypervisor is authentic and the exchanged information is not exposed to the guest.

Figure 1.2: AppShield protects an application through an isolated execution environments built upon Guardian (the reliable secure foothold). The I/O flows between the protected application and hardware I/O devices are protected by DriverGuard through trusted paths. For user passwords, they are specifically protected by K-Guard.

Based on Guardian, we propose AppShield, which protects critical applications by putting them into isolated execution environments (IEE). AppShield is able to reliably and efficiently protect data secrecy and integrity of a critical application, as well as its execution integrity, against kernel rootkit attacks. Specifically, AppShield leverages the hardware-assisted virtualization techniques [46] to isolate the application's address space such that all accesses from the untrusted OS are blocked except those explicitly authorized by the application through system calls. The protected application is allowed to utilize the main memory in the same fashion as in a normal (unprotected) setting, and to access the memory with native speed, i.e. without encryption/decryption or being intercepted. AppShield localizes the performance overhead to the protected application and keeps the performances of those unprotected applications unaffected.

The inputs and outputs of protected application are not protected by AppShield so that they could be tampered by the untrusted OS. To fix this gap, we propose DriverGuard to support trusted paths between the protected application and hardware input/output devices. DriverGuard is a holistic and compact I/O protection

system making use of a combination of cryptographic and virtualization techniques. In particular, the trusted path built by DriverGuard focuses on those devices that render raw data, e.g., sound cards and printers, or generate raw data for applications, e.g., seismic sensors and fingerprint scanners. Disk and network I/O are less concerned, because such data could be simply protected through encryption.

The combination of IEE and TP could protect almost all applications and sensitive data. But for certain user data, we could do it better, even in terms of security. In this dissertation, we purpose a dedicated system *KGuard* to protect user passwords in the increasingly popular online services without needing any IEE and trusted path. In particular, KGuard does not trust any software component in the guest kernel and user space (without IEE requirement), and also not leverage any special hardware to assist the protection. Note that KGuard is able to protect user passwords against all kernel- and application-level key-loggers as well as all kinds of network eavesdroppers.

Based on the above proposed systems, and many other existing virtualization-based security systems, we summarize the common security primitives into our secure foothold (Guardian), upgrading it to be a framework/template of secure foothold so that it could be easily customized by end users according to their demands to harden their systems. To demonstrate the value of the framework, we create four security utilities, i.e., hypervisor-based firewall, device monitoring, software runtime attestation and user present attestation for password authentication. The experiment results show that we only need adding a few lines of code to achieve all these security services, and the performance overheads are insignificant.

### 1.6.1 Dissertation Organization

The remainder of this dissertation includes the following chapters. Chapter 2 summarizes the related work, and Chapter 3 presents Guardian as a lightweight and reliable system foothold. Based on Guardian, Chapter 4 describes AppShield that creates isolated execution environments to protect critical applications. Chapter 5

presents a trusted path scheme that is a generic solution to protect all kinds of I/O data, and Chapter 6 presents KGuard to protect user passwords in the web authentication services. Chapter 7 summarizes a framework of secure foothold that could be directly used or customized by end users to harden their systems. Finally, Chapter 8 concludes the dissertation and discusses a few directions for the future work.

# Chapter 2

# **Related Work**

We first describe isolated execution environment (IEE) approaches, and then we present the trusted path schemes which aims to protect I/O data. The IEE scheme are complementary with trusted path mechanism to protect the whole lifecycle of application and I/O data. Finally we describe the hypervisor security and the root of trust to illustrate the reasonability of choosing the hypervisor as system secure foothold.

## 2.1 Application Protection

There are several approaches proposed to protect application through creating isolated execution environments, and all of them attempted to remove the OS out of TCB.

#### 2.1.1 Self-contained Code Protection

Flicker [57] system built on the TPM-based Dynamic Root Of Trust (DROT) technology can build an isolation environment to protect a piece of code and data. Due to the limitation of the TPM, the latency of the Flicker system is significantly high. To minimize the latency, TrustVisor [56] scheme are proposed. By leveraging virtualization technology, TrustVisor virtualizes the physical TPM into Virtual TPM (VTPMs) and migrate them into hypervisor space. Note that both of them simplify

the problem setting by assuming that the protected code is self-contained with predefined inputs and outputs (e.g., inputs are the initial parameters and outputs are the final returns); and that the protected execution does not involve dynamic memory allocation or deallocation. Protecting complex environment such as the whole application or device drivers may lead both schemes to failure.

#### 2.1.2 Whole Application Protection

**Secure-Processor-Based Protection.** AEGIS [90] and XOM OS [53] are secure-processor based approaches that provide compartments to isolate one application from others. Both of them incur poor computability since they require substantial modifications on the OSes and applications. AEGIS [90] also provide an alternative implementation, which requires to build security into the OS.

Bastion [12] and SecureME [22] aim to deal with untrusted OS and untrusted hardware attacks simultaneously with the assistance of a secure processor. Bastion focuses on the protection of a security module, while SecureME attempts to provide privacy and integrity for data and code of the application. SecureME requires modifications on both OSes and applications.

In addition, a Processor-Measured Application Protection Service P-MAPS [72] is announced by Intel, which is built upon Intel TXT [24] and Intel VT [46] hardware capabilities. P-MAPS provides runtime isolation to protect standard applications with small TCB. P-MAPS is quite similar to our scheme at a high level. However, the details of P-MAPS are unavailable for public to conduct an in-depth comparison.

Microkernel-Based Protection. EROS[81], Perseus[68], Microsoft's NGSCB [29] and Nizza [37] are microkernel(or small kernel) based solutions. They attempt to run commodity OS and untrusted applications in the low-assurance partitions, and run the applications with higher security requirements in the high-assurance partitions, which are isolated and protected by the microkernel itself. However, all of them incur compatibility issue since they may require splitting or

even redesigning on the applications.

**Virtualization-Based Protection.** The approaches like TERRA [34] and Proxos [92] are hypervisor-based trust partitioning systems. They protect applications by isolating them into trusted domains with application-specific OSes. These systems incurs large TCB since they include all secure domains inside. In addition, they are still vulnerable once the application-specific OSes are compromised.

OverShadow [17], CHAOS [16] and SP<sup>3</sup> [106] aim to protect the whole application execution against malicious application and OSes. However, all of them need complex encryption and decryption operations on the application data. Obviously, these additional costly cryptographic operations may reduce the performance and increase the latency of the whole system, especially for the protected application. In addition, none of them claims that they protect applications from the MS attack. Thus, the data and code integrity may still be broken by potentially compromised OS. InkTag [41] is a new proposed approach, which also protects the whole application and verifies the OS behaviors through paraverfication technique. The paraverfication technique needs to modify the source code of the kernel, which is not always available. Thus, it may lead to the failure of the protection on the close-source OSes, e.g., Windows. In addition, it is unclear if InkTag can defend against the new attacks identified in our dissertation 4.

BIOS-Based Protection. Lockdown [97] system relies on a BIOS-assisted lightweight hypervisor and an ACPI-based mechanism to provide two switchable worlds - green world for trusted applications and red world for untrusted applications. Lockdown uses a trusted path built upon LEDs to provide a verifiable protection. The main drawback of the Lockdown system is the switch latency is too high. The switch requires 31 seconds on Windows and 13 – 28 seconds on Linux. SecureSwitch [91] system that is quite similar to Lockdown also leverages a BIOS-assisted mechanism for secure instantiation and management of trusted execution environments. The switch latency is relatively smaller. The switch requires 6 sec-

onds by using the ACPI standard. Both approaches needs to shut down one world to run another one, meaning they can not simultaneously execute two worlds.

#### 2.2 I/O Data Protection

We attempt to categorize these relevant trusted path schemes according to the differences of their secure foothold.

#### 2.2.1 Virtualization-based Protection

The trusted path [109] proposed by Zhou et al. aims to assure the secrecy and authenticity of I/O data transferred between a periphery device and an application. To build an exclusive trusted path between the device and the expected application, the hypervisor fixes the device configuration space which is achieved using Virtual Machine Control Structure/Block, Nested/Extended Page tables and IOMMU to prevent unauthorized software and DMA access, and interrupt delivery path which is achieved using Interrupt Remapping features and LAPIC x2APIC mode to make sure that the interrupt is delivered to expected handler. The expected applications are extended to support user-level drivers, which directly issue command to devices through the built trusted path. Obviously, it suffers compatibility issues since applications are numerous and any new application will need to be modified to satisfy the trusted path requirements. In comparison, DriverGuard requires modifications on driver code only. Moreover, DriverGuard does not need to defend against interrupt spoofing attack since it focuses on the secrecy of the I/O data between devices and applications, and only authorized PCB is able to access the decrypted I/O data. Even if the unauthorized codes are involved by unintended interrupt, they still can not access the protected I/O data.

The virtualization-based trusted path schemes are closely related to our work. BitVisor [84] is a dedicated hypervisor to I/O management. It uses a parapass-through mechanism whereby access operations on the monitored devices are intercepted and the operations on the other devices pass through without any checking.

The interception allows the hypervisor to protect itself and to perform security functions on the device I/O. However this approach does not protect the I/O data in the kernel space. BitVisor does not claim that they protect the MMIO mapping attacks.

Hypervisors with privileged root domains (e.g., the *Dom0* in Xen) are able to assign different device drivers to separate virtual machines (e.g., *driver domains* in Xen) and securely associate them with application virtual machines (e.g., *guest domains* in Xen) [23, 8, 6, 75, 104]. These hypervisors isolate the device resources (i.e., I/O ports and the memory address-space, including MMIO regions) belonging to a device driver domain from other domains. Note that all these schemes do not consider the MMIO mapping attacks. Moreover, their TCBs enclose the whole operating system, which dramatically increases their trusted code bases.

#### 2.2.2 Hardware-based Protection

The Zone Trusted Information Channel (ZTIC) [50] is a dedicated hardware, which provides a trusted path for users to confirm online transactions. The ZTIC-based trusted path completely bypasses the legacy channel in the users' computers. Bumpy [59] system proposes to protect user keyboard inputs by building a trust environment. It requires an encryption-capable keyboard and therefore is not applicable to generic devices.

The special-device-based schemes usually combine with cryptographic technology to protect the secrets in user and kernel space, such as Bumpy, which usually requires many mediations on the system. Such medications not only consiquently affect the compatibility of the scheme, but also often significantly reduce the usability, and even make the scheme impractical sometimes.

The UTP system [30] proposes an isolated kernel module to temporally manage user-centric I/O devices (e.g., keyboard and display) and enables a remote server to verify that a transaction summary is confirmed by a local keyboard input. BIND [83] binds data and code and uses cryptographic techniques to guarantee the integrity of data. However BIND is limited to derived data and can not help on the

confidentiality of the I/O data. Both of them require a hardware supported secure execution environment (e.g., secure kernel based on the AMD's Secure Execution Mode chip), which often occurs high latency and significant performance overhead.

#### 2.2.3 OS-based Protection

Langweg et al. [51] propose a COTS-based scheme to solve the confidentiality, integrity and authenticity of input and output data<sup>1</sup>. Authors focus on the windows platform, where the Windows message mechanism is able to be exploited by a malicious program to access the input and output messages (data) which are originally intended for other applications. By leveraging the advantages of the the DirextX, authors build a secure user interface to directly fetch input data and access the display hardware in exclusive mode. Trusted paths for browsers [107] focus on providing a trusted GUI to user, protecting user inputs to the intended browser. These two schemes only address security issues at the driver-applications interface, whereas the battlefield of DriverGuard is the entire I/O path. BitE [58] is an approach for preventing user-space malicious applications from accessing sensitive user input via a dedicated trusted path between input devices and the target application, and providing visual verification feedback to the user to prove that the input is really caught by the expected application.

All of them suffer from a large TCB since they are built atop large operating systems, and some of them even contains the Window Manager [58].

## 2.3 Hypervisor Security

Comparing with legacy monolithic Operating Systems, the hypervisor is more secure since its size is relatively smaller and the exported attack surfaces for guest domains are considerably less. Although there have been several attacks discovered to compromise some versions of hypervisors [94, 27, 49, 69], the security of the hypervisor can be enhanced through some existing mechanisms. The TPM-based

<sup>&</sup>lt;sup>1</sup>The confidentiality of the input data is not done.

authenticated boot can verify the integrity of the hypervisor when being launched, and the hardware-assisted virtualization technology, i.e., Intel VT-x and AMD V, is able to significantly reduce the code size of the hypervisor, thereby the attack surface is reduced. Furthermore, there are some sophisticated framework systems [99, 98, 5, 69] proposed to enhance the security of the hypervisor. HyperGuard [69], HyperCheck [98] and HyperSentry [5] are three System Management Mode (SMM)-based frameworks to measure and verify the integrity of hypervisors. The code for the SMM mode are protected by hardware chipset. HyperSafe [99] is a lightweight approach that protects existing bare-metal hypervisors with a unique self-protection capability to provide lifetime control flow integrity. In order to e-liminate the programming bugs in the hypervisor, the rigorous formal verification mechanism [39] is able to be used to prove the correctness of the hypervisor.

Many hypervisor-based security systems have been designed and reported in the literature. For instance, a hypervisor can be applied for I/O related protection [84, 19], for kernel integrity protection [78, 71, 100, 65, 4, 60, 105], and for user space protection [34, 17, 106, 56]. By studying these systems, we identify interception and manipulation as the hypervisor's major security primitives which are adopted in Guardian as well. Our work has remarkable differences with the aforementioned systems. Guardian caters to the enduser's security needs, instead of the security of platform components such as the kernel or a user process. This demands Guardian to be highly efficient, user friendly and compatible with the operating system and applications, such that it is suitable for practical use. Most existing systems just briefly mention the TPM based secure boot for loading the hypervisor. In contrast, we devise a novel method to establish the hypervisor as the root of trust and show how to build a variety of security services on top of it.

# 2.4 Root of Trust

#### 2.4.1 Software-based Root of Trust

Software-based ROTs have been proposed and used in [77, 3, 79]. The trust establishment is based on a challenge-response protocol. A speed-optimized function (code block) is established as the ROT on a platform if, within an acceptable time delay, it can compute a correct checksum of memory regions according to a given challenge. It is based on the assumption that it incurs a noticeably longer delay for any other implementation of this function. It also has a restriction on both the adversary's capability, for instance no collusion with a third party, as mentioned in [28]) and the capabilities of the target platforms. In addition, to stop the proxy attack, it may even require to unplug the network and disable the wireless to physically cut down the connection with outside. These limitations and requirements lead to inconvenience or even to impracticability. Thus, software ROTs are unqualified to be a security foothold for normal users' computers.

### 2.4.2 Hardware-based Root of Trust

The hardware-based ROT can be categorized into static ROTs and dynamic ROTs. A static ROT is a built-in platform component. When the platform boots up, a trust chain can be established from the ROT up to the operating system. The TPM chip [96] is a typical example of static hardware ROT. As a chip on the mother-board, it is secure against all software attacks. Secure (or authenticated) boot up, remote attestation and sealed storage are the main security services provided by the TPM framework. The main disadvantages of TPM are its low speed, inflexibility and passiveness. Therefore, to support various security services, it usually requires assistance from certain secure software routine (e.g., hypervisor). IBM's secure co-processor [2] is a strong hardware root of trust with such a high price tag that it is not feasible for the mass market. SMART [28] is a hardware-software co-designed scheme, where a piece of code works on a modified *low-end* microcontroller u-

nits (MCU) to function as a dynamic ROT. The SwitchBlade architecture [11] can prevent persistent rootkits from infecting security-critical files (e.g., kernel image) with an ROT residing on the disk controller. These ROTs may be integrated with Guardian though carefully design and implementation.

AMD Secure Virtual Machine (SVM) [1] and Intel Trusted Execution Technology (TXT) [24] are dynamic ROTs. These new processor features allow a piece of code to be securely executed in an isolated environment enforced by the hardware. Despite of their easiness of use, they incur high latency as showed in the Flicker system [57]. Fortunately, the high latency may be tolerable for the end-users, since it only required once when the system as well as Guardian boots up. The boot mechanism of Guardian is compatible with dynamic ROT techniques.

# **Chapter 3**

# **Reliable Secure Foothold**

In this chapter, we harness the fast-growing hardware-assisted virtualization techniques to build a tiny but reliable hypervisor as the security foothold for personal computers. The hypervisor we propose is named as Guardian. Guardian has two prominent new features which are the enabling techniques for the hypervisor to become a security foothold. The first is a new secure bootup and shutdown mechanism, which enhances the existing hardware-based security boot up by offering integrity and availability protection of the TCB image and critical information. The other feature is a secure user-hypervisor interface which allows the end-user to issue commands to and receive responses from Guardian at runtime. The interface is secure in the sense that the channel between the human end-user and the hypervisor is authentic and the exchanged information is not exposed to the guest. We also propose two practical security utilities based on Guardian. The first is a device monitor utility, whereby the user can instruct Guardian to monitor the state of peripheral devices, e.g., a camera. The second is a hyper-firewall whereby Guardian inspects inbound/outbound network traffic and drops illegal packets. We have implemented Guardian on a desktop with a Linux guest. Guardian consists of around 25K SLOC, and the utilities consist of around 2.1K SLOC. Our experiments show that Guardian inflicts an insignificant workload to the whole system.

The growing hardware support for virtualization will continue to empower the

hypervisor with more effective and stronger security control over commodity platforms with smaller code size and better performance. We envisage that using a hypervisor as a generic security foothold is a promising direction to greatly boost up the security for commodity platforms. Our work presented in this chapter is an important step towards this ultimate goal. We summarize our contributions as follows:

- We design and implement Guardian which is the first system to provide both integrity and availability guarantees. Note that all existing hypervisors do not achieve the availability guarantee.

- 2. We design and build a device monitor and a hyper-firewall as two security utilities on top of Guardian.

In the next section, we present our research objectives and threat model. Then we present the design of Guardian in Section 3.2. In Section 3.3, we describe the implementation and the evaluation. Finally, we conclude the chapter in Section 3.4.

# 3.1 Problem Definition

We aim to provide a tiny and reliable hypervisor as a security foothold for personal computers. Namely, we undertake to furnish the end-user with a reliable security basis when the conventional one (typically the operating system) fails. Though the security foothold, the human user can configure security policies and manage resources in the platform. It not only boosts up the system security, but also facilitates the end-user to determine the trustworthiness of her system. Note that we do *not* attempt to detect and remove malicious software from the platform, nor is to protect the operating system or a user application.

### 3.1.1 Threat Model

Since our goal is to assist the end-user, we assume that they are security-conscious users, who are happy and intended to use our system to protect their systems. We do

not consider any human adversary who may have physical access to the system. For instance, the adversary can issue malicious DMA accesses by inserting extra physical devices (e.g., a firewire device). A malicious human user can always remove the hypervisor from the platform.

The adversary in our threat model is malware residing in the operating system which can subvert the operating system and launch arbitrary attacks. However, we assume that they can not compromise the hypervisor. Note that the hypervisor makes use of hardware-assisted virtualization techniques to defend against malicious software accesses and illicit DMA accesses. This assumption can be more reasonably held if the hypervisor has a tiny code size and simple logic so that only a small attack interface is exposed to the adversary. Existing techniques [99, 98, 5, 69] can also be applied to enhance hypervisor security.

We assume that the adversary can not compromise the hardware devices whose behavior always exactly follow their specifications. We also assume the system firmware is trusted. In fact, the modern BIOS has a built-in hardware lock mechanism [45, 91] to set itself as read-only so that the OS cannot tamper with it. Furthermore, the modern BIOS only accepts signed updates [93, 97]. Due to the complexity of the x86 platform (e.g., optional ROM), this assumption may not always true. Nonetheless, it is still possible to validate the system firmware by the proposed attestation approach [52] or by a trusted system integrator.

# 3.2 Design of Guardian

In this section, we introduce the techniques for establishing Guardian as a security foothold, and describe the functionalities of the two secure user interfaces.

# 3.2.1 Establishing Guardian as a Security Foothold

To establish Guardian as a security foothold, it is necessary but not sufficient to ensure a secure boot. The secure boot alone can only validate the integrity of the system's TCB image during booting up, while a reliable security foothold needs

both integrity and availability guarantee, so that the system still boots up into a trusted state even if the TCB image on the hard drive are modified by attackers. We do not elaborate the details of secure boot (e.g., TPM-based secure boot [96]) to avoid verbosity as it has been widely used in the literature. Our focus is to explain how to ensure that the intact TCB image is always available for the boot up. The TCB of our system consists of the BIOS, the bootloader-core and the Guardian image. Recall that the BIOS is protected by the hardware and is trusted in our threat model. Therefore, we intend to protect the bootloader core and the Guardian image against runtime attacks.

A straightforward approach is for Guardian to intercept and validate every disk I/O, such that any access to the security critical image residing on the disk is blocked. Obviously, this solution is costly due to the high overhead and complexity of a disk I/O interception multiplied by the huge number of disk operations.

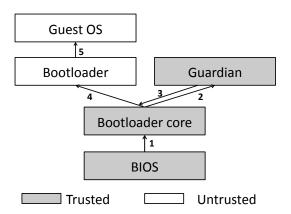

We devise a novel scheme without interposing on disk operations. The basic idea (visualized in Figure 3.1) is that once Guardian is launched, it immediately relocates its image and the bootloader core from the disk into a protected memory region *prior to* launching the guest. Then, Guardian intercepts all power off events, and writes the protected image back to the disk before cleaning up the memory. In the following, we describe the details of secure boot up and secure shutdown, which in tandem with runtime protection bolster the availability of Guardian throughout its whole life cycle.

#### **Secure Bootup**

Figure 3.2 illustrates the disk layout for Guardian, where a special partition, referred to as the *hypervisor-partition*, is created during installation to avoid being trespassed by normal file systems. To allow for a secure boot without increasing the TCB size and complexity, we make slight changes on the bootloader (e.g., Grub 2). The BIOS passes the control to the bootloader core in the boot track. The bootloader core includes the Master Boot Record (MBR), the diskboot image and the basic-

Figure 3.1: Protection of the TCB (from power up to power down). The TCB consists of the Guardian image and the bootloader core. The protected memory for the TCB image is reserved by Guardian and inaccessible for the guest OS.

function image, which provides all basic functions and usually has to load other modules and configuration files such as *grub.cfg* to launch an operating system due to the limited size of the boot track (32KB in maximum).

Figure 3.2: An illustration of the disk layout.

Our modification is on the basic-function image only, such that it always launches Guardian *before* loading other components including the OS. In specific, once the core is loaded to the CPU by the BIOS (illustrated by Step 1 in Figure 3.3), it checks a bit flag in main memory (referred to as VMM\_flag) which indicates Guardian's presence. If VMM\_flag is not set, i.e., the core immediately passes the control to Guardian whose image is placed at a *fixed* disk address upon installation (Step 2 in Figure 3.3). The address of Guardian is hard-coded into the core, such that it loads Guardian directly using disk I/O without involving any file system.

After occupying the CPU, Guardian loads the TCB image into a reserved memory region. It then configures the hypervisor page table, the EPT and IOMMU to ensure that the reserved region is not in the hypervisor or the guest's space and not accessible by DMA devices either. Separating the reserved region from the hypervisor space ensures no accidental accesses to the region. (As shown later, Guardian must map the region into its space by re-configuring the page table in order to access it.)

Finally, Guardian sets VMM\_flag indicating its presence, and passes the control back to the bootloader core (Step 3). After asserting the flag is set, the core loads other modules and configuration files (Step 4) and proceeds to boot up the guest in the normal way (Step 5).

Figure 3.3: The sequence of secure bootup.

**Device Configuration Space Protection.** A rootkit may manipulate the device configuration space (e.g., the space-overlapping attack [109]) to thwart Guardian to intercept certain I/O events or access to I/O data. In order to defeat the configuration space manipulations and conflicts/overlapping between different devices, Guardian is poised to intercept and validate any update to the device configuration registers after its boot up. Note that these registers are located in the northbridge chipset [31]. The interception are realized via configuring Virtual-Machine Control Structure (VMCS) for I/O ports and the EPT for MMIO regions.

#### **Secure Shutdown**

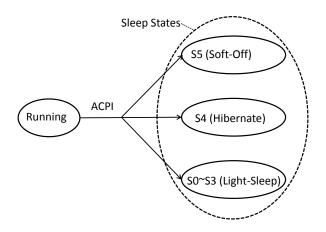

The guest may modify the Guardian image on the disk. Therefore, when the system is powered off, the TCB saved in the reserved memory must be written back to their original locations in the disk for the next round of execution. There exist two types of shutdown events. One type is the sleep events, where the system enters a sleep state through the Advanced Configuration and Power-management Interface (ACPI) [40]; the other is the reboot event, where the system restarts from the BIOS. Guardian intercepts both types of shutdown events and responds accordingly.

ACPI Sleep. The ACPI sleep event is managed by the Operating System Power Management (OSPM) subsystem on the modern ACPI-compatible system. Receiving commands from software (e.g., system call) or external interrupts (e.g., the System Control Interrupt triggered by pressing the power/sleep button or closing the laptop lid), the OSPM subsystem sets the PM1a\_CNT register to force the system entering the corresponding sleep state. Note that Guardian prohibits the ACPI sleep event to be triggered by the optional sleep control and PM1b\_CNT registers. Specifically, there is a 32-bit pointer in the Fixed ACPI Table (FADT) pointing to the PM1b\_CNT block. Guardian clears this pointer and intercepts accesses to the PM1b\_CNT register. The same method is used on the control sleep register.

Guardian intercepts the guest's sleep command issued to the PM1a\_CNT register. Note that the actual interception method depends on whether the register is accessed by PIO or MMIO. The former involves VMCS configuration whereas the latter requires the EPT.

Among the six Sleep states (S0 to S5) defined in the ACPI specification (in Figure 3.4), the light-sleep (S0 to S3) states are not of concern, because the main memory remains powered and Guardian remains alive. Therefore, Guardian performs no action. For the soft-off state (S5) where the system will be powered off, Guardian restores the TCB image back to the respective disk locations by using direct disk I/O operations. Note that Guardian needs to re-activate the disk which has

Figure 3.4: ACPI sleep states.

been closed (but remains powered) before the ACIP sleep command is issued. In the end, Guardian clears VMM\_flag and resumes the intercepted ACPI command which turns the platform off.

It is slightly more complicated to deal with the hibernation state S4 due to the need for platform context saving. Guardian needs to save its context into the hypervisor partition, in addition to the restoration work done for S5. For the guest context, Guardian disables and prohibits the ACPI S4BIOS Transition  $^1$ , which bypasses Guardian as the BIOS directly saves all memory content into the hard disk including Guardian's context. Therefore, only the OS-assisted hibernation method is supported and the OS must write its own context into the disk before hibernation.

Note that after the PM1a\_CNT register is set, the platform passes the point of no return, because the ACPI hardware will force the platform to enter S4 or S5 state and no software will be loaded to the CPU. In other words, Guardian is the last piece of code executed before shutdown, which guarantees the security of the TCB and critical data resting on the disk.

**System Reboot.** There are three possible ways to reboot a system. One is ACPI reset, which is activated by the ACPI reset register. Note that the system will immediately reboot once the reset register is set. The ACPI reset register can be accessed by port I/O or memory-mapped I/O, which can be intercepted by Guardian through

$<sup>^{1}</sup>$ It clears the F bit in the Firmware ACPI Control Structure (FACS) and intercepts accesses to the SMI\_CMD command register, which is S4BIOS service activation.

configuring the VMCS or EPT, respectively. The second way is essentially triggered by the CPU INIT signal. Guardian intercepts the event through configuring the VMCS.

In the third way, an attacker can switch the CPU to the real mode and jump to the BIOS entry to reboot the system. The tricky part is that it can bypass the INIT and ACPI reset mechanisms, meaning that the previous two interception methods will fail to intercept this one. To intercept it, a straightforward solution is to intercept the CPU switch from protected mode to real mode. However, the cost will significantly rise up when legitimate CPU-mode switches take place frequently, e.g., in Windows. Our solution is to prevent jumping to the BIOS reboot-routine from the guest by configuring the EPT. Any attempts from the guest OS to reboot the system will be intercepted by Guardian whose response is to repeat Step 3-5 in secure bootup without rebooting the whole platform.

#### Recovery

Guardian provides an alternative secure boot mechanism, where the system is able to boot up from a trusted-storage, such as a live CD or a read-only USB token. The bootup sequence is the same as the one described in Section 3.2.1. For convenience, the end-user can configure the system always boot up from a trusted storage, such that the system still can boot up into a trusted state.