# University of South Florida **Scholar Commons**

Graduate Theses and Dissertations

Graduate School

January 2012

# Development of a Bi-Directional Electronics Platform for Advanced Neural Applications

Luca Abbati University of South Florida, lucaabbati@mail.usf.edu

Follow this and additional works at: http://scholarcommons.usf.edu/etd

Part of the <u>Biomedical Engineering and Bioengineering Commons</u>, <u>Electrical and Computer Engineering Commons</u>, and the <u>Neurosciences Commons</u>

#### Scholar Commons Citation

Abbati, Luca, "Development of a Bi-Directional Electronics Platform for Advanced Neural Applications" (2012). *Graduate Theses and Dissertations*.

http://scholarcommons.usf.edu/etd/4271

This Dissertation is brought to you for free and open access by the Graduate School at Scholar Commons. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact scholarcommons@usf.edu.

## Development of a Bi-Directional Electronics Platform

for Advanced Neural Applications

by

#### Luca Abbati

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Department of Electrical Engineering

College of Engineering

University of South Florida

Co-Major Professor: Stephen E. Saddow, Ph.D.

Co-Major Professor: Andrea Scorzoni, Ph.D.

Christopher L. Frewin., Ph.D.

Andrew M. Hoff, Ph.D.

Mark Jaroszeski, Ph.D.

Salvatore D. Morgera, Ph.D.

Sylvia Thomas, Ph.D.

Date of Approval: October 12, 2012

Keywords: Neural Recording, Action Potential, Embedded Neural Interface, Brain Stimulation, Low Noise Recording System

Copyright © 2012, Luca Abbati

#### ACKNOWLEDGMENTS

When you see the final goal closer and closer the easiest thing to do is to keep on walking to get there, as fast as possible. But if you turn back for a second, you can see the enormous amount of people that helped you to get there, silently and patiently.

I would like to say thank you to my co-major professors Dr. Stephen E. Saddow and Dr. Andrea Scorzoni for their precious help, their inspiration, their efforts to keep me on track with their experience and to point me in the correct direction when things were confusing.

I would like to say thank you to the committee members and Pisana Placidi at University of Perugia, for their help, comments, support that helped me to find the path to this final result which is an outstanding step in my life. In particular I would like to acknowledge Dr. C.L. Frewin for sharing his vision of a neural recording system with me, to help me with writing the system specification and for all the support during the system design and test.

I would like to say thank you to Dr. E. Weeber of University of South Florida, Byrd Institute, Dr. J.J. Pancrazio and Hamid Charkhkar of George Mason University for letting me use their lab for neural recording and for helping me a lot during the measurements.

Thank you to Dr. Christopher Locke, Joe Register, Justin King for all the precious work they did to help me each and every day to get closer to succeed and for being very

good friends, and thanks to the whole SiC group at USF for their encouragement and support.

Thank you to all the people that supported my path and my personal life during my Ph.D. time, thank you to Elisa for her unconditional love and for the continuous inspiration, thanks to my family that supported me in all the circumstances during the whole period never stopping to believe in me.

And last but not least, thanks to my second family, The Saddow family, Vaine and Luchino and Stephen, because every time I am here in Tampa they make feel like I am home. I will bring memories of these days with me for the rest of my life.

## TABLE OF CONTENTS

| LIST OF TABLES                                                                                                                           | iv |

|------------------------------------------------------------------------------------------------------------------------------------------|----|

| LIST OF FIGURES                                                                                                                          | V  |

| ABSTRACT                                                                                                                                 | X  |

| CHAPTER 1: INTRODUCTION                                                                                                                  | 1  |

| 1.1 Basics of Brain Computer Interfacing                                                                                                 | 1  |

| 1.2 Signal Propagation within the Body and Methods for Recording and Stimulation                                                         | 6  |

| 1.3 Long-term Performance of Implanted Devices                                                                                           |    |

| 1.4 Summary and Organization of Dissertation                                                                                             |    |

| CHAPTER 2: PHYSIOLOGY OF EXCITABLE CELLS AND INTERFACING                                                                                 | 20 |

| METHODS2.1 The Cell Membrane                                                                                                             |    |

|                                                                                                                                          |    |

| <ul><li>2.2 Ionic Currents in the Solution and Through the Membrane</li><li>2.3 The Parallel Conductance Model of the Membrane</li></ul> |    |

| 2.3.1 Membrane Permeability and Nernst Equilibrium                                                                                       |    |

| 2.4 Membrane Structure and Channels Conductance                                                                                          |    |

| 2.4.1 Currents Through a Single Channel                                                                                                  |    |

| 2.4.2 Voltage and Patch Clamps                                                                                                           |    |

| 2.5 The Hodgkin-Huxley Membrane Model                                                                                                    |    |

| 2.6 Action Potentials                                                                                                                    |    |

| 2.6.1 Stimulation Threshold Voltage                                                                                                      |    |

| 2.6.2 Other Important Parameters                                                                                                         |    |

| 2.7 Recording Action Potentials                                                                                                          |    |

| 2.7.1 Passive High Pass Filter Input                                                                                                     |    |

| 2.7.2 Capacitive Inverting Input                                                                                                         |    |

| 2.7.3 Differential Capacitive Input                                                                                                      |    |

| 2.7.4 Active Pixel Sensor Micro Electrode Array                                                                                          |    |

| 2.7.5 Recording Unit with Active Stimulation Artifact Compensation                                                                       |    |

| 2.7.6 OSFET Input Stage                                                                                                                  |    |

| 2.8 Summary                                                                                                                              |    |

| CHAPTER 3: DESIGN AND PROTOTYPING OF A CUSTOM BRAIN                                                                                      |    |

| COMPUTER INTERFACE                                                                                                                       | 59 |

| 3.1 Motivation and System Specifications                                                                                                 |    |

| 3.1.1 Specifications for Noise. Gain and Randwidth                                                                                       |    |

| 3.1.2 Specifications for Stimulation Voltage Pulse Generator           | 61  |

|------------------------------------------------------------------------|-----|

| 3.1.3 Signal Digitalization and Persistent Storage                     | 62  |

| 3.1.4 Specifications Summary                                           |     |

| 3.2 A System Overview                                                  |     |

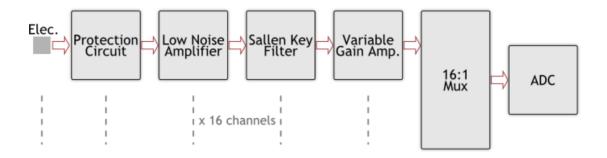

| 3.3 System Architecture: Design and Simulation                         | 66  |

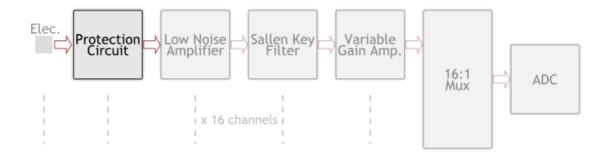

| 3.3.1 The Protection Circuit                                           | 66  |

| 3.3.2 The Low Noise Amplifier                                          | 69  |

| 3.3.3 The Sallen & Key Filter                                          | 72  |

| 3.3.4 The Variable Gain Amplifier                                      | 74  |

| 3.3.5 The Multiplexing and Data Conversion Unit                        | 77  |

| 3.3.6 The Stimulation Circuit                                          |     |

| 3.3.7 Putting it All Together                                          | 80  |

| 3.4 The FPGA Based Control Unit                                        | 81  |

| 3.4.1 The Atlys FPGA Development Board                                 | 83  |

| 3.4.2 The Gain Control Unit                                            |     |

| 3.4.3 The ADC Data Acquisition Unit                                    | 86  |

| 3.4.4 The Digital Filtering Unit                                       | 88  |

| 3.4.5 The Ethernet Module                                              |     |

| 3.4.6 The Java Based Acquisition and Storage Driver                    | 92  |

| 3.5 Summary                                                            |     |

|                                                                        |     |

| CHAPTER 4: ELECTRICAL AND BIOLOGICAL TEST OF THE                       |     |

| BI-DIRECTIONAL BMI ELECTRONICS SYSTEM                                  | 95  |

| 4.1 Electrical Test and Characterization                               | 96  |

| 4.1.1 Gain Considerations and Measurements                             | 96  |

| 4.1.2 Bandwidth Measurement                                            |     |

| 4.1.3 Input Referred Noise Measurement                                 | 100 |

| 4.2 Biological Testing: Recording and Stimulation of Action Potentials | 103 |

| 4.2.1 Testing the Recording Electronics                                | 104 |

| 4.2.2 Testing the Stimulation Electronics Module                       | 107 |

| 4.3 Summary                                                            | 111 |

|                                                                        |     |

| CHAPTER 5: CONCLUSIONS AND FUTURE WORKS                                | 114 |

| 5.1 System Design and Electrical Testing                               |     |

| 5.2 Biological Measurements and Performance Comparison                 | 117 |

| 5.3 Design and Biological Test of the Stimulation Circuit              | 118 |

| 5.4 The FPGA Control Unit                                              | 118 |

| 5.5 What Is Next?                                                      | 119 |

| 5.5.1 From the Prototype to the Full 16 Channel Board                  | 119 |

| 5.5.2 Design of a Custom ±50 V Voltage Regulator                       | 119 |

| 5.5.3 Capacitive Coupling Between the Stimulation Circuit and the      |     |

| Recording Unit                                                         | 120 |

| 5.5.4 Blind Time After Stimulation Pulse                               | 121 |

| 5.5.5 Neural Recording Using from Silicon Carbide MEA                  | 125 |

|                                                                        |     |

| REFERENCES                                                             | 127 |

| APPENDICES |                        | . 133 |

|------------|------------------------|-------|

| Appendix A | Electric Schematics    | . 134 |

| Appendix B | FPGA Firmware          | . 141 |

| Appendix C | Copyrights Permissions | . 164 |

## LIST OF TABLES

| Table 2.1 | Typical experimental intracellular and extracellular concentrations of the main ion species from a squid axon nerve. | 27  |

|-----------|----------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2 | A summary of the electrical characteristics from the high pass filter input architecture                             | 45  |

| Table 2.3 | A summary of the predicted electrical characteristics from the capacitive inverting input architecture.              | 48  |

| Table 2.4 | A summary of the electrical characteristics from the differential capacitive input architecture.                     | 51  |

| Table 2.5 | A summary of the electrical characteristics from the active Pixel Sensor Micro Electrode Array.                      | 53  |

| Table 2.6 | A summary of the electrical characteristics from the recording unit with active stimulation artifact compensation.   | 55  |

| Table 2.7 | A summary of the electrical characteristics from the OSFET input stage architecture.                                 | 58  |

| Table 3.1 | A summary of the system specifications                                                                               | 64  |

| Table 4.1 | Calculated and measured gain values for the different amplification stages                                           | 98  |

| Table 4.2 | Output and input system noise measured and calculated from time domain recording, respectively.                      | 102 |

## LIST OF FIGURES

| Figure 1.1 | (A) Typical commercially available EEG system for consumer applications                                                                                                                                                                                                            | 3    |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.2 | A 3D quad 64 electrode module for <i>in vivo</i> implantation                                                                                                                                                                                                                      | 5    |

| Figure 1.3 | An implantable electrode array ready to be installed in a macaque monkey's brain                                                                                                                                                                                                   | 5    |

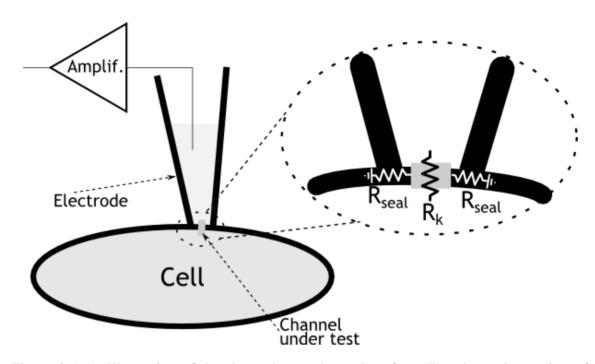

| Figure 1.4 | A typical simplified experimental setup for patch clamp (i.e., intracelluar) measurements consists of a invasive voltage patch clamp with an high resistance seal (R $\sim$ G $\Omega$ ), a current or voltage amplifier and a data acquisition instrument such as an oscilloscope | 8    |

| Figure 1.5 | Optical microscope image of a typical micro electrode array (MEA) with the cells cultured on an insulating layer and the electrode traces underneath.                                                                                                                              | . 10 |

| Figure 1.6 | A simplified model of a typical MEA recording experiment                                                                                                                                                                                                                           | 10   |

| Figure 1.7 | An overview of the Active Pixel Sensor Micro Electrode Array (APS-MEA) system, where the electrodes are in several rows and columns                                                                                                                                                | . 12 |

| Figure 1.8 | Optogenetics involves the stimulation of neural APs with light                                                                                                                                                                                                                     | . 14 |

| Figure 1.9 | The UIA (a) before and (b) after implantation                                                                                                                                                                                                                                      | . 17 |

| Figure 2.1 | A schematic representation of the cell membrane that divides the cell's intracellular and extracellular volumes (not to scale)                                                                                                                                                     | . 20 |

| Figure 2.2 | A permeable membrane separates two volumes called intracellular and extracellular                                                                                                                                                                                                  | . 25 |

| Figure 2.3 | The parallel conductance equivalent model of the cell membrane                                                                                                                                                                                                                     | . 27 |

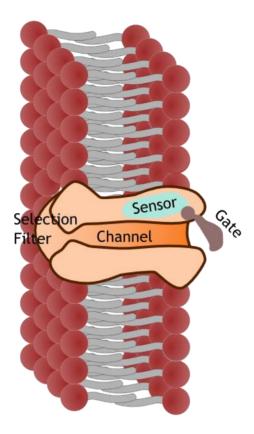

| Figure 2.4 | A schematic representation (not to scale) of a typical ion channel                                                                                                                                                                                                                 | . 29 |

| Figure 2.5 | An illustration of the electrode-membrane interface                                                                                                                                                                                                                                | 31   |

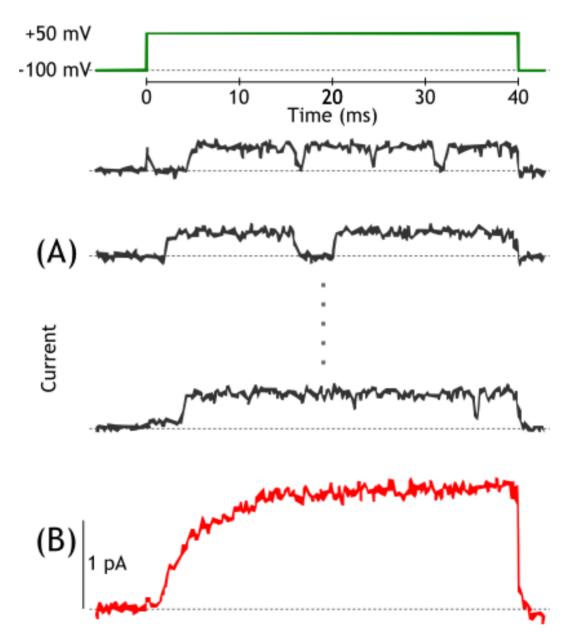

| Figure 2.6  | An example of patch-clamp recording of unitary <i>K</i> currents in a squid giant axon during a voltage step from –100 to 50 mV                                                                                                                                      | . 33 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

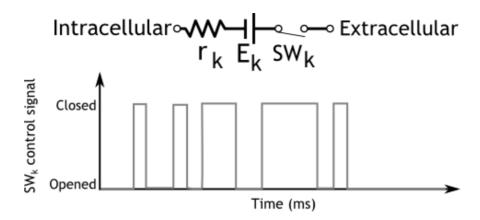

| Figure 2.7  | A simplified model of a signal potassium channel with a constant resistance $r_k$ of 50 G $\Omega$ (or $g_k$ of 20 pS), the Nernst potential $E_k$ and a switch that is closed (or opened) in response to the changes in concentrations and membrane voltage $V_m$ . | . 34 |

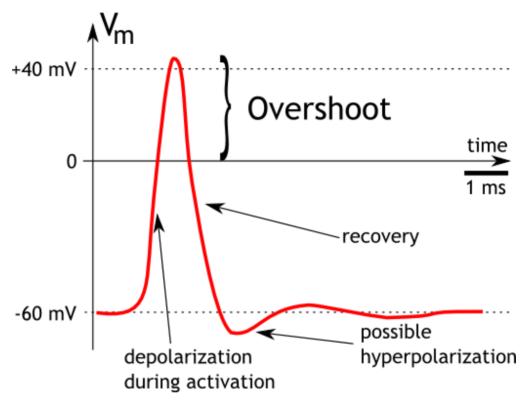

| Figure 2.8  | Diagram of an AP, with the depolarization phase followed by a recovery phase.                                                                                                                                                                                        |      |

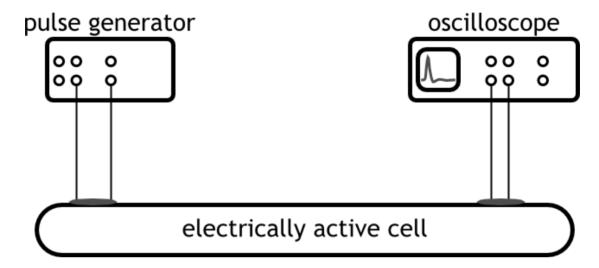

| Figure 2.9  | A simple experimental setup for recording of an AP                                                                                                                                                                                                                   | . 38 |

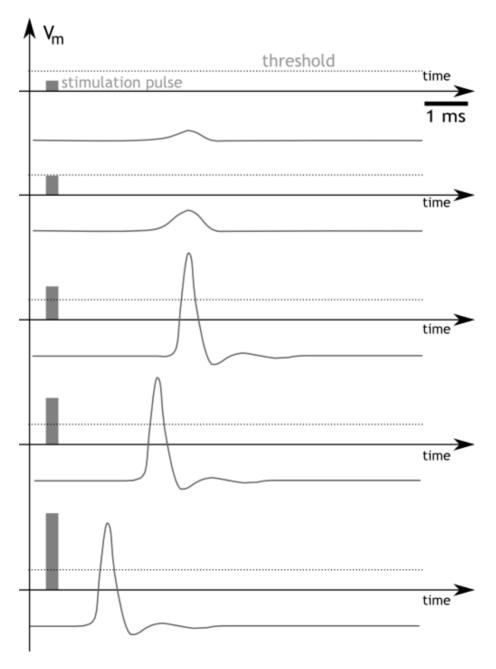

| Figure 2.10 | A diagram of stimulated electrical activity following a stimulation pulse.                                                                                                                                                                                           | . 39 |

| Figure 2.11 | A schematic representation of a typical MEA setup where neural tissue lays atop an array of micro-electrodes                                                                                                                                                         | . 41 |

| Figure 2.12 | The single-ended input low pass filter and preamplification stage is directly connected to the recording electrode.                                                                                                                                                  | . 43 |

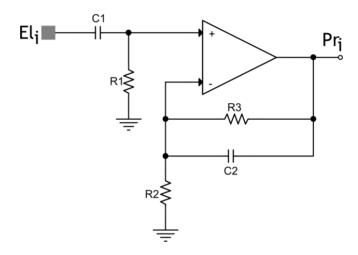

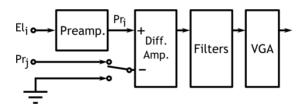

| Figure 2.13 | A schematic view of the Obeid architecture                                                                                                                                                                                                                           | . 43 |

| Figure 2.14 | The input circuit of the Olsson/Wise architecture where the gain is obtained as $-C_1/C_2$ . $C_1 = 10$ pF, $C_2 = 0.1$ pF for a nominal fixed gain value of 100.                                                                                                    | . 47 |

| Figure 2.15 | The recording front end of the capacitive input differential architecture                                                                                                                                                                                            | . 49 |

| Figure 2.16 | A schematic representation of the circuit                                                                                                                                                                                                                            | . 52 |

| Figure 2.17 | The circuit diagram with both the amplification circuitry and the active stimulus artifact compensation system                                                                                                                                                       | . 54 |

| Figure 2.18 | The basic circuit diagram of the OSFET electrode approach                                                                                                                                                                                                            | . 55 |

| Figure 2.19 | The schematic diagram of the experiment for reconnection of two separates neurons.                                                                                                                                                                                   | . 57 |

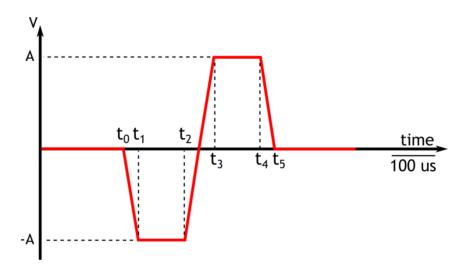

| Figure 3.1  | Desired stimulation pulse waveform                                                                                                                                                                                                                                   | . 62 |

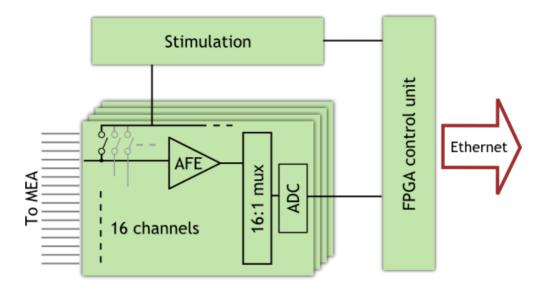

| Figure 3.2  | A system overview of the whole unit assembly                                                                                                                                                                                                                         | 65   |

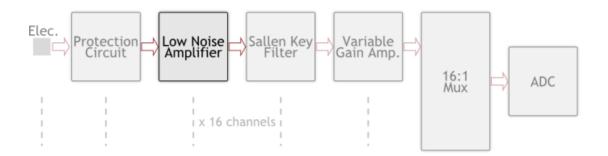

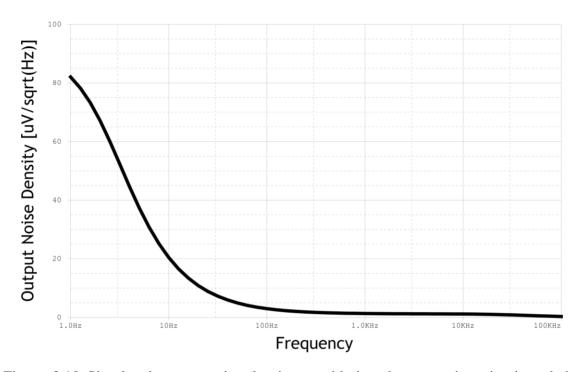

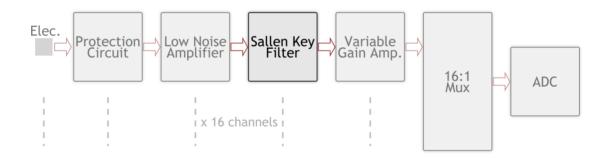

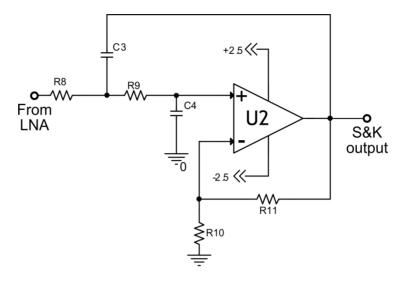

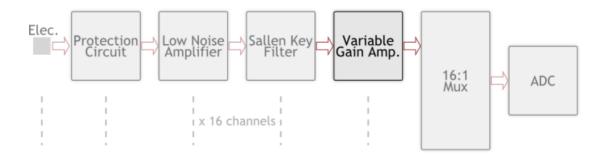

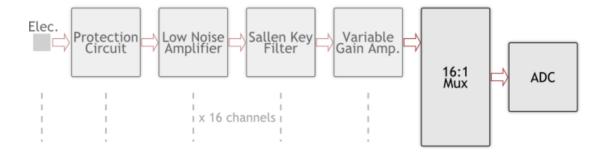

| Figure 3.3  | A block diagram representation of the AFE unit for signal recording showing, in order: the electrode, the protection circuit, the low noise amplifier, the Sallen & Key filter, the variable gain amplifier, the multiplexer and the analog to digital converter.                                               | 66   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 3.4  | The protection circuit: the first interface to the electrode.                                                                                                                                                                                                                                                   | 67   |

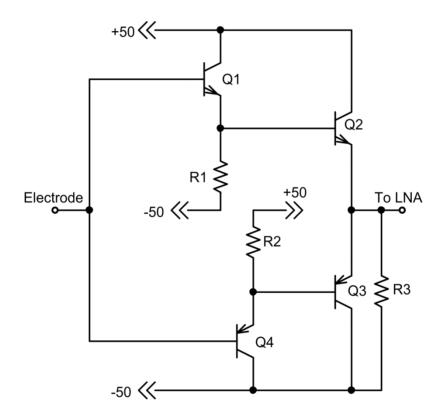

| Figure 3.5  | The schematic circuit of the protection block. $R_1$ and $R_2$ are 5.6 M $\Omega$ resistors that provide a path to switch off the second transistor of the Darlington configuration                                                                                                                             | 67   |

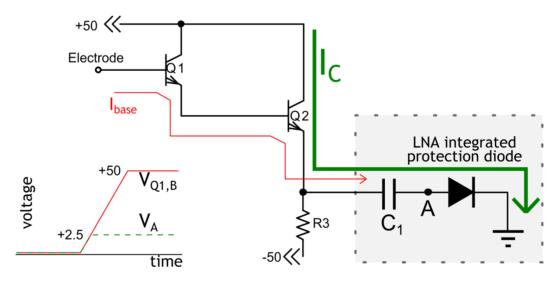

| Figure 3.6  | The current path through the protection circuit during a positive stimulation pulse                                                                                                                                                                                                                             | 69   |

| Figure 3.7  | The low noise amplifier is the first real stage of filtering and amplification in the system.                                                                                                                                                                                                                   | 70   |

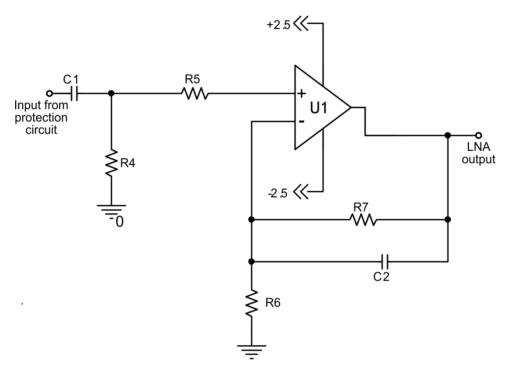

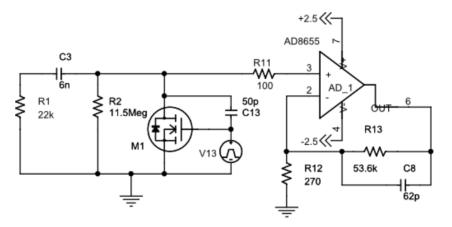

| Figure 3.8  | The LNA circuit schematic with the high pass input filter realized by $C_1$ =6 $nF$ and $R_4$ =11.5 $M\Omega$ , the protection resistance $R_5$ =100 $\Omega$ and the active low pass filter made of $U_1$ ( $AD8655$ , $Analog\ Devices$ ), $R_6$ =270 $\Omega$ , $R_7$ =53.6 $k\Omega$ , and $C_2$ =62 $pF$ . | 71   |

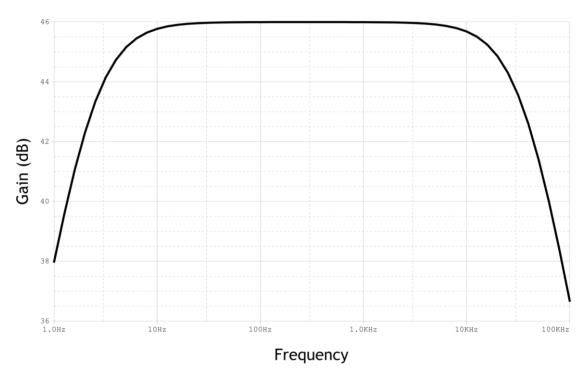

| Figure 3.9  | Simulated frequency response of the low noise amplifier                                                                                                                                                                                                                                                         | 72   |

| Figure 3.10 | Simulated output noise density considering the protection circuit and the LNA                                                                                                                                                                                                                                   | 73   |

| Figure 3.11 | The Sallen & Key filter after the preamplification stage to reduce aliasing in by the ADC downstream.                                                                                                                                                                                                           | . 73 |

| Figure 3.12 | Circuit schematic of the second order Sallen & Key filter                                                                                                                                                                                                                                                       | 74   |

| Figure 3.13 | The variable gain amplifier in the amplification chain                                                                                                                                                                                                                                                          | 74   |

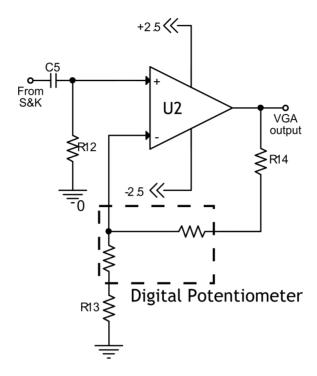

| Figure 3.14 | Circuit schematic of the variable gain amplifier                                                                                                                                                                                                                                                                | 75   |

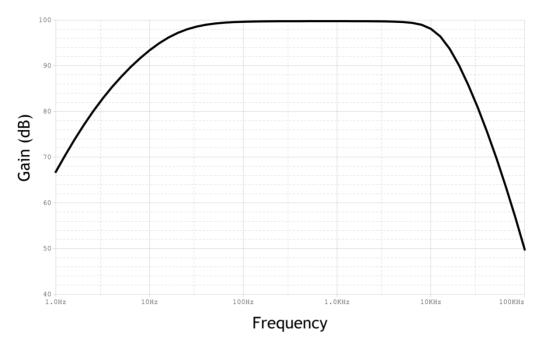

| Figure 3.15 | Simulated frequency response of the whole analog conditioning chain                                                                                                                                                                                                                                             | 77   |

| Figure 3.16 | The analog multiplexer ends the amplification chain                                                                                                                                                                                                                                                             | 77   |

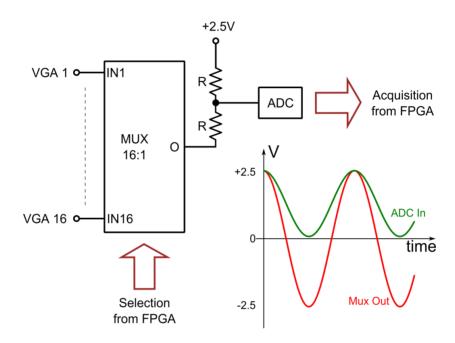

| Figure 3.17 | Circuit schematic for the TDM and ADC units                                                                                                                                                                                                                                                                     | 78   |

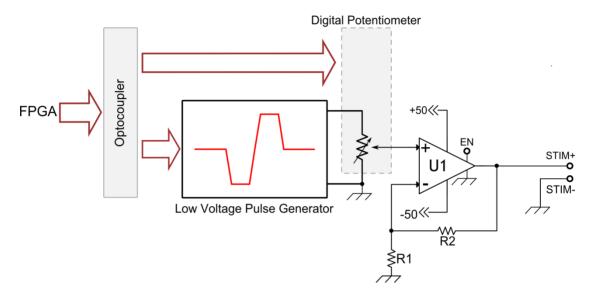

| Figure 3.18 | A schematic diagram of the stimulation circuit                                                                                                                                                                                                                                                                  | 79   |

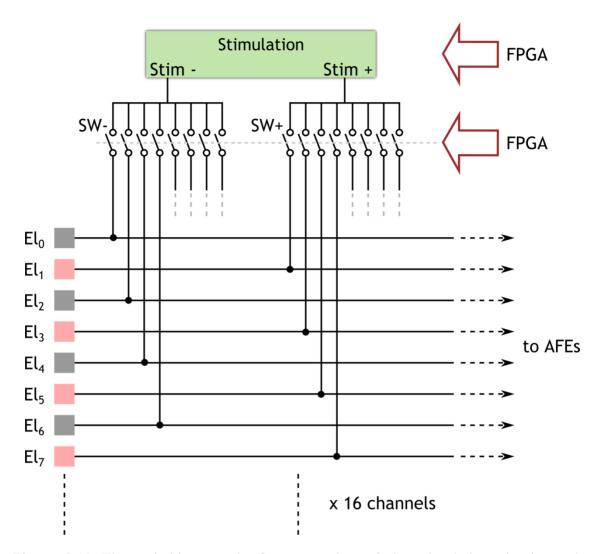

| Figure 3.19 | The switching matrix for connection of the stimulation circuit to the electrodes                                                                                                                                                                                                                                | 82   |

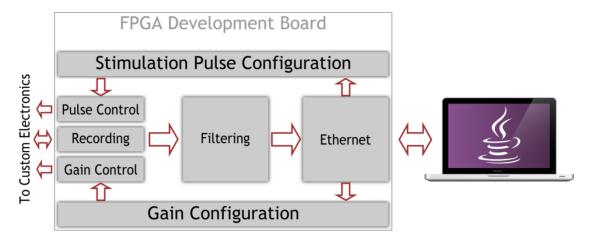

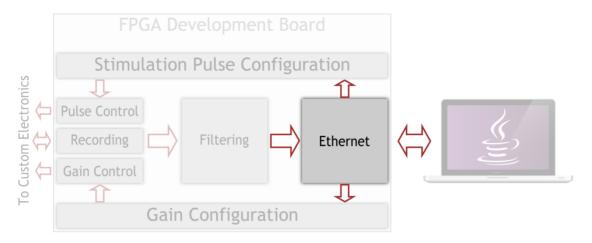

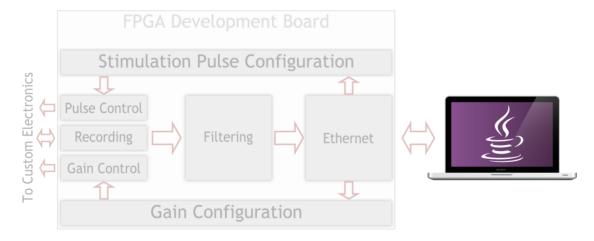

| Figure 3.20 | A high level architecture overview of the FPGA control unit                                                                                                          | 83  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

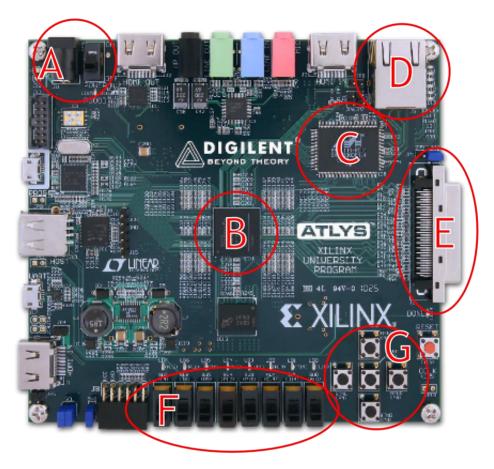

| Figure 3.21 | The Digilent Atlys FPGA development board                                                                                                                            | 84  |

| Figure 3.22 | The amplification core management unit in the FPGA hierarchy                                                                                                         | 85  |

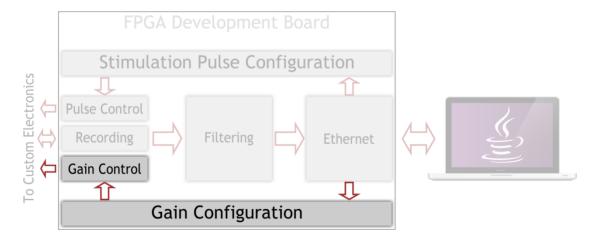

| Figure 3.23 | Block diagram of the amplifying gain control unit.                                                                                                                   | 86  |

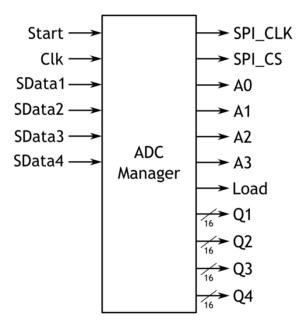

| Figure 3.24 | Block diagram of the ADC unit directly connected to the custom electronics.                                                                                          | 87  |

| Figure 3.25 | The input and output scheme of the ADC manager.                                                                                                                      | 88  |

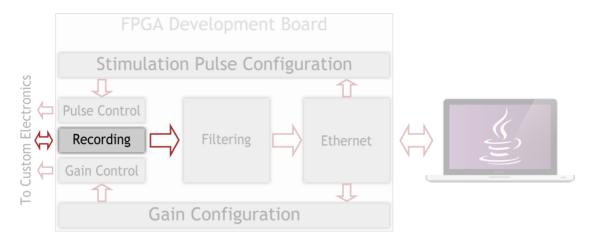

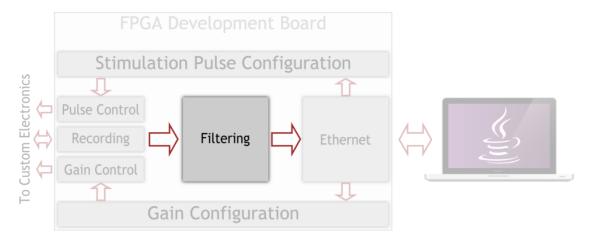

| Figure 3.26 | Block diagram of the system with the filtering stage after the data acquisition module.                                                                              | 89  |

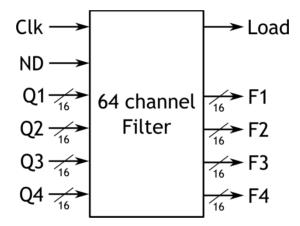

| Figure 3.27 | The I/O scheme of the filtering module                                                                                                                               | 89  |

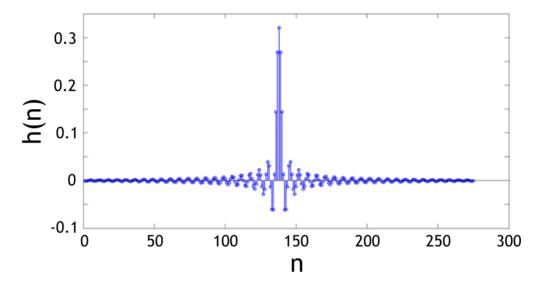

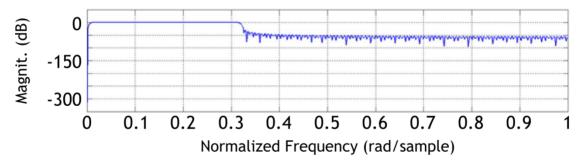

| Figure 3.28 | The 274 samples of the impulse response using the Kaiser window method                                                                                               | 90  |

| Figure 3.29 | The frequency response of the digital FIR filter                                                                                                                     | 90  |

| Figure 3.30 | Block diagram of the system with the Ethernet module highlighted                                                                                                     | 92  |

| Figure 3.31 | The PC receives data from the Ethernet module and transmits the configuration parameters to control the system                                                       | 92  |

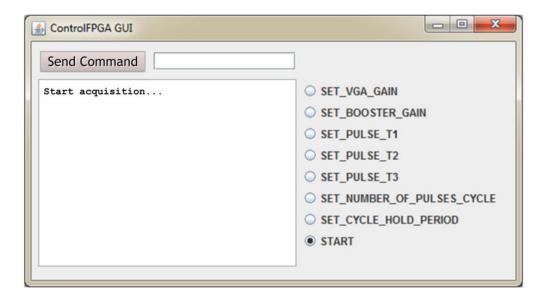

| Figure 3.32 | The GUI for system configuration and acquisition initialization                                                                                                      | 93  |

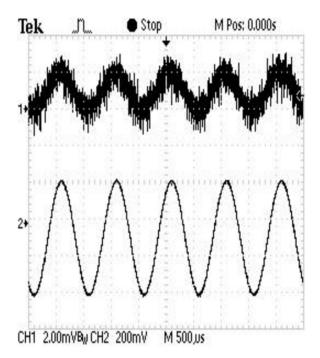

| Figure 4.1  | The measured test signal before and after the first stage of amplification                                                                                           | 98  |

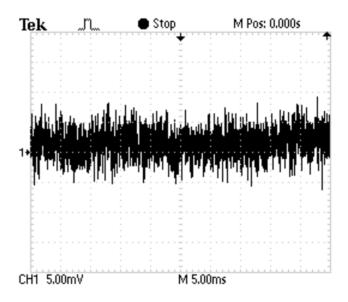

| Figure 4.2  | A sample of the output noise recorded at the <i>VGA</i> output with the input short circuited to the reference voltage                                               | 101 |

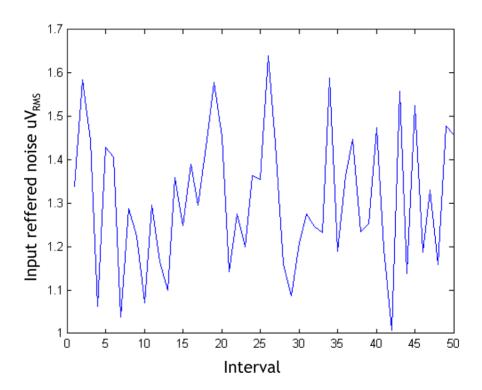

| Figure 4.3  | Input referred noise for 50 consecutive intervals lasting 1 ms each for a gain of 98.93 dB, measured to extract the worst case scenario on a series of measurements. | 103 |

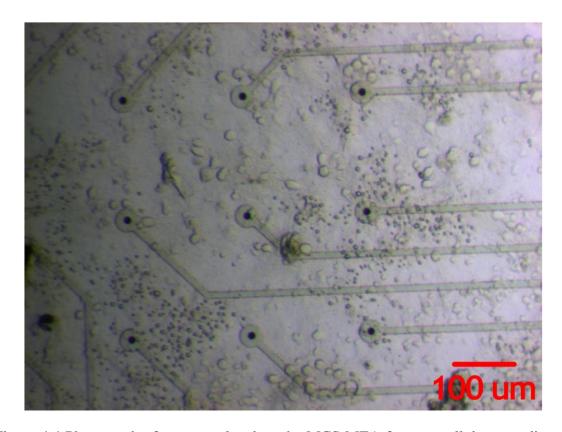

| Figure 4.4  | Photograph of neurons plated on the MCS MEA for extracellular recording at GMU                                                                                       | 105 |

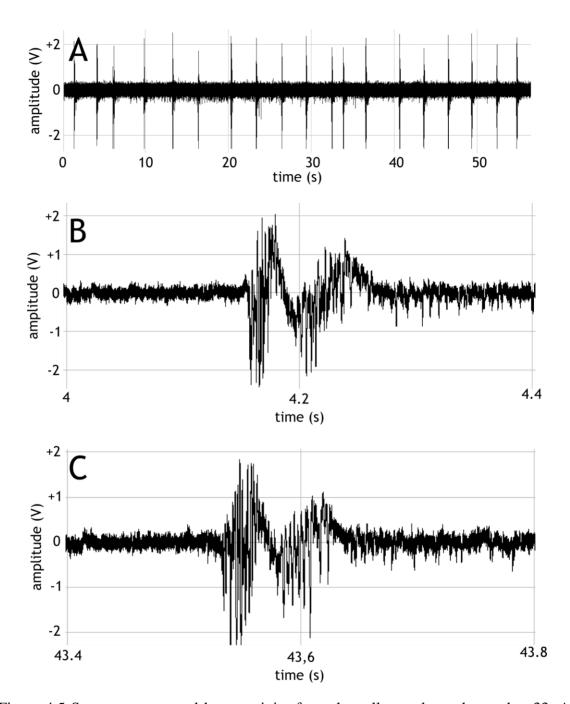

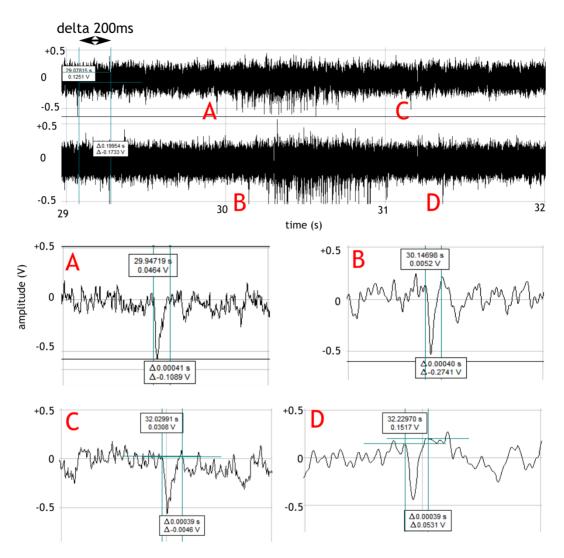

| Figure 4.5  | Spontaneous neural burst activity from the cells on electrode number 33                                                                                              | 106 |

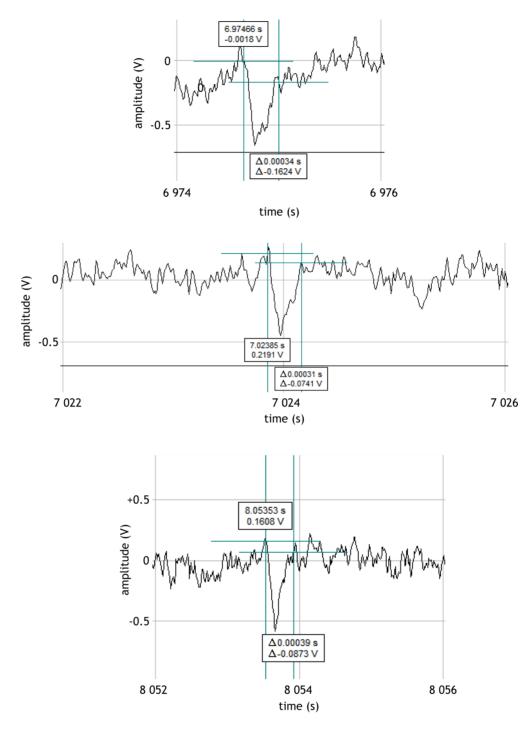

| Figure 4.6 | Single action potential recordings on electrode 33, gain set to 8000 V/V                                              | . 108 |

|------------|-----------------------------------------------------------------------------------------------------------------------|-------|

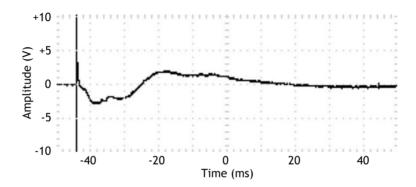

| Figure 4.7 | A comparison between our custom electronics and a commercial recording instrument from Plexon.                        | . 109 |

| Figure 4.8 | fEPSP CA1 hippocampal response induced by the stimulation circuit                                                     | . 110 |

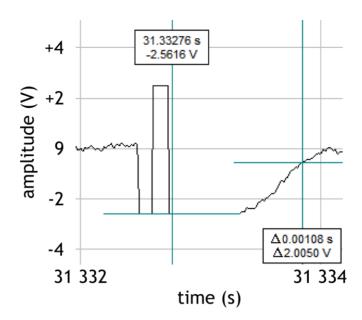

| Figure 4.9 | The output response of the amplification channel for a biphasic $\pm 1~V$ stimulation pulse at the input              | . 111 |

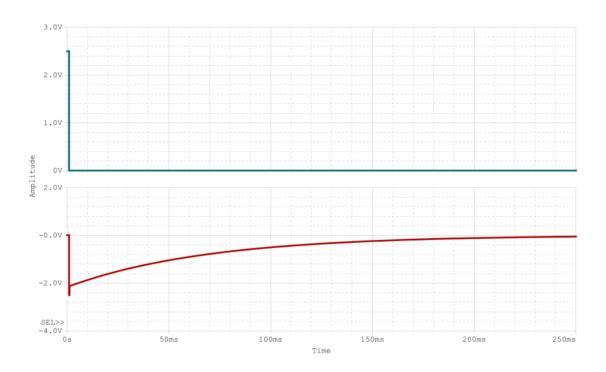

| Figure 5.1 | The AFE input stage electrical equivalent circuit model and was simulated with PSpice <sup>TM</sup> .                 | . 122 |

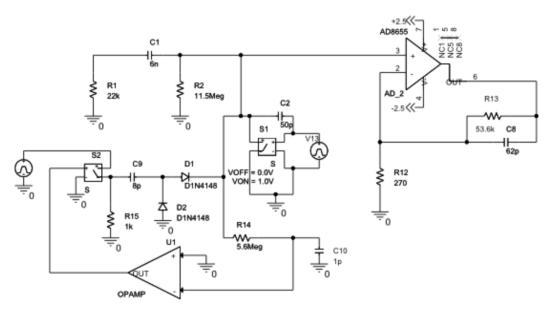

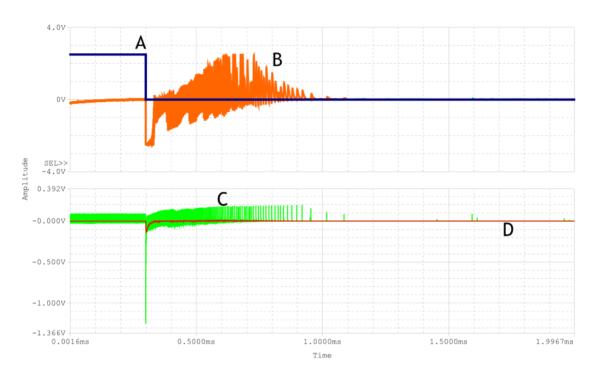

| Figure 5.2 | Simulation of the blind time in the amplifier chain after the stimulation pulse has been applied                      | . 123 |

| Figure 5.3 | The proposed circuit to reduce blindness time after voltage stimulation                                               | . 124 |

| Figure 5.4 | The simulated evolution of the <i>LNA</i> output using the proposed stimulation artifact suppression circuit          | . 125 |

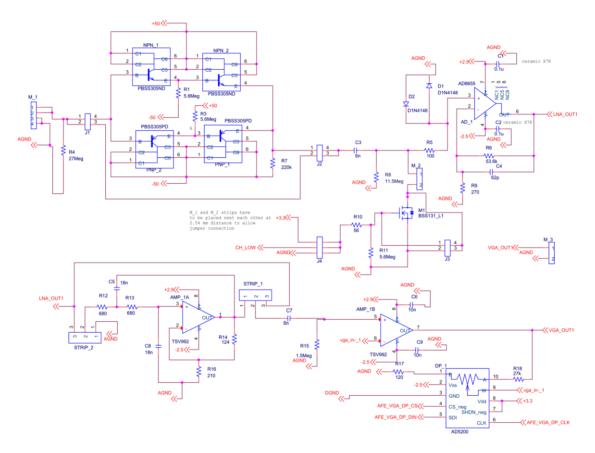

| Figure A.1 | Circuit schematic of a typical channel from the electrode interface to the VGA output                                 | . 135 |

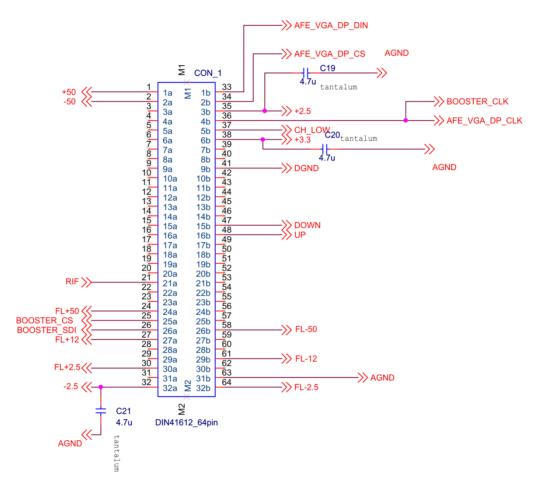

| Figure A.2 | Connection diagram of the DIN41612 connector for digital data interfacing and power supply lines                      | . 136 |

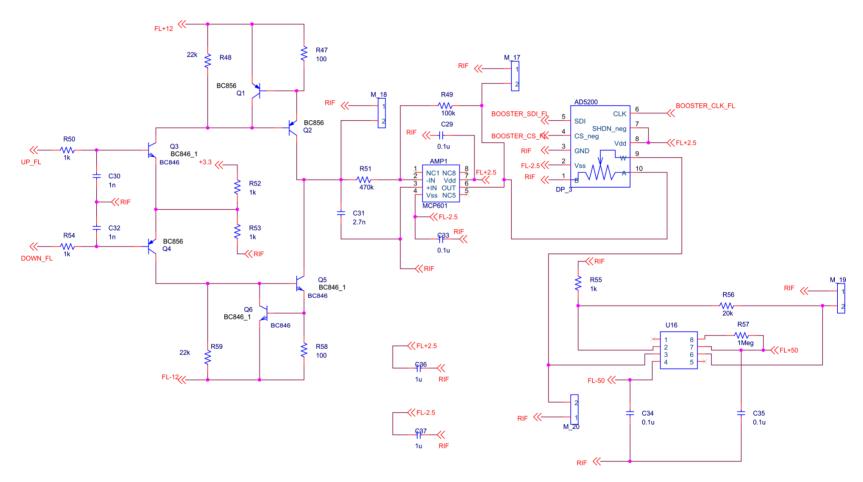

| Figure A.3 | Circuit schematic of the stimulation unit                                                                             | . 137 |

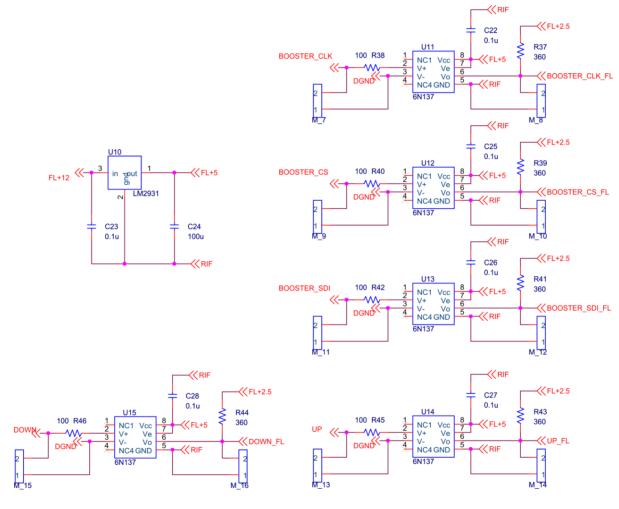

| Figure A.4 | Schematic diagram of the opto-isolation stage to connect the floating stimulation circuit digital signals to the FPGA | . 138 |

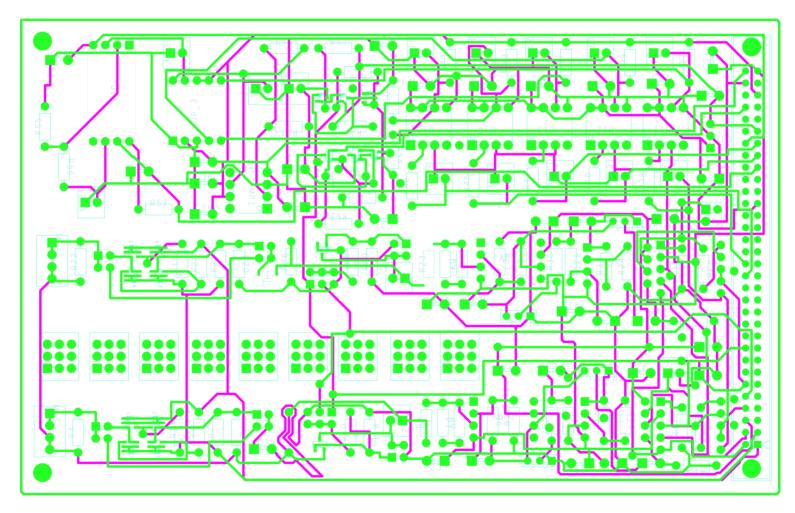

| Figure A.5 | Top and bottom layer of the PCB circuit layout                                                                        | . 139 |

| Figure A.6 | Connection scheme and list of all the control and power signals                                                       | . 140 |

#### **ABSTRACT**

This work presents a high-voltage, high-precision bi-directional multi-channel system capable of stimulating neural activity through bi-phasic pulses of amplitude up to  $\pm 50 \text{ V}$  while recording very low-voltage responses as low as tens of microvolts. Most of the systems reported from the scientific community possess at least one of the following common limitations: low stimulation voltages, low gain capabilities, or insufficient bandwidth to acquire a wide range of different neural activities.

While systems can be found that present remarkable capabilities in one or more specific areas, a versatile system that performs over all these aspects is missing. Moreover, as many novel materials, like silicon carbide, are emerging as biocompatible interfaces, and more specifically as neuronal interfaces, it becomes mandatory to have a system operating across a wide range of voltages and frequencies for both physiological and electrical compatibility testing. The system designed and proven during this doctoral research effort features a  $\pm 50$  V bi-phasic pulse generator, 62 to 100 dB of software selectable amplification, and a wide 18 Hz to 12 kHz bandwidth.

In addition to design and realization we report about biological testing consisting in the acquisition of neural signals from tissue cultures using an MEA where faithful signal recording was achieved with superior fidelity to a commercial system used to sample signals from the same culture. The only system parameter that was less robust than the commercial system was the noise level, which due to our higher bandwidth was somewhat expected. More importantly our custom electronics outperformed in terms of

lower delay and lower cost of realization. All of these results plus suggested future works are listed for the reader's convenience.

#### CHAPTER 1: INTRODUCTION

#### 1.1 Basics of Brain Computer Interfacing

The acquisition and control of neuronal signals that propagate across the human body have been well investigated for several decades and is considered to be a very promising technology for both electronics and medicine. Common use of this technology involves neural circuits realized on silicon chips to build 'brain inspired' logic devices, the subsequent analysis of neural signals propagating across the body, the recording of complex neural activities, the restoration of neural pathways damaged after a trauma [1] or disease, and the study of the effects of drugs on the nervous system. An understanding of the mechanism behind the transmission of neural signals in the body requires a vast variety of concepts from many areas of research: from electrophysiology to neuroscience for interpretation of the signals, from electrical engineering to realize the electronic interfacing systems to signal processing techniques to acquire and recognize neural activity, from material science to medicine to understand and control how invasive implants can survive in the body's harsh environment and how the material's properties change over the course of the time.

Over the course of the years many methods have been presented to establish bidirectional communication with neural tissue from the human body and their feasibility have been proven *in-vitro*, *ex-vivo*, and *in-vivo*. A device capable of establishing a communication to and from the brain, a neural system or, more in general an electrically

active cell, is called the Brain Computer Interface (BCI) or, more in general, the Brain Machine Interface (BMI).

It is estimated that only in the United States almost 12,000 new cases of brain or spinal cord traumas are documented every year [2]. The patients that face these traumas are, in most of the cases, forced to be assisted in most of their daily activity and this significantly deteriorates the quality of life of both them and their families. Only a small percentage of these cases have been reported to recover to an almost normal life style after the injury occurs. Such numbers justify also a serious analysis of the economics behind the patient's health care. In many cases members of the family that are involved in assisting their loved ones must leave their jobs and their usual life style in order to help take care of the patient. These considerations clearly demonstrate how investments in such areas are strategic from a dual perspective – both economically as well as life style of those affected by neurological disease and trauma.

An important branch of biological research during the past few years has been aimed at reconnecting interrupted neural pathways by exploiting stem cells to regenerate nerves. The problem with this approach is that in nerve bundles there are hundreds, or even thousands, of parallel neural paths that connect different parts of the brain to the muscles or to the body receptors (i.e. tactile reaction). Such a huge number of parallel and independently operating pathways should be reconnected in such a way that the pathways before and after the injury are exactly restored. Brain auto-adaptive capability, known in the field of neuroscience as brain plasticity, is not able to fully map the badly connected paths and at the same time. At the present time, there exists no reliable biological control technique allowing stem cells to perfectly reconnect the corresponding pathways to each

other – an engineering solution to this vexing problem is clearly needed in order to provide near-term relief to thousands of patients suffering from neurological disease and trauma.

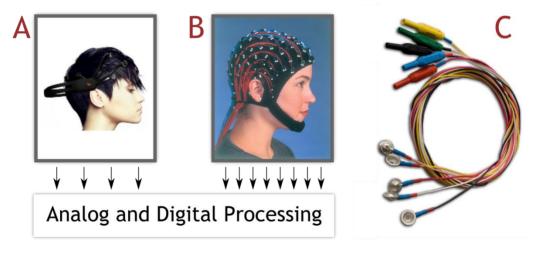

At a very high level, we can divide the different approaches for communication with electrically excitable cells in two categories: invasive and non-invasive devices. The most popular non-invasive interfacing technique is electroencephalography (EEG) [6],[7], where electrical activity of the brain is captured along the scalp (Figure 1.1). This approach requires external electrodes to be applied to the scalp and an external analog and digital processing unit to acquire, filter, amplify and interpret the electrical waveforms.

Figure 1.1 (A) Typical commercially available EEG system for consumer applications. (B) A typical EEG system suitable for research featuring a large number of points of acquisition and (C) typical electrodes used for acquiring brain activity. Image sources: www.jnetdirectbiosciences.com emotiv.com/, computace.blogspot.com, electrodes.sagura.com/

The main advantage deriving from the non-invasiveness of this method is the fact that it is fast to apply, does not present long-term side effects that could harm the person under test, is well established and is inexpensive. The main disadvantages are the fact that it is unidirectional, i.e. it is only capable of recording spontaneously generated brain activity and cannot perform stimulation. In addition EEG offers a very low spatial resolution being largely limited by the maximum number of applicable electrodes. Another big disadvantage is that the subject using such a device must wear an uncomfortable scalp electrode array holder that can largely limit their movement. These kinds of systems have been demonstrated to be capable of accomplishing different tasks, such as, for example 1D and 2D pointer control on a PC display [8] or to navigate a wheelchair for paralyzed subjects [9].

On the other hand implantable invasive devices [10],[11],[12] allow for a higher spatial resolution and ideally, once installed, they are transparent to the user and work without restrictions. However such devices have to function with some stringent constraints in order to be implantable in the human body for a long period of time. First of all they have to be low power devices allowing for longer time periods between system re-charge during their normal operating periods. Second, they have to be biocompatible, i.e. they cannot be recognized as being foreign to the human body so that a localized immune system response is not induced by their presence.

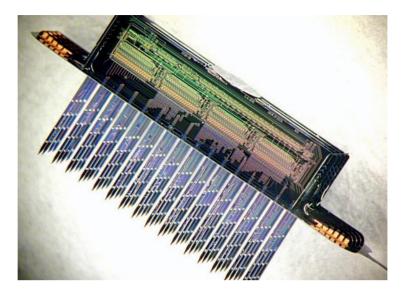

Such systems have been successfully used in research experiments on animals to demonstrate their capability to control complex neural prostheses and systems. Figure 1.2 shows a typical 3D electrode array for implantation in the brain. Typically these systems consist of an array of electrodes that can be easily inserted within the cerebral tissue to establish bi-directional communication. Such systems have been proven to correctly acquire neural activity from the brain and have been used to control artificial prostheses after implantation in macaque monkeys (Figure 1.3).

Figure 1.2 A 3D quad 64 electrode module for *in vivo* implantation from [10]. The system features both the electrodes and on board analog signal conditioning to increase signal-to-ratio by limiting the distance between the point of acquisition and amplification. © 2005 IEEE.

Figure 1.3 An implantable electrode array (source [12]) ready to be installed in a macaque monkey's brain. © 2003 PNAS.

# 1.2 Signal Propagation within the Body and Methods for Recording and Stimulation

While a deeper investigation of the electro-chemical phenomena behind the signal transfer within the body will be investigated more in depth in Chapter 2, it is worth to say now that such signals propagate in the body by means of electro-chemical action potentials (APs), i.e., a change in electrical potential between the inside and outside of an electrically-active cell that moves in a given direction along an electrically active cell [13]. We refer to intracellular recording when we have direct access to the internal volume of the cell and the measured voltage,  $V_m$ , is the potential difference between the inside and outside of the cell membrane  $V_{in}$  -  $V_{out}$ . We refer to extracellular recording when we measure a potential difference between an area in close proximity to the outside of the electrically active cell and a reference voltage, typically the potential of the electrolyte fluid in which the cell resides. Typically intracellular AP signals are in the order of tens of millivolts, while the extracellular recording range is from tens of microvolts to a few millivolts, with most of the information in the 100 Hz to 10 kHz frequency range.

The possibility of stimulating and recording APs simply by forcing intracellular (or extracellular) currents and the ability to read the AP through simple electrodes led, in the past few decades, to many research groups working in this field. Here is presented a review of the most interesting approaches and devices that exist in the literature to the present day to stimulate and to record action potentials. A more accurate examination of selected papers will be presented in Chapter 2 when the different methods to perform electrical characterization will be taken into account.

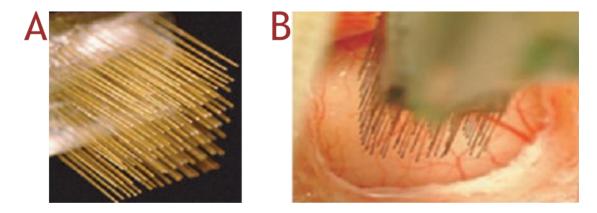

In the literature many different systems are reported that differ from each other from an architectural point of view, but from a biological point of view there are two underlying methods that really define the type of recording: Patch Clamping for intracellular recording and stimulation and microelectrode arrays (MEAs) for extracellular recording.

Patch Clamping [13],[14] consists of a pipette with highly resistant sides that is inserted, for example for voltage measurements, inside the cell volume. In a typical simple experiment the intracellular electrolytic medium can flow inside the pipette and a conductive wire is put through the pipette which serves as the electrical contact. The electrical potential of the inner cellular volume is transferred to a voltage or current amplifier and the output is connected to an oscilloscope. The oscilloscope reference voltage is kept at the electrolytic fluid voltage which is the potential of the extracellular space. When an electric action potential flows along the cell membrane and reaches the pipette, an electrical change in potential is detected and displayed on the oscilloscope.

This technique has been one of the first explored for the study of the cell membrane structure and electrical behavior. It allows very precise measurements of the electro-physiological phenomena that occur at the membrane electrolyte interface. The main disadvantage of this technique is the reduced number of patch clamps that can be used at once and the fact that it is strongly invasive for the cell, eventually forcing the cell to die.

Figure 1.4 A typical simplified experimental setup for patch clamp (i.e., intracelluar) measurements consists of a invasive voltage patch clamp with an high resistance seal (R ~  $G\Omega$ ), a current or voltage amplifier and a data acquisition instrument such as an oscilloscope.

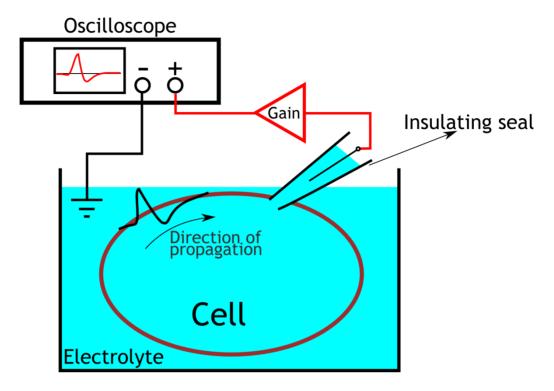

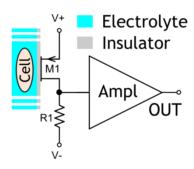

An alternative approach developed lately to increase the number of recording sites is the Micro Electrode Array (MEA) approach which, as stated earlier, is an extracellular method.

In these devices a planar or three dimensional array of micron-scale electrodes are deposited on a bulk material, such as silicon. After the conductive material deposition that realizes the electrode, typically an insulating layer is deposited on the top to avoid short circuits of the signal traces due to the conductive electrolytic fluid. Neural or electrically active cells are then cultured on top of the MEA are plated on the top surface in close proximity to the electrodes. Indeed cells that are too distant from the electrode

will not contribute to signal recording, with a distance of a few micrometers, being sufficient to prevent recording from individual neurons at that distance.

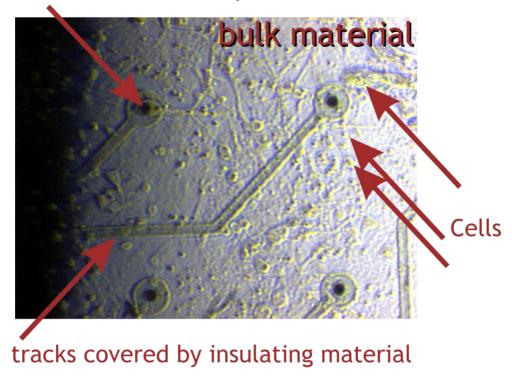

Figure 1.5 shows a typical MEA application where the cells are cultured with different methods on an insulating material that covers the conductive traces which bring the signals away from the recording sites to the off-chip signal amplifiers.

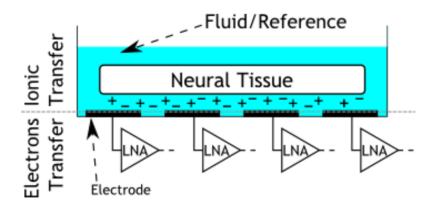

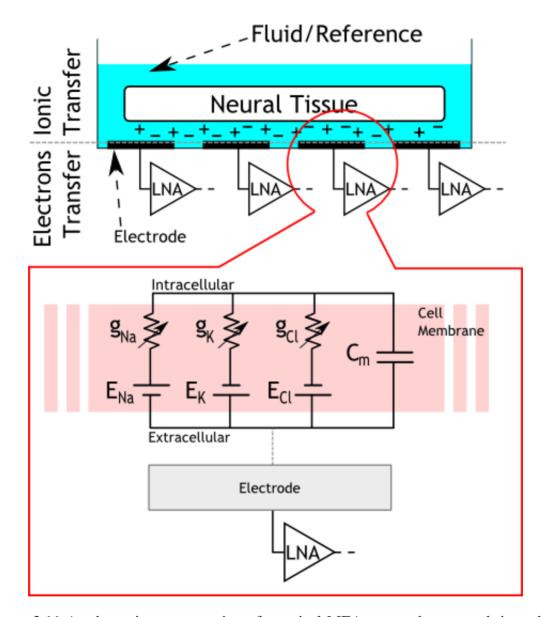

In a typical system (Figure 1.6), the cell is placed in a conductive ionic fluid in close proximity to a planar electrode array. As the action potential flows along the membrane it causes a variation in the ionic concentration in the surrounding area. This variation is detected by the electrode and is amplified through a low noise amplifier (LNA) and filtered. A more in depth explanation of the physical and chemical phenomena that occurs at the membrane-electrode interface will be presented in Chapter 2.

The MEA approach is an *in vitro* technique and is non-invasive and allows for long term measurement of action potentials on a large scale.

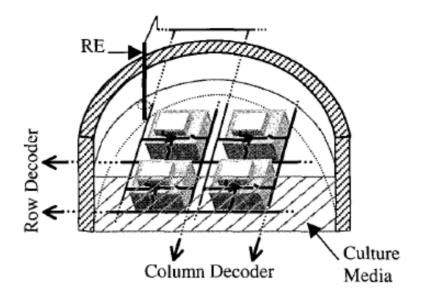

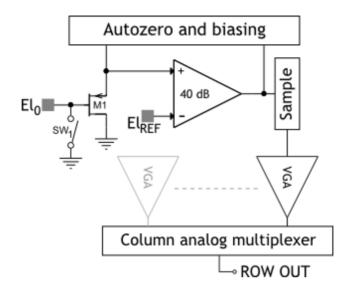

Active Pixel Sensor Micro Electrode Arrays (APS-MEAs) are an interesting approach for high resolution recording of APs [15],[16],[17]. The APS-MEA consists of an array of micron scale gold electrodes that are integrated on a silicon chip (Figure 1.7).

## Electrodes not covered by insulator

Figure 1.5 Optical microscope image of a typical micro electrode array (MEA) with the cells cultured on an insulating layer and the electrode traces underneath.

Figure 1.6 A simplified model of a typical MEA recording experiment. The electrical signals are passed from the membrane to an electrode by means of ionic current. The electrode is connected to a low noise amplifier, LNA, that can be at the recording site or in another area where the signal is to be filtered and amplified.

Electrodes consist of  $20 \times 20 \ \mu m^2$  gold pads disposed with a pitch of  $40 \ \mu m$ . In every spot both the electrode and the preamplifier stage are integrated. This approach reduces the distance between the measuring electrode and the amplification stage, significantly improving the SNR of the signal. This device is realized with a standard  $0.5 \ \mu m$  CMOS process on a silicon substrate. Depending on the number of micro electrodes the analog signal is sampled using a bank of ADCs and digitalized information is read with a FPGA based digital circuit. The usage of a FPGA allows for high speed data processing while reading the sampled signals out of the ADC bank.

The MEA approach presents a huge advantage in terms of spatial resolution and signal to noise ratio of the acquired signal. If the MEA is realized, like in this case on a silicon substrate, the first stages of filtering and amplification can be realized in close proximity to the electrode that is considered. The degree of filtering and amplification, and the bandwidth of the read-out circuit, is limited by the spatial constraints for a given resolution.

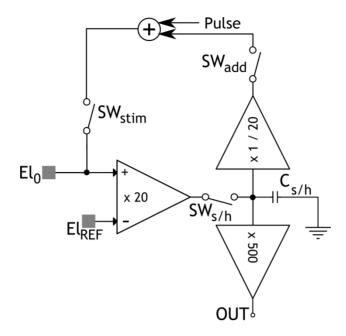

In [18] is presented an integrated circuit that features both recording and stimulation capability. This system features a bidirectional interface between the neurons and an electronic system. Both the analog front end for the recording and the stimulation are complex systems; therefore the filtering section is important in order to read out a signal that inherently has a low SNR ratio. The designer has to focus on the noise level at the amplification stage. Given the high gain needed, i.e. up to 100 dB, the risk of a high noise power at the output of the device exists. This risk is much more evident when the analog front end is moved from the same substrate of the electrode to an external PCB which presents, typically, long connection lines to the electrode pads.

Figure 1.7 An overview of the Active Pixel Sensor Micro Electrode Array (APS-MEA) system, where the electrodes are in several rows and columns. The neural cells are placed in a solution which is used as the reference voltage of the system. © 2001 IEEE.

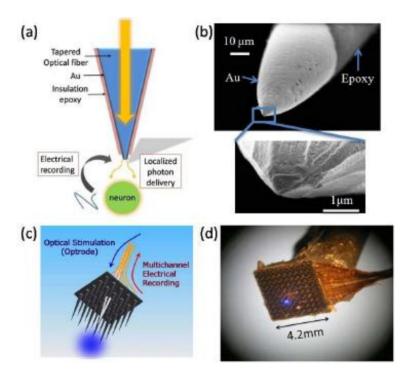

Stimulation of APs in neurons is not only realized by means of electric current or voltage pulses. In [19] optical pulses are reported to be capable of stimulating action potentials across the membrane. What the authors propose is a hybrid electrical-optic electrode, named an 'Optrode'. A tapered optical glass fiber termination is double coated with a thin gold (Au) layer and an electric insulator. A 440 nm light pulse is sent across the glass fiber which was reported to stimulate an action potential. APs can be recorded electronically using the same electrode and a set of other electrodes (Figure 1.8). The optrode is assembled on a commercially available device based on the Utah probe standard array architecture. The authors reported that they could stimulate the APs and simultaneously read signals from all the electrodes of the array at the same time.

While avoiding some phenomena typical of electrically generated APs (i.e., electrolysis at the electrode-solution interface when voltage pulses over 1 V are applied

[20][21]), this method has the disadvantage of requiring a biologically modified neuron. The activation of the AP arises because of a special light-sensitive protein channel called a Channelrhodopsin-2 (ChR2) [22]. This protein channel is native to seaweed and has to be biologically implanted in the neuronal tissue for optical stimulation to be possible.

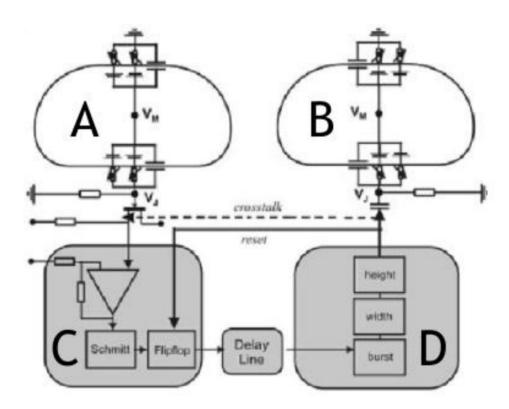

Researchers have also investigated the possibility of transferring an AP signal between two neurons not directly in contact. In [1] authors were able to read a signal from neuron 'A' through capacitive coupling and, after a given amount of time, they were also able to stimulate the same AP to another neuron. This could be useful in a scenario where a neural path is broken because of an injury or an infection. With proper placing of such a system it would be possible to recover the full neural pathway in the damaged area and continue the propagation of the AP. A common characteristic of systems capable of reading APs is the very low noise profile, which should properly read voltages of tens or hundreds of microvolts.

Using stem cells researchers are able to restore neural path of a few centimeters in length. This is a very promising technique because, in principle, it is able to restore broken neural pathways without the implantation of a foreign alien device that can cause an immune system response. The main problem with this method is that an actual nerve bundle is typically made of hundreds or thousands of parallel neural fibers that bring information from the brain to a given muscle or receptor in the body. With restoring the neural path with stem cells there is no control over the mapping of the restored paths. Ideally, the  $i^{th}$  path before the damage should be reconnected to the same  $i^{th}$  path after the damaged area, channeling the correct flow of information from the brain to the final destination muscle or receptor. This is not possible because of the lack of control

methods during the growth of the stem cells. While it is true that the brain is capable of auto-calibration to restore some functionality (i.e., plasticity), it has been shown that this is not feasible when a large area of brain tissue is involved, due to the complexity of the neural network of interconnections. Electronic devices can play an important role in filling this gap.

Figure 1.8 Optogenetics involves the stimulation of neural APs with light. (a) Concept schematic of single optrode. (b) SEM images of the optrode tip. The exposed metallic part of the tip is approximately 50 $\mu$ m, appearing brighter in the upper image. (c) Schematic of the hybrid device. The optrode is coupled to the MEA through a laser drilled hole. (d) An optical microscope image of the device, showing. © 2009 IEEE.

The task of acquiring and processing neural signals at low signal levels is complex and requires an extended signal processing capability. For this reason embedded systems have been proposed that are capable of stimulating and recording APs. An example is found in [23], where a 16-channel PCB-based acquisition system was proposed, entirely realized using off-the-shelf commercially available components. The

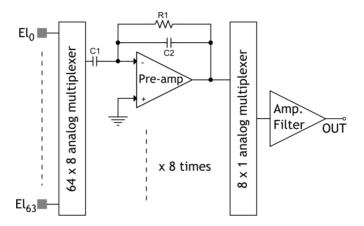

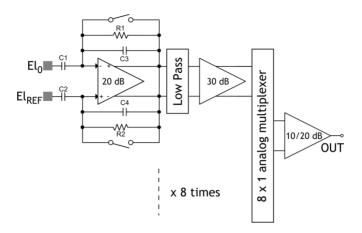

system consists of a pre-amplification and filtering section with a maximum gain of 94 dB and a bandwidth of between 445 Hz and 6.6 kHz. The architecture consists of 16 parallel analog stages that filter and amplify the signal before a 1 MSPS ADC. Information from the ADC is read using an external Complex Programmable Logic Device (CPLD) based system [24] which also controls the signals connection to the ADC stage. The main disadvantage of this architecture is that filtering of the signal at the analog front end limits the number of channels that can be read in the same system since, as the number of channels increases to hundreds, the space required for discrete components grows out of control. This makes this approach unsuitable for larger systems. Considering that often the read-out of useful information consists of hundreds of simultaneous channels, we can say that this approach is only valid for a limited scale research activity.

The solution adopted when the number of channels increases beyond, say, 16, is to transfer the analog front end with the filtering and amplification stage onto a chip, ideally within the same substrate as the micro electrodes interfacing with the cells. In [25] such a system was reported. In this architecture 64 channels are filtered and pre-amplified using the same number of integrated low noise amplifiers. Then all the channels are transferred to a dedicated PCB and time domain multiplexed (TDM) to an ADC. The values from the ADC are read using a fast FPGA, stored to a RAM and sent to a PC for further elaboration and visualization. This architecture allows for a larger number of channels while using off-the-shelf commercially available electronic devices.

#### 1.3 Long-term Performance of Implanted Devices

While different systems found in the literature differ from each other from many points of view, all of them that are integrated circuits present a common characteristic:

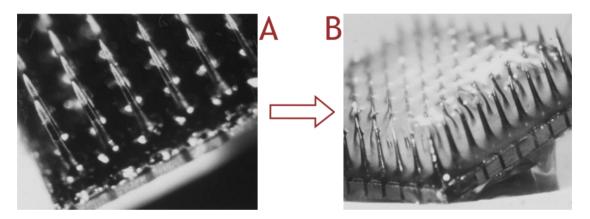

the bulk material used to realize the electrodes or the underlying read-out circuitry is silicon (Si). In both the approach where only the electrodes are integrated, or the whole amplification stage is integrated, systems are realized typically with a standard CMOS process on a silicon substrate. Studies on silicon showed that long-term implantation of devices realized with this material results in failures of the device itself [26]. Figure 1.9 illustrates what happens at the electrode-brain interface after a certain time of implantation. The authors implanted different penetrating silicon electrode arrays, commonly known as the Utah intracortical array (or UIA) into a cat's brain and selectively analyzed both the recording signal quality and the physiological phenomena at the electrode brain interface. What they noticed is that after months both the electrical performance degraded and the electrodes were encapsulated in such a way that, in many cases, the device completely failed. This and other studies suggest that other materials have to be investigated in order to realize implantable and reliable devices able to withstand the human body's harsh environmental challenges and be perform for a time comparable to a human lifetime.

In [27] a comparative qualitative study of different materials in contact with brain cells was reported. Based on AFM investigation of the cells after a given amount of time in contact with the material, the authors assert that brain cells demonstrate a lower adhesion to silicon, which is qualitatively important additional evidence that silicon is not the preferred material for long term implantable biomedical devices. Silicon Carbide, on the other hand, represents a very promising alternative to silicon chips for the realization of long term implantable and biocompatible electrodes as shown in this study where a high degree of neural attachment was observed.

SiC is a well-known material used in many industries that that require operation in harsh environments [28]. It presents mechanical characteristics better than the silicon for micromachining purposes and it is possible to use fabrication processes compatible with standard IC devices, which makes the usage of this material a very promising choice. The confirmation of silicon carbide as a biocompatible material would open an incredibly interesting area of numerous biomedical device interests. This is because both the electrodes and the electronic circuitry could be realized on the same substrate with standard CMOS processes and, most importantly, the device could last for years, opening the way to a wide set of medical applications in the field of neural engineering.

Figure 1.9 The UIA (a) before and (b) after implantation. Encapsulation of a silicon UIA after a few months in cat brain was observed. This phenomena causes a degradation or malfunctioning of the electrode electrical capability to record action potential, and eventually results in device failure after time. Image from [26].

#### 1.4 Summary and Organization of Dissertation

In this chapter an introduction to the dissertation research that will be presented in the following chapter has been made. The motivation for the development of advance brain-machine-interface devices, including the ever important stimulation and recording electronics, has been made. Indeed, with thousands of new patients suffering from some form of neurological disease or trauma each year, and with the cost of medical care

skyrocketing, the need for low-cost, effective, long-term operable systems is clear. The main problem facing modern neuroengineers is the lack of a suitable biocompatible material that is more than just a plastic coating, such as polymers and other films, but is capable of performing sensing as well as supporting advanced electronics. This is critical since restoring neural pathways involves a high degree of neural signal processing, such as filtering and amplification, which can only be done with modern semiconductor platforms. In the USF SiC Group, Tampa, FL, a long history of exploring SiC for biomedical applications has been assembled [58] and, more recently, focused research on developing biomedical devices for neurological applications has been on-going [60]. Based on the early work done by Coletti [59], that demonstrated the biocompatibility of SiC to skin and connective tissue in-vitro, and follow-on work by Schettini [61] that demonstrated that 3C-SiC was hemocompatible, Frewin set out to prove that 3C-SiC was suitable for the neural environment [60]. Perhaps the most interesting outcome of his work was the demonstration that 3C-SiC was far superior to diamond for neural compatibility in-vitro, and when primary neurons were used this material performed equally to polyimide, the gold standard of neurocompatible materials at that time. The USF SiC Group had fabricated 3C-SiC MEA's but was in need of a low-cost, highly effective electronics platform to perform in-vitro experiments (in the first stage) and, eventually, to use in in-vivo studies (in the next stage of research). With this need this dissertation was born with the goal of assembling a highly effective, bi-directional electronics platform for these applications.

The dissertation is organized as follows. After the introductory chapter which was summarized above, Chapter 2 discusses the theory behind the electrical signal

transmission across the body and the mechanisms that determine the generation and propagation of action potentials. Moreover in Chapter 2 I will present a review of a few different existent systems from the literature that have been successfully tested for neural recording and I will individually highlight the most significant features that each of them shows.

Chapter 3 will report on the system specification of the custom electronics we designed, with an complete overview of the many different parts that together compose the system. The chapter is divided in basically three parts, an initial part about the motivations and the specifications we were imposed, a second part with the design and simulation of the electronics boards and a third part showing the FPGA firmware for the control unit that coordinate and synchronize the whole system during both stimulation and recordings.

Chapter 4 will summarize the test that we made to validate the architecture. Firstly, a complete electrical test and characterization have been performed with an accurate measurement important parameters like the gain, the bandwidth and the input referred noise: such measurements, will be compared with the values expected from the simulations performed. Secondly, the system has been tested *in-vitro* with both dissociated neural cells and C57BL/6J hippocampal brain slices.

Chapter 5 will summarize all the work done and propose some possible path to improve and complete the system that presents many possible evolutions in both the analogical electrical part and the software used to manage it.

# CHAPTER 2: PHYSIOLOGY OF EXCITABLE CELLS AND INTERFACING METHODS

#### 2.1 The Cell Membrane

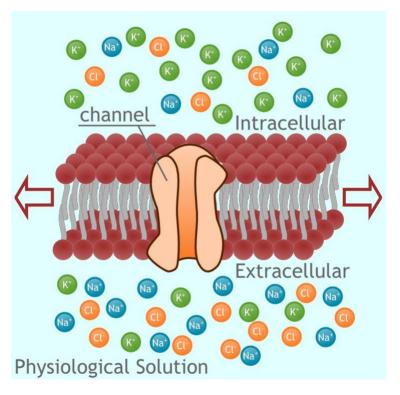

The membrane of a cell is a layer that separates the cellular internal and external volumes, which are called, respectively, the intracellular and extracellular areas [13]. Figure 2.1 shows a schematic overview of a limited portion of the cell membrane.

Figure 2.1 A schematic representation of the cell membrane that divides the cell's intracellular and extracellular volumes (not to scale). Typical membrane dimensionless than 100 Å with a typical thickness of the internal lipidic layer of 30 Å, while an ion diameter can be as low as 1 Å. The ions in the image are sodium (Na $^+$ ), potassium (K $^+$ ) and chloride (Cl $^-$ ). There are other ion species but these are the ones that play the most important role, with Na $^+$  and K $^+$  dominating over the others.

The cell membrane is mainly comprised of a double lipid layer, that blocks the transfer of ions across the membrane, and complex protein assembles that comprise the so called membrane *channels* and *pumps*, whose main function is to regulate the transfer of ions across the membrane. Ions are the unique mechanism of conduction across the membrane, the most important ion species are sodium (Na<sup>+</sup>), potassium (K<sup>+</sup>) and chloride (Cl<sup>-</sup>) with the first two being the most important for the physical propagation of action potentials (Aps). Ions are present in the physiological fluid representing the cell's environment in different concentrations in the intracellular and extracellular volumes. The lipid layer prevents the passage of ions between these two areas, acting as an insulating layer from the electrical point of view. Both *pumps* and *channels* are typically selective, i.e. they permits the passage only of specific ions species and contribute to the overall equilibrium between the intracellular and extracellular spaces, with the difference being that the *pumps* move ions against their natural flow, while the *channels* permits the passage of species according to their natural flow, as explained in the next sections.

The intracellular and the extracellular spaces permit the movement of charged ions, while the lipid layer prevents the ions from going through. This assemble can be electrically modeled as an electrical insulator, the lipid layer that divides the two conductive areas, the intracellular and extracellular spaces. From an electrical point of view this is perfectly equivalent to a capacitor and is named the *transmembrane* capacitance,  $C_m$ , per unit of area

$$C_m = \frac{ke_0}{d} \tag{2.1}$$

where k is the dielectric costant, $e_0$  is the permittivity and d is the membrane's insulating layer thickness. Typical values for the parameters above are k=3 and d=30 Å=3 nm that gives a typical transmembrane capacitance value of 0.9  $\mu\text{F/cm}^2$ .

## 2.2 Ionic Currents in the Solution and Through the Membrane

Ions move in a solution that permits their mobility because of two causes: differences in concentration between two points in space or an electric field. Differences in spatial concentration of a given ion cause all of the molecules of that ion species to move in order to have, as a final result, a flat constant concentration all across the available space. This process, known as *diffusion*, arises mainly because of the thermal energy store in such ions. The process of diffusion, and in particular the flux of a given ion species through a section of unity area, can be quantitatively described by the Fick's law:

$$\overline{I_d} = -D\nabla C$$

(2.2)

where D is a constant dependent on the solution and the particular ion that is typically determined from experiment and C is the localized concentration of a particular ion.  $J_d$  is the current density in  $A/cm^2$ .

Ions are charged particles, which means that they are sensitive to electric fields and that they move consequently. Different ions present a different atomic number and, therefore, a different mass and dimension. For this reason different ion species shows a different *mobility* when they encounter an electric field in solution. *Mobility* is defined as the maximum velocity that a given ion can reach in a specific solution when a unity electric field is constantly applied to it. The ionic flux of the *i*<sup>th</sup> ion in a given solution is given by the law

$$\overline{J_e} = -u_i \frac{Z_i}{|Z_i|} C_i \nabla \Phi \tag{2.3}$$

where  $u_i$  is the  $i^{th}$  ion mobility,  $Z_i$  is its valence,  $C_i$  is its localized concentration and  $\nabla \Phi$  is the applied electric field in the particular point of interest. Even in this case the flux represents the number of ions flowing through a unit area cross section.

The diffusion constant, D, and the mobility, u, are related by Einstein's law

$$D_i = \frac{u_i RT}{|Z_i|F} \tag{2.4}$$

for the  $i^{th}$  ion species where R is the gas constant, F is Faraday's constant and T is the absolute temperature.

The resulting flux of ions that arises from the superposition of the two phenomena for the  $i^{th}$  ion species is

$$\overline{J_i} = \overline{J_d} + \overline{J_e} = -\left(u_i \frac{Z_i}{|Z_i|} C_i \nabla \Phi + D \nabla C_i\right)$$

(2.5)

which, combined with (2.4), gives the Nernst-Planck equation

$$\overline{J_i} = -D\left(\frac{Z_i C_i F}{RT} \nabla \Phi + \nabla C_i\right). \tag{2.6}$$

This value can be multiplied by the number of charges in each mole  $Z_iF$  to obtain a current density

$$\overline{J_i} = Z_i F \overline{J_i} \tag{2.7}$$

which represents the current per unit of area of the cross section that the ion flux goes through.

#### 2.3 The Parallel Conductance Model of the Membrane

The potential difference,  $V_m$ , between the internal and the external surfaces of the membrane is called the *transmembrane potential* and is defined as

$$V_m = \Phi_i - \Phi_e. \tag{2.8}$$

The value of this potential difference at resting condition varies between different types of excitable cells. As a reference we can assume that a typical value for  $V_m$  is - 60 mV and that it does not exceed  $\pm 100 \text{ mV}$ . Even if this is a relatively low voltage, the value of the electric field across the membrane is very high due to the very thin layer over which this potential difference is measured, i.e. the membrane thickness which is well below 100 Å.

# 2.3.1 Membrane Permeability and Nernst Equilibrium

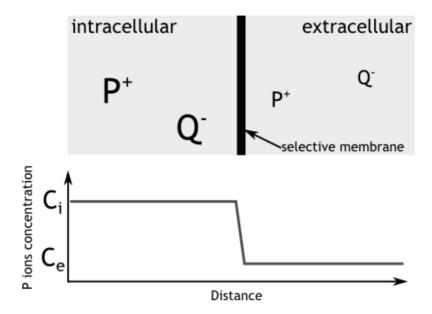

Figure 2.2 shows a typical concentration cell useful to study the dynamics of ions moving across two regions of a volume with different concentrations. Ions are assumed to be equally concentrated in their region, the membrane is permeable only to one ion species P<sup>+</sup> while the other species Q<sup>-</sup> cannot pass through.

Assuming that at the time  $t_0$ the P and Q ion concentration in the same compartment are the same, the transmembrane voltage  $V_m$  is 0 V because on each side of the membrane there is the same amount of positive and negative charges. As time passes,  $P^+$  ions start to move from the intracellular to the extracellular compartment because of the concentration difference.  $V_m$  is then given by

$$V_m = \Phi_i - \Phi_e = \Delta P^+ / C_m \tag{2.9}$$

where  $C_m$  is the membrane capacitance and  $\Delta P^+$  is the number of  $P^+$  ions that moved from the intracellular to the extracellular space.

Figure 2.2 A permeable membrane separates two volumes called intracellular and extracellular. In both volumes two hypothetical ion species are present,  $P^+$  and  $Q^-$ , with  $P^+$  and  $Q^-$  ion concentration in the intracellular area being larger than the one in the extracellular area. The selective membrane is permeable only to  $P^+$  ions.

Assuming the membrane to be a perfect insulator, we have that the electric field across the membrane is

$$E = \frac{V_m}{d} = \frac{\Delta P^+}{C_m d} \tag{2.10}$$

where d is the membrane thickness. The relation above affirms that as more and more  $P^+$  ions leave the intracellular volume, an electric field if formed whose direction is from the extracellular toward the intracellular space. This field clearly works against the movement of positive charges due the concentration difference until the two different phenomena reach an equilibrium characterized from the total current density  $\overline{J_p}$  for the ion  $P^+$  to be null. From (2.7) we have that for  $\overline{J_p} = 0$

$$\nabla C_p = -\frac{Z_p C_p F}{RT} \nabla \Phi. \tag{2.11}$$

Considering only the dimension perpendicular to the membrane surface and integrating the relation above and transforming the natural logarithm to the base 10 logarithm we obtain the relation between the transmembrane potential  $V_m$  and the concentration at the equilibrium, also known as the *Nernst Potential*, for the  $P^+$  ion:

$$V_m^{eq} = \frac{58}{Z_p} log_{10} \left( \frac{\left[ C_p \right]_{external}}{\left[ C_p \right]_{internal}} \right)$$

(2.12)

with  $V_m^{eq}$  being typically around 100 mV.

For the main ion species involved in the transmission of APs we can say that at equilibrium they have a specific *Nernst Potential* that combines to give the overall resulting  $V_m$ . We can call these values  $E_{Na}$ ,  $E_K$  and  $E_{Cl}$  that are based on typical measurements as shown in Table 2.1, which are positive, negative and negative, respectively (the chloride has an external concentration that is larger than the intracellular, but its valence is -1).

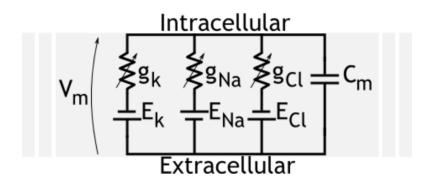

Assuming that channels in the membrane are selective, i.e. are permeable under certain conditions to only one species of ion, we can say that, based on the number of channels opened at a certain point in time for a given ion, the  $i^{th}$  ion experiences a given transmembrane conductivity which is a quantitative indication of how many ions can flow through the membrane at a given time t. The superposition of this consideration for the three species gives the *equivalent parallel conductance model* for the cell membrane (Figure 2.3).

Table 2.1 Typical experimental intracellular and extracellular concentrations of the main ion species from a squid axon nerve [13].

|                       | Intracellular mM | Extracellular mM |

|-----------------------|------------------|------------------|

| <i>K</i> <sup>+</sup> | 397              | 20               |

| Na <sup>+</sup>       | 50               | 437              |

| Cl                    | 40               | 556              |

Figure 2.3 The parallel conductance equivalent model of the cell membrane.  $C_m$  is the membrane capacitance per cm<sup>2</sup>,  $g_k$ ,  $g_{Na}$  and  $g_{Cl}$  the membrane conductance for the respective ion and  $E_K$ ,  $E_{Na}$  and  $E_{Cl}$  the Nernst Potential for the single species.  $E_K$ ,  $E_{Na}$  and  $E_{Cl}$  in this figure have to be intended as positive numbers and the polarity of the voltage source gives the direction. The actual  $V_m$  is the result of the superposition of the three branches.

The current on each branch is given by

$$I_i = g_i(V_m - E_i) (2.13)$$

where  $E_i$  is considered with the proper sign. At the same time the current  $I_c$  through the capacitance is

$$I_c = C_m \frac{dV_m}{dt} {.} {(2.14)}$$

At resting condition the voltage  $V_m$  is constant,  $I_c$  is null and the total net current must be zero. This condition gives:

$$I_m = 0 = I_{Na} + I_K + I_{Cl} (2.15)$$

which when combined with (2.13) for each ion species gives the *parallel conductance* equation for the resting transmembrane potential

$$V_m^{rest} = \frac{g_k E_k + g_{Cl} E_{Cl} + g_{Na} E_{Na}}{g_k + g_{Cl} + g_{Na}}.$$

(2.16)

#### 2.4 Membrane Structure and Channels Conductance