# University of South Florida Scholar Commons

Graduate Theses and Dissertations

Graduate School

2011

# Stress-Strain Management of Heteroepitaxial Polycrystalline Silicon Carbide Films

Christopher William Locke

University of South Florida, clocke@mail.usf.edu

Follow this and additional works at: http://scholarcommons.usf.edu/etd

Part of the American Studies Commons, Electrical and Computer Engineering Commons, and the Materials Science and Engineering Commons

#### Scholar Commons Citation

Locke, Christopher William, "Stress-Strain Management of Heteroepitaxial Polycrystalline Silicon Carbide Films" (2011). *Graduate Theses and Dissertations*.

http://scholarcommons.usf.edu/etd/3211

This Dissertation is brought to you for free and open access by the Graduate School at Scholar Commons. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact scholarcommons@usf.edu.

#### Stress-Strain Management of Heteroepitaxial Polycrystalline Silicon Carbide Films

by

### Christopher Locke

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Department of Electrical Engineering

College of Engineering

University of South Florida

Major Professor: Stephen E. Saddow, Ph.D.

Andrew M. Hoff, Ph.D.

Sylvia Thomas, Ph.D.

Rasim Guldiken, Ph.D.

Andrea Severino, Ph.D.

Date of Approval: March 28, 2011

Keywords: Silicon Carbide, Heteroepitaxy, Residual Stress, Chemical Vapor Deposition, Polysilicon

Copyright © 2011, Christopher Locke

#### **ACKNOWLEDGEMENTS**

I have reached a milestone in my life that would not have been realized without the nurturing support of those whom believed in me. First, I would like to thank my parents, Pete and Sandy, and sisters, Kimberly and Sara, who have always been at my side providing the unconditional love and support which has fostered my spirit to drive through the difficult times. I would like to thank my advisor, Dr. Stephen Saddow, who believed in me and supported me through my graduate years, both as mentor and friend. I have been truly blessed to have been guided by such a magnificent person. A great deal of appreciation is owed to Dr. Andrew Hoff who has helped with my research and has been so generous to offer me a teaching assistant position. Many thanks are owed to Dr. Sylvia Thomas, Dr. Andrea Severino, Dr. Guldiken, and Dr. Ashok Kumar for their much appreciated support. I would like to thank my friend Dr. Chris Frewin for his unyielding loyalty and his gracious generosity that helped me get to this milestone. I would like to express my gratitude for the invaluable services and advice that Robert Tufts and Richard Everly have provided me over the years. Many thanks to Dr. Francesco LaVia, Ruggero Anzalone, Corrado Bongiorno, Massimo Camarda, at IMM-CNR. I would like to extend my thanks to Dr. John Bumgarner and Dr. Priscila Spagnol for their valuable contribution during the early development of the polysilicon-on-oxide stack. I would like to thank Dr. Submaranian "Subbu" Krishnan and Dr. Sunil Arya for offering their services and facility. And a final heartfelt thank you to my engineering family- the SiC Group!.

### TABLE OF CONTENTS

| LIST OF TAI | BLES    |                                                         | iii |

|-------------|---------|---------------------------------------------------------|-----|

| LIST OF FIG | URES    |                                                         | iv  |

| ABSTRACT    |         |                                                         | vii |

| CHAPTER 1   | SILICO  | ON CARBIDE: A MATERIAL FOR                              |     |

|             |         | ECHANICAL SYSTEMS (MEMS)                                | 1   |

| 1.1         | Introdu | · · · · · · · · · · · · · · · · · · ·                   | 1   |

| 1.2         |         | epitaxial Silicon Carbide                               | 4   |

| 1.2         |         | Why Heteroepitaxial Silicon Carbide?                    | 6   |

|             |         | Fabrication of Silicon Carbide MEMS                     | 8   |

|             |         | Stress-Induced Deformation of Heteroepitaxial Films     | 11  |

| 1.3         |         | icon-on-Oxide Substrates for Heteroepitaxial Silicon    |     |

|             | Carbide | <u> •</u>                                               | 12  |

| 1.4         | Influen | ice of Polysilicon Seed-Layer Thickness on Silicon      |     |

|             |         | e Film Stress                                           | 14  |

| 1.5         | Overvi  | ew of the Organization of This Dissertation             | 16  |

| CHAPTER 2   | HETEI   | ROEPITAXIAL SILICON CARBIDE STRUCTURE,                  | 17  |

| GROWTH, A   | ND THI  | IN FILM MECHANICS                                       |     |

| 2.1         | Crystal | Structure of Silicon Carbide                            | 17  |

| 2.2         | Overvi  | ew of CVD                                               | 19  |

|             | 2.2.1   | Early Stages of CVD Film Growth                         | 22  |

| 2.3         | Overvi  | ew of Heteroepitaxial Defects                           | 24  |

|             | 2.3.1   | Line Defects                                            | 24  |

|             | 2.3.2   | Planar Defects                                          | 26  |

|             | 2.3.3   | Grain Boundaries                                        | 32  |

| 2.4         | Structu | ral Evolution of Polycrystalline Thin Films             | 33  |

| 2.5         | Mechai  | nical Properties of Thin Films                          | 34  |

|             | 2.5.1   | Sources of Stresses in Thin Films                       | 35  |

|             | 2.5.2   | Stress Control of Polycrystalline Silicon Carbide Films |     |

|             |         | via CVD Process Parameters                              | 37  |

|             | 2.5.3   | Analysis of Thin Film Stress                            | 45  |

|             |         | 2.5.3.1 Stoney Equation                                 | 46  |

|             |         | 2.5.3.2 Cantilever Deflection                           | 50  |

|             |         | 2.5.3.3 Planar Rotating Beam                            | 53  |

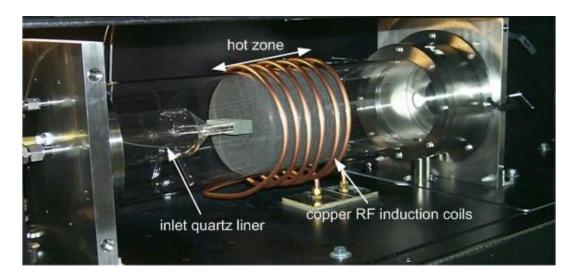

| 2.6              | CVD Reactor Hardware                                            | 55  |

|------------------|-----------------------------------------------------------------|-----|

| CHAPTER 3        | DEVELOPMENT OF LOW-TEMPERATURE POLY-SiC                         |     |

| <b>GROWTH PR</b> | OCESS FOR POLY-Si-ON-OXIDE SUBSTRATES                           | 58  |

| 3.1              | Motivation for Reducing Process Temperature                     | 59  |

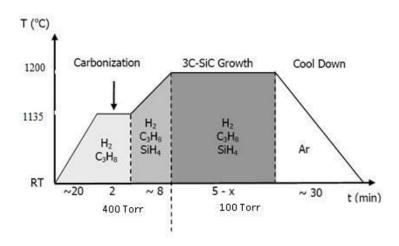

| 3.2              | Low Temperature Process Development                             | 60  |

|                  | 3.2.1 Low Temperature Baseline Process                          | 61  |

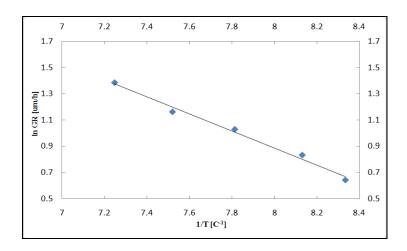

|                  | 3.2.2 Optimized Low Temperature Process                         | 64  |

| 3.3              | Poly-SiC Growth on Poly-Si-on-Oxide Substrates                  | 67  |

|                  | 3.3.1 Motivation for 3C-SiC Growth on Oxide Layers              | 68  |

|                  | 3.3.2 Deposition of Poly-Si Layer on SiO <sub>2</sub> / (111)Si | 70  |

|                  | 3.3.3 Polysilicon Carbide Growth Process                        | 71  |

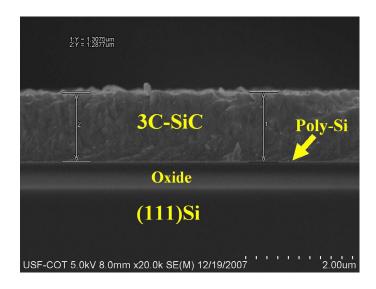

| 3.4              | Analysis of the Poly-SiC-on-Oxide Film                          | 73  |

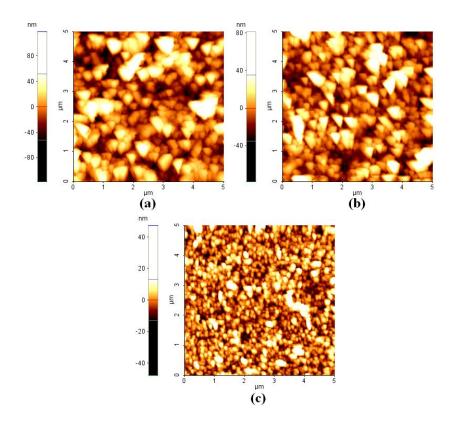

|                  | 3.4.1 AFM Analysis                                              | 73  |

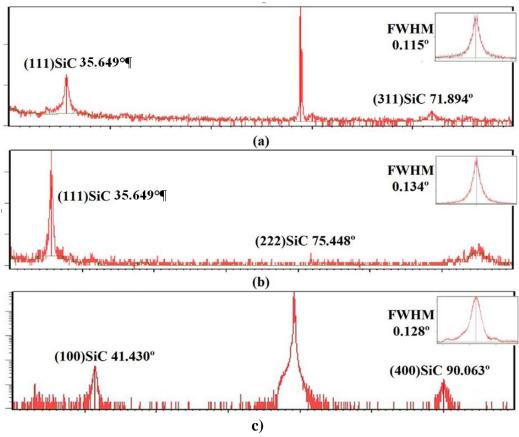

|                  | 3.4.2 XRD Analysis                                              | 75  |

| 3.5              | Summary                                                         | 77  |

| CHAPTER 4        | INFLUENCE OF POLYSILICON SEED-LAYER THICKNESS                   |     |

| ON POLY-Si       | C RESIDUAL STRESS                                               | 79  |

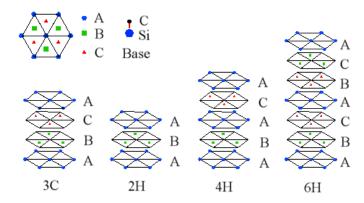

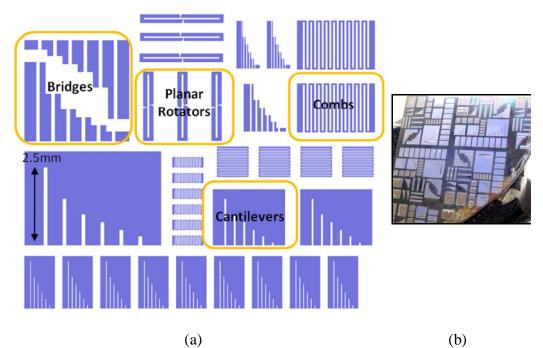

| 4.1              | Fabrication of SiC MEMS on an Oxide Release Layer               | 81  |

|                  | 4.1.1 Test Growth on Patterned Polysilicon-on-Oxide             |     |

|                  | Substrates                                                      | 82  |

|                  | 4.1.2 Poly-SiC MEMS Fabrication Procedure                       | 84  |

| 4.2              | Film Morphology                                                 | 87  |

| 4.3              | Stress-Strain Analysis                                          | 89  |

| CHAPTER 5        | SUMMARY AND FUTURE WORKS                                        | 96  |

| 5.1              | Summary                                                         | 96  |

| 5.2              | Future Work                                                     | 98  |

|                  | 5.2.1 3C-SiC Growth on SOI Substrates                           | 99  |

|                  | 5.2.2 Residual Stress Characterization                          | 100 |

|                  | 5.2.3 MEMS Fabrication                                          | 101 |

| REFERENCE        | S                                                               | 103 |

| APPENDICE        | S                                                               | 111 |

| Annen            | dix A Mechanics of the Biaxial Deflection of a Plate            | 112 |

## LIST OF TABLES

| Table 1.1 | Properties of commonly used SiC polytypes compared with Si and Diamond.                                   | ompared with Si 3 |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------|-------------------|--|--|

| Table 4.1 | Maximum stress gradient values from cantilever deflection measurements acquired via optical profilometry. | 95                |  |  |

## LIST OF FIGURES

| Figure 1.1  | Illustration of the affect of lattice mismatch in heteroepitaxy                                                                         | 5  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1.2  | Schematic representation of antiphase domain boundary (APB) annihilation with film thickness                                            | 7  |

| Figure 1.3  | Fabrication of a free-standing cantilever                                                                                               | 10 |

| Figure 2.1  | Four examples of SiC polytype stacking sequences                                                                                        | 18 |

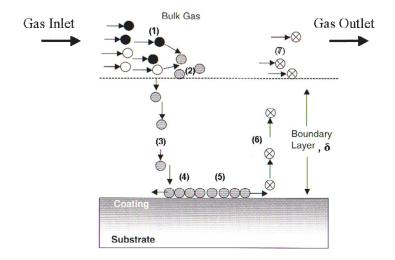

| Figure 2.2  | Schematic diagram of mechanistic steps which occur during the CVD process                                                               | 20 |

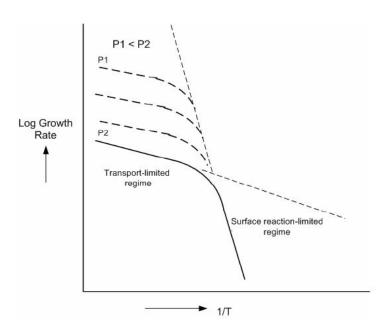

| Figure 2.3  | Generalized process trend showing the dependence of process temperature and pressure on growth rate via CVD                             | 21 |

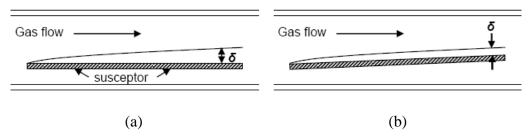

| Figure 2.4  | Illustration of the boundary layer, $\delta$ , in a horizontal reactor with: (a) flat susceptor design, and (b) tilted susceptor design | 22 |

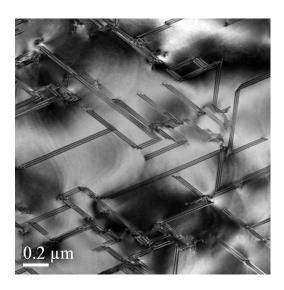

| Figure 2.5  | Stacking faults revealed in a (100)3C-SiC film via PV-TEM. SF density estimated to be $\sim 5 \times 10^4$ cm <sup>-1</sup>             | 27 |

| Figure 2.6  | Example of hetero defects in (100)3C-SiC from X-TEM                                                                                     | 28 |

| Figure 2.7  | Schematic representation of micro-twin defect in SiC on Si heteroepitaxy                                                                | 29 |

| Figure 2.8  | Micro-twinned crystal defect (dark cluster in center of micrograph) observed with plan-view TEM (PV-TEM)                                | 29 |

| Figure 2.9  | Geometrical consideration of the formation of an APB when SiC is grown on (100)Si substrate with an atomic step                         | 30 |

| Figure 2.10 | Stacking fault generation schematic showing the error in crystal layer formation resulting in a stacking fault defect                   | 31 |

| Figure 2.11 | Evolution of grain structure with film growth                                                                                           | 34 |

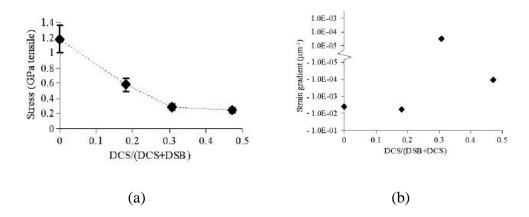

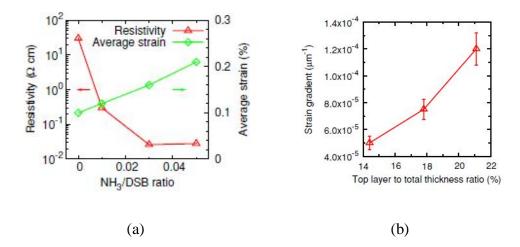

| Figure 2.12 | Relationship of the DCS fraction in the gas mixture to, (a) the residual film stress and, (b) the strain gradient                                          | 38 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.13 | Results using DCS to control residual stress in poly SiC films                                                                                             | 39 |

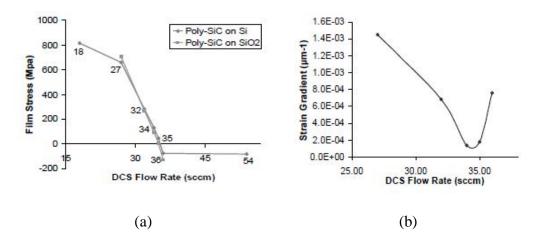

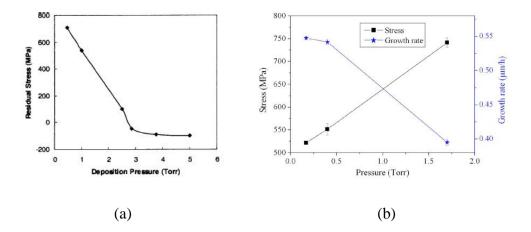

| Figure 2.14 | Residual stress versus deposition pressure trends for poly-SiC                                                                                             | 42 |

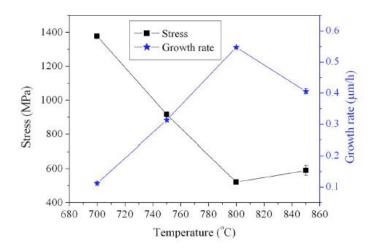

| Figure 2.15 | Poly-SiC residual film stress and growth rate vs. temperature at 0.17 Torr deposition pressure                                                             | 43 |

| Figure 2.16 | The use of tailored $N_2$ doping during poly-SiC deposition to control film strain                                                                         | 45 |

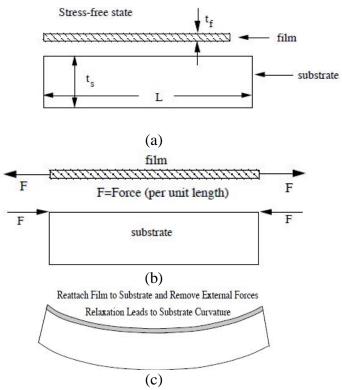

| Figure 2.17 | The generation of biaxially deformed film-substrate system from, (a) an initially stress-free system                                                       | 47 |

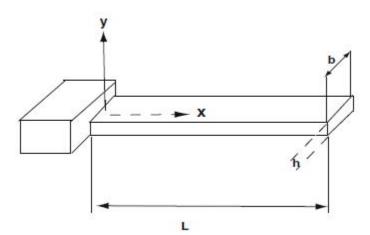

| Figure 2.18 | Illustration of a cantilever structure with length, "L", width," b", and thickness, "h"                                                                    | 50 |

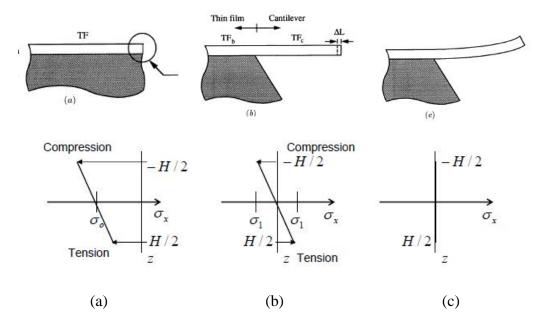

| Figure 2.19 | Stress states present in a thin film cantilever far from the anchor point                                                                                  | 52 |

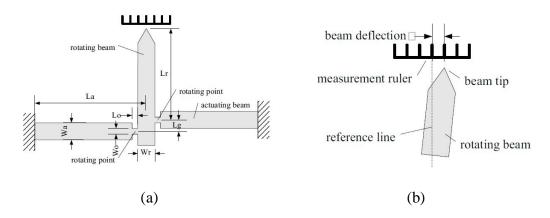

| Figure 2.20 | Schematic illustration of a conventional planar micro-rotating structure (Drieenhuizen 1993) used to measure strain gradient in a thin film                | 54 |

| Figure 2.21 | Photograph of the MF2 CVD horizontal reactor at USF                                                                                                        | 57 |

| Figure 3.1  | Initial baseline low temperature (1200°C) CVD growth process schedule                                                                                      | 62 |

| Figure 3.2  | Plot of the deposition rate vs. inverse temperature using the optimized low-temperature/ low pressure growth process at various growth temperatures        | 67 |

| Figure 3.3  | AFM micrographs of the surfaces of the SiC deposition grown on (a) poly-Si/SiO $_2$ / (111)Si, (b) (111)Si, and (c) (100)Si                                | 74 |

| Figure 3.4  | Cross-section SEM micrograph of a 3C-SiC film grown on the poly-Si/ $SiO_2$ / (111)Si compliant stack                                                      | 75 |

| Figure 3.5  | XRD $\theta$ -2 $\theta$ diffraction surveys for the 3C-SiC films grown on (a) poly-Si/SiO <sub>2</sub> / (111)Si, (b) (111)Si, and (c) (100)Si substrates | 76 |

| Figure 4.1  | Stress as a function of deposition temperature for polysilicon films                                                                                       | 80 |

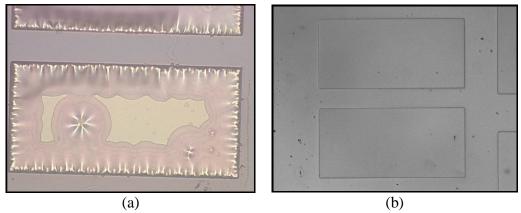

| Figure 4.2  | (a) Mask layout details of the first test mask consisting of cantilevers/ combs, bridges, and planar rotators of various dimensions                                                                                          | 82  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.3  | Optical micrographs of 3C-SiC grown on the patterned poly-Si/SiO $_2$ / (111)Si substrates                                                                                                                                   | 83  |

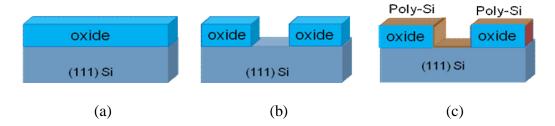

| Figure 4.4  | Summary of the patterning of anchor points for the SiC-based MEMS structures prior to epitaxial growth of the 3C-SiC                                                                                                         | 85  |

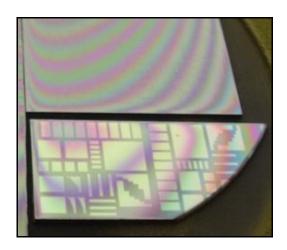

| Figure 4.5  | A polysilicon-on-oxide substrate after poly-SiC deposition                                                                                                                                                                   | 86  |

| Figure 4.6  | Optical image of the patterned and dry-etched poly-SiC                                                                                                                                                                       | 87  |

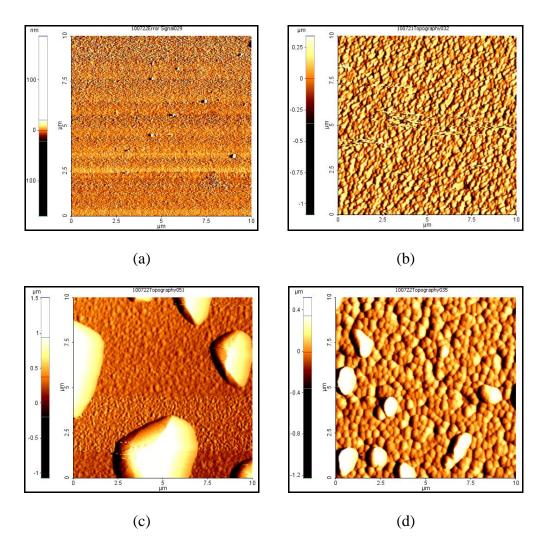

| Figure 4.7  | Top: Atomic force microscopy (AFM) scans of the polysilicon seed layer (a) 20nm thick and, (b) 100nm thick                                                                                                                   | 89  |

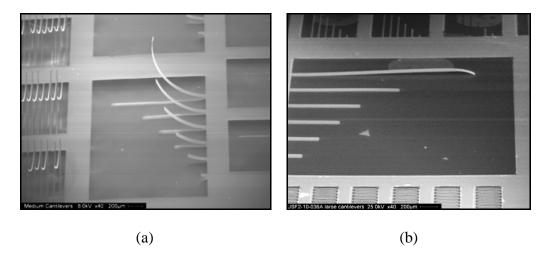

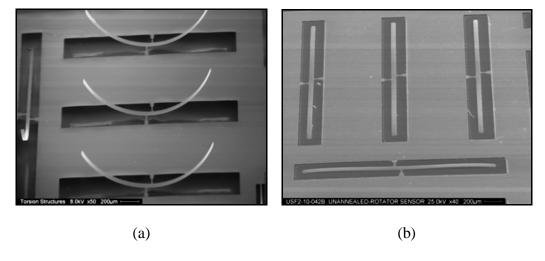

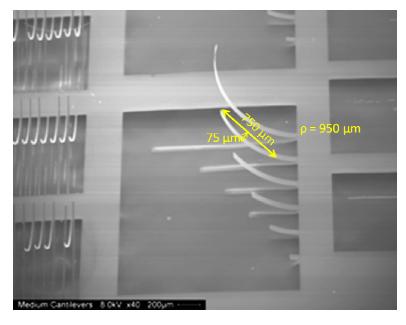

| Figure 4.8  | SEM images viewed from a 45° tilt of poly-SiC cantilevers fabricated from poly-SiC grown on polysilicon-on-oxide using a (a) 20 nm thick seed layer and, (b) 100 nm thick seed layer                                         | 91  |

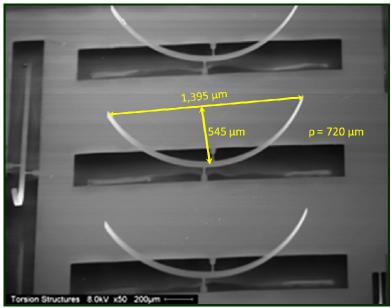

| Figure 4.9  | SEM images taken at a 45° tilt angle of planar rotator structures displaying the stress gradients present in (a) poly-SiC film grown on a 20 nm polysilicon seed layer (b) poly-SiC grown on a 100 nm polysilicon seed layer | 91  |

| Figure 4.10 | SEM image of the cantilevers from Figure 4.8(a) and the planar rotator structures from Figure 4.10(a)                                                                                                                        | 92  |

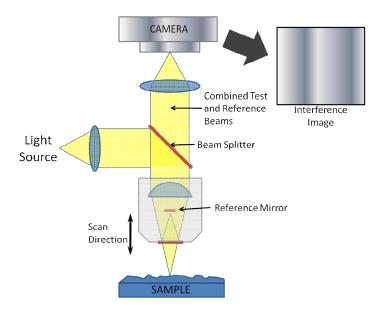

| Figure 4.11 | Schematic of an optical profilometer                                                                                                                                                                                         | 94  |

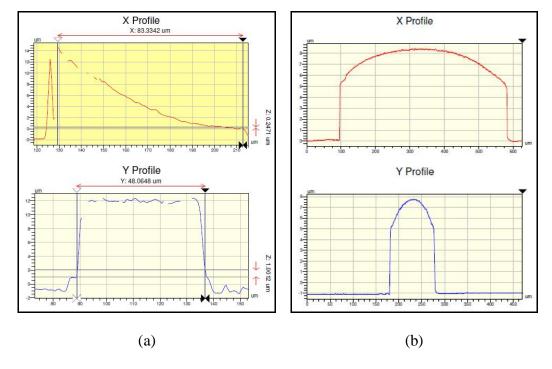

| Figure 4.12 | Optical profilometer data of poly-SiC cantilevers micromachined from poly-SiC grown from (a) a 20 nm poly-Si seed layer and, (b) a 100 nm thick poly-Si seed layer                                                           | 95  |

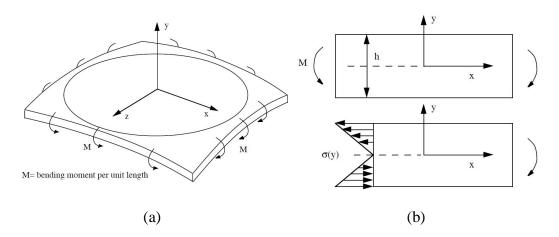

| Figure A.1  | (a) Schematic of a bending moment applied to a plate and a cross-section diagram (b) showing the resulting stress gradient                                                                                                   | 112 |

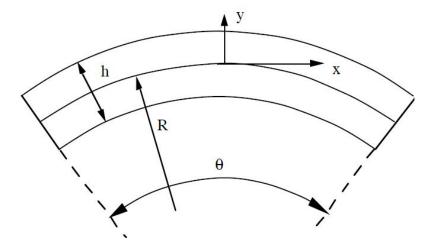

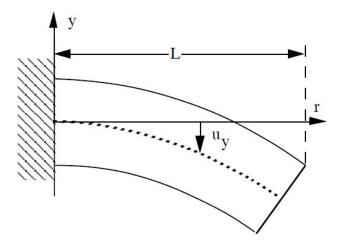

| Figure A.2  | Geometric parameters defining a simply bent beam                                                                                                                                                                             | 115 |

| Figure A.3  | Cantilever deformed by a bending moment                                                                                                                                                                                      | 116 |

#### **ABSTRACT**

Silicon carbide (SiC) is one of the hardest known materials and is also, by good fortune, a wide bandgap semiconductor. While the application of SiC for high-temperature and high-power electronics is fairly well known, its utility as a highly robust, chemically-inert material for microelectrical mechanical systems (MEMS) is only beginning to be well recognized. SiC can be grown on both native SiC substrates or on Si using heteroepitaxial growth methods which affords the possibility to use Si micromachining methods to fabricate advanced SiC MEMS devices.

The control of film stress in heteroepitaxial silicon carbide films grown on polysilicon-on-oxide substrates has been investigated. It is known that the size and structure of grains within polycrystalline films play an important role in determining the magnitude and type of stress present in a film, i.e. tensile or compressive. Silicon carbide grown on LPCVD polysilicon seed-films exhibited a highly-textured grain structure and displayed either a positive or negative stress gradient depending on the initial thickness of the polysilicon seed-layer. In addition a high-quality (111) oriented 3C-SiC on (111)Si heteroepitaxial process has been developed and is reported. SiC MEMS structures, both polycrystalline (i.e., poly-3C-SiC) and monocrystalline (i.e., 3C-SiC) were realized using micromachining methods. These structures were used to extract the stress properties of the films, with a particular focus on separating the gradient and uniform stress components.

# CHAPTER 1: SILICON CARBIDE: A MATERIAL FOR MICROELECTROMECHANICAL SYSTEMS (MEMS)

#### 1.1 Introduction

Although silicon is a well-suited material for a wide range of sensor and actuator applications, it is limited for electronic devices at temperatures below 250°C. In addition its mechanical properties begin to degrade at temperatures above 600°C (Mehregany, 1998) which limit its use for high temperature and harsh environment applications. Consequently when silicon-based MEMS technology is used in harsh environments, the expensive and bulky cooling and packaging systems that need to be implemented in order to keep the devices within operating limits are expensive or sometimes prohibitive. As the demand grows to implement cost-saving and space-saving microsensor and microactuator technologies in harsh environments, one must look for other material options that can satisfy the requirement of long-term device survivability and lowproduction costs. To meet the demands for high-temperature ( $\geq 350^{\circ}$ C) MEMS, there is a need for an electronic material exhibiting a wide bandgap, good mechanical (and chemical) stability, and good thermal stability over a large temperature range. An ideal material platform for harsh-environment MEMS would also exhibit an extensive range of robustness that would withstand a multitude of environments. It would be chemically inert to corrosive attack, it would exhibit outstanding wear resistance, it would

demonstrate radiation-hardness (i.e., rad-hard), and it could be biologically implantable. Although this may appear to be an unrealistic "wish-list", there are material candidates that seem to meet these demanding criteria.

Diamond is one such candidate that is currently being explored. It is the hardest known natural material, scoring a 10 on the Mohs hardness scale. It has the highest thermal conductivity of any known material; five times greater than silver, the second highest thermal conductor. It has a wide band gap and can be doped to exhibit semiconductor properties. It has excellent thermal and mechanical stability, except in high-temperature (≥ 700°C) oxygen environments, in which it readily oxidizes (i.e., surface turns to graphite). This drawback excludes it for use as a material for combustion microsensors. Therefore diamond-based MEMS have found limited use, mostly in low-temperature RF applications and in biomedical applications as a coating for Si-based sensors and devices.

Silicon Carbide (SiC) is another candidate that appears to fulfill the requirements of a MEMS platform material for a multitude of harsh environmental conditions. It has long been recognized as a semiconductor with excellent physical, electrical and chemical characteristics (see Table 1.1). It has excellent mechanical and electrical stability at high temperatures. It is inert to nearly all wet chemistry, and it can only be etched by molten alkaline hydroxides at temperatures ≥600°C. Silicon carbide doesn't melt, but sublimes at temperatures exceeding 1800°C. Silicon carbide demonstrates excellent wear resistance, having a 9.15 wear resistance rating as compared to 10 for diamond. It is the third hardest known material, only diamond and boron nitride exceed it. Silicon carbide can be thermally oxidized to form a passivating SiO₂ layer, although the oxidation rate is

slow when compared to silicon. Surface passivation using a hydrogen-terminated surface has been shown to form flatband conditions for several hours (C. Coletti 2008). 100mm diameter silicon carbide wafers grown from bulk crystals are commercially available from several manufacturers; 150mm wafers with defect densities less than 10 cm<sup>-2</sup> have been recently reported. Monocrystalline and polycrystalline silicon carbide has been epitaxially grown on silicon substrates up to 150mm in diameter.

Table 1.1 Properties of commonly used SiC polytypes compared with Si and Diamond. (Casady and Johnson 1996) (Harris 1995).

| and Diamond. (Casady and                                                     |                      | , `                                                                 |                                                                      |                                                                    |                                                                       |

|------------------------------------------------------------------------------|----------------------|---------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|

| Property                                                                     | 4H-SiC               | 6H-SiC                                                              | 3C-SiC                                                               | Si                                                                 | Diamond                                                               |

| Energy bandgap at 300K                                                       | 3.20                 | 3.00                                                                | 2.29                                                                 | 1.12                                                               | 5.45                                                                  |

| Intrinsic Carrier<br>Concentration at 300K<br>(cm <sup>-3</sup> )            | 5x10 <sup>-9</sup>   | 1.6x10 <sup>-6</sup>                                                | 1.5x10 <sup>-1</sup>                                                 | 1x10 <sup>10</sup>                                                 | ~10 <sup>-27</sup>                                                    |

| Critical breakdown electric field (MV/cm)                                    | 2.2                  | 2.5                                                                 | 2.12                                                                 | 0.25                                                               | 1-10                                                                  |

| Saturated electron drift velocity (x 10 <sup>7</sup> cm/s)                   | 2.0                  | 2.0                                                                 | 2.5                                                                  | 1.0                                                                | 1.5                                                                   |

| Electron mobility (cm <sup>2</sup> /V-s)                                     | 1000                 | 600                                                                 | 800                                                                  | 1450                                                               | 480                                                                   |

| Hole mobility (cm <sup>2</sup> /V-s)                                         | 115                  | 100                                                                 | 40                                                                   | 470                                                                | 1600                                                                  |

| Thermal Conductivity at 300K (W cm <sup>-1</sup> K <sup>-1</sup> )           | 3.7                  | 3.6                                                                 | 3.6                                                                  | 1.49                                                               | 6-20                                                                  |

| Coefficient of Thermal Expansion at 300K (10 <sup>-6</sup> K <sup>-1</sup> ) | 4.3 ⊥c<br>4.7 ∥c     | 4.3 ⊥c<br>4.7 ∥c                                                    | 3.2                                                                  | 3.0                                                                | 1.0                                                                   |

| Lattice constant (a, c in Å)                                                 | a=3.0730<br>c=10.053 | a=3.0806<br>c=15.1173                                               | a=4.3596                                                             | a=5.430                                                            | a=3.5668                                                              |

| Elastic coefficient* (GPa) *calculated                                       | C <sub>44</sub> =600 | C <sub>11</sub> =500<br>C <sub>12</sub> =92<br>C <sub>44</sub> =168 | C <sub>11</sub> =352<br>C <sub>12</sub> =120<br>C <sub>44</sub> =233 | C <sub>11</sub> =167<br>C <sub>12</sub> =65<br>C <sub>44</sub> =80 | C <sub>11</sub> =1079<br>C <sub>12</sub> =124<br>C <sub>44</sub> =578 |

#### 1.2 Heteroepitaxial Silicon Carbide

Epitaxy is the growth of a thin layer on a crystal substrate in which the substrate is a template for the growth such that the proper atomic arrangement is achieved.

Heteroepitaxy is the growth of an epitaxial layer on a seed crystal of a different crystal type. Cubic SiC, more commonly referred to as 3C-SiC, may be heteroepitaxially grown on Si substrates. Since the growth of single crystal, large-area, bulk 3C-SiC crystals has not been demonstrated, heteroepitaxy is needed to grow 3C-SiC crystals. However, the near 20% lattice mismatch between Si and SiC typically leads to an epitaxial film that is highly defective and therefore not suitable for electronic devices. This is generally because interfacial defects propagate into the 3C-SiC device layer and result in high leakage currents in 3C-SiC/Si devices. Indeed, the issues impeding the growth of high quality, monocrystalline 3C-SiC/Si heteroepitaxial films have proven to be so difficult to overcome that many groups have abandoned 3C-SiC/Si. In this thesis, we aim to use a novel substrate alongside a tailored stoichiometric bilayer structure to mitigate film stresses arising from defects with the goal of developing device-quality 3C-SiC/Si layers.

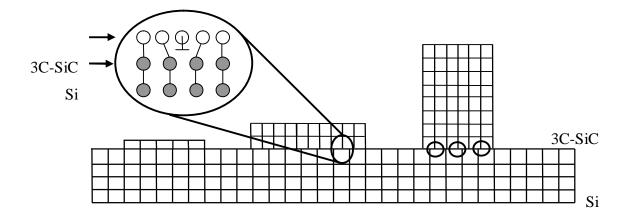

Figure 1.1 Illustration of the effect of lattice mismatch in heteroepitaxy. The  $\perp$  symbol denotes the location of a missing row of atoms which is known as a line defect. Note the stretched and compressed covalent bonds at the interface resulting from the lattice mismatch between the two crystals. [ref]

As seen in the above figure, there is a strain in the epilayer from an attempt by the epilayer (a  $_{3\text{C-SiC}} = 4.3596\text{Å}$ ) to accommodate the substrate's lattice constant (a<sub>Si</sub> = 5.43095Å) (Harris 1995). The attempt to accommodate the mismatch not only produces crystal defects, but these defects in the epitaxial layer have a mosaic morphology in the case of the (100)3C-SiC/(100)Si system. While a carbonization step is normally employed which converts the starting Si surface to SiC and acts as a buffer layer to reduce the stress, this does not completely accommodate the lattice mismatch. With this buffer layer, there are still a fair amount of dislocations which must be reduced if 3C-SiC is to be useful for electronic devices such as MOSFETs.

One of the most successful methods to grow 3C-SiC is by chemical vapor deposition (CVD). The standard precursor chemistry typically used is the silane-propane-hydrogen gas system. Although extensive work has been performed since the early 1980's, there is still a lack of good quality 3C-SiC on Si epitaxial material. While

growth rates up to 40  $\mu$ m/h on undulant Si (100) substrates by cold-wall CVD have been reported to produce SiC substrates with near bulk quality, defects originating from the undulant substrate persist (Nagasawa, Yagi and Kawahara 2002). More relevant for device manufacturing were studies performed using hot-wall CVD, which resulted in growth rates up to 50  $\mu$ m/h (Reyes, spring MRS 2006). While these films were relatively flat (i.e., low residual stress) they were far from 'defect free' which is generally a minimum condition to allow for electronic devices to be successfully realized.

#### 1.2.1 Why Heteroepitaxial Silicon Carbide?

Unlike the more commonly studied hexagonal forms of SiC, 4H-SiC and 6H-SiC, 3C-SiC has the ability to be heteroepitaxially grown on Si, allowing for the growth of SiC on large area substrates. Si wafers are inexpensive and are currently manufactured as large as 12 inches in diameter. 3C-SiC could be epitaxially grown on large-area Si wafers to produce seeds for bulk growth. Currently, only bulk SiC is available in the 4H and 6H polytype with boule sizes capable of producing a maximum 4 inch size wafer at a cost of nearly \$2000-\$2500 per wafer (Cree, Inc. 2009). Furthermore, bulk SiC grown by physical vapor transport contains screw dislocation densities near 10-200 cm<sup>-2</sup> that can penetrate into the epitaxial layer during growth and lead to device failure. Because of the cubic crystal structure of 3C-SiC, these screw dislocations are energetically unfavorable and do not in occur in 3C heteroepitaxy.

Heteroepitaxy opens opportunities for silicon carbide growth on a variety of novel substrates in order to exploit or suppress certain attributes. In order to reduce the detrimental effects stemming from the coefficient of thermal expansion mismatch between SiC and Si,

3C-SiC has been grown on Si<sub>x</sub>Ge<sub>(1-x)</sub> substrates. 3C-SiC films have also been grown on silicon substrates patterned with inverted nanopyramids to successfully reduce defect propagation via defect annihilation within the films (D'Arrigo 2010), see Figure 1.2. Fabrication of devices, e.g. MEMS, can be facilitated by growing polycrystalline SiC on sacrificial oxide release layers by using a polysilicon seed layer. The oxide layer can be etched with hydrofluoric acid (HF) to release the patterned SiC MEMS structures. This avoids problems that silicon wet etchants may present when releasing SiC directly from a Si substrate- masking effects due to bubble formation on the substrate surface and the increased risk of structural damage due to agitation, especially with submicron thick films. The polysilicon seed-layer can be tailored to impact the grain characteristics of the poly SiC film, resulting in a highly-textured poly-SiC film (C. L. Frewin 2009). Indeed, this preliminary work was the motivation for this dissertation research where the next logical step was to realize MEMS devices on the poly-SiC on oxide wafers.

Figure 1.2 Schematic representation of antiphase domain boundary (APB) annihilation with film thickness. The solid line represents the Si-SiC interface. Note that the APBs form at the atomic steps of the Si surface. (Mendez, et al. 2005)

#### 1.2.2 Fabrication of Silicon Carbide MEMS

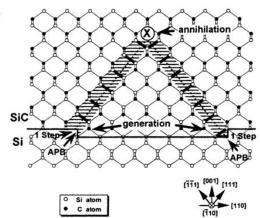

Although the micromachining of single-crystal bulk silicon carbide, i.e. 4H-SiC and 6H-SiC, has been demonstrated using SiC-epi on SiC bulk substrates to produce pressure sensors (Okojie 1996), heteroepitaxial SiC has the advantage of being grown on relatively inexpensive, high quality, large area Si substrates and readily processed using many of the conventional Si bulk micromachining techniques. The high etch resistance of silicon carbide to the wet chemistries used to process Si and SiO<sub>2</sub> allows SiC to act as an etch stop during a broad range of processing steps. Figure 1.3 shows a process flow demonstrating the realization of diaphragm and cantilever structures from epi-SiC on Si. In the case of the backside etch, the SiC membrane serves as an etch stop to provide excellent thickness control of the membrane. Freestanding SiC microstructures, like the cantilever shown in Figure 1.3, are first patterned using dry etching (plasma) and then the structure is released by etching the bulk silicon with an anisotropic wet etchant, e.g. KOH, TMAH, or EDP.

As previously mentioned, wet etching isn't practical to use to pattern silicon carbide, so plasma etching techniques have been developed. The fluorine-based plasma chemistries developed for the etching of Si, SiO<sub>2</sub>, and Si<sub>3</sub>N<sub>4</sub> are also used for SiC. SF<sub>6</sub>, NF<sub>3</sub>, CHF<sub>3</sub>, and CF<sub>4</sub> are commonly mixed with O<sub>2</sub> at pressures below 200 mTorr to promote reactive ion etching and suppress sputtering of the substrate (M. Z. Mehregany 1998). Although, the oxygenated plasmas quickly erode common photoresist masks, photoresists, such as AZ® 4620 manufactured by AZ Electronic Materials, are available that are resistant enough against erosion in fluorine-based plasmas to serve as a dry etch soft mask. Photoresist masks can exhibit etching selectivity up to 1:1, which is fine for

patterning larger feature sizes ( $\geq$  4µm) or processing thin SiC films. However, aluminum or nickel hard masks are preferred for patterning SiC in etching plasmas since only thin metal coatings are needed owing to the high selectivity of the metal films (1:40 for Ni on 3C-SiC). Nevertheless, aluminum hard masks are prone to an effect called micromasking, a phenomena that occurs when sputtered atoms from the metal mask deposit on the surrounding etch field and masks the undying material of the etch field. Grass-like structures result if the etching environment has a high-degree of anisotropy. The addition of small amounts of hydrogen to the gas mixture reduces this effect (M. Z. Mehregany 1998).

Figure 1.3 Fabrication of a free-standing cantilever. (a) CVD growth of 3C-SiC film on a Si substrate. (b) Mask material (shown in orange) is spun (photoresist) or deposited (metal) on the wafer and then patterned. (c) The 3C-SiC is dry etched using  $SF_6/O_2$  plasma. (d) Mask layer is removed. (e) Structure is released by etching the underlying silicon with a heated 20% KOH solution.

Surface micromachining is a process in which sacrificial thin films are used as a platform for the deposition of a structural layer, but are then removed to release a freestanding MEMS structure. Silicon bulk micromachining techniques can be used for processing monocrystalline, polycrystalline, and amorphous SiC, however, conventional surface micromachining is currently only possible with poly and amorphous SiC. Polycrystalline SiC structural layers can be deposited on a poly-Si or SiO<sub>2</sub> sacrificial layer to exploit the fact that SiC is highly resistant to Si and SiO<sub>2</sub> etchants. When poly-Si is used as a sacrificial layer, a thin oxide layer is used to protect the underlying Si substrate during the release of the structure from the sacrificial layer. Poly-SiC grown on  $SiO_2$  and  $Si_3N_4$  films tend to form randomly-oriented, equiaxed grains. In contrast, the crystal grains of the poly-SiC film grown on poly-Si matches the textured grains of poly-Si, forming a polycrystalline epitaxy (Zorman 1996). This suggests that one could vary the microstructure of the SiC film to tailor the device's performance by selecting the appropriate poly-Si substrate deposition conditions. The work discussed in this dissertation explores the influence of thickness-dependant microstructure changes (i.e. grain size and grain texture) of thin polysilicon films on the SiC film.

#### 1.2.3 Stress-Induced Deformation of Heteroepitaxial Films

As discussed earlier, heteroepitaxial SiC offers several benefits over bulk-grown SiC since heteroepitaxial SiC can be incorporated into current silicon processing technology and a variety of substrates can be implemented to suit design/ fabrication needs. Unfortunately, the heteroepitaxial growth of 3C-SiC on Si is exacerbated by a 20% lattice mismatch and 8% coefficient of thermal expansion (CTE) between Si and 3C-SiC

(refer to Table 1.1), which leads to in-plane stress within the film. The stress that develops within the SiC film near the SiC-Si interface is tensile, resulting in concave bowing of the wafer or, in the case of growth on (111)Si substrates, film delamination and cracking. Often the atomic bonds along crystal planes will break and reform to relieve film stress, leaving behind dangling bonds which are referred to as misfit dislocations (Smith 1995). At the edge of the wafer or areas where the film-substrate system terminate, deformation of the film edge will occur due to the film being "pinned" at the film-substrate interface, refer to Figure 1.3(a). This deformation will cause out-of-plane bending of free-standing structures As the film grows, a stress gradient parallel to the direction of growth frequently develops within 3C-SiC films, causing out-of-plane deformation of released structures, Figure 1.3(b). These material growth-related issues need to be addressed before 3C-SiC can be realistically considered as a replacement for Si-based MEMS device structures.

#### 1.3 Polysilicon-on-Oxide Substrates for Heteroepitaxial Silicon Carbide

SiC is a semiconductor material that is desirable for many power electronics and MEMS applications due to its wide band gap, mechanical resilience, robust thermal properties, and chemical inertness. However, many of these inherent properties create extreme difficulties when processing MEMS devices with this material. SiC chemical resistance reduces the effectiveness of wet chemical etching and requires the use of dry etching techniques involving reactive ion etching (i.e., DRIE/RIE). Fortunately, 3C-SiC, can be grown heteroepitaxially on Si substrates, and the addition of this Si layer allows for many more processing options in device manufacturing. For example, one can utilize the Si substrate as a sacrificial layer for the creation of freestanding 3C-SiC MEMS structures (Beheim and Evans 2006) (Carter, et al. 2000). However, the recipes used to

etch Si in DRIE/RIE have a similar etch rate with SiC, thereby excluding selectivity and reducing accuracy for the desired structure (Beheim and Evans 2006) (McLane and Flemish 1996) (Rosli, Aziz and Hamid 2006). Freestanding SiC MEMS devices using sacrificial Si layers have also encountered difficulties during device fabrication resulting from unetched Si preventing the complete release of the structure (Beheim and Evans 2006) (Carter, et al. 2000). Silicon dioxide, SiO<sub>2</sub>, has been traditionally used as an etchstop in Si processing involving DRIE/RIE, and can be easily removed by wet chemistry processes to allow for the full release of freestanding structures (Federico, et al. 2003). With this in mind, silicon-on-insulator, SOI, substrates provide an excellent media for the creation of freestanding SiC devices by providing not only an oxide for the etch-stop for DRIE/RIE, but also a Si crystal seed layer for the heteroepitaxial growth of the 3C-SiC (Shimizu, Ishikawa and Shibata 2000) (Myers, Saddow, et al. 2004).

SOI provides some additional benefits for the growth of 3C-SiC as shown in previous studies (Shimizu, Ishikawa and Shibata 2000) (Myers, Saddow, et al. 2004). The high temperatures required for the growth of single-crystal 3C-SiC soften the SiO<sub>2</sub> layer, allow dispersion of stress caused by the ~20% lattice mismatch between SiC and Si, and suppress the formation of voids caused by Si evaporation at the 3C-SiC/Si interface (Carter, et al. 2000). Although thick SOI seed layers (>50 nm) have been shown to produce 3C-SiC films that are of comparable quality when compared to 3C-SiC films grown on single-crystal Si substrates, the benefits of the epitaxial growth of 3C-SiC on SOI are realized when 3C-SiC is deposited on a thin (<50 nm) seed layer of Si, which produces excellent quality 3C-SiC (Shimizu, Ishikawa and Shibata 2000) (Myers, Saddow, et al. 2004). However, a major drawback of using SOI in the production of 3C-

SiC devices is the fact that it requires extensive processing techniques (Shimizu, Ishikawa and Shibata 2000) (Myers, Saddow, et al. 2004). These processes add to the overall production cost of the device. In addition many MEMS devices do not require single-crystal SiC material for proper functionality. A cost-efficient, easily produced wafer stack consisting of poly-Si/SiO<sub>2</sub>/Si layers could replace the SOI substrate if poly-SiC is desired as a material for MEMS applications.

The SiC Group at the University of South Florida has been investigating the optimization of the new process of growing thin-film 3C-SiC on a thin (≤ 100nm) polycrystalline Si (poly-Si) seed layer. The poly-Si is CVD-deposited on a CVD-deposited SiO₂/ Si (111) stack and poly-3C-SiC is formed on this poly-Si seed layer. The CVD deposited poly-Si seed layer appears to exhibit a highly-textured grain structure, in other words, the polycrystalline grains are oriented in a preferred direction. The texturing of the poly-Si layer is very sensitive to its deposition temperature. It is reported that the films are deposited favoring the <110> orientation and, once annealed, tend to arrange in the <111> orientation (Parr and Gardiner 2001). Growing the 3C-SiC via the poly-Si seed layer on an oxide release layer will provide a versatile substrate for the fabrication of free-standing, highly-crystalline 3C-SiC MEMS structures with low residual stress.

1.4 Influence of Polysilicon Seed-Layer Thickness on Silicon Carbide Film Stress

The behavior of polycrystalline films is largely determined by the grain morphology and the general orientation of the crystallites within the film (i.e., film texture). Smaller grain size, especially when they exhibit columnar structure, usually results in a higher concentration of small angle grain boundaries. These boundaries tend

to be areas of lower density and the interatomic forces within the boundary try to close the gaps, which results in a tensile stress on the surrounding crystallites (Koch 1994). Polysilicon films deposited at temperatures  $\geq 610^{\circ}$ C form a conical grain structure and exhibit compressive stress (Parr and Gardiner 2001). The origin of the compressive stress is not well understood, but is believed to be a result of hydrogen incorporation into the growing film (Yu et. al) or the insertion of excess adatoms into the grain boundaries (citation). Early in the deposition small, randomly oriented grains grow and compete with one another depending on their orientation with respect to the growing film. Crystallites oriented for fast vertical growth will out-compete slower growing misoriented grains. This results in fewer, but larger, conically shaped grains as the film grows (see Figure 1.5). Compressive polysilicon films tend to exhibit positive stress gradients and, as a result, curl upward when released from the substrate (Madou 2002).

Silicon carbide films were grown on polysilicon seed layers deposited under conditions which favor cone-shaped grain growth and compressive intrinsic stress.

Cantilevers fabricated from 3C-SiC films grown on a ~20nm thick polysilicon layer demonstrated a positive gradient stress, i.e. upward curl, whereas cantilevers fabricated from 3C-SiC films grown from a ~100nm polysilicon seed-layer developed a negative gradient stress, i.e. downward curl. Surface probe analysis of the polysilicon layers revealed substantial size and morphology differences of the surface structure of the gains. Transmission electron microscopy (TEM) of the 3C-SiC film grown on the 100nm thick polysilicon seed-layer showed relatively well-ordered grains near the SiC-Si interface with increasing randomness of the grain orientations away from the interface.

#### 1.5 Overview of the Organization of This Dissertation

SiC demonstrates roboust electrical, chemical, and mechanical performance suitable for use in harsh environments where Si-based MEMS devices would fail. Unfortunately, the chemical inertness is a desirable property for device application; it presents challenges for the processing of heteroepitaxial SiC films. Coupled with the inherent problems of heteroepitaxial growth, new techniques to reduce or eliminate these issues must be investigated if SiC is to be realized as the preferred fabrication material for harsh environment devices. Chapter 2 will discuss the principles of CVD growth and hardware, since chemical vapor deposition is the primary means of growing 3C-SiC. An overview of crystal defects and polycrystalline film growth as they apply to heteroepitaxial growth of 3C-SiC on Si will be then be presented. The chapter will conclude with a mechanical analysis of thin film stress. Chapter 3 will discuss the first experiments to realize high-quality poly-3C-SiC films on poly-Si on oxide wafers. Chapter 4 presents the first experiments aimed at producing MEMS structures on the poly-3C-SiC on oxide layers developed and presented in Chapter 3. Based on the lessons learned in this phase of the research the MEMS structures were re-designed so that stressstrain information could be extracted directly from the released MEMS structures. Finally, Chapter 5 will discuss future research exploring post fabrication annealing of MEMS structures micromachined from the stoichiometry-dependent bilayer film and further characterization of the microstructure of the polycrystalline SiC films.

# CHAPTER 2: HETEROEPITAXIAL SILICON CARBIDE STRUCTURE, GROWTH, AND THIN FILM MECHANICS

#### 2.1 Crystal Structure of Silicon Carbide

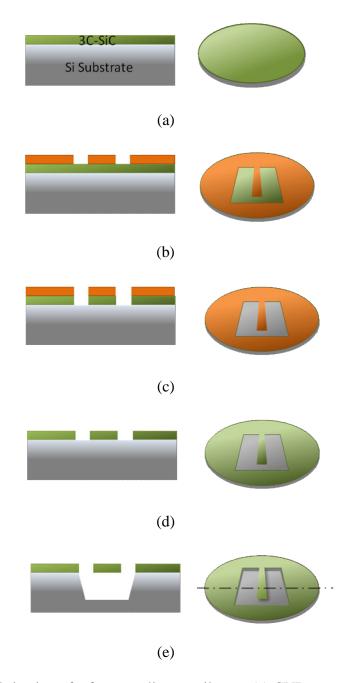

Silicon carbide can exist in many different crystal structures depending on growth conditions, a phenomenon called polytypism. Polytypism is a special case of polymorphism, in which the crystal structures between two polymorphs differ only in the way identical, two-dimensional layers of close-packed layers are stacked. In the case of SiC, polytypes vary by the different stacking sequences of the tetragonally-bonded Si-C subunits, with more than 220 polytypes known to exist (Foll 2006). However, an overwhelming majority of electronic materials research is concerned with only three of these polytypes: 4H-SiC, 6H-SiC, and 3C-SiC. The 4H, 6H, and 3C designation, called the Ramsdell notation, is the most wide-spread method of identifying polytypes (Foll 2006). The number-letter prefix designates the quantity of close-packed Si-C layers required for each unit cell and whether the polytype is a hexagonal (H), cubic (C), or rhombohedral (R) crystal system. For example, 4H-SiC indicates a hexagonal crystal system comprised of a repetitive, uniquely-ordered stacking sequence of four (4) Si-C subunit layers.

The hexagonal close-packed structure is a main reason for the high stability of the hexagonal SiC polytypes. The 4H-SiC polytype has the highest stability due to the

alternating cubic and hexagonal layers (Park, et al. 1994). 6H-SiC has a low, anisotropic electron mobility, while 4H-SiC has a much higher electron mobility and is less anisotropic, i.e. less directionally dependent (Casady and Johnson 1996). Thus 4H-SiC is, at present, the most commonly used polytype for electronic devices (Saddow and Agarwal 2004).

Figure 2.1 Four examples of SiC polytype stacking sequences. Each point represents a lattice point on which the Si-C basis is attached. Each layer is the close packed plane of the crystal system and is differentiated by "A", "B", or "C", which is determined by the relation of each layer's lattice point positions to the interstitial spaces of the other layers (Saddow and Agarwal 2004).

The 'A', 'B', and 'C' labels in Figure 2.1 denote the position of the lattice points, a collection of periodic points in space, on which the Si-C subunits are located. As seen in Figure 2.1, 4H-SiC has a stacking sequence of ABCB, or 4 layers, therefore the designation is 4H. This structure has an equal number of cubic and hexagonal lattice sites. The 6H-SiC structure has 6 stacking layers before the sequence repeats ABCACB, and, finally, 3C-SiC is a continuation of the ABC stacking sequence which has purely cubic symmetry. Due to differences in stacking sequence, the electrical, mechanical and optical properties vary for each polytype of SiC, as shown in Table 1.1.

#### 2.2 Overview of CVD

Chemical vapor deposition (CVD) is a technique in which a solid film is formed onto a surface by a chemical reaction emanating from vapor phase precursors. The chemical reactions generally undergo activation by ohmic heating, RF induction heating, plasma, or light. It is a technique often employed for the uniform growth of high quality thin films. The common types of CVD are 1) Organometallic Vapor Phase Epitaxy (OMVPE) 2) Plasma Enhanced Chemical Vapor Deposition (PECVD) 3) Photo CVD 4) Low Pressure CVD and 5) Atmospheric Pressure CVD. Chemical vapor deposition involves a series of sequential steps beginning with the vapor phase and progressing through a series of quasi steady-state reactions which culminate in the development of a sold film. The progression from vapor phase to film growth can be summarized by the following sequence of events. First, the gaseous reactants diffuse through the stagnant fluid layer (i.e. so called 'boundary layer') to the growth surface. Second, the reactants adsorb on the surface and then usually undergo some surface migration to reach a reaction site (i.e., dangling chemical bond). Third, the reactants undergo a chemical reaction which may be catalyzed by the surface. Fourth, the reaction by-products undergo desorption from the surface. Fifth, the reaction by-products diffuse through the boundary layer, enter the gas stream and are exhausted out of the reactor. Finally, the condensed product is incorporated into the structure of the developing film. The process is summarized in Figure 2.2 below.

Figure 2.2 Schematic diagram of mechanistic steps which occur during the CVD process. (1) Gas inlet, (2) dissociation of reactants, (3) diffusion of reactants to the surface, (4) adsorption of reactants to the surface, (5) heterogeneous surface reaction, (6) desorption of by-products, (7) diffusion of by-products back into the bulk gas (Park and Sudarshan 2001).

Although many rate-limiting steps are known to exist, the deposition rate of CVD processes is primarily governed by two mechanisms: mass transport and surface kinetics. These two rate-limiting steps are influenced by several process parameters. The temperature and pressure of the reaction environment greatly impact the deposition process. The pressure controls the thickness of the boundary layer and, as a result, affects the rate of the reactant and product diffusion (Sivaram 1995). At low pressures, the boundary layer is thinner, which minimizes the diffusion time across the region. This is known as the reaction-rate-limited CVD regime; where the rate of deposition is limited by the reaction rate of reactants on the surface and is more sensitive to temperature (Sivaram 1995). If the temperature is low, then an oversupply of reactants is created due to the molecules reacting slowly (Sivaram 1995). If the temperature is high, then the surface reactions take place quickly and the reaction rate is limited by the diffusion of

molecules. This is generally the case for high pressures as the boundary layer is thicker and diffusion becomes the rate-limiting step. The growth regime (transport-limited or surface reaction-limited) is determined by the slowest process (diffusion or chemical reaction) (Smith 1995). Figure 2.3 illustrates how both the temperature and pressure during CVD affects the growth rate.

Figure 2.3 Generalized process trend showing the dependence of process temperature and pressure on growth rate via CVD (Smith 1995).

Another important process parameter that influences reaction rate is gas velocity. The CVD process involves the transport of precursor gases through the use of a carrier gas, which is designed to flow in a laminar manner although occasionally some turbulence is present (Park and Sudarshan 2001). When a fluid flows over a stationary surface, a thin layer of fluid immediately above the surface is stationary. This is known as the boundary layer, as stated above, and is inversely proportional to the gas velocity

and directly proportional to the fluid viscosity and pressure. In a horizontal CVD reactor design, the boundary layer increases along the direction of the carrier gas flow (as the temperature of the gas increases), which leads to an exponential decrease in the deposition rate. Tilting the susceptor increases the gas velocity by continuously decreasing the cross-sectional area and thus reduces the thickness of the boundary layer along the flow direction (Rossi 1988). Figure 2.4 illustrates these principles.

Figure 2.4 Illustration of the boundary layer,  $\delta$ , in a horizontal reactor with: (a) flat susceptor design, and (b) tilted susceptor design (Pierson 1999).

#### 2.2.1 Early Stages of CVD Film Growth

The initial stages of film growth are characterized by three major phenomena which occur independent of the type of film growth technique. The material first condenses out of the vapor phase and nucleates on a substrate. This condensation process begins with the reactant species impinging on the surface and bonding to the substrate atoms at the gas-substrate interface. The probability that an impinging atom will be adsorbed onto the surface is related to a quantity called the sticking coefficient, which is the ratio of the amount of material condensed on the surface to the total amount of impinging atoms, Figure 2.1 (Sivaram, S 1995). Once an atom is adsorbed onto the surface it must overcome a surface binding energy, Q<sub>desort</sub>, in order to leave the surface.

Given the vibrational frequency, v, of the adsorbed atom, the length of time,  $\tau_s$ , which an atom stays on the surface, is expressed by:

$$\tau_{s} = \left(\frac{1}{v}\right) \cdot \exp\left(\frac{Q_{desorb}}{kT}\right) \tag{2.1}$$

When Q<sub>desob</sub> is large in comparison to kT, the adsorbed atom will spend a long time on the surface, so the chance of the atom being incorporated on the surface is high (Sivaram, S 1995). When the energy of the surface atoms is on the order of kT, then the adsorbed atom will have a high probability of being desorbed. Once incorporated onto the surface, the condensed atoms or molecules tend to aggregate and form small clusters on the surface of the substrate, a process called nucleation. These small clusters are in a constant free energy struggle between the releasing of free energy when forming a cluster and having to pay an energy cost when forming a surface interface between two distinct phases. Small clusters are unstable if the energy released from the formation of its volume cannot sustain the creation of its surface. Once the clusters have reached a critical size, any addition of molecules to the cluster releases energy instead of costing energy and nucleation growth can be sustained. Then the randomly formed nucleation sites reach a saturation density and undergo island coalescence via the diffusion and continuing capture of adatoms. This saturation point occurs when the internuclear distances are on the order of the mean surface diffusion length. As the islands grow, they assimilate subcritical nuclei and coalesce with other islands, forming a connected network. Eventually, the steady-state growth above the first layer occurs. However,

CVD processes add an additional step to the film growth process; a chemical reaction among the surface-adsorbed reactants occurs at the gas-substrate interface. Whereas simple condensation is always exothermic, a majority of CVD reactions are endothermic which means they must usually wait until they interact with the heated substrate.

Another important feature of the CVD process that complicates this general growth sequence is that the intrinsic impurities, in the form of reaction products, need to be considered in the vicinity of the film growth (Sivaram, S 1995).

#### 2.3 Overview of Heteroepitaxial Defects

Given the nature of heteroepitaxy, i.e. growing a crystalline material on a different crystalline material (substrate), it is nearly impossible to generate a perfect, mono-crystalline film. Other than the introduction of impurities from contamination, the common source of extrinsic crystal defects found in heteroepitaxy stems from a mismatch between the lattice constant and the coefficient of thermal expansion between the substrate and film. These disparities create line defects, such as dislocations, or planar defects as is the case for micro-twins, stacking faults, and grain boundaries.

#### 2.3.1 Line Defects

Dislocations are linear defects resulting from the deviation of atoms from the lattice site positions of the crystalline structure. The disruptions of the atomic arrangement associated with dislocations typically extend through the structure along a line. Dislocations that commonly occur in heteroepitaxy are of the edge and misfit type.

Edge dislocations can be thought of as a disturbance originating from the insertion or removal of a partial plane of atoms from the crystal structure. The region at the end of the partial plane, where the atomic arrangement maximally deviates from the normal lattice sites, is called the dislocation line. The surrounding region is the dislocation core, which is an area of large strain and dangling bonds that runs alongside the dislocation line. The energy of propagation for an edge dislocation is much lower than the total bond energy of the atoms lying in the propagation plane. This is explained by the fact that an edge dislocation proceeds through a crystal peristaltic fashion. At any given moment, only one bond is broken while the atoms surrounding the dislocation are distorted from their equilibrium positions.

Another type of dislocation that is closely related to the edge dislocation, but is not seen in 3C-SiC heteroepitaxy, is the screw dislocation. This dislocation is often thought of as a crystal system which has been subjected to shear stress sufficient enough to overcome the elastic limits of the crystal. The result is the shifting of one side of the crystal relative to the other side by one or more lattice constants. In this case, the dislocation line runs in the direction of the shift. Referencing the atoms located within a plane perpendicular to the dislocation line, if an attempt is made to form a closed path around the dislocation line by connecting the atoms together, a helix will be formed. The once parallel planes of the crystal are now joined by a helical path; this is why this type of dislocation is referred as a screw dislocation. Although this dislocation is not seen in as-grown crystalline 3C-SiC films, its introduction is important for the understanding of grain boundaries.

Heteroepitaxial dislocations, called misfit dislocations, form at the interface of two crystals with different lattice constants. In an attempt to minimize the interatomic bonding strain induced by the lattice mismatch, the atomic planes of the thin film will be distorted at the interface and will no longer be equally spaced. The roughly equidistant points along the interface where the lattice deviations are the greatest correspond to the misfit dislocations. If the heteroepitaxial film has a coefficient of thermal expansion different than the substrate, then when temperature changes occur, usually during postgrowth cooling, misfit dislocations occur in order to relieve in-plane stress present near the film-substrate interface.

#### 2.3.2 Planar Defects

Planar defects correspond to disturbances of the crystal structure resulting from the two dimensional deviation of atoms from their corresponding lattice sites. Planar defects commonly found in heteroepitaxial films are stacking faults (SF), microtwins, antiphase boundaries (APB), and double position boundaries (DPB).

Stacking faults occur when a mistake occurs in the stacking sequence of the planes of atoms along certain directions. If planes of densely-packed spheres (atoms) are to be stacked on each other, one finds that there are two sets of interstitial spaces to place the next densely-packed plane. As a result, it is possible to lay three planes in succession without the co-alignment of interplanar atoms. In a perfect crystalline structure, a stacking sequence will eventually repeat in a periodic fashion. The face-centered cubic (FCC) structure is created when the stacking sequence repeats as ABCABC...and the hexagonal close packed (HCP) structure is created from the sequence ABABAB... In the

case of the zinc blende structure of 3C-SiC, it is not unusual to see stacking errors occur in the stacking of the {111} planes since the nearest-neighbor bonding is not affected by stacking faults. In fact, the energy associated with stacking faults is very low when compared to other planar defects since the defect is only due to the nearest-neighbor arrangement and not disturbances of the crystal structure. This mistake may arise during the film growth or when plastic deformation has occurred to the film. Figures 2.5 and 2.6 show a plan-view and cross-sectional TEM micrograph of the stacking faults present in a 3C-SiC film grown heteroepitaxially on (100)Si.

Figure 2.5 Stacking faults revealed in a (100)3C-SiC film via PV-TEM. SF density estimated to be  $\sim 5 \times 10^4$  cm<sup>-1</sup>. Data provided by C. Bongiorno, IMM-CNR, Catania, Italy.

Figure 2.6 Example of hetero defects in (100)3C-SiC from X-TEM. Note the defects along the (111) planes, also threading dislocations and stacking faults. Image courtesy C. Bongiorno, IMM-CNR, Catania, Italy.

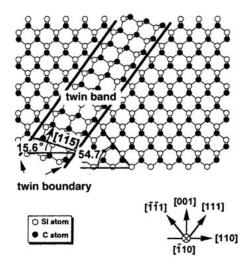

Another type of planar defect resulting from the change of the planar stacking sequence is the micro-twin or, simply, twin. The distinctive feature of a twin is that the planar arrangements on opposite sides of the stacking disruption are mirror images of each other. For example, the stacking sequence ABCABCACBACBA...possesses a reflection about the A-plane located at the center of the palindrome. In the diamond or zinc blende structure, twinning occurs mostly about the (111) plane. Twinning causes a change in the crystal orientation. For crystal growth along the <111> direction in the zinc blende structure, the orientation of the crystal planes in the twinned region are along the <111> or <115> direction. A very smooth surface morphology can result in 3C-SiC heteroepitaxial growth along the <111> direction since the twinning plane is the same as the growth plane. Figure 2.7 (a) shows a schematic representation of a micro-twin while Figure 2.8 shows a plan-view TEM micrograph of an actual micro-twin present in a 3C-SiC film grown on (100)Si.

Figure 2.7 Schematic representation of micro-twin defect in SiC on Si heteroepitaxy. (Mendez, et al. 2005)

Figure 2.8 Micro-twinned crystal defect (dark cluster in center of micrograph) observed with plan-view TEM (PV-TEM). Data courtesy of C. Bongiorno, IMM-CNR, Catania, IT.

A planar defect that frequently occurs during the growth of (100)3C-SiC on (100)Si substrates is the antiphase boundary (APB). This type of defect is prevalent during APCVD growth and is significantly reduced at lower growth pressures (Cho and Carter 2001). The APB occurs when two islands having different ordered phase

coalesce. In the early stages of the film growth, partial surface steps may cause a relative position shift between the atomic stacking of different islands. In the case of SiC, due to surface roughness of the carbonized Si substrate, some islands of SiC may sit higher relative to others. As the islands grow and coalesce, a Si or C layer of one island may bond with another Si or C atom of another island forming a Si-Si or C-C bond as illustrated in Figure 2.9. These boundaries tend to propagate along the {111} planes (Ishida, Takahashi and Okumura 2003). However, the etching experiments of Li and Giling have shown evidence that APBs can propagate along the {110} plane (Ishida, Takahashi and Okumura 2003).

Figure 2.9 Geometrical consideration of the formation of an APB when SiC is grown on (100)Si substrate with an atomic step. Note the bonding of Si-Si and C-C atoms. (Cho and Carter 2001)

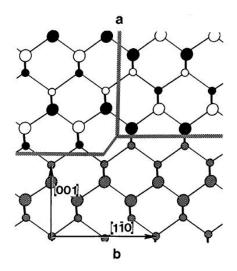

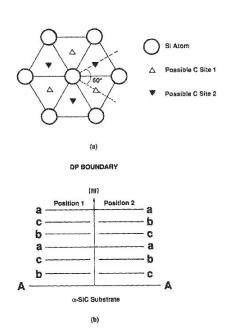

The double position boundary (DPB) is a special case of twinning in which separate domains are rotated about a 180° twin axis. This is seen when a FCC type crystal structure is grown in the (111) orientation on a (111) surface of a hexagonal crystal

(Kong, et al. 1987). This is commonly seen in 3C-SiC films grown on the basal plane of the hexagonal SiC polytypes. As illustrated in Figure 2.10(a), the (111) surface has two equivalent types of sites that the C atoms can locate. As a result, two different nuclei orientations can develop which are rotated 60° relative to each other. When these nuclei coalesce into each other, a DPB is formed. In Figure 2.10(b), the relative shift of the stacking sequence between neighboring domains is shown. The upper case "A" represents the surface of the substrate, while the lower case "a b c..." represents the stacking layers of the epitaxy. One can see that every third layer offers the opportunity to form a perfect bond across the interface, Si-C for example, the other planes cannot form this type of bond (Kong, et al. 1987). As a result, the boundary is somewhat disordered and the internal energy is high (Kong, et al. 1987).

Figure 2.10 Stacking fault generation schematic showing the error in crystal layer formation resulting in a stacking fault defect. (a) top view representation and (b) side view showing the plane stacking sequence (Kong, et al. 1987).

#### 2.3.3 Grain Boundaries

Since this dissertation involves the growth and characterization of polycrystalline films, it is worth looking at the role grain boundaries play in polycrystalline systems. Polycrystalline materials consist of several small crystalline regions, called grains or crystallites, bonded together by crystallographically defective regions called grain boundaries. Grain boundaries are interfaces where two crystals having different orientations meet without a disruption in the continuity of the material (Hirth 1968). Grain boundaries are generally categorized as low-angle grain boundaries and high-angle grain boundaries. Low-angle grain boundaries can be viewed as being comprised of several distinct and isolated dislocations whose properties are directly dependent on the degree of misorientation, ( $\leq 10^{\circ}$ ). An idealized, simplified case of creating a low-angle grain boundary is through a tilt and twist.boundary.

In the case of a tilt boundary, the crystal lattice can be visualized as being bent by an applied force about an axis parallel to the boundary plane. To reduce the energy associated by the bending, one can insert a wedge into the crystal. Edge dislocations, which are an extra plane of atoms, act like an imaginary wedge. As the bending angle is increased, more dislocations must be incorporated into the deformation in order to reduce the energy of the deformation.

The twist boundary involves rotation about an axis perpendicular to the boundary plane. In order to minimize the energy associated with the twist, two sets of perpendicular screw dislocations need to be introduced into a plane to create localized distortions. Generally, grain boundaries are never a pure tilt or twist boundary, but a combination of the two. When the angle of misorientation becomes large, the

dislocations become numerous and begin to overlap each other creating a very disordered boundary region.

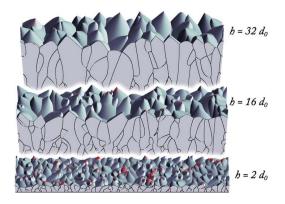

## 2.4 Structural Evolution of Polycrystalline Thin Films

Grain formation in polycrystalline films grown using CVD processes is sensitive to several parameters such as temperature, deposition rate, dopant concentration, pressure, and impurity concentration. The structures of polycrystalline systems usually are governed by complicated, materials-specific phenomena (Thompson 2000). The processes described in this section are simple, generalized trends of behavior for materials. Polycrystalline films typically begin with the nucleation and coalescence of individual crystal islands on a substrate, an overview of this process was discussed in section 2.2.1. Grain growth is largely driven by the minimization of the excess energy associated with the total grain boundary area; as the grain boundary area decreases, the grain size must increase. Grain structure formation can occur through two distinct evolutionary processes. In one case, the grain boundaries formed early after island impingement are immobile and grain growth proceeds from the epitaxial growth of columnar structures. As the film grows, the grains oriented with the faster growing facets favoring vertical film growth will out-compete slower growing, misoriented grains, Figure 2.11. Sometimes this is referred to as conical grain growth.

Figure 2.11 Evolution of grain structure with film growth. Cross-sectional slices of a simulated film at various thicknesses revealing grain evolution due to competitive grain growth among conical grains. The film thickness, h, is expressed in terms of the initial grain spacing, d<sub>0</sub>. (Ophus 2010)

When the grain boundaries are mobile, the in-plane grain growth proceeds as the film thickens. The resulting grains appear to have an equiaxed, columnar shape that traverses the thickness of the film. As the film grows, the in-plane grain size increases with roughly the same scale. Often times, as unfavorable grain orientations are occluded due to competitive growth and the faster growing orientations drive film thickening, conical growth can lead to columnar grain growth with roughly parallel boundaries.

### 2.5 Mechanical Properties of Thin Films

While many thin film devices may be sought after for their electronic, magnetic, or optical properties, these devices are often limited by their mechanical properties. In the course of the deposition of thin films of materials, large stresses can develop, sometimes exceeding the tensile strength of the bulk material. These intrinsic stresses are often held responsible for the failure of thin film devices; in extreme situations the film may crack or peel from the substrate from where they are grown. From a technological point of view, it is important to understand the mechanisms responsible for thin-film

stress and develop methods to reduce or compensate for the impact these stresses have on thin-film bases devices.

#### 2.5.1 Sources of Stresses in Thin Films

This section will open with a few distinctions that need to be introduced between widely employed and, occasionally misused, terminology. Stress, often denoted by the Greek letter,  $\sigma$ , is defined as the force, F, applied over a cross-sectional area, A, whose units are the same as pressure. It is simply expressed as,

$$\sigma = \frac{F}{A} \tag{2.2}$$

Strain, denoted by the Greek letter,  $\epsilon$ , is a measure of a change of length,  $\Delta L$ , arising from the displacement of a particle in a body based on a reference length, L. The length change may occur because of the application of an external or internal force, the expansion of a material from a temperature difference, etc. It is frequently expressed as a ratio,

$$\varepsilon = \frac{\Delta L}{L} \tag{2.3}$$

By convention,  $\sigma > 0$  and  $\epsilon > 0$  are tensile stress and strain and  $\sigma < 0$  and  $\epsilon < 0$  are compressive stress and strain, respectively. Residual stresses are those stresses that exist within a body when thermal gradients or externally applied loads have been removed.

Three sources of stress that can contribute to thin film's residual stress are intrinsic, epitaxial, and thermal.

Intrinsic stress refers to the collective stresses that develop during the growth of the film. It does not arise from the lattice mismatch or the thermal expansion-related strains of the film-substrate system, but occurs because of the film deposition process (e.g. nucleation, island coalescence, grain growth, film thickening, etc.), and develops under non-equilibrium conditions.

Epitaxial stress arises when a lattice parameter mismatch exists between the film and the substrate. This occurs when the film is very thin and there is coherency between the lattice sites of the film and the substrate. The misfit strain,  $\epsilon_{mf}$ , by the distortion of the lattice spacing creates stress is given by

$$\varepsilon_{\rm mf} = \frac{\left(a_{\rm s} - a_{\rm f}\right)}{a_{\rm s}} \tag{2.4}$$

Where a<sub>s</sub> and a<sub>f</sub> are the substrate and film lattice constant, respectively. Once an epitaxial film reaches a critical thickness, t<sub>c</sub>, the lattice becomes sufficiently strained and it becomes energetically favorable to form misfit dislocations in the film at the interface. The misfit dislocations introduce a stress field into the immediate area which relaxes the stressed interface. In the case of 3C-SiC, once the film grows past the critical thickness, 5 SiC lattice cells slightly exceed the distance spanned by 4 Si cells (i.e., 20% lattice mismatch). Sometimes epitaxial stress is lumped with other growth-related stresses as a

source of intrinsic stress but there is this fine distinction which is important to understand in order to try and reduce/eliminate.

Thermal stress is generated when strain is created from the material-dependent differential expansion between the film and substrate during a temperature change. This is often referred to as the Coefficient of Thermal Expansion (CTE). When the  $t_f << t_s$ , the stress is related to the strain in the film at a certain temperature, T, by:

$$\sigma_{\text{therm}} = \left(\frac{E_f}{(1 - v_f)}\right) \cdot (\alpha_f - \alpha_s) \cdot (T_{\text{dep}} - T)$$

(2.5)