### A MODULAR PIPELINED MEDIUM GRAIN RECONFIGURABLE

#### PROCESSOR CORE

By

JASON DANIEL VAN DYKEN

A dissertation submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

WASHINGTON STATE UNIVERSITY School of Electrical Engineering and Computer Science

August 2012

To the Faculty of Washington State University:

The members of the Committee appointed to examine the dissertation of

JASON DANIEL VAN DYKEN find it satisfactory and recommend that it be accepted.

José G. Delgado-Frias, Ph.D., Chair

Partha Pratim Pande, Ph.D.

David E. Bakken, Ph.D.

# Acknowledgment

This academic endeavor would not have been possible without the help and support of many people, and has been carried out in conjunction with the High Performance Computer Systems (HiPerCopS) research group and the School of Electrical Engineering and Computer Science at WSU.

Foremost, I would like to thank Professor José Delgado-Frias, who has been my advisor throughout my doctoral and master's research. His encouragement, patience, and enthusiasm throughout this process have been invaluable. Dr. Delgado helped find solutions to the many roadblocks and challenges encountered and his guidance and insights have made this dissertation possible.

In addition I would like to thank Professors Partha Pande and David Bakken, who serve on my committee, for their encouragement and advice both in and out of the classroom. They have pushed me to broaden my base of knowledge and helped to guide my research and academic coursework. Next, I would like to thank my fellow graduate students in the HiPerCopS research lab for sharing their knowledge and for their camaraderie. Specifically, Mike Turi and Zhe Zhang, have made the many hours spent in lab much more enjoyable.

I would especially like to thank my family for their unending support and encouragement. At no point during this endeavor, even when I doubted my progress toward this goal, did my parents belief in my abilities or conviction that I would reach my goal waiver, which has meant so much to me. Thank you for instilling in me the stubborn determination and strong work ethic that has allowed me to reach this point.

Most importantly, I would like to thank my wife Crystal, for her patience with, and tolerance of, my odd work hours and habits. Her unconditional support and companionship has afforded me the strength I needed to complete this dissertation. She has made my life so much more enjoyable than I could ever have imagined. Crystal keeps me grounded and continuously ensures that I am exposed to new topics outside of my direct interests and research, such as all things yarn related.

iv

#### A Modular Pipelined Medium Grain Reconfigurable Processor Core

Abstract

By Jason Daniel Van Dyken, Ph.D. Washington State University August 2012

Chair: José G. Delgado-Frias

This research focuses on a modular and scalable implementation of a MIPS compliant processor core for a medium-grain reconfigurable hardware. The core of this research is built upon the design of four autonomous modular functional units that provide all the operations required of a MIPS core.

Four novel extremely configurable execution cores have been designed to implement a five-stage processor architecture Each of the cores can be configured for varying path widths and forwarding schemes, which have been evaluated for criteria involving area (cell count), delay, and execution efficiency. A comparative study with other reconfigurable hardware has shown the proposed cores' effective clock rate is 3% above the average for similar cores when utilizing 150nm and 90nm CMOS, and 0.99% below the average Xilinx and Altera soft processor speeds for 65nm and 45nm CMOS technologies. The proposed hardware has no specialized hardwired units such as multipliers or adders that are available in Xilinx and Altera chips. Ongoing research on FinFET technology has shown that a system clock of 5 GHz can reasonably be achieved. An analysis of the hardware has also been conducted examining issues of hardware design and the energy required for the designs to operate and how the cores would be affected if the hardware were modified. The results of this analysis have shown that module power consumption averages 0.248 mW for 8-bit and 1.855 mW for 32-bit data path widths and that the average energy required for executing a SPEC integer benchmark is 2.06  $\mu$ J.

Lastly, designs for implementing a reorder buffer and reservation stations have been completed, which can be configured to track a varying number of instructions. Using these new modules with the previously analyzed components a superscalar core may be built. This core has been analyzed to determine the optimal configuration of the reorder buffer and reservation stations, and undergone the same evaluations as the five-stage cores to determine the best operation configuration and energy requirements. This analysis comparing the superscalar core with a five-stage execution core shows that a speedup of 2.073 can easily be achieved while increasing cell count by only 29%.

vi

# TABLE OF CONTENTS

| Ab  | stract       |                                           | v   |

|-----|--------------|-------------------------------------------|-----|

| Lis | t of Tables  |                                           | x   |

| Lis | t of Figures | 5                                         | xii |

| 1.  | Introduc     | tion and Background                       | 1   |

|     | 1.1 Back     | ground                                    | 2   |

|     | 1.2 Outli    | ine                                       | 7   |

| 2.  | Executio     | n Modules                                 | 9   |

|     | 2.1 AES      | Components                                | 10  |

|     | 2.1.1        | S-Box Transform                           | 11  |

|     | 2.1.2        | Add Round Key Transform                   | 13  |

|     | 2.1.3        | Mix Columns Transform                     | 15  |

|     | 2.1.4        | Key Expansion                             | 17  |

|     | 2.2 Proces   | sor Modules                               | 19  |

|     | 2.2.1        | Bitwise Logic                             | 20  |

|     | 2.2.2        | Multiplication, Addition, and Subtraction | 22  |

|    | 2.    | 2.3   | Shifting and Rotating                  | 26 |

|----|-------|-------|----------------------------------------|----|

|    | 2.    | 2.4   | Comparator                             | 31 |

|    | 2.    | 2.5   | Other Components                       | 36 |

|    | 2.3 N | Modu  | le Functional Simulation               | 38 |

| 3. | Exe   | cutio | on Cores and Forwarding                | 42 |

|    | 3.1   | Five  | -Stage Architecture Adaptation         | 43 |

|    | 3.2   | Exec  | cution Cores                           | 45 |

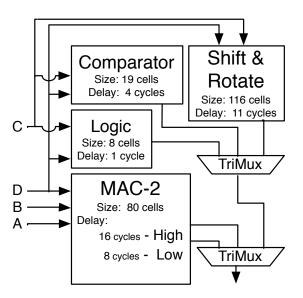

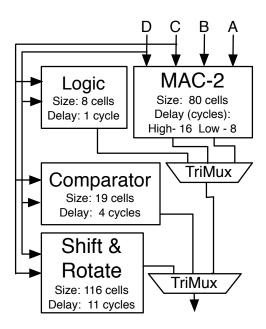

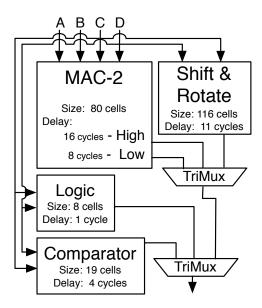

|    | 3.    | 2.1   | Half-MAC Core                          | 45 |

|    | 3.    | 2.2   | Shift Centric Core                     | 47 |

|    | 3.    | 2.3   | Comparator Centric Core                | 49 |

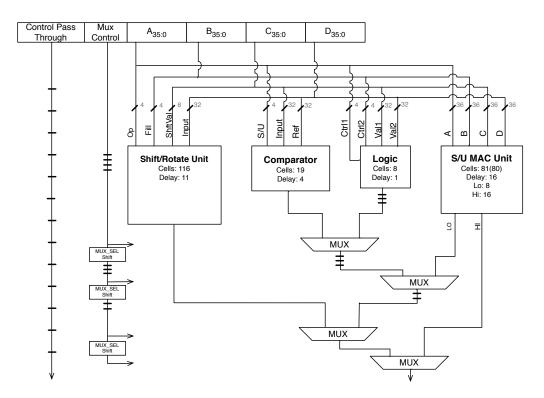

|    | 3.    | 2.4   | ExCore                                 | 50 |

|    | 3.    | 2.5   | Branch and Jumps                       | 52 |

|    | 3.3   | Forv  | varding Mechanisms                     | 53 |

| 4. | Five  | e-Sta | ge Core and Forwarding Scheme          |    |

|    | Peri  | form  | ance Evaluation                        | 56 |

|    | 4.1   | Past  | Lessons                                | 57 |

|    | 4.2   | Perf  | ormance Evaluation                     | 60 |

|    | 4.3   | Com   | parative Analysis                      | 66 |

| 5. | Har   | dwar  | e Analysis and Design Characterization | 72 |

|    | 5.1   | Harc  | lware Design Analysis                  | 73 |

|    | 5.2   | Harc  | lware Energy Analysis                  | 75 |

|    | 5.3   | Combined Energy and Performance Analysis | 79  |

|----|-------|------------------------------------------|-----|

| 6. | Sup   | erscalar Architecture                    | 84  |

|    | 6.1   | Additional Components                    | 86  |

|    | 6.    | 1.1 Reorder Buffer                       | 86  |

|    | 6.    | 1.2 Reservation Stations                 | 88  |

|    | 6.2   | Superscalar Core                         | 92  |

|    | 6.3   | Performance Evaluation                   | 93  |

|    | 6.4   | Power and Energy Evaluation              | 97  |

|    | 6.5   | Comparison with Five-Stage Cores         | 101 |

| 7. | Con   | cluding Remarks                          | 106 |

|    | 7.1   | Contributions                            | 107 |

|    | 7.2   | Future Directions                        | 111 |

| Bi | bliog | raphy                                    | 113 |

| A. | Cell  | ular Configurations                      | 118 |

| B. | Con   | trol Logic                               | 156 |

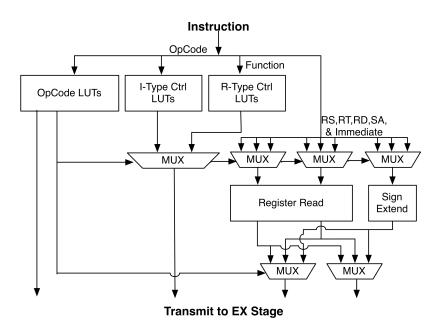

|    | B.1   | Control Logic at ID Stage                | 157 |

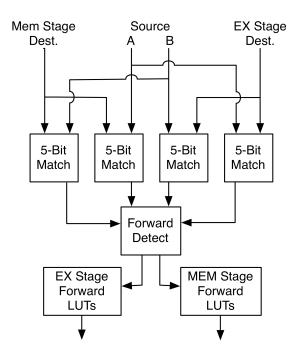

|    | B.2   | Forwarding Control Logic                 | 158 |

| C. | Cell  | Utilization                              | 160 |

| D. | Pub   | lications                                | 164 |

|    | D.1   | Journal Papers                           | 164 |

|    | D.2   | Conference Papers                        | 164 |

# LIST OF TABLES

| 2.1 | Logic Operations and Control Signals                 | 21 |

|-----|------------------------------------------------------|----|

| 2.2 | MAC Unit Cell Count Comparison                       | 25 |

| 2.3 | MAC-2 Input Organization                             | 26 |

| 2.4 | Comparator Output Generation                         | 34 |

| 3.1 | Core and Module Sizing based on Path Width           | 47 |

| 4.1 | AES Implementation Comparisons                       | 57 |

| 4.2 | Optimal Performance Characteristics for Cores        |    |

|     | and Forwarding Schemes                               | 63 |

| 4.3 | Cycles (in Millions) Needed to Complete 5 Benchmarks |    |

|     | Totaling 3.85M Instructions                          | 63 |

| 4.4 | Design Technology Size and Processor Clock in MHz    | 71 |

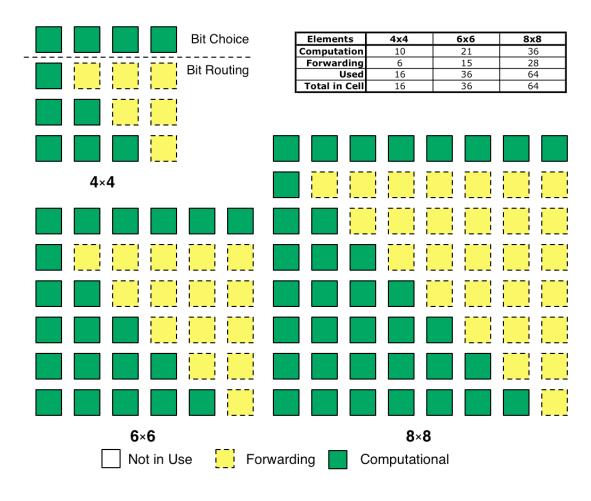

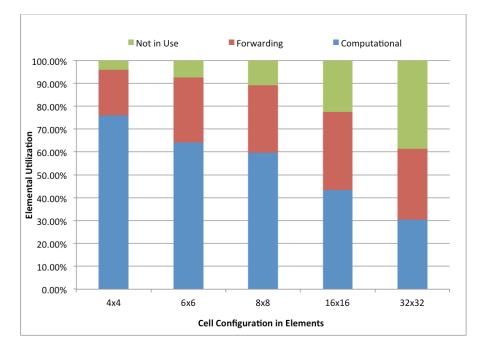

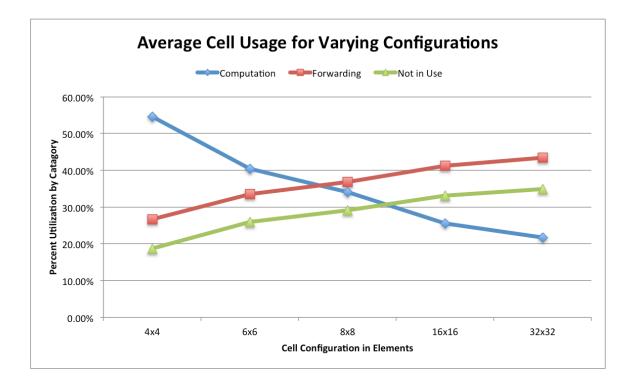

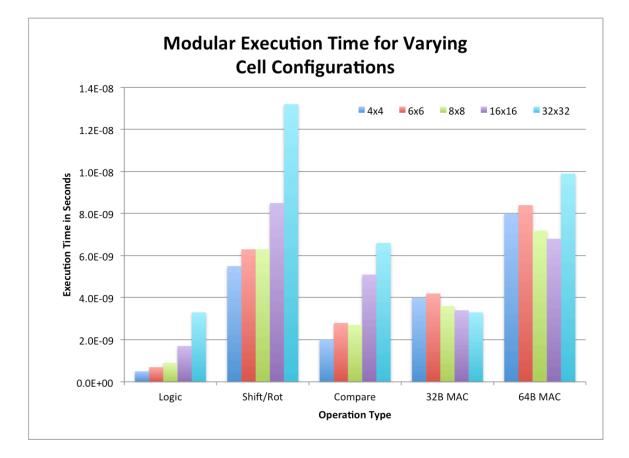

| 5.1 | Cell Utilization for Varying Configurations          | 75 |

| 5.2 | Module Power Consumption                             | 77 |

| 5.3 | Benchmark Energy Consumption                         | 79 |

| 6.1 | Superscalar Configuration Evaluation                 | 95 |

| 6.2 | Reorder Buffer Usage and Core Area                    | 97  |

|-----|-------------------------------------------------------|-----|

| 6.3 | Cycle and Energy Requirements for Varying             |     |

|     | Reservation Station and Reorder Buffer Configurations | 99  |

| 6.4 | Superscalar Energy and Cycle Requirements             | 100 |

| 6.5 | Five-Stage and Superscalar Core Comparisons           | 102 |

# LIST OF FIGURES

| 1.1  | Structure of an Element                     | 4  |

|------|---------------------------------------------|----|

| 1.2  | Cell in Memory Mode                         | 5  |

| 1.3  | Element and Cell in Math Mode               | 6  |

| 2.1  | S-Box 8-Bit LUT Implementation              | 12 |

| 2.2  | S-Box Hardware Layout                       | 13 |

| 2.3  | 8-Bit Xor Cell                              | 14 |

| 2.4  | Alternate Add Round Key                     | 15 |

| 2.5  | Multiply by 2 and 3                         | 16 |

| 2.6  | Key Expansion                               | 18 |

| 2.7  | Logic Cell Organization                     | 21 |

| 2.8  | Logic Module Layout and Placement           | 22 |

| 2.9  | Cell Types based on Elemental Configuration | 23 |

| 2.10 | 16-Bit MAC Units                            | 24 |

| 2.11 | Shift Cell                                  | 28 |

| 2.12 | 16-Bit Right Shift Unit                     | 29 |

| 2.13 | Shift Module                                   | 30 |

|------|------------------------------------------------|----|

| 2.14 | Comparator Top Cell                            | 32 |

| 2.15 | Comparator Bottom Cell                         | 33 |

| 2.16 | Comparator Collector Cell                      | 35 |

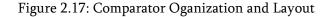

| 2.17 | Comparator Organization and Layout             | 36 |

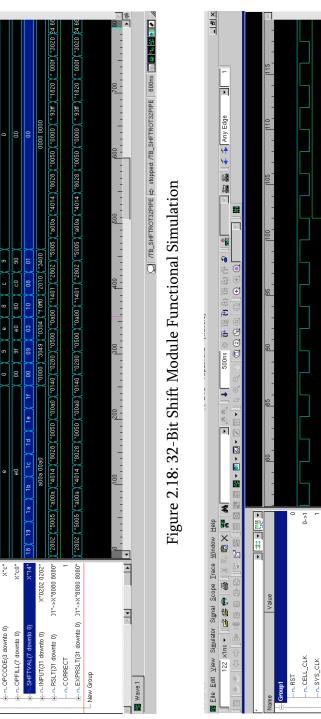

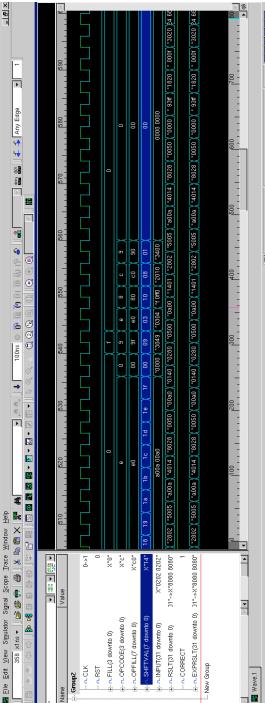

| 2.18 | 32-Bit Shift Module Functional Simulation      | 41 |

| 2.19 | 32-Bit MAC-2 Module Functional Simulation      | 41 |

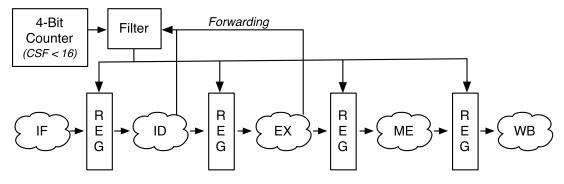

| 3.1  | Five-Stage Core Architecture Adaptation        | 44 |

| 3.2  | <sup>1</sup> / <sub>2</sub> MAC Execution Core | 46 |

| 3.3  | Shift Centric Core                             | 48 |

| 3.4  | Comparator Centric Core                        | 49 |

| 3.5  | Original ExCore Layout                         | 50 |

| 3.6  | ExCore                                         | 51 |

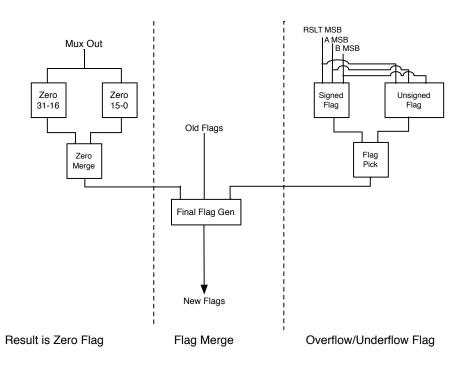

| 3.7  | Flag System                                    | 52 |

| 3.8  | Module Forwarding Schemes                      | 54 |

| 4.1  | Power Consumption of FPGAs                     | 58 |

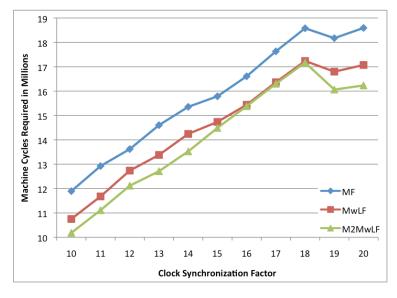

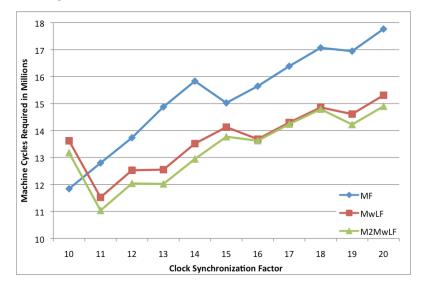

| 4.2  | 1/2MAC Performance for SC Benchmark            | 64 |

| 4.3  | ExCore Performance for Compress Benchmark      | 64 |

| 5.1  | Shift Cell Scaling                             | 74 |

| 5.2  | Cellular Utilization Characterization          | 76 |

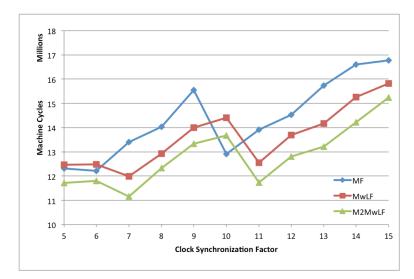

| 5.3  | ExCore Cycles for the Espresso Benchmark       | 78 |

| 5.4  | ExCore Energy Characteristics for the Espresso Benchmark            | 78  |

|------|---------------------------------------------------------------------|-----|

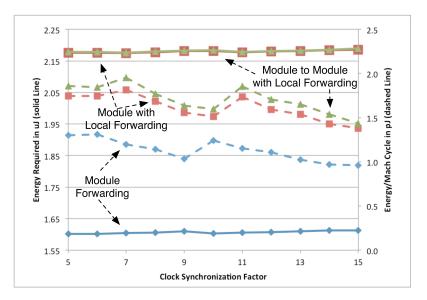

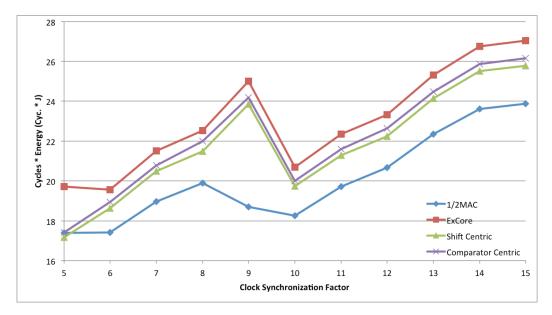

| 5.5  | Cycles × Energy vs. CSF for Espresso Benchmark on ½MAC Core         | 80  |

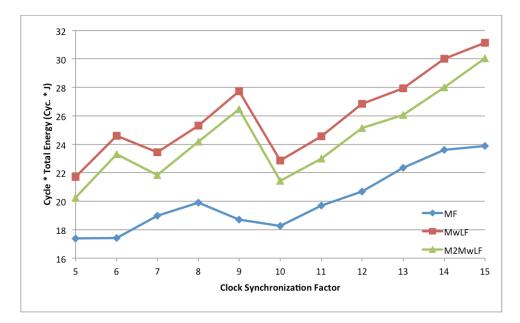

| 5.6  | Core Cycles × Energy Characterization for Espresso                  |     |

|      | Benchmark Utilizing Module Forwarding                               | 81  |

| 5.7  | Core Cycles $\times$ Energy Characterization for Espresso Benchmark |     |

|      | Utilizing Module to Module with Local Forwarding                    | 82  |

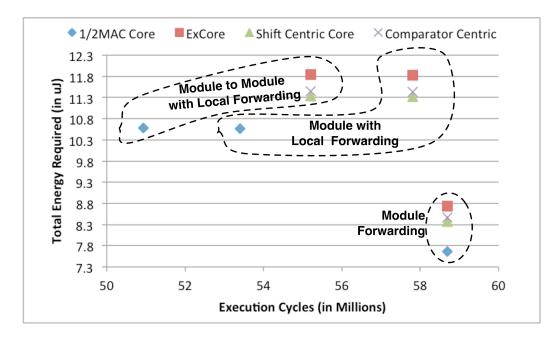

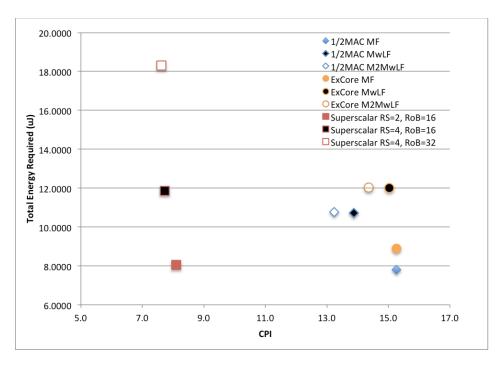

| 5.8  | Total Energy vs. Total Cycles                                       | 83  |

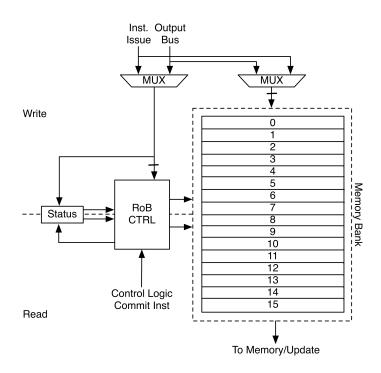

| 6.1  | Reorder Buffer Structure                                            | 87  |

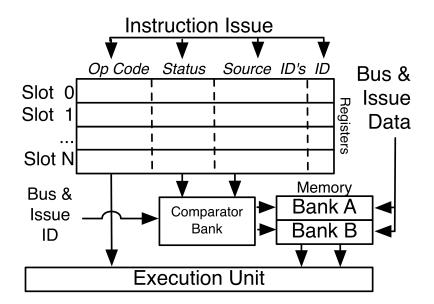

| 6.2  | Reservation Station Structure                                       | 90  |

| 6.3  | Two Slot Reservation Station Cellular Layout                        | 91  |

| 6.4  | Four Slot Reservation Station Cellular Layout                       | 91  |

| 6.5  | Superscalar Core                                                    | 92  |

| 6.6  | Reorder Buffer Average Usage by Area Required                       | 97  |

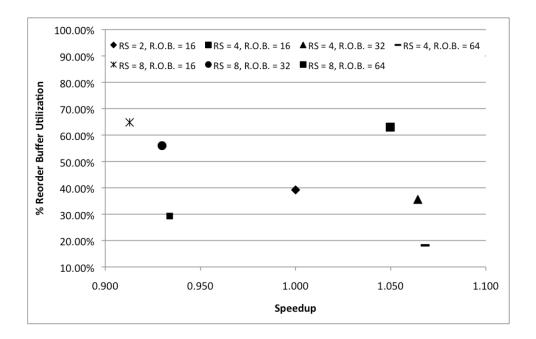

| 6.7  | Reorder Buffer Usage vs. Speedup                                    | 98  |

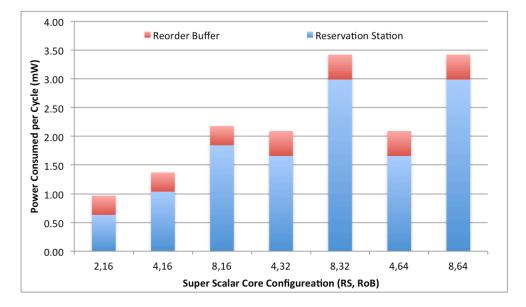

| 6.8  | Power Requirements for Varying Reservation                          |     |

|      | Station and Reorder Buffer Configurations                           | 99  |

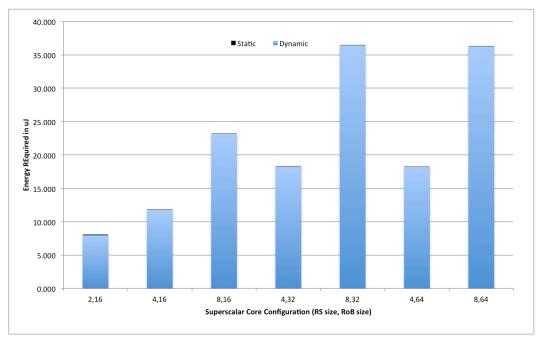

| 6.9  | Energy Required for Executing 3.85 Million Instructions             | 100 |

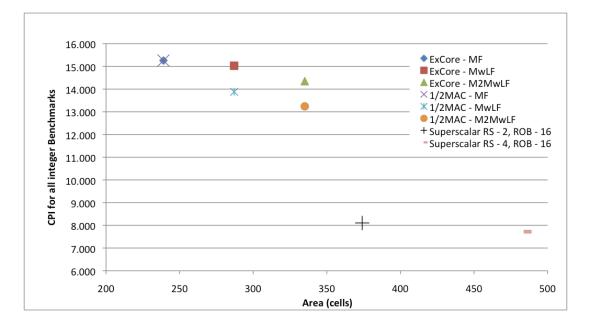

| 6.10 | Superscalar and Five-Stage CPI vs. Area                             | 102 |

| 6.11 | Superscalar and Five-Stage Energy vs. CPI                           | 103 |

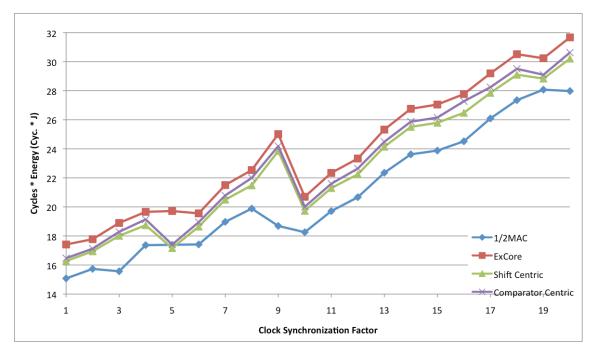

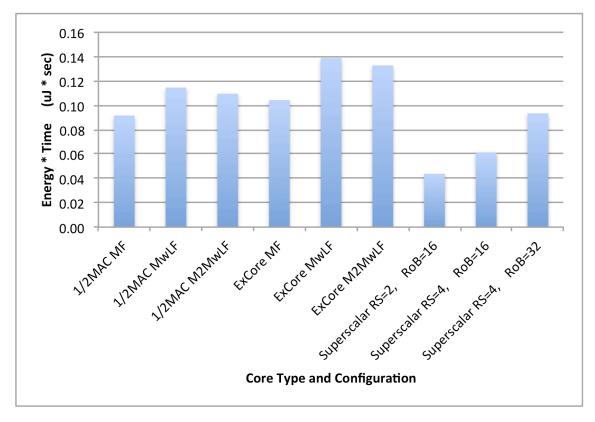

| 6.12 | Superscalar and Five-Stage Energy-Delay Product                     | 104 |

## Chapter 1

# Introduction and Background

As computer technology continues to advance the reliance of more devices upon general-purpose processors or microcontrollers continue to grow. This in part is due to the falling costs of digital devices, and the ease with which they can be designed and updated. To help integrate digital systems, designers have increasingly focused on two major design paradigms to implement digital systems, the first being to utilize specialized application specific integrated circuits (ASICs), the other is to focus on a single chip implementation that can be comprised of a System-on-Chip or reconfigurable hardware. All of these options typically rely on some form of a processing unit to execute the code that manages the device's operation.

While ASICs and System-on-Chip designs typically have high performance processing units available, reconfigurable hardware offers promising alternatives to these platforms such as the ability to rapidly prototype systems and the potential for fault tolerance; faults may be avoided by routing around the faults. One such platform that has been developed is a medium grain reconfigurable architecture [1] based solely on memory cells, which allow for complete flexibility in design placement and fault avoidance since there is no special hardware components that require set design placement to access. To date the hardware has been used for the implementation of DSP algorithms. The primary focus of this work is the implementation of a MIPS compliant processor core for the target reconfigurable hardware that will not only provide reliable general purpose computing, but be easily translated into more complex processing architectures that provide high levels of performance. A secondary goal is the ability to provide a means for encrypting and decrypting data using the Advance Encryption Standard (AES) algorithm since the algorithm is not able to be efficiently implemented in code for standard processors without specialized execution hardware and instructions.

### 1.1 Background

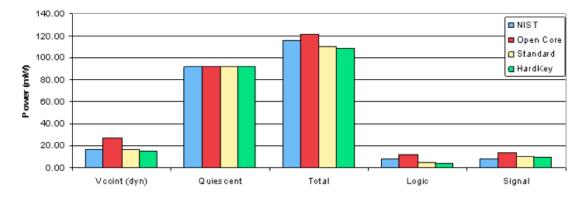

This research study started with a primary focus of finding a reconfigurable hardware method for securing communication between wireless sensor networks (WSNs). The means of securing communication was not the only critical concern, but special attention had to be given to the energy required to secure the communications since many WSNs rely on low power sensor nodes. The AES algorithm was chosen as the focus because of its prominence in private and symmetric key encryption algorithms. In the initial study FPGAs were chosen to investigate the implementation issues surrounding AES and how they could affect the power required to secure communications. It became readily apparent that while FPGAs could increase hardware utilization and reduce the physical chip count, the power required to integrate an FPGA would not always be possible or prudent, which will be explained further in Chapter 4. As a result the research shifted focus from FPGAs to a novel Medium-Grain Reconfigurable hardware platform that is expected to be much more power conscious and adaptable to new technology implementations, which will allow maximum performance for minimal power.

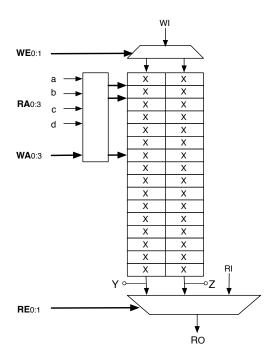

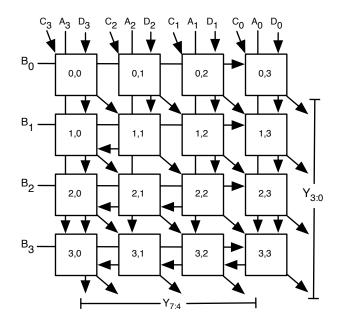

In the following paragraphs an overview of the target hardware's architecture is presented. The smallest piece of reconfigurable hardware is termed an element, and similar to most modern reconfigurable hardware designs the core of this hardware is memory. Each element contains 32 1-bit memory locations organized into two 16-bit columns. The memory bank is surrounded by interface components that allow for control of the memory that includes read and write capabilities along with multiplexers for routing data, which also provides the ability to act as a pass-through for other element outputs. The elemental structure is shown in Figure 1.1.

Figure 1.1: Structure of an Element

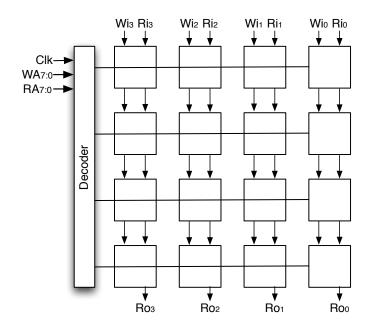

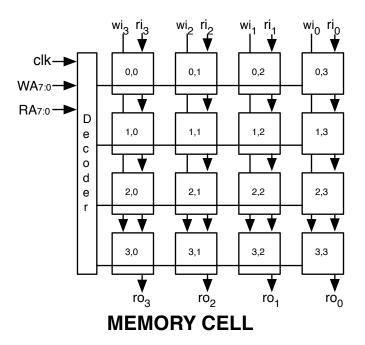

The reconfigurable hardware is then organized into cells containing a 4×4 grid of elements and is the smallest amount of hardware that can be individually allocated to a design. Each cell can take on one of two configurations, which define how the memory is accessed. The first mode that will be detailed is the Memory mode, and is shown in Figure 1.2. In memory mode the elements are organized into a 128×4-bit memory bank. These structures provide independent read and write control signals, which are used to offer single cycle concurrent read and write operations, to any of the 128 memory locations.

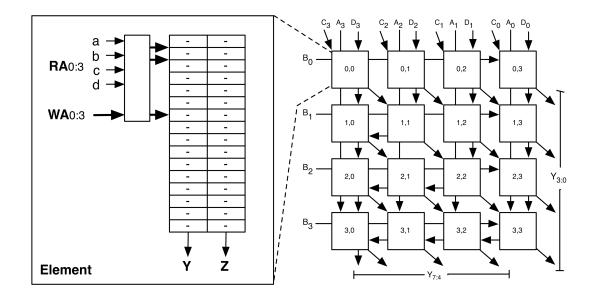

Cells and elements can also be configured to operate in math mode, as shown in Figure 1.3. In math mode the write control signals are disabled turning each element into a 4 input look up table (LUT) with two outputs, which are the Y and Z

Figure 1.2: Cell in Memory Mode

lines detailed in Figure 1.1. By disabling the read enable mux the cell becomes flexible and dynamic by allowing the elements to more easily communicate with each other, facilitating the implementation of more complex mathematical functions. This capability allows for the math cell's output to become 8-bits wide compared to the 4bit output in memory mode. The structure of the math cell was chosen to allow for a multiply and accumulate operation to be computed, which is detailed in Chapter 2.

The target hardware contains two parallel communication networks, one being a local mesh network and the other being a global tree network [2]. The local mesh network connects neighboring cells together and allows for any neighboring cell to be communicating data with minimum delay, while the global pipelined communication tree is used to allow cells to communicate with distant cells. Utilizing the global pipelined tree incurs a single cycle of delay for every level traversed; this is

Figure 1.3: Element and Cell in Math Mode

turn leads to a logarithmic delay time with respect to the distance between cells. An additional cycle of delay can be added in each node of the tree to allow for data arrival synchronization.

One of the key attributes that help to differentiate this architecture from traditional reconfigurable hardware platforms is how the clock is defined. Most reconfigurable hardware platforms determine the maximum clock rate by the longest delay in logic between memory elements, however the target hardware defines the maximum clock frequency by the time required for a cell to complete its most complex operation, which can be roughly calculated as one over seven times the elemental delay. This was done so that 4-bit multiply and accumulate operations could be carried out in a single cycle by a cell in math mode. The clock rate is facilitated by built-in pipelining registers on each of the cell's outputs and pipelined communication tree. This means that the maximum clock rate is technology dependent and not on the mapping of a given design. In simulations it has been shown that using 180 and 90 nm MOSFETs allows for clocks speeds of 267 and 720 MHz, respectively [3]. Scaling these results show that a speed of 2 GHz can be achieved in 45nm or better technology. Ongoing research utilizing future technologies such as FinFETs, similar to Intel's 3D or tri-gate Transistors [4], has shown that speeds of 3 to 5 GHz can reasonably be achieved [5].

## 1.2 Outline

In the remainder of this study the following topics will be introduced. Chapter 2 will provide an explanation of how the different execution modules that facilitate MIPS compatibility and carry out the computational operations will be presented, including details on implementation. Next in Chapter 3, the proposed schemes for using the modules together as an execution core for a five-stage processor will be introduced, along with the ways in which forwarding can be implemented and optimized. Chapter 4 will provide an analysis of our approach and its results. This will include a more thorough discussion of the work with FPGAs, a performance evaluation of the designs and their custom configuration options, and finally a comparative analysis of this work with other reconfigurable hardware based processors. An investigation of the power consumption characteristics of the hardware for a five-stage core as well as how the hardware is organized will be presented in Chapter 5. Chapter 6 will focus on the work done to investigate the implementation of a superscalar core and how its performance compares to that of the completed five-stage cores in performance, cell count, and energy required. Lastly, Chapter 7 offers concluding remarks including what knowledge was gained and how this research should continue to proceed in the future.

# Chapter 2

# **Execution Modules**

In this chapter the modules required to implement a processor core and facilitate AES encryption and decryption operations will be introduced. In keeping with the separation of primary and secondary goals as outlined in the chapter 1 the first group of modules that will be introduced are those designed to facilitate AES encryption and decryption operations. Next the modules that have been designed for the implementation of a processor core will be introduced. Each module discussion will include its provided operations, cellular implementation, sizing, and layout details. Once all modules have been introduced the means by which they were verified to function as intended will be provided. The actual bit configuration for the modules detailed in this chapter can be found in Appendix A.

## 2.1 AES Components

In this section the modules that have been designed to facilitate hardware based encryption and decryption of data utilizing the AES algorithm will be introduced. The reason why AES has been chosen is that it has become the standard for symmetric-key cryptography since it became officially adopted and approved of by the US Government in 2002 and is detailed in [6]. The AES algorithm encrypts data in 128-bit blocks that are organized into 4x4 matrices of 8-bit values, called state, which means that modules must operate on 8-bit blocks of data at a minimum rather than the 4-bit blocks used in the processor components. There are four primary transformations that take place during encryption and decryption, three of which will be presented in the following sections. The reason why only three of the transformations are detailed is that one of the transformations, termed the Shift Rows transform, has been demonstrated to provide better performance when implemented in the data routing network and not using logic elements [7] or in the target hardware's case cells. Lastly the key expansion transformation will be detailed along with how it can be implemented using the other components described.

| $ \begin{bmatrix} 1 & 0 & 0 & 0 & 1 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 & 1 & 1 & 1 \\ 1 & 1 & 1 & 0 & 0 & 0 & 1 & 1 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 1 \\ 1 & 1 & 1 & 1 & 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 &$ | <b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b><br><b>X</b> | $+ \begin{bmatrix} 1 \\ 1 \\ 0 \\ 0 \\ 1 \\ 1 \\ 1 \end{bmatrix}$ |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--|

| 00111110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | X <sub>6</sub><br>X <sub>7</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1<br>0                                                            |  |

Equation 2.1: S-Box Transform

### 2.1.1 S-Box Transform

The S-Box, meaning substitution box, transform is what produces nonlinearity into the AES cipher. The mathematical operation that is performed in this transform is derived from a multiplicative inverse over the finite field {2<sup>8</sup>} and is combined with an affine transform to strengthen the transformation against simple algebraic attacks. This transform represented mathematically is shown in Equation 2.1. This computation though is not easily implemented in hardware, but lends itself particularly well to implementation via LUT, because the mapping is 1:1 and thus only 256 8-bit memory locations are needed. By focusing on the LUT implementation the resulting module will be the most ideally optimized for the target hardware since the target hardware is already made up of pure memory and can be used in a efficient manner with minimal delay for computation.

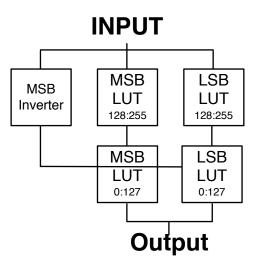

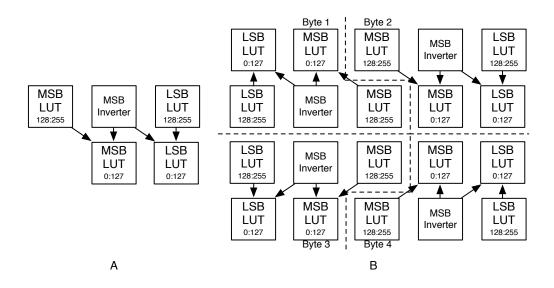

Figure 2.1: S-Box 8-Bit LUT Implementation

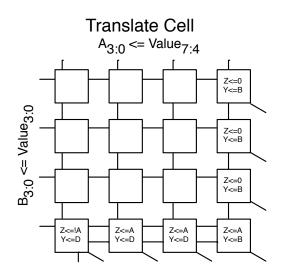

The design that was settled on for an 8-bit LUT module is detailed in Figure 2.1, and is built with 5 cells. Since each cell is able to provide 128 4-bit memories two cells are needed in parallel to produce an 8-bit string, two serially connected cells are also needed to provide 256 different memory locations which results in the two parallel cells feeding serially into two other parallel cells. The fifth cell is used as a data read control signal, since the input data is already 8-bits and the most significant bit in the memory cell serves as a read enable all that must be done to utilize the serially connected cells is to invert the MSB of the input. This means that the upper cells contain all the transforms for inputs ranging from 128 to 255, while the lower cells contain the transforms ranging from 0 to 127.

The inverse operation for this transformation known as the Inverse S-Box is implemented the same way as the forward S-Box with the only difference being the contents of the LUTs. These modules require 2 cycles to perform the transform and

Figure 2.2: S-Box Hardware Layout

require 5 cells for every 8-bits of data that must be concurrently processed. A physical layout for an 8-bit module is shown in Figure 2.2A, and as is shown in Figure 2.2B four transforms allowing for a 32-bit data path can be fit into a 4x5 block of cells without any wasted hardware.

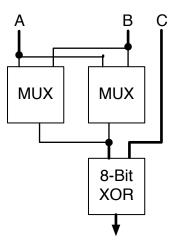

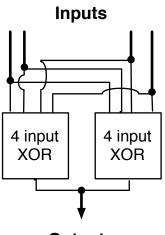

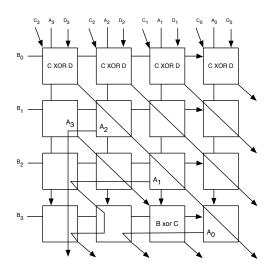

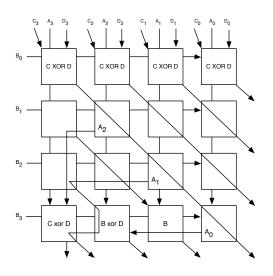

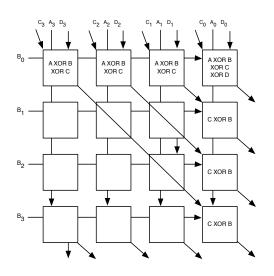

### 2.1.2 Add Round Key Transform

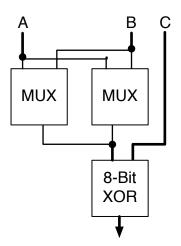

The Add Round Key transformation is carried out through the XORing of the 128-bit state with one of the round keys. Since the inverse of an XOR function is an XOR function the inverse Add Round Key transformation is itself a simple XOR operation. Although this transform could be carried out using the logic cell presented in section 2.2.1, an 8-bit XOR cell has been designed, shown in Figure 2.3, which reduces the cells needed for adding round keys by half. This translates into a forward

Figure 2.3: 8-Bit Xor Cell

and inverse transformation requiring 1 cell per 8-bits of data being concurrently processed and 1 cycle of delay to complete the designated transform.

It should be noted that when the last round of encryption is being computed the Mix Column transform is omitted from the round. Rather than implement two round blocks in hardware a simple solution is to attach multiplexers to the input of the Add Round Key transformations which can choose the data coming from to Mix Column module or the result of the S-Box transformations via the hard wired Shift Rows transform. This can be seen in Figure 2.4 adds two cells to the Add Round Key module per 8-bits of processed data, and increases the delay by one cycle but greatly reduces overall cell count for most standard AES implementations.

Figure 2.4: Alternate Add-Round-Key

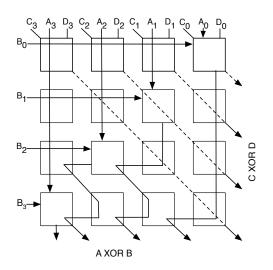

## 2.1.3 Mix Columns Transformation

The Mix Columns operation is the only operation that requires more than 8bits of data at once, since the shift row transformations can be carried out through routing. The Mix Column operation and its inverse are shown in Equation 2.2 A and B, and generate new values for each of the values in the state by using a series

$$\begin{bmatrix} 2 & 3 & 1 & 1 \\ 1 & 2 & 3 & 1 \\ 1 & 1 & 2 & 3 \\ 3 & 2 & 2 & 1 \end{bmatrix} \times \begin{bmatrix} s_{0,0} s_{0,1} s_{0,2} s_{0,3} \\ s_{1,0} s_{1,1} s_{1,2} s_{1,3} \\ s_{2,0} s_{2,1} s_{2,2} s_{2,3} \\ s_{3,0} s_{3,1} s_{3,2} s_{3,3} \end{bmatrix} = \begin{bmatrix} s'_{0,0} s'_{0,1} s'_{0,2} s'_{0,3} \\ s'_{1,0} s'_{1,1} s'_{1,2} s'_{1,3} \\ s'_{2,0} s'_{2,1} s'_{2,2} s'_{2,3} \\ s'_{3,0} s'_{3,1} s'_{3,2} s'_{3,3} \end{bmatrix}$$

A: Forward Mix Column Transform

$$\begin{bmatrix} E & B & D & 9 \\ 9 & E & B & D \\ D & 9 & E & B \\ B & D & 9 & E \end{bmatrix} \times \begin{bmatrix} s_{0,0} s_{0,1} s_{0,2} s_{0,3} \\ s_{1,0} s_{1,1} s_{1,2} s_{1,3} \\ s_{2,0} s_{2,1} s_{2,2} s_{2,3} \\ s_{3,0} s_{3,1} s_{3,2} s_{3,3} \end{bmatrix} = \begin{bmatrix} s'_{0,0} s'_{0,1} s'_{0,2} s'_{0,3} \\ s'_{1,0} s'_{1,1} s'_{1,2} s'_{1,3} \\ s'_{2,0} s'_{2,1} s'_{2,2} s'_{2,3} \\ s'_{3,0} s'_{3,1} s'_{3,2} s'_{3,3} \end{bmatrix}$$

B: Inverse Mix Column Transform

Equation 2.2: Mix Column and Inverse Mix Column Transformations

weighted summations of each column. The purpose of this transform is to increase entropy in the encrypted data and to ensure that the final output is dependent upon all of the plaintext and intermediate round bits.

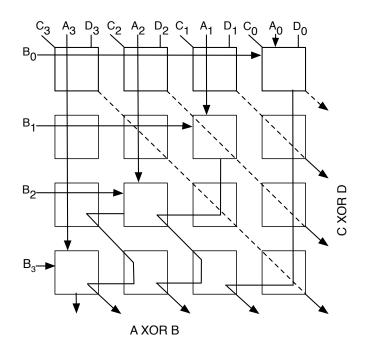

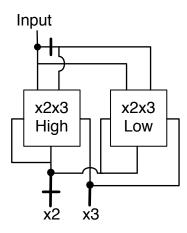

To implement the forward transformation each of the column's state values must first be multiplied by two and three, which can be done using only two cells as shown in Figure 2.5. The cells take in the input data and generate their corresponding x2 result that is then output and routed back to the cells input. Once the x2 result is sent back to the cell inputs, it is combined with the original input, delayed one cycle and sent to another input, to generate the x3 result. This means that the two required factors for completing the Mix Column transform can be generated using two cells and two cycles of delay. The designated results of the multiplication blocks along with original data values can then be fed into two parallel cells capable of a four input 4-bit XOR operation to generate each of the new state column values.

Figure 2.5: Multiply by 2 and 3

This means that 16 cells and 3 cycles of delay are needed to complete the forward Mix Column operations for a single column of the state when using a four input XOR block. There may be one or two cycles of added delay though as signals are routed to more distant cells. The inverse Mix Column transform requires scaling factors of 14, 13, 11, and 9, which can be done through a series of x2 multiplier blocks as detailed in [8], which would increase the cells required to 52 and the delay to 7 cycles. Further optimizations may be possible to reduce cell count for the inverse transform, but this would most likely increase the total delay of the unit.

### 2.1.4 Key Expansion

Since the AES algorithm is based on repeated rounds of transformation operations the original key must be used to generate a unique key for every round called a round key and is used to ensure maximum entropy in the encryption process. The processes of generating new keys is the largest transformation of the AES algorithm, but can be looked at as a series of 4 smaller transformations. The key expansion process is the same regardless of whether encryption or decryption is being carried out and all that changes is the order in which the round keys are used.

Round keys are generated using the original key or the previous round key and a round constant that can be stored in a LUT. The round key is generated using the following steps and is shown in Figure 2.6: **Rotate Word:** The rotate word transform takes the final 32 bits of the state and performs a right rotate of 8 places. This transform like the Shift Rows Transform is best accomplished through direct routing.

**Substitute Words:** The final 32-bits of the key then undergo a bit substitution to increase differences between round keys. The substitution that is carried out on the bits is the same S-Box substitution previously described in this section 2.1.1 and would require 16 cells and three cycles of delay.

Add Round Constant: A round constant is then added to bits 96 through 103 through an XOR operation. The round constant is best implemented through the use of a LUT and 8-Bit XOR cell, which would require three cells and one cycle to complete the operation.

Figure 2.6: Key Expansion

**XOR Stage:** The result of the previous transformations is then XORed with the first 32-bits of the previous key to generate the first 32-bits of the new round key. The newly generated bits are then XORed with the second 32-bit block from the previous key to generate the next 32-bits of the new round key, which is repeated until the new key reaches 128 bits or 4 words. The method used to implement this process that best balances cell count and delay would include 16 8-bit XOR cells and require 4 cycles of delay.

The cell count and delay requirements of the key expansion process as shown in Figure 2.6 would be 37 cells and 7 cycles, with the round constant LUT adding 2 cells to the total cell count. However it is possible for the round constant to be generated as part of the control logic and eliminate the 2 LUT cells.

## 2.2 Processor Modules

Before the actual components that make up an ALU or other critical CPU components could be designed the required functionality needed be determined. As previously mentioned it has been decided to provide a set of instructions that would be compatible with the MIPS instruction set as outlined in [9]. Using this as a base line for functionality allows for some flexibility in the design process, if an implementation could offer additional functionality without detrimentally affecting the component's size and delay characteristics than the added functionality would be included. Another goal of the design process has been to ensure that the modules can scale efficiently and are not locked to a set data path width. In the remainder of this section the designed components are presented, each component discussion includes an overview of how a four-bit operation is carried out along with a description of how the design can be expanded to more than 4-bits. Finally a brief discussion is provided on other support components that are critical for the implementation of a processing unit. An early version of these components has been presented [10].

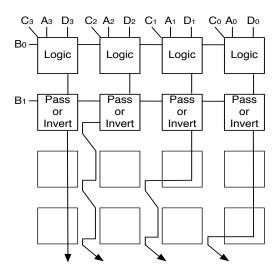

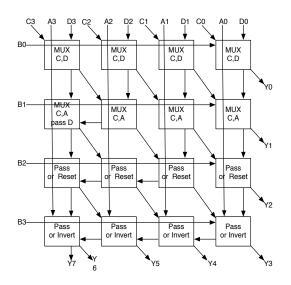

### 2.2.1 Bitwise Logic

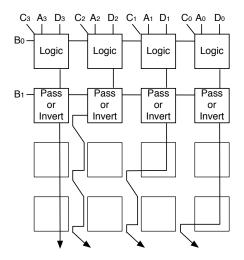

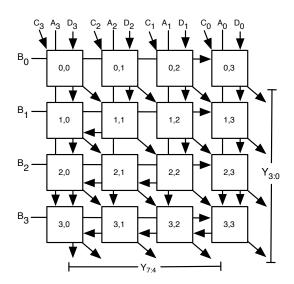

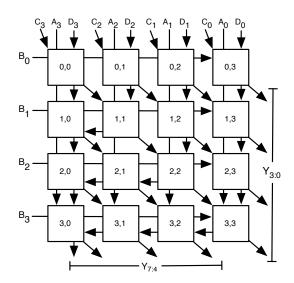

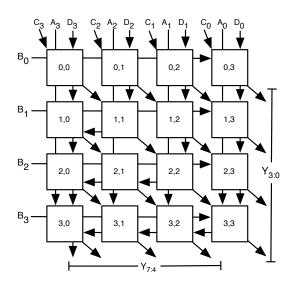

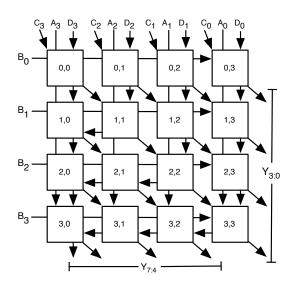

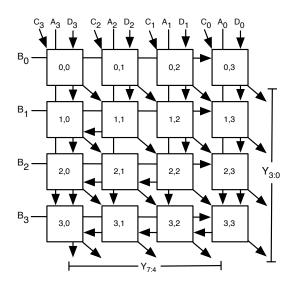

When implementing a unit for bitwise logic the critical functions that must be included are AND, OR, XOR, and NOT. This fits perfectly with the target hardware since two inputs could be allocated as data inputs  $\{C_{3:0}, D_{3:0}\}$ , with the other two inputs  $\{A_x, B_0\}$  being allocated for use as a function select. The remaining cells in the design could be used to route the data to either the Y<sub>7:4</sub> or Y<sub>3:0</sub> outputs. Using this implementation all of the logic operations contained in the standard MIPs ISA could be provided.

In keeping with the goal of providing extra functionality when there would be little or no cost to the cell count or delay requirements for a execution unit it was decided to use the second row of elements and the B<sub>1</sub> input as an optional inverter. This meant that with the use of 1 extra input bit in an established control signal the logic functions, NAND, NOR, XNOR, and a pass-through could be provided. This is shown in Table 2.1, and Figure 2.7.

| Control Index                     | B <sub>1</sub> |          |

|-----------------------------------|----------------|----------|

| (B <sub>0</sub> ,A <sub>n</sub> ) | 0              | 1        |

| 0,0                               | C and D        | C nand D |

| 0,1                               | C or D         | C nor D  |

| 1,0                               | not C          | С        |

| 1,1                               | C xor D        | C xnor D |

TABLE 2.1: LOGIC OPERATIONS AND CONTROL SIGNALS

Figure 2.7 Logic Cell Organization

One of the benefits to bitwise logic is that there is no need for any knowledge about neighboring bits or their result to complete the designated operation. This results in a completely parallel computation structure, with the delay remaining unchanged for any path width and the cells required for a given operation to be calculated by simply dividing the path width by four. For a 16-bit unit four cells are required and one cycle is needed to complete any supported operation, similarly a 64bit unit requires 16 cells and one cycle to complete a given operation.

Figure 2.8: Logic Module Layout and Placement

When it comes to layout this unit is the most flexible of all of the units, since there is no need to communicate information about other bits such as their input values or output. This allows for the Module to be placed in as small a region as possible, or spread out and placed in cells that are not being used, but surrounded by cells currently allocated for other modules. The most obvious way to layout the modules is shown in figure 2.8, where in 2.8 A the cells are placed in a straight line. Alternately in Figure 2.9 B the cells are placed in a rectangle where X×Z equals the Path Width divided by 4.

### 2.2.2 Multiplication, Addition, and Subtraction

Rather than design components for each of these operations it was decided to use a component originally detailed in [11] and for which the math cell was designed.

Figure 2.9: Cell Types based on Elemental Configuration

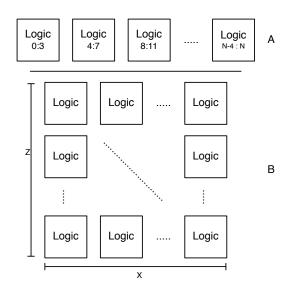

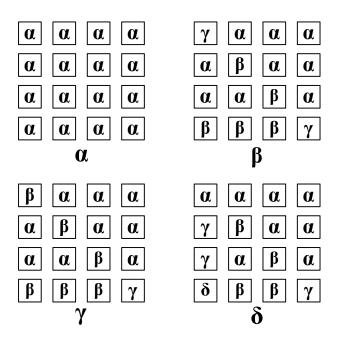

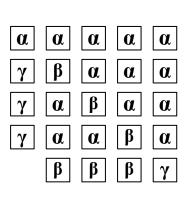

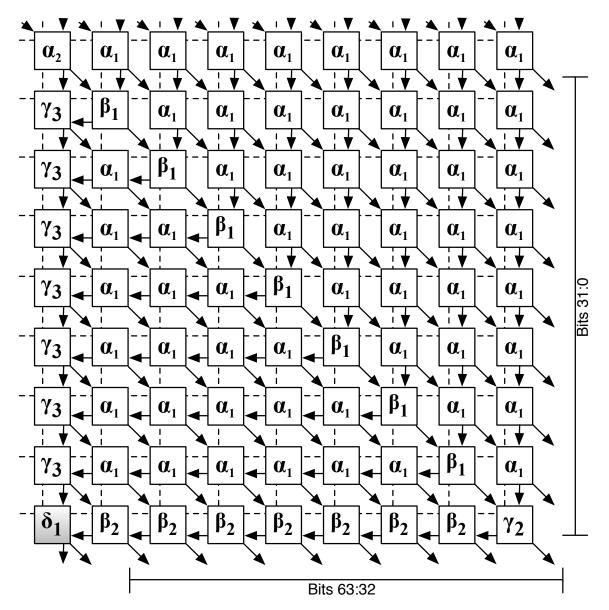

The unit is able to carry out a multiply and accumulate (MAC) operation. When every element in a cell is programmed to implement (2Z + Y) = (A AND B) + C + D, a 4-bit MAC of the form  $(A \times B) + C + D$  is obtained, with the resulting output being an 8-bit value. This configuration though is only for unsigned numbers, but with minor changes can be adapted to accept signed values, along with varying input widths. The changes that are required to enable the module to accept signed numbers involve changing the configuration of elements internal to each cell. The four elemental configurations that can enable a signed MAC operate are termed Alpha, Beta, Gamma, and Delta, and are chosen based on which if any of its inputs represent a sign bit. Using these elemental configurations there are four separate cellular configurations that are used to make up a MAC unit greater than 4-bits. The four different cell types

A: Standard Signed MAC Unit

B: 16-Bit MAC-2 Unit and Layout

Dashed lines represent signed bits

Figure 2.10: 16-Bit MAC Units

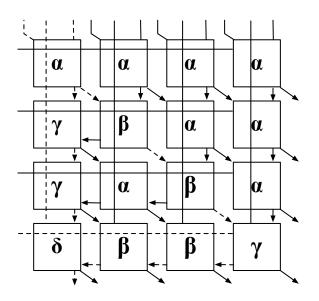

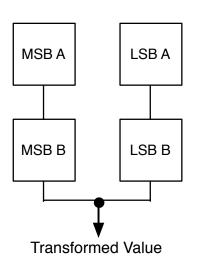

are detailed in Figure 2.9 and show how the different elemental configurations are used to implement the cells, which share the same naming scheme as the cells themselves. Figure 2.10A shows the implementation of a 16-bit MAC unit and how signed bits are routed through the MAC unit.

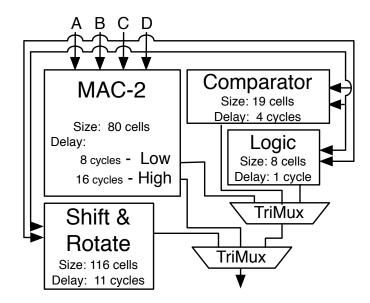

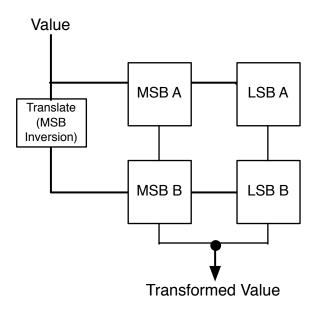

The obvious method for providing signed and unsigned operations in a processor core is to utilize 2 MAC units one configured for each type of input. However, this is not a responsible use of hardware, so a different method had to be found. The solution that was derived and termed the MAC-2 is based on implementing an optional sign extension module, which could be placed in the instruction decode section of a processor, and then to implement a MAC unit that was capable of computing a multiple and accumulate operation of N+4 bit, and then ignoring the highest 8 bits of output. The benefit of this method is detailed in Table 2.2. As Table 2.2 shows the savings is minimal in terms of cell count for 8 bit data paths, but rapidly increases to almost 50% for larger data path widths. Additionally by utilizing the MAC-2 any standard arithmetic function can be completed except for division by controlling which input the data is routed to. As is shown in Table 2.3 multiplications can be computed by sending the data values to the A and B MAC-2 inputs. Subtraction operations can be accomplished by multiplying the subtrahend by -1 and adding it to the minuend. Addition operations can be completed by simply routing the two addends to the C and D inputs, but to minimize input usage and hardware routing paths the operation will be computed by multiplying the augend by 1 and adding the other addend to its result. Furthermore if a specific application required incrementing operations by set amounts the MAC-2's unused input could be adapted for that purpose, much like the ARM processors use barrel shifters in conjunction with adders for quick multiplications [12].

| Path Width |     | Area in Cel | MAC-2 Savings |               |  |

|------------|-----|-------------|---------------|---------------|--|

|            | MAC | Dual MAC    | MAC-2         | over Dual MAC |  |

| 8          | 4   | 10          | 8             | 20.00%        |  |

| 16         | 16  | 36          | 24            | 33.33%        |  |

| 32         | 64  | 136         | 80            | 41.18%        |  |

| 64         | 256 | 528         | 288           | 45.45%        |  |

TABLE 2.2: MAC UNIT CELL COUNT COMPARISONS

As is demonstrated in Table 2.2 the MAC-2 unit scales at a rate of (N/4)<sup>2</sup>-1, while the delay required for operation scales at a rate of N/4 cycles for N-bit operations or N/2 cycles for 2N-bit operations. This translates to a 16-bit MAC-2 unit requiring 15 cells and 4 or 16 cycles and a 64-Bit MAC-2 unit requiring 255 cells and 8 or 32 cycles for N and 2N-bit operations respectively. One drawback to the MAC units is that they require a set placement pattern that allows for built in pipelining to be utilized if needed and to eliminate extra delay when communicating carryout or borrow-in information. Figure 2.10B shows the required implementation for a 16-bit MAC-2 unit.

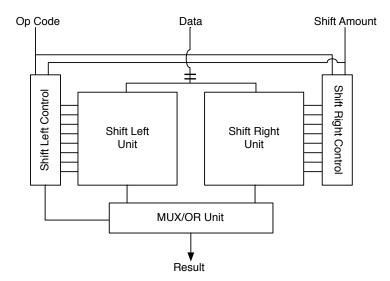

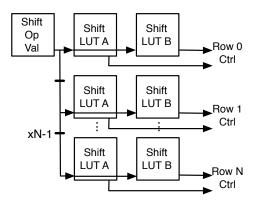

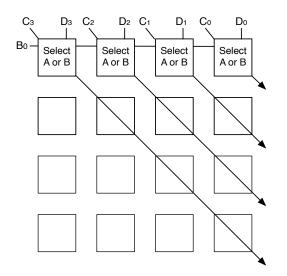

#### 2.2.3 Shifting and Rotating

When designing the shift module the main operations that needed to be included were the shift left logical, shift right logical and shift right arithmetic operations. After examining different methods for implementing the unit a shifter has been chosen that would reduce delay and hardware when compared to more popular barrel shifters like those detailed in [13]. The shifter is made up of a single shifting

| MAC     | Input |   |   |   |  |

|---------|-------|---|---|---|--|

| Fuction | Α     | В | С | D |  |

| X × Y   | Х     | Y | - | 1 |  |

| X + Y   | 1     | Y | - | Х |  |

| X - Y   | -1    | Y | - | Х |  |

TABLE 2.3: MAC-2 INPUT ORGANIZATION

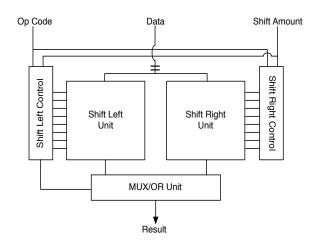

cell, which can carry out shifts of 0, 1, 2, 3, or 4 bits and relies on inputs ordered {C<sub>3:0</sub>, D<sub>3:0</sub>}. Left and right shifts require separate, but identical configuration, cells that can be connected to a MUX to choose the appropriate output.

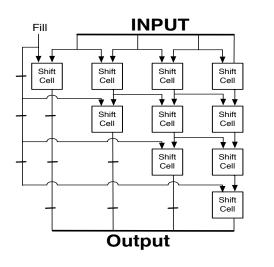

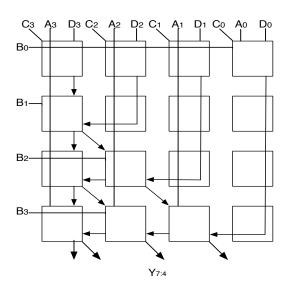

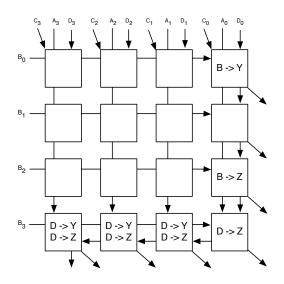

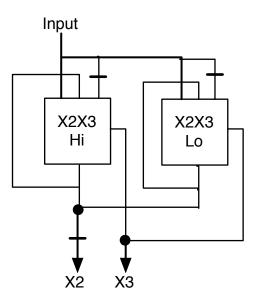

The basic shift cell is shown in Figure 2.11 and as detailed in the figure shows the top row of elements are used as bit select blocks or basic two input multiplexers. The remaining elements in the cell are configured to act as a router and based on the A<sub>3:1</sub> and B<sub>3:1</sub> inputs can route the selected bits to any block for output. This configuration allows for any continuous sequence of 4 bits to be output from the cell from the original input of {C<sub>3:0</sub>, D<sub>3:0</sub>}. When being used for left moving operations the input should be ordered with the original bits being sent to the C<sub>3:0</sub> input and the shift in bits occupying the D<sub>3:0</sub> input. The right moving operations require the opposite input ordering with the original bits being connected to the D<sub>3:0</sub> input and the fill bits tied to the C<sub>3:0</sub> input.

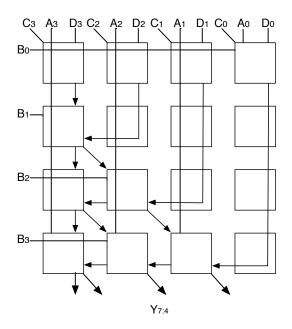

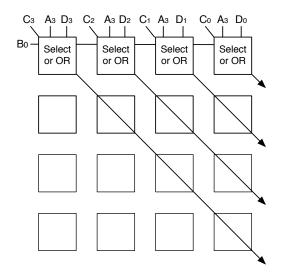

To facilitate operands greater than 4 bits, cells must be used in parallel with bits being shifted into one block being the primary bits in the neighboring block. Additionally shifts of greater than four bits can be implemented in one of two ways. The first method is through repeated use of the cells broken up into 4 or fewer bit shifts. An alternative method, which is used for this work, is based on feeding the output of the shifter into another shifter allowing for a total shift of 8 bits, which can be repeated to offer shifting of any number of bits. This method also allows for one shifting cell to be eliminated for every row of shifters, because if a shift of greater than four is taking place, one cell will output four of the fill bits and this will not change no matter how many more places are shifted. This is detailed in figure 2.12, which shows a 16-bit right shifter capable of shifting up to 16 places.

A rotate operation may be implemented simply by modifying the output MUX, which chooses the left or right shifter, to compute an OR operation of the two shifted values representing left and right shifts. This is only valid if the two shifters shift by complimentary amounts that when added equal the total path width. An example of this is that 8-bit value 10010110 when shifted left by 2 becomes 01011000, and when ORed with the same value shifted right by 6 (00000010), becomes a left rotate by 2 or 01011010. Since this required no additional hardware and only minor

Figure 2.11: Shift Cell

modifications of the output mux and control logic it was added to the standard functions offered in our MIPS ISA compliant architecture.

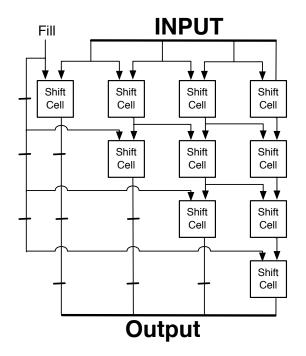

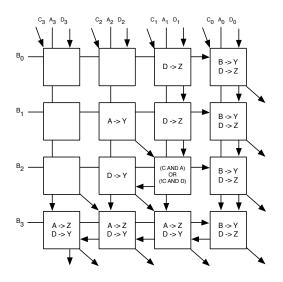

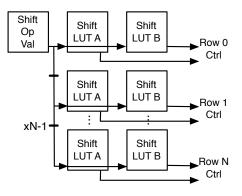

In addition to the shift cells and output mux it was decided that the control logic should be made internal to the shift module. By doing this the modules inputs could be reduced to the 3 inputs: data, shift amount, and function, eliminating the control signals needed for each row of shift cells as inputs. To generate the control signals two memory cells are needed for each row of unidirectional shifts and must be used to generate the control signals a cycle before the data arrives at the controlled cells. Additionally a cell for modifying the input shift value to a memory index is needed for each shift direction. This creates a delay overhead of 2 cycles and a sizeable increase in the total cell count requirements but ensures a self-sufficient

Figure 2.12: 16-Bit Right Shift Unit

module that can easily be integrated into any type of processor or device requiring shift or rotate functionality.

A diagram of the shifter with the control logic is shown in Figure 2.13. Like the MAC-2, the shift module relies not only on neighboring bits, but also on distant bits within a word, if the shift/rotate amount is significantly large, and serial computations. This means that rather than slowing increasing the delay in the component as the path width increases the delay increases linearly and can be calculated by computing 3+N/4. The cell count requirement for shifting and selecting an output are not easily defined by a single equation, but for a four bit shift requires  $3\times(N/4)$ , and for every for extra 4-bits of shifting  $2\times((N/4)-i)$  cells are required, where *i* is the distance from the first shifting row of cells. This leads to a 16-bit shifter requiring 24 cells for shifting, 20 cells for control logic and 7 cycles for computation,

Figure 2.13: Shift Module

similarly a 64-bit shift unit would require 288 cells for shifting, 68 cells for control logic and 19 cycles for the operation to be completed.

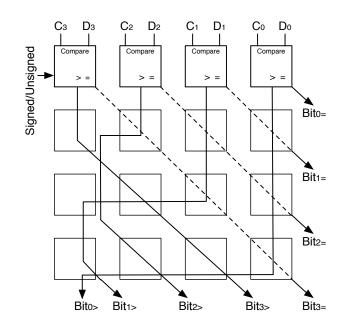

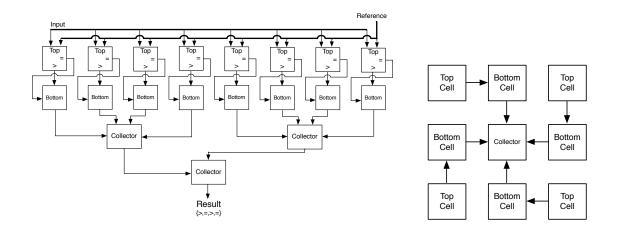

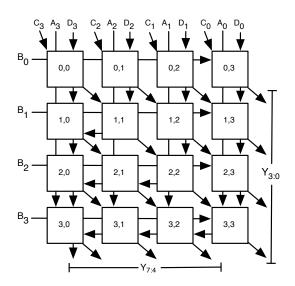

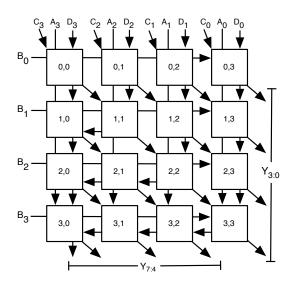

#### 2.2.4 Comparator

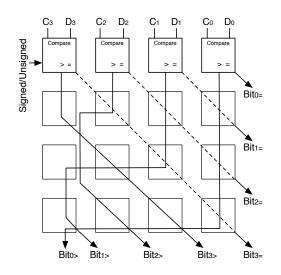

Comparators in modern processors are depended upon for two primary instruction types, the first being branching where the decision to branch is based on whether a number is equal to zero or to another number. The second major use for comparators in processors is "set on" instructions which can range from set on:  $<, >, \leq$ ,  $\geq$ , = or  $\neq$ . These instructions allow for the processor to make decisions on what to do based on the state of a register or registers. In the target reconfigurable hardware the comparator is one of the more challenging components to implement because unlike other operations there are three pieces of information needed to make a decision that are: has a decision been made, are the bits equal, or is the comparison bit greater than the reference bit. This causes one of the limitations of the math cell layout to come to light, which is that the last cell in each row can only transmit 1 bit of information about itself to the rest of the cell. To overcome this issue the comparator is broken up into 2 cells, the first being an information generation cell and the second being a decision-making cell.

The information generation cell or top cell is a very simple cell. As shown in Figure 2.14, the top row of elements in the cell output whether the bits are equal on one output and whether the comparison bit is greater than reference bit. The equal

Figure 2.14: Comparator Top Cell

bits are then routed to the  $Y_{3:0}$  outputs representing the bit order { $B_{3=}$ ,  $B_{2=}$ ,  $B_{1=}$ ,  $B_{0=}$ }. Similarly the greater than bits are routed to the  $Y_{7:4}$  outputs, except that the bit order is reversed to represent { $B_{0>}$ ,  $B_{1>}$ ,  $B_{2>}$ .  $B_{3>}$ }, which allows for the complexity of the decision cell to be reduced. If the input values are in 2's compliment form all that must be done is to have the most significant bit's information generation modified to output a greater than if the comparison bit is zero while the reference bit is 1 or vice versa, otherwise all information generation operations are the same. To include this functionality the  $B_0$  input of a cell can be used to indicate signed comparison and that standard behavior should be modified.

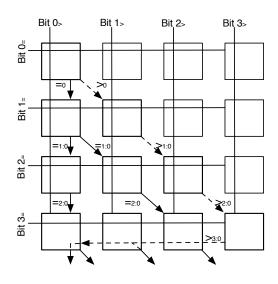

The decision cell or bottom cell, as shown in figure 2.15 is actually quite simple and elegant since the bits representing greater than comparisons have been reversed in the information generation cell, otherwise the decision cell would have become much more complex. As is shown in Figure 2.15 the cell operates on two different data paths. The first path is dedicated to the greater than comparisons and routes data from the upper left corner down to the lower right. While data is moving from element to element the greater than comparisons are merged into a single greater than decision, if a more significant bit is found to be greater than its reference than the previous decision is set aside and replaced with the most significant bit. The second data path is dedicated to equal detection and transmits data in a tree pattern, from the top of the cell to the bottom. With each additional level the equal information incorporates an additional bit of information so that by the time the data reaches the bottom of the cell, the left most three cells know if the original 4 input bits are equal or not. Using the greater than and equal bits the output Y<sub>40</sub> can be set

Figure 2.15: Comparator Bottom Cell

to show the result of any of the comparison operations on any or all of the outputs, as detailed in Table 2.4. To make the comparator more adaptable to expansion the output bits are mapped as follows:  $\{>, =, >, =\}$ .

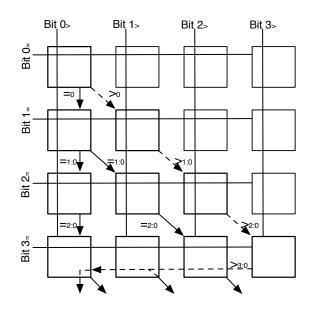

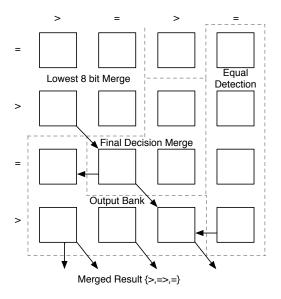

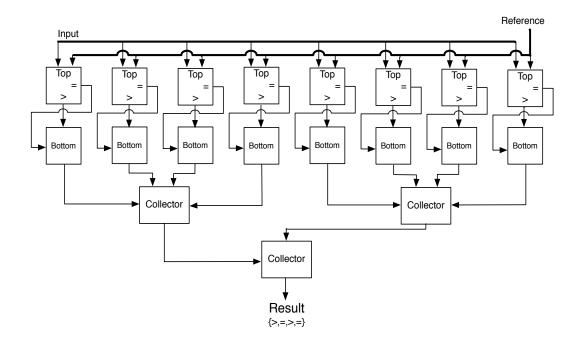

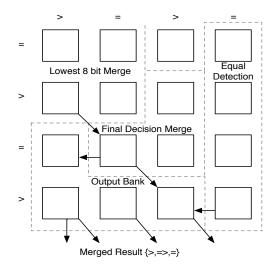

Rather than rely on the sequential nature of comparisons and chain the output of one 4-bit comparison into the input of another, a parallel implementation was adopted to reduce delay while minimally increasing the required number of cells. The final cell that needed to be designed to complete the module is a collector cell, which is shown in figure 2.16. The cell is divided into four parts with the cell's four inputs being ordered {A, B, C, D} for order of significance. Part J is used to merge the C and D inputs to make a decision on the eight least significant bits' comparison. Part K takes the resulting decision from Part J and using the A and B inputs makes a decision for the entire 16 bits on whether the comparison input is greater than the reference and passes the result to Part M. Part L checks if each of the 4-bit segments are equal and if so sets an equal bit that is sent to Part M. Finally Part M takes the output from Parts K and L and can output any of the comparative results on the Y74 output. To

| Operation   | Logic<br>Derivation |  |  |

|-------------|---------------------|--|--|

| >           | >                   |  |  |

| <u>&gt;</u> | > or =              |  |  |

| <           | !(> or =)           |  |  |

| <u>&lt;</u> | !>                  |  |  |

| =           | =                   |  |  |

| ≠           | !=                  |  |  |

TABLE 2.4: Comparator Output Generation

ensure the module is highly scalable Part M is set to output the results in the form {>. =. >. =}, which can then be sent to another collector cell if needed. Additionally output of the final collector cell can be modified to show the result of any supported comparison operations. A Diagram of the final module structure is shown in figure 2.17 A.

Using the collector cell allows for comparison operations to be computed in parallel, so that while the path width and cell count are increasing at a rate close to (N/4)×2+N/16+N/64... the delay required to complete the operation is increasing at a much slower rate, closely following 2+N/16+N/64... This translates to a 16-bit comparator requiring 9 cells and 3 cycles of delay while a 64-bit comparator requires 37 cells and only 4 cycles of delay. An added benefit of relying on parallel

Figure 2.16: Comparator Collector Cell

computations is that the comparator can be made to fit in a relatively small number of cells on the chip, as is shown in the layout of a 16-bit comparator in Figure 2.17 B.

#### 2.2.5 Other Components

Other key support units/components that allow the execution units to be integrated into a processor core are presented below. The implementation of these components is briefly described along with their basic sizing details.

*Register File.* The register file is simply a block of memory that can concurrently read two values, while writing to another. This can be built by allocating two parallel groups of cells in memory mode and connecting the write inputs to the same source. Using this model 2 cells are needed for every 4-bits in the data path and will provide up to 128 register locations. Typically there are 32 general-purpose registers plus the Hi/Lo registers for

A: 32-Bit Module Organization

B: 16-Bit Comparator Layout

multiplication and division operations, by partitioning these memory locations accordingly a processor supporting 2 threads can easily be realized.

- Program Counter. Since the program counter is meant to increment the PC value by four or another constant value a scaled down MAC unit can be used which simply takes the addends and computers next PC value. The optimized MAC is essentially the far right row in Figure 13.b and requires N/4 cells placed serially and requires N/4 cycles to generate the new PC value.

- *TriMux.* Due to the architecture of the basic math cell a 2:1 mux can be implemented that only utilizes 25% of the elements in a cell. To increase cell utilization a 3:1 mux has been designed that can also set, reset and invert the chosen input bits. This unit makes data routing much more efficient, since building a 4:1 mux requires 2 cells rather than 3 cells. The TriMux requires N/4 cells for implementation and has no specific placement requirements since cells contain no interdependencies.

- *Pipeline Registers.* Pipeline registers can be implemented by using one input of a cell in math mode as feedback from the output, which allows for the current data to be saved for multiple cycles. The remaining 3 inputs can be used for new data input, set, and reset signals. This means that one cell is needed for every 4-bits of input and can be places in nonadjacent locations.

#### 2.3 Module Functional Simulation

One important aspect of the module design process that has not yet been touched on is the method for ensuring that the designs function as intended. It is critical that each cell and module will work as expected, without exception, because they will serve as the core of a processor or coprocessor that must be reliable in order to be utilized. In this section the method used to verify the modules' functionality will first be detailed, this will include a detailed description of the method used as well as an explanation for why the method was chosen. Lastly the module functional simulation results will be described.

When attempting to verify that modules and their cells were functioning properly there were three possible choices. The first method was to use hand calculations to prove functionality; this method was quickly abandoned though due to the size and complexity of some of the modules along with the ease with which human error could be introduced. The second method considered was to utilize a simulator developed by another student, which included basic cell placement capabilities. This option was appealing but in the end could not be used due to the simulator's inability to track signals internal to modules and size constraints when implementing the larger modules such as the MAC-2 and shift modules. The final method that was considered and ultimately chosen was to use VHDL modules to implement the basic memory and math cells on an elemental level and then through component mappings connect the cells together to form each of the modules.

The VHDL approach was particularly appealing since it allowed for signals not just within a module to be tracked during simulation, but also signals within a cell, and since VHDL is a common hardware definition language it also meant that there were many software suites that could be used to complete the simulation process without having to write custom simulation software. Similarly test benches could be made to use VHDL's file IO features so that expanding a test set required only adding the additional test to a text file. This method also allowed for modules of any size to be designed, and for modules to be made of other modules if needed.

The process to ensure each of the modules started at a cellular level; first each cell type in a given module was tested to ensure it reacted properly to the given stimulus. Once each of the cells had been verified any groups of cells that were used together to carry out part of a modules operation were then tested. Finally the module was built for a 32-bit path-width and tested with a sufficient number of inputs for each provided operation to ensure that everything was functioning correctly.

Each of the processor modules as well as the support modules has been thoroughly verified to function properly through this simulation process. An example of the verification output is shown in Figure 2.18 and 2.19, which

39

demonstrates that the Shift and MAC-2 modules consistently output the correct results. Each of the modules designed to carry out encryption transformations were also verified to ensure proper functionality. Decryption transformation modules did not undergo the same thorough testing because they work identically to their encrypting transformations with only modified memory values.

ି & ▲

900 391360 391360

8 -2/

500 600 600

400

300

200

a la contra de la

•

T A

167776272 152463 152463

4294967288 2147483648

4294967295 391358

34359738367 67109904

2147483647 327680

n. A(35 downto 0) n-B(35 downto 0) n\_C(35 downto 0) n-D(35 downto 0)

2147483647

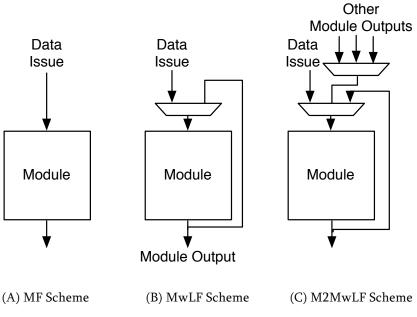

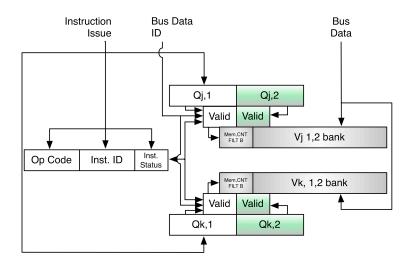

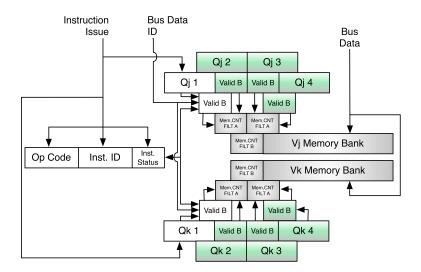

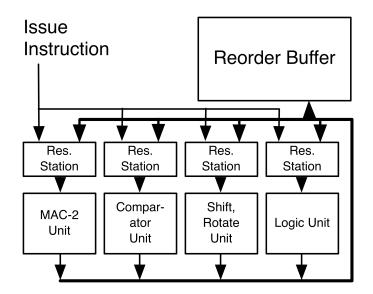

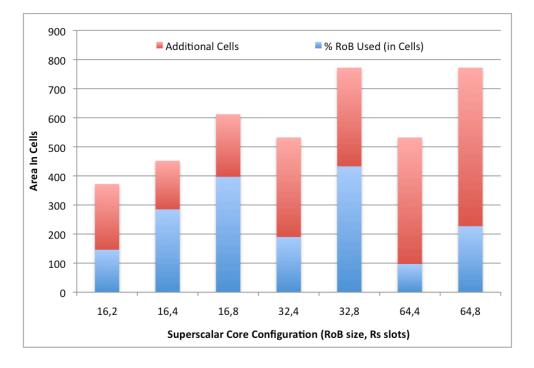

32