### University of Louisville ThinkIR: The University of Louisville's Institutional Repository

**Electronic Theses and Dissertations**

12-2017

# Control of power electronic interfaces in distributed generation.

Mohammad Mohebbi University of Louisville

Follow this and additional works at: https://ir.library.louisville.edu/etd Part of the <u>Controls and Control Theory Commons</u>, and the <u>Power and Energy Commons</u>

**Recommended** Citation

Mohebbi, Mohammad, "Control of power electronic interfaces in distributed generation." (2017). *Electronic Theses and Dissertations*. Paper 2861. https://doi.org/10.18297/etd/2861

This Doctoral Dissertation is brought to you for free and open access by ThinkIR: The University of Louisville's Institutional Repository. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of ThinkIR: The University of Louisville's Institutional Repository. This title appears here courtesy of the author, who has retained all other copyrights. For more information, please contact thinkir@louisville.edu.

# CONTROL OF POWER ELECTRONIC INTERFACES IN DISTRIBUTED GENERATION

By

Mohammad Mohebbi

B.Sc. Electrical Engineering, Amirkabir Univ. of Tech. M.Sc. Electrical Engineering, Iran Univ. of Sci. & Tech.

A Dissertation

Submitted to the Faculty of the J.B. Speed School of Engineering of the University of Louisville in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

Department of Electrical and Computer Engineering University of Louisville Louisville, Kentucky

December 2017

# CONTROL OF POWER ELECTRONIC INTERFACES IN DISTRIBUTED GENERATION

By

Mohammad Mohebbi

B.Sc. Electrical Engineering, Amirkabir Univ. of Tech.M.Sc. Electrical Engineering, Iran Univ. of Sci. & Tech.

A Dissertation Approved On

October 23, 2017

by the following Dissertation Committee:

Michael McIntyre (Dissertation Director)

Tamer Inanc

John Naber

Chris Richards

# DEDICATION

This dissertation is dedicated to my wife, Nadieh, who has been a constant source of support and encouragement during the challenges of my journey of Ph.D. and life. I am truly thankful for having you in my life. This work is also dedicated to my parents who have always loved me unconditionally.

I dedicate this work and give special thanks to my parent-in-law who never left my side. This work is also dedicated to my wonderful daughter, Nikki. I love you to the moon and back.

# ACKNOWLEDGEMENTS

This work would not have been possible without the help of many people. I would like to express my deepest gratitude to my advisor, Dr. Michael McIntyre, for his excellent guidance, advice, caring, and for giving me so many wonderful opportunities.

Similar, profound gratitude goes to Dr. John Naber, a member of my dissertation committee for his great help and strong support. I have had the pleasure to work with Dr. Naber and his research group during this and other related projects.

I extend my thanks to the rest of my committee members, Dr. Tamer Inanc and Dr. Chris Richards. Each of the members of my dissertation committee has provided me extensive professional guidance and helpful suggestions.

I would like to thank Joseph Latham, who as a good friend, was always willing to help and give his best suggestions. It would have been a lonely lab without him.

# ABSTRACT

# CONTROL OF POWER ELECTRONIC INTERFACES IN DISTRIBUTED GENERATION

Mohammad Mohebbi

October 23, 2017

Renewable energy has gained popularity as an alternative resource for electric power generation. As such, Distributed Generation (DG) is expected to open new horizons to electric power generation. Most renewable energy sources cannot be connected to the load directly. Integration of the renewable energy sources with the load has brought new challenges in terms of the system's stability, voltage regulation and power quality issues. For example, the output power, voltage and frequency of an example wind turbine depend on the wind speed, which fluctuate over time and cannot be forecasted accurately. At the same time, the nonlinearity of residential electrical load is steadily increasing with the growing use of devices with rectifiers at their front end. This nonlinearity of the load deviates both current and voltage waveforms in the distribution feeder from their sinusoidal shape, hence increasing the Total Harmonics Distortions (THD) and polluting the grid. Advances in Power Electronic Interfaces (PEI) have increased the viability of DG systems and enhanced controllability and power transfer capability. Power electronic converter as an interface between energy sources and the grid/load has a higher degree of controllability compared to electrical machine used as the generator. This controllability can be used to not only overcome the aforementioned shortfalls of integration of renewable energy with the grid/load but also to reduce THD and improve the power quality. As a consequence, design of a sophisticated controller that can take advantage of this controllability provided by PEIs to facilitate the integration of DG with the load and generate high quality power has become of great interest. In this study a set of nonlinear controllers and observers are proposed for the control of PEIs with different DG technologies. Lyapunov stability analysis, simulation and experimental results are used to validate the effectiveness of the proposed control solution in terms of tracking objective and meeting the THD requirements of IEEE 519 and EN 50160 standards for US and European power systems, respectively.

# TABLE OF CONTENTS

| Chapter 1 |                                                                           | . 1 |

|-----------|---------------------------------------------------------------------------|-----|

| Introdu   | ction and Motivation                                                      | . 1 |

| Chapter 2 |                                                                           | . 8 |

| Vehicle   | e to Grid Utilizing a Backstepping Controller for Bidirectional Full-Brid | ge  |

| Converter |                                                                           | . 8 |

| 2.1 V2    | 2G system Design                                                          | . 9 |

| 2.1.1     | Five-Level ANPC Inverter                                                  | 10  |

| 2.1.2     | Bidirectional Full-Bridge Converter                                       | 11  |

| 2.1.3     | Dynamic Model of Bidirectional Full-Bridge Converter                      | 12  |

| 2.2 Ba    | ckstepping Controller                                                     | 13  |

| 2.2.1     | Control Objectives                                                        | 13  |

| 2.2.2     | Assumptions                                                               | 14  |

| 2.2.3     | Controller Design                                                         | 14  |

| 2.2.4     | Stability Analysis                                                        | 16  |

| 2.3 Sin   | mulation Results                                                          | 17  |

| 2.4 Su    | mmary                                                                     | 22  |

| Chapter 3 |                                                                           | 24  |

| Energy    | Efficient DC to AC Power Conversion                                       | 24  |

| 3.1 Sy    | stem Design                                                               | 26  |

| 3.1.1     | Bidirectional Buck Converter                                              | 27  |

| 3.1.3 H-Bridge Inverter                                                                                                                                                                          |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|                                                                                                                                                                                                  |    |

| 3.2 Control Design                                                                                                                                                                               |    |

| 3.2.1 Error System Development                                                                                                                                                                   |    |

| 3.2.2 Control Input Design                                                                                                                                                                       |    |

| 3.2.3 Stability Analysis                                                                                                                                                                         |    |

| 3.3 Simulation Results                                                                                                                                                                           |    |

| 3.3.1 Bidirectional Buck converter                                                                                                                                                               |    |

| 3.3.2 H-Bridge Inverter                                                                                                                                                                          |    |

| 3.3.3 Switching Loss                                                                                                                                                                             |    |

| 3.3.4 Harmonic Distortions                                                                                                                                                                       |    |

| 3.4 Summary                                                                                                                                                                                      |    |

| <ul><li>4.1 System Model</li><li>4.2 Control System Development</li></ul>                                                                                                                        |    |

| 5 1                                                                                                                                                                                              |    |

|                                                                                                                                                                                                  |    |

| 4.2.1 Error System Development                                                                                                                                                                   | 48 |

| <ul><li>4.2.1 Error System Development</li></ul>                                                                                                                                                 |    |

| <ul> <li>4.2.1 Error System Development</li></ul>                                                                                                                                                |    |

| <ul><li>4.2.1 Error System Development</li></ul>                                                                                                                                                 |    |

| <ul> <li>4.2.1 Error System Development</li></ul>                                                                                                                                                |    |

| <ul> <li>4.2.1 Error System Development</li> <li>4.2.2 Control Input Design</li> <li>4.2.3 Periodic Learning Design</li> <li>4.2.4 Stability Analysis</li> <li>4.3 Simulation Results</li> </ul> |    |

| <ul> <li>4.2.1 Error System Development</li></ul>                                                                                                                                                |    |

| <ul> <li>4.2.1 Error System Development</li></ul>                                                                                                                                                |    |

| <ul> <li>4.2.1 Error System Development</li></ul>                                                                                                                                                |    |

| 5.2 Control System Development                           |                      |

|----------------------------------------------------------|----------------------|

| 5.2.1 Error System Development                           |                      |

| 5.2.2 Control Design                                     | 64                   |

| 5.2.3 Stability Analysis                                 | 67                   |

| 5.2.4 Variable Gain Control                              |                      |

| 5.3 Output Current Observer                              |                      |

| 5.3.1 Stability Analysis                                 | 72                   |

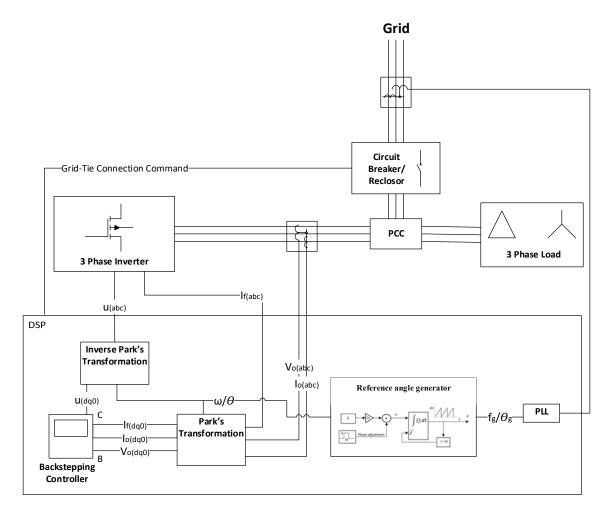

| 5.4 Transition from Standalone to Grid-Tie               |                      |

| 5.5 Simulation Result                                    |                      |

| 5.5.1 Unbalanced Load                                    |                      |

| 5.5.2 Nonlinear Load                                     |                      |

| 5.5.3 Transition from Standalone to Grid-tie             |                      |

| 5.5.4 Output Current Observer                            |                      |

| 5.6 Summary                                              |                      |

| CHAPTER 6                                                |                      |

| A Backstepping Controller Combined with Inductor Current | t and Output Current |

| Observers                                                |                      |

| 6.1 System Model                                         |                      |

| 6.2 Control System Development                           |                      |

| 6.2.1 Stability Analysis                                 |                      |

| 6.3 Simulation Result                                    |                      |

| 6.4 Summary                                              |                      |

| CHAPTER 7                                                |                      |

| Filter-Based Control of Power Electronics Interfaces     |                      |

| 7.1 System Model                                       | 100 |

|--------------------------------------------------------|-----|

| 7.2 Filter-Based Control Development                   | 101 |

| 7.2.1 Stability Analysis                               |     |

| 7.3 Experimental Results                               | 105 |

| 7.3.1 Buck Converter                                   |     |

| 7.3.2 H-Bridge-Inverter                                |     |

| 7.4 Summary                                            | 111 |

| CHAPTER 8                                              |     |

| Filter-Based Controller with Unknown System Parameters |     |

| 8.1 System Model                                       | 114 |

| 8.2 Filter-Based Control for Unknown System Parameters | 115 |

| 8.2.1 Stability Analysis                               |     |

| 8.3 Experimental Results                               | 121 |

| 8.4 Summary                                            | 125 |

| CHAPTER 9                                              | 126 |

| Filter-Based Controller with Parameters Discrepancy    | 126 |

| 9.1 System Model                                       | 127 |

| 9.2 Filter-Based Control Development                   | 128 |

| 9.2.1 Stability Analysis                               |     |

| 9.3 Experimental Results                               |     |

| 9.4 Summary                                            |     |

| CHAPTER 10                                             |     |

| Conclusion and Future Works                                     | 143 |

|-----------------------------------------------------------------|-----|

| 10.1 Conclusion                                                 | 143 |

| 10.1.1 Backstepping Controller                                  | 143 |

| 10.1.2 Filter-Based Controller                                  | 144 |

| 10.2 Future Work                                                | 145 |

| 10.2.1 Grid-Tie Mode                                            | 145 |

| 10.2.2 Hierarchical Cooperative Control Scheme and Optimization | 145 |

| References                                                      | 147 |

| Appendix A                                                      | 160 |

| Curriculum Vitae                                                | 162 |

# LIST OF TABLES

| TABLE 2.1 V2G System Parameters                                            |                  |

|----------------------------------------------------------------------------|------------------|

| TABLE 3.1 BIDIRECTIONAL BUCK CONVERTER SIMULATION PARAMETERS.              |                  |

| TABLE 3.2 H-BRIDGE INVERTER SIMULATION PARAMETERS                          | 40               |

| TABLE 3.3 SWITCHING POWER LOSS COMPARISON.                                 | 43               |

| TABLE 3.4 HARMONIC DISTORTIONS COMPARISON                                  | 43               |

| TABLE 4.1 SYSTEM PARAMETERS FOR H-BRIDGE INVERTER AND LEARNING BACKSTEPPIN | NG CONTROLLER.54 |

| TABLE 5.1 SYSTEM PARAMETERS FOR 3-PHASE INVERTER                           | 76               |

| TABLE 5.2 HARMONIC DISTORTIONS                                             | 79               |

| TABLE 6.1 SYSTEM PARAMETERS                                                | 94               |

| TABLE 7.1 BUCK CONVERTER SYSTEM PARAMETERS                                 |                  |

| TABLE 7.2 SYSTEM PARAMETERS                                                | 109              |

| TABLE 8.1 SYSTEM PARAMETERS                                                |                  |

| TABLE 8.2 PERFORMANCE COMPARISON                                           |                  |

| TABLE 9.1 SYSTEM PARAMETERS                                                |                  |

# LIST OF FIGURES

| FIG. 1.1 BUCK-TYPE CONVERTER.                                                                    | 2     |

|--------------------------------------------------------------------------------------------------|-------|

| FIG. 1.2 GENERAL STRUCTURE FOR DG                                                                | 2     |

| FIG. 2.1 SYSTEM BLOCK DIAGRAM FOR GENERATING 240 [Vrms] SPLIT-PHASE AC VOLTAGE FROM 240          | V DC  |

| INPUT                                                                                            | 9     |

| FIG. 2.2 TWO PARALLEL FIVE-LEVEL SIMPLIFIED ANPC WITH 180° PHASE DIFFERENCE                      | 10    |

| FIG. 2.3 BIDIRECTIONAL FULL-BRIDGE CONVERTER.                                                    | 12    |

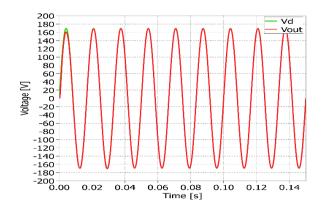

| FIG. 2.4 OUTPUT VOLTAGE, $Vout(t)$ , and the desired voltage, $Vd(t)$ , of Bidirectional Full-BF | RIDGE |

| Converter                                                                                        | 19    |

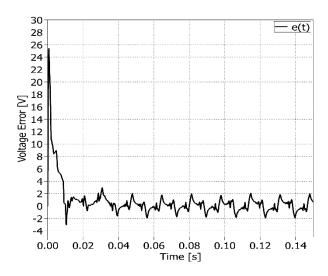

| FIG. 2.5 VOLTAGE TRACKING ERROR, $e(t)$ of Bidirectional Full-Bridge Converter                   | 19    |

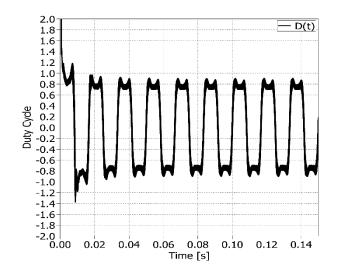

| FIG. 2.6 CONTROL DUTY CYCLE, $D(t)$ , OF BI-DIRECTIONAL FULL-BRIDGE CONVERTER.                   | 20    |

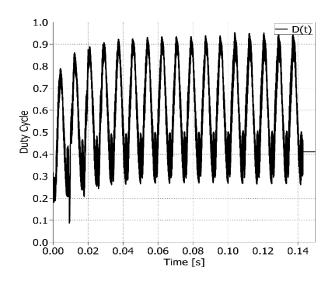

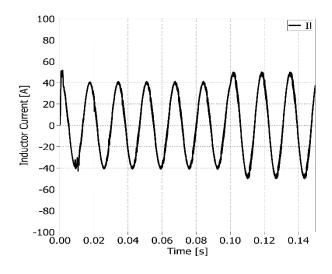

| FIG. 2.7 BIDIRECTIONAL FULL-BRIDGE CONVERTER INDUCTOR CURRENT.                                   | 20    |

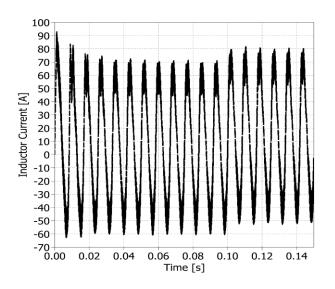

| FIG. 2.8 BIDIRECTIONAL FULL-BRIDGE CONVERTER ESTIMATED DISTURBANCE.                              | 21    |

| FIG. 2.9 ANPC INVERTER LINE TO NEUTRAL OUTPUT VOLTAEGE.                                          | 21    |

| FIG. 2.10 ANPC INVERTER LINE TO LINE OUTPUT VOLTAEGE                                             | 22    |

| FIG. 2.11 OUTPUT VOLTAGE NORMALIZED HARMONICS WITH RESPECT TO FUNDAMENTAL.                       | 22    |

| FIG. 3.1 SYSTEM BLOCK DIAGRAM FOR GENERATING 120 [Vrms] AC VOLTAGE FROM 240V DC INPUT            | 26    |

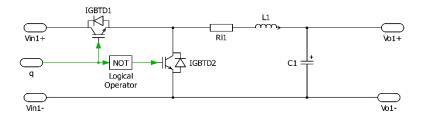

| FIG 3.2 BIDIRECTIONAL BUCK CONVERTER.                                                            | 27    |

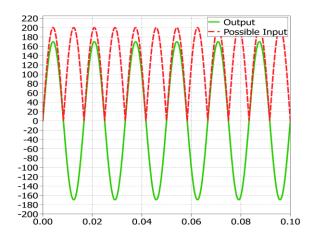

| FIG. 3.3 POSSIBLE INVERTER INPUT AND OUTPUT SIGNALS.                                             | 30    |

| FIG. 3.4 TRAJECTORY SIGNAL AND ABSOLUTE VALUE OF OUTPUT AC SIGNAL.                               | 31    |

| FIG. 3.5 H-BRIDGE INVERTER.                                                                      | 31    |

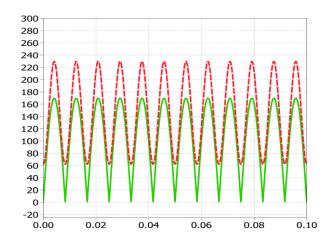

| FIG. 3. 6 CONVERTER OUTPUT VOLTAGE AND THE DESIRED VOLTAGE.                                      | 38    |

| FIG. 3.7 CONVERTER VOLTAGE TRACKING ERROR.                                                       | 38    |

| FIG. 3.8 CONVERTER CONTROL DUTY CYCLE.                                                           | 39    |

| FIG. 3.9 CONVERTER INDUCTOR CURRENT                                                                       |

|-----------------------------------------------------------------------------------------------------------|

| FIG. 3.10 INVERTER OUTPUT VOLTAGE AND THE DESIRED VOLTAGE                                                 |

| FIG. 3.11 INVERTER VOLTAGE TRACKING ERROR                                                                 |

| FIG. 3.12 INVERTER CONTROL DUTY CYCLE                                                                     |

| FIG. 3.13 INVERTER INDUCTOR CURRENT                                                                       |

| FIG. 5.1 H-BRIDGE INVERTER WITH OUTPUT LC FILTER AND LOAD                                                 |

| FIG. 4.2 INVERTER DESIRED VOLTAGE, OUTPUT VOLTAGE AND OUTPUT CURRENT                                      |

| FIG. 4. 3 CONTROLLER TRACKING ERRORS                                                                      |

| FIG. 4. 4 INVERTER CONTROL DUTY CYCLE                                                                     |

| FIG. 4. 5 ACTUAL AND DESIRED CURRENT OF THE INDUCTOR                                                      |

| FIG. 4. 6 ESTIMATION OF SYSTEM DISTURBANCES                                                               |

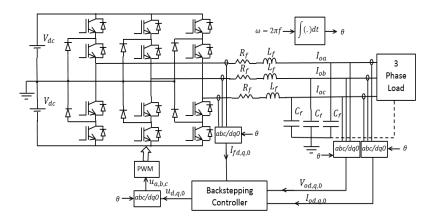

| FIG. 5. 1 3L3L FOUR-WIRE DIODE CLAMPED INVERTER WITH OUTPUT <i>LC</i> FILTER                              |

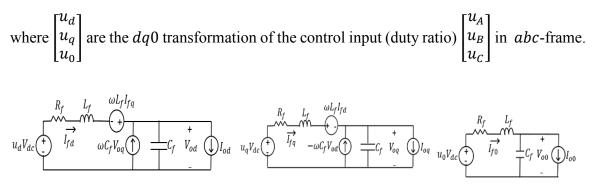

| FIG. 5.2 EQUIVALENT <i>DQ0</i> CIRCUITS OF THE 3L3L DIODE CLAMPED INVERTER WITH OUTPUT <i>LC</i> FILTER60 |

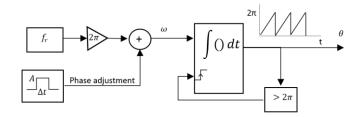

| FIG. 5.3 REFERENCE ANGLE GENERATOR                                                                        |

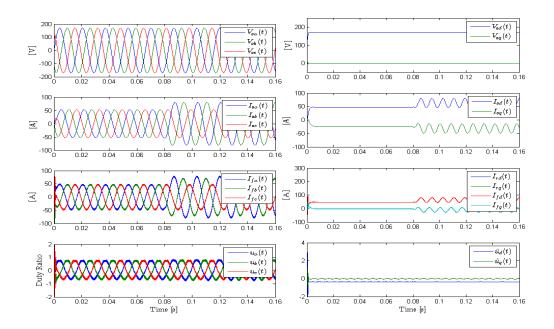

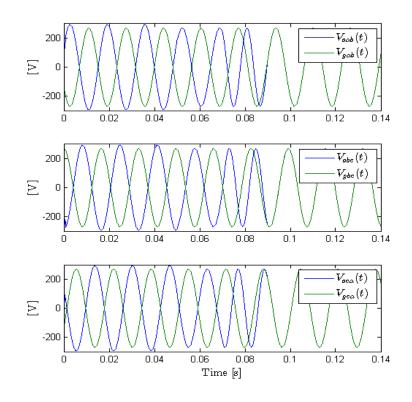

| FIG. 5.5 INVERTER PERFORMANCE UNDER BALANCED/UNBALANCED LOAD                                              |

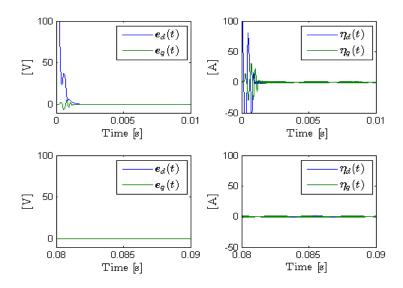

| FIG. 5.6 TRACKING ERROR UNDER BALANCED/UNBALANCED LOAD                                                    |

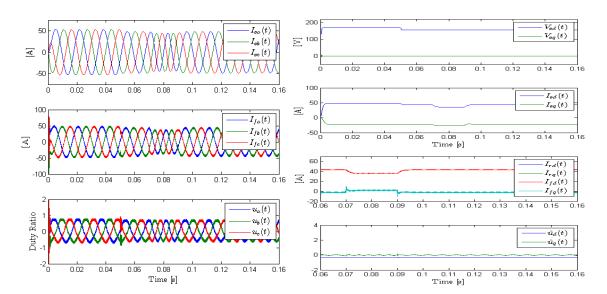

| FIG. 5.7 INVERTER PERFORMANCE UNDER NONLINEAR LOAD                                                        |

| FIG. 5.8 TRACKING ERROR UNDER NONLINEAR LOAD                                                              |

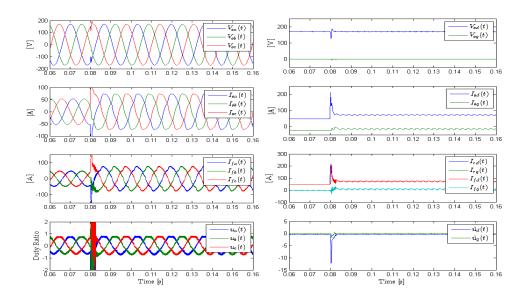

| FIG. 5.9 LINE-TO-LINE VOLTAGE OF INVERTER AND GRID IN TRANSITION FROM STANDALONE TO GRID-TIE. 81          |

| FIG. 5.10 INVERTER PERFORMANCE IN TRANSITION FROM STANDALONE TO GRID-TIE                                  |

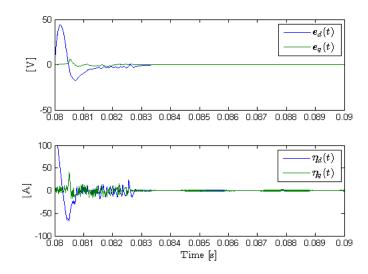

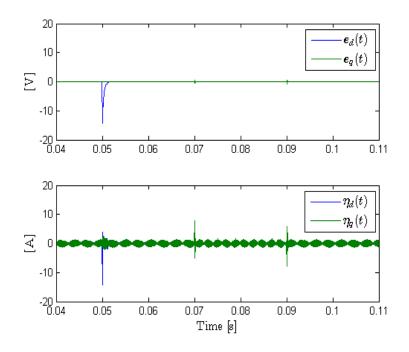

| FIG. 5.11 TRACKING ERROR IN TRANSITION FROM STANDALONE TO GRID-TIE                                        |

| FIG. 5.12 INVERTER PERFORMANCE WITH LOAD-CURRENT OBSERVER UNDER BALANCED/UNBALANCED LOAD.                 |

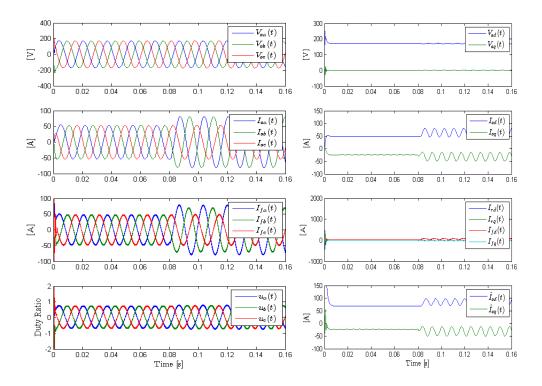

|                                                                                                           |

| FIG. 5.13 TRACKING ERROR WITH LOAD-CURRENT OBSERVER UNDER BALANCED/UNBALANCED LOAD84                      |

| FIG. 5.14 INVERTER PERFORMANCE WITH LOAD-CURRENT OBSERVER UNDER NONLINEAR LOAD                            |

| FIG. 5.15 TRACKING ERROR WITH LOAD-CURRENT OBSERVER UNDER NONLINEAR LOAD                                  |

| FIG. 6.1 H-BRIDGE INVERTER WITH OUTPUT <i>LC</i> FILTER                                                   |

| FIG. 6.2 TRANSIENT AND STEADY-STATE RESULTS UNDER LINEAR LOAD, LOAD1                                      |

| FIG. 6.3 TRANSIENT AND STEADY-STATE ERRORS UNDER UNDER LINEAR LOAD, LOAD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 95                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| FIG. 6.4 TRANSIENT AND STEADY-STATE RESULTS UNDER NONLINEAR LOAD, LOAD2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 96                                                                              |

| FIG. 6.5 TRANSIENT AND STEADY-STATE ERRORS UNDER NONLINEAR LOAD, LOAD2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 96                                                                              |

| FIG. 6.6 TRANSIENT RESULTS IN RESPONSE TO NO LOAD TO NOMINAL RESITIVE LOAD STEP CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 97                                                                              |

| FIG. 6.7 TRANSIENT ERRORS IN RESPONSE TO NO LOAD TO NOMINAL RESISTIVE LOAD STEP CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 97                                                                              |

| FIG. 7.1 BUCK-TYPE CONVERTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 101                                                                             |

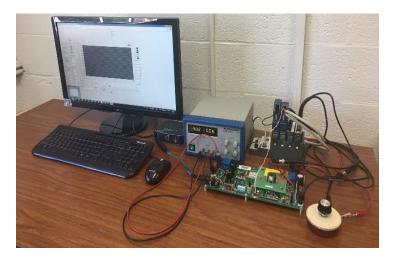

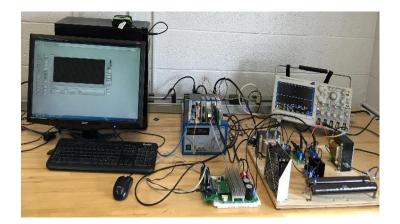

| FIG. 7.2 EXPERIMENTAL SETUP OF THE BUCK CONVERTER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 105                                                                             |

| FIG. 7.3 OUTPUT VOLTAGE, $Vo(t)$ , and the desired voltage, $Vd(t)$ , of the buck converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 106                                                                             |

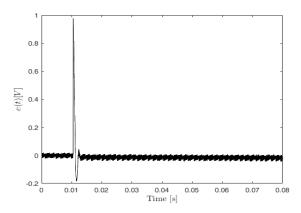

| FIG. 7.4 VOLTAGE TRACKING ERROR, $e(t)$ OF THE BUCK CONVERTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107                                                                             |

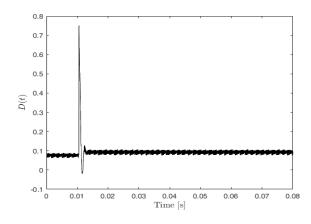

| FIG. 7.5 The duty ratio control signal, $D(t)$ of the buck converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 107                                                                             |

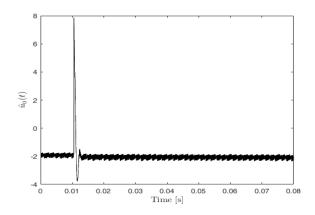

| FIG. 7.6 The estimated system disturbance, $u0(t)$ of the buck converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107                                                                             |

| FIG. 7.7 EXPERIMENTAL SETUP OF THE H-BRIDGE INVERTER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 108                                                                             |

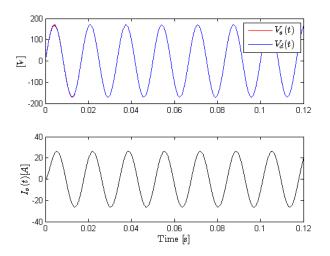

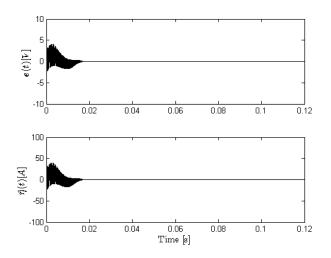

| FIG. 7.7 STEADY-STATE RESULTS UNDER <i>RL</i> LOAD FOR THE H-BRIDGE INVERTER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 109                                                                             |

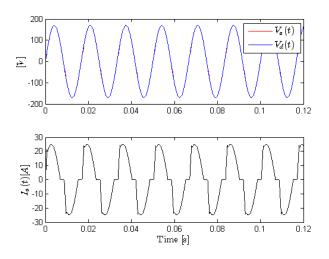

| FIG. 7.7 STEADY-STATE RESULTS UNDER HIGHLY DISTORTING NONLINEAR LOAD FOR THE H-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BRIDGE                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                 |

| INVERTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 110                                                                             |

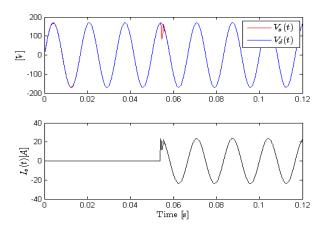

| INVERTER<br>Fig. 7.7 Transient results in response to -50% step change in amplitude of the reference vo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OLTAGE                                                                          |

| Fig. 7.7 Transient results in response to $-50\%$ step change in amplitude of the reference vo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DLTAGE<br>111                                                                   |

| FIG. 7.7 TRANSIENT RESULTS IN RESPONSE TO -50% STEP CHANGE IN AMPLITUDE OF THE REFERENCE VOUNDER RESISTIVE LOAD FOR THE H-BRIDGE ONVERTER.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DLTAGE<br>111<br>114                                                            |

| <ul> <li>FIG. 7.7 TRANSIENT RESULTS IN RESPONSE TO -50% STEP CHANGE IN AMPLITUDE OF THE REFERENCE VOUNDER RESISTIVE LOAD FOR THE H-BRIDGE ONVERTER.</li> <li>FIG8.1 H-BRIDGE INVERTER WITH OUTPUT LC FILTER.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DLTAGE<br>111<br>114                                                            |

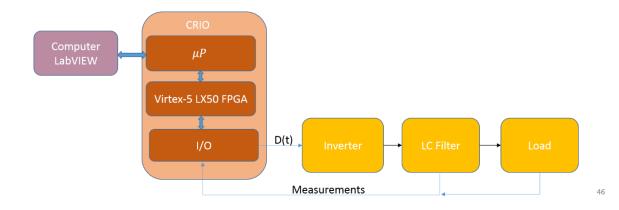

| <ul> <li>FIG. 7.7 TRANSIENT RESULTS IN RESPONSE TO -50% STEP CHANGE IN AMPLITUDE OF THE REFERENCE VOUNDER RESISTIVE LOAD FOR THE H-BRIDGE ONVERTER.</li> <li>FIG8.1 H-BRIDGE INVERTER WITH OUTPUT <i>LC</i> FILTER.</li> <li>FIG. 8.2 EXPERIMENTAL SETUP BLOCK DIAGRAM.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          | DLTAGE<br>111<br>114<br>121<br>123                                              |

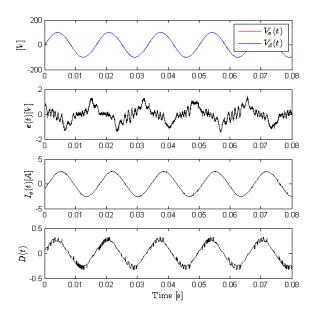

| <ul> <li>FIG. 7.7 TRANSIENT RESULTS IN RESPONSE TO -50% STEP CHANGE IN AMPLITUDE OF THE REFERENCE VOUNDER RESISTIVE LOAD FOR THE H-BRIDGE ONVERTER.</li> <li>FIG8.1 H-BRIDGE INVERTER WITH OUTPUT <i>LC</i> FILTER.</li> <li>FIG. 8.2 EXPERIMENTAL SETUP BLOCK DIAGRAM.</li> <li>FIG. 8.3 STEADY-STATE RESULTS UNDER RL LOAD.</li> </ul>                                                                                                                                                                                                                                                                                                                                    | DLTAGE<br>111<br>114<br>121<br>123<br>124                                       |

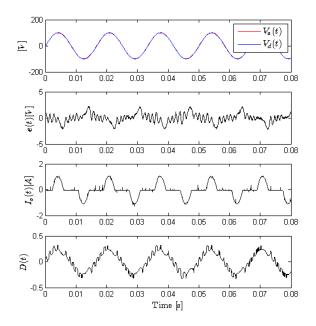

| <ul> <li>Fig. 7.7 Transient results in response to -50% step change in amplitude of the reference volunder resistive load for the H-bridge onverter.</li> <li>Fig8.1 H-Bridge inverter with output <i>LC</i> filter.</li> <li>Fig. 8.2 Experimental setup block diagram.</li> <li>Fig. 8.3 Steady-state results under RL load.</li> <li>Fig. 8.4 Steady-state results under highly distorting nonlinear load.</li> </ul>                                                                                                                                                                                                                                                    | DLTAGE<br>111<br>114<br>121<br>123<br>124<br>DLTAGE                             |

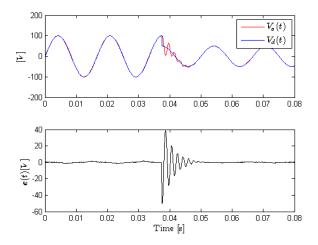

| <ul> <li>Fig. 7.7 Transient results in response to -50% step change in amplitude of the reference volunder resistive load for the H-bridge onverter.</li> <li>Fig8.1 H-Bridge inverter with output <i>LC</i> filter.</li> <li>Fig. 8.2 Experimental setup block diagram.</li> <li>Fig. 8.3 Steady-state results under RL load.</li> <li>Fig. 8.4 Steady-state results under highly distorting nonlinear load.</li> <li>Fig. 8.5 Transient results in response to -50% step change in amplitute of the reference volume.</li> </ul>                                                                                                                                          | DLTAGE<br>111<br>121<br>123<br>124<br>DLTAGE<br>125                             |

| <ul> <li>FIG. 7.7 TRANSIENT RESULTS IN RESPONSE TO -50% STEP CHANGE IN AMPLITUDE OF THE REFERENCE VOUNDER RESISTIVE LOAD FOR THE H-BRIDGE ONVERTER.</li> <li>FIG8.1 H-BRIDGE INVERTER WITH OUTPUT <i>LC</i> FILTER.</li> <li>FIG. 8.2 EXPERIMENTAL SETUP BLOCK DIAGRAM.</li> <li>FIG. 8.3 STEADY-STATE RESULTS UNDER RL LOAD.</li> <li>FIG. 8.4 STEADY-STATE RESULTS UNDER HIGHLY DISTORTING NONLINEAR LOAD.</li> <li>FIG. 8.5 TRANSIENT RESULTS IN RESPONSE TO -50% STEP CHANGE IN AMPLITUTE OF THE REFERENCE VOUNDER RESISTIVE LOAD.</li> </ul>                                                                                                                           | DLTAGE<br>111<br>114<br>121<br>123<br>124<br>DLTAGE<br>125<br>128               |

| <ul> <li>FIG. 7.7 TRANSIENT RESULTS IN RESPONSE TO -50% STEP CHANGE IN AMPLITUDE OF THE REFERENCE VOUNDER RESISTIVE LOAD FOR THE H-BRIDGE ONVERTER.</li> <li>FIG8.1 H-BRIDGE INVERTER WITH OUTPUT <i>LC</i> FILTER.</li> <li>FIG. 8.2 EXPERIMENTAL SETUP BLOCK DIAGRAM.</li> <li>FIG. 8.3 STEADY-STATE RESULTS UNDER RL LOAD.</li> <li>FIG. 8.4 STEADY-STATE RESULTS UNDER HIGHLY DISTORTING NONLINEAR LOAD.</li> <li>FIG. 8.5 TRANSIENT RESULTS IN RESPONSE TO -50% STEP CHANGE IN AMPLITUTE OF THE REFERENCE VOUNDER RESISTIVE LOAD.</li> <li>FIG. 9.1 H-BRIDGE INVERTER WITH OUTPUT LC FILTER.</li> </ul>                                                                | DLTAGE<br>111<br>121<br>123<br>123<br>DLTAGE<br>125<br>128<br>135               |

| <ul> <li>FIG. 7.7 TRANSIENT RESULTS IN RESPONSE TO -50% STEP CHANGE IN AMPLITUDE OF THE REFERENCE VOUNDER RESISTIVE LOAD FOR THE H-BRIDGE ONVERTER.</li> <li>FIG8.1 H-BRIDGE INVERTER WITH OUTPUT <i>LC</i> FILTER.</li> <li>FIG. 8.2 EXPERIMENTAL SETUP BLOCK DIAGRAM.</li> <li>FIG. 8.3 STEADY-STATE RESULTS UNDER RL LOAD.</li> <li>FIG. 8.4 STEADY-STATE RESULTS UNDER HIGHLY DISTORTING NONLINEAR LOAD.</li> <li>FIG. 8.5 TRANSIENT RESULTS IN RESPONSE TO -50% STEP CHANGE IN AMPLITUTE OF THE REFERENCE VOUNDER RESISTIVE LOAD.</li> <li>FIG. 9.1 H-BRIDGE INVERTER WITH OUTPUT LC FILTER.</li> <li>FIG. 9.2 EXPERIMENTAL SETUP OF THE H-BRIDGE INVERTER.</li> </ul> | DLTAGE<br>111<br>121<br>123<br>123<br>124<br>DLTAGE<br>125<br>128<br>135<br>136 |

| FIG. 9.6 TRANSIENT RESPONSE OF THE FILTER-BASED CONTROLLER UNDER RESISTIVE LOAD            |

|--------------------------------------------------------------------------------------------|

| FIG. 9.7 TRANSIENT RESPONSE OF THE OUTPUT FEED-FORWARD CONTROLLER UNDER RESISTIVE LOAD 139 |

| FIG. 9.8 STEADY-STATE RESPONSE OF THE FILTER-BASED CONTROLLER UNDER A HIGHLY DISTORTING    |

| RECTIFIER LOAD                                                                             |

| FIG. 9.9 STEADY-STATE RESPONSE OF THE OUTPUT FEED-FORWARD CONTROLLER UNDER A HIGHLY        |

| DISTORTING RECTIFIER LOAD140                                                               |

| FIG.9.10 STEADY-STATE RESPONSE OF THE FILTER-BASED CONTROLLER WITH +50% INDUCTANCE         |

| DISCREPANCY UNDER RL LOAD141                                                               |

| FIG. 9.11 STEADY-STATE RESPONSE OF THE FILTER-BASED CONTROLLER WITH +50% CAPACITANCE       |

| DISCREPANCY UNDER RL LOAD141                                                               |

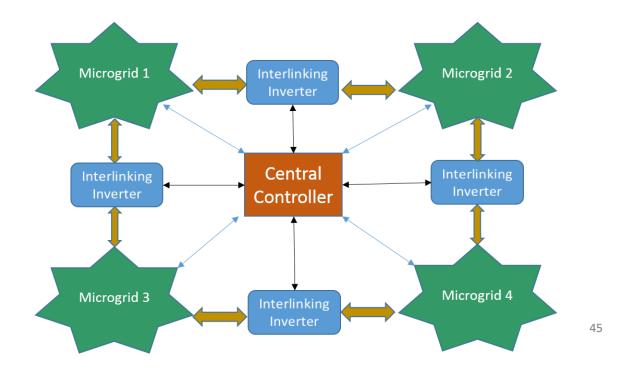

| Fig. 10.1 Multi microgrid system146                                                        |

# CHAPTER 1

#### INTRODUCTION AND MOTIVATION

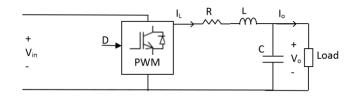

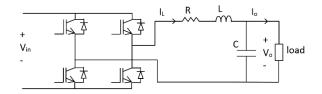

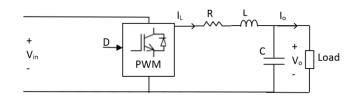

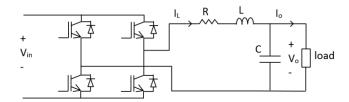

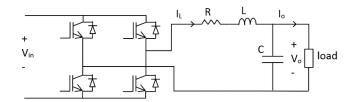

As Distributed Generation (DG) systems [1]-[2][3] [4], Vehicle to Grid (V2G) [5], Battery Energy Storage System (BESS) [6] and Uninterruptable Power Supplies (UPS) [7]-[8][9][10] are more widely adopted, pulse width modulated (PWM) power converters have become more broadly utilized for voltage conversion. Among a wide variety of structures proposed for the PWM power converters, those composed of a switching circuit followed by an output *LC* filter have gain more popularity for the DC:DC power converters and DC:AC standalone voltage source inverters (VSI) [1]- [10]. Fig. 1.1 demonstrate a general class of PWM converters consisting of a PWM switching circuit followed by an output *LC* filter. This class of PWM covertures includes a wide variety of both dc-dc and dc-ac converters such as buck, synchronous buck, forward, push-pull, full and half-bridge converters and inverters with output *LC* filter. All the converters/ inverters in this class can be considered as derivatives of the basic buck converter. Because of the same dynamic model for all the converter/inverter in this class, any controller developed for each is applicable for others as well.

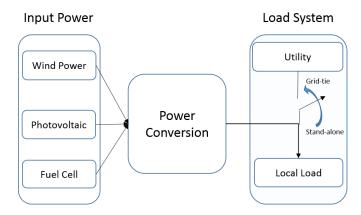

As shown in Fig 1.2, a power inverters have two operation modes: stand-alone and grid-tie. In stand-alone mode, the local load is supplied by the inverter. Therefore, generation of a high-quality output voltage with low distortion and excellent voltage

1

Fig. 1.1 Buck-type converter.

regulation as well as disturbance rejection are the essential requirements of the associated control system. Good transient response and insensitivity to the load and system parameter variations are other metrics in the performance evaluation of inverters, which also necessitates the use of high performance controllers. In grid-tie mode, the inverter is controlled as a current source. The grid-tie inverters, known as grid-feeding power converters, can participate in the control of the grid voltage amplitude and frequency by adjusting, in a higher level control layer, the references of their active and reactive power. In a lower level control layer, the local controller is responsible to keep the active and reactive power generated by the inverter as close as possible to their reference values.

Fig. 1.2 General structure for DG

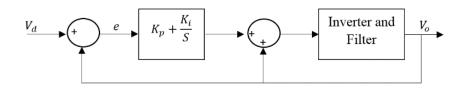

Many control techniques such as proportional-resonant (PR) [11], [12], multiloop feedback control [13]-[14] [15] dead-beat control [16] and repetitive control [17]-

[18][19][20][21][22][23][24] have been proposed to control a single phase VSI in standalone mode. Although a single output voltage measurement is sufficient for the control of the inverter, to the best knowledge of the authors, the majority of the existing control approaches require an inductor current measurement. Using two measurements gives these controllers improved system stability and dynamic performance through both output voltage and inductor current regulation. For example, a simple multiloop control technique utilizes two traditional Proportional, Integral, and Derivative (PID) controllers to regulate both output voltage and inductor current in the voltage and current control loops, respectively. Finite loop gain of the PID controller at the fundamental frequency and its sensitivity to the load variations have motivated combining other techniques such as frame transformation [25]-[26][27] and Load Current Feedback (LCF) [14], [28], [29] to the multiloop control scheme. These combinations alleviate shortfalls of the multiloop control scheme at the cost of more computational complexity resulting from signal transformations between frames and an extra current sensor for an output current measurement.

Repetitive control is known for its capability to overcome periodic disturbances, whose frequencies are less than half of the sampling frequency [17]- [24]. However, slow dynamics and poor tracking performance especially to nonperiodic disturbances are the main practical limitations of this technique. A multi-resonant harmonic compensator which eliminates low-order load current harmonics and periodic disturbances with specific frequencies has been applied to inverter control as shown in [30]-[31][32][33] [34]. Lack of a systematic method of stabilization is a general problem for both repetitive and resonant regulator control schemes [35]. In [36] a Fuzzy control strategy was used to control the inverter system, with a genetic algorithm used in conjunction to optimize the fuzzy

controller. The scheme presented in [36] has an acceptable dynamic response and output voltage waveform at the cost of a complex algorithm.

Nonlinear control techniques such as backstepping controller and sliding mode control have been shown to demonstrate good tracking performance. Discrete-time sliding mode control technique has been used in multi-loop feedback systems due to its overshoot-free tracking capability [37]. However, the dependency of these controllers to the knowledge of the system parameters limits their practical application. In [38] the performance of two nonlinear controllers, namely backstepping and sliding mode controllers, are compared with a conventional PID controller. The results show the backstepping controller outperforming the other two controllers. The sliding mode controller always generates a very harsh command compared to backstepping [38]. The control laws of the proposed backstepping and sliding mode controllers in [38] depend on the numerical derivative of the output current which increase the level of the noise in the system.

In the majority of the control schemes presented for the control of power converters with output *LC* filter, at least two sensors are used to measure the output voltage and the inductor current. In practice this inductor current measurement has a significant amount of ripple and measurement noise resulting from the switching scheme. This noise and ripple are then propagated into the control algorithm adding noise and disturbance to the system. Some control schemes use capacitor current measurement instead of the inductor current measurement [8], [14], [39]- [40] [41] where the same problem remains. Also some works use an output current sensor in addition to the other two sensors [14], [26], [39] to reduce the effect of the high frequency noise and ripple resulting from switching, utilization of a low-pass filter (LPF) is suggested. Addition of LPF introduces phase delays, which can

have an adverse effect on the control schemes, which can limit any performance improvement.

In this dissertation, nonlinear control techniques such as backstepping controller and filter-based controller are utilized for the control of power converters in different applications of DG systems. To overcome the shortfalls of the backstepping controller such as dependency of the control law to the inductor current measurement and numerical derivative of the noisy current measurement, as seen in [38], a combination of the backstepping controller with other control techniques such as inductor current observer, output current observer, nonlinear sliding technique and periodic learning is proposed. Also, filter-based control techniques are developed as effective control schemes which require only single output voltage measurement in their control law. The proposed filterbased control schemes not only eliminate the need for costly current sensors to measure the inductor and/or output currents, but also they are robust against system parameter discrepancy and system disturbances. For each developed control scheme, a Lyapunov stability analysis is presented which proves that the voltage tracking objective is achieved by the controller with all signals remaining bounded. Simulation and/or experimental results further validate the proposed approaches.

The rest of the dissertation is organized as follows. In Chapter 2, a backstepping controller is utilized to control a two-stage PEI in the V2G application. The proposed controller in this chapter is combined with sliding technique to compensate for the uncertainty presented by the derivative of the output current presence in the model. An energy efficient two-stage DC to AC PEI is presented in Chapter 3. A typical DC:AC conversion system consists of two stages, a DC:DC converter to generate the necessary bus

voltage followed by an inverter which generates the desired AC output. A modification of this system is proposed for the purpose of reducing switching losses. The proposed twostage system consists of a buck converter which produces a mixed (DC+AC) signal which is fed to an H-Bridge inverter. This mixed signal is designed such that it reduces the switching loss across the inverter switches while still providing the necessary voltage for the inverter input. Backstepping controllers are designed to achieve output voltage tracking objectives for both stages. In Chapter 4, a nonlinear backstepping controller combined with a periodic disturbance learning observer is proposed for the control of a single-phase H-Bridge inverter under both linear and nonlinear loads. The proposed learning scheme takes into account the periodic nature of the system and observes the periodic disturbance and unmeasurable uncertainties of the system. Chapter 5 details an extension of the proposed control techniques for the control of a 3-phase 4-wire diode clamped inverter with an output LC filter under different loads including balanced, unbalanced, linear and nonlinear loads. Also, the seamless transition of inverter from standalone to grid-tie is investigated while the inverter is under the control of the proposed controller. Furthermore, a load-current observer is combined with the proposed backstepping controller to enhance the behavior of the controller.

As an effort to remove the inductor current measurement from the control law, an inductor current observer is developed and combined with a backstepping controller in Chapter 6. The elimination of the sensor along with the removal of current ripple and noise from the control algorithm provides an advantage over existing arts in this area. To further improve the performance of the control law and make it robust against system parameters discrepancies and compensate for system disturbances, in Chapter 7, 8 and 9 filter-based

control approach is investigated. This control technique inherently benefits from an internal observer so that its control law is only relying on the system output and it doesn't need extra measurement for the other system states. The basic form of the proposed filter-based controller is presented in Chapter 7. The control law of the proposed filter-based controller relies only on the output voltage measurement which eliminate the need for costly current sensors to measure the inductor and/or output currents. Also, a disturbance observer is combined to the developed control scheme which makes it more suitable for practical purposes and compensates for an unknown disturbance in the model. Various system uncertainty including dead-time in modulation scheme, voltage drop across switching devices and input voltage deviations are compensated with this unknown disturbance observer. To reduce the control sensitivity to the system parameters and compensate for parameter variation, two extension of the filter-based control scheme are presented in Chapter 8 and 9. In the earlier scheme, presented in Chapter 8, the control law is developed for unknown system parameters whereas in the later scheme, presented in Chapter 9, the nominal values of the system parameters are utilized and the control scheme compensates for parameter discrepancies. Finally, conclusions and suggested future work are given in Chapter 10.

# **CHAPTER 2**

# VEHICLE TO GRID UTILIZING A BACKSTEPPING CONTROLLER FOR BIDIRECTIONAL FULL-BRIDGE CONVERTER

With environmental and climate change issues, increasing oil prices, concerns about energy security, decreasing fossil energy reserves, and environmental related legislation, plug-in electric and hybrid vehicles (PEVs) sales are increasing. Meanwhile with "vehicle to grid" (V2G) technology, electric vehicles can work as distributed resources and power can be sent back to the utility. This fact places V2G as an emerging technology with the potential to revolutionize the electric power industry [42]. V2G technology utilizes the energy stored in a battery electric vehicle (BEV) or plug-in hybrid electric vehicle (PHEV) for connection to the grid. This technology can be used in conjunction with a Smart Grid or as a supplemental/backup power source for a household [5]. One such application is the use of a V2G interface to power a household entirely from the vehicle's battery. This system would replace the need for a large backup generator and add the convenience of a more portable system located in the user's vehicle. The main objective of this system is to produce a sufficient, sustained power source.

A V2G system typically consists of a two-stage power electronic interface (PEI). The first PEI stage is a DC:DC converter which steps up/down the voltage of the EV's battery

pack to the bus voltage necessary for the second PEI stage, the inverter. The inverter converts this DC bus voltage to an AC voltage compatible with that of the grid. This work focuses on the design and control scheme of the DC:DC converter stage of the V2G system [43]. A robust design for this PEI necessitates the ability to adapt to a varying input voltage and an unknown load while still maintaining the desired output voltage. As such, a backstepping controller is ideal because of its adaptive nature. Development of such a controller is presented herein as designed for a full-bridge DC:DC converter. The second PEI stage of the design is implemented via two parallel ANPC inverters with 180° phase difference providing a fixed magnitude, fixed frequency split-phase AC voltage.

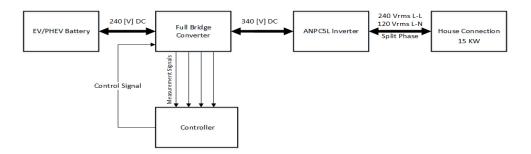

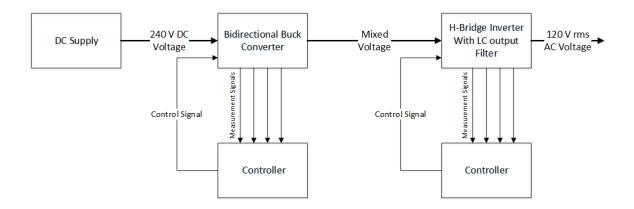

## 2.1 V2G system Design

The proposed two-stage V2G system is shown in Fig. 2.1. As shown the first PEI stage is designed to convert the 240 [V] DC voltage of the battery pack to the 340 [V] DC bus voltage necessary for inversion. The second PEI stage consists of two five-level ANPC inverters which convert the 340 [V] bus voltage to a 240 [ $V_{rms}$ ], 60 [Hz] split-phase AC voltage. In the subsequent section, the bidirectional full-bridge converter and the related controller are designed to meet the requirements set by the second stage inverters.

Fig. 2.1 System Block Diagram for Generating 240 [*V<sub>rms</sub>*] Split-Phase AC Voltage from 240V DC Input.

#### 2.1.1 Five-Level ANPC Inverter

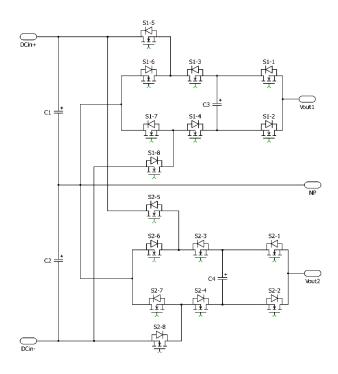

Two parallel five-level ANPC (ANPC5L) converters with 180° phase difference, shown in Fig. 2.2, are capable of generating a five-level 120  $[V_{rms}]$  line-to-neutral output voltage and nine level 240 $[V_{rms}]$  line-to-line split-phase AC voltage which fulfills the harmonic limits of the IEEE519 standard when a simple LC filter is applied.

Fig. 2.2 Two parallel five-level simplified ANPC with 180° phase difference.

In order to reduce the cost and size of the inverter, a simplified ANPC5L topology was chosen which requires only one floating capacitor. The voltage of this floating capacitor is controlled based on redundant switching states [44]. The modified switching scheme proposed in [45] is used to prevent unwanted high frequency switching which causes high switching loss and failure to the circuit. In the reverse path when the battery is charged by utility power, all the inverter switches are off. In this case the body diodes of the switches make two parallel full-bridge rectifiers.

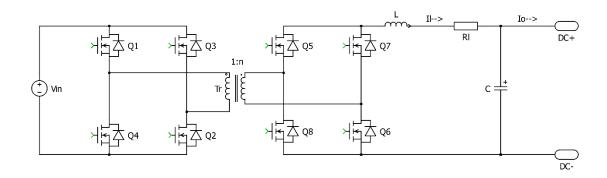

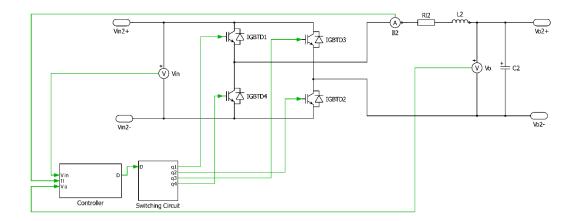

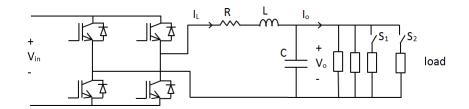

#### 2.1.2 Bidirectional Full-Bridge Converter

The proposed inverter design requires a larger DC voltage than what the vehicle's battery can provide. As such, an interface is needed to increase the voltage level from the supply allowing 9 [kW] power output at the 120 [V<sub>rms</sub>] and 6 [kW] power output at the 240  $[V_{rms}]$  to be maintained. This stage needs to provide the 340 [V] required by the inverter stage, referred to as the DC Link bus, using the 240 [V] input from the EV/PHEV's battery with a minimal amount of variance to prevent generation of additional harmonics in the inverter output. An output voltage ripple maximum of 1% was selected for the design. To have ground isolation and voltage boosting a bidirectional full-bridge converter topology, shown in Fig. 2.3, was selected for this design. Proper switching of this bidirectional converter ensures that the converter always operates in continuous conduction mode even when the inductor current is negative. This bidirectional power flow is necessary to allow for the proper exchange of reactive power between the complex load of the inverter and the DC link. Since the converter feeds the inverter stage with complex load whose voltage and current are not necessary in phase, therefore for keeping the dc-link voltage at the desired value we need to provide the discharge path for the dc-link capacitors to compensate the effect of negative reactance power on the dc-link capacitors. This path can be provided with the proper switching of the converter switches. Logical functions given in (2.1) show the gate signal generation for the converter switches. This switching scheme keeps the converter in the continuous conduction mode even when the inductor current is negative.

Fig. 2.3 Bidirectional Full-Bridge Converter.

$$Q1 = (D > Tri1)$$

$$Q4 = \sim Q1$$

$$Q3 = (D > Tri2)$$

$$Q2 = \sim Q3$$

$$Q5 = Q6 = HC1$$

$$Q7 = Q8 = \sim HC1$$

(2.1)

Where Tri1 and Tri2 are the two triangular waveforms which act as carrier references for PWM modulation. *HC*1 is a Boolean variable which is True in the first half of the switching cycle and false in the second and *D* is the duty ratio of the converter.

## 2.1.3 Dynamic Model of Bidirectional Full-Bridge Converter

Utilizing the state averaging method [46], [47], the dynamic model of the full-bridge converter with switching scheme represented by (2.1) can be written as:

$$L\dot{I}_{l} = -R_{L}I_{l} - V_{out} + 2V_{in}\frac{N_{2}}{N_{1}}(D+d_{0})$$

(2.2)

$$C\dot{V}_{out} = I_l - I_o. \tag{2.3}$$

Where  $V_{in}(t) \in \mathbb{R}$  is the average input voltage supplied by the battery,  $I_1(t) \in \mathbb{R}$  is the average current through the inductor L and  $R_L$  is its series resistance.  $V_{out}(t) \in \mathbb{R}$  and  $I_o(t) \in \mathbb{R}$  are output voltage and current, respectively.  $\frac{N_2}{N_1}$  is the transformer turns ratio. The term  $d_0$  represents an assumed constant disturbance within the switching.

#### 2.2 Backstepping Controller

There are two uncertainties which the bidirectional full-bridge converter system must be capable of adapting for. First, it is assumed that the battery voltage will change as the system discharges. Secondly, it is assumed that the load may also vary as the consumers vary their power consumption. In an effort to meet the input voltage requirements set by the ANPC inverter stage, a novel backstepping control scheme is developed for the bidirectional full-bridge converter stage. This controller works to maintain a fixed DC link voltage in the presence of a varying battery state of charge (SOC) and variable load. Recent works such as [5], [48] have shown that increased performance is achieved if the control scheme also compensates for an unknown disturbance within the PWM scheme, therefore this development includes the additional adaptive term to compensate for this disturbance.

#### 2.2.1 Control Objectives

A control input  $D(t) \in \mathbb{R}$  for the bidirectional full-bridge converter, with the dynamic model given in (2.2) and (2.3), is developed such that the output voltage of the

converter,  $V_{out}(t) \in \mathbb{R}$ , tracks a desired output voltage,  $V_d(t) \in \mathbb{R}$ , in the presence of an unknown complex load and a constant disturbance in the system.

#### 2.2.2 Assumptions

There are several assumptions that must be made for this controller design:

The bidirectional converter switching scheme is according to (1). Therefore the converter is always in the continuous conduction mode.

- The signals  $V_{in}(t)$ ,  $V_{out}(t)$ ,  $I_o(t)$ , and  $I_l(t)$  are measurable.

- The parameters R<sub>L</sub>, L, and C are known constants.

- The desired output voltage trajectory signal, V<sub>d</sub>(t), and its first and second derivative are bounded, V<sub>d</sub>, V<sub>d</sub>, V<sub>d</sub> ∈ L<sub>∞</sub>.

- The output current and its derivative are bounded,  $I_o(t), \dot{I}_o(t) \in \mathcal{L}_{\infty}$ .

#### 2.2.3 Controller Design

In order to meet the desired voltage, tracking error signal  $e(t) \in \mathbb{R}$  and auxiliary error signal  $\eta(t) \in \mathbb{R}$  are defined as:

$$e = V_d - V_{out} \tag{2.4}$$

$$\eta = I_d - I_l \tag{2.5}$$

Where  $I_d(t) \in \mathbb{R}$  is an auxiliary control signal which will be designed subsequently. To account for the unknown disturbance, an error signal  $\tilde{d}_0 \in \mathbb{R}$  is developed as follows:

$$\tilde{d}_0 = d_0 - \hat{d}_0 \tag{2.6}$$

where  $\hat{d}_0 \in \mathbb{R}$  is the estimated disturbance which will be defined subsequently.

Taking the time derivative of (2.4) and (2.5) and substituting for  $\dot{V}_{out}$  and  $\dot{I}_l$  from (2.2) and (2.3), and multiplying by *C* and *L* respectively, the open loop system error can be rewritten as:

$$C\dot{e} = C\dot{V}_d - I_d + \eta + I_o \tag{2.7}$$

$$L\dot{\eta} = L\dot{I}_d + R_l I_l + V_{out} - 2V_{in} \frac{N_2}{N_1} (D + d_o).$$

(2.8)

From the subsequent stability analysis, the auxiliary controller,  $I_d(t)$ , and the duty ratio of the PWM control signal, D(t), are defined as in follows:

$$I_d \triangleq C\dot{v}_d + k_1 e + I_o \tag{2.9}$$

$$D \triangleq \frac{1}{V_{in}\frac{N_2}{N_1}} \left[ W_1 + e + k_2\eta + k_3 sgn(\eta) - V_{in}\frac{N_2}{N_1}\hat{d}_0 \right]$$

(2.10)

where

$$W_1 = LC\ddot{V}_d + k_1 L\dot{V}_d + \frac{k_1 L(I_o - I_l)}{c} + R_l I_l + V_{out}.$$

(2.11)

where  $k_1, k_2, k_3 \in \mathbb{R}^+$  are controller gains. The parameter update law for the unknown disturbance is defined as follows:

$$\dot{\hat{d}}_o \triangleq -k_4 \eta V_{in} \frac{N_2}{N_1} \tag{2.12}$$

where  $k_4 \in \mathbb{R}^+$  is a positive gain. Substituting (2.7) and (2.8) for  $I_d(t)$  and D(t) from (2.9) and (2.10) give us the following closed loop system error equations:

$$C\dot{e} = -k_1 e + \eta \tag{2.13}$$

$$L\dot{\eta} = L\dot{I}_o - e - k_2\eta - k_3sgn(\eta) - V_{in}\frac{N_2}{N_1}\tilde{d}_o.$$

(2.14)

#### 2.2.4 Stability Analysis

*Theorem 1:* Using the closed loop error system equations found in (2.13) and (2.14), the error signals defined in (2.4) and (2.5) are regulated as follows:

$$e(t), \eta(t) \to 0 \text{ as } t \to \infty$$

(2.15)

when the following gain condition is met

$$k_3 > L\dot{I}_o.$$

(2.16)

*Proof:* A non-negative scalar function,  $S(t) \in \mathbb{R}$  is defined in (2.16).

$$S = \frac{1}{2}Ce^2 + \frac{1}{2}L\eta^2 + \frac{1}{2}k_4^{-1}\tilde{d}_0^2$$

(2.17)

Taking the derivative of (2.17) with respect to time and substituting for the closed loop error signals from (2.13) and (2.14), the expression in (2.18) is obtained for time derivative of S(t) where (2.12) is also utilized.

$$\dot{S} = -k_1 e^2 - k_2 \eta^2 - k_3 |\eta| + \eta L \dot{I}_o.$$

(2.18)

The expression in (2.18) can be upper bounded as follows:

$$\dot{S} \le -k_1 e^2 - k_2 \eta^2 - (k_3 - L\dot{I}_o) |\eta|.$$

(2.19)

Assuming that the control gain  $k_3$  is selected as stated in (2.16), then (2.19) can be further simplified as:

$$\dot{S} \le -k_1 e^2 - k_2 \eta^2 \tag{2.20}$$

From (2.17) and (2.20) it is clear that  $e(t), \eta(t), \tilde{d}_0 \in \mathcal{L}_\infty$  and that  $e(t), \eta(t) \in \mathcal{L}_2$ . From (2.4) and by considering that  $V_d(t) \in \mathcal{L}_\infty$ , therefore  $V_{out}(t) \in \mathcal{L}_\infty$ . Then, from (2.9) and assuming  $I_o(t), \dot{V}_d(t) \in \mathcal{L}_\infty$ , it is clear that  $I_d(t) \in \mathcal{L}_\infty$ , hence from (2.5) we can see that  $I_l(t) \in \mathcal{L}_\infty$  .From (2.13) and  $e(t), \eta(t) \in \mathcal{L}_\infty$  it is clear that  $\dot{e}(t) \in \mathcal{L}_\infty$ . From (2.6) and because  $d_0(t), \tilde{d}_0(t) \in \mathcal{L}_\infty$  it is clear that  $\hat{d}_0(t) \in \mathcal{L}_\infty$ . From (2.11), it can be shown that  $W_1(t) \in \mathcal{L}_\infty$  because  $\ddot{v}_d(t), \dot{v}_d(t), I_l(t), V_{out}(t) \in \mathcal{L}_\infty$ . Additionally, from (2.10) it is clear that  $D(t) \in \mathcal{L}_\infty$ . Therefore we have proved that all signals in the closed loop are bounded. Now we will prove that the error signals, e(t) and  $\eta(t)$ , converge to zero as  $t \rightarrow \infty$ . From (2.13) and  $e(t), \eta(t), \in \mathcal{L}_\infty$  it is clear $\dot{e}(t) \in \mathcal{L}_\infty$ . From (2.14), and assuming  $\dot{I}_o(t)$   $\in \mathcal{L}_\infty$  it is clear that  $\dot{\eta}(t) \in \mathcal{L}_\infty$ . Since  $e(t), \eta(t) \in \mathcal{L}_\infty \cap \mathcal{L}_2$  and  $\dot{e}(t), \dot{\eta}(t) \in \mathcal{L}_\infty$ , according to the Barbalat's Lemma [49] it is clear that  $e(t), \eta(t) \to 0$  as  $t \to \infty$ .

#### 2.3 Simulation Results

To validate the system design and evaluate the performance of the developed controller numerical simulation using PLECS software is completed. The simulation parameters are presented in Table 2.

| Parameter            | Value        | Unit | Parameter    | Value       | Unit |

|----------------------|--------------|------|--------------|-------------|------|

| V <sub>in</sub>      | 240          | V    | C3=C4        | 200         | μF   |

|                      | – .05ramp(t) |      |              |             |      |

| V <sub>d</sub>       | 340          | V    | K1           | 4           | -    |

| F <sub>sw_Conv</sub> | 50           | KHz  | K2           | 2           |      |

| (Converter           |              |      |              |             |      |

| Switching            |              |      |              |             |      |

| frequency)           |              |      |              |             |      |

| F <sub>sw_Inv</sub>  | 20           | KHz  | K3           | .01         | -    |

| (Inverter            |              |      |              |             |      |

| Switching            |              |      |              |             |      |

| frequency)           |              |      |              |             |      |

| L                    | 100          | μH   | K4           | 1           |      |

| С                    | 1            | mF   | $Z_1$ (Load1 | 3.9 + j1.88 | Ω    |

|                      |              |      | impedance)   |             |      |

| C1=C2                | 2            | mF   | $Z_2$ (Load2 | 13 + j6.4   | Ω    |

|                      |              |      | impedance)   |             |      |

Table 2.1 V2G System Parameters

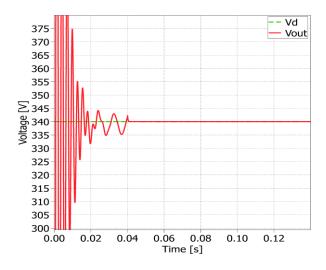

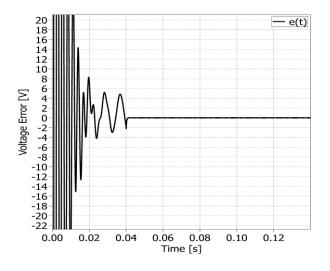

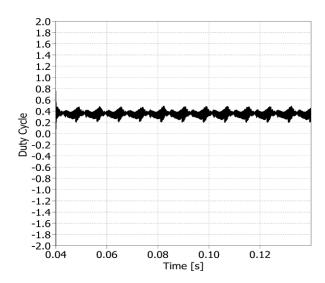

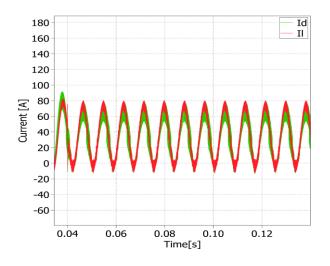

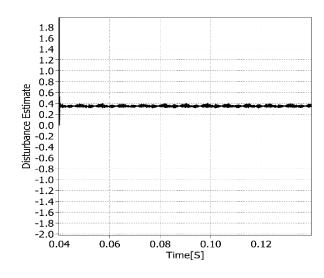

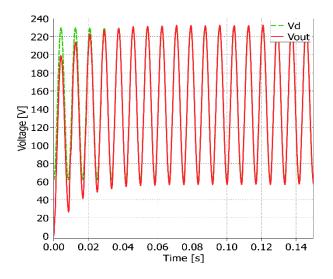

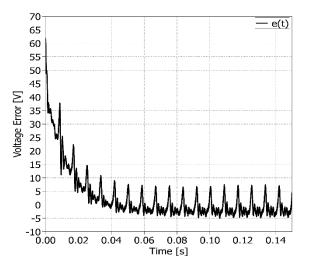

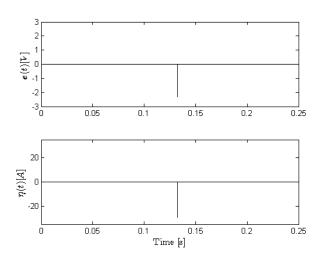

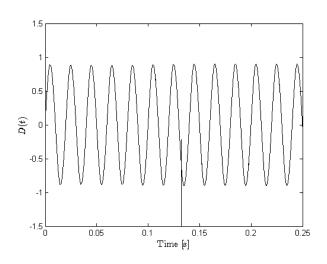

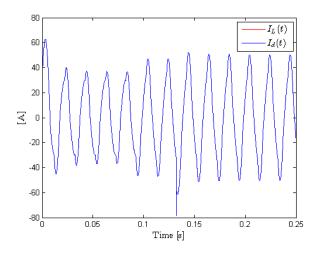

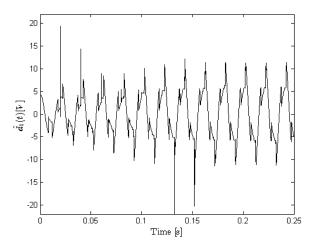

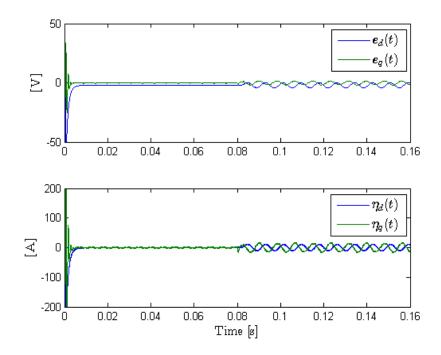

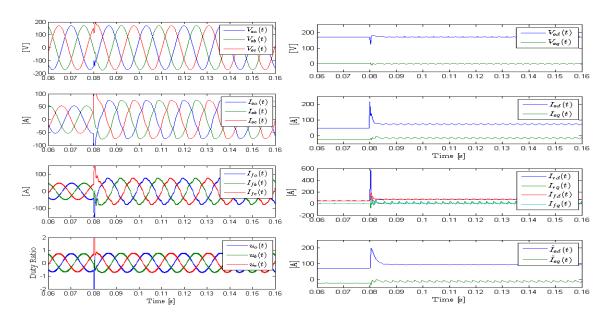

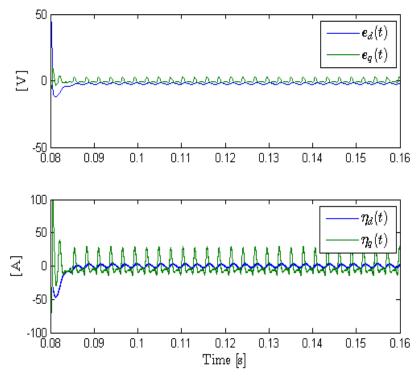

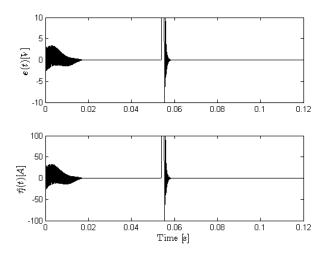

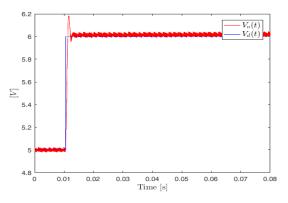

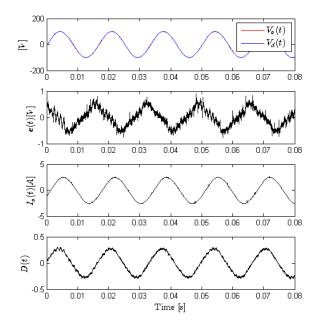

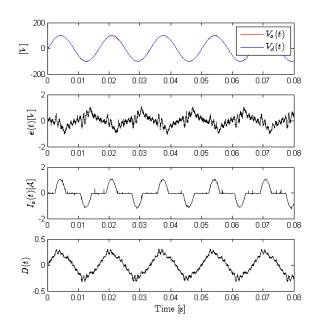

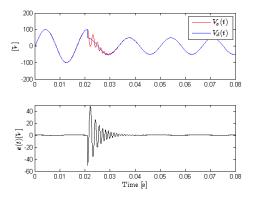

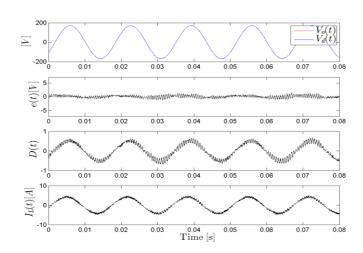

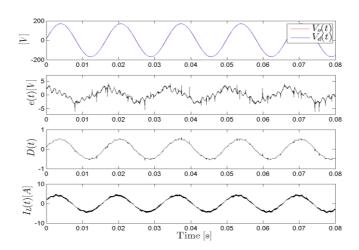

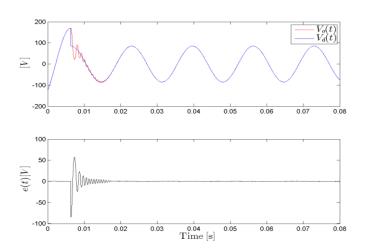

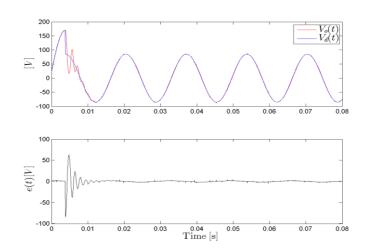

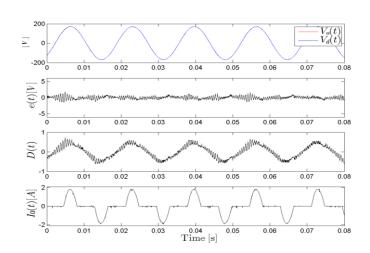

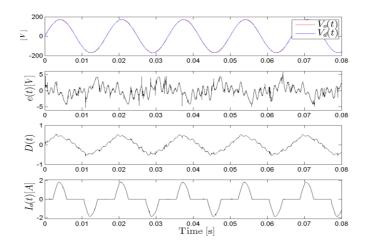

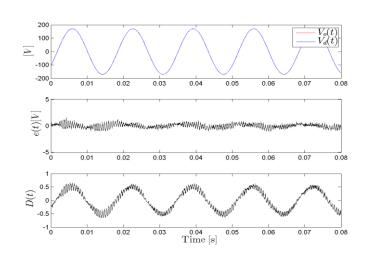

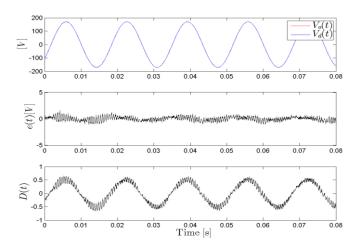

To facilitate the simulation, the converter was operated with a fixed duty cycle for t < 0.04 [*sec*]. After this the duty cycle generated by the controller was applied to the converter. At t = 0.08 [sec.] the simulated load changes from  $Z_1 = 3.9 + j1.88 [\Omega]$  to  $Z_2 = 13 + j6.4 [\Omega]$ . To simulate changes in the battery SOC, the input voltage to the converter stage  $V_{in}$  reduces linearly with a slope of 0.05[V/S] from its initial value, 240[V]. Fig. 2.4 shows the tracking performance of the converter. Signals e(t) and duty cycle, D(t), are seen in Fig. 2.5 and 2.6 respectively. From these figures it is clear that the converter and its developed controller work well within the desired parameters in closed loop control, achieving an output voltage 340 [V] with a very low ripples. Comparing the inductor current with its desired value  $I_a$  in Fig. 2.7, it can be seen that the converter is always in the continuous conduction mode and that control is maintained even when the inductor current is negative. Fig. 2.8 shows that the estimated disturbance in duty ratio converges to a constant value.

Fig. 2.4 Output voltage,  $V_{out}(t)$ , and the desired voltage,  $V_d(t)$ , of Bidirectional Full-Bridge

#### Converter.

Fig. 2.5 Voltage tracking error, e(t) of Bidirectional Full-Bridge Converter.

Fig. 2.6 Control duty cycle, D(t), of Bi-Directional Full-Bridge Converter.

Fig. 2.7 Bidirectional Full-Bridge Converter Inductor Current.

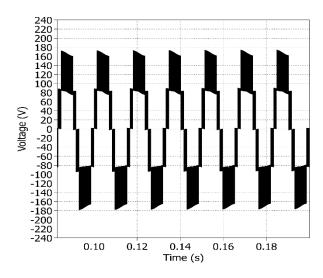

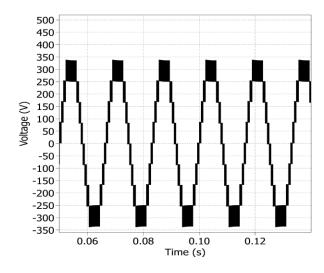

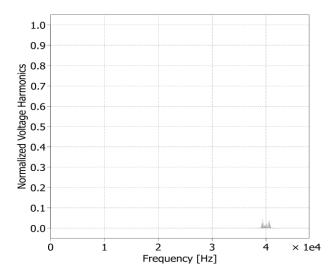

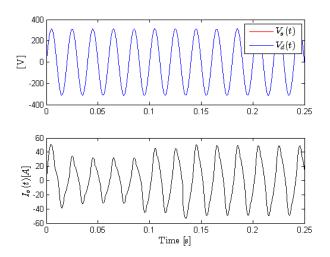

The level-shifted four-carrier PWM scheme with unity modulation index and 20 kHz carrier frequency ( $f_{tri}$ ) is selected for system level simulation of the ANPC inverter. The line-to-neutral and line-to-line output voltage of the inverter are shown in Fig. 2.9 and 2.10 respectively. The normalized Fourier coefficients of the line-to-line output voltage are illustrated in Fig. 2.11. As can be seen in Fig. 2.11, the individual voltage distortion for  $f < 2f_{tri} = 40$  kHz is less than 0.03% which is well within the harmonic limits set by IEEE

519. Implementation of a simple LC filter at the output fulfills total voltage distortion limits of IEEE 519 and also removes high frequency harmonics around  $f = 2f_{tri}$ .

Fig. 2.8 Bidirectional Full-Bridge Converter Estimated Disturbance.

Fig. 2.9 ANPC Inverter Line to Neutral Output Voltaege.

Fig. 2.10 ANPC Inverter Line to Line Output Voltaege.

Fig. 2.11 Output Voltage Normalized Harmonics with Respect to Fundamental.

# 2.4 Summary

A typical DC:AC conversion system consists of two stages, a DC:DC converter to generate the necessary bus voltage followed by an inverter which generates the desired AC output. A modification of this system is proposed for the purpose of reducing switching losses. The proposed two-stage system consists of a buck converter which produces a